# Runtime Monitoring for Dependable Hardware Design

Zur Erlangung des akademischen Grades eines

Doktors der Ingenieurwissenschaften

von der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

genehmigte

Dissertation

von

### Arunkumar Vijayan

aus Pandalam, India

Tag der mündlichen Prüfung: 06.06.2019

Erster Gutachter:Prof. Dr. Mehdi B. Tahoori, KITZweiter Gutachter:Prof. Krishnendu Chakrabarty, Duke University

### Acknowledgement

First of all, I would like to express my immense gratitude to my advisor Prof. Mehdi Tahoori for his relentless support throughout my PhD. His guidance helped me in overcoming several obstacles in my research. In addition, I am extremely grateful to my co-advisor Prof. Krishnendu Chakrabarty in supporting me throughout my research with guidance and motivation.

I would like to thank all of my colleagues in the Chair of Dependable Nano Computing at Karlsruhe Institute of Technology for their technical as well as personal support. I especially thank Dr. Saman Kiamehr for his invaluable support as a friend and a mentor. I would also like to thank Dr. Fabian Oboril, Dr. Mojtaba Ebrahimi and Dr. Farshad Firouzi for their contributions to my research and for the numerous technical discussions we had.

Words cannot express my thankfulness to my wonderful colleagues Sarath Mohanachandran, Dr. Mohammad Saber Golanbari, Dr. Anteneh Gebregiorgis, Dr. Rajendra Bishnoi and Samir Ben Dodo who were with me almost throughout my journey with their continuous support in personal and professional life.

I would also like to thank Ms. Iris Schroeder-Piepka for her friendly support and also for handling all the required documents during the entire PhD. Along with that, I thank Ms. Audrey Bohlinger who helped a lot with the paperwork in the final months of my PhD.

Nothing would have been possible without the love and support of three special people in my life; my mother Geetha, my father Vijayan and my wife Amitha. I am indebted to them for the sacrifices they have made to see me achieve this goal.

Arunkumar Vijayan Kleinbachstr. 19a 76227 Karlsruhe

Hiermit erkläre ich an Eides statt, dass ich die von mir vorgelegte Arbeit selbstständig verfasst habe, dass ich die verwendeten Quellen, Internet-Quellen und Hilfsmittel vollständig angegeben haben und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen - die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

> Karlsruhe, April 2019 Arunkumar Vijayan

### Abstract

With technology scaling advancement and globalization of integrated circuit (IC) manufacturing, a host of vulnerabilities affect dependability of computing hardware. Each integrated circuit chip is born with a unique personality due to process variations and grows uniquely due to operating conditions, workload and environment. Hence, design-time solutions for dependability, based on deterministic models, are no longer sufficient for ICs fabricated at nanoscale technology nodes. There is a need for runtime analysis of the state of a system and adoption of appropriate mitigation actions to ensure dependability.

Transistors are prone to workload-dependent aging phenomena that increase delay in circuit paths leading to false computations. In addition, specific workloads can induce accelerated aging leading to reduction in reliable lifetime of a chip. Apart from aging, transient computational errors (soft errors) can be caused by chip exposure to radiations that can result in abnormal behavior in critical systems. The propagation or masking of such errors is dependent on the workload executed on the system. Fabricated chips can also include malicious circuits called hardware Trojans, deliberately inserted during chip design or manufacture, that can compromise security. Due to the stealthy nature of inserted malicious circuits before their activation, it is extremely difficult to verify the chip as Trojan-free.

The complexity of these dependability issues makes simple dependability modeling and mitigation inefficient. This complexity arises from various sources including design (technology, device, circuit and architecture) parameters, fabrication parameters, runtime workload and environment. This is the motivation to explore machine learning and runtime methods that can potentially deal with such complexities.

In this thesis, we propose solutions to ensure dependable operation of computing hardware under different workload and environmental conditions. We devise machine learning techniques to model, monitor and mitigate various dependability effects. Different learning methods are used to identify low cost workload observables and to build prediction models that correlate the workload observables with dependability metrics corresponding to reliability and security attributes. We also developed low cost hardware monitoring circuits that can capture the workload observables during runtime with lower area and power overheads. In contrast to the state-of-the-art techniques exploiting micro-architectural observables for monitoring, we explore the potential of workload characterization at logic level of hardware abstraction. We identify better logic level features to enable fine-grained runtime monitoring. This logic-level analysis also comes with several knobs to tune for higher prediction accuracy and lower overheads.

We experimented this philosophy of identifying logic-level observables based on learning methods and implementing low cost monitors to enable adaptive mitigation of static aging, dynamic aging, radiation-induced soft errors and also to identify the activation of hardware Trojans. In this regard, we developed a prediction model to track the workload impact on aging degradation of a chip that can be used on-the-fly to decide upon mitigation techniques such as task migration, dynamic voltage and frequency scaling. This prediction model is implemented in software that potentially ranks workloads based on their aging stress severity. To ensure resilience against accelerated aging effect, we propose a monitoring hardware that monitors a subset of critical flip-flops for an accelerated aging phase of the workload and raise a flag when a timing-critical path experiences severe aging stress. We implemented a technique to

### Kurzfassung

relax the stress by the execution of a specific subroutine that exercises the critically stressed timing paths. We propose a technique to estimate the online soft-error vulnerability of memory arrays and logic cores based on the monitoring of a small set of flip-flops in the design. We also developed a method based on anomaly detection to identify workload signatures of hardware Trojan payload during runtime activation of a Trojan as a last line of defense. Based on these experiments, this thesis demonstrates the potential of advanced feature extraction at logiclevel of abstraction and learning-based prediction based on runtime data to achieve better dependability for hardware designs.

### Zusammenfassung

Mit dem Voranschreiten der Technologieskalierung und der Globalisierung der Produktion von integrierten Schaltkreisen eröffnen sich eine Fülle von Schwachstellen bezüglich der Verlässlichkeit von Computerhardware. Jeder Mikrochip wird aufgrund von Produktionsschwankungen mit einem einzigartigen Charakter geboren, welcher sich durch seine Arbeitsbedingungen, Belastung und Umgebung in individueller Weise entwickelt. Daher sind deterministische Modelle, welche zur Entwurfszeit die Verlässlichkeit prognostizieren, nicht mehr ausreichend um Integrierte Schaltkreise mit Nanometertechnologie sinnvoll abbilden zu können. Der Bedarf einer Laufzeitanalyse des Zustandes steigt und mit ihm die notwendigen Maßnahmen zum Erhalt der Zuverlässigkeit. Transistoren sind anfällig für auslastungsbedingte Alterung, die die Laufzeit der Schaltung erhöht und mit ihr die Möglichkeit einer Fehlberechnung. Hinzu kommen spezielle Abläufe die das schnelle Altern des Chips befördern und somit seine zuverlässige Lebenszeit reduzieren. Zusätzlich können strahlungsbedingte Laufzeitfehler (Soft-Errors) des Chips abnormales Verhalten kritischer Systeme verursachen. Sowohl das Ausbreiten als auch das Maskieren dieser Fehler wiederum sind abhängig von der Arbeitslast des Systems. Fabrizierten Chips können ebenfalls vorsätzlich während der Produktion boshafte Schaltungen, sogenannte Hardwaretrojaner, hinzugefügt werden. Dies kompromittiert die Sicherheit des Chips. Da diese Art der Manipulation vor ihrer Aktivierung kaum zu erfassen ist, ist der Nachweis von Trojanern auf einem Chip direkt nach der Produktion extrem schwierig.

Die Komplexität dieser Verlässlichkeitsprobleme machen ein einfaches Modellieren der Zuverlässigkeit und Gegenmaßnahmen ineffizient. Sie entsteht aufgrund verschiedener Quellen, eingeschlossen der Entwicklungsparameter (Technologie, Gerät, Schaltung und Architektur), der Herstellungsparameter, der Laufzeitauslastung und der Arbeitsumgebung. Dies motiviert das Erforschen von maschinellem Lernen und Laufzeitmethoden, welche potentiell mit dieser Komplexität arbeiten können.

In dieser Arbeit stellen wir Lösungen vor, die in der Lage sind, eine verlässliche Ausführung von Computerhardware mit unterschiedlichem Laufzeitverhalten und Arbeitsbedingungen zu gewährleisten. Wir entwickelten Techniken des maschinellen Lernens um verschiedene Zuverlässigkeitseffekte zu modellieren, zu überwachen und auszugleichen. Verschiedene Lernmethoden werden genutzt, um günstige Überwachungspunkte zur Kontrolle der Arbeitsbelastung zu finden. Diese werden zusammen mit Zuverlässigkeitsmetriken, aufbauend auf Ausfallsicherheit und generellen Sicherheitsattributen, zum Erstellen von Vorhersagemodellen genutzt. Des Weiteren präsentieren wir eine kosten-optimierte Hardwaremonitorschaltung, welche die Überwachungspunkte zur Laufzeit auswertet. Im Gegensatz zum aktuellen Stand der Technik, welcher mikroarchitektonische Überwachungspunkte ausnutzt, evaluieren wir das Potential von Arbeitsbelastungscharakteristiken auf der Logikebene der zugrundeliegenden Hardware. Wir identifizieren verbesserte Features auf Logikebene um feingranulare Laufzeitüberwachung zu ermöglichen. Diese Logikanalyse wiederum hat verschiedene Stellschrauben um auf höhere Genauigkeit und niedrigeren Overhead zu optimieren.

Wir untersuchten die Philosophie, Überwachungspunkte auf Logikebene mit Hilfe von Lernmethoden zu identifizieren und günstigen Monitore zu implementieren um eine adaptive Vorbeugung gegen statisches Altern, dynamisches Altern und strahlungsinduzierte Soft-Errors zu schaffen und zusätzlich die Aktivierung von Hardwaretrojanern zu erkennen.

#### Kurzfassung

Diesbezüglich haben wir ein Vorhersagemodell entworfen, welches den Arbeitslasteinfluss auf alterungsbedingte Verschlechterungen des Chips mitverfolgt und dazu genutzt werden kann, dynamisch zur Laufzeit vorbeugende Techniken, wie Task-Mitigation, Spannungs- und Frequenzskalierung zu benutzen.

Dieses Vorhersagemodell wurde in Software implementiert, welche verschiedene Arbeitslasten aufgrund ihrer Alterungswirkung einordnet. Um die Widerstandsfähigkeit gegenüber beschleunigter Alterung sicherzustellen, stellen wir eine Überwachungshardware vor, welche einen Teil der kritischen Flip-Flops beaufsichtigt, nach beschleunigter Alterung Ausschau hält und davor warnt, wenn ein zeitkritischer Pfad unter starker Alterungsbelastung steht. Wir geben die Implementierung einer Technik zum Reduzieren der durch das Ausführen spezifischer Subroutinen auftretenden Belastung von zeitkritischen Pfaden. Zusätzlich schlagen wir eine Technik zur Abschätzung von online Soft-Error-Schwachstellen von Speicherarrays und Logikkernen vor, welche auf der Überwachung einer kleinen Gruppe Flip-Flops des Entwurfs basiert.

Des Weiteren haben wir eine Methode basierend auf Anomalieerkennung entwickelt, um Arbeitslastsignaturen von Hardwaretrojanern während deren Aktivierung zur Laufzeit zu erkennen und somit eine letzte Verteidigungslinie zu bilden. Basierend auf diesen Experimenten demonstriert diese Arbeit das Potential von fortgeschrittener Feature-Extraktion auf Logikebene und lernbasierter Vorhersage basierend auf Laufzeitdaten zur Verbesserung der Zuverlässigkeit von Harwareentwürfen.

## Contents

| Ał | tract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | viii                                                   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Kı | zfassung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | x                                                      |

| Co | tents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xiii                                                   |

| GI | ssary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | xvi                                                    |

| Li | of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xix                                                    |

|    | of Tables<br>of own publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xxi<br>xxiv                                            |

| 1  | Introduction1.1Problem statement and objective1.2Contribution of this Thesis1.3Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 3                                                    |

| 2  | Background         2.1       Dependability Challenges: Overview of Hardware Reliability and Security         2.2       Reliability Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\begin{array}{cccccccccccccccccccccccccccccccccccc$   |

| 3  | <ul> <li>2.5 Summary</li> <li>Dynamic Aging Monitoring and Delay Prediction</li> <li>3.1 Overview</li> <li>3.2 Introduction, Motivation and Contributions</li> <li>3.3 Related Work</li> <li>3.4 Proposed Methodology</li> <li>3.5 Offline Correlation Analysis and Prediction Model Generation</li> <li>3.5.1 Aging-Induced Delay Degradation and SP Extraction</li> <li>3.5.2 Predictor Training Using Support-Vector Machines</li> <li>3.5.3 Representative Flip-Flop Selection (Space Sampling)</li> <li>3.5.4 Time Complexity of Flip-Flop Selection Methods</li> <li>3.5.5 Time Sampling</li> <li>3.6 Run-time Stress Monitoring</li> </ul> | <b>29</b> . 29 . 31 . 33 . 33 . 33 . 35 . 36 . 39 . 39 |

|   | 3.7         | Experimental Results                                                                                      | 41       |  |  |  |

|---|-------------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|

|   |             |                                                                                                           | 42       |  |  |  |

|   |             |                                                                                                           | 42       |  |  |  |

|   |             | 8                                                                                                         | 42       |  |  |  |

|   |             | J.                                                                                                        | 44       |  |  |  |

|   |             | * 0 0                                                                                                     | 44       |  |  |  |

|   | 3.8         |                                                                                                           | 45       |  |  |  |

|   | <b>J</b> .0 | Summary                                                                                                   | 40       |  |  |  |

| 4 | Stat        | Static Aging Monitoring and Mitigation                                                                    |          |  |  |  |

|   | 4.1         | Overview                                                                                                  | 47       |  |  |  |

|   | 4.2         | Introduction, motivation and contributions                                                                | 47       |  |  |  |

|   | 4.3         | Related Work                                                                                              | 49       |  |  |  |

|   | 4.4         | Proposed Methodology                                                                                      | 50       |  |  |  |

|   | 4.5         |                                                                                                           | 52       |  |  |  |

|   | -           |                                                                                                           | 52       |  |  |  |

|   |             | U U                                                                                                       | 54       |  |  |  |

|   | 4.6         |                                                                                                           | 59       |  |  |  |

|   | 1.0         |                                                                                                           | 59       |  |  |  |

|   |             | 0 0 0                                                                                                     | 60       |  |  |  |

|   | 4.7         |                                                                                                           | 62       |  |  |  |

|   | 4.1         | 1                                                                                                         |          |  |  |  |

|   |             |                                                                                                           | 64       |  |  |  |

|   |             | 8                                                                                                         | 65<br>65 |  |  |  |

|   |             |                                                                                                           | 65       |  |  |  |

|   | 4.0         |                                                                                                           | 66       |  |  |  |

|   | 4.8         | Summary                                                                                                   | 66       |  |  |  |

| 5 | Soft        | E-Error Vulnerability Prediction                                                                          | 67       |  |  |  |

|   | 5.1         | -                                                                                                         | 67       |  |  |  |

|   | 5.2         |                                                                                                           | 67       |  |  |  |

|   | 5.3         |                                                                                                           | 69       |  |  |  |

|   | 5.4         |                                                                                                           | 71       |  |  |  |

|   | 5.5         |                                                                                                           | 72       |  |  |  |

|   | 0.0         |                                                                                                           | 73       |  |  |  |

|   |             |                                                                                                           |          |  |  |  |

|   |             |                                                                                                           | 75<br>76 |  |  |  |

|   | FC          | 0                                                                                                         | 76<br>70 |  |  |  |

|   | 5.6         | J.                                                                                                        | 79       |  |  |  |

|   | 5.7         | 1                                                                                                         | 80       |  |  |  |

|   |             |                                                                                                           | 80       |  |  |  |

|   |             | 1                                                                                                         | 80       |  |  |  |

|   |             |                                                                                                           | 81       |  |  |  |

|   |             |                                                                                                           | 83       |  |  |  |

|   |             | 5.7.5 Overheads $\ldots$ | 84       |  |  |  |

|   |             | 5.7.6 Optimization Prospects                                                                              | 85       |  |  |  |

|   | 5.8         | Summary                                                                                                   | 86       |  |  |  |

| 6 | Uar         | durara Traian Datastian                                                                                   | 87       |  |  |  |

| 6 |             | 5                                                                                                         |          |  |  |  |

|   | 6.1         |                                                                                                           | 87       |  |  |  |

|   | 6.2         | Introduction, motivation and contributions                                                                | 87       |  |  |  |

|   | 6.3         | Preliminaries and Related Work                                                                            | 88       |  |  |  |

|     | 6.4             | Proposed Methodology |                                                                      |     |

|-----|-----------------|----------------------|----------------------------------------------------------------------|-----|

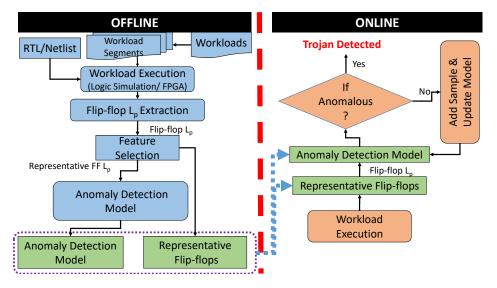

|     |                 | 6.4.1                | Offline Characterization and Construction of Anomaly-Detection Model | 93  |

|     |                 | 6.4.2                | Online Monitoring and Incremental Prediction                         | 95  |

|     | 6.5             | Experi               | mental Results                                                       | 97  |

|     |                 | 6.5.1                | Experimental Setup                                                   | 98  |

|     |                 | 6.5.2                | Implementation of Different Trojans                                  | 98  |

|     |                 | 6.5.3                | Trojan Detection Accuracy                                            | 101 |

|     |                 | 6.5.4                | Representative Flip-flop Selection                                   | 103 |

|     |                 | 6.5.5                | Overheads                                                            | 103 |

|     |                 | 6.5.6                | Limitations of the proposed approach                                 | 104 |

|     | 6.6             | Summ                 | ary                                                                  | 105 |

| 7   | Con             | clusion              |                                                                      | 107 |

|     | 7.1             | Summ                 | ary and conclusion                                                   | 107 |

| Bil | Bibliography 10 |                      |                                                                      | 109 |

# Glossary

| 3PIP                           | Thid-party Intellectual Property                                                                             |

|--------------------------------|--------------------------------------------------------------------------------------------------------------|

| ACE<br>ATPG                    | Architecturally Correct Execution<br>Automatic Test Pattern Generation                                       |

| BTI                            | Bias Temperature Instability                                                                                 |

| CMOS                           | Complementary Metal Oxide Semiconductor                                                                      |

| DVFS                           | Dynamic Voltage and Frequency Scaling                                                                        |

| FF<br>FIT<br>FPGA              | flip flop<br>Failure in Time<br>Field Programmable Gate Array                                                |

| GBM                            | Gradient Boosting Machine                                                                                    |

| HCI                            | Hot Carrier Injection                                                                                        |

| ISA                            | Instruction Set Architecture                                                                                 |

| LUT<br>LVF                     | Look-Up-Tables<br>Logic Vulnerability Factor                                                                 |

| MTTF<br>MVF                    | Mean Time To Failure<br>Memory Vulnerability Factor                                                          |

| overfitting                    | situation in which predictor model fits to noise in training data.                                           |

| RTL                            | Register Transfer Level                                                                                      |

| SER<br>SoC<br>SP<br>STA<br>SVM | Soft Error Rate<br>System-on-Chip<br>Signal Probability<br>Static Timing Analysis<br>Support Vector Machines |

| TDDB                           | Time Dependent Dielectric Breakdown                                                                          |

| VCD                 | Value Change Dump                                              |

|---------------------|----------------------------------------------------------------|

| VF                  | Vulnerability Factor                                           |

| VLSI                | Very-Large-Scale Integration                                   |

|                     |                                                                |

| workload            | Set of input patterns and states applied to a hardware design. |

| workload observable | Representative of the signal activity of a workload.           |

| workload phase      | A workload segment with uniform characteristics.               |

|                     |                                                                |

# List of Figures

| 1.1<br>1.2   | Illustration of complexity and performance increase with technology scaling ad-<br>vancement in microprocessors for the last four decades [1]                   | $\frac{1}{4}$ |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2.1          | Illustration of the attributes of dependability in the scope of this thesis [8]                                                                                 | 7             |

| 2.2          | Dependability threats and their causal relationship [8]                                                                                                         | 7             |

| 2.3          | NBTI Aging Models [36]                                                                                                                                          | 8             |

| 2.4          | Illustration of stress and recovery phases due to NBTI                                                                                                          | 9             |

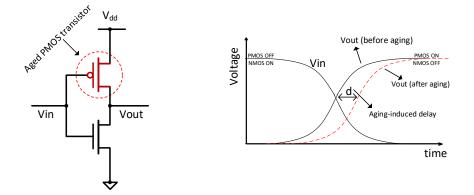

| $2.5 \\ 2.6$ | Comparison of $\Delta V_{th}$ due to D-BTI (duty cycle ( $\alpha$ )=0.5) and S-BTI Illustration of an aged CMOS inverter (INV1) and the corresponding deviation | 9             |

|              | in input-ouput characteristics in the form of an additional delay in the switching                                                                              |               |

|              | functionality.                                                                                                                                                  | 11            |

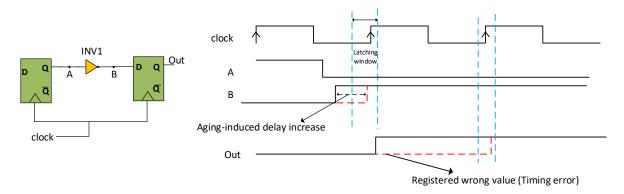

| 2.7          | Illustration of a timing violation and failure caused by an aging-induced delay increase in a timing path.                                                      | 11            |

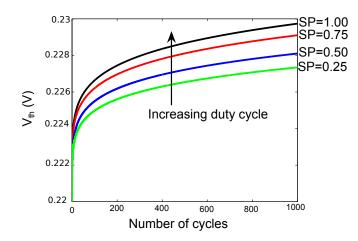

| 2.8          | The dependence of $V_{th}$ on signal probability (SP) [44] $\ldots \ldots \ldots \ldots \ldots$                                                                 | 12            |

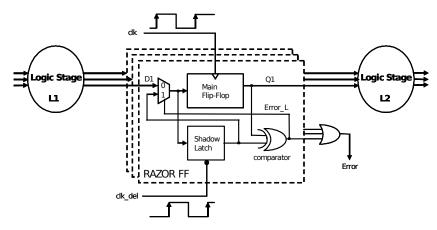

| 2.9          | Razor flipflop deployed in a timing path to monitor the delay and restore the correct value in case of a timing error [22]                                      | 13            |

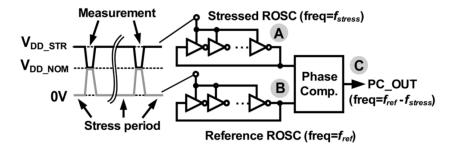

| 2.10         | Illustration of BTI monitoring by measuring the beat frequency between two                                                                                      |               |

|              | ring oscillators with one of them under stress and the other used as a reference [45].                                                                          | 13            |

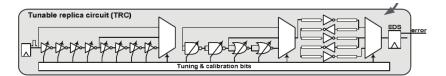

| 2.11         | Illustration of tunable replica circuits that can be tuned to match the delay of                                                                                |               |

|              | critical paths for monitoring [46]                                                                                                                              | 13            |

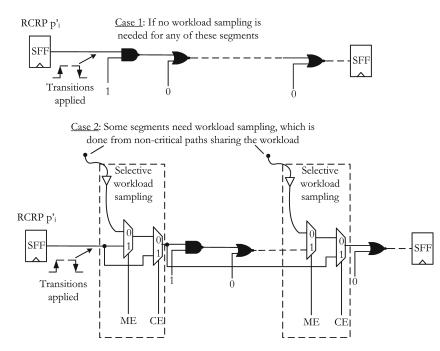

| 2.12         | Representative critical reliability paths showing representation of critical paths                                                                              |               |

|              | with or without workload sampling [47].                                                                                                                         | 14            |

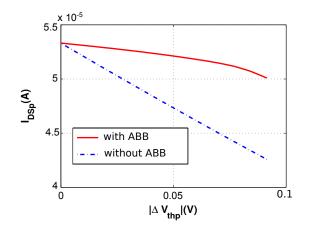

| 2.13         | Illustration of the driving strength $((I_{DSp}))$ of two aging-stressed PMOS tran-                                                                             |               |

|              | sistors, one with and the other without adaptive body biasing [20]                                                                                              | 15            |

| 2.14         | Illustration of the dependence of NBTI-induced threshold voltage degradation                                                                                    |               |

|              | on supply voltage $[19]$                                                                                                                                        | 15            |

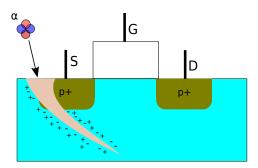

| 2.15         | Effect of alpha-particle strike on a transistor eventually leading to soft error.                                                                               | 16            |

| 2.16         | Illustration of logical masking or propagation of transient pulse from the input                                                                                |               |

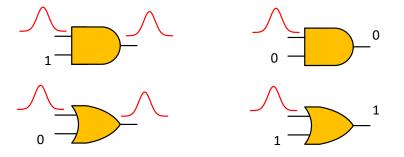

|              | of a logic gate for different input combinations.                                                                                                               | 17            |

| 2.17         | Illustration of electrical masking in the form of several stages of transient pulse                                                                             |               |

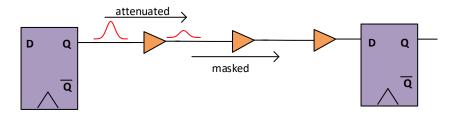

|              | attenuation.                                                                                                                                                    | 18            |

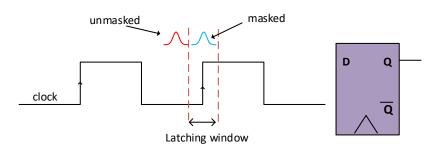

| 2.18         | Illustration of latching-window masking where the transient pulse reaches out-                                                                                  |               |

|              | side the latching window of a flipflop.                                                                                                                         | 18            |

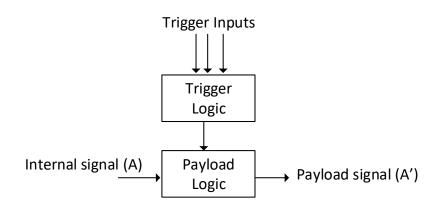

| 2.19         | Illustration of a hardware Trojan architecture with a trigger logic and payload.                                                                                | 20            |

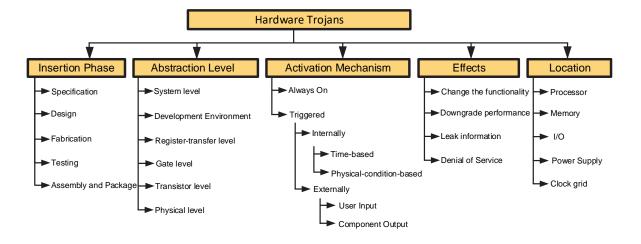

|              | Hardware Trojan Taxonomy based on different characteristics of Trojans $[61]$ .                                                                                 | 21            |

| 2.21         | Illustration of linear two-class classification with maximum-margin hyperplane                                                                                  |               |

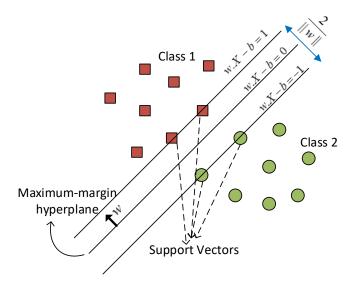

|              | in support vector machines                                                                                                                                      | 23            |

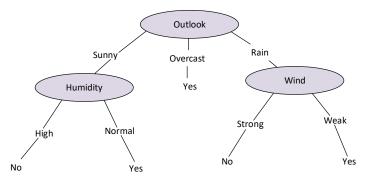

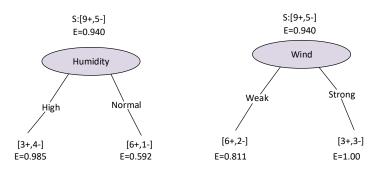

|              | Illustration of a decision tree demonstrating a two-class classification [66]                                                                                   | 24            |

|              | Illustration of information gain comparison between two attributes [66]                                                                                         | 25            |

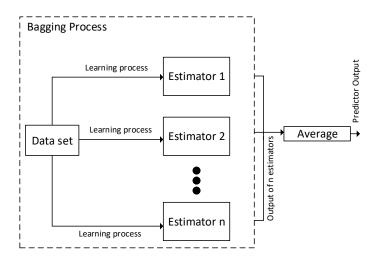

|              | Illustration of bagging technique.                                                                                                                              | 26            |

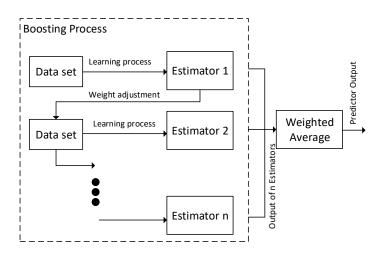

| 2.25         | Illustration of boosting technique                                                                                                                              | 26            |

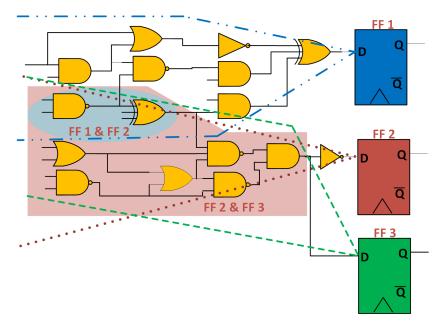

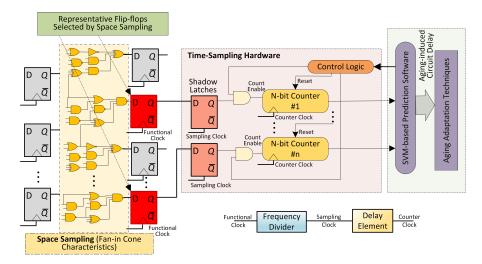

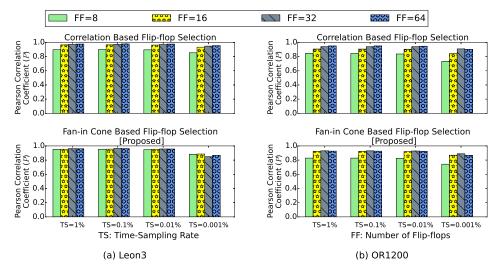

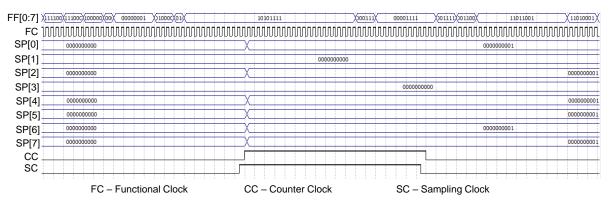

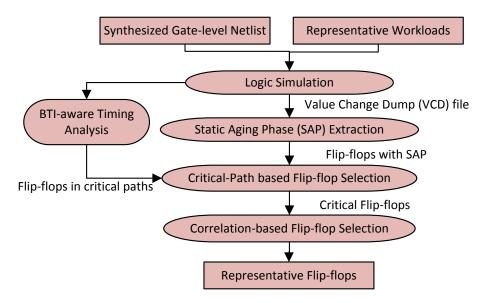

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8           | The difference in $\Delta D_{min}$ at different time points in the lifetime of a circuit<br>Flow-chart showing the steps involved in the offline characterization phase<br>Illustration of the support-vector regression model                  | 32<br>34<br>35<br>37<br>38<br>40<br>41<br>44 |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

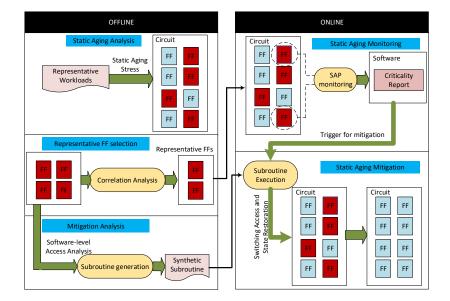

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \end{array}$ | Overview of the proposed technique                                                                                                                                                                                                              | 51<br>52<br>53<br>55                         |

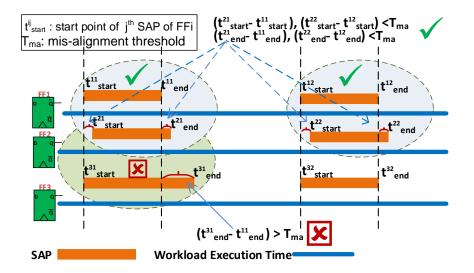

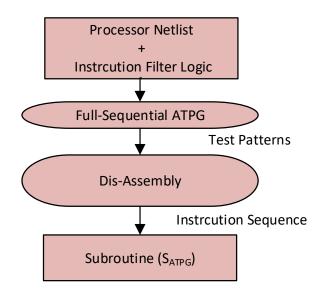

| $4.6 \\ 4.7 \\ 4.8$                                            | aging                                                                                                                                                                                                                                           | 56<br>58<br>60                               |

| 4.9                                                            | the logic gates under static aging in their forward fanout cone                                                                                                                                                                                 | 61                                           |

| 4.10                                                           | flip-flop on subsequent switching events                                                                                                                                                                                                        | 62<br>64                                     |

| 5.1                                                            | The VF of the memory arrays and sequential logic blocks in Leon3 for three MiBench workloads (experimental setup described in Section 5.7). $\dots$                                                                                             | 70                                           |

| 5.2                                                            | Variation of instruction-cache MVF of Leon3 and SP of a selected flip-flop during<br>MiBench workload execution.                                                                                                                                | 72                                           |

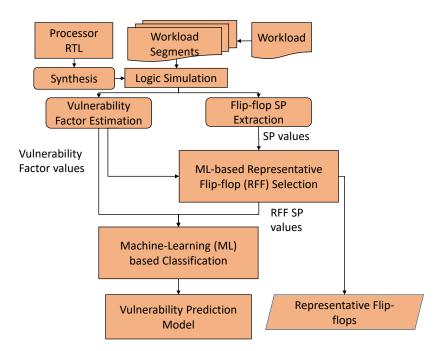

| 5.3                                                            | Offline correlation analysis and prediction model generation                                                                                                                                                                                    | 73                                           |

| 5.4                                                            | Illustration of ACE and un-ACE intervals based on the read and write access                                                                                                                                                                     | <b>F</b> 4                                   |

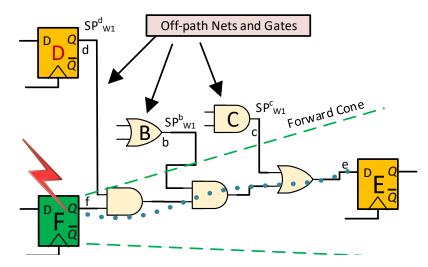

| 5.5                                                            | patterns.       Flip-flop SEU due to particle strike and error propagation scenario in a timing path.                                                                                                                                           | 74<br>75                                     |

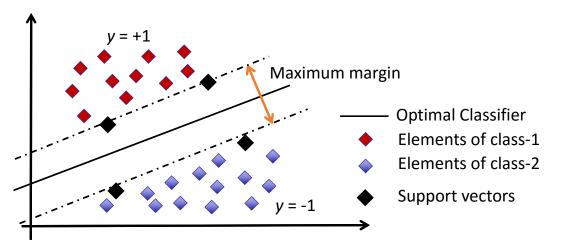

| 5.6                                                            | Illustration of two-class SVM classification.                                                                                                                                                                                                   | 77                                           |

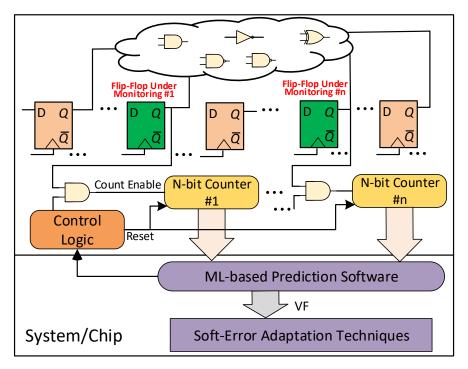

| 5.7                                                            | Illustration of flip-flop SP monitoring methodology.                                                                                                                                                                                            | 79                                           |

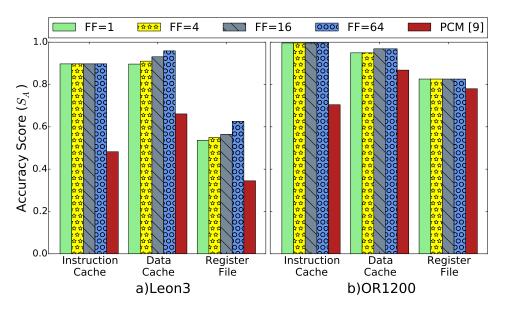

| 5.8                                                            | Comparison of accuracy scores $(S_A)$ of the proposed method with PCM (prediction based on performance counters as explained in Section 5.7.4) for (a) Leon3,                                                                                   |                                              |

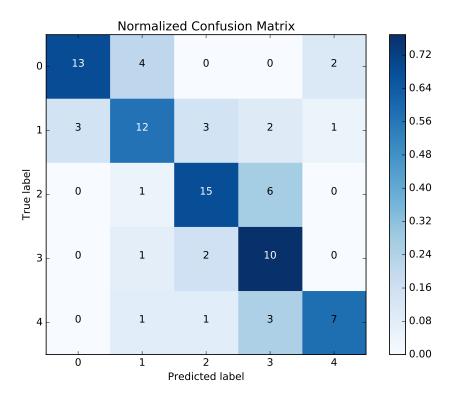

| 5.9                                                            | and (b) OR1200 memory arrays by varying number of monitored flip-flops (FF).<br>Confusion matrix showing predicted and true class labels for LVF prediction for<br>the logic core of Leon3. The number of test samples corresponding to each VF | 81                                           |

|                                                                | class is overlayed on the matrix                                                                                                                                                                                                                | 83                                           |

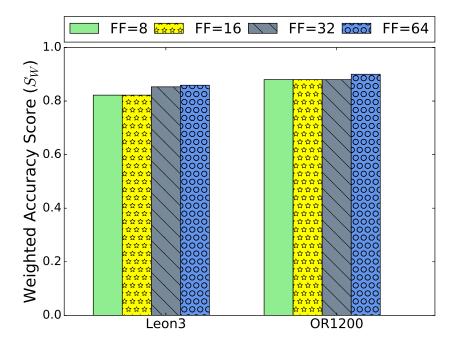

|                                                                | Variation in Weighted Accuracy Score $(S_W)$ for LVF prediction with the number<br>of representative flip-flops selected for Leon3 and OR1200 logic cores                                                                                       | 84                                           |

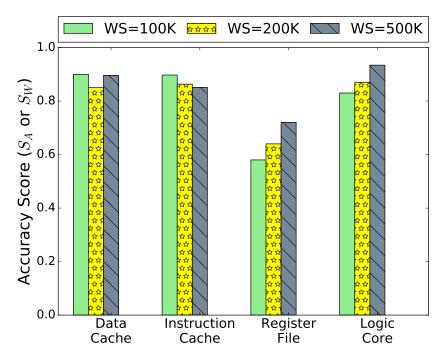

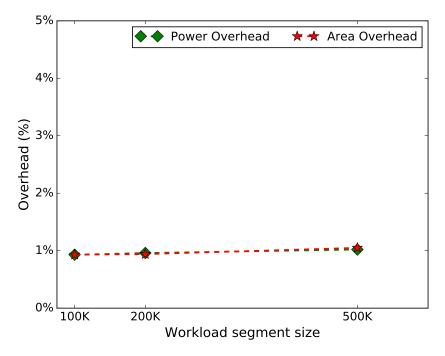

| 5.11                                                           | Variation of prediction accuracy with workload-segment size (WS) for different                                                                                                                                                                  | or                                           |

| 5.12                                                           | hardware structures in Leon3                                                                                                                                                                                                                    | $\frac{85}{86}$                              |

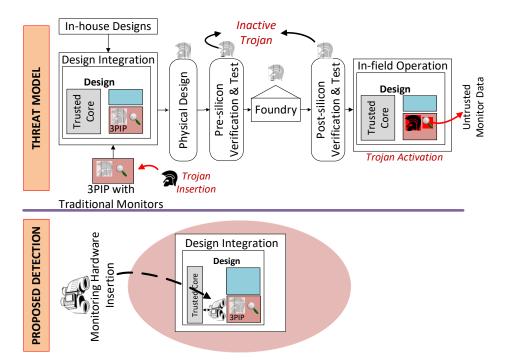

| 6.1                                                            | Threat model showing stages of Trojan insertion and activation in SoC design<br>flow along with the proposed detection technique                                                                                                                | 89                                           |

| 6.2  | Illustration of a Trojan attack scenario including manipulation of architectural- |    |

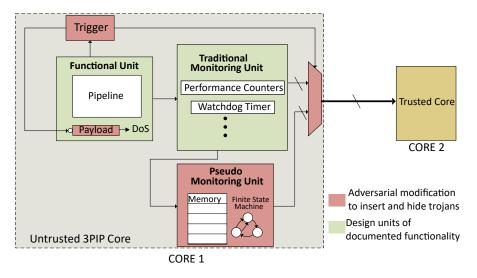

|------|-----------------------------------------------------------------------------------|----|

|      | level monitors to mask the attack.                                                | 90 |

| 6.3  | Proposed flow showing offline characterization, prediction model construction     |    |

|      | and its online deployment                                                         | 93 |

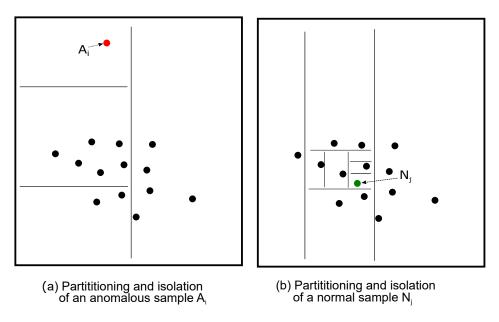

| 6.4  | Isolation properties of samples by random partitioning                            | 95 |

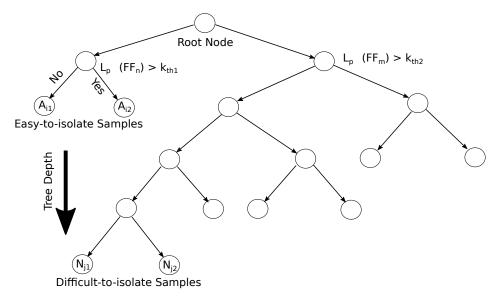

| 6.5  | Illustration of a random decision tree for isolating samples                      | 97 |

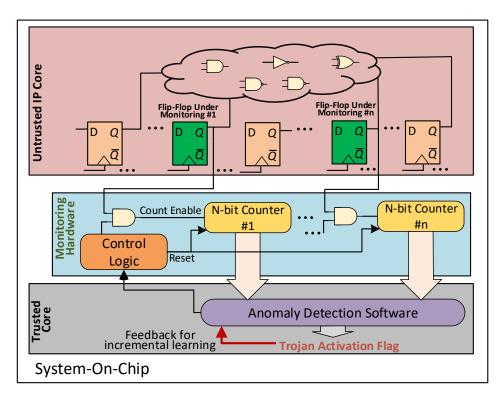

| 6.6  | Illustration of runtime monitoring hardware and anomaly detection                 | 98 |

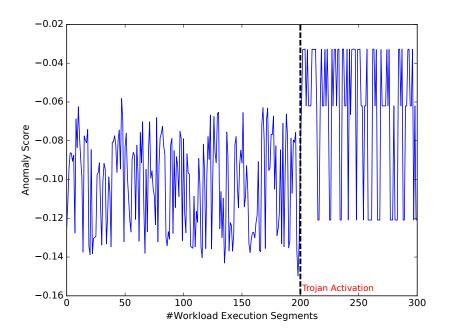

| 6.7  | Illustration of the shift in anomaly score when the NOP-insertion Trojan is       |    |

|      | activated during the execution of a susan smooth application in Leon3             | 99 |

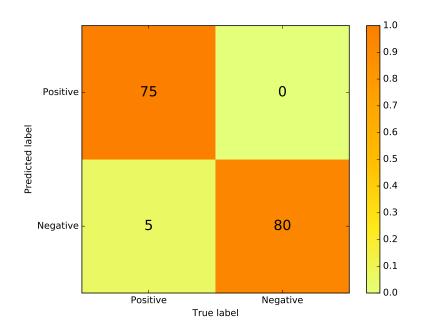

| 6.8  | The confusion matrix showing the number of true and false predictions corre-      |    |

|      | sponding to two classes, (1) positive (Trojan activated) and negative (no Trojan  |    |

|      | activated)                                                                        | 02 |

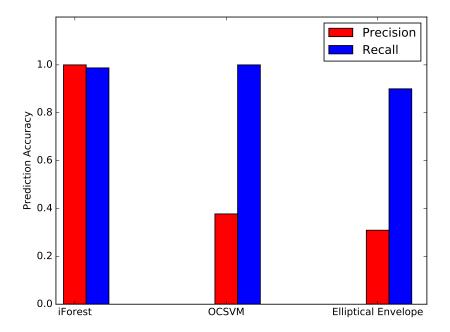

| 6.9  | Comparison of performances of different anomaly detection algorithms on Tro-      |    |

|      | jan detection.                                                                    | 03 |

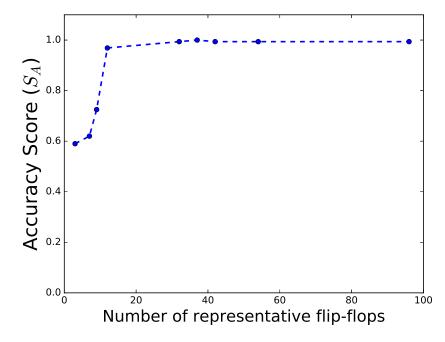

| 6.10 | The variation in prediction accuracy of Trojan activation in Leon3 with the       |    |

|      | number of flip-flops selected for monitoring.                                     | 04 |

# List of Tables

| $3.1 \\ 3.2$        | Hypothetical training set with four data samples                                                                 |     |

|---------------------|------------------------------------------------------------------------------------------------------------------|-----|

| $4.1 \\ 4.2 \\ 4.3$ | Functionality based flip-flop switching                                                                          |     |

|                     | Fabscalar with $T_{sad\_min} = 3$ million cycles                                                                 | 63  |

| 5.1                 | Hypothetical training set with five data samples                                                                 | 76  |

| 6.1                 | Functionalities covered by selected Trojans and the corresponding Trojans im-<br>plemented on different designs. | 96  |

| 6.2                 | $\label{eq:prediction} \mbox{ Prediction performance metrics of the proposed anomaly detection method } \ . \ .$ | 100 |

### List of own publications included in this thesis

### Transactions

- [24] Vijayan, Arunkumar and Koneru, Abhishek and Kiamehr, Saman and Chakrabarty, Krishnendu and Tahoori, Mehdi B, "Fine-grained aging-induced delay prediction based on the monitoring of run-time stress," in *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, 2018.

- [27] Vijayan, Arunkumar and Kiamehr, Saman and Ebrahimi, Mojtaba and Chakrabarty, Krishnendu and Tahoori, Mehdi B, "Online Soft-Error Vulnerability Estimation for Memory Arrays and Logic Cores," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2018.

- [26] Vijayan, Arunkumar and Kiamehr, Saman and Oboril, Fabian and Chakrabarty, Krishnendu and Tahoori, Mehdi B, "Workload-Aware Static Aging Monitoring and Mitigation of Timing-Critical Flip-Flops," in *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems, 2018.

- [29] Vijayan, Arunkumar and Tahoori, Mehdi B, and Chakrabarty, Krishnendu "Runtime Identification of Hardware Trojans by Feature Analysis on Gate-level Unstructured Data and Anomaly Detection," under Review in *IEEE Transactions on Information*, *Forensics and Security*, 2019.

### Conferences

- [28] Vijayan, Arunkumar and Koneru, Abhishek and Ebrahimi, Mojtaba and Chakrabarty, Krishnendu and Tahoori, Mehdi B, "Online soft-error vulnerability estimation for memory arrays," in VLSI Test Symposium (VTS), 2016.

- [25] Vijayan, Arunkumar and Kiamehr, Saman and Oboril, Fabian and Chakrabarty, Krishnendu and Tahoori, Mehdi B, "Workload-aware static aging monitoring of timingcritical flip-flops.," in Asia and South Pacific Design Automation Conference (ASP-DAC), 2017.

### List of co-author publications not included in this thesis

- Koneru, Abhishek, Arunkumar Vijayan, Krishnendu Chakrabarty, and Mehdi B. Tahoori. "Fine-grained aging prediction based on the monitoring of run-time stress using DfT infrastructure." In *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 51-58.*, 2015.

- Tahoori, Mehdi B., Abhijit Chatterjee, Krishnendu Chakrabarty, Abhishek Koneru, Arunkumar Vijayan, and Debashis Banerjee. "Self-awareness and self-learning for resiliency in real-time systems." In *IEEE 21st International On-Line Testing Symposium (IOLTS)*, pp. 128-131., 2015.

- Firouzi, Farshad, Fangming Ye, Arunkumar Vijayan, Abhishek Koneru, Krishnendu Chakrabarty, and Mehdi B. Tahoori. "Re-using BIST for circuit aging monitoring." In 20th IEEE European Test Symposium (ETS), pp. 1-2., 2015.

### **1** Introduction

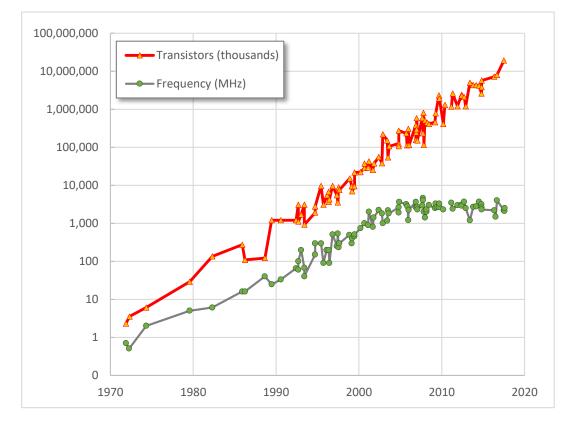

The past fifty years of semiconductor industry was an era of aggressive technology scaling reaching to sub-10 nm device sizes. The tremendous improvement in complexity (in terms of number of transistors) and performance (in terms of operating frequency) achieved for various microprocessor generations is illustrated in Fig. 1.1 [1]. According to Moore's law, the number of transistors in a semiconductor chip doubles every 18 months due to technology scaling [2]. This enables chips with increasing complex functionality, higher performance and lower perfunction cost for every new generation. For example, the central processor chip of IBM z14 processor contains 6.1 billion transistors [3] in contrast to less than a billion transistors in IBM z10 released a few years before z14 [4]. The average transistor cost reduced by  $10 \times$  due to technology scaling from 130 nm node to 14 nm node [5]. Even the latest smartphones like iPhone XS can do 5 trillion operations per second in comparison to Cray 2, the fastest supercomputer of early 1990s, capable of only 1.9 billion operations per second [6]. As a result of the increase in performance and cost reduction in implementing complex functionalities, semiconductor chips have revolutionized automotive, space, healthcare, multimedia and communication domains [7].

Figure 1.1: Illustration of complexity and performance increase with technology scaling advancement in microprocessors for the last four decades [1].

In the modern society, the ubiquity of semiconductor chips demands dependable operation for an expected lifetime. Dependability is defined as the ability to deliver trusted service [8].

With technology scaling advancement, many dependability challenges aggravate and hence, failure rate increases [9]. Smaller device sizes bring increasing variations between transistors during fabrication and also vulnerability to different environmental and runtime variations. The failure-free operation of a chip can be significantly affected by different reliability mechanisms such as device aging or radiation-induced soft errors [10]. Device aging refers to a set of degradation mechanisms that affect transistor properties, eventually leading to unexpected failures in computation. Soft errors are caused by alpha particles from packaging materials or neutrons from cosmic rays that may strike a semiconductor chip, and temporarily induce a wrong value in a memory cell or a circuit node leading to system failures. In addition to these sources of unreliabilities, several security threats have emerged due to the increasing globalization of semiconductor design and fabrication stages [11]. Each step in the design of a complex system-on-chip (SoC) is vulnerable to security issues such as inclusion of stealthy malicious logic called hardware Trojans, by third-party vendors [12]. Because of the ever increasing complexity, the verification and test efforts fall short to ensure secure operation of chips. Hence, techniques to ensure dependability of hardware designs with reliability and security as the two most relevant attributes are attaining primary focus in today's computing world.

The design-time solutions against reliability and security challenges in the context of dependable hardware design can be less efficient in the new era where chips are exposed to complex runtime variations. The rate of degradation of integrated circuits due to aging of transistors can significantly vary with the type of workload executed on them, the operating temperature, and the variations in supply voltage [13]. The vulnerability of circuits to radiation-induced soft errors also varies with the workload nature, and other runtime parameters [14]. The role of design decisions to ensure security in semiconductor chips is limited due to the threat of additional hardware inclusion at a later stage in the fabrication process [15]. Hence, in addition to design-time optimization of circuits for better reliable and secure operation, runtime monitoring is required to guide appropriate adaptation actions.

Cost-effective runtime monitoring can assist in tuning several knobs available to alleviate the impact of dependability issues. In modern-day systems, a large number of sensors and monitors are incorporated to track several runtime parameters such as power consumption and supply voltage [16]. With rising dependability requirements in various domains [17], there is a need for dependability monitors and models to make runtime decisions that can ensure dependable operation of a chip.

### 1.1 Problem statement and objective

Semiconductor chips, after fabrication, are utilized in different ways and are exposed to different set of runtime parameters. Hence, solutions for dependability problems cannot be static and needs to be adaptable against variations during lifetime operation of each chip. It is essential to use runtime data to make predictions on the status of various degradation and vulnerability parameters. Accurate prediction models are required in this regard which can guide adaptation actions in a proactive manner.

One of the transistor aging mechanisms known as Bias Temperature Instability (BTI) degrades the threshold voltage of a transistor that eventually results in slower switching of logic gates made of these transistors [39]. Aging of transistors leads to degradation of circuit delays, eventually increasing the number of timing violations, and a decrease in the expected lifetime [18]. If the degradation rate can be tracked in a fine-grained manner, appropriate adaptation actions such as adaptive voltage scaling [19], body biasing [20] or reliability-aware task mapping [21] can be taken. In the case of radiation-induced soft errors, each phase of a workload executed on a design, such as a processor, can have a specific nature causing higher or lower vulnerability towards soft error events measured in terms of vulnerability factor. Prediction of accurate vulnerability factor during runtime can enable cost-effective protection mechanisms. In the case of security threats, malicious hardware (hardware Trojans) can get activated during runtime, and the prediction of the Trojan activation serves as a last line of defense. With increasing complexity of systems, the runtime monitoring and prediction of these parameters meet several challenges. The generation of enormous amount of runtime data during workload execution on a hardware block necessitates careful spatial and temporal selection of probing points in the hardware block. Reuse of existing monitors cannot be always an effective solution due to the granularity of access and hence, new cost-efficient runtime monitors with less overheads are required. Predictions from the patterns in runtime data needs to be fast and accurate to enable proactive mitigation of dependability issues.

Modern systems incorporate a range of sensors and monitors (e.g., razor flip-flops [22], critical path monitors (CPM) [23]) to track the impact of several reliability mechanisms on the functionality and performance of a circuit. These reliability mechanisms include aging due to Bias Temperature Instability (BTI) [10] and supply voltage fluctuations. In addition, additional hardware is added in the form of redundant units or error correction units in order to tackle the impact of radiation- induced soft errors [10]. With these sensor data available online, suitable adaptation policies can be triggered on-the-fly that can help in resilient operation of a system. However, the fundamental problem of the above method lies in the fact that these sensors monitor the effect (e.g., path delay increase due to BTI) of a reliability phenomenon rather than its cause (nature of workload). Hence, the adaptation policies can only be triggered after a measurable degradation occurs on the circuit. In addition, to secure against activation of hardware Trojans, performance-monitor based detection techniques are deployed. However, these monitors can be tampered by an adversary. In short, dependability-aware selection of appropriate features to monitor runtime data and development of prediction models that can predict accurately from the selected features are the needs of the hour.

The objective of this thesis is to enable runtime predictions on different dependability mechanisms by logic-level data analysis, and by exploiting machine learning techniques for workload compaction and representation. Different learning methods are used to identify low cost workload observables, and to build prediction models that correlate the workload observables with reliability and security metrics.

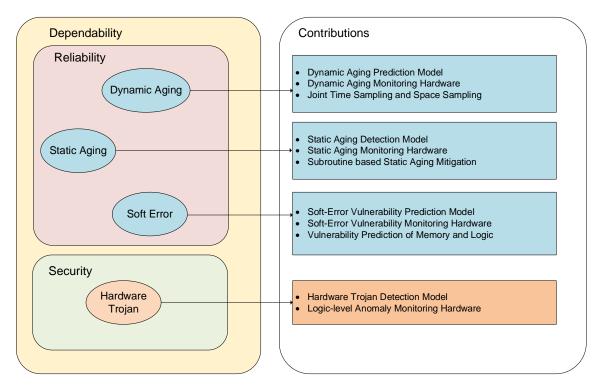

### 1.2 Contribution of this Thesis

In this thesis, we target the improvement of overall dependability of integrated circuits by analyzing the impact of runtime variations on various reliability and security issues as illustrated in Fig. 1.2. We devise machine learning techniques to model, monitor and mitigate various dependability effects originating from imperfections in device fabrication, design issues, and impact of runtime workload and environment. We target early runtime prediction of the impact of a workload phase on resilient operation of a circuit. This information about the impact of a workload phase can guide proper mitigation actions proactively such as relaxation of aging stress or tackling vulnerability of a circuit to soft errors. In this regard, these learning techniques can be used to correlate workload patterns to corresponding impact on system dependability under aging, soft errors and malicious Trojans. We propose a methodology to monitor hardware designs online, and predict dependability metric values on-the-fly based on prediction models constructed offline. Our technique involves workload analysis to extract hidden information that describes the relationship between the workload executed on the design, and corresponding values of dependability metrics (Eg: circuit-path-delay increase).

The workload data (set of system states over time) is analyzed in the logic level to maximize

the information content to use for reliability and security analysis. However, this increases the complexity of analysis and hence, we deploy domain-specific feature selection and feature engineering techniques to capture important features of a workload segment. In this regard, suitable workload observables are identified offline using correlation analysis and feature elimination techniques. A prediction model is built offline to correlate the workload observable with the dependability metric under consideration. Low cost hardware monitors are proposed to track the workload observables online and the monitoring information is fed to software predictors to make early predictions on the reliability and security metrics.

Figure 1.2: Overall contributions of this thesis in different attributes of dependability.

In particular, the novel contribution of this thesis are listed below.

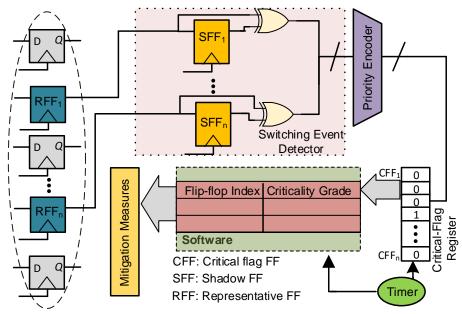

- Dynamic Aging Monitoring and Delay Prediction [24]: Dynamic aging of transistors due to Bias Temperature Instability (BTI) involves aging stress and recovery phases resulting in long term degradation of circuit paths. This mechanism degrades path delay over time leading to timing failures. Direct monitoring of path delays based on actual measurements can only track a coarse-grained aging trend. We propose a finegrained aging monitoring scheme based on estimating runtime aging stress of workloads. A prediction model generated offline based on workload stress analysis is implemented online with a low overhead monitoring hardware to make predictions on aging rates. As a result, we can achieve timely workload-stress estimations and aging rates during runtime that can be used in turn to take appropriate proactive and fine-grain mitigating actions and prevent the circuit from aging at higher rates.

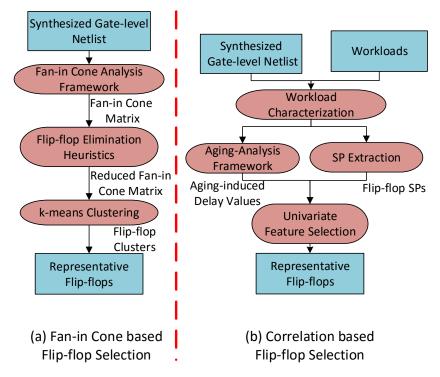

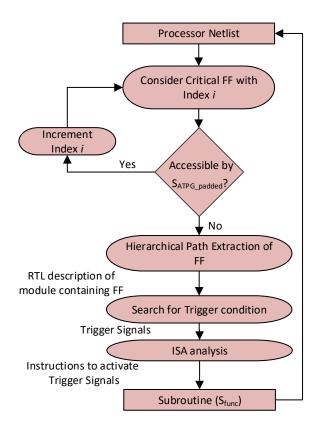

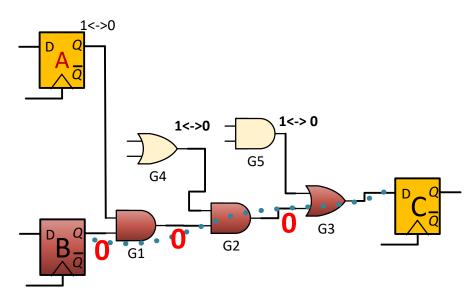

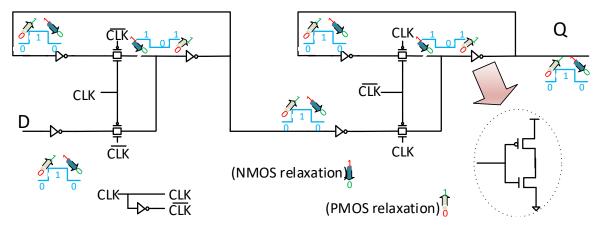

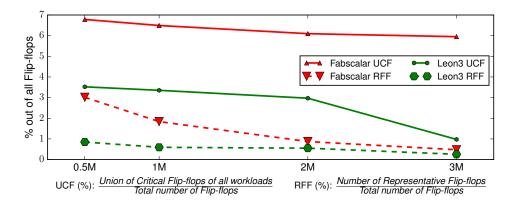

- Static Aging Monitoring and Mitigation [25, 26]: Circuits are exposed to accelerated aging rates (static BTI) while the transistors are stressed for extended period of time without any recovery phase. This scenario can occur based on the nature of workload phase and it can lead to early timing failures as one year of dynamic BTI stress is similar to a few hours of static BTI stress. To address this problem, we identify correlated static aging phases of timing critical flipflops in an offline correlation

analysis and deploy a runtime monitoring scheme to raise a flag when the circuit enters an accelerated aging phase. A synthetic subroutine based mitigation technique is also proposed to relax the aging stress by exercising aged gates and flip-flops. This leads to an improvement in the overall lifetime of the circuit compared to the case where only dynamic BTI is considered.

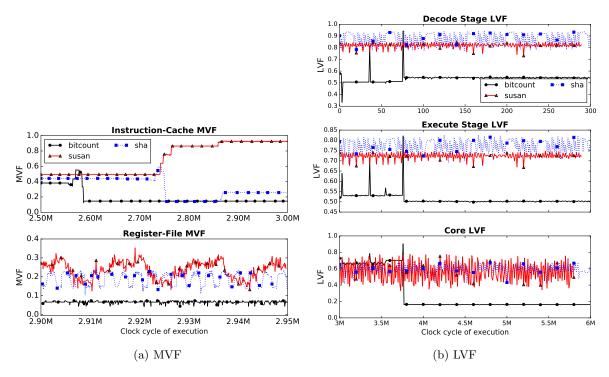

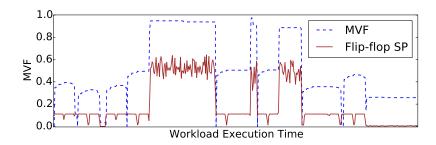

- Soft-Error Vulnerability Prediction [27, 28]: The vulnerability of a system to soft errors is dynamic in nature due to various masking effects in different levels of abstraction. Hence, it is desirable to have a vulnerability prediction scheme that can turn on and off online protection mechanisms in a cost-effective manner. In this regard, we proposed a low overhead soft-error vulnerability prediction scheme by monitoring only a small number of flip-flops during runtime. Our prediction model can predict the online vulnerability of a whole system comprising of memory arrays and logic cores significantly more accurate than the state-of-the-art prediction techniques based on performance counters.

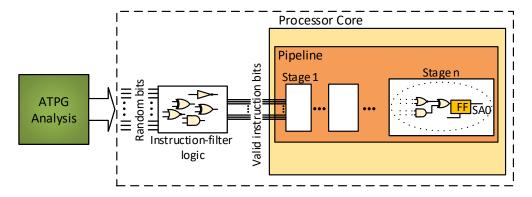

- Runtime Hardware Trojan Detection [29]: During the age of globalization of chip design and fabrication, untrusted designs in the form of third-party intellectual property (3PIP) poses a threat of malicious hardware inclusion in the form of hardware Trojans. The stealthy nature of these Trojans makes them hard to be identified before in-field operation of the chip. Hence, runtime techniques serve as a last line of defense. The state-of-the-art runtime detection techniques monitors functionally defined (semantically significant) signals to capture Trojan activation and these signals are vulnerable to be masked by a rogue designer. We propose an anomaly detection technique based on logic-level signals (semantically insignificant) that are hard to be masked by an adversary at a 3PIP level. We could achieve high classification accuracy on the identification of Trojan activation by monitoring the workload profile of a small number of flipflops in the processor core.

All aforementioned techniques involve workload characterization of open-source processor designs at logic level of abstraction. To accelerate the workload characterization, a Field-Programmable Gate Array (FPGA) implementation of open source processor core was used with cross-compiled workloads executed on the FPGA platform. We have used Leon3 [30] and OpenRISC 1200 [31] processor designs along with SPEC [32] and MiBench [33] workloads. For prediction model generation, python-based scikit-learn library [34] was used. In short, the workload execution environment was developed on a real FPGA platform in addition to a post-synthesis simulation environment that can carry out cycle-accurate workload simulations.

### 1.3 Outline

This chapter describes the motivation and contribution of this thesis. The rest of this thesis is organized as follows:

Chapter 2 provides a brief description of each reliability and security challenge considered in this thesis. The discussion spans from the basic physical effects governing the application-level impact of the dependability issues to the state-of-the-art runtime techniques available in the context of this thesis.

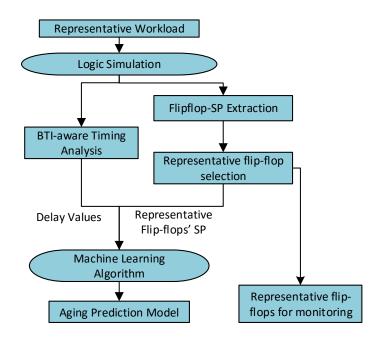

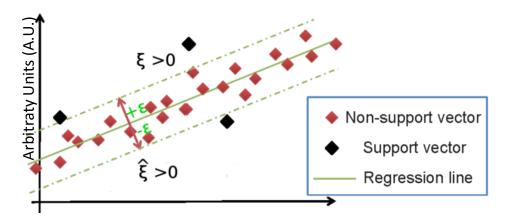

In Chapter 3, our methodology to cost-efficiently address the need for dynamic aging prediction is presented. Our fine-grained aging monitoring scheme to analyze and compare the aging stress of workloads during runtime is discussed. Offline prediction model construction based on machine learning is explained with examples and the overhead of online monitoring hardware is calculated. Further, space and time sampling techniques are described to reduce power and area overheads of monitoring.

#### 1 Introduction

Chapter 4 presents the worst-case scenario of circuit delay degradation due to static aging and analyzes the impact on different processor designs. A low overhead runtime monitoring scheme is detailed along with a mitigation scheme based on software subroutines. The lifetime improvement due to the proposed monitoring and mitigation scheme is also reported.

In Chapter 5, a low overhead runtime soft-error vulnerability prediction schemes for memory arrays and logic cores of a system is presented. The offline prediction model construction based on two machine learning algorithms is discussed in detail. The overall design of the online monitoring scheme to observe a small set of flipflops is explained with corresponding overheads.

Chapter 6 discusses a scheme for the runtime prediction of hardware Trojan activation. An anomaly detection technique based on monitoring the workload profile of selected circuit nodes is presented. The prediction accuracy achieved on a Trojan-inserted open source processor core executing several workloads is reported.

Finally, Chapter 7 concludes the thesis and a discussion on future implication of this work is given.

### 2 Background

In this chapter, the basic challenges to dependable hardware design in the age of aggressive technology scaling and globalized chip fabrication are discussed. In the context of this thesis, a brief introduction to dependability, various reliability and security challenges, and their runtime impact are discussed. Furthermore, a brief introduction to machine learning techniques is also provided.

# 2.1 Dependability Challenges: Overview of Hardware Reliability and Security

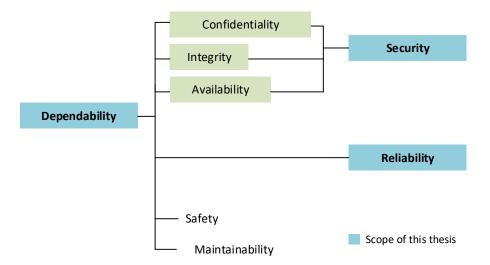

A computing system is said to be dependable if it can be trusted with its intended functionality. Dependability is the system property that integrates reliability, availability, safety, security and maintainability [8]. The emphasis on these different attributes can be different based on the underlying application. In the context of this thesis, security and reliability attributes are given a higher emphasis, and the term *dependability* is used as a hypernym as shown in Fig. 2.1.

Figure 2.1: Illustration of the attributes of dependability in the scope of this thesis [8].

Figure 2.2: Dependability threats and their causal relationship [8].

According to [8], security is defined as the concurrent existence of confidentiality, integrity and availability. Confidentiality is satisfied only if there is no unauthorized disclosure of information. Integrity demands no improper alterations to system state. Availability can be described as the readiness of correct service. Reliability is termed as a measure of the continuous delivery of correct service.

### 2 Background

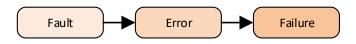

In addition to the different attributes of dependability as discussed previously, dependability threats are manifested in the form of faults, errors, and failures as illustrated in Fig. 2.2. Fault can be a physical defect on a device. An error in the functionality of a system can be caused by a fault. If an external service is affected by the propagation of this error, a failure is said to be occurred. In short, a fault produces an error, that in turn causes a failure. It can also happen that a fault remains dormant or an error may not propagate based on other characteristics of a system.

With a general overview of the different attributes and threats of dependability, we examine the specific reliability and security aspects tackled in this thesis. With technology scaling advancement, a host of vulnerabilities affect reliability of VLSI designs. In a modern SoC design, billions of transistors are packed in a single chip and this increases the complexity of verification and test efforts. In addition, several transistor degradation mechanisms such as aging cause slowing down of computations over time eventually leading to failures. Transient soft errors, caused by radiations, are another reliability issue that can cause bit flips in circuit nodes that can eventually propagate to cause system failures. The runtime dependence of these reliability issues adds an additional layer of complexity that makes design-time solutions inadequate. On the other hand, the globalization of chip design and fabrication stages introduces serious security concerns. The possibility of malicious hardware inclusion in a chip called hardware Trojan at any stage of design flow emerges as a major security threat for government bodies and other customers of the chip. In the following sections, we present an in-depth discussion on specific reliability and security challenges.

### 2.2 Reliability Challenges

Reliability R(t) is defined as the probability that a computing system performs correct functionality for a given period of time t under specified conditions without any failure [35]. In the realm of hardware design, sources of unreliabilities include aging of transistors, radiationinduced soft errors, process variation, susceptibility to noise, and increasing complexities in different hardware abstraction levels. The severity of these reliability issues on a particular chip is largely dependent on the usage scenarios. To quantify the reliability of a system, different metrics such as *Mean Time To Failure (MTTF)* are used. The *MTTF* of a system is the time for which the system is expected to operate without any failure.

In the context of this thesis, two reliability issues, (a) circuit aging phenomenon, and (b) radiation-induced soft error are discussed in detail.

### 2.2.1 Circuit Aging

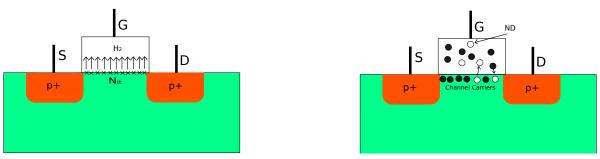

(a) Reaction-Diffusion Mechanism

Figure 2.3: NBTI Aging Models [36]

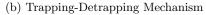

Figure 2.4: Illustration of stress and recovery phases due to NBTI

Circuit aging refers to the various degradation or wear-out mechanisms that make circuits less reliable over time leading to the occurrence of failures before the end of expected device lifetime. The degradation mechanisms include Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), Time Dependent Dielectric Breakdown (TDDB) and electromigration (EM). BTI, HCI and TDDB degrade the transistor characteristics. BTI causes an increase in the threshold voltage of a transistor that is turned on. Both PMOS (by Negative Bias Temperature Instability (NBTI)) and NMOS (by Positive Bias Temperature Instability (PBTI)) transistors are prone to this effect in advanced technology nodes. This effect can necessitate additional timing margin compromising performance of circuits to prevent early timing failures. HCI is caused by the high lateral electric field due to drain-to-source voltage  $(V_{ds})$  of a transistor leading to the penetration of gate oxide by high energy carriers. This leads to a degradation in the threshold voltage of the transistor which eventually can cause timing failures. TDDB causes degradation of gate oxide characteristics leading to a leakage path through the oxide. In the worst case, it can cause a hard breakdown or permanent damage of the transistor. Electromigration causes wear out of interconnects due to high current density causing timing delays, open circuit or short circuit. In the context of this thesis, we describe BTI models and the effect of BTI on circuit delay in detail.

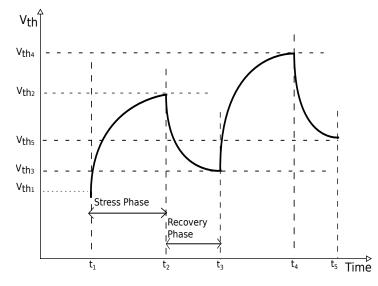

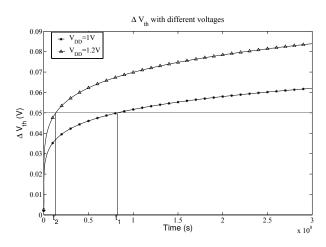

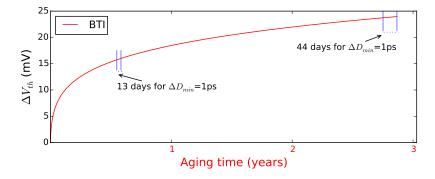

Figure 2.5: Comparison of  $\Delta V_{th}$  due to D-BTI (duty cycle ( $\alpha$ )=0.5) and S-BTI.

Bias Temperature Instability (BTI) is one of the major reliability threats in nanoscale tech-

nology nodes. Although both PMOS and NMOS transistors are affected by Negative Bias Temperature Instability (NBTI) and Positive Bias Temperature Instability (PBTI) respectively, we limit our analysis to NBTI. NBTI can cause an increase in the threshold voltage  $(V_{th})$ of transistors along with a decrease in transconductance  $(g_m)$  and saturation current  $(I_{Dsat})$ at negative gate voltages and elevated temperatures. The modeling of this phenomenon is complicated due to a recovery phase that involves a partial recovery of transistor degradation when a positive gate voltage is applied. The long-term effect of NBTI on a design is heavily dependent on the type and history of stress due to the workload under execution.

NBTI can be explained using two different mechanisms, (1) Reaction-Diffusion (RD) model [37, 38], or (2) Trapping/Detrapping (TD) Model [39, 40]. According to RD model, increase in threshold voltage occurs due to the breaking of covalent (Si-H) bonds at interface resulting in the generation of interface traps as illustrated in Fig. 2.3a. The increase in  $V_{th}$  is assumed to follow a power law relation with the time under stress and an exponential relation with the applied stress voltage.

The TD model proposes a fundamentally different phenomenon to explain the thresholdvoltage increase, i.e., the capture and emission of charge carriers by interface traps as illustrated in Fig. 2.3b. The capture time constant determines the probability of trapping and emission time constant determines the probability of detrapping. The threshold voltage increases gradually with the change in number of occupied traps and hence, follows a logarithmic relation in  $V_{th}$  shift. TD model assumes a logarithmic relation with stress time and an exponential relation with temperature and stress voltage.

In short, both aging mechanisms assume a stress phase and a recovery phase for a transistor under NBTI as shown in Fig. 2.4 based on the type of bias applied. During a normal workload execution, the bias of a transistor alternates causing alternate stress and recovery phases. In long term, the cumulative effect of NBTI heavily depends on the type of workload executed on the design.

The  $V_{th}$  increase under dynamic stress estimated using a long-term NBTI model for time duration t can be expressed as in equation 2.1 [41],

$$\Delta V_{thd} = \left(\frac{n^2 K_v^2 \alpha C t}{\zeta^2 t_{ox}^2 (1-\alpha)}\right)^n,\tag{2.1}$$

where  $t_{ox}$  is the oxide thickness,  $\zeta$  is the diffusion coefficient,  $\alpha$  is the stress duty cycle, n is the time exponent, typically 0.16, and  $K_v$  is a function of  $V_{qs}$ ,  $V_{th}$  and temperature.

In short, since long-term NBTI effect (termed as dynamic BTI (D-BTI)) involves recovery phases after most of the stress phases (stress duty cycle < 1), the overall effect on  $V_{th}$  and thereby, on the circuit delay is minimal for a short duration of a few hours.

The worst-case increase in  $V_{th}$ , and therefore the circuit delay, occurs when there are continuous stress phases and no recovery phases (stress duty cycle = 1). This scenario, termed as static BTI (S-BTI), induces accelerated aging. The  $V_{th}$  shift under static stress ( $\Delta V_{ths}$ ) is given by equation 2.2 [41],