## Universidad de Valladolid

# E. T. S. Ingeniería Informática Trabajo Fin de Grado

Grado en Ingeniería Informática

Desarrollo de un modelo de programación para simplificar el uso de aceleradores hardware

Autor:

Alejandro Alonso Mayo

Tutor:

Dr. Héctor Ortega Arranz Dr. Arturo González Escribano

# Agradecimientos

Quiero agradecer mi familia, quienes me han apoyado y ayudando a centrarme en el desarrollo de este trabajo. También a mis amigos quienes me apoyaban, me animaban y me escuchaban cuando necesitaba hablar con alguien. A Héctor Ortega Arranz y a Arturo González Escribano, mis tutores, quiero agradecerles por responder pacientemente dudas, aconsejarme y guiarme durante el transcurso del proyecto. Al resto del grupo Trasgo de la Uva a quienes no les faltó tiempo para ayudarme cuando tenía algún problema.

## Resumen

Hoy en día el uso de aceleradores hardware, como las GPUs o las XeonPhi entre otros, está cada vez más extendido dentro del contexto de la computación de alto rendimiento. Desarrollar aplicaciones que usen estos aceleradores puede ser una tarea compleja, sobretodo si dicha aplicación conlleva una gestión no trivial de transferencias de memoria o una compleja configuración del dispositivo.

En este proyecto se pretende desarrollar una biblioteca para el desarrollo de aplicaciones que usen aceleradores hardware. Esta biblioteca pretende liberar al programador de tediosas tareas como la gestión de transferencias, configuración del acelerador y la sincronización, entre otros, a la vez que se evitan posibles fallos de una incorrecta gestión manual.

## Abstract

Today the use of hardware accelerators such as GPUs or XeonPhi among others, is increasingly widespread within the context of high performance computing. Developing applications using these accelerators can be very complex, especially if the application needs a nontrivial memory transfer management or a complex configuration of the device.

This project aims to create a software development library to use hardware accelerators. This library helps the programmer with tedious tasks of programming these accelerators, such as the transferences management, and the device configuration and synchronization, among others. It also prevents possible mistakes due to incorrect manual handling.

# Índice general

| Ín | $\mathbf{dice}$ | de figuras                                                   | XII |

|----|-----------------|--------------------------------------------------------------|-----|

| Ín | dice            | de cuadros                                                   | XIV |

| Ι  | Int             | troducción y Planificación                                   | 1   |

| 1. | Intr            | roducción                                                    | 3   |

|    | 1.1.            | Dispositivos Aceleradores Hardware                           | 3   |

|    |                 | 1.1.1. Introducción a los aceleradores                       | 3   |

|    |                 | 1.1.2. Programación de aceleradores                          | 3   |

|    |                 | 1.1.3. Dificultades en la programación de aceleradores       | 4   |

|    | 1.2.            | Objetivos del proyecto                                       | 5   |

|    | 1.3.            | Metodología utilizada                                        | 5   |

|    | 1.4.            | Estructura del documento                                     | 6   |

| 2. | Plai            | nificación del proyecto                                      | 9   |

|    | 2.1.            | Entregables del proyecto                                     | 9   |

|    | 2.2.            | Gestión de tiempo                                            | 10  |

|    |                 | 2.2.1. Planes de iteración                                   | 10  |

|    | 2.3.            | Costes del proyecto                                          | 15  |

|    | 2.4.            | Gestión de riesgos                                           | 19  |

|    |                 | 2.4.1. Perspectiva general                                   | 19  |

|    |                 | 2.4.2. Lista de riesgos                                      | 20  |

|    |                 | 2.4.3. Riesgos priorizados                                   | 26  |

|    | 2.5.            | Gestión de configuraciones                                   | 27  |

|    |                 | 2.5.1. Documentación                                         | 27  |

|    |                 | 2.5.2. Código fuente del prototipo y de los casos de estudio | 27  |

|    |                 | 2.5.3. Resultados experimentales                             | 27  |

| 3. |                 | uimiento del proyecto                                        | 29  |

|    | 3.1.            | Seguimiento de las iteraciones                               | 29  |

|    |                 | 3.1.1. Seguimiento primera iteración                         |     |

|    |                 | 3.1.2. Seguimiento segunda iteración                         | 30  |

|    |                 | 3.1.3. Seguimiento tercera iteración                         | 31  |

|    | 3.2.            | Conclusiones de la planificación                             | 33  |

#### ÍNDICE GENERAL

| 4. Introducción a CUDA 4.1. Arquitectura de CUDA | 37 |

|--------------------------------------------------|----|

|                                                  | J  |

|                                                  |    |

| 4.1.1. Funcionamiento de la GPU                  |    |

|                                                  |    |

| 4.2. Modelo de programación                      |    |

| 4.2.1. Kernels                                   |    |

|                                                  |    |

| 5. Introducción a Hitmap                         | 4: |

| 5.1. Carácteristicas de Hitmap                   |    |

| -                                                |    |

| - v                                              |    |

| <del>-</del>                                     |    |

| 5.1.3. Comunicaciones                            |    |

| 5.2. Arquitectura de Hitmap                      |    |

| 5.2.1. Dominio de los tiles                      |    |

| 5.2.2. Tiles, Mapeo y Comunicaciones             |    |

| TTT 4 411 1 TO 2                                 |    |

| III Análisis y Diseño                            | 51 |

| 6. Modelo de comunicadores                       | 5: |

| 6.1. Modelo general                              |    |

| 6.1.1. Configuración de los trabajos             |    |

| 6.1.2. Comunicaciones                            |    |

| 6.1.3. Lanzamiento de kernels                    |    |

| 6.2. CPU como acelerador                         |    |

| 6.2.1. Comunicaciones                            |    |

| 6.2.2. Lanzamiento de kernels                    |    |

| 6.3. Contextos: otra posible alternativa         |    |

| 6.3.1. Posible ejemplo                           |    |

| 6.3.2. Desestimación de la alternativa           |    |

| 7. Análisis                                      | 6  |

| 7.1. Análisis de requisitos                      |    |

|                                                  |    |

| 7.1.1. Requisitos funcionales                    |    |

| 7.1.2. Requisitos no funcionales                 |    |

| 7.2. Casos de uso                                |    |

| 7.3. Modelo de objetos                           |    |

| 8. Modelo de diseño                              | 67 |

| 8.1 Modele estructural                           |    |

| O.I. MOUEIO ESH UCTUIAL                          |    |

|                                                  |    |

| 8.1.1. Estructura Comm                           |    |

| 8.1.1. Estructura Comm                           |    |

| 8.1.1. Estructura Comm                           |    |

|            | 8       | 3.2.2.  | Enlazado y Desenlazado de variables          | 73  |

|------------|---------|---------|----------------------------------------------|-----|

|            | 8       | 3.2.3.  | Creación y destrucción de variables internas | 75  |

|            | 8       | 3.2.4.  | Ejecución de kernels                         | 75  |

| I          | 7 In    | ıplen   | nentación y Pruebas                          | 81  |

| 9.         | Imple   | ement   | ación del modelo                             | 83  |

|            | _       |         | nienta de generación de código               | 83  |

|            |         |         | es de función y parámetros comunes           | 84  |

|            |         |         | uración de los kernels de GPU                | 84  |

|            |         | _       | Carácterización de los kernels               | 84  |

|            | ç       | 0.3.2.  | Asignación del rol de los parámetros         | 86  |

|            | 9.4. T  | Unifica | ción de los paradigmas CPU-GPU               | 86  |

|            | S       | 0.4.1.  | Lanzamiento asíncrono de kernels             | 86  |

|            | S       | 0.4.2.  | Emulación de hilos de GPU                    | 87  |

|            | 9.5. I  | Mapeo   | de variables                                 | 88  |

|            | 9.6. I  | Lanzar  | niento de kernels                            | 88  |

| 10         | .Pruel  | bas so  | obre el prototipo                            | 91  |

|            | 10.1. I | Plan d  | e pruebas                                    | 91  |

|            | 1       | 0.1.1.  | Pruebas de unidad                            | 91  |

|            | 1       | 0.1.2.  | Pruebas de integración                       | 92  |

|            | 1       | 0.1.3.  | Pruebas de validación                        | 92  |

|            | 10.2. I | Resulta | ados de las pruebas                          | 92  |

| <b>T</b> 7 | T7      | •       |                                              | 00  |

| V          | EX]     | perir   | nentación y Conclusiones                     | 99  |

| 11         | _       |         |                                              | 01  |

|            |         |         | oción del estudio experimental               |     |

|            |         |         | oción de la máquina de experimentación       |     |

|            |         |         | de estudio                                   |     |

|            |         |         | Suma de matrices                             |     |

|            |         |         | Multiplicación de matrices                   |     |

|            |         |         | PDE Jacobi                                   | 104 |

|            |         |         | •                                            | 104 |

|            |         |         | 1 0                                          | 104 |

|            |         |         | <u>.</u>                                     | 105 |

|            |         |         |                                              | 106 |

|            | 1       | 1.4.4.  | Resumen de los resultados                    | 106 |

| <b>12</b>  |         |         |                                              | 15  |

|            |         |         | 1                                            | 115 |

|            |         |         | 1                                            | 116 |

|            | 12.3.   | Гrabaj  | o futuro                                     | 116 |

### ÍNDICE GENERAL

| VI Apéndices y Bibliografía                       | 117              |

|---------------------------------------------------|------------------|

| A. Contenido del CD-ROM A.1. Árbol de directorios | <b>119</b> . 119 |

| Bibliografía                                      | 121              |

# Índice de figuras

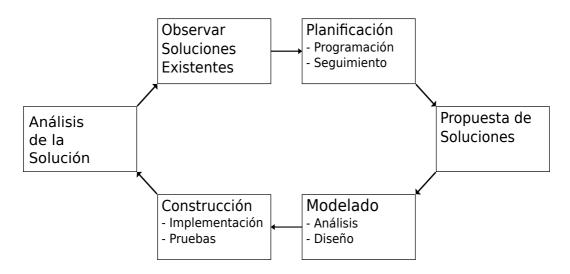

| 1.1.  | Gráfico explicativo de la metodología utilizada                | 7  |

|-------|----------------------------------------------------------------|----|

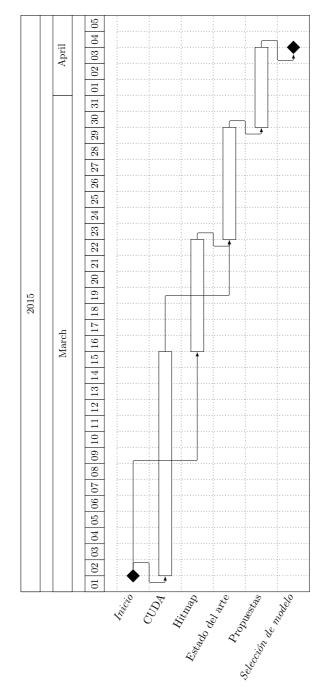

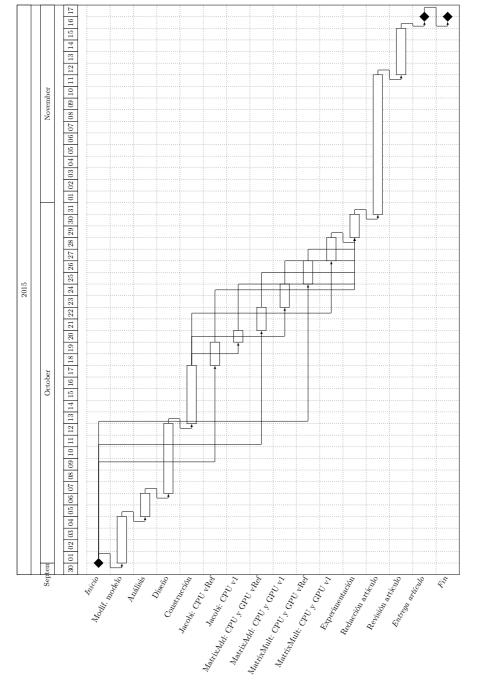

| 2.1.  | Diagrama de Gantt Iteración 1                                  | 11 |

| 2.2.  | Diagrama de Gantt Iteración 1 (cont)                           | 12 |

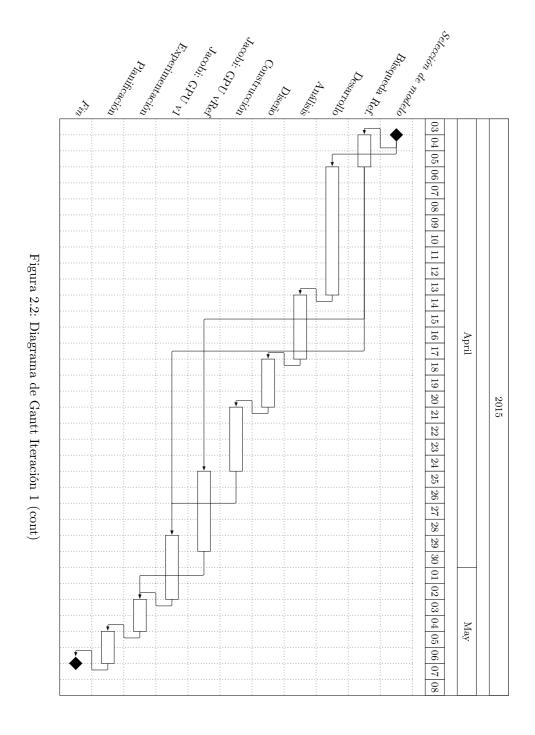

| 2.3.  | Diagrama de Gantt Iteración 2                                  | 14 |

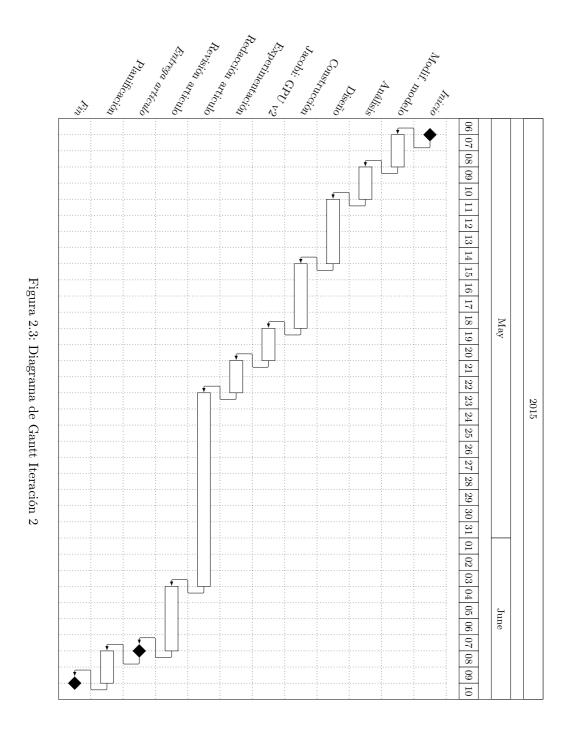

| 2.4.  | Diagrama de Gantt Iteración 3                                  | 17 |

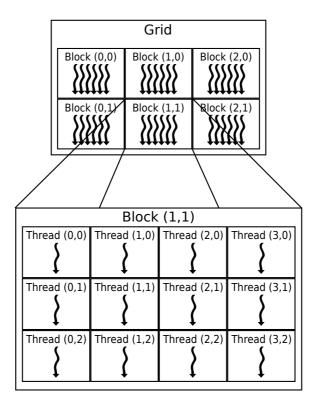

| 4.1.  | Jerarquia de un Grid                                           | 38 |

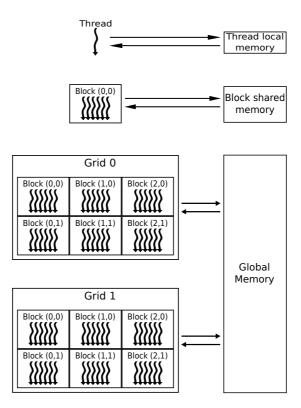

| 4.2.  | Jerarquia de memoria                                           | 39 |

| 4.3.  | Ejemplo de definición de un kernel en CUDA                     | 41 |

| 4.4.  | Ejemplo de kernel que se ejecuta en un bloque bidimensional    | 41 |

| 4.5.  | Ejemplo de programa CUDA con memoria dinámica                  | 43 |

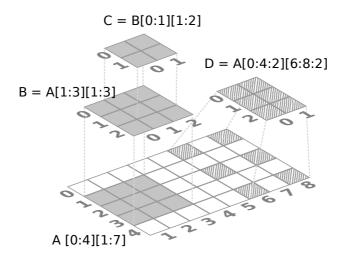

| 5.1.  | Ejemplo de selecciones jerárquicas de tiles en hitmap          | 47 |

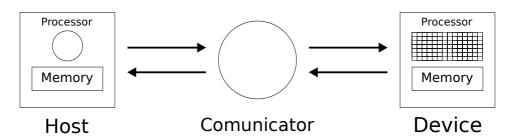

| 6.1.  | Visión general de un comunicador.                              | 53 |

| 6.2.  | Ejemplo de caracterización                                     | 55 |

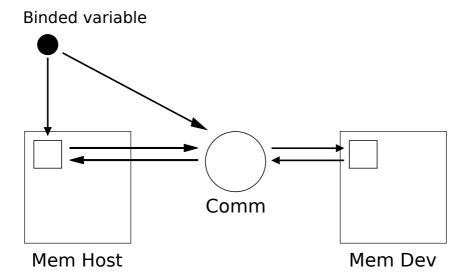

| 6.3.  | Variable enlazada                                              | 56 |

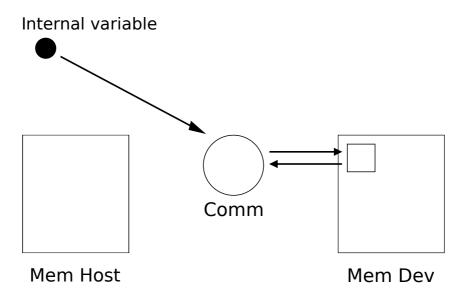

| 6.4.  | Variable interna                                               | 57 |

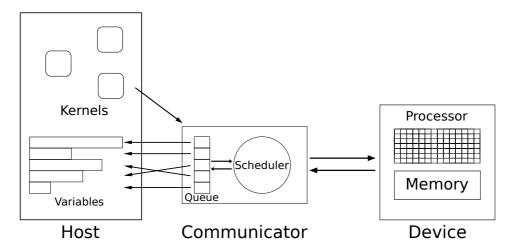

| 6.5.  | Comunicador detallado                                          | 58 |

| 6.6.  | Posible ejemplo de la propuesta de contexto                    | 59 |

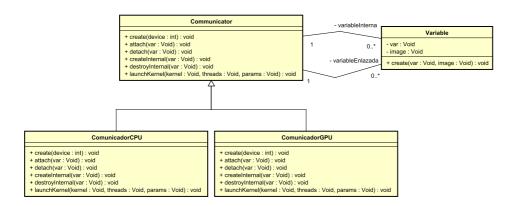

| 7.1.  | Modelo de objetos de los comunicadores                         | 66 |

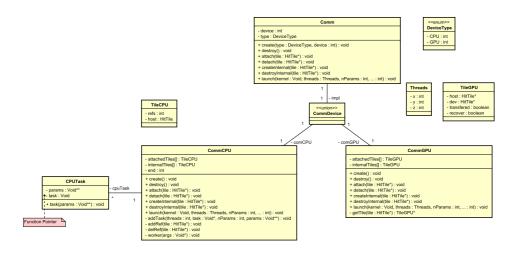

| 8.1.  | Clases que conforman los comunicadores                         | 67 |

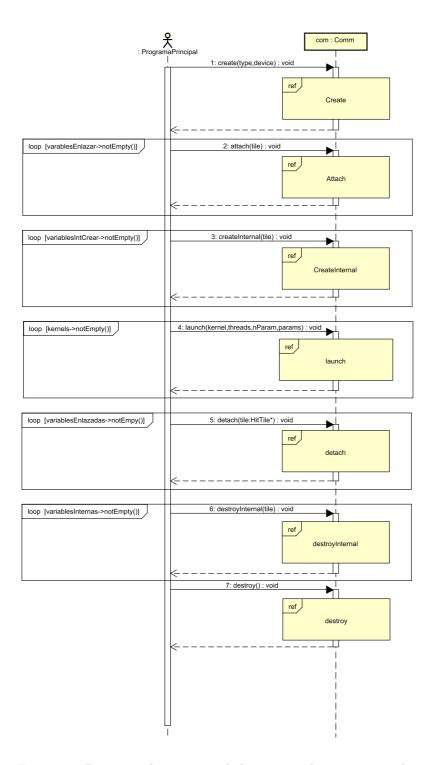

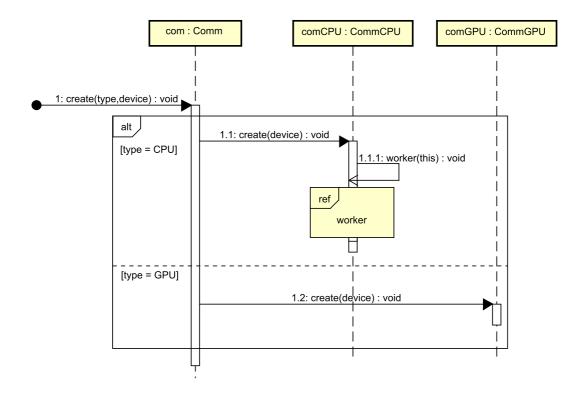

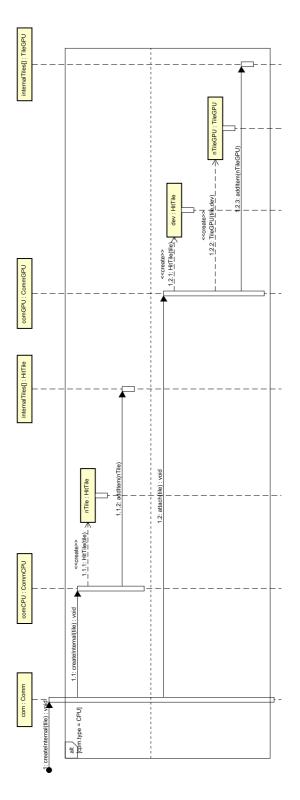

| 8.2.  | Diagrama de secuencia de la creación de un comunicador         | 71 |

| 8.3.  | Diagrama de secuencia de la creación de un comunicador         | 72 |

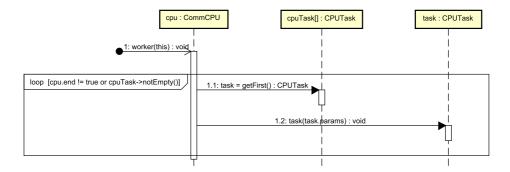

| 8.4.  | Diagrama de secuencia del hilo worker en un comunicador de CPU | 73 |

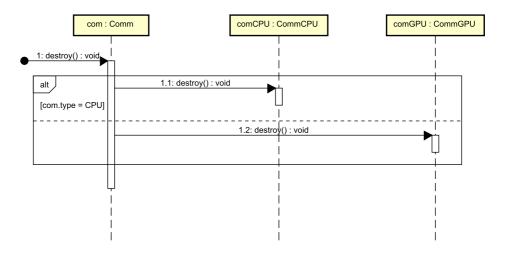

| 8.5.  | Diagrama de secuencia de la destrucción de un comunicador      | 73 |

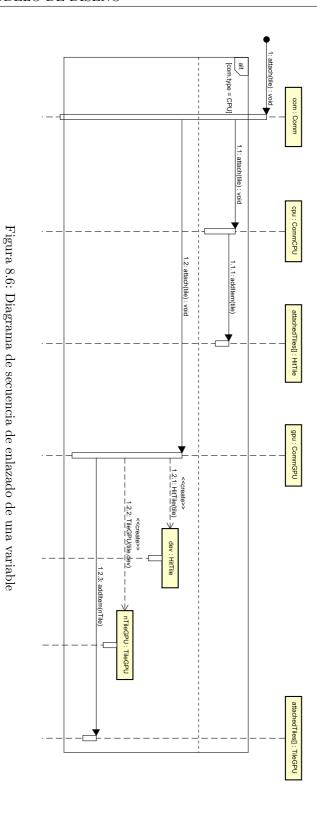

| 8.6.  | Diagrama de secuencia de enlazado de una variable              | 74 |

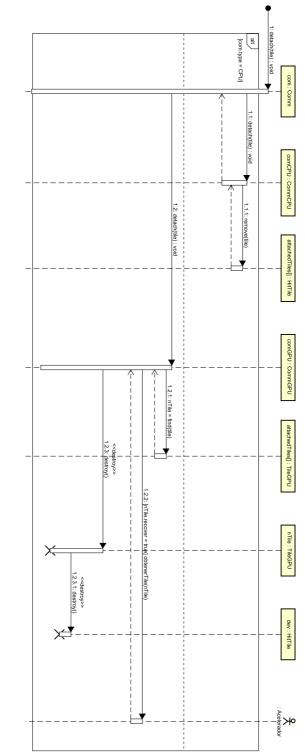

| 8.7.  | Diagrama de secuencia de desenlazado de una variable           | 76 |

| 8.8.  | Diagrama de secuencia de creación de variables internas        | 77 |

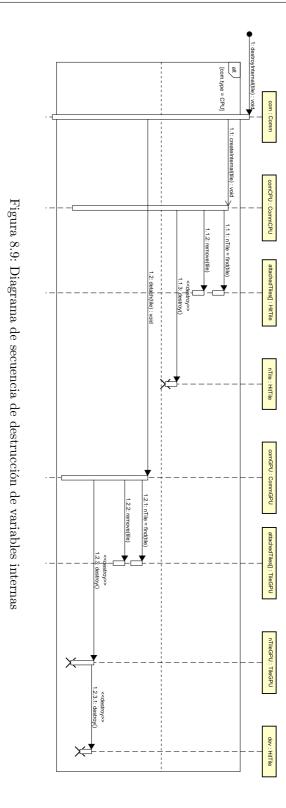

| 8.9.  | Diagrama de secuencia de destrucción de variables internas     | 78 |

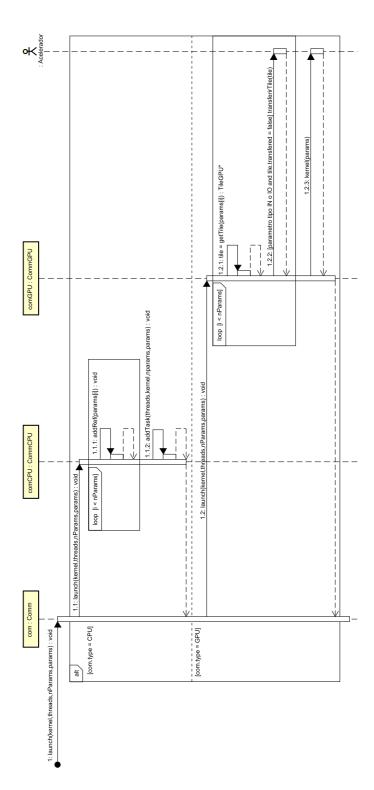

| 8.10. | Diagrama de secuencia del lanzamiento de un kernel             | 79 |

| 9.1.  | Ejemplo de algunas de las cabeceras de funciones del prototipo | 84 |

#### ÍNDICE DE FIGURAS

| 9.2.  | Ejemplo de caracterización de kernels                                           | 85  |

|-------|---------------------------------------------------------------------------------|-----|

| 9.3.  | Ejemplo de cabecera de un kernel GPU                                            | 86  |

| 9.4.  | Posible código para la paralelización de los kernels                            | 87  |

| 9.5.  | Ejemplo de cabecera de un kernel CPU                                            | 88  |

|       |                                                                                 |     |

| 11.1. | Pseudocódigo de la suma de matrices                                             | 103 |

| 11.2. | Pseudocódigo de la suma de matrices                                             | 104 |

| 11.3. | Pseudocódigo PDE de Jacobi en secuencial                                        | 105 |

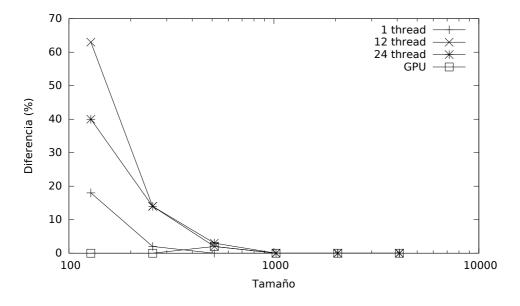

| 11.4. | Gráfico de diferencia en tiempos de ejecución de la suma de matrices            | 108 |

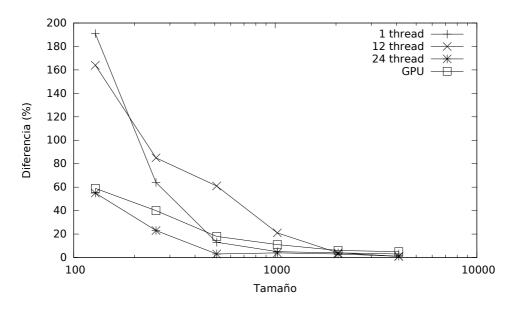

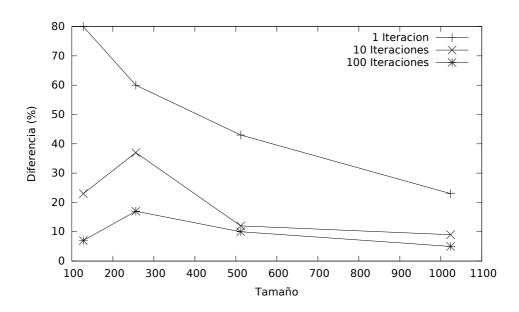

| 11.5. | Gráfico de diferencia en tiempos de ejecución de la multiplicación de matrices. | 108 |

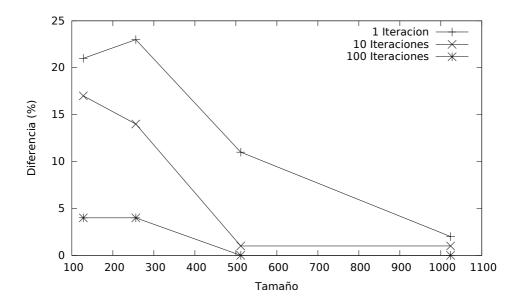

| 11.6. | Gráfico de diferencia en tiempos de ejecución del Jacobi en la CPU              | 111 |

| 11.7. | Gráfico de diferencia en tiempos de ejecución del Jacobi en la GPU              | 113 |

# Índice de cuadros

| 2.1.  | Actividades de la primera iteración          | 13  |

|-------|----------------------------------------------|-----|

| 2.2.  | Actividades de la segunda iteración          | 15  |

| 2.3.  | Actividades de la tercera iteración          | 16  |

| 2.4.  | Presupuesto estimado                         | 18  |

| 2.5.  | Lista priorizada de los riesgos              | 26  |

| 3.1.  | Seguimiento de la primera iteración          | 30  |

| 3.2.  | Seguimiento de la segunda iteración          | 31  |

| 3.3.  | Seguimiento de la tercera iteración          | 32  |

| 7.1.  | Lista de requisitos funcionales              | 62  |

| 7.2.  | Lista de requisitos no funcionales           | 63  |

| 10.1. | Pruebas de unidad                            | 93  |

| 10.2. | Pruebas de unidad (cont.)                    | 94  |

| 10.3. | Pruebas de integración                       | 95  |

| 10.4. | Pruebas de validación                        | 96  |

| 10.5. | Resultados de pruebas de unidad              | 96  |

| 10.6. | Resultados de pruebas de integración         | 97  |

| 10.7. | Resultados de pruebas de validación          | 97  |

| 11.1. | Esfuerzo en el desarrollo                    | 106 |

| 11.2. | Esfuerzo de portar el algoritmo              | 106 |

| 11.3. | Rendimiento de la suma de matrices           | 107 |

|       | Rendimiento de la multiplicación de matrices |     |

| 11.5. | Rendimiento de la PDE Jacobi                 | 110 |

| 11.6. | Rendimiento de la PDE Jacobi.(cont)          | 111 |

# Parte I Introducción y Planificación

## Capítulo 1

## Introducción

En este capítulo se pretende describir la motivación para la realización de un nuevo modelo que nos simplifique el uso de los aceleradores hardware que es el propósito de este proyecto. Para ello se explicará qué son los aceleradores hardware junto con la problemática a la hora de programar aplicaciones que los utilicen.

Posteriormente se realizará una descripción de los objetivos concretos del proyecto, así como la metodología utilizada para su realización y la estructura del presente documento.

#### 1.1. Dispositivos Aceleradores Hardware

Los aceleradores son dispositivos hardware que se añaden a un sistema informático y que permiten mejorar su rendimiento ejecutando tareas concretas de un programa que se diseñan específicamente para las arquitecturas de dichos dispositivos.

#### 1.1.1. Introducción a los aceleradores

Las plataformas de computación de altas prestaciones incluyen cada vez más aceleradores hardware, como las GPUs, o la XeonPhi entre otros. Esta tendencia es observable desde en máquinas personales hasta en grandes plataformas de supercomputación, como se puede ver por ejemplo en las primeras posiciones de la lista de los 500 mayores supercomputadores del momento [22].

Ahora, con el uso de los aceleradores han aparecido nuevos problemas y soluciones a la hora de programar aplicaciones que aprovechen el potencial de estos dispositivos como se hablará a continuación.

#### 1.1.2. Programación de aceleradores

La programación para plataformas que incluyen aceleradores se basa en dos posibles aproximaciones. La primera es utilizar un modelo único de programación que haga transparente en cierta medida las diferencias conceptuales entre los modelos de programación utilizados en los aceleradores y en los los "hosts" (máquinas convencionales de cómputo donde se alojan los aceleradores). En esta línea se encuentran OpenACC [3] y la propuesta de OpenMP 4.0 [4].

Sin embargo, en estos modelos las aplicaciones que no son altamente regulares y poco sincronizadas no son fáciles de expresar. Además, el código generado no contiene optimizaciones basadas en el conocimiento que tiene el programador de las características del código original que se ejecutará en los aceleradores, ni optimizaciones de parámetros que deban decidirse en tiempo de ejecución.

La segunda es construir programas mezclando modelos de programación diferentes para la computación en aceleradores y en hosts. Ejemplos de esta aproximación incluyen el uso del modelo de paso de mensajes, como por ejemplo MPI [11], con modelos de programación orientados a GPUs de fabricantes concretos, por ejemplo CUDA [2, 8]. Esta aproximación necesita un mayor conocimiento por parte del programador de los modelos, lenguajes y técnicas de programación de los diferentes aceleradores, y la tediosa labor de organizar la gestión de memoria para hacer accesibles los datos a los diferentes aceleradores en los momentos apropiados. A cambio, el programador tiene todo el control sobre los recursos de los dispositivos, pudiendo optimizar su programa para conseguir un buen rendimiento en una máquina concreta.

Además de las aproximaciones contadas anteriormente también existen múltiples propuestas intermedias. OpenCL [19] es un ejemplo de modelo en el que la mayor parte de las tareas de sincronización y manejo de estructuras de datos en un sistema heterogéneo se ocultan. Pero el programador escribe sus kernels teniendo en cuenta el modelo de multihilos agrupados, y las restricciones de sincronización propios de ciertos tipos de aceleradores. De nuevo, la genericidad implica menos capacidad de tomar decisiones automáticas sobre optimizaciones propias de cada plataforma, para obtener el máximo rendimiento. Muchas bibliotecas de funciones específicas para ciertos campos, o ciertas plataformas aceleradoras, incluyen pequeñas abstracciones para facilitar la gestión de memoria entre el acelerador y el host, pero sin capacidad de contemplar optimizaciones guiadas (e.g. MCUDA [20], o hiCUDA [7]).

#### 1.1.3. Dificultades en la programación de aceleradores

Los aceleradores hardware tienen una serie de dificultades que complican el desarrollo de aplicaciones portables que usen dispositivos. Estas dificultades hacen que el tiempo de desarrollo se alargue, en ocasiones significativamente, y obliga a que los programadores deban tener un alto conocimiento del funcionamiento de estos aceleradores. A su vez, el grado de dificultad añadido repercute en un potencial aumento en la cantidad de errores por parte de programador, lo cual deriva en un alargamiento innecesario en el tiempo de desarrollo.

Las dificultades comunes que normalmente nos podemos encontrar durante la programación con aceleradores son las siguientes:

- Escoger una correcta configuración del dispositivo [9, 23]: la configuración indica al acelerador hardware parametros y condiciones en las que tiene que trabajar el dispositivo acelerador para un trabajo determinado. Una buena o mala configuración, adecuada al trabajo a realizar, tiene un importante impacto en la eficiencia del dispositivo y en el tiempo de ejecución.

- Gestión de transferencias [9]: La mayor parte de los dispositivos no pueden acceder directamente a datos que no estén en su espacio de memoria, o si es posible el acceso es muy ineficiente. Esto obliga a que cuando un acelerador necesita un conjunto de datos, estos tengan que ser transferidos previamente a su memoria local, a donde sí puede acceder. Lo mismo ocurre con los resultados de una operación, los cuales se

escriben en la memoria local y después se transfieren donde sean necesarios (el host u otro dispositivo).

• Adaptación de los programas [9]: algunos aceleradores hardware, especialmente las GPUs, usan un modelo de programación diferente al tradicional de CPU. Por este motivo, cuando se desea utilizar un programa CPU (secuencial o paralelo) en una GPU es necesario un proceso de adaptación del programa. Dicho proceso de adaptación tiene que tener en cuenta las características de la plataforma a la que se está adaptando, para poder realizar optimizaciones dependientes de la plataforma los cuales pueden tener un gran impacto en el rendimiento.

## 1.2. Objetivos del proyecto

Como se ha introducido, la programación de aceleradores hardware tiene una serie de dificultades específicas. Estas dificultades obligan a gastar tiempo focalizándose en detalles que están fuera del objetivo de la aplicación que pretenden desarrollar, alargando consecuentemente el tiempo de desarrollo de dichas aplicaciones. A su vez, dichas dificultades, pueden llevar a que el programador, en caso de que no este muy versado en el uso de estos aceleradores o que nunca los haya utilizado, cometa errores, especialmente de configuración y gestión de transferencias.

Este proyecto tiene como principal objetivo buscar una solución a dichos problemas. Para ello se pretende desarrollar un modelo, y un prototipo que verifique este modelo, que cumpla los siguientes objetivos:

- Configuración automática del dispositivo: Si el programador lo desea, por desconocimiento o para reducir el tiempo de desarrollo, debe poder delegar a nuestro modelo la configuración de parámetros y condiciones de ejecución del dispositivo de forma automática.

- Transferencias transparentes al programador: El modelo debe administrar las transferencias sin que el programador tenga que conocer los mecanismos necesarios para que los datos contenidos en las estructuras de datos a transferir lleguen al dispositivo.

- Unificar distintos paradigmas de programación heterogénea: Idear una forma de programación que acerquen los paradigmas de programación entre distintos tipos de aceleradores, permitiendo a los programadores reducir la necesidad de adaptación de los algoritmos o programas.

## 1.3. Metodología utilizada

Este proyecto es un trabajo de investigación en el que se pretende buscar una nueva solución a un problema existente. La investigación no es un trabajo rectilíneo hacia la solución si no que requiere de una evolución constante, donde una vez se ha llegado a la última etapa es posible encontrar posibles mejoras adicionales para la nueva solución. En este tipo situaciones y otras parecidas se necesita un modelo de proceso diseñado explícitamente para adaptarse a un producto que evoluciona con el tiempo. Además la metodología tiene que ser una metodología de investigación la cual difiere ligeramente del las metodologías para el desarrollo de software convencional.

Para cumplir con los requisitos de metodología de este trabajo, éste ha sido basado en el paradigma de hacer prototipos [16] y en el método de investigación en ingeniería del software [1]. El paradigma de hacer prototipos consiste en una metodología evolutiva en el cual durante una serie de iteraciones donde para cada iteración se realizan todos los pasos de: obtención de requisitos, planificar la iteración, análisis y diseño del prototipo, construcción del prototipo y, por último, entrega y evaluación. El método de investigación en ingeniería del software consiste en una metodología donde la investigación se divide en 4 partes diferenciadas: observar las soluciones existentes, proponer mejores soluciones, construir o desarrollar esa nueva solución y analizar sus resultados. Obteniendo así una metodología de investigación basada en prototipos la cual es evolutiva.

Por tanto, la metodología utilizada en este trabajo consiste en realizar una serie de iteraciones donde en cada iteración se realizarán los siguientes pasos: observar las soluciones existentes, planificar la iteración, proponer mejores soluciones, análisis y diseño del prototipo, construcción del prototipo y analizar sus resultados.

- 1. Observar las soluciones existentes: Se trata de una fase exploratoria, donde la documentación relacionada será analizada a fondo con el fin de detectar no sólo las limitaciones que serán abordarse durante el proceso de investigación, sino también posibles mejoras y/o nuevas soluciones aún no contempladas.

- 2. Planificar la iteración: En esta fase se fijarán plazos para las distintas fases de la iteración, asi como los hitos importantes. Esta fase es de suma importancia puesto que asegura que el proyecto entregue resultados en las fechas establecidas.

- 3. Proponer soluciones mejores: Esta fase está dedicada al análisis y diseño de encontrar una mejor solución tratando de superar los límites u obtener ventaja de las posibles mejoras detectadas previamente.

- 4. Análisis y diseño del prototipo: En esta fase se realizará el análisis y diseño del prototipo a partir de la propuesta de solución obtenida.

- 5. Construcción del prototipo: Durante esta fase se realiza la implementación del prototipo junto con las pruebas que validen la buena construcción del mismo.

- 6. Analizar la nueva solución: Los prototipos implementados de las soluciones se evalúan empíricamente, con el fin de corroborar si resuelven los problemas descubiertos en la primera fase.

#### 1.4. Estructura del documento

Esta memoria se encuentra dividida en 5 grandes partes: introducción y planificación, conocimientos previos y propuestas, análisis y diseño, implementación y pruebas, y experimentación y conclusiones.

La primera y presente parte corresponde a la introducción y planificación. Esta parte continuará explicando, en el Capítulo 2, la planificación realizada para el desarrollo del proyecto y posteriormente, en el Capítulo 3, el seguimiento de dicha planificación.

A lo largo de la segunda parte se introducirán diferentes tecnologías necesarias para comprender este proyecto. En el Capítulo 4 se hace una introducción al funcionamiento de

Figura 1.1: Gráfico explicativo de la metodología utilizada.

los dispositivos CUDA y a su modelo de programación permitiendo así entender mejor la motivación de este proyecto. En el Capítulo 5 se inroduce la biblioteca Hitmap usada en la implementación del prototipo del proyecto.

En la tercera parte se realizará un análisis y diseño del proyecto. Primero, en el Capítulo 6, se desarrollará el modelo teórico, el cual posteriormente se desarrollará. En el Capítulo 7 se realizará un pequeño análisis del modelo desarrollado, del cual se obtendrán: los requisitos, los casos de uso y el modelo de objetos; para el desarrollo de un prototipo donde realizar la experimentación. Por último, en el Capítulo 8 se realizará el modelo del diseño del prototipo donde se decidirá su estructura y su forma de actuar.

La cuarta parte se especificará como se ha realizado la implementación, en el Capítulo 9, y las pruebas que se le han realizado al prototipo, en el Capítulo 10). En la implementación se especificarán las herramientas utilizadas, posibles alternativa y porqué se escogió dicha herramienta. Además se explicará como se realizó la implementación de las partes más importantes del prototipo. En las pruebas se especificará la batería de pruebas realizadas y sus correspondientes resultados.

En la quinta y última parte se realizará una serie de experimentos, en el Capítulo 11, con los que se desea medir el rendimiento del modelo y el esfuerzo de programar utilizando el modelo elegido. A partir de la experimentación se obtendrán una serie de resultados que se utilizarán en el Capítulo 12 para sacar conclusiones sobre el modelo y el propio proyecto.

## Capítulo 2

# Planificación del proyecto

En este capítulo se va a describir la planificación del proyecto. La planificación de un proyecto consiste en el planteamiento, la organización y el control de los recursos con motivo de alcanzar los objetivos del mismo.

Este capítulo se divide en cinco secciones. En la primera sección se explican los artefactos más importantes que conforman el proyecto. En la segunda sección se especifica cómo se va a gestionar el tiempo del que se dispone para la realización del proyecto. En la tercera sección se especifica como se va a gestionar el coste del proyecto. En la cuarta sección se listan los riesgos y cómo se debe actuar en caso de que ocurran. Por último, en la quinta sección se especifica como se va a realizar la gestión de configuraciones, es decir, almacenamiento de los artefactos, control de cambios, etc.

## 2.1. Entregables del proyecto

Durante el desarrollo del proyecto se generan y utilizan una serie de artefactos, quienes son objeto de modificaciones. Al término de este desarrollo, dichos artefactos conforman la documentación del proyecto, la cual está recopilada en la presente memoria. Los artefactos que pertenecen a este proyecto son:

- Gestión del Proyecto: son los documentos relacionados con la planificación y el seguimiento del proyecto. Esta documentación consta de los siguientes artefactos:

- Planes de iteración (S. 2.2.1): Es el conjunto de todas las actividades pertenecientes a una iteración programadas con sus dependencias.

- Plan de riesgos (S. 2.4): Este documento incluye una lista de los riesgos conocidos y vigentes en el proyecto junto con las acciones específicas a realizar en caso de que ocurra.

- Seguimiento del proyecto (C. 3): Este documento contiene los cambios que se producen sobre lo planificado e intenta evitar situaciones críticas como consecuencia de los mismos.

- Análisis y diseño: Son los documentos relacionados con el desarrollo del sistema. Contiene los siguientes artefactos.

- Modelo propuesto (C. 6) Contiene el modelo teórico propuesto en este proyecto que será el que se desarrolle. Aquí se explica como funciona y sus capacidades.

- Modelo de Análisis (C. 7) Contiene una visión inicial del comportamiento del sistema, así como la lista de requisitos que debe cumplir, los casos de uso y el modelo de objetos.

- Modelo de Diseño (C. 8) Contiene los modelos del diseño que se va a implementar en el prototipo, detallando la estructura estática del sistema.

- Implementación: contiene toda la documentación relativa a la implementación del proyecto. Consta de los siguientes artefactos:

- Modelo de implementación (C. 9): Contiene una descripción de los detalles de la implementación del prototipo. Especialmente las herramientas utilizadas y cómo se han resuelto los problemas encontrados.

- Pruebas (C. 10): Contiene la especificación de cada una de las pruebas realizadas, junto con su entrada y su salida esperada. Además, contiene las tablas con los resultados de dichas pruebas.

- Código fuente (CD-ROM, ver anexo A)

- Experimentación (C. 11): Contiene la especificación y los resultados de los experimentos realizados sobre el prototipo creado.

#### 2.2. Gestión de tiempo

Durante el desarrollo de un proyecto con un plazo de tiempo limitado es importante tener en cuenta en qué se usa el tiempo. Una buena gestión del tiempo permite realizar el proyecto en la mayor brevedad posible, al paralelizar trabajos por ejemplo. La gestión del tiempo también permite reducir las repercusiones de un retraso en una tarea.

#### 2.2.1. Planes de iteración

#### Plan iteración 1

En la primera iteración se tiene como objetivo crear una versión del prototipo con la interfaz que debiera tener una biblioteca que implementa nuestro modelo. Para lograr esto, es necesario realizar un estudio del estado del arte y de tecnologías relacionadas con este proyecto. A partir de esto, se pensará en varias propuestas de modelo de entre las cuales se seleccionará y desarrollará uno, a partir del cual se desarrollará un prototipo.

El prototipo en esta iteración será una interfaz sin ningún tipo de funcionalidad. Esta interfaz sin funcionalidad constará de una serie de funciones que no realizan ninguna acción, que al aplicarla sobre un problema, nos permitirá medir el esfuerzo de desarrollo y comprobar así si nuestro modelo simplifica la programación.

Para las pruebas se utilizará un problema frecuente en computación de alto rendimiento programado tanto usando la nueva interfaz como sin usarla. Esto nos permitirá comparar el esfuerzo de desarrollo, es decir, el coste de programarlo, aunque el prototipo no sea funcional.

La lista de actividades de la primera iteración se puede observar en el Cuadro 2.1, asi como los diagramas de Gantt correspondientes en las Figuras 2.1 y 2.2.

Figura 2.1: Diagrama de Gantt Iteración 1

| No | Nombre de la actividad               | Fecha inicio | Fecha fin | Actividades |

|----|--------------------------------------|--------------|-----------|-------------|

|    |                                      |              |           | Precedentes |

| 1  | Inicio                               | 2/03/15      | 2/03/15   |             |

| 2  | Aprendizaje de CUDA                  | 2/03/15      | 15/03/15  | 1           |

| 3  | Aprendizaje de Hitmap                | 16/03/15     | 22/03/15  | 1           |

| 4  | Exploración del estado del arte      | 23/03/15     | 29/03/15  | 2,3         |

| 5  | Propuesta de posibles modelos        | 30/03/15     | 3/04/15   | 4           |

| 6  | Selección de modelo                  | 4/04/15      | 4/04/15   | 5           |

| 7  | Búsqueda de problemas de referencia  | 4/04/15      | 5/04/15   | 6           |

| 8  | Desarrollo del modelo                | 6/04/15      | 13/04/15  | 6           |

| 9  | Análisis del prototipo               | 14/04/15     | 17/04/15  | 8           |

| 10 | Diseño del prototipo                 | 18/04/15     | 20/04/15  | 9           |

| 11 | Construcción del prototipo           | 21/04/15     | 24/04/15  | 10          |

| 12 | Construcción del experimento Jacobi: | 25/04/15     | 29/04/15  | 7           |

|    | GPU vRef                             |              |           |             |

| 13 | Construcción del experimento Jacobi: | 30/04/15     | 2/05/15   | 7,11        |

|    | GPU v1                               |              |           |             |

| 14 | Experimentación                      | 3/05/15      | 4/05/15   | 12,13       |

| 15 | Planificación siguiente iteración    | 5/05/15      | 6/05/15   | 14          |

| 16 | Fin                                  | 7/05/15      | 7/05/15   | 15          |

Cuadro 2.1: Actividades de la primera iteración

#### Plan iteración 2

En la iteración anterior se demostró que el uso de los comunicadores realmente reducía el esfuerzo en el desarrollo. Para la segunda iteración se revisará el modelo añadiendo las modificaciones que se consideren oportunas a partir de lo ya observado en la iteración anterior.

Junto con las modificaciones en el modelo, se deberá realizar un prototipo funcional que implemente la mayor parte de las funcionalidades que se plantean. Este prototipo se utilizará para realizar mediciones de rendimiento que nos permitirán determinar el overhead en tiempo de ejecución que se produce con el uso de este modelo. Para medirlo en un caso práctico, se utilizará el mismo problema de la iteración anterior pero adaptado a la nueva versión del prototipo. Así, comparando los resultados con los de la versión de referencia podremos ver la diferencia en el rendimiento. En esta iteración se volverá a medir el esfuerzo de desarrollo con el fin de comprobar que los cambios realizados en el modelo no aumentan el esfuerzo de desarrollo obtenido en la primera iteración. Los resultados de la experimentación de esta iteración servirán para la preparación de un articulo, incluido en la planificación, para las Jornadas de Paralelismo.

La lista de actividades de la segunda iteración se puede observar en el Cuadro 2.2, asi como el diagrama de Gantt la Figura 2.3.

#### Plan iteración 3

Para la tercera iteración se modificará el modelo añadiendo la posibilidad de poder tratar un conjunto de núcleos de la CPU como si fuera un acelerador hardware externo. Posteriormente se deberá modificar el prototipo para que se adapte de nuevo al modelo, junto con

| No | Nombre de la actividad                   | Fecha inicio | Fecha fin | Actividades |

|----|------------------------------------------|--------------|-----------|-------------|

|    |                                          |              |           | Precedentes |

| 1  | Inicio                                   | 7/05/15      | 7/05/15   |             |

| 2  | Modificación del modelo                  | 7/05/15      | 8/05/15   | 1           |

| 3  | Análisis del prototipo                   | 9/05/15      | 10/05/15  | 2           |

| 4  | Diseño del prototipo                     | 11/05/15     | 14/05/15  | 3           |

| 5  | Construcción del prototipo               | 15/05/15     | 18/05/15  | 4           |

| 6  | Construcción del experimento Jacobi:     | 19/05/15     | 20/05/15  | 5           |

|    | GPU v2                                   |              |           |             |

| 7  | Experimentación                          | 21/05/15     | 22/05/15  | 6           |

| 8  | Redacción del artículo para las Jornadas | 23/05/15     | 3/05/15   | 7           |

|    | de Paralelismo                           |              |           |             |

| 9  | Revisión del artículo                    | 4/06/15      | 7/06/15   | 8           |

| 10 | Entrega del artículo                     | 8/06/15      | 8/06/15   | 9           |

| 11 | Planificación de la siguiente iteración  | 8/06/15      | 9/06/15   | 10          |

| 12 | Fin                                      | 10/06/15     | 10/06/15  | 11          |

Cuadro 2.2: Actividades de la segunda iteración

los experimentos ya creados para que se adapten al mismo. Así mismo, se deberán obtener versiones de referencia de CPU para un conjunto más amplio de aplicaciones incluyendo Jacobi, la suma de matrices y la multiplicación de matrices, al igual que versiones de referencia de GPU para la suma de matrices y la multiplicación de matrices. Además, también se deberán construir versiones de los experimentos usando nuestro prototipo. En esta iteración se medirá el esfuerzo de desarrollo, el overhead y el coste de migrar una versión de GPU a una de CPU y viceversa. Los resultados de la experimentación de esta iteración servirán para la preparación de un articulo, incluido en la planificación, para el workshop HLPGPU celebrado dentro de la conferencia HiPEAC.

La lista de actividades de la segunda iteración se puede observar en el Cuadro 2.3, así como el diagrama de Gantt la Figura 2.4.

## 2.3. Costes del proyecto

Las estimaciones de costes son necesarias para establecer un presupuesto para el proyecto o para asignar un precio para el software de un cliente. Existen tres parámetros involucrados en el cálculo del coste total de un proyecto de desarrollo de software.

- Los costes hardware y software, incluyendo el mantenimiento.

- Los costes de viaje y capacitación.

- Los costes de esfuerzo.

Tanto en este proyecto como en otros muchos, los costes dominantes son los costes de esfuerzo. Los ordenadores con potencia suficiente para desarrollar software son relativamente baratos. Por otro lado, el software necesario para el desarrollo de la mayoría del Proyecto ha sido gratuito, dado que todos poseen licencia libre. Aunque haya costes de viaje, son una pequeña parte comparados con los costes de esfuerzo. Además, el uso de correo electrónico,

| No | Nombre de la actividad               | Fecha inicio | Fecha fin | Actividades   |

|----|--------------------------------------|--------------|-----------|---------------|

|    |                                      |              |           | Precedentes   |

| 1  | Inicio                               | 1/10/15      | 1/10/15   |               |

| 2  | Modificación del modelo              | 1/10/15      | 4/10/15   | 1             |

| 3  | Análisis del prototipo               | 5/10/15      | 6/10/15   | 2             |

| 4  | Diseño del prototipo                 | 7/10/15      | 12/10/15  | 3             |

| 5  | Construcción del prototipo           | 13/10/15     | 17/10/15  | 4             |

| 6  | Construcción del experimento Jacobi: | 18/10/15     | 19/10/15  | 1             |

|    | CPU vRef                             |              |           |               |

| 7  | Construcción del experimento Jacobi: | 20/10/15     | 20/10/15  | 5             |

|    | CPU v1                               |              |           |               |

| 8  | Construcción del experimento Matri-  | 21/10/15     | 22/10/15  | 1             |

|    | xAdd: CPU y GPU vRef                 |              |           |               |

| 9  | Construcción del experimento Matri-  | 23/10/15     | 24/10/15  | 5             |

|    | xAdd: CPU y GPU v1                   |              |           |               |

| 10 | Construcción del experimento Matrix- | 25/10/15     | 26/10/15  | 1             |

|    | Mult: CPU y GPU vRef                 |              |           |               |

| 11 | Construcción del experimento Matrix- | 27/10/15     | 28/10/15  | 5             |

|    | Mult: CPU y GPU v1                   |              |           |               |

| 12 | Experimentación                      | 29/10/15     | 30/10/15  | 6,7,8,9,10,11 |

| 13 | Redacción del artículo para HLPGPU   | 31/10/15     | 11/11/15  | 12            |

| 14 | Revisión del articulo                | 12/11/15     | 15/11/15  | 13            |

| 15 | Entrega del articulo                 | 16/11/15     | 16/11/15  | 14            |

| 16 | Fin                                  | 16/11/15     | 16/11/15  | 15            |

Cuadro 2.3: Actividades de la tercera iteración

Figura 2.4: Diagrama de Gantt Iteración 3

| Concepto                                                  | Cantidad         | Precio (€) |  |  |  |  |

|-----------------------------------------------------------|------------------|------------|--|--|--|--|

| Herramientas de desarrollo                                |                  |            |  |  |  |  |

| Ubuntu Linux 14.10                                        | 1                | 0,00       |  |  |  |  |

| CMake v2.8.11                                             | 1                | 0,00       |  |  |  |  |

| GCC v4.8.3                                                | 1                | 0,00       |  |  |  |  |

| GDB v7.6.1                                                | 1                | 0,00       |  |  |  |  |

| VIM v7.4                                                  | 1                | 0,00       |  |  |  |  |

| GanttProject v2.7.1                                       | 1                | 0,00       |  |  |  |  |

| Inkscape v0.91                                            | 1                | 0,00       |  |  |  |  |

| I⁴T <sub>E</sub> X                                        | 1                | 0,00       |  |  |  |  |

| DropBox                                                   | 1                | 0,00       |  |  |  |  |

| GitLab                                                    | 1                | 0,00       |  |  |  |  |

| Subtotal                                                  |                  | 0,00       |  |  |  |  |

| $Mcute{aquinas}$                                          |                  |            |  |  |  |  |

| Acer Travelmate 5740-334G32MN                             | 1                | 496,00     |  |  |  |  |

| Subtotal                                                  |                  | 496,00     |  |  |  |  |

| Alquiler Máquinas                                         |                  |            |  |  |  |  |

| Intel Xeon CPU E5-2620 (24 CPUs) con tarjeta gráfica Nvi- | 384 (h*cpu)      | 2,00       |  |  |  |  |

| dia GeForce GTX Titan Black                               |                  |            |  |  |  |  |

| Subtotal                                                  |                  | 768,00     |  |  |  |  |

| Alquiler Servidores                                       |                  |            |  |  |  |  |

| VPS                                                       | 12 meses         | 10,00      |  |  |  |  |

| Subtotal                                                  |                  | 120,00     |  |  |  |  |

| Horas de trabajo                                          | Horas de trabajo |            |  |  |  |  |

| Número de horas                                           | 1168             | 12.50      |  |  |  |  |

| Subtotal                                                  |                  | 14.600,00  |  |  |  |  |

| Total                                                     |                  | 15.984,00  |  |  |  |  |

Cuadro 2.4: Presupuesto estimado

teléfono y sitios web compartidos reducen el coste de los viajes y del tiempo hasta en un  $50\,\%$ .

Los costes de esfuerzo no son sólo los salarios de los ingenieros que intervienen en el proyecto. Las organizaciones calculan los costes de esfuerzo en función de los costes totales, donde se tiene en cuenta el coste total para hacer funcionar la organización y dividen éste entre el número de personas productivas. Por lo tanto, los siguientes costes son parte de los costes totales:

- 1. Costes de proveer, aclimatar e iluminar oficinas.

- Los costes del personal de apoyo como administrativos, secretarias, limpiadores y técnicos.

- 3. Los costes de redes y de comunicaciones.

- Los costes de los recursos centralizados como las bibliotecas, los recursos recreativos, etc.

- 5. Los costes de seguridad social, pensiones seguros privados, etc.

Según Sommerville [18], este factor de carga normalmente es el doble del salario de un ingeniero del software, dependiendo del tamaño de la organización y sus sobrecargas asociadas. Sin embargo, como en nuestro proyecto todos los costes mencionados corren a cargo de la Universidad de Valladolid, se ha decidido no tenerlos en cuenta a la hora de elaborar un presupuesto. Por tanto, teniendo todo esto en cuenta, el coste aproximado sería de: 15.984 €. En el Cuadro 2.4 se puede ver un desglose de los costes estimados de este proyecto. Hay que tener en cuenta que el coste de alquiler del cluster usado para experimentación se calcula como CosteAlquiler = HorasComputacion \* NumeroProcesadores \* Precio donde se han calculado unas 8 horas de computación por iteración (segunda y tercera iteración). El precio de alquiler por hora se estima en función de costes medios habituales en centros de supercomputación regionales o del CIEMAT.

## 2.4. Gestión de riesgos

Durante el desarrollo de un proyecto pueden surgir contratiempos que afecten al proyecto provocando pérdidas y retrasos. Un riesgo es un posible problema que tiene potencial para producirse en el proyecto. Para evitar los riesgos se va a realizar una lista con todos los posibles casos y crear un plan de acción para cada uno en caso de que surja.

#### 2.4.1. Perspectiva general

Los riesgos que se listan a continuación se describen mediante una serie de campos:

- **Probabilidad:** Estimación de la probabilidad de que se produzca el riesgo. Los posibles valores que puede tener este campo según su probabilidad: muy baja (<=0,2), baja (>0,2 y <=0,4), media (>0,4 y <=0,6), alta (>0,6 y <=0,8) y muy alta (>0,8).

- Consecuencias: Indica el nivel de magnitud e importancia que se le da a las posibles consecuencias que producirá el riesgo en caso de que se haga realidad. Los posibles valores son: despreciable (<=0,2), marginal (>0,2 y <=0,4), crítico (>0,4 y <=0,8) y catastrófico (>0,8).

- Descripción: Contienen una descripción del riesgo indicando como podría producirse.

- Contexto: Contiene una explicación del contexto en el que se puede desarrollar el riesgo descrito. Principalmente describe cuándo, cómo y por qué puede producirse un riesgo.

- **Análisis:** Se hace una breve descripción de las consecuencias que podrían producirse en caso de que el riesgo se haga realidad.

- Estrategia de resolución: Tipo de estrategia que se utilizará para solventar el problema en caso de que se produzca un riesgo. Estas estrategias podrán ser:

- Evasión: previene la ocurrencia del riesgo reduciendo su probabilidad a cero.

- Protección: reduce la probabilidad y/o consecuencia del riesgo antes de que ocurra.

- Reducción: reduce la probabilidad y/o consecuencia del riesgo después de que ocurra.

- Investigación: obtener más información para eliminar o reducir la incertidumbre

- Reserva: utilizar la planificación reservada previamente o la holgura del presupuesto.

- Transferencia: reorganizar las cosas para desplazar el riesgo a cualquier parte (por ejemplo, a otro grupo)

Hay que considerar además la aceptación del riesgo que se produce cuando el coste de la evitación del riesgo puede ser más grande que el coste que puede suponer si se produce.

■ Plan de acción: Descripción de las medidas que se tomarán en caso de que se produzca el riesgo.

#### 2.4.2. Lista de riesgos

#### R-1. Cambios en la propuesta modelo

Probabilidad: Depende de la iteración:

■ Primeras iteraciones: Alta (0.8)

■ Últimas iteraciones: Baja (0.4)

Consecuencias: Depende de la iteración:

■ Primeras iteraciones: Marginal (0.3)

• Últimas iteraciones: Crítico (0.7)

**Descripción:** El modelo teórico, que contiene la solución propuesta, puede ser modificado. Estas modificaciones pueden ser mejorar la descripción de alguno de los conceptos que introduce o añadir un nuevo concepto alterando drásticamente el modelo.

Contexto: Durante el desarrollo del prototipo, los casos de prueba e incluso la experimentación, se pueden detectar errores o posibles mejoras en la solución propuesta. Dichos errores o propuestas pueden llevar a una modificación del modelo teórico añadiendo o modificando alguno de los conceptos del mismo.

Análisis: Una modificación del modelo, dependiendo de la gravedad de las modificaciones, puede tener grandes consecuencias. Esto se debe a que las modificaciones en el modelo implica que de debe modificar todo aquello que dependa de él, provocando graves retrasos en el desarrollo del prototipo.

Estrategia de resolución: Investigación y Reducción

Plan de acción: En caso de que se detecte una posible mejora, se deberá estudiar las consecuencias de introducir dicho cambio en el modelo. En el estudio se tendrá en cuenta si el cambio está dentro del marco de los objetivos del proyecto, el coste de modificar el prototipo y el coste de realizar la experimentación necesaria añadida. Una vez realizado este estudio se decidirá si se aplicará dicho cambio al modelo y la iteración, la presente o la siguiente, en la que se realizará el cambio.

# R-2. Cambios en los requisitos

**Probabilidad:** Depende de la iteración:

■ Primeras iteraciones: Alta (0.9)

■ Últimas iteraciones: Baja (0.4)

Consecuencias: Depende de la iteración:

■ Primeras iteraciones: Despreciable (0.1)

■ Últimas iteraciones: Crítico (0.7)

**Descripción:** Durante el desarrollo del proyecto cabe la posibilidad de que ocurran algunos cambios en los requisitos, tanto los funcionales como los no funcionales.

Contexto: En las distintas etapas del desarrollo del prototipo es posible que se detecte una nueva funcionalidad que deba ser añadida, o tipos de problemas a los que se puede aplicar el proyecto que no se han contemplado con anterioridad, incurriendo en la posible necesidad de un cambio en los requisitos. En cualquier caso puede resultar relevante añadirlos en el marco de desarrollo del prototipo puesto que pueden permitir adaptarse mejor al modelo teórico planteado.

Análisis: El impacto de los cambios de requisitos puede afectar significativamente al desarrollo del prototipo incrementando el coste y tiempo de desarrollo. Estos cambios pueden hacer que se cambie el diseño y la implementación e incluso ambos, además de obligar a volver a realizar la experimentación. Dicha avalancha de cambios, cuya gravedad depende del estado de desarrollo del prototipo, puede provocar que el proyecto no sea terminado en el plazo establecido.

Estrategia de resolución: Investigación y Reducción

Plan de acción: Una vez que se ha detectado un posible cambio en los requisitos del prototipo se analizará el impacto de realizar ese cambio concreto. Dependiendo del impacto y la fase en la que se ha detectado se actuará de la siguiente forma: en las primeras fases de la iteración, siempre se realizarán los cambios; sin embargo, en las etapas finales se realizará únicamente cuando el impacto sea trivial o su realización sea crítica. Cuando no se realiza un cambio en la iteración actual, estos cambios se realizarán en la siguiente iteración.

# R-3. No completitud o ambigüedad de los requisitos

Probabilidad: Baja (0.4)

Consecuencias: Crítico (0.7)

**Descripción:** Los requisitos que fueron analizados que se están utilizando como base en nuestro prototipo, pueden no estar completos o no entenderse claramente.

Contexto: Durante el desarrollo del prototipo, se utilizan los requisitos para saber qué funcionalidad se debe implementar. Los requisitos se obtienen a partir de la propuesta del modelo desarrollada previamente, la cual puede no ser comprendida completamente a la hora de realizar los requisitos. A su vez, los requisitos pueden tener una mala redacción lo cual puede derivar en confusión a la hora de interpretarlos.

Análisis: Esto puede resultar en que el prototipo no cumpla completamente con los objetivos impuestos y no sirva para la experimentación que demuestre la eficacia del modelo teórico.

Estrategia de resolución: Investigación y Reducción

Plan de acción: Lo primero que se debe realizar es un análisis de la importancia en cuanto a los requisitos ambiguos, a la vez que se analiza el impacto en el cambio de éstos. Aquellos requisitos con gran importancia, independientemente del impacto que produzca, o con impacto despreciable serán modificados o añadidos en la misma iteración. Para los requisitos con menor importancia, pero con impacto apreciable, sus cambios se aplicarán en iteraciones posteriores.

### R-4. Mal diseño

**Probabilidad:** Media (0.3)

Consecuencias: Marginal (0.4)

**Descripción:** El modelo de diseño realizado puede no tener el nivel de detalle suficiente, dejando muchos puntos abiertos, o mostrar incoherencias.

Contexto: Al comenzar las tareas de implementación, o durante su realización, faltan detalles en el diseño teniendo que tomar en este momento decisiones que ya deberían haber sido tomadas. Esto puede surgir debido a que el diseñador no ha tenido en cuenta completamente todos los escenarios posibles, o se le ha pasado por alto algún detalle crucial.

Análisis: Un diseño incompleto, o con incoherencias, puede afectar de forma grave al desarrollo del proyecto, pues se desplaza parte de la carga de trabajo de la fase de diseño a la de implementación alargando el mismo y produciendo grandes retrasos no planificados en éste. Esto se magnifica si la parte incompleta del diseño afecta, en mayor o menor medida, a otra parte del diseño impidiendo su implementación.

# Estrategia de resolución: Reducción

Plan de acción: Lo que se debe hacer en este caso es modificar las partes del diseño que sean vitales y nos permitan realizar un prototipo funcional. Estas modificaciones no tienen que ser el mejor diseño posible pero si tienen que ser un diseño suficiente para que el prototipo sea válido. Todos aquellos errores encontrados, tanto los arreglados como los que no, se tendrán en cuenta durante la fase de diseño de la iteración siguiente.

# R-5. Retraso en la finalización de las actividades

**Probabilidad:** Media (0.5)

Consecuencias: Crítico (0.5)

**Descripción:** El desarrollo de las actividades termina fuera del plazo establecido para ello.

Contexto: Durante el desarrollo de una actividad, pueden surgir una serie de contratiempos que finalmente pueden ocasionar un retraso en la actividad. Esto puede ser debido a eventos inesperados, que se produzcan riesgos o recursos insuficientes.

Análisis: El retraso en la finalización de actividades supone un problema respecto al cumplimiento de los plazos de las actividades siguientes, no sólo las que dependen de esta, si no también de las que no, puesto que el equipo de desarrollo tiene un número limitado de recursos humanos. Cuanto más adelante ocurra, peores son las consecuencias puesto que más cercana se encuentra la fecha de entrega y se dispone de menos tiempo para subsanar las consecuencias.

# Estrategia de resolución: Reserva y Reducción.

Plan de acción: En caso de que se produzca el riesgo será necesario hacer un reajuste en la planificación empleando las posibles holguras para comprobar la gravedad del tiempo perdido. En caso de que se produzca un retraso grave o cualquier nivel de gravedad en fechas cercanas a la fecha de entrega, se aumentará el tiempo dedicado al proyecto (horas extra) para recuperar el tiempo perdido, con su consiguiente aumento en el coste del proyecto.

### R-6. Errores en bibliotecas de terceros

Probabilidad: Media (0.4)

Consecuencias: Marginal (0.3)

**Descripción:** Durante la fase de construcción se detecta un error en una biblioteca que no pertenece al proyecto.

Contexto: Mientras se está implementando o en las pruebas, es posible que se detecten incoherencias en los resultados de una función de una biblioteca de terceros. Esto puede ocurrir con mucha frecuencia puesto que, entre otros, las bibliotecas que se usan son prototipos de otros equipos de investigación.

**Análisis:** Esto puede producir un retraso en las actividades que dependan de la funcionalidad con errores de estas bibliotecas de terceros.

Estrategia de resolución: Reducción y Transferencia.

Plan de acción: En el caso de que ocurra el riesgo, la primera acción a tomar es intentar evitar esa funcionalidad usando funciones similares de la misma biblioteca o de otras y reportar el error al equipo de desarrollo de la otra biblioteca. En caso de no ser posible evitar su uso se intentará implementar por cuenta propia dicha funcionalidad. Por último, si no ha sido posible implementar esa funcionalidad por cuenta propia tan sólo queda ponernos en contacto con el equipo de desarrollo de la biblioteca.

# R-7. Pérdida de datos

**Probabilidad:** Baja (0.3)

Consecuencias: Catastrófico (1.0)

**Descripción:** Pérdida parcial o total de documentación, resultados experimentales y/o código fuente.

**Contexto:** En cualquier momento, debido a un error humano o un fallo catastrófico en el hardware o en el software, se pueden perder parte o la totalidad de los datos relativos al proyecto.

Análisis: La pérdida de los datos puede conllevar a grandes consecuencias, mayores cuanto más avanzado esté el proyecto y más próxima esté la fecha de finalización del proyecto, puesto que puede sea necesario volver a realizar la totalidad o parte el trabajo que se ha realizado hasta el momento.

Estrategia de resolución: Evasión y Protección.

Plan de acción: Para evitar la perdida de datos se usaran sistemas de control de versiones. Estos sistemas impiden que por error humano se borre un archivo o datos que nunca deberían ser borrados al poder recuperar en cualquier momento dicha versión del mismo. En caso de error de hardware, estas pérdidas se reducirán mediante el uso de copias de seguridad; tanto en discos físicos, servidores remotos o sistemas en la nube; que nos permitan recuperar versiones anteriores al fallo o por lo menos una versión lo más actualizada posible. Los sistemas utilizados se explicarán con más detalle en la sección 2.5.

### R-8. Fallos del hardware

**Probabilidad:** Muy baja (0.2)

Consecuencias: Marginal (0.4)

**Descripción:** Una de las máquinas de experimentación sufre un fallo de hardware que requiere de una sustitución de componentes.

Contexto: Las máquinas de experimentación al igual que cualquier ordenador puede estropearse en cualquier momento pudiendo necesitar de piezas de repuesto. Estas piezas de repuesto no se pueden cambiar inmediatamente. Se necesita tiempo para que el encargado del mantenimiento pueda realizar las reparaciones, pudiendo tardar desde unas pocas horas a varios días. Durante este tiempo, la maquina no estará disponible para su uso.

Análisis: Las máquinas de experimentación son necesarias durante la fase de experimentación, no siendo necesarias durante el resto de fases. Estos experimentos se utilizarán para obtener los resultados experimentales, los cuales son importantes para el desarrollo del proyecto.

Estrategia de resolución: Evasión, Protección y Reserva.

Plan de acción: Utilizar para la experimentación máquinas dentro de un sistema de colas que seleccione automáticamente una de las máquinas disponibles. En caso de fallo, se puede utilizar otra de las máquinas disponibles para la experimentación. También es posible realizar otras tareas, estudiando la planificación, para dar tiempo a los técnicos a realizar las reparaciones.

# R-9. Enfermedad del alumno

**Probabilidad:** Media (0.4)

Consecuencias: Crítico (0.8)

**Descripción:** El alumno sufre una enfermedad que le impide trabajar temporalmente en el proyecto.

Contexto: Las personas pueden enfermar especialmente en invierno. Durante el periodo de enfermedad no es posible realizar ningún trabajo relacionado con el proyecto. Dependiendo de la gravedad o la enfermedad esto se puede alargar por un único día a varias semanas.

**Análisis:** El proyecto no puede avanzar mientras el alumno está enfermo. Esto puede tener graves consecuencias en el avance del proyecto al causar retrasos en las diferentes actividades que conforman el proyecto.

Estrategia de resolución: Reserva.

Plan de acción: En caso de que se produzca el riesgo será necesario hacer un reajuste en la planificación empleando las posibles holguras. Además, se aumentará el tiempo dedicado al proyecto (horas extra) para recuperar el tiempo perdido, con su consiguiente aumento en el coste del proyecto.

# 2.4.3. Riesgos priorizados

Una vez que hemos identificado los riesgos se va a realizar una lista priorizada con ellos que servirá para ver cuales hay que tener más en cuenta. Esta lista se ordenará por la exposición al riesgo que es el producto de la probabilidad por las consecuencias (Exposicion = Probabilidad \* Consecuencias). Para que sea más sencillo de entender la exposición al riesgo se categoriza en los siguientes valores: bajo (<=0.1), moderado (>0.1 - <=0.2), significante (>0.2 - <=0.3), alto (>0.3). En los riesgos que tengan varios valores en probabilidad y/o consecuencias se tendrá en cuenta el peor caso (el valor mayor) a la hora mostrar los datos y de ordenar. La lista priorizada de los datos se puede ver en la Cuadro 2.5.

| Riesgo                          | Consecuencias      | Probabilidad  | Exposición          |

|---------------------------------|--------------------|---------------|---------------------|

| R-9. Enfermedad del alumno      | Crítico (0.8)      | Media (0.4)   | Alto (0.32)         |

| R-7. Pérdida de datos           | Catastrófico (1.0) | Baja (0.3)    | Significante (0.3)  |

| R 1. Cambios en la propuesta    | Crítico (0.7)      | Baja (0.4)    | Significante (0.28) |

| de modelo                       |                    |               |                     |

| R-2. Cambios en los requisitos  | Crítico (0.7)      | Media (0.4)   | Significante (0.28) |

| (Etapa Construcción)            |                    |               |                     |

| R 3. No completitud o ambi-     | Crítico (0.7)      | Baja (0.4)    | Significante (0.28) |

| güedad de los requisitos.       |                    |               |                     |

| R 5. Retraso en la finalización | Crítico (0.5)      | Media (0.5)   | Significante (0.25) |

| de actividades.                 |                    |               |                     |

| R 4. Mal diseño.                | Marginal (0.4)     | Media (0.3)   | Moderado (0.12)     |

| R-6. Errores en bibliotecas de  | Marginal $(0.3)$   | Media (0.4)   | Moderado (0.12)     |

| terceros                        |                    |               |                     |

| R-8. Fallos del hardware        | Marginal (0.4)     | Muy baja(0.1) | Bajo (0.04)         |

Cuadro 2.5: Lista priorizada de los riesgos

# 2.5. Gestión de configuraciones

El actual proyecto tiene como propósito el desarrollo de un modelo de programación. Por tanto dicho proyecto constará principalmente de artefactos relativos a la documentación, código fuente del prototipo y de los casos de estudio, y los resultados experimentales. A continuación hablaremos con más detalle de cómo se gestionarán los distintos tipos de artefactos.

# 2.5.1. Documentación

Toda la documentación, incluido el presente documento, se almacenará en un directorio en la nube usando el servicio de Internet llamado Dropbox y al finalizar el proyecto, también se almacenará en el CD-ROM que acompaña a este documento (ver apéndice A).

Dropbox es un servicio en la nube que te permite sincronizar de forma automática todo el contenido de un directorio de tu equipo con un directorio virtual en sus servidores. A este servicio pueden estar conectados múltiples dispositivos, lo cual nos permite acceder al contenido de la carpeta virtual desde cualquiera de los ordenadores en los que trabajemos, sincronizando la carpeta o accediendo a través de su aplicación web, o podemos acceder a través de dispositivos móviles mediante su app. Además Dropbox también nos ofrece un sistema sencillo de control de versiones, lo cual nos aporta seguridad en caso de borrado o modificación indebida de algún documento.

# 2.5.2. Código fuente del prototipo y de los casos de estudio

El código fuente del prototipo y de los casos de estudio se almacenará en un repositorio de código en una VPS (Virtual Private Server) usando la aplicación GitLab y al finalizar el proyecto, también se almacenará la última versión en el CD-ROM que acompaña a este documento (ver apéndice A). Dicha VPS estará almacenada en un servidor con discos redundantes al cual se le realizarán copias de seguridad semanales. La propia máquina virtual también sincroniza sus datos con otra VPS de mismas características.

GitLab es una aplicación web para la gestión de repositorios git. Además de repositorios git también tiene soporte para wiki y gestión de incidencias lo cual nos permite una gestión más completa de nuestros proyectos software. Por último, también es compatible con otras servicios de gestión de repositorios como GitHub, permitiéndonos importar proyectos que tuvieramos almacenados allí.

# 2.5.3. Resultados experimentales

Los resultados experimentales, son un caso especial de documentación formada por archivos de texto plano que contienen los resultados de los experimentos realizados con el prototipo. Una vez realizados los experimentos, estos archivos no se pueden modificar y se almacenarán en un archivo comprimido junto con la documentación del proyecto. En dicho archivo comprimido se indicará la máquina donde se ha realizado la experimentación y con qué versión del prototipo se ha probado.

Los resultados experimentales, al igual que la documentación, se almacenará en un directorio en la nube usando el servicio de Internet llamado Dropbox; también se almacenará en la máquina donde se realizaron las pruebas y al finalizar el proyecto, se almacenará la última versión en el CD-ROM que acompaña a este documento (ver apéndice A).

# Capítulo 3

# Seguimiento del proyecto

En el presente capítulo se describe cómo se ha realizado el trabajo de desarrollo del proyecto con respecto al plan previsto durante las diferentes iteraciones. Este seguimiento se realiza para poder detectar cualquier inconsistencia, en términos de tiempo, entre la planificación y las actividades que se están realmente realizando.

# 3.1. Seguimiento de las iteraciones

Para cada iteración se muestra la siguiente información:

- Desarrollo real: aquí se muestran las fechas de inicio y fin reales de cada actividad realizada junto con la diferencia en días entre la fecha de finalización planificada y la real.

- Riesgos producidos: se manifiestan los riesgos que se han producido y cómo se ha llevado a cabo el plan previsto.

- Observaciones: cualquier otro detalle observado durante la iteración.

# 3.1.1. Seguimiento primera iteración

# Riesgos producidos

- R-9. Enfermedad alumno: durante la actividad de experimentación el alumno sufrió una enfermedad que le impidió trabajar durante 2 días. Sin embargo, esta actividad pudo completarse antes del tiempo esperado debido a que se disponía de tiempo sobrante. Este riesgo, que en su momento no se tuvo en cuenta, ha sido añadido a la gestión de riesgos.

- R-5. Retraso en la finalización de las actividades: En las actividades de aprendizaje de CUDA, aprendizaje de Hitmap, desarrollo del modelo, análisis del modelo y diseño del prototipo; sus fechas de finalización fueron posteriores a las planificadas. Debido a que los retrasos no fueron en fechas cercanas a la fecha planificada para el fin de la iteración y que no se consideraron graves, se optó por aceptar el riesgo.

| No | Nombre de la actividad               | Fecha inicio | Fecha fin | Retraso |

|----|--------------------------------------|--------------|-----------|---------|

|    |                                      |              |           | (días)  |

| 1  | Inicio                               | 2/03/15      | 2/03/15   | 0       |

| 2  | Aprendizaje de CUDA                  | 2/03/15      | 16/03/15  | 1       |

| 3  | Aprendizaje de Hitmap                | 17/03/15     | 24/03/15  | 2       |

| 4  | Exploración del estado del arte      | 25/03/15     | 28/03/15  | -1      |

| 5  | Propuesta de posibles modelos        | 29/03/15     | 3/04/15   | 0       |

| 6  | Selección de modelo                  | 4/04/15      | 4/04/15   | 0       |

| 7  | Búsqueda de problemas de referencia  | 4/04/15      | 4/04/15   | -1      |

| 8  | Desarrollo del modelo                | 5/04/15      | 15/04/15  | 2       |

| 9  | Análisis del prototipo               | 16/04/15     | 18/04/15  | 1       |

| 10 | Diseño del prototipo                 | 19/04/15     | 22/04/15  | 2       |

| 11 | Construcción del prototipo           | 23/04/15     | 24/04/15  | 0       |

| 12 | Construcción del experimento Jacobi: | 25/04/15     | 26/04/15  | -3      |

|    | GPU vRef                             |              |           |         |

| 13 | Construcción del experimento Jacobi: | 27/04/15     | 28/05/15  | -4      |

|    | GPU v1                               |              |           |         |

| 14 | Experimentación                      | 29/05/15     | 2/05/15   | -2      |

| 15 | Planificación siguiente iteración    | 3/05/15      | 5/05/15   | -1      |

| 16 | Fin                                  | 7/05/15      | 7/05/15   | -1      |

Cuadro 3.1: Seguimiento de la primera iteración

# Observaciones

Durante esta iteración se ha descubierto que la planificación de actividad no ha estado muy ajustada, esto es debido a la inexperiencia del alumno a la hora de realizar planificaciones temporales. Por ejemplo, no se ha tenido en cuenta que en esta iteración solo se implementaba una interfaz con un mínimo de funcionalidad, por tanto el tiempo de implementación fue mínimo. Otro ejemplo, es que no se ha tenido en cuenta que las versiones de referencia de los experimentos se pueden obtener de fuentes públicas oficiales.

En esta iteración ha habido una serie de tareas que duraron más de lo estimado, como una planificación muy ajustada o por producirse un riesgo, en especial la tarea de desarrollo del modelo y la tarea de experimentación que fueron las más largas. La primera se produjo porque hubo ciertos detalles difíciles de concretar (véase rol de los parámetros y variables internas en el Capítulo 6). La segunda se debió a que el alumno sufrió de una enfermedad que le impidió trabajar durante 2 días.

# 3.1.2. Seguimiento segunda iteración

# Riesgos producidos

■ R-5. Retraso en la finalización de las actividades: En las actividades de construcción del prototipo, construcción del experimento Jacobi: GPU v2 y Experimentación; sus fechas de finalización fueron posteriores a las planificadas. Debido a que los retrasos no fueron en fechas cercanas a la fecha planificada para el fin de la iteración y que no se consideraron graves, se optó por aceptar el riesgo.

| No | Nombre de la actividad                   | Fecha inicio | Fecha fin | Retraso |

|----|------------------------------------------|--------------|-----------|---------|

|    |                                          |              |           | (días)  |

| 1  | Inicio                                   | 7/05/15      | 7/05/15   | 0       |

| 2  | Modificación del modelo                  | 7/05/15      | 8/05/15   | 0       |

| 3  | Análisis del prototipo                   | 9/05/15      | 9/05/15   | -1      |

| 4  | Diseño del prototipo                     | 10/05/15     | 13/05/15  | -1      |

| 5  | Construcción del prototipo               | 14/05/15     | 20/05/15  | 2       |

| 6  | Construcción del experimento Jacobi:     | 21/05/15     | 22/05/15  | 2       |

|    | GPU v2                                   |              |           |         |

| 7  | Experimentación                          | 23/05/15     | 23/05/15  | 1       |

| 8  | Redacción del artículo para las Jornadas | 24/05/15     | 1/05/15   | -2      |

|    | de Paralelismo                           |              |           |         |

| 9  | Revisión del artículo                    | 2/06/15      | 7/06/15   | 0       |

| 10 | Entrega del artículo                     | 8/06/15      | 8/06/15   | 0       |

| 11 | Planificación de la siguiente iteración  | 8/06/15      | 9/06/15   | 0       |

| 12 | Fin                                      | 10/06/15     | 10/06/15  | 0       |

Cuadro 3.2: Seguimiento de la segunda iteración

# Observaciones