# Implementation and verification of a hardware-based controller for a three-phase induction motor on an FPGA

by

Marcel Cases Freixenet BSc

A thesis submitted in partial fulfilment of the requirements for the degree of Industrial Electronics and Automatic Control Engineering

Supervisors David Soler Jimenez (UPC) Aleksander Sudnitsõn (TalTech)

Escola Politècnica Superior d'Enginyeria de Manresa Universitat Politècnica de Catalunya. BarcelonaTech, and

> School of Information Technologies Tallinn University of Technology. TalTech

> > Manresa

Submitted March 2019

# Implementation and verification of a hardware-based controller for a three-phase induction motor on an FPGA

Marcel Cases Freixenet

Implementation and verification of a hardware-based controller for a three-phase induction motor on an FPGA Book size: A4 Pages: 64 Word count: 12.530 Document written with  $IATEX 2_{\varepsilon}$ Compilation date: March 8, 2019

The electronic version of this thesis can be downloaded from: https://www.marcelcases.com

Licensed under Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International CC BY-NC-SA 4.0

### Abstract

### català

L'objectiu d'aquesta tesi és estudiar diverses tècniques de control motor per tal d'implementar i verificar un controlador basat en *hardware* per a un motor d'inducció trifàsic, desenvolupat en llenguatge VHDL i funcionant en una FPGA Artix-7 (Xilinx). Aquest controlador està basat en tècniques de variació de freqüència. Els mòduls que defineixen la descripció de *hardware* funcionen simultàniament entre ells, i permeten agilitzar el sistema, millorant el rendiment i la resposta del motor, en comparació amb un microcontrolador. Aquesta tesi està relacionada amb els sistemes digitals, l'electrònica de potència i els sistemes de control.

### eesti keel

Käesoleva töö eesmärk on uurida mootorite juhtimise peamisi tehnikaid, et projekteerida ja rakendada riistvarapõhist kontrollerit kolmefaasilise induktsioonimootori jaoks, mis on välja töötatud VHDL keeles ja töötab Artix-7 FPGA (Xilinx). See kontroller põhineb muutuva sagedusega ajamitehnikatel. Moodulid, mis määratlevad selle kontrolleri riistvara kirjelduse, suhtlevad üksteisega ja võimaldavad mootoril kiiremini reageerida ning parandavad ka selle jõudlust võrreldes mikrokontrolleriga. Käesolev töö on seotud digitaalsüsteemide, võimsuselektroonika ja juhtimissüsteemidega.

### English

The aim of this thesis is to study the main techniques of motor control in order to implement and design a hardware-based controller for a three-phase induction motor, developed in VHDL language and running on an Artix-7 FPGA (Xilinx). This controller is based on variable-frequency drive techniques. The modules that define this controller's hardware description run concurrently to each other, and they allow the motor to have a better time response and they also improve its performance compared to a microcontroller. This thesis is related to digital systems, power electronics and control systems.

Dedicat a tothom qui m'ha ajudat

## **Table of Contents**

| Li | st of Figures                                                                                                                                                       | v        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Li | st of Tables                                                                                                                                                        | vi       |

| Li | stings                                                                                                                                                              | vii      |

| Ał | obreviations                                                                                                                                                        | viii     |

| I  | Background                                                                                                                                                          | 1        |

| 1  | Introduction                                                                                                                                                        | 2        |

|    |                                                                                                                                                                     | 2        |

| 2  | Motivation                                                                                                                                                          | 4        |

| 11 | Control methods for Alternating Current Induction Motors                                                                                                            | 5        |

| 3  | Variable-frequency Drive                                                                                                                                            | 6        |

|    | 3.1 V/Hz scalar control                                                                                                                                             | 7        |

| 4  | Field-oriented Control                                                                                                                                              | 9        |

|    | 4.1 Clarke transformation (the $(a, b, c) \rightarrow (\alpha, \beta)$ projection)                                                                                  | 10       |

|    | 4.2 Park transformation (the $(\alpha, \beta) \rightarrow (d, q)$ projection) 4.3 Inverse Park transformation (the $(d, q) \rightarrow (\alpha, \beta)$ projection) | 11<br>12 |

|    | 4.5 Inverse Fark transformation (the $(a, q) \rightarrow (a, p)$ projection) 4.4 Space Vector Pulse Width Modulation                                                | 12       |

|    | 4.4.1 SPWM vs SVPWM                                                                                                                                                 | 14       |

|    | 4.5 PI regulators                                                                                                                                                   | 14       |

| 5  | Direct Torque Control                                                                                                                                               | 16       |

|    | 5.1 DTC vs FOC                                                                                                                                                      | 17       |

|    |                                                                                                                                                                     |          |

|    | I Workflow: implementing the controller and necessary hard-                                                                                                         | 10       |

|    | ware                                                                                                                                                                | 18       |

| 6  | Field Programmable Gate Arrays                                                                                                                                      | 19       |

|    | 6.1 FPGA over a microcontroller                                                                                                                                     | 20       |

|    | 6.2 Artix-7 FPGA and Basys 3 board                                                                                                                                  | 20       |

|              | $6.3 \\ 6.4$                           | Xilinx's Vivado Design Suite                                                                                                                                                                                                                                                              | 22<br>23                                                                                       |

|--------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 7            | <b>Inve</b><br>7.1<br>7.2              | ABB's three-phase induction motor                                                                                                                                                                                                                                                         | <b>24</b><br>24<br>26                                                                          |

| 8            | <b>Imp</b><br>8.1<br>8.2<br>8.3        | lementation and Verification of a scalar VFD on an FPGA with VHDL<br>Entity                                                                                                                                                                                                               | <ul> <li>28</li> <li>28</li> <li>29</li> <li>31</li> </ul>                                     |

|              | 0.0                                    | Components and functions                                                                                                                                                                                                                                                                  | 31<br>31<br>32<br>33                                                                           |

|              | 8.4                                    | <ul> <li>Verification of the Variable-frequency Drive (VFD) scalar control</li> <li>8.4.1 Testbench of the scalar control</li> <li>8.4.2 Assertion of the dead time and other short circuit preventions .</li> </ul>                                                                      | 33<br>33<br>34                                                                                 |

|              | 8.5<br>8.6                             | Simulation and testingField Programmable Gate Array (FPGA) usage8.6.1Utilization8.6.2Power                                                                                                                                                                                                | 34<br>36<br>36<br>36                                                                           |

| 9            | Sim<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5 | ulation and Verification of a vector FOC on an FPGA with VHDL         Clarke transformation         Park transformation         9.2.1         Component: Trigonometry         Inverse Park transformation         Space Vector Pulse Width Modulation         Simulation and Verification | <ul> <li>37</li> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> <li>42</li> </ul> |

| IV Ending 47 |                                        |                                                                                                                                                                                                                                                                                           |                                                                                                |

| 10           | Con                                    | clusion                                                                                                                                                                                                                                                                                   | 48                                                                                             |

| 11           | Futi                                   | ıre work                                                                                                                                                                                                                                                                                  | 49                                                                                             |

| Bi           | bliog                                  | raphy                                                                                                                                                                                                                                                                                     | 50                                                                                             |

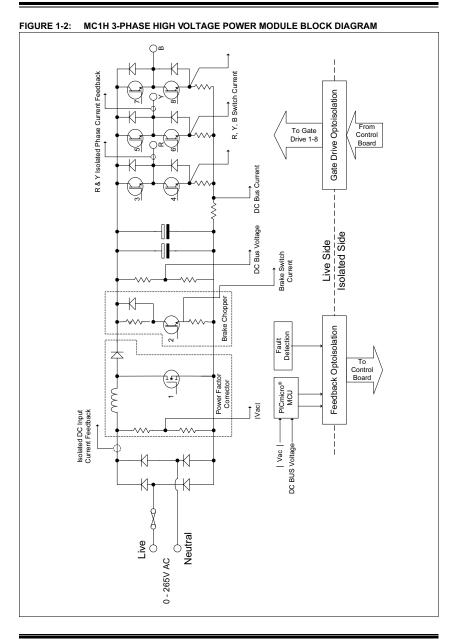

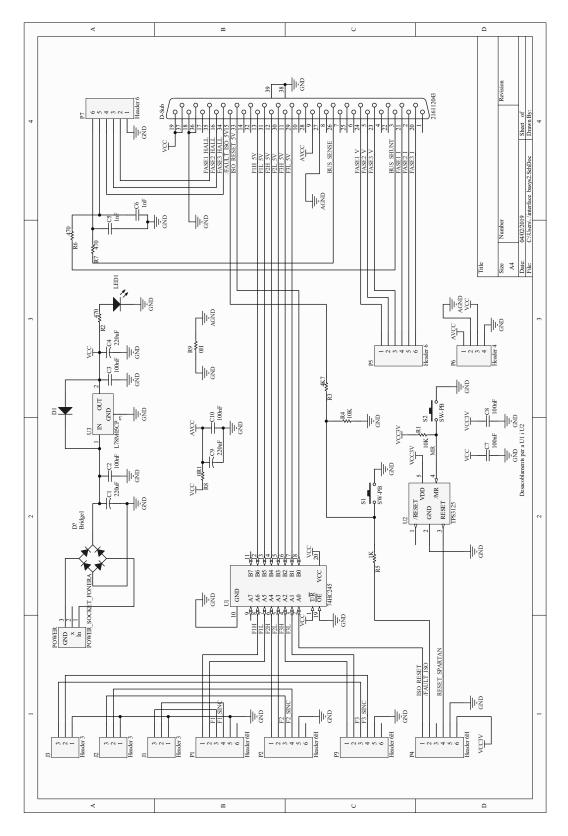

| Ap           | penc<br>A<br>B                         | lices<br>MC1H 3-Phase Power Module Block Diagram                                                                                                                                                                                                                                          | <b>51</b><br>51<br>52                                                                          |

## **List of Figures**

| 3.1 | Classification of induction motor control strategies   | 6  |

|-----|--------------------------------------------------------|----|

| 3.2 | A three-phase inverter and its control signals         | 7  |

| 3.3 | Sine PWM wave generation                               | 8  |

| 4.1 | A Field-oriented Control diagram                       | 9  |

| 4.2 | Clarke transformation and its projections              | 10 |

| 4.3 | Park transformation and its orthogonal projections     | 11 |

| 4.4 | Space Vector Pulse Width Modulation (SVPWM) sectors    | 13 |

| 4.5 | Reference vector as a combination of adjacent vectors  | 13 |

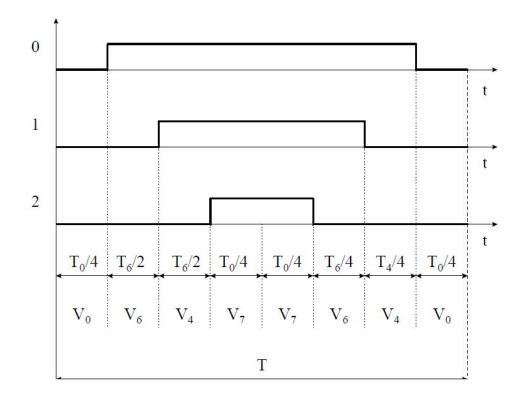

| 4.6 | Pattern of SVPWM in the 3rd sector                     | 14 |

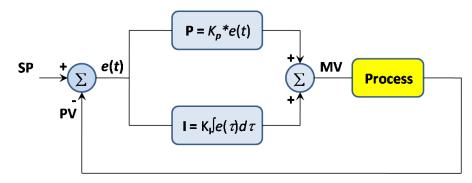

| 4.7 | PI control diagram                                     | 15 |

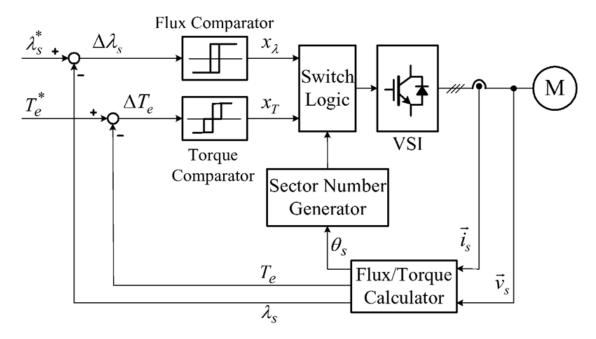

| 5.1 | A Direct Torque Control diagram                        | 16 |

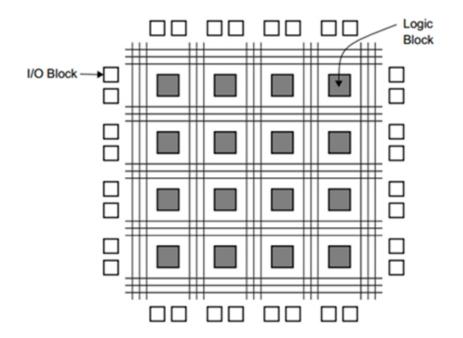

| 6.1 | FPGA architecture                                      | 19 |

| 6.2 | A Xilinx's Basys 3 board                               | 21 |

| 6.3 | Vivado Design Suite user interface                     | 23 |

| 7.1 | Dead time requirements                                 | 24 |

| 7.2 | Dead time in a single-phase inverter                   | 25 |

| 7.3 |                                                        | 25 |

| 7.4 | ABB's three-phase motor                                | 27 |

| 7.5 | 3-phase and corresponding magnetic field orientation   | 27 |

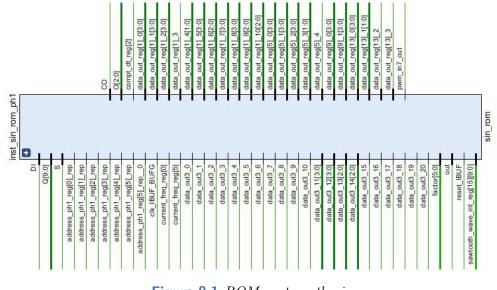

| 8.1 | ROM after synthesis                                    | 32 |

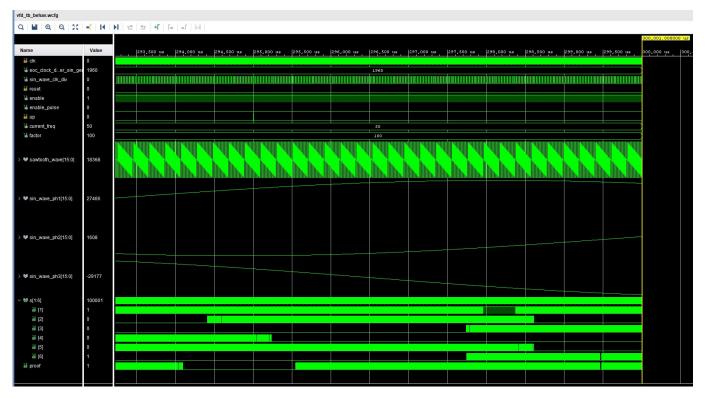

| 8.2 | Simulation of the scalar control at 50Hz               | 35 |

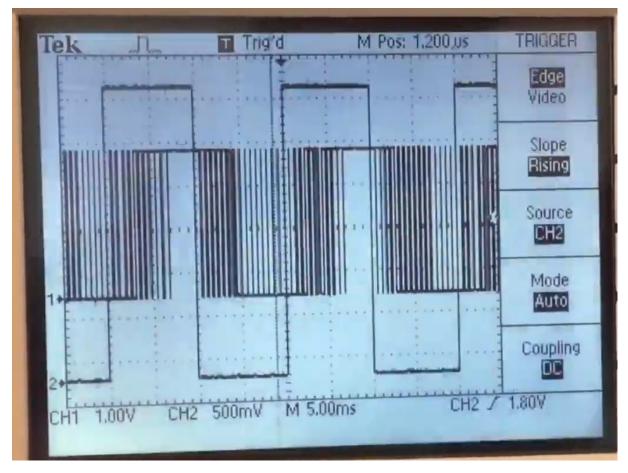

| 8.3 | Phase R signals of the scalar control at 50Hz          | 35 |

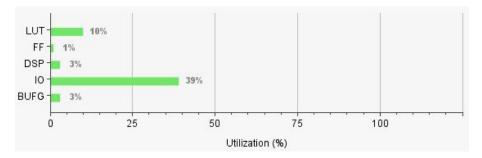

| 8.4 | FPGA usage                                             | 36 |

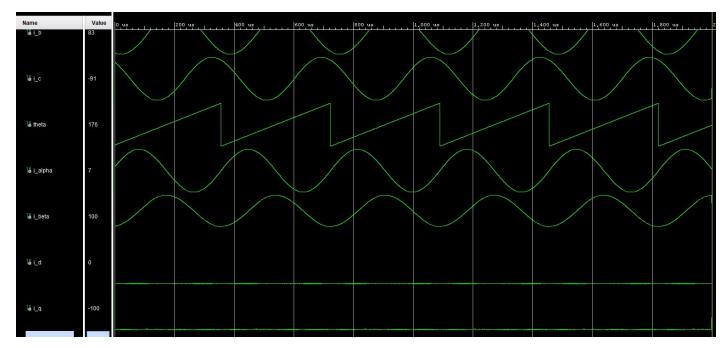

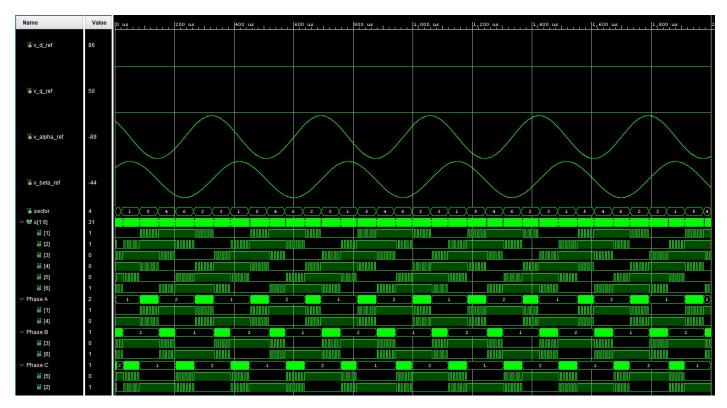

| 9.1 | 1                                                      | 45 |

| 9.2 |                                                        | 45 |

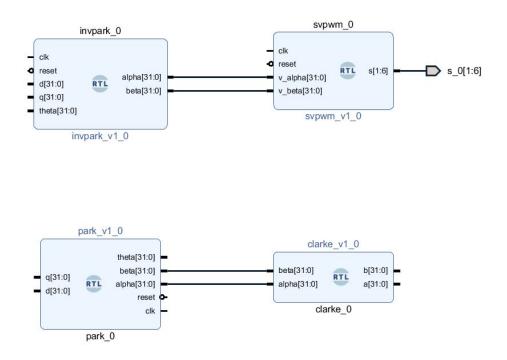

| 9.3 | Field-oriented Control (FOC) representation as a block | 46 |

| 9.4 | FOC block diagram                                      | 46 |

## **List of Tables**

| 5.1 | Direct Torque Control (DTC) vs FOC | 17 |

|-----|------------------------------------|----|

| 6.1 | Basys 3's main features            | 21 |

| 8.1 | Resources utilization              | 36 |

## Listings

| 8.1  | Used libraries in the project                                                               | 28 |

|------|---------------------------------------------------------------------------------------------|----|

| 8.2  | Entity declaration of the top-level file                                                    | 29 |

| 8.3  | Sawtooth signal generation                                                                  | 29 |

| 8.4  | Three-phase sine signal generation                                                          | 30 |

| 8.5  | Frequency set using the physical buttons                                                    | 30 |

| 8.6  | Three-phase PWM signals generation                                                          | 30 |

| 8.7  | Phase signals generation                                                                    | 31 |

| 8.8  | Entity of 16-bit 1024 address ROM memory containing the sine values .                       | 31 |

| 8.9  | Architecture of 16-bit 1024 address ROM memory                                              | 31 |

| 8.10 | Entity of a variable clock divider                                                          | 32 |

| 8.11 | Architecture of a variable clock divider                                                    | 32 |

| 8.12 | Function gen eoc                                                                            | 33 |

| 8.13 | TestBench: increasing the frequency                                                         | 33 |

| 8.14 | Short circuit assertion statement                                                           | 34 |

| 9.1  | Clarke transformation description in VHDL                                                   | 37 |

| 9.2  | Park transformation description in VHDL                                                     | 38 |

| 9.3  | Trigonometry component description in VHDL                                                  | 39 |

| 9.4  | Inverse Park transformation description in VHDL                                             | 40 |

| 9.5  | SVPWM description in VHDL (Entity)                                                          | 41 |

| 9.6  | SVPWM description in VHDL (Architecture: state machine)                                     | 41 |

| 9.7  | SVPWM description in VHDL (Architecture: behavioral)                                        | 42 |

| 9.8  | Routing the components on the top level file                                                | 43 |

| 9.9  | Stimulus generation (TestBench) $(I) \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 43 |

| 9.10 | Stimulus generation (TestBench) (II)                                                        | 44 |

## Abbreviations

| AC    | Alternating Current                     |

|-------|-----------------------------------------|

| ACIM  | Alternating Current Induction Motor     |

| ADC   | Analog-to-digital Converter             |

| ASIC  | Application-specific Integrated Circuit |

| BLDC  | Brushless DC electric motor             |

| DC    | Direct Current                          |

| DTC   | Direct Torque Control                   |

| FOC   | Field-oriented Control                  |

| FPGA  | Field Programmable Gate Array           |

| HDL   | Hardware Description Language           |

| IGBT  | Insulated-gate Bipolar Transistor       |

| LUT   | Look-up Table                           |

| PI    | Proportional Integral                   |

| PMSM  | Permanent-magnet Synchronous Motor      |

| RTL   | Register-transfer Level                 |

| SPWM  | Sinusoidal Pulse Width Modulation       |

| SVPWM | Space Vector Pulse Width Modulation     |

| THD   | Total Harmonic Distortion               |

| VFD   | Variable-frequency Drive                |

| VHDL  | VHSIC Hardware Description Language     |

| VHSIC | Very High Speed Integrated Circuit      |

## Part I

## Background

## **1** Introduction

Thomas Davenport<sup>1</sup> developed the first motor powered by electricity. Soon after, Nikola Tesla<sup>2</sup> discovered Alternating Current (AC) electricity, and he implemented it to power the first Alternating Current Induction Motor (ACIM) in 1887.

AC motors have been improved ever since, both in their assembly and their control methods. They are used in many sectors: in industrial drives, vehicles (cranes, trains, cars, buses) or construction, among others. Nowadays they are boosting the electric mobility day after day as they are being used more frequently in the automotive industry.

It is estimated that about 25% of the world's electrical energy is consumed by electric motors, specifically in industrial applications. The way these motors are commanded has a direct impact in the consumption of energy and the motor's performance. This is why these control techniques have to be optimized, depending on the type of motor they have to control, to avoid energy losses and damaging components built in the motor.

There are many control techniques used to manage their operation. When it comes to three-phase ACIMs, the ones that are used in machines that require high torque, there are two main techniques developed enough to control them: Direct Torque Control (DTC) and Field-oriented Control (FOC).

Both techniques are based on classic Variable-frequency Drives (VFDs), as well as V/Hz control, but they have the ability to adjust some parameters, like the motor voltage magnitude, the current angle of the motor, and the frequency of the shaft so as to control in a more precise way the magnetic flux and the torque of the motor.

FOC is a control technique in which the currents that flow through the stator, the stationary part of the motor system (outer part), are represented as two orthogonal components that can be addressed like a vector. In order to do this, some processes have to be described or programmed. These processes are the Clarke transformation, the Park transformation, and the Inverse Park transformation. Then the output signal is sent to a Space Vector Pulse Width Modulation (SVPWM) module, which has the

<sup>&</sup>lt;sup>1</sup>Thomas Davenport (9 July 1802 - 6 July 1851) was a Vermont blacksmith who constructed the first American DC electric motor in 1834.

<sup>&</sup>lt;sup>2</sup>Nikola Tesla (10 July 1856 - 7 January 1943) was a Serbian-American inventor, electrical engineer, mechanical engineer, and futurist who is best known for his contributions to the design of the modern alternating current (AC) electricity supply system.

function to chop the signal so that the power module, or inverter, is able to give to each one of the three phases of the motor the required voltage and current at any moment.

DTC is a less common ACIM control method that calculates and estimates the torque and magnetic flux of the motor in order to directly control the torque of the motor's shaft, and thus its speed. This involves measuring the current and voltage of the motor. The main difference compared to FOC is that it is not necessary to measure or estimate the current rotor position. The SVPWM or any other PWM modules are not necessary.

This thesis is the result of a period of research in the fields of electric motor control techniques and Hardware Description Languages (HDLs) design. The main goal of the experimental part of this project is to implement a VFD method on a FPGA using Vivado Design Suite, a Xilinx's IDE for HDLs, so that each process of this control system run concurrently to each other. This allows us to analyze the impact that it has in the motor: speed response, harmonics reduction, and other improvements compared to the motor control with classical microcontrollers.

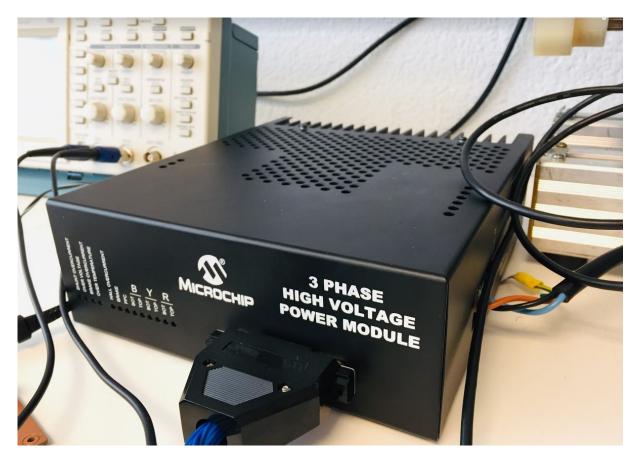

The thesis is structured in two clearly differentiated parts: one is the theoretical background ( $\Rightarrow$  Part II) where FOC, DTC and general V/Hz (VFD) methods are studied and analyzed as well as every component that pertains to these methods; and the other one ( $\Rightarrow$  Part III) is the implementation of the VFD (V/Hz) controller in VHSIC Hardware Description Language (VHDL) on a FPGA and the description of the hardware used: FPGA board, power module, motor, voltage level circuits, and wiring. A study of the performance of this control method is also included.

## 2 Motivation

My personal motivation when choosing a topic for my Bachelor's thesis was my interest in FPGA technology and the advantages of synthesized hardware over the classic microcontrollers or any other device used to perform the operations involved in the control of Alternating Current Induction Motor methods.

Firstly, my motivation to study the hardware design and FPGAs beyond the contents studied in class was my first approach to what this thesis has ended up being. It was the opportunity I had to attend the course *Digital Systems Design with VHDL* at TalTech that helped me to learn concepts of FPGAs, VHDL and the software suite, Vivado, and to widen my previous knowledge of the VHDL language.

My intention was to find a useful application where FPGAs could have a real improvement of performance and time response. This is why, while defining the experimental part of the thesis, a good option was the implementation of a motor control method in VHDL. This was also a good reason to study in depth the most common used methods of ACIM control, and this has allowed me to develop a research and more theory-oriented part for this thesis. This is why this thesis is multidisciplinary, as it involves topics related to mathematical transformations, hardware design, power electronics, control systems and informatics, to name a few.

Finally, the availability of means was key to the success of the experimental part, this is, the FPGA board (Basys 3), the power module (inverter), the board designed specifically to connect the board with the power module, and the induction motor available in the laboratories of my university.

## Part II

## **Control methods for Alternating Current Induction Motors**

### 3 Variable-frequency Drive

Variable-frequency Drive (VFD), also known as *variable speed drive* or *inverter drive*, is a group of control techniques based on adjustable-speed drive for ACIMs. The methods related to VFD are widely used in electro-mechanical drive systems to control AC motor speed and torque by varying motor input frequency and voltage.

VFDs have many applications in industry. Not only ACIMs can be controlled with these strategies. Some of the purposes of VFD beyond motor control are the commandment of AC-AC and DC-AC drives.

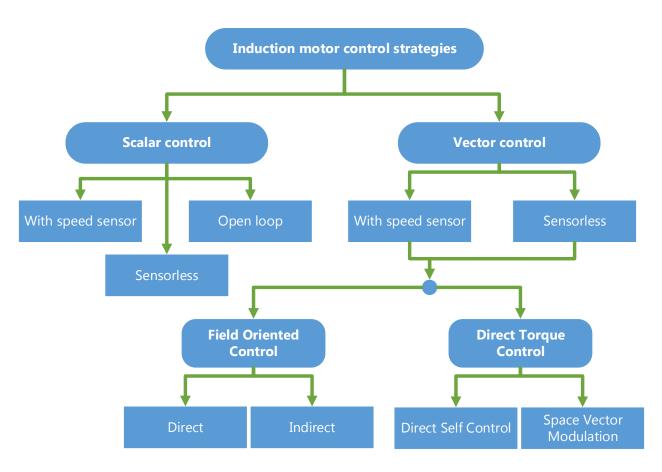

Figure 3.1 Classification of induction motor control strategies

This part of the project studies the three principal techniques for ACIM control: V/Hz (scalar control), and Field-oriented Control and Direct Torque Control (vector control).

### 3.1 V/Hz scalar control

Among the motor control techniques studied in this thesis, VFD Volt/Hertz scalar control is the most simple in concept and design, despite having some drawbacks, the most prominent of them being the impossibility to stabilize the motor at low frequencies (up to 5Hz), and a slow response in speed changes when the motor has a load.

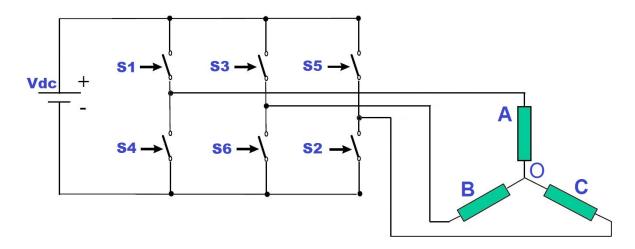

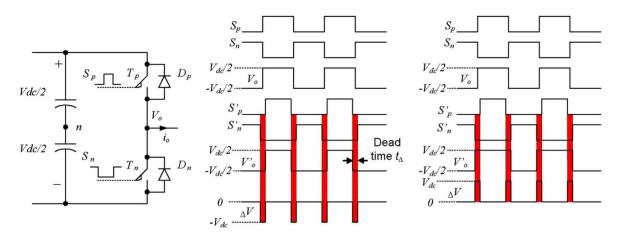

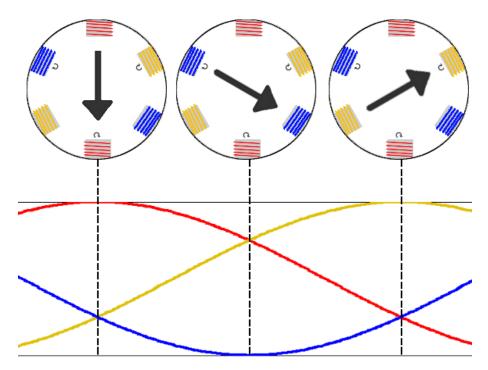

This strategy consists in providing the switches of an inverter ( $\Rightarrow$  Figure 3.2) with a signal corresponding to the current state of the switch (ON or OFF), thus defining the desired current orientation of the magnetic field.

Figure 3.2 A three-phase inverter and its control signals

In order to obtain a sinusoidal signal at the outputs to the motor's three phases, the signal driven through the six switches of the inverter's circuit has to be controlled somehow. This can be done by generating a variable PWM signal at a specific frequency, much higher than the rotation frequency of the magnetic field. When this signal is generated, the duty cycle of the PWM wave can be adjusted at real time so that the output signal to the phases of the motor follows a sine pattern.

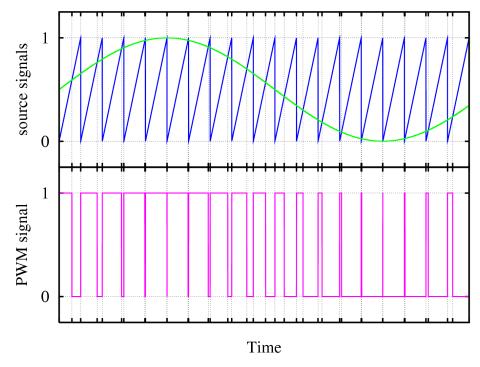

To produce the corresponding control signal for the Insulated-gate Bipolar Transistors (IGBTs), it has to be compared by a sine signal (in light green) stored in a ROM and a sawtooth signal (in dark blue), and according to this comparison, the duty cycle of the PWM (pink) is established at every moment, as shown on  $\Rightarrow$  Figure 3.3.

This comparison of signals, which generates a variable PWM output, has to be performed for each one of the three phases of the system concurrently, making sure that the sine signals are shifted 120 degrees to each other.

The torque of the motor's shaft when using a scalar control method can be controlled by directly modifying the amplitude of the output sine signals. This is why the sine signal before the comparison with the sawtooth signal is modulated by a factor,

Figure 3.3 Sine PWM wave generation

from 0 to 100. This factor is directly proportional to the current set frequency, from 0Hz to the nominal speed of the motor (usually 3000rpm or 50Hz). For speeds greater than the nominal speed, the factor remains 100. This factor will prevent the inverter and the motor from receiving high currents at low speeds, which could be harmful for the system.

## **4 Field-oriented Control**

Field-oriented Control (FOC), commonly referred as *vector control*, is a technique used to control three-phase Alternating Current Induction Motors based on VFD that is stator-centric. This means that all of the operations that have to be performed in order to run a FOC are made from the stator's reference frame, and they are represented by a vector.

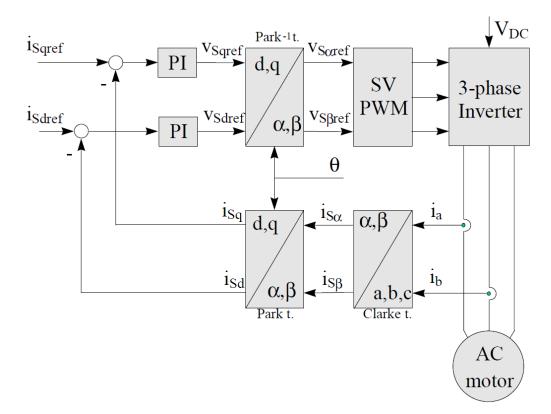

In order to run a FOC, the signal coming from the feedback of the system, which is the magnitude of the current on two phases from the power module to the motor, has to be treated and modified by two mathematical transformations: the Clarke transformation and the Park transformation, as shown in  $\Rightarrow$  Figure 4.1. These transformations lead to a new reference frame, named (d, q), which is time-invariant.

An ACIM controlled by a FOC, after the required mathematical transformations, can be controlled in a way similar of the DC motors. This allows to control the motor in a more accurate way, whether it is in steady state or transient.

Figure 4.1 A Field-oriented Control diagram

## 4.1 Clarke transformation (the $(a, b, c) \rightarrow (\alpha, \beta)$ projection)

Clarke transformation, also known as Alpha-beta transformation, named after Edith Clarke<sup>1</sup>, is a mathematical transformation that has the purpose to convert a three-phase system into a bi-dimensional, time-variant system  $(a, b, c) \rightarrow (\alpha, \beta)$ .

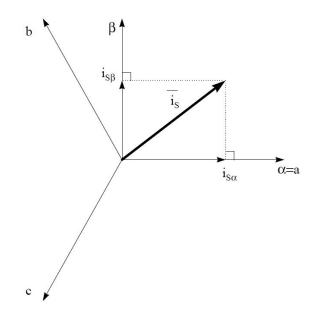

Figure 4.2 Clarke transformation and its projections

In a three-phase system, the signals of the three phases (a, b, c) are represented by three different axis separated  $\frac{2\pi}{3}rads$  to each other. After the Clarke transformation, the projection of the vectors is represented only by two orthogonal components,  $(\alpha, \beta)$ . For this result, it is assumed that the axis a and the axis  $\alpha$  are in the same direction.

$$\begin{cases} i_{S\alpha} = i_a \\ i_{S\beta} = \frac{1}{\sqrt{3}}i_a + \frac{2}{\sqrt{3}}i_b \end{cases}$$

$$(4.1)$$

A product of matrix is used to solve this system:

$$\begin{pmatrix} i_{S\alpha}(t) \\ i_{S\beta}(t) \end{pmatrix} = \sqrt{\frac{2}{3}} \begin{pmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{pmatrix} \begin{pmatrix} i_a(t) \\ i_b(t) \\ i_c(t) \end{pmatrix}$$

(4.2)

The resulting system is still time-variant.

<sup>&</sup>lt;sup>1</sup>Edith Clarke (February 10, 1883 - October 29, 1959) was the first female electrical engineer and the first female professor of electrical engineering at the University of Texas at Austin.

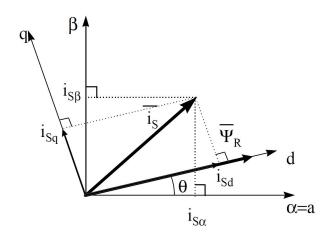

### 4.2 Park transformation (the $(\alpha, \beta) \rightarrow (d, q)$ projection)

Park transformation, named after Robert H. Park<sup>2</sup>, is considered the most critical process of the FOC. This projection transforms a two phase orthogonal system, which is made up by the output signals of the Clarke transformation, into a new rotating reference frame  $(\alpha, \beta) \rightarrow (d, q)$ , which is a time-invariant system. The only requirement is to consider the *d* axis aligned with the rotor flux.

Figure 4.3 Park transformation and its orthogonal projections

The result of this projection is sometimes known as *Direct-quadrature-zero transformation* when referring to the product of the Clarke transformation and the Park transformation together.

The flux and torque are components of a new vector. This vector is calculated by solving the linear system of the  $\Rightarrow$  Equation 4.3.

$$\begin{cases} i_{Sd} = i_{S\alpha} \cos \theta + i_{S\beta} \sin \theta \\ i_{Sq} = -i_{S\alpha} \sin \theta + i_{S\beta} \cos \theta \end{cases}$$

(4.3)

In this equation,  $\theta$  is the rotor flux position, and it has to be either measured or estimated. Knowledge of the rotor flux position is the core of the correct performance of FOC.

From this transformation on, the system is treated as if we were rotating inside of the armature or the shaft.

<sup>&</sup>lt;sup>2</sup>Robert H. Park (March 15, 1902 - February 18, 1994) was an American electrical engineer and inventor.

## **4.3** Inverse Park transformation (the $(d,q) \rightarrow (\alpha,\beta)$ projection)

The Inverse Park transformation is the process in which the reference signals and the feedback processed signals are transformed again from the rotating reference into a two-phase orthogonal system  $(d,q) \rightarrow (\alpha,\beta)$ . It transforms voltage signals instead of current in order to command the IGBTs of the inverter.

The equations that define this transformation are the following:

$$\begin{cases} v_{S\alpha ref} = v_{Sdref}\cos\theta - v_{Sqref}\sin\theta\\ v_{S\beta ref} = v_{Sdref}\sin\theta + v_{Sqref}\cos\theta \end{cases}$$

(4.4)

The voltage vector, which is the output of the Inverse Park transform block, is then applied as the input vector to the SVPWM component.

### 4.4 Space Vector Pulse Width Modulation

The Space Vector Pulse Width Modulation (SVPWM) is a technique used to transform an orthogonal reference, represented by a vector, to digital pulses that directly control the inverter that provides the signal to the three phases of an ACIM.

This technique is based on PWM and is applicable to different types of AC motors, such as ACIMs, Brushless DC electric motors (BLDCs) and Permanent-magnet Synchronous Motors (PMSMs).

Some studies of SVPWM reveal that this technique utilizes DC voltage more efficiently and generates less harmonic distortion when compared to the classic Sinusoidal Pulse Width Modulation (SPWM) method. [1]

The commutation of these switches must respect the following conditions:

- $\Box$  three of the switches must always be ON and three always OFF, and

- □ the upper and the lower switches of the same branch have to be driven with two complementary signals in order to avoid short-circuits.

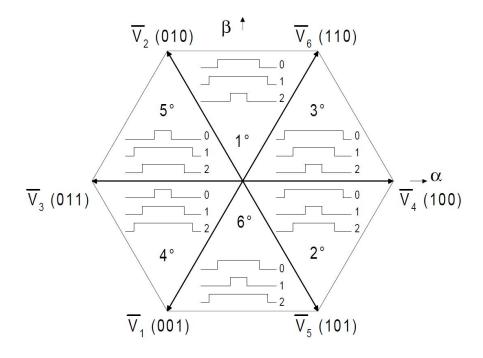

SVPWM can be represented by vectors that divide the plan into six sectors  $\Rightarrow$  Figure 4.4. Depending on the sector that the voltage reference is in, two adjacent vectors are chosen. These two adjacent vectors are time-weighted in a sample period to produce the desired output voltage to the inverter.

Figure 4.4 SVPWM sectors

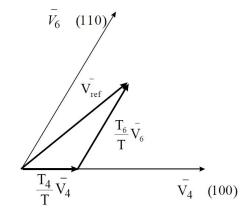

As an example, if the current orthogonal input vector was located on the 3rd sector, like in  $\Rightarrow$  Figure 4.5, then a linear system made from the adjacent vectors would have to be solved ( $\Rightarrow$  Equation 4.5).

Figure 4.5 Reference vector as a combination of adjacent vectors

$$\begin{cases} T = T_4 + T_6 + T_0 \\ \overline{V}_{ref} = \frac{T_4}{T} \overline{V}_4 + \frac{T_6}{T} \overline{V}_6 \end{cases}$$

(4.5)

Where  $T_4$  and  $T_6$  are the times during which the vectors  $V_4$ ,  $V_6$  are applied and  $T_0$  the time during which the zero vectors are applied.

The  $\Rightarrow$  Figure 4.6 shows the output time-weighted signal that feeds the inverter. This would be the configuration for the third sector too.

Figure 4.6 Pattern of SVPWM in the 3rd sector

#### 4.4.1 SPWM vs SVPWM

Both techniques Sinusoidal Pulse Width Modulation and Space Vector Pulse Width Modulation have the same objective: feeding the transistors of the inverter to produce a sinusoidal signal than can make the motor turn. However, each system has a different method to achieve this purpose.

While SPWM generates a 3-phase frequency from a simple PWM sine-sawtooth wave comparison, SVPWM is a more sophisticated technique that provides a higher voltage to the motor with lower Total Harmonic Distortion, providing a more efficient use of the supply voltage.

In SPWM, the locus of the reference vector is inside of a circle with a radius of  $1/2V_{dc}$ , while in SVPWM the locus is located at  $1/\sqrt{3}V_{dc}$ . This difference shows that the output voltage of SVPWM is 15.47% more efficient than that of SPWM.

#### 4.5 PI regulators

The Proportional Integral (PI) regulators in FOC have the function to regulate the two signals that are the input to the control system: the torque component reference and the flux component reference. They are dependent on the constants that have to be set in order to reach the quickest time response with the lowest overshooting possible.

Before these two signals are regulated by the PI regulators, they are compared with the output vector of the Park transformation and an error signal is calculated. Finally, the regulated signal is the input to the Park transformation component.

Figure 4.7 PI control diagram

### **5 Direct Torque Control**

Direct Torque Control (DTC) is a more recent AC motor control method developed by ABB engineers in 1985. DTC is optimal for ACIMs and PMSMs. This technique is also based on vector VFDs.

The principles of operation of the DTC is to monitor the flux dynamics of the stator and then to directly manipulate the flux that goes through the stator in the form of a vector. This vector is proportional to the torque force at the motor's shaft. Thus, DTC directly controls torque and stator flux, and indirectly controls the stator currents and voltages.

Figure 5.1 A Direct Torque Control diagram

In a DTC, torque and flux can be changed very fast by modifying the references. It also has high efficiency and low losses. The step response has virtually no overshoot. No coordinate transforms are needed, all calculations are done in stationary coordinate system. No separate modulator is needed (although it can be used). The hysteresis control defines the switch control signals directly. There is no need for PI current controllers. Thus no tuning of the control is required and the same control can be used in different motors.

According to ABB, the main **advantages** of DTC over other control methods are the following:

- $\square$  No need for motor speed or position feedback.

- □ Installation of costly encoders or other feedback devices can be avoided.

- □ DTC control available for different types of motors, including PMSM and the newer synchronous reluctance motors.

- □ Accurate torque and speed control down to low speeds, as well as full startup torque down to zero speed.

- $\square$  Excellent torque linearity.

- $\square$  High static and dynamic speed accuracy.

- $\square$  Absence of co-ordinate transform.

However, DTC has some drawbacks:

- □ Possible problems during starting.

- □ Requirement of torque and flux estimators, implying the consequent parameters identification.

### 5.1 DTC vs FOC

Direct Torque Control is considered to have a slight better performance than FOC for the following reasons:

| Coordinates reference frame         Controlled variables         Parameter sensitivity         Rotor speed measurement         Coordinate transformations | DTC | (d, q) at stationary reference frame    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|

|                                                                                                                                                           | FOC | (d, q) at rotor                         |

| Controlled variables                                                                                                                                      | DTC | Torque and stator flux                  |

|                                                                                                                                                           | FOC | Rotor flux, torque current and rotor    |

|                                                                                                                                                           | FUC | flux current                            |

| Parameter sensitivity                                                                                                                                     | DTC | Stator resistance                       |

|                                                                                                                                                           | FOC | (d, q) inductances and rotor resistance |

| Poter gread mangurament                                                                                                                                   | DTC | Not required                            |

| -                                                                                                                                                         | FOC | Required (measured or estimated)        |

| Coordinate transformations                                                                                                                                | DTC | Not required                            |

| Coordinate transformations                                                                                                                                | FOC | Required (Clarke and Park)              |

| Switching lossos                                                                                                                                          | DTC | Lowest                                  |

| Switching losses                                                                                                                                          | FOC | Low                                     |

| Processing requirements                                                                                                                                   | DTC | Lower                                   |

| r rocessing requirements                                                                                                                                  | FOC | Higher                                  |

Table 5.1 DTC vs FOC

## Part III

# Workflow: implementing the controller and necessary hardware

### 6 Field Programmable Gate Arrays

Field Programmable Gate Arrays (FPGAs) are a hardware-based technology designed to performing calculations, routing digital signals, and controlling embedded systems using programmable logic.

FPGAs consist of arrays of logic blocs that are programmable. The chip that contains the FPGA is surrounded by programmable routing resources, which allow the hardware designer to make interconnections between these logic units. Some of these units have ports that connect the internal signals with physical signals.

The first FPGA was introduced by Xilinx in 1985. Nowadays, most of the commercially available FPGAs are manufactured by Xilinx and Altera (Intel), which make up 90% of FPGAs market, but recently more companies have started developing their own FPGA boards.

Figure 6.1 FPGA architecture

### 6.1 FPGA over a microcontroller

Microcontrollers have become a dominant component in modern electronic design. They are highly versatile and inexpensive, and can do many of the operations needed in industry, automotive or any other field. They usually are a person's first introduction to the fields related to electronics. Nonetheless, a microcontroller is built around a processor and processors come with fundamental limitations. In some cases, an FPGA can be more useful than a classical microcontroller.

By definition, a processor performs its tasks by executing instructions sequentially, this is, that the processor's operations are inherently constrained: the desired functionality must be adapted to the available instructions and, in most cases, it is not possible to accomplish multiple processing tasks simultaneously, even if the instruction set is designed to be highly versatile.

A good alternative to these limitations would be a hardware-based approach, close to the functionality of Application-specific Integrated Circuits (ASICs). This is where FPGAs have their niche: they have a time performance close to that of ASICs but without the need of having additional hardware. In the case a FPGA is used, its operation will be described in a Hardware Description Language, like VHDL or Verilog, and once the code has been synthesized, the final result will have a behavior like a real hardware component. An advantage is that this code can be rewritten and re synthesized as many times as necessary, and the modules of a top level project are run concurrently to each other, avoiding the sequential operation that microcontrollers have.

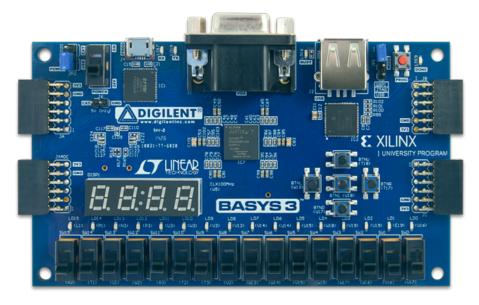

### 6.2 Artix-7 FPGA and Basys 3 board

Basys  $3 \Rightarrow$  Figure 6.2 is a FPGA development board intended for education purposes that includes a FPGA chip (Artix-7) and a complete set of peripherals ready to use together. Hardware descriptions for the Basys 3 can be written in VHDL or Verilog, and synthesized, on Vivado Design Suite. In case of the necessity of a coprocessor for a given project, a simple ALU can be instantiated on the architecture of this project to work as a processor, and a compiled C program can be run on it.

Basys 3 is the board that has been used for this motor control project given the huge amount of cells (more than the necessary for this project), the 12-bit resolution ADC converter and the ability to connect the board with the power module. Its main features are summarized in  $\Rightarrow$  Table 6.1

Figure 6.2 A Xilinx's Basys 3 board

| Artix-7 FPGA Trainer Board Features                           |                                  |  |

|---------------------------------------------------------------|----------------------------------|--|

| On-chip analog-to-digital converter (XADC, 12-bit resolution) |                                  |  |

|                                                               | Key Specifications               |  |

| FPGA part number                                              | XC7A35T-1CPG236C                 |  |

| Logic cells                                                   | 33,280 in 5200 slices            |  |

| Block RAM                                                     | 1,800 Kbits                      |  |

| DSP slices                                                    | 90                               |  |

| Internal clock                                                | 100MHz                           |  |

| Connee                                                        | ctivity and Onboard I/O          |  |

| Pmod connectors                                               | 3                                |  |

| Switches                                                      | 16                               |  |

| Buttons                                                       | 5                                |  |

| User LED                                                      | 16                               |  |

| 7-seg displays                                                | 4-Digit                          |  |

| VGA                                                           | 12-bit                           |  |

| USB                                                           | HID Host (KB/Mouse/Mass Storage) |  |

| Electrical characteristics                                    |                                  |  |

| Power                                                         | USB (5V in)                      |  |

| Logic level                                                   | 3.3V output                      |  |

| Physical characteristics                                      |                                  |  |

| Width                                                         | 7.1 cm                           |  |

| Length                                                        | 12.2 cm                          |  |

Table 6.1 Basys 3's main features

### 6.3 Xilinx's Vivado Design Suite

Vivado Design Suite by Xilinx is the development platform of hardware description for all types of Xilinx's boards. The whole process of hardware description can be handled in the suite, from highlighting the code, simulating or synthesizing to implementing, programming and debugging the output of the project on the boards.

Usually, a project on Vivado consists in the following steps:

- **Code** The first and most important part of the project consists in the development of the code, in VHDL or Verilog. This is the part where the entity (input and output ports) and the architecture (behavioral model) are defined.

- **Block design integration** Although this part is optional, it consists in integrating components or IP's (Intellectual Property modules) to the main project and to wire them in a graphical, more user-friendly way.

- **Simulation** Simulation is a key part of the hardware description process. it allows us to test every part of the code and to monitor each one of the internal signals so that the developer can easily find mistakes or the source of an unexpected behavior of the code. Usually simulations run according to a *testbench*, which is an independent VHDL piece of code, compiled (not synthesized), that defines the state of the inputs at every moment.

- **RTL analysis** Register-transfer Level (RTL) is a design abstraction which shows a model of a digital circuit in terms of the flow of digital signals (data) between hardware registers, and the logical operations performed on those signals. This analysis generates a sketch of the VHDL code pre-synthesis.

- **Synthesis** Process that transforms high level constructs in human-readable code, which don't have real physical hardware that can be wired up to do your logic, into low level logical constructs which can be literally modeled in the form of transistor logic or look-up tables or other FPGA or ASIC hardware components.

- **Implementation** Vivado implementation includes all steps necessary to place and route the netlist onto device resources, within the logical, physical, and timing constraints of the design.

- **Programming and debugging** Last part of the process. A bitstream file is generated and programmed into the FPGA.

| vfd - [D:/Marcel/TFG/codi/vfd/vfd.xpi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | pr] - Vivado 2018.2 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Eile Edit Flow Tools Reports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Window Layout Yiew Belo Q- Cluick Access Synthesis Out-of-dt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ate details 🔦 |

| 🖷, 🖘 🖈 🖻 🐘 🗙 🕨, 🕸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 目 ✿ ∑ 然 彡 ダ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .ayout 🗸      |

| Flow Navigator 😤 🔍 🔤 🕅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R0Ject Manager - v/d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ? >           |

| PROJECT MANAGER     Sellings     Add Sources     Language Templates     PIP Catalog     PIP INTEGRATOR     Create Block Design     Open Block Design     Generate Block Design     Generate Block Design     SitiuLLATION     Run Simulation     SINULLATION     RUL SINULATION     RUL SINULATION     SINULLATION     RUL SINULATION      SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION     SINULATION | ROJECT MANAGER - Md         Sources       ? _ O X         Y = 0 + 0       Y       Vidual x         D Marcel/TFGKcodMMMdstcsbources_thewMd.hd       X       D         Q X = 0 + 1       Project Summary       Vidual x         D Marcel/TFGKcodMMMdstcsbources_thewMd.hd       Q       X       X       X       X       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y       Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ?>><br>*<br>* |

| MPLEMENTATION     Nun Implementation     Open Implemented Design     PROGRAM AND DEBUG     Generate Bitstram     Open Manager     Nun                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LUbrar: A Left and the model of the second o | ? _ C         |