# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Blackmore, Craig

Title: Inductive Logic Programming for Compiler Tuning

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

#### Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Inductive Logic Programming for Compiler Tuning

By

CRAIG BLACKMORE

Department of Computer Science UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements for award of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Engineering.

December 2018

Word count: Thirty-two thousand words

ABSTRACT

Software performance is heavily dependent on the compiler settings used to generate executables from source code. These settings have a significant impact on execution time, energy consumption and code size, and they can be modified easily without the need to alter the underlying source code nor the compiler itself.

Automated Compiler Tuning (ACT) is the practice of selecting compiler settings to improve the performance of computer software. Existing work shows significant potential gains beyond industry standard GCC -03, but the search space is very large. This motivated the development of predictive machine learning approaches, most of which rely on feature vectors of simple statistics that summarise program characteristics. Inductive Logic Programming (ILP) can potentially exploit full program structure that existing methods do not consider.

This thesis applies ILP to ACT to investigate the hypothesis that exploiting full program structure increases the accuracy and effectiveness of predictive compiler tuning. It explores the design, feasibility and benefits of applying ILP to discover meaningful rules that relate effective compiler settings to program structure. During the process, assumptions in existing work are identified and challenged to increase understanding of the problem and give a robust evaluation of compiler tuning techniques.

The research is conducted on the industry standard GCC compiler and a state-of-the-art benchmark suite targeting ARM Cortex-M3 (CM3) and Cortex-A8 (CA8) processors. The ILP method outperforms two state-of-the-art approaches and also identifies settings that should always be disabled to improve performance on the target platform. This leads to the construction of two new program-agnostic optimisation levels that outperform GCC's -03 and are competitive with program-specific predictive approaches. Finally, a case study on an image classification application from the ARM CMSIS Neural Network library finds an 8% improvement over -03 on the CM3.

### **ACKNOWLEDGEMENTS**

I would like to thank my supervisors Oliver Ray and Kerstin Eder for their valuable feedback, time and support throughout my PhD. Thank you to Simon Hollis for first introducing me to this research area.

My thanks to Jeremy Bennett, Simon Cook, Ed Jones, Graham Markall and everyone at Embecosm for hosting my internship, for valuable discussions and their continuing commitment to compiler research.

Thank you to friends and colleagues at the University including: James Pallister, Steve Kerrison, Jeremy Morse, Kyriakos Georgiou, Dejanira Araiza Illan and many more.

Thank you to my family for encouraging and supporting me throughout my life. My thanks to David Timms, Udoyon Bhaduri, James Dixon, Julie Cox, Alex Neill and all of my open mic friends for keeping my love of music alive. Finally, thank you to Kuiama Lewandowski for always knowing what to say when I needed it the most and being there through the highs and lows with endless cups of tea and moral support.

# **AUTHOR'S DECLARATION**

I declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ..... DATE: .....

# TABLE OF CONTENTS

|    |         |         | F                                                 | Page |

|----|---------|---------|---------------------------------------------------|------|

| Li | st of ' | Tables  |                                                   | xi   |

| Li | st of ] | Figure  | s                                                 | xiii |

| Li | st of ] | Listing | ţs                                                | xv   |

| 1  | Intr    | oducti  | on                                                | 1    |

|    | 1.1     | Resear  | rch questions                                     | 3    |

|    | 1.2     | Contri  | $\operatorname{butions}$                          | 4    |

|    | 1.3     | Relate  | d publications                                    | 6    |

|    | 1.4     | Thesis  | structure                                         | 7    |

| 2  | Bac     | kgrour  | nd                                                | 9    |

|    | 2.1     | Compi   | ler tuning                                        | 9    |

|    |         | 2.1.1   | Problems in compiler tuning                       | 10   |

|    |         | 2.1.2   | Standard optimisation levels                      | 11   |

|    |         | 2.1.3   | Iterative compilation                             | 11   |

|    |         | 2.1.4   | Machine learning                                  | 15   |

|    |         | 2.1.5   | Scope                                             | 21   |

|    | 2.2     | Induct  | ive Logic Programming                             | 22   |

|    |         | 2.2.1   | Motivating example                                | 23   |

|    | 2.3     | Hardw   | vare platforms                                    | 24   |

|    | 2.4     | Bench   | marks                                             | 25   |

|    |         | 2.4.1   | Bristol/Embecosm Embedded Benchmark Suite (BEEBS) | 25   |

|    |         | 2.4.2   | Collective Benchmarks (cBench)                    | 27   |

|    | 2.5     | Measu   | ring energy and time                              | 28   |

| 3  | Qua     | ntifyir | ng the potential benefits of compiler tuning      | 29   |

|    | 3.1     | BEEB    | S data initialisation                             | 30   |

|    | 3.2     | Evalua  | ating configurations                              | 31   |

|    | 3.3     | Standa  | ard optimisation levels                           | 31   |

|   | 3.4  | Analysing the configuration space with Random Iterative Compilation | 35 |  |  |

|---|------|---------------------------------------------------------------------|----|--|--|

|   |      | 3.4.1 Distribution of results                                       | 35 |  |  |

|   |      | 3.4.2 Energy-time correlation                                       | 40 |  |  |

|   | 3.5  | Finding further improvements with Combined Elimination              | 40 |  |  |

|   |      | 3.5.1 Comparison of RIC and CE                                      | 41 |  |  |

|   |      | 3.5.2 Impact of different baselines                                 | 44 |  |  |

|   | 3.6  | Summary of potential gains                                          | 45 |  |  |

| 4 | Re-e | evaluation of predictive compiler tuning approaches                 | 47 |  |  |

|   | 4.1  | Evaluating machine learning models                                  | 47 |  |  |

|   | 4.2  | Milepost                                                            | 48 |  |  |

|   |      | 4.2.1 Results                                                       | 48 |  |  |

|   | 4.3  | COBAYN                                                              | 50 |  |  |

|   |      | 4.3.1 Choice of flags                                               | 50 |  |  |

|   |      | 4.3.2 Performance of COBAYN models                                  | 52 |  |  |

|   | 4.4  | Summary of results                                                  | 53 |  |  |

| 5 | Con  | Constructing new program-agnostic optimisation levels 5             |    |  |  |

|   | 5.1  | Constructing program-agnostic optimisation levels                   | 56 |  |  |

|   |      | 5.1.1 Adapting combined elimination                                 | 56 |  |  |

|   |      | 5.1.2 Threshold trade-off in constructing -Ocm3                     | 57 |  |  |

|   |      | 5.1.3 Analysis of two excluded flags                                | 58 |  |  |

|   |      | 5.1.4 Cross-validation of -Ocm3                                     | 60 |  |  |

|   |      | 5.1.5 Testing on other platforms                                    | 62 |  |  |

|   | 5.2  | Finding a small set of good configurations                          | 63 |  |  |

|   |      | 5.2.1 Method                                                        | 64 |  |  |

|   |      | 5.2.2 Results                                                       | 66 |  |  |

|   | 5.3  | Conclusion                                                          | 67 |  |  |

| 6 | Арр  | lying ILP to compiler tuning                                        | 71 |  |  |

|   | 6.1  | Method                                                              | 72 |  |  |

|   |      | 6.1.1 Identifying examples of significant flags                     | 72 |  |  |

|   |      | 6.1.2 Extracting program features for ILP+FV                        | 76 |  |  |

|   |      | 6.1.3 Extracting Intermediate Representation for ILP+IR             | 76 |  |  |

|   |      | 6.1.4 Learning rules for bad flags                                  | 77 |  |  |

|   | 6.2  | Results and evaluation                                              | 78 |  |  |

|   |      | 6.2.1 ILP+FV and ILP+IR                                             | 78 |  |  |

|   |      | 6.2.2 Hybrid approach                                               | 80 |  |  |

|   | 6.3  | Conclusion                                                          | 81 |  |  |

| 7 | Foc                                                       | using l                                                                 | LP based compiler tuning                                                                                                                                                                                                                                                                                                                                                                | 83                                                                                             |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 7.1                                                       | Limita                                                                  | ations of initial approach                                                                                                                                                                                                                                                                                                                                                              | 83                                                                                             |

|   | 7.2                                                       | Impro                                                                   | ved Inductive Logic Programming based compiler tuning                                                                                                                                                                                                                                                                                                                                   | 84                                                                                             |

|   |                                                           | 7.2.1                                                                   | Identifying significantly good or bad flags                                                                                                                                                                                                                                                                                                                                             | 84                                                                                             |

|   |                                                           | 7.2.2                                                                   | Restricting the search space                                                                                                                                                                                                                                                                                                                                                            | 85                                                                                             |

|   |                                                           | 7.2.3                                                                   | ILP search algorithm and cost function                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                             |

|   |                                                           | 7.2.4                                                                   | Cross-validation of new ILP approach                                                                                                                                                                                                                                                                                                                                                    | 86                                                                                             |

|   |                                                           | 7.2.5                                                                   | Insights from human-readable rules                                                                                                                                                                                                                                                                                                                                                      | 86                                                                                             |

|   | 7.3                                                       | Const                                                                   | ructing a new program-agnostic optimisation level                                                                                                                                                                                                                                                                                                                                       | 87                                                                                             |

|   |                                                           | 7.3.1                                                                   | Performance of -Ocm3-ilp                                                                                                                                                                                                                                                                                                                                                                | 87                                                                                             |

|   | 7.4                                                       | Testin                                                                  | g on the Cortex-A8 processor                                                                                                                                                                                                                                                                                                                                                            | 88                                                                                             |

|   | 7.5                                                       | Conclu                                                                  | asion                                                                                                                                                                                                                                                                                                                                                                                   | 89                                                                                             |

| 8 | Tra                                                       | nsfera                                                                  | bility of compiler tuning methods and models across platforms and                                                                                                                                                                                                                                                                                                                       |                                                                                                |

|   |                                                           |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                |

|   | to a                                                      | real w                                                                  | orld application                                                                                                                                                                                                                                                                                                                                                                        | 91                                                                                             |

|   | <b>to a</b><br>8.1                                        |                                                                         | <b>vorld application</b><br>vell do the compiler techniques perform on different platforms?                                                                                                                                                                                                                                                                                             | <b>91</b><br>91                                                                                |

|   |                                                           | How v                                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                |

|   | 8.1                                                       | How v                                                                   | vell do the compiler techniques perform on different platforms?                                                                                                                                                                                                                                                                                                                         | 91                                                                                             |

|   | 8.1                                                       | How v<br>Can k                                                          | vell do the compiler techniques perform on different platforms?                                                                                                                                                                                                                                                                                                                         | 91<br>92                                                                                       |

|   | 8.1                                                       | How v<br>Can k<br>8.2.1                                                 | vell do the compiler techniques perform on different platforms? nowledge gained on one platform help to optimise another platform? Transferability of best configurations found by iterative compilation                                                                                                                                                                                | 91<br>92<br>92                                                                                 |

|   | 8.1                                                       | How v<br>Can k<br>8.2.1<br>8.2.2                                        | vell do the compiler techniques perform on different platforms?                                                                                                                                                                                                                                                                                                                         | 91<br>92<br>92<br>92                                                                           |

|   | 8.1                                                       | How v<br>Can k<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                      | vell do the compiler techniques perform on different platforms? nowledge gained on one platform help to optimise another platform? Transferability of best configurations found by iterative compilation Transferability of program-agnostic optimisation levels                                                                                                                        | <ul> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>92</li> <li>94</li> </ul>             |

|   | 8.1<br>8.2                                                | How v<br>Can k<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.3<br>8.2.4<br>Do the   | vell do the compiler techniques perform on different platforms?         nowledge gained on one platform help to optimise another platform?         Transferability of best configurations found by iterative compilation         Transferability of program-agnostic optimisation levels         Transferability of machine learning models         Summary                             | <ul> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>92</li> <li>94</li> <li>96</li> </ul> |

| 9 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul> | How v<br>Can k<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.3<br>8.2.4<br>Do the   | vell do the compiler techniques perform on different platforms?          nowledge gained on one platform help to optimise another platform?          Transferability of best configurations found by iterative compilation          Transferability of program-agnostic optimisation levels          Transferability of machine learning models          Summary          al evaluation | <ul> <li>91</li> <li>92</li> <li>92</li> <li>92</li> <li>94</li> <li>96</li> <li>97</li> </ul> |

| 9 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul> | How v<br>Can k<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>Do the<br>Critica | vell do the compiler techniques perform on different platforms?          nowledge gained on one platform help to optimise another platform?          Transferability of best configurations found by iterative compilation          Transferability of program-agnostic optimisation levels          Transferability of machine learning models          Summary          al evaluation | 91<br>92<br>92<br>92<br>94<br>96<br>97<br>98                                                   |

# **LIST OF TABLES**

| TAB | LE P                                                                                       | age      |

|-----|--------------------------------------------------------------------------------------------|----------|

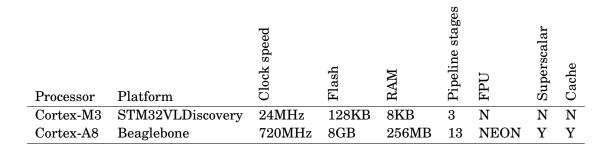

| 2.1 | Hardware features of the target platforms                                                  | 25       |

| 3.1 | Average improvement found by RIC for execution time, energy consumption and code           |          |

| 3.2 | size                                                                                       | 36<br>45 |

| 4.1 | Average improvement made by Milepost and COBAYN                                            | 53       |

| 5.1 | Average improvement made by program-agnostic configurations                                | 68       |

| 6.1 | Average improvement made by ILP prototype                                                  | 81       |

| 7.1 | Average improvement made by ILP                                                            | 90       |

| 8.1 | Average improvement made by transferring the best RIC configuration for each               |          |

|     | BEEBS program on the CM3 to the CA8 and vice versa                                         | 97       |

| 8.2 | Average improvement made by transferring program-agnostic configurations between           |          |

|     | CM3 and CA8                                                                                | 97       |

| 8.3 | Average improvement made by transferring ILP models between CM3 and CA8 $\ .$              | 97       |

| 8.4 | Summary of improvements on neural network case study program $\ldots \ldots \ldots \ldots$ | 98       |

| 8.5 | Average relative standard deviation in the RIC dataset                                     | 100      |

# **LIST OF FIGURES**

| FIG  | IGURE                                                                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 2.1  | HV metric                                                                                                    | 14 |

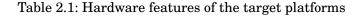

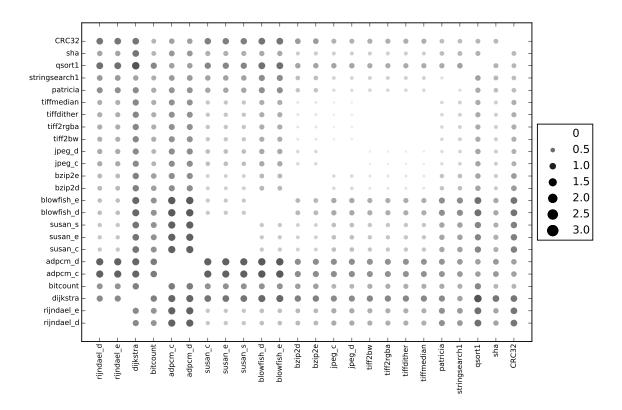

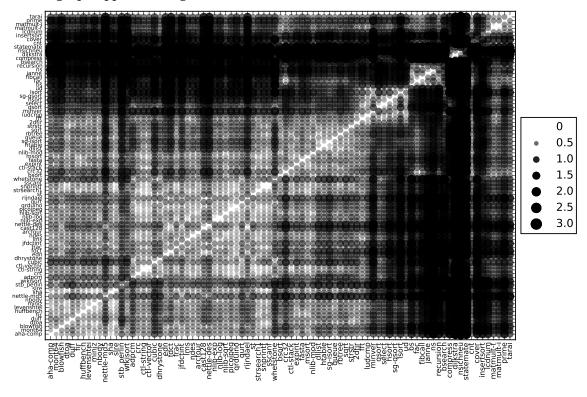

| 2.2  | Euclidean distance between normalised feature vector of each cBench program                                  | 26 |

| 2.3  | Euclidean distance between normalised feature vector of each BEEBS program                                   | 26 |

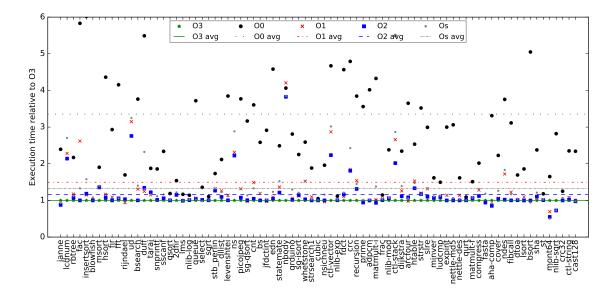

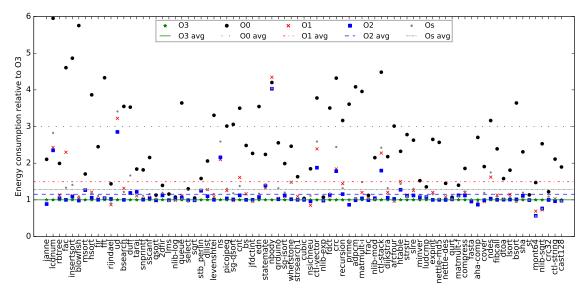

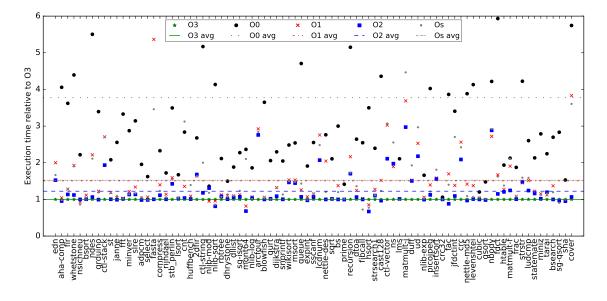

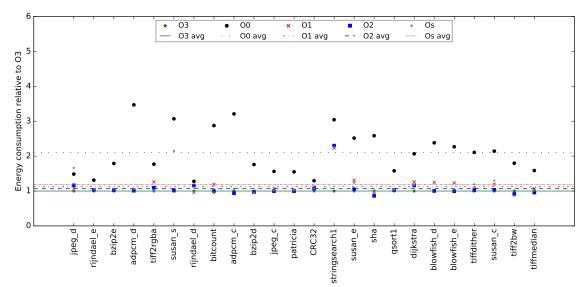

| 3.1  | Execution time of standard optimisation levels (CM3 BEEBS)                                                   | 32 |

| 3.2  | Energy consumption of standard optimisation levels (CM3 BEEBS) $\ldots \ldots \ldots$                        | 32 |

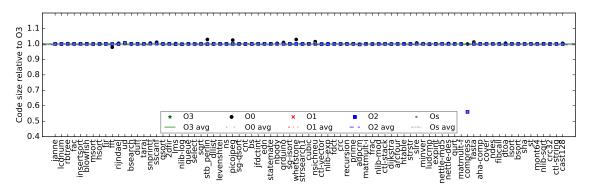

| 3.3  | Code size of standard optimisation levels (CM3 BEEBS)                                                        | 32 |

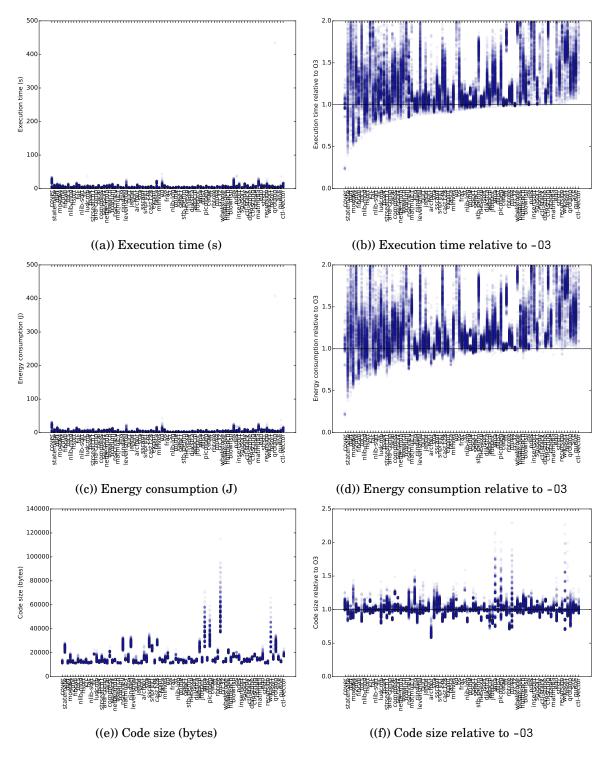

| 3.4  | Execution time of standard optimisation levels (CA8 BEEBS)                                                   | 33 |

| 3.5  | Energy consumption of standard optimisation levels (CA8 BEEBS) $\ldots \ldots \ldots$                        | 33 |

| 3.6  | Code size of standard optimisation levels (CA8 BEEBS) $\ldots \ldots \ldots \ldots \ldots \ldots$            | 33 |

| 3.7  | Execution time of standard optimisation levels (CA8 cBench) $\ldots \ldots \ldots \ldots \ldots$             | 34 |

| 3.8  | Energy consumption of standard optimisation levels (CA8 cBench) $\ldots \ldots \ldots$                       | 34 |

| 3.9  | Code size of standard optimisation levels (CA8 cBench)                                                       | 34 |

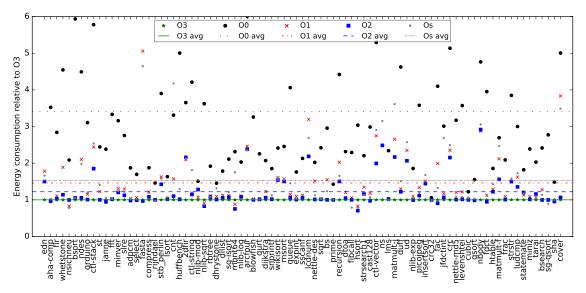

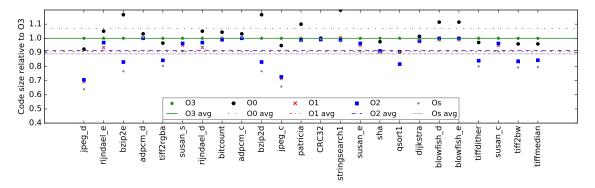

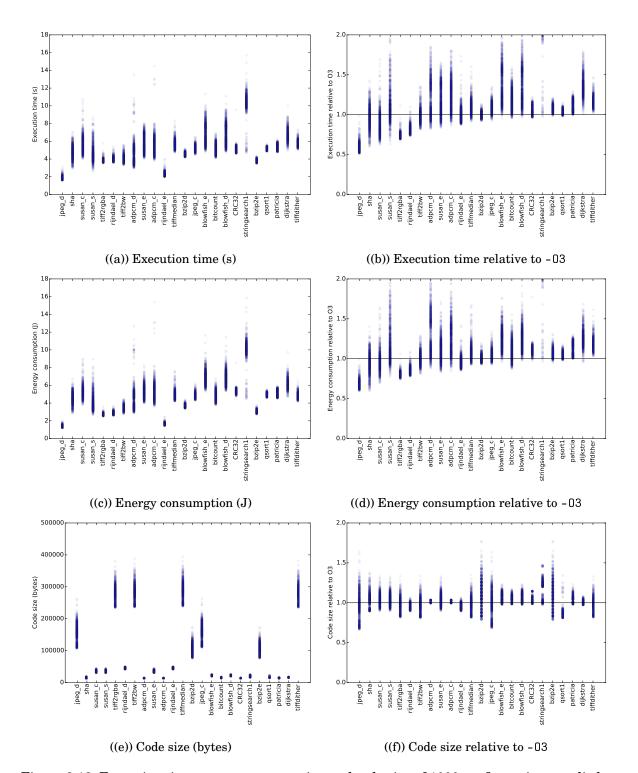

| 3.10 | Execution time, energy consumption and code size of 1000 random configurations                               |    |

|      | applied to each benchmark (CM3)                                                                              | 37 |

| 3.11 | Execution time, energy consumption and code size of 1000 configurations applied to                           |    |

|      | each benchmark (CA8 BEEBS)                                                                                   | 38 |

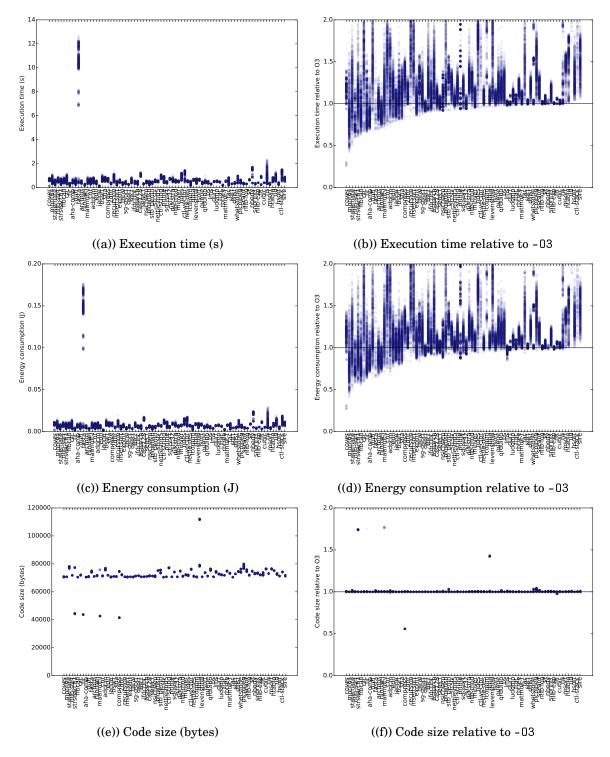

| 3.12 | Execution time, energy consumption and code size of 1000 configurations applied to                           |    |

|      | each benchmark (CA8 cBench)                                                                                  | 39 |

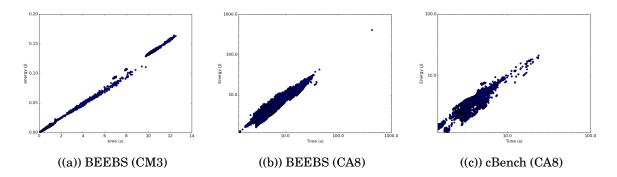

| 3.13 | $Correlation \ between \ time \ and \ energy \ for \ 1000 \ random \ configurations \ across \ all \ bench-$ |    |

|      | marks                                                                                                        | 40 |

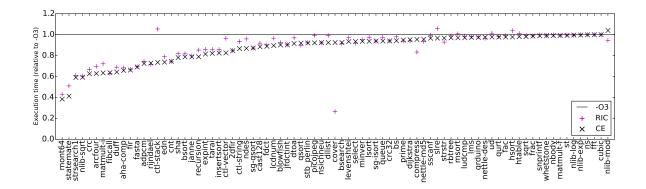

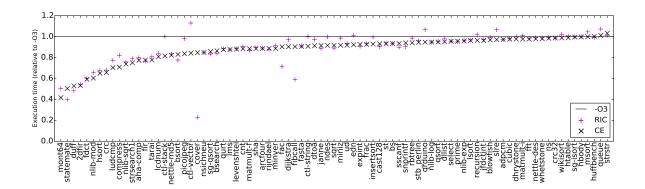

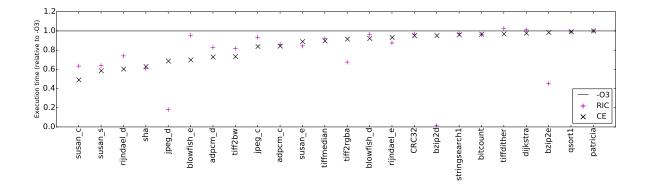

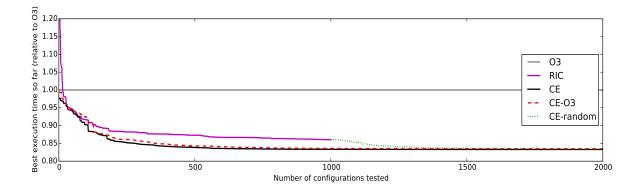

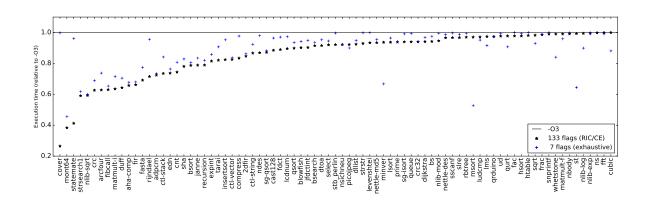

| 3.14 | Best execution time achieved by RIC (1000 configurations) and CE (CM3) $\ \ldots \ \ldots$ .                 | 41 |

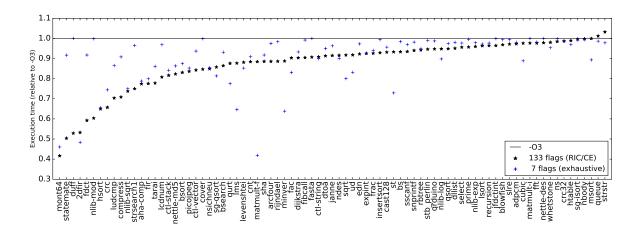

| 3.15 | Best execution time achieved by RIC (1000 configurations) and CE (CA8 BEEBS) $~$                             | 41 |

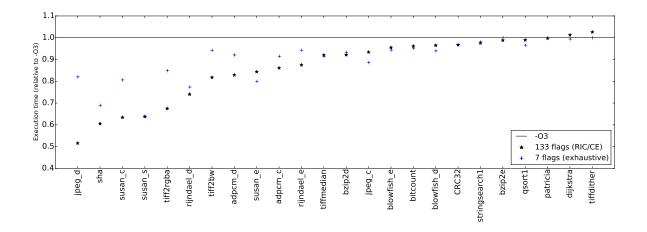

| 3.16 | Best execution time achieved by RIC (1000 configurations) and CE (CA8 cBench)                                | 41 |

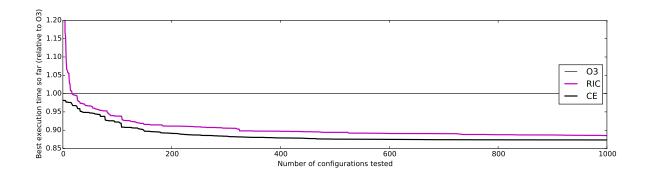

| 3.17 | Average of best execution time for each benchmark after each configuration tested by                         |    |

|      | RIC (1000 configurations) and CE (CM3) $\ldots$                                                              | 42 |

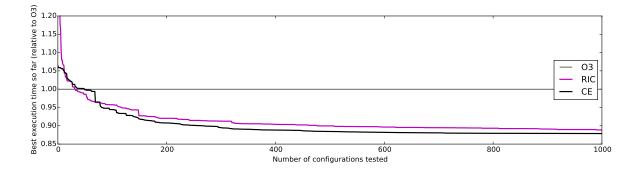

| 3.18 | Average of best execution time for each benchmark after each configuration tested by                         |    |

|      | RIC (1000 configurations) and CE (CA8 BEEBS)                                                                 | 42 |

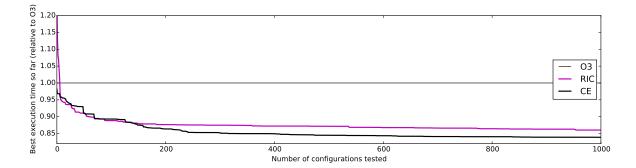

| 3.19 | Average of best execution time for each benchmark after each configuration tested by       |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | RIC (1000 configurations) and CE (CA8 cBench)                                              | 42 |

| 3.20 | Best execution time achieved after each configuration tested for 1000 random configu-      |    |

|      | rations, CE-all, CE-O3 and CE-random (relative to O3)                                      | 44 |

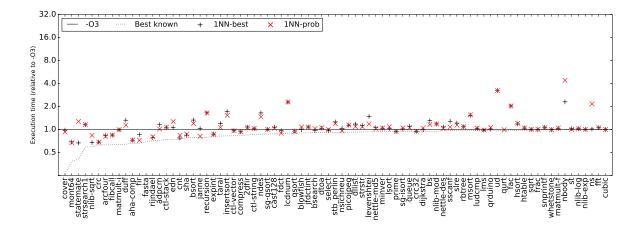

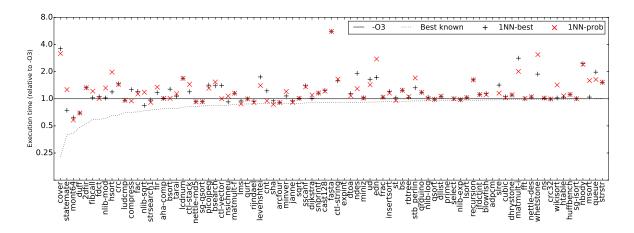

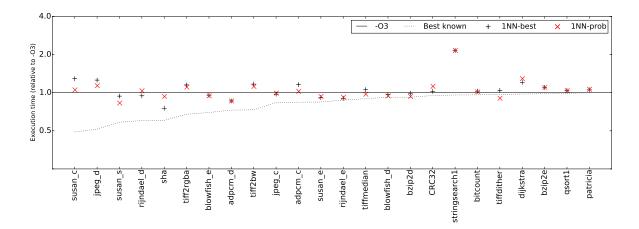

| 4.1  | Performance of 1NN-best and 1NN-prob (CM3)                                                 | 48 |

| 4.2  | Performance of 1NN-best and 1NN-prob (CA8 BEEBS)                                           | 49 |

| 4.3  | Performance of 1NN-best and 1NN-prob (CA8 cBench)                                          | 49 |

| 4.4  | Performance of exhaustive search (7 flags) and RIC/CE search (133 flags) (CM3) $\ldots$    | 51 |

| 4.5  | Performance of exhaustive search (7 flags) and RIC/CE search (133 flags) (CA8 BEEBS)       | 51 |

| 4.6  | Performance of exhaustive search (7 flags) and RIC/CE search (133 flags) (CA8 cBench) $$   | 51 |

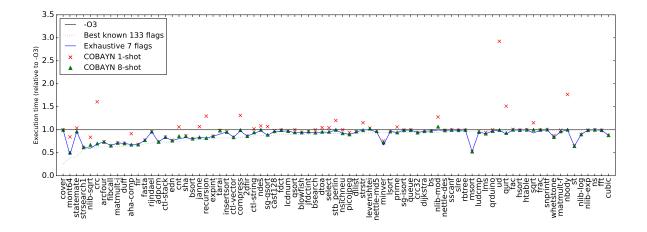

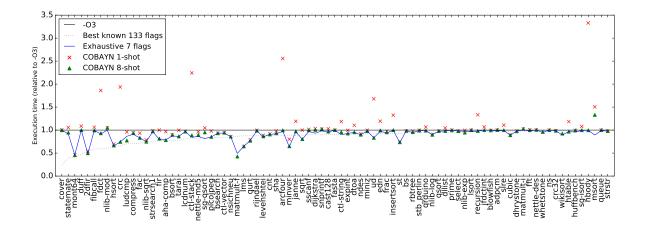

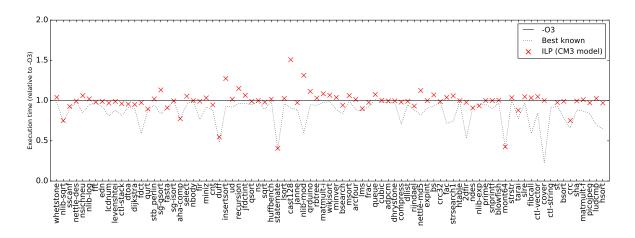

| 4.7  | Performance of COBAYN in 1-shot and 8-shot mode (CM3)                                      | 54 |

| 4.8  | Performance of COBAYN in 1-shot and 8-shot mode (CA8 BEEBS)                                | 54 |

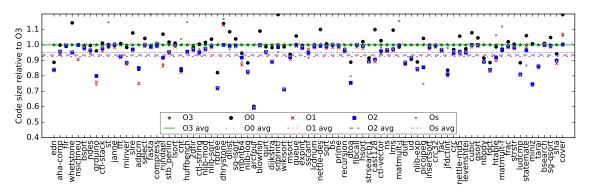

| 5.1  | Trade-off between thresholds for constructing -Ocm3                                        | 58 |

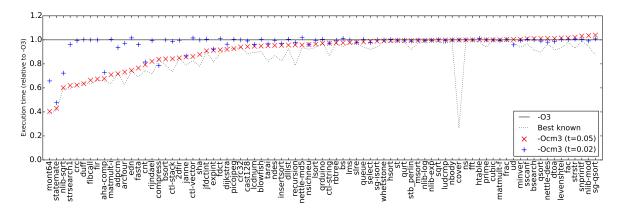

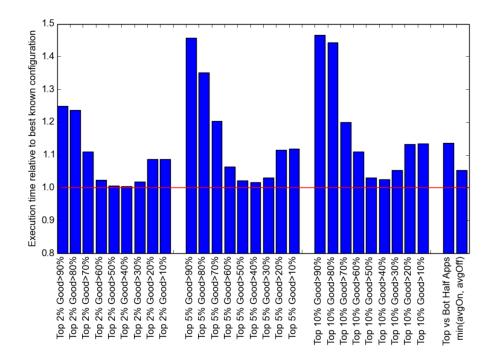

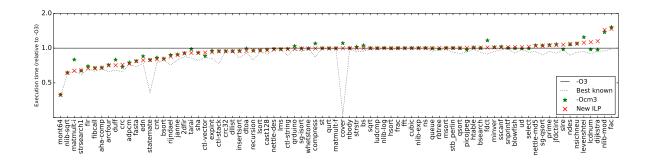

| 5.2  | 10-fold cross-validation of -0cm3, Milepost 1NN and COBAYN 1-shot (logarithmic scale)      | 61 |

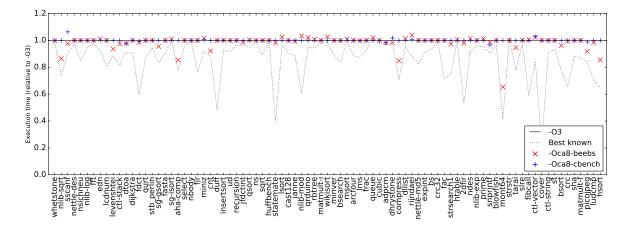

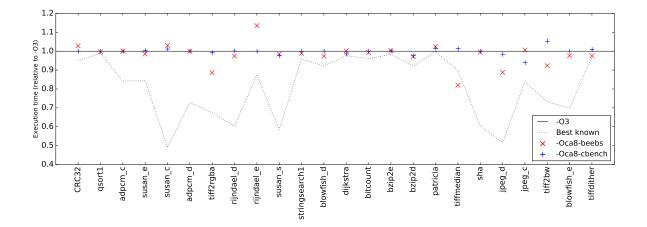

| 5.3  | Performance of -Oca8-beebs and -Oca8-cbench on CA8 BEEBS                                   | 63 |

| 5.4  | Performance of -Oca8-beebs and -Oca8-cbench on CA8 cBench                                  | 64 |

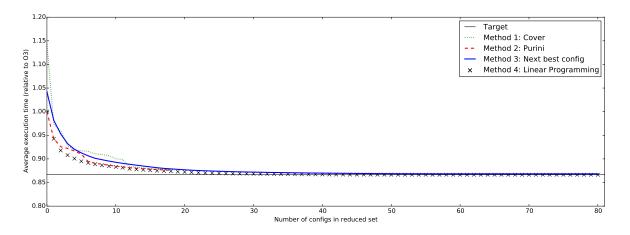

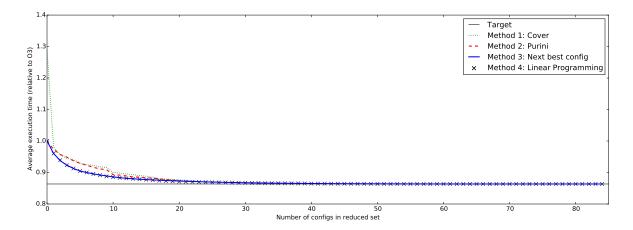

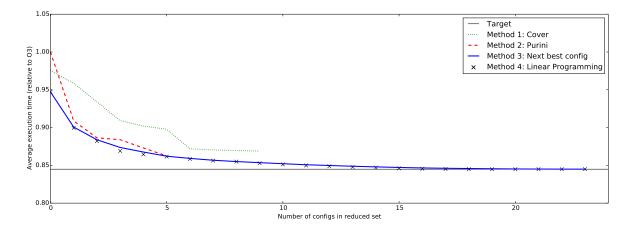

| 5.5  | Performance of each method for producing a reduced set (CM3) $\ldots \ldots \ldots \ldots$ | 67 |

| 5.6  | Performance of each method for producing a reduced set (CA8 BEEBS)                         | 67 |

| 5.7  | Performance of each method for producing a reduced set (CA8 cBench)                        | 68 |

| 6.1  | Comparison of flag selection methods                                                       | 75 |

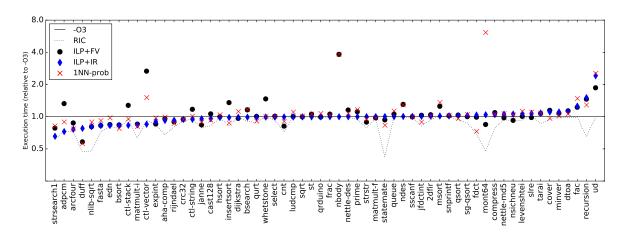

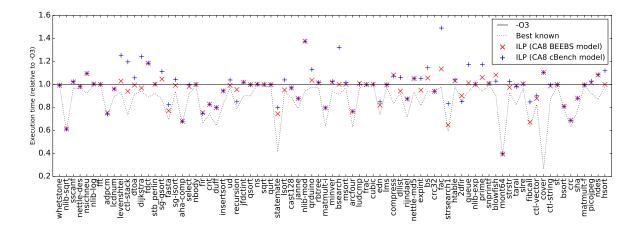

| 6.2  | ILP+FV, ILP+IR, 1NN-prob and best of 1000 random configurations                            | 79 |

| 6.3  | ILP+IR/1NN-prob/O3 hybrid and best of 1000 random configurations                           | 80 |

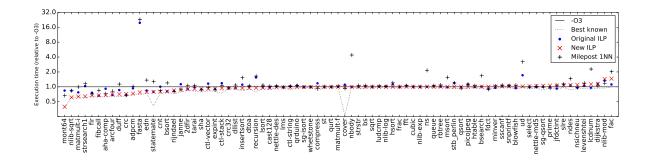

| 7.1  | Performance of new ILP compared to original ILP approach and Milepost 1NN (loga-           |    |

|      |                                                                                            | 86 |

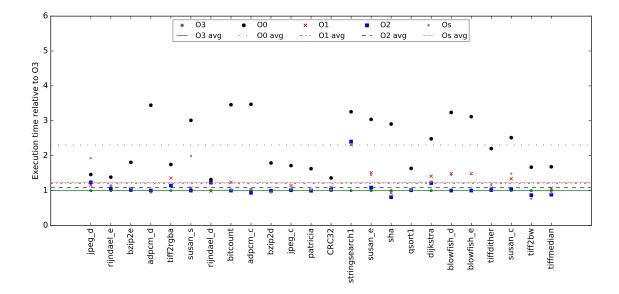

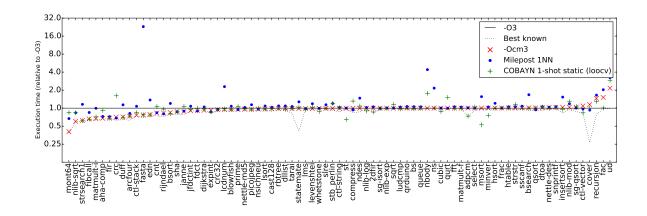

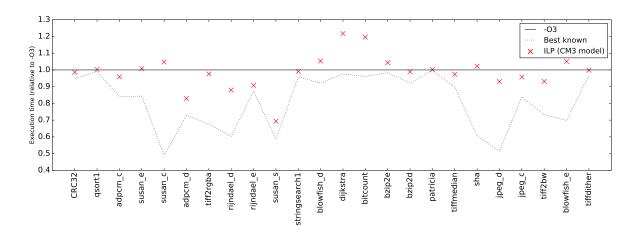

| 7.2  | Performance of -Ocm3-ilp on the Cortex-M3 (logarithmic scale)                              | 88 |

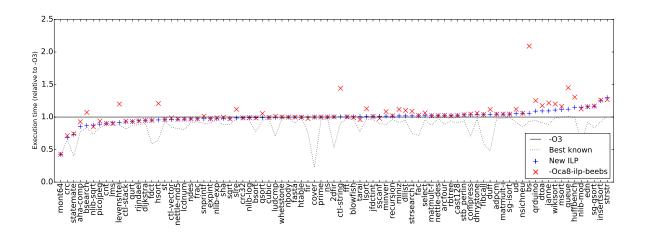

| 7.3  | <b>▲</b>                                                                                   | 89 |

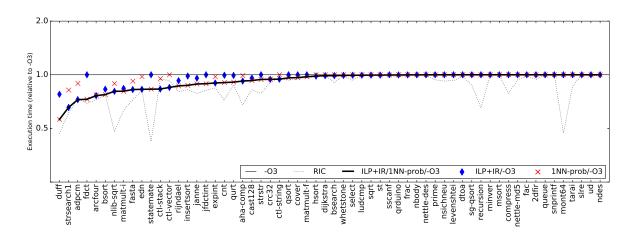

| 7.4  | Performance of new ILP method and -Oca8-ilp on CA8 cBench                                  | 89 |

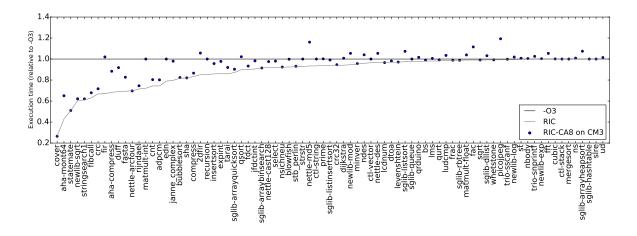

| 8.1  | Best RIC configuration for CM3 tested on the CA8                                           | 93 |

| 8.2  | Best RIC configuration for CA8 tested on the CM3                                           | 93 |

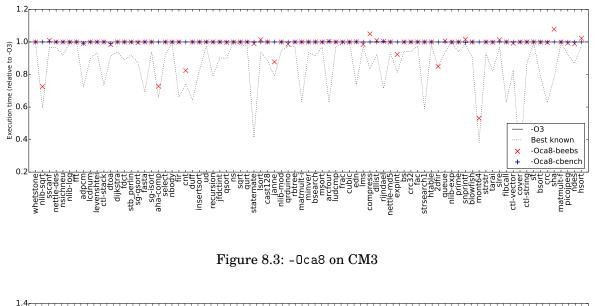

| 8.3  | -Oca8 on ${ m CM3}$                                                                        | 94 |

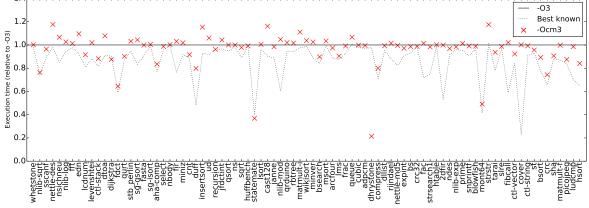

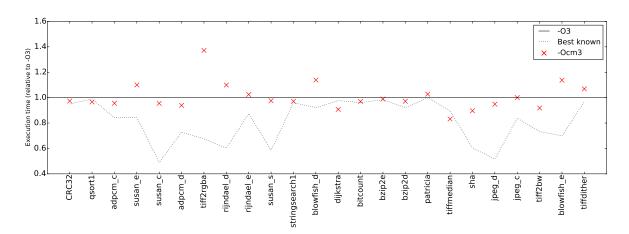

| 8.4  | -Ocm3 on CA8 BEEBS                                                                         | 94 |

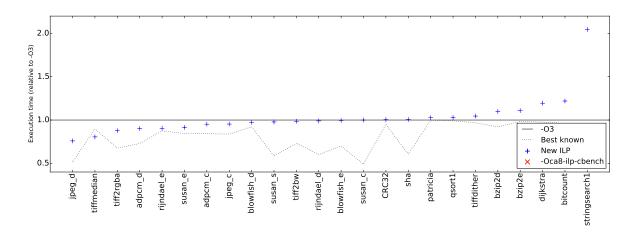

| 8.5  | -Ocm3 on CA8 cBench                                                                        | 95 |

| 8.6  | CA8 ILP BEEBS and cBench models tested on CM3                                              | 95 |

| 8.7  |                                                                                            | 96 |

| 8.8  | CM3 ILP model tested on CA8 (cBench)                                                       | 96 |

LIST OF LISTINGS

| LISTING |                                |    |

|---------|--------------------------------|----|

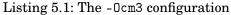

| 5.1     | The -Ocm3 configuration        | 58 |

| 5.2     | The -Oca8-beebs configuration  | 63 |

| 5.3     | The -Oca8-cbench configuration | 63 |

### INTRODUCTION

As Internet of Things (IoT) edge devices take on more computationally intensive tasks, the execution time and energy consumption of applications running on embedded systems becomes increasingly important. The whole system stack, from low level physical design of hardware to high level design of software and algorithms, contributes to the energy and time efficiency of an application. The compiler has a significant impact on how efficiently the software utilises the underlying hardware.

Modern compilers offer a range of standard optimisation levels (e.g. -01, -02, -03) that are intended to progressively improve the execution time of programs at the expense of increased compile time, code size and/or conformance to software standards (Sec. 2.1.2). The most well known is the -03 optimisation level provided by the industry standard GCC compiler [69] (and its more recent competitor Clang [70]). Previous work [27, 19, 57, 10, 18, 3] has shown that -03 is far from optimal in many cases; by selectively enabling or disabling compiler flags that control optimisation settings, the compiler can be fine-tuned to improve the performance of a given program and target platform. This leads to significant gains without the need to modify the underlying source code or compiler, but it is infeasible to search exhaustively for the optimal configuration of flags due to the very large search space.

The optimal set of compiler flags is dependent on the target program, platform, compiler and metric. Furthermore, optimisations can interact in complex and unknown ways [19, 57]; for example, applying one optimisation could improve or hinder the success of a later optimisation.

Automatically tuning the selection of these flags is essential to feasibly address the diverse range of programs that can be written, tailor the compiler to its growing set of supported platforms and handle the increasing number of optimisations added to each new version of the compiler. Keeping up with embedded platforms is more difficult than for more popular x86 targets which have a much larger user base and therefore receive a lot more development effort.

Additionally, embedded platforms may not possess all of the hardware features necessary for some optimisations to be successful.

Existing work [27, 59, 71, 61, 22] uses random sampling or more complex iterative compilation methods (which evaluate the performance of a given program compiled with a large number of different configurations) to search for configurations that improve the performance of a target program. This is a time consuming task that must be repeated for each program and platform pair. The slow search time motivated other studies to use iterative compilation to train machine learning approaches to predict good configurations more quickly, at the cost of potentially reduced performance for an unseen program.

Most predictive compiler tuning approaches rely on feature vectors of simple program properties that summarise characteristics of the source code. These predefined features seem to be selected because they are simple and easy to measure rather than for their predictive power [48, 45]. Furthermore, reducing programs to these feature vectors loses valuable structural information that could be used to make more accurate models.

This thesis explores how Inductive Logic Programming (ILP) can exploit an Intermediate Representation (IR) of programs that preserves structural information in order to produce more accurate models by automatically identifying relevant program features. The proposed method uses ILP to infer logical rules that relate effective compiler flags to program features. These rules can be easily converted into sentences and thus provide a white-box approach that gives insight into the relationship between program structure and compiler flags.

In developing the ILP compiler tuning approach, several assumptions in previous work are challenged to increase understanding of the problem and give a robust evaluation of compiler tuning techniques. The choice of benchmarks, evaluation techniques and measurement setup is essential – a re-evaluation of two state-of-the-art predictive approaches shows that they may not work as well as previously thought.

The ILP approach learns several facts that suggest some flags should always be enabled or disabled for the target platform. These facts are used to construct new program-agnostic optimisation levels tailored to each target platform. In this case, the new levels are a by-product of the learned model, but other techniques have specifically targeted the goal of automatically constructing new optimisation levels [38]. Such approaches have received much less attention from the compiler tuning community than machine learning approaches and there does not exist a good comparison between the two. This thesis shows that program-agnostic optimisation can often outperform more complex machine learning techniques that target individual programs.

In industry there are benefits to seeking out program-agnostic configurations rather than applying machine learning to individual programs. The new configurations can be constructed once and distributed easily to be used by many and they do not require machine learning implementations to be installed and tuned. Furthermore, the new optimisation levels could also be tested rigorously to increase confidence in their robustness, for example, by running the GCC test suite on these configurations.

# **1.1 Research questions**

The primary objective of this thesis is to design, implement and evaluate an ILP based compiler tuning approach to investigate the hypothesis that learning directly from IR increases predictive accuracy. The following aims and research questions were investigated in order to realise this objective.

#### Investigate the potential gains of compiler tuning

- What is the actual impact of the standard optimisation levels on execution time, energy consumption and code size?

- What are the potential gains from fine-tuning optimisation selection?

- What is the relationship between energy consumption and execution time?

- How can it be ensured that benchmarks provide a realistic evaluation of compiler tuning techniques?

#### Evaluate state-of-the-art predictive approaches on the target platforms

• How well do two state-of-the-art predictive approaches work on a diverse set of benchmarks on the target platforms?

# Determine whether tuning to the platform as whole is sufficient or if program-specific optimisation is indeed required

- Are some optimisations universally good/bad for performance on a given platform?

- Can a single program-agnostic configuration perform well or is it beneficial to choose settings for each program?

- Can a small set of configurations be constructed such that there exists at least one good configuration for each program, thus providing a smaller set of configurations on which to run iterative compilation?

#### Design, develop and evaluate an ILP based compiler tuning approach

- How can the effects of individual optimisations within a configuration be quantified?

- Is it feasible to apply ILP to compiler tuning?

- How can ILP based compiler tuning be designed?

- How can relevant features be automatically discovered by the machine learner?

## Investigate the generality and transferability of the techniques developed in this thesis

- How well do compiler tuning techniques perform on different platforms and benchmarks and how can an appropriate method be selected for a given scenario?

- Can models learned for one platform yield useful information for another?

- How well do the results seen on benchmark suites translate to real world improvements on a realistic use case?

# **1.2 Contributions**

This section summarises the main contributions of this thesis.

**Contribution to a large open source embedded benchmark suite.** The Bristol/Embecosm Embedded Benchmark Suite (BEEBS) is the largest and most diverse free open source benchmark suite for resource limited embedded systems. This thesis fixes a conceptual flaw in the design of the suite to provide a robust and realistic evaluation of compiler tuning techniques (Sec. 3.1).

**Analysis of potential gains of compiler tuning** In this thesis, the development of compiler tuning methods is motivated by exploring the potential improvements available for execution time, energy consumption and code size (Ch. 3). Iterative compilation is used to time-intensively search the configuration space and provide a lower bound on the improvements available. These experiments find a strong correlation between energy and time on each platform. The analysis also finds that Combined Elimination (CE) [59] outperforms the commonly used Random Iterative Compilation (RIC) [27, 63, 3] in several cases, which is in contrast to a previous study [18]. The results produced in this analysis form the basis for machine learning training data in the rest of this work.

**Re-evaluation of two state-of-the-art predictive compiler tuning approaches** Milepost [27] and COBAYN [10] are re-evaluated on the two platforms targeted by this thesis using the BEEBS benchmark suite which is over three times as large as cBench used in the original studies. The BEEBS programs present a harder challenge to the machine learner and offer a more thorough and realistic evaluation of compiler tuning techniques. Consequently, BEEBS uncovers limitations that were not visible in previous evaluations with cBench. These

re-evaluations enable the previous work to be compared directly with the methods developed in this thesis on the same experimental setup.

**Construction of program-agnostic configurations** For each platform, a single configuration that outperforms -03 across a whole set of representative benchmarks is constructed (Ch. 5). The new configurations provide significant gains and, once constructed, can be applied to any new program with no further effort. They also outperform existing more complex machine learning approaches in several cases, but they still do not capture all of the available improvements found by iterative compilation, therefore, a program-specific approach is still beneficial.

In between program-agnostic and program-specific configuration is the task of finding a small set of configurations for the platform such that, for each program, there exists at least one good configuration. This thesis presents an Integer Linear Programming solution to this problem that improves the state of the art [63] by guaranteeing the optimal reduction of a larger set of configurations. This creates a small set of configurations tailored to the target platform on which a small iterative compilation search can be performed.

**Design, development and evaluation of ILP based compiler tuning** This thesis explores whether an ILP based method can be developed that automatically discovers relevant program features to learn more accurate models than feature vector approaches (Ch. 6). First a prototype ILP approach that leverages IR is designed, implemented and evaluated against a feature based approach (Ch. 6). The initial approach uncovers some limitations that are addressed in Ch. 7 to create an even more accurate model that provides better performance. These centre around improving the training input for ILP and modifying the way in which the ILP system searches for and evaluates candidate rules. As part of this process, practical limitations are identified and overcome to enable the approach to be applied to large programs.

**Analysis of the generality and transferability of compiler tuning approaches** Compiler tuning can be applied to a range of platforms, but the model for each platform is usually trained and tested in isolation. Chapter 8 shows that knowledge gained for one platform can also improve performance for a second platform and potentially save the effort of performing a new iterative search and/or constructing a new model for the second platform.

The techniques developed in this thesis are tested on a Neural Network case study, on which program-agnostic optimisation provides the best speed-up and energy improvement, reinforcing the finding that program-agnostic configuration is competitive with more complex machine learning approaches.

In conclusion, the ILP approach developed and evaluated in this thesis outperforms existing feature vector based approaches thus confirming the hypothesis that learning directly from IR increases predictive accuracy.

# **1.3 Related publications**

• C. Blackmore, O. Ray, and K. Eder.

A logic programming approach to predict effective compiler settings for embedded software.

Theory and Practice of Logic Programming, 15(4-5):481-494, 2015

This paper introduces the design, implementation and evaluation of the prototype ILP approach. The work is presented in Ch. 6 with extra detail on design decisions. This paper also includes an early version of the Milepost re-evaluation that appears in Ch. 4.

• C. Blackmore, O. Ray, and K. Eder.

Automatically discovering human-readable rules to predict effective compiler settings for embedded software.

#### Automated Reasoning Workshop, 2017

This extended abstract provides an interim update to the ILP approach by focusing the generation and processing of training inputs. Chapter 7 builds on this work.

• C. Blackmore, O. Ray, and K. Eder.

Automatically tuning the gcc compiler to optimize the performance of applications running on embedded systems.

#### arXiv:1703.08228 [cs.DC], 2017

This paper demonstrates the benefit of constructing program-agnostic configurations for embedded platforms. The work also appears in Ch. 5. The paper also fixes a conceptual flaw in the design of BEEBS and provides an comparison of the RIC and CE methods – these contributions appear in Ch. 3. Although the paper is is not published in a peer-reviewed venue, the authors feel the results are worthy of dissemination.

• C. Blackmore, O. Ray, M. Kull, M. G. Rahman, P. Flach, and N. Lachiche.

Reframing of Classification and Regression Tasks for Predicting the Effects of Compiler Settings on Multiple Embedded Systems.

#### In 2nd International Workshop on Learning over Multiple Contexts, 2015

This paper gives an introduction to the challenges of targeting multiple platforms with compiler tuning. It inspired work in Ch. 8.

• K. Georgiou, C. Blackmore, S. Xavier-de Souza, and K. Eder.

Less is more: Exploiting the standard compiler optimization levels for better performance and energy consumption. In Proceedings of the 21st International Workshop on Software and Compilers for Embedded Systems, SCOPES '18, pages 35–42, New York, NY, USA, 2018. ACM

This paper targets optimisation sequences in Clang/LLVM. It shows how performance can be improved significantly by applying fewer of the optimisations defined in an existing standard optimisation level while preserving their original ordering. Specifically, the approach searches for the optimal point at which to stop applying the sequence of optimisations in -02. The work falls outside the scope of this thesis, although it defines an interesting problem that the techniques in this thesis could be applied to in future.

## **1.4 Thesis structure**

The rest of this thesis is structured as follows:

**Chapter 2 – Background** This chapter provides the background necessary to understand the scope of this thesis and the wider context of this research area. First there is a review of the various approaches to compiler tuning with particular focus on iterative compilation and predictive approaches. Then there is an introduction to Inductive Logic Programming and its contrast to propositional machine learning techniques that are used by most existing predictive compiler tuning approaches. Finally, there is a summary of the hardware platforms targeted in this research and the benchmarks used to measure the impact of different configurations.

**Chapter 3 – Quantifying the potential benefits of compiler tuning** To motivate the exploration of compiler tuning techniques, this section investigates the potential benefits available that compiler tuning offers on a range of platforms and programs. Iterative compilation is used to intensively search for configurations that improve execution time, energy consumption and/or code size on the experimental setup described in this chapter. The advantages and disadvantages of two iterative compilation approaches are analysed. The exploration of the compiler tuning space provides a lower bound on the available improvements for techniques developed in later chapters that, once trained, aim to quickly find a good configuration for a given program.

**Chapter 4 – Re-evaluation of predictive compiler tuning approaches** Two state-of-theart machine learning compiler tuning approaches are evaluated on the two target platforms of this thesis using a much more diverse set of benchmarks than the original studies. This highlights the importance of a representative data set and a carefully designed evaluation methodology. The results provide comparative data for the methods developed in this thesis.

**Chapter 5 – Constructing new program-agnostic optimisation levels** This chapter seeks to find program-agnostic configurations that outperform GCC's -03 optimisation level. These program-agnostic configurations offer a convenient alternative to the default optimisation levels

available in GCC. The fact that these program-agnostic configurations do not capture all of the potential benefits seen in Ch. 3 confirms a predictive approach is indeed required to target programs directly, as explored in the next chapter (Ch. 6).

**Chapter 6 – Applying ILP to compiler tuning** A new ILP-based approach for predicting effective configurations is designed, developed and evaluated. In contrast to previous work, ILP aims to exploit a relational intermediate representation of programs to relate program structure to effective compiler flags. The method outperforms existing propositional approaches and produces human-readable rules that explain why particular flags should be enabled or disabled.

**Chapter 7 – Focusing ILP based compiler tuning** Additional analysis of the ILP approach identifies some limitations that are overcome to produce an even more effective methodology by focusing aspects of the training phase.

**Chapter 8 – Transferability of compiler tuning methods and models across platforms and to a real world application** Compiler tuning techniques can be applied to a wide range of platforms and programs but each platform is usually tested in isolation. This chapter explores how well each approach performs on different platforms and benchmark suites and provides insight into which methods work well in different scenarios. The transferability of a model from one platform to another is also tested.

Finally, a key part of this chapter demonstrates that the advantages seen on benchmark programs in the previous chapters are applicable to real world applications. A case study on the CM3 shows how a Neural Network classifier can be sped-up by 8% on the Cortex-M3 using the program-agnostic configuration created in (Ch. 5).

**Chapter 9 – Conclusion** The impact of the thesis contributions are summarised in the conclusion chapter and directions for future work are recommended.

### BACKGROUND

This thesis combines the research area of compiler tuning with the declarative machine learning technique of Inductive Logic Programming. Compiler tuning is the process of fine-tuning compiler settings to optimise one or more performance goals (e.g. execution time, energy consumption, code size). Inductive Logic Programming aims to infer logical rules that relate specific facts to general rules. Applying ILP to compiler tuning is of particular interest because ILP can directly exploit a relational representation of IR thus retaining important structural information that is not captured by propositional machine learning features used in existing predictive approaches.

The following sections provide the background necessary to understand the scope of this thesis and the wider context of this research area. First there is an introduction to compiler tuning and a review of existing approaches (Sec. 2.1). This is followed by an introduction to ILP (Sec. 2.2) and its contrast to propositional machine learning techniques that are used by most existing predictive compiler tuning approaches. Finally, there is a brief overview of the hardware platforms, benchmarks and measurement techniques that will be used to evaluate compiler tuning techniques in later chapters.

# 2.1 Compiler tuning

There is great potential for compilers to optimise code by applying different transformations that compiler writers have invested considerable effort in developing. Applying the correct set of optimisations is crucial to performance but choosing this set is challenging due to the larger number of flags available and often not well understood interactions between them [19, 57]. Furthermore, the best configuration is dependent on the program and target platform. The challenge increases as new optimisations are added to the compiler, for example, 50 optimisation flags have been added to GCC over the last three years.<sup>1</sup>

#### 2.1.1 Problems in compiler tuning

Two major problems in compiler tuning are choosing which optimisations to apply (the *optimisation selection problem*) (Sec. 2.1.1.1) and selecting the order in which to apply those optimisations (the *phase ordering problem*) (Sec. 2.1.1.2). Tackling either problem can significantly improve one or more compiler tuning goals (e.g. execution time, energy consumption and/or code size) (Sec. 2.1.1.3); most work has focused on the optimisation selection problem [8].

#### 2.1.1.1 Optimisation selection problem

The aim of the optimisation selection problem is to find the set of optimisations that provide the best performance for a given program. The amount of control over optimisations is dependent on the compiler. Each optimisation is applied during a particular stage of compilation, called a *pass*, but not all compilers allow passes to be manipulated directly, instead they can be controlled indirectly via command-line flags. The mapping between flags and passes is complex and often undocumented.

The main mechanism for controlling fine-grained optimisations in GCC is through binary flags that may enable or disable one or more optimisation passes and parameterised flags that control numerical settings for optimisations (e.g. unroll factor, loop tiling size). This thesis focuses on binary flags. Each flag begins with -f and most have an opposite version beginning with -fno that disables the optimisation (e.g. function inlining can be switched on using finline-functions and switched off using -fno-inline-functions).

There are additional flags that directly enable or disable passes (-fenable-kind-pass and -fdisable-kind-pass) but these are only intended for use by compiler developers to debug the compiler and using them can easily produce invalid combinations due to functional dependencies between passes and untested/unsupported combinations. In production, users are expected to use the normal -f and -fno flags [69]. Regardless of whether flags or passes are manipulated, the user is unable to change the order in which passes are applied; this is determined internally by GCC's pass manager.

An exhaustive search of the optimisation space is infeasible due to the large number of optimisations available. For example, GCC 4.9.3 has over 150 flags that can be enabled or disabled. This results in over  $2^{150}$  possible configurations which would take over  $10^{36}$  years to search exhaustively supposing optimistically that it takes a second to compile and run a program with a single configuration.

<sup>&</sup>lt;sup>1</sup>This figure is based on the flags listed by gcc -help=opt -Q in GCC 4.9.3 (May 2015) and GCC 8.0.1 (Mar 2018).

#### 2.1.1.2 Phase-ordering problem

The phase-ordering problem aims to find the optimal sequence of optimisations to apply. In theory, the configuration space is infinite as passes can be applied any number of times, although the benefits are likely to diminish after a while. In contrast to GCC, the LLVM optimiser opt gives the user direct control over the selection and ordering of optimisation passes.

Techniques addressing the optimisation selection problem can be applied to a wider range of compilers than the phase ordering problem as more compilers offer control over optimisation selection than ordering.

#### 2.1.1.3 Compiler tuning goals

Compiler tuning can be used to target any goal that a) can be measured and b) can be influenced by the compiler. Most work has focused on improving execution time, code size and/or compilation time, including multi-objective goals that seek to improve a combination of these metrics. Recently, there has been increased interest in optimising energy consumption which is particularly important on battery powered embedded systems (e.g. IoT devices) but only a few works in compiler tuning focus on energy [57, 32].

#### 2.1.2 Standard optimisation levels

Modern compilers provide standard optimisation levels which enable a predefined set of optimisations. GCC provides -00, -01, -02 and -03 which enable an increasing set of optimisations at the expense of code size [69]. There is also -0s which is similar to -02 except it disables optimisations expected to increase code size. Finally, -0fast applies additional optimisations to -03 that do not conform to industry standards (e.g. IEEE floating point) and therefore compromise precision and reproducibility. Although these optimisation levels are convenient for the user, better settings can often be found with extra effort (Sec. 2.1.3.1 below).

#### 2.1.3 Iterative compilation

Early work on compiler tuning focused on iterative compilation methods [43] that compile a target program with several different compiler configurations and evaluate the performance of each resulting compilation in order to find a good one. This is a time-consuming task that must be repeated for each new program and platform combination but in practice it yields significant gains. There are several approaches for selecting which configurations to test in iterative compilation; these can be split into the following three categories:

1. No prior knowledge (RIC [27, 10, 3], Fractional Factorial Design (FFD) [57]) – all configurations tested are chosen before running the experiments.

- 2. Feedback directed (CE [59], Optimisation Space Exploration (OSE) [71], Statistical Selection (SS) [61], Genetic Algorithm (GA) [3]) the results of previous iterations are used to direct the search.

- 3. Machine learning guided [18, 10]) a trained machine learning model is used to bias the configuration selection at each iteration.

Techniques in the first two categories can be used on any new program, do not require a model to be learned but are time-consuming as they select and evaluate a large number of configurations. The third category represents an overlap between iterative and predictive methods and will be discussed in Sec. 2.1.4.

Most iterative compilation studies have targeted the performance of individual programs (Sec. 2.1.3.1). The task of creating new optimisation levels that improve the performance of a wide range of programs has received less attention (Sec. 2.1.3.2), but as Ch. 5 concludes, solutions to this problem are competitive with state-of-the-art machine learning based approaches.

#### 2.1.3.1 Program-specific iterative compilation

The simplest approach, *Random Iterative Compilation* (RIC), uses straight-forward random sampling of compiler flags to construct a set of configurations for evaluation. Fursin et al. reported an average speed-up of 15% on an ARC embedded processor and 33% and 40% on Intel and AMD general purpose processors respectively [27]. More advanced methods use knowledge from previous iterations to guide the search and decide which configuration to try next, however, existing studies conclude that RIC often outperforms them [3, 18].

Cooper et al. [22] used a genetic algorithm to search the optimisation space for sequences that reduce code size. Based on the GA results, a single optimisation sequence was constructed manually that performed within 6% of the best sequence found by GA on each program. Running the GA separately for each module in the program gave up to 2% improvement over using the same sequence for the whole program. The GA approach still requires a new search for each program, therefore, like other iterative methods it is time-consuming. Agakov et al. [3] later used a GA to optimise for execution time and found that RIC performed better overall.

Another approach called *Combined Elimination (CE)* seeks to analyze the effect of each flag relative to an initial baseline, which has all flags enabled, and continually updates the baseline by disabling the flag that has the largest negative impact on performance. As CE is used later in this thesis, a brief description of the CE algorithm presented by Pan et al. [59] is given as follows. The algorithm uses Relative Improvement Percentage (RIP) to measure the impact of a given flag in relation to a given configuration and target program. Let  $F_1, F_2, ..., F_n$  be the set of available compiler flags. The impact of flag  $F_i$  relative to the baseline configuration B is calculated by the following:

$$RIP_{B(F_i)} = \frac{T_{B(F_i=0)} - T_B}{T_B} * 100$$

where  $T_B$  is the execution time of the target program when compiled with configuration B and  $T_{B(F_i=0)}$  is the execution time given by the same configuration with flag  $F_i$  disabled. The algorithm proceeds as follows:

- 1. Let  $S = \{F_1, F_2, ..., F_n\}$  be the optimisation search space and  $B = \{F_1 = 1, F_2 = 1, ..., F_n = 1\}$  be the baseline configuration with all flags enabled.

- 2. Calculate the  $RIP_{B(F_i)}$  for each flag  $F_i \in S$ .

- 3. Let  $X = \{X_1, X_2, ..., X_m\}$  be the set of flags with negative RIPs sorted in ascending order such that  $X_1$  has the most negative RIP.

- 4. If  $X = \emptyset$  then terminate with *B* as the final configuration.

- 5. Remove  $X_1$  from *S* and *X* and let  $B = B(X_i = 0)$ .

- 6. For i = 2 to *m* recalculate  $RIP_{B(X_i)}$  and if  $RIP_{B(X_i)} < 0$  remove  $X_i$  from *S* and *X* and let  $B = B(X_i = 0)$ .

- 7. Goto step 2.

Pan et al. [59] showed that CE outperforms two other iterative compilation approaches called Optimization-Space Exploration (OSE) [71] and Statistical Selection (SS) [61]. OSE searches a subset of the optimisation space and iteratively combines good performing configurations; and SS aims to identify whether each flag has a positive or negative effect for the target program and enable/disable them accordingly. Later, Cavazos et al. compared RIC and CE and concluded that RIC outperformed CE. Chapter 3 reaches the opposite conclusion, albeit on a different experimental setup, and the strengths and weaknesses of the two approaches are discussed.

A small number of studies have used iterative compilation to reduce energy consumption. Gheorghita et al. [32] used the Wattch simulator [17] to model energy consumption in their iterative compilation experiments which tested different parameters for loop unrolling and tiling optimisations. The study concluded that iterative compilation is also beneficial in reducing energy consumption. Configurations that improved runtime also often reduced energy consumption, but there were several cases for which this was not true. In addition, time efficient configurations were more likely to also be energy efficient than vice versa.

Pallister et al. [57] used iterative compilation to quantify the effects of individual flags on the energy consumption of embedded platforms including the CM3 and CA8 using 82 flags from GCC 4.7 and an early version of BEEBS which contained ten benchmarks. Fractional Factorial Design [33] was used to systematically select a subset of the optimisation space intended to capture interactions between flags. The study found a set of five flags for the fdct benchmark running on the CM3 that improved both time and energy but in disproportionate amounts. On the CA8, execution time often decreased more then energy consumption. One exception was noted where enabling -ftree-vectorize on 2dfir improved energy but not execution time.

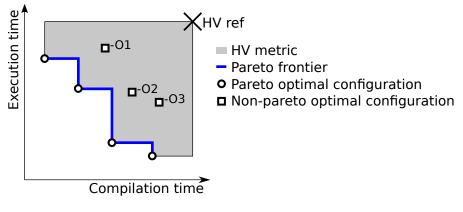

Figure 2.1: HV metric

#### 2.1.3.2 Program-agnostic iterative compilation

Iterative compilation is usually applied to a single target program. In contrast, Hoste et al. [38] proposed Compiler Optimisation Level Exploration (COLE) to find new optimisation levels by changing the goal of iterative compilation to optimise the average performance of a benchmark suite rather than the performance of a single program. A genetic algorithm was used to search the configuration space with the multi-objective goal of reducing compilation time and execution time. The approach produced a set of eleven *Pareto optimal* configurations (a Pareto optimal configuration dominates all other tested configurations on at least one of the objectives). Of the eleven configurations, the first provides the best overall compilation time and the last gives the best overall execution time.

Overall, the majority of improvements were for compilation time rather than execution time. The best configuration for execution time made a modest 3% improvement over -O3 on GCC 4.1.2 but with a 38% faster compilation time.

A set of Pareto optimal configurations, known as a *Pareto frontier*, is typically evaluated using the hypervolume (HV) metric which measures the objective space covered in excess of the *HV reference* (often selected as the worse performance observed for any configuration). In COLE, the HV metric of the eleven new optimisation levels was compared to that of the existing -01, -02 and -03 levels.

At benchmark level, only the HV metric (Fig. 2.1) was reported, which confounds the impact of each individual configuration and obscures whether the improvements are for execution time or compilation time. It is also not clear whether some programs performed significantly poorly under the COLE optimisation levels.

COLE found several programs that were insensitive to program-specific optimisation; in these cases, targeting the program directly with iterative compilation offered little improvement over the program-agnostic configurations. There is no existing comparison to quantify the additional benefit that program-specific machine learning models offer over constructing program-agnostic optimisations. The latter has been largely overlooked in this domain and is addressed in Ch. 5.

Purini et al. [63] aimed to downsample a large set of randomly sampled configurations to a reduced set that contains at least one good configuration for each benchmark. Once generated, the reduced set can then be used for a small iterative compilation search on new programs. The study targeted the phase-ordering problem on LLVM and defined a good configuration as performing better than -02. Each of the three methods tested had the primary objective of covering the most benchmarks with the reduced set (a benchmark is covered if the reduced set contains at least one good configuration for that benchmark). Such an objective treats each program as equally important and as a consequence, the approach may focus too much on programs with small available gains and not enough on those with higher potential for improvement. Chapter 5 proposes an Integer Logic Programming solution to this problem that, in contrast to [63], guarantees the best k reduction of the initial pool of configurations, with the primary objective of improving the overall performance of the benchmark suite.

#### 2.1.4 Machine learning

Due to its time-intensive nature, it is clearly infeasible to use full iterative compilation every time a programmer wants to compile a new program. This motivated other studies to use iterative compilation data to train machine learning based approaches that seek to predict a suitable configuration to optimise a given target program. Typically, these methods train a model that takes an input describing characteristics of the target program and outputs a predicted configuration. These methods exhibit a trade-off between the time taken to find a solution and the quality of that solution.

In the *training phase* a model is learned that correlates program features to effective configurations. In the *deployment phase* the model predicts k configurations for the target program, called *k*-shot prediction. When k = 1, a single configuration is chosen. When  $k \ge 2$ , iterative compilation must be run on each predicted configuration to determine the best one, thus compromising on search time to reach further improvements. The latter mode uses machine learning to guide the iterative compilation search and has been shown to find good configurations faster than naive random iterative compilation [3, 18]. The stronger the model, the lower k should be required to achieve good performance.

Many predictive compiler tuning approaches rely on feature vectors of statistical aggregates that summarize characteristics of the target program code. These methods seek to correlate program features with effective configurations but finding the most relevant features is nontrivial (Sec. 2.1.4.4). Features are typically chosen by intuition or onerously generating and evaluating different candidates. The optimal feature set may also depend on the platform and tuning task at hand. The ILP method introduced in this thesis embeds feature construction into the machine learning process.

The rest of this section summarises various machine learning approaches to compiler tuning including 1-nearest-neighbour and decision trees (Sec. 2.1.4.1); bayesian networks (Sec. 2.1.4.2)

and neural networks (Sec. 2.1.4.3). Finally there is an overview of existing methods for constructing and selecting features for predictive compiler tuning (Sec. 2.1.4.4).

#### 2.1.4.1 1-nearest-neighbour and decision trees

Fursin et al. [27] explored 1-nearest-neighbour (1NN) and decision tree methods for reducing the execution time, code size and compilation time of programs. They created Milepost GCC which extracts features from programs for use in machine learning. The results of leave-one-out cross validation on an embedded ARC processor showed average speed-ups of 11% for 1NN and 5% for decision trees.

The study was based on 22 benchmarks from the cBench suite [1]. Training data were produced by using iterative compilation to evaluate the execution time, code size and compilation time of 1000 random configurations of 88 optimisations from GCC 4.4. Each program was flattened into a feature vector consisting of 56 features, extracted by Milepost GCC, which describe various aspects of the code such as number of basic blocks and number of conditional branches.<sup>2</sup>

The 1NN method finds the nearest training program T to the test program S based on the euclidean distance between their feature vectors (which are normalised by the number of instructions (feature 24)). Then one of two methods is used to select a configuration. In 1NN-best, the configuration which gave the best execution time for T during training is predicted for S. In 1NN-prob, a probability distribution is produced for the nearest neighbour by selecting the set of configurations that performed within 5% of the best found configuration and calculating the frequency that each flag appears in that set.

In more detail, the 1NN-prob prediction is the Maximum Likelihood Estimation (MLE) for the probability density function given in Eq. (2.1) (originally published in [27]). The probability function is calculated in the same way as the earlier Independent Identically Distributed (IID) approach in [3], the main difference is that the earlier work samples iteratively from the distribution whereas Milepost uses the MLE for its 1-shot prediction.

(2.1)

$$P(x|T^{j}) = \prod_{i=1}^{L} P(x_{i}|T^{j})$$

The Milepost study concluded that 1NN-prob performed better than 1NN-best and explains that this could be because 1NN-prob is less sensitive to flags that appear in good configurations by chance that may have a negligible impact on the training program, but a more significant effect on the test program. Chapter 4 also concludes that 1NN-prob performs better than 1NN-best and the decision tree method.

The decision tree method (referred to as the 'transductive machine learning model' in [27]) frames the tuning problem differently to 1NN. Rather than predict the best set of flags, the

$<sup>^{2}</sup>$ A full list of the Milepost features is available in [27].