## **Energy-Precision Tradeoffs in the Graphics Pipeline**

Jeff Pool

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

> Chapel Hill 2012

> > Approved by:

Anselmo Lastra

Montek Singh

Dinesh Manocha

Steve Molnar

John Poulton

### © 2012 Jeff Pool ALL RIGHTS RESERVED

#### ABSTRACT

#### JEFF POOL: Energy-Precision Tradeoffs in the Graphics Pipeline. (Under the direction of Anselmo Lastra and Montek Singh.)

The energy consumption of a graphics processing unit (GPU) is an important factor in its design, whether for a server, desktop, or mobile device. Mobile products, such as smart phones, tablets, and laptop computers, rely on batteries to function; the less the demand for power is on these batteries, the longer they will last before needing to be recharged. GPUs used in servers and desktops, while not dependent on a battery for operation, are still limited by the efficiency of power supplies and heat dissipation techniques. In this dissertation, I propose to lower the energy consumption of GPUs by reducing the precision of floating-point arithmetic in the graphics pipeline and the data sent and stored on- and off-chip.

The key idea behind this work is twofold: energy can be saved through a systematic and targeted reduction in the number of bits 1) computed and 2) communicated. Reducing the number of bits computed will necessarily reduce either the precision or range of a floating point number. I focus on saving energy by way of reducing precision, which can exploit the over-provisioning of bits in many stages of the graphics pipeline. Reducing the number of bits communicated takes several forms. First, I propose enhancements to existing compression schemes for off-chip buffers to save bandwidth. I also suggest a simple extension that exploits unused bits in reduced-precision data undergoing compression. Finally, I present techniques for saving energy in on-chip communication of reduced-precision data.

By designing and simulating variable-precision arithmetic circuits with promising energy versus precision characteristics and tradeoffs, I have developed an energy model for GPUs. Using this model and my techniques, I have shown that significant savings (up to 70% in computation in the vertex and pixel shader stages) are possible by reducing the precision of the arithmetic. Further, my compression approaches have enabled improvements of 1.26x over past work, and a general-purpose compressor design has achieved bandwidth savings of 34%, 87%, and 65% for color, depth, and geometry data, respectively, which is competitive with past work. Lastly, an initial exploration in signal gating unused lines in on-chip buses has suggested savings of 13–48% for the tested applications' traffic from a multiprocessor's register file to its L1 cache.

## ACKNOWLEDGMENTS

I have been incredibly blessed and have lots of people to thank for my having had a smooth and fruitful time learning and working at UNC. God has indeed been good to me!

Anselmo Lastra and Montek Singh, my advisors, have been indispensable. Without their encouragement, direction, and unflagging dedication to producing the best quality work, I'd be nowhere near the completion of anything worth completing. So, thanks to them for pushing me to meet deadlines, their help in sussing out the real issues and obstacles in my research, and their ruthless editing over the last five years. They have provided immeasurable insight into not only the problems encountered in my research, but also into how to be more effective at research in general.

My committee members, Dinesh Manocha, Steve Molnar, and John Poulton, also deserve a very large "thank you." Their feedback on my work was invaluable at all stages: my proposal, defense, and on up to the final version of this dissertation. My work has improved not insignificantly as a direct result of our discussions as I was forced to look at things from all sorts of new angles, not just ones with which I was familiar.

I also am grateful to NVIDIA for providing me with the phenomenal experience of having four summer internships working on a multitude of challenging problems. Seeing the amount of effort it takes to wind up with a functioning piece of silicon at the end of the process was eye-opening, and having the opportunity to be a part of this process was a true thrill. Those summers would have been far less productive and engaging without the help and guidance of my mentors there: Paul MacDougal, Lars Nyland, and Steve Molnar.

As an undergraduate at the University of South Carolina, I was very fortunate to have an advisor willing to make me figure out what I really wanted to do. Robert Pettus was that advisor, and he urged me to seek an internship with his past students Chris King and Michael Sechrest. They graciously allowed me to work for them at IDV, Inc., despite my lack of experience. My time there was fantastic, and their guidance and generosity was an integral part of my starting down the road of Computer Science.

As much as the aforementioned parties have pushed me to learn and grow academically, I am enormously grateful to my family and friends for everything else. My parents, Mike and Dale, and brother, Greg, have supported me unconditionally in everything I do. I could not have asked for anything more from them, and I rarely even had to ask at all. They, along with my friends (old, new, near, and far), were incredibly understanding and tolerant of my going into hiding for weeks and even months at a time to get things done. Everyone played their own important role in keeping me going—thank you all for the continued pushes, proofreading, kind words, and help that defies categorization!

Finally, my research was supported by the National Science Foundation under grant CCF-0702712, and equipment was provided by NSF Research Infrastructure grant number 0303590.

# TABLE OF CONTENTS

| LIST OF TABLES x                  |      |        |                                       |      |  |

|-----------------------------------|------|--------|---------------------------------------|------|--|

| LIST OF FIGURES xi                |      |        |                                       |      |  |

| LI                                | ST ( | OF AB  | BREVIATIONS                           | ciii |  |

| 1                                 | Iı   | ntrodu | $\operatorname{ction}$                | 1    |  |

|                                   | 1.1  | Motiva | $\operatorname{ation}$                | 1    |  |

|                                   | 1.2  | Backg  | round: Graphics Pipeline              | 2    |  |

|                                   | 1.3  | The U  | se of Graphics Hardware               | 3    |  |

|                                   | 1.4  | Contri | bution: Precision-Energy Tradeoff     | 4    |  |

|                                   | 1.5  | Result | ·s                                    | 5    |  |

|                                   |      | 1.5.1  | Energy Model                          | 5    |  |

|                                   |      | 1.5.2  | Energy Savings in Computation         | 6    |  |

|                                   |      | 1.5.3  | Energy Savings in Communication       | 8    |  |

|                                   | 1.6  | Outlin | e of This Thesis                      | 9    |  |

| 2 Background and Related Research |      |        | ound and Related Research             | 10   |  |

|                                   | 2.1  | Power  | and Energy                            | 10   |  |

|                                   | 2.2  | Saving | g Energy in Computation               | 13   |  |

|                                   |      | 2.2.1  | Power, Clock, and Signal Gating       | 13   |  |

|                                   |      | 2.2.2  | Dynamic Voltage and Frequency Scaling | 14   |  |

|                                   |      | 2.2.3  | Workload Reduction                    | 16   |  |

|                                   | 2.3  | Saving | g Energy in Communication             | 16   |  |

|                                   | 2.4  | Variab | De-Precision Applications             | 17   |  |

|                                   |      | 2.4.1  | Graphics                              | 17   |  |

|                                   |      | 2.4.2  | Physics                               | 21   |  |

| 3        | E   | Energy Model                                                                                                                                                  |  |  |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | 3.1 | Motivation                                                                                                                                                    |  |  |

|          | 3.2 | Related Research                                                                                                                                              |  |  |

|          | 3.3 | Approach                                                                                                                                                      |  |  |

|          |     | 3.3.1 Instruction-Level Energy Measurements                                                                                                                   |  |  |

|          |     | 3.3.2 Frame-Level Energy Prediction                                                                                                                           |  |  |

|          | 3.4 | Validation                                                                                                                                                    |  |  |

|          | 3.5 | Case Studies                                                                                                                                                  |  |  |

|          |     | 3.5.1 Architectural Study $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 38$                                                                        |  |  |

|          |     | 3.5.2 Algorithmic Study $\ldots \ldots 41$                                                     |  |  |

|          | 3.6 | Conclusions                                                                                                                                                   |  |  |

|          |     |                                                                                                                                                               |  |  |

| 4        | V   | Cariable-Precision Arithmetic Circuit Implementation                                                                                                          |  |  |

|          | 4.1 | Motivation $\ldots \ldots 45$                                             |  |  |

|          | 4.2 | Related Research                                                                                                                                              |  |  |

|          | 4.3 | Hardware Implementation                                                                                                                                       |  |  |

|          |     | 4.3.1 Modified Adder Designs                                                                                                                                  |  |  |

|          |     | 4.3.2 Modified Multiplier Designs                                                                                                                             |  |  |

|          | 4.4 | Simulation Setup                                                                                                                                              |  |  |

|          | 4.5 | Results                                                                                                                                                       |  |  |

|          |     | 4.5.1 Energy and Power Savings                                                                                                                                |  |  |

|          |     | $4.5.2  \text{Area Overheads}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                               |  |  |

|          |     | 4.5.3 Timing Overheads $\ldots \ldots \ldots$ |  |  |

|          |     | 4.5.4 Comparison with Other Techniques                                                                                                                        |  |  |

|          | 4.6 | Conclusion                                                                                                                                                    |  |  |

|          |     |                                                                                                                                                               |  |  |

| <b>5</b> | E   | nergy Savings in Computation                                                                                                                                  |  |  |

|          | 5.1 | $Motivation \dots \dots$                                |  |  |

|          | 5.2 | Related Research                                                                                                                                              |  |  |

|          | 5.3 | Reduced-Precision Shading                                                                                                                                     |  |  |

|          |     | 5.3.1 Vertex Shaders $\dots \dots \dots$                      |  |  |

|          |     | 5.3.2 Pixel Shaders $\ldots \ldots 70$                      |  |  |

|          | 5.4 | Precision Selection                                                                                                                                           |  |  |

|          |     | 5.4.1 Static Program Analysis                                                                                                                                 |  |  |

|   |              | 5.4.2   | Dynamic Programmer-Directed Selection       | 73  |

|---|--------------|---------|---------------------------------------------|-----|

|   |              | 5.4.3   | Automatic Closed-Loop Selection             | 74  |

|   |              | 5.4.4   | Local Shader Errors vs. Final Image Errors  | 77  |

|   | 5.5          | Precisi | ion to Energy Model                         | 78  |

|   |              | 5.5.1   | Addition                                    | 78  |

|   |              | 5.5.2   | Multiplication                              | 79  |

|   |              | 5.5.3   | Reciprocal/Reciprocal Square Root           | 79  |

|   |              | 5.5.4   | Dot Product                                 | 80  |

|   |              | 5.5.5   | Multiply-Add                                | 80  |

|   |              | 5.5.6   | MIN/MAX                                     | 80  |

|   |              | 5.5.7   | Summary                                     | 80  |

|   | 5.6          | Experi  | imental Setup                               | 80  |

|   |              | 5.6.1   | Programmer-Directed Precision Selection     | 81  |

|   |              | 5.6.2   | Simulator                                   | 81  |

|   |              | 5.6.3   | Data Sets                                   | 82  |

|   | 5.7          | Result  | s                                           | 86  |

|   |              | 5.7.1   | Vertex Shaders                              | 86  |

|   |              | 5.7.2   | Pixel Shaders                               | 90  |

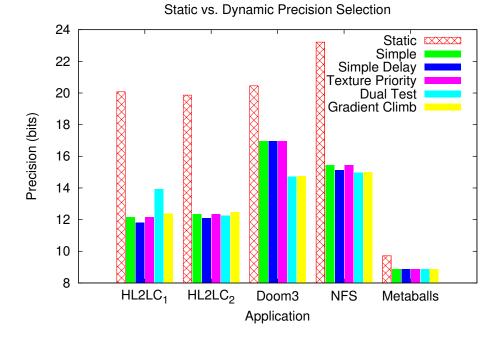

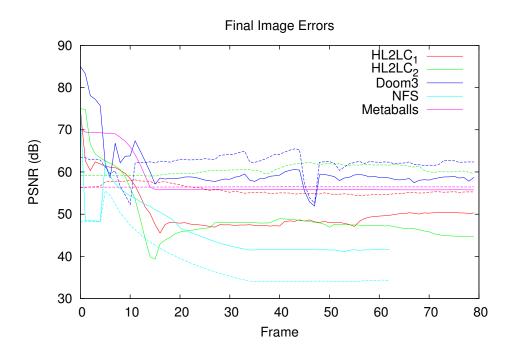

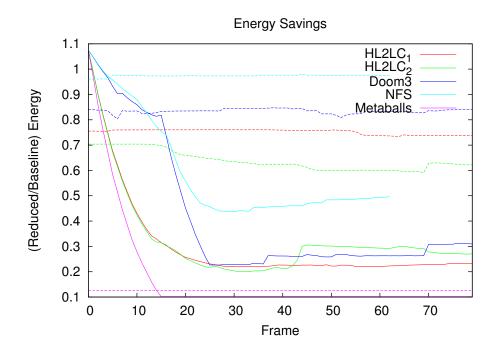

|   |              | 5.7.3   | Precision Selection                         | 90  |

|   | 5.8          | Conclu  | sion                                        | 98  |

|   |              | 5.8.1   | Future Work                                 | 99  |

| 6 | $\mathbf{E}$ | nergy   | Savings in Communication                    | 101 |

|   | 6.1          | Motiva  | ation                                       | 101 |

|   | 6.2          | Relate  | d Research                                  | 101 |

|   |              | 6.2.1   | Geometry Buffer Compression                 | 101 |

|   |              | 6.2.2   | Color/Depth Buffer Compression              | 102 |

|   | 6.3          | Impro   | ving Compression of Off-Chip Data           | 103 |

|   |              | 6.3.1   | Description of the Current State-of-the-Art | 104 |

|   |              | 6.3.2   | Proposed General-Purpose Compressor Design  | 106 |

|   |              | 6.3.3   | Proposed Techniques                         | 108 |

|   |              | 6.3.4   | Compressing Reduced-Precision Data          | 112 |

|   |              | 6.3.5   | Experimental Setup                          | 113 |

|   |              | 6.3.6   | Results and Discussion                      | 115 |

|   | 6.4          | Signal  | Gating of On-Chip Data                      | 123 |

|                 |              | 6.4.1  | Approach                             | 123 |

|-----------------|--------------|--------|--------------------------------------|-----|

|                 |              | 6.4.2  | Experimental Setup                   | 124 |

|                 |              | 6.4.3  | Results                              | 125 |

|                 |              | 6.4.4  | Other Levels of the Memory Hierarchy | 126 |

|                 | 6.5          | Conclu | sion                                 | 127 |

|                 |              | 6.5.1  | Future Work                          | 128 |

|                 |              |        |                                      |     |

| 7               | $\mathbf{S}$ | umma   | ry and Conclusion                    | 130 |

|                 | 7.1          | Summ   | ary                                  | 130 |

|                 |              | 7.1.1  | Energy Model                         | 130 |

|                 |              | 7.1.2  | Variable-Precision Hardware          | 131 |

|                 |              | 7.1.3  | Energy Savings in Computation        | 131 |

|                 |              | 7.1.4  | Energy Savings in Communication      | 132 |

|                 | 7.2          | Future | e Work                               | 132 |

|                 |              | 7.2.1  | Energy Model                         | 133 |

|                 |              | 7.2.2  | Variable-Precision Hardware          | 133 |

|                 |              | 7.2.3  | Energy Savings in Computation        | 134 |

|                 |              | 7.2.4  | Energy Savings in Communication      | 134 |

|                 |              |        |                                      |     |

| BIBLIOGRAPHY 13 |              |        |                                      | 135 |

# LIST OF TABLES

| 3.1 | Energy consumption of floating-point operations on a GPU                     | 28  |

|-----|------------------------------------------------------------------------------|-----|

| 3.2 | Energy consumption of memory operations on a GPU                             | 29  |

| 3.3 | The energy cost of fixed-function hardware.                                  | 31  |

| 4.1 | Area overheads of the modified adders                                        | 63  |

| 4.2 | Area overheads of the modified multipliers                                   | 63  |

| 4.3 | Time overheads of the modified adders                                        | 64  |

| 4.4 | Time overheads of the modified multipliers.                                  | 64  |

| 5.1 | Summary of average error per vertex at various precisions                    | 86  |

| 5.2 | Statically determined precisions                                             | 90  |

| 5.3 | Programmer-directed errors and energy savings                                | 98  |

| 5.4 | Strengths and weaknesses of precision selection techniques                   | 98  |

| 6.1 | Encoding the value '12' as a Fibonacci code                                  | 111 |

| 6.2 | Compression rates of geometric data sets                                     | 120 |

| 6.3 | Energy used in one bit line over a distance of $100\mu m. \dots \dots \dots$ | 125 |

| 6.4 | Energy used in one bit line over a distance of 1mm                           | 125 |

| 6.5 | Latch enable/disable penalties.                                              | 126 |

| 6.6 | Maximum on-chip savings for application precisions                           | 127 |

# LIST OF FIGURES

| 1.1  | A simplified view of the traditional graphics pipeline                         | 3  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | "Crysis" is an example of a program that can benefit from my techniques.       | 5  |

| 1.3  | The accuracy of my energy model for GPUs                                       | 6  |

| 1.4  | Reduced-precision pixel shading need not have perceptible loss of quality.     | 7  |

| 1.5  | Range reduction is effective when used with dynamic bucket selection           | 8  |

| 2.1  | A CMOS inverter.                                                               | 11 |

| 2.2  | A CMOS inverter (output capacitance and power drains illustrated)              | 11 |

| 2.3  | Z-fighting in "Grand Theft Auto: IV."                                          | 19 |

| 3.1  | Test applications used to validate my energy model                             | 26 |

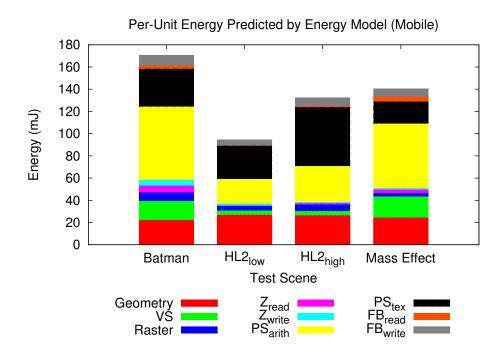

| 3.2  | Accuracy of the developed energy model                                         | 36 |

| 3.3  | Energy used per stage of the graphics pipeline                                 | 36 |

| 3.4  | Energy efficiency of tiled versus untiled renderers                            | 40 |

| 3.5  | Energy consumption of a hypothetical graphics pipeline                         | 42 |

| 3.6  | Test scenes from the bump-mapping application                                  | 43 |

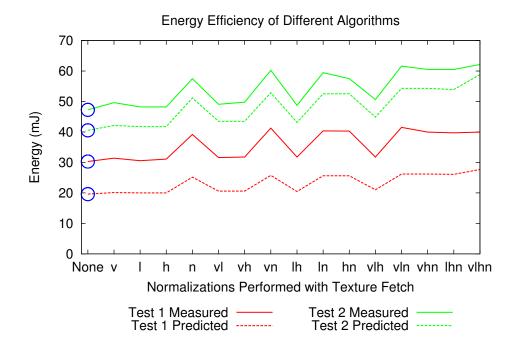

| 3.7  | Results of the algorithmic change experiment (bump-mapping). $\ldots$          | 43 |

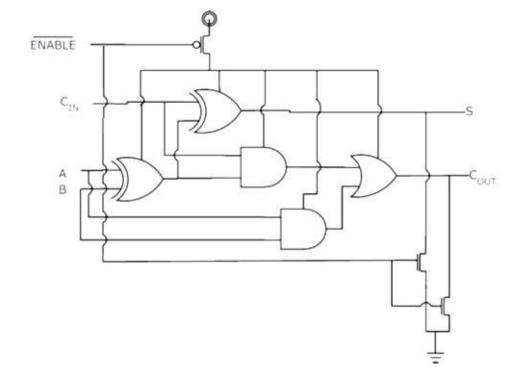

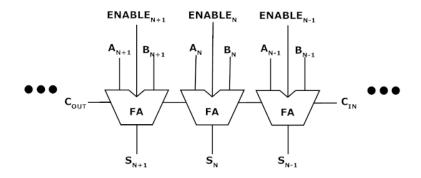

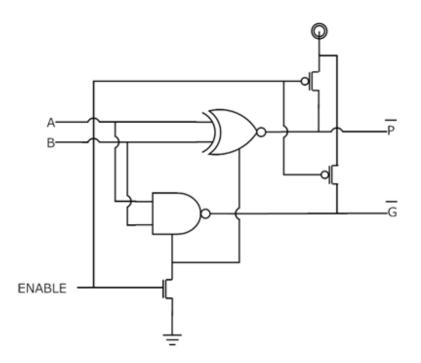

| 4.1  | A modified full adder used in power-gated variable-precision circuits.         | 49 |

| 4.2  | A section of a modified ripple carry adder                                     | 51 |

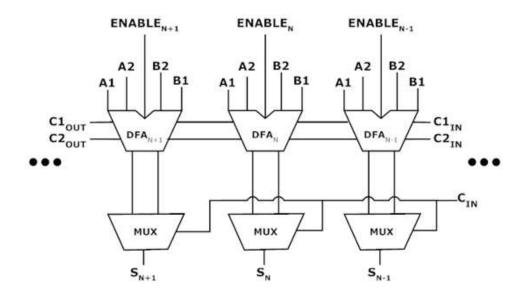

| 4.3  | A portion of the modified carry-select adder                                   | 52 |

| 4.4  | Power gating applied to the first stage of a Brent-Kung adder                  | 53 |

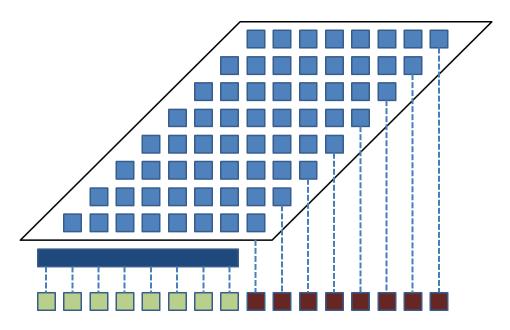

| 4.5  | An abstracted representation of an $8x8$ carry-select multiplier               | 55 |

| 4.6  | Gating only one operand, the multiplicand                                      | 55 |

| 4.7  | Gating both operands of a multiplier                                           | 56 |

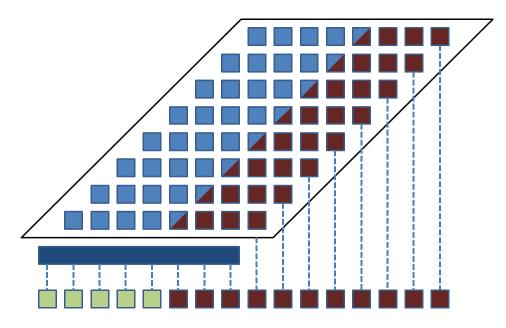

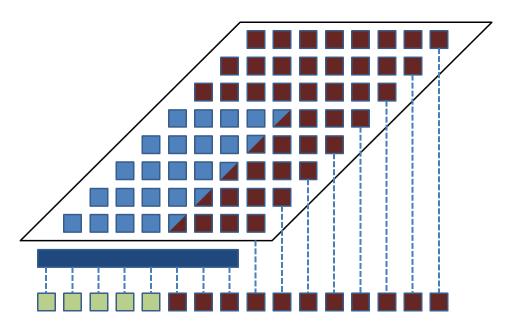

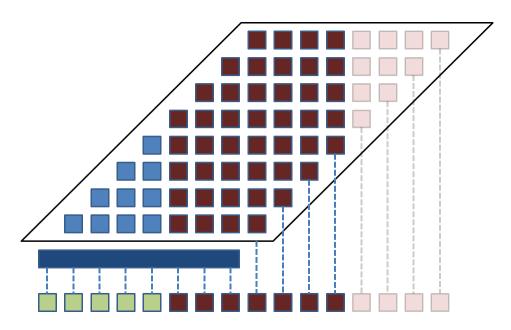

| 4.8  | Column truncation with variable-precision hardware. $\ldots$ $\ldots$ $\ldots$ | 56 |

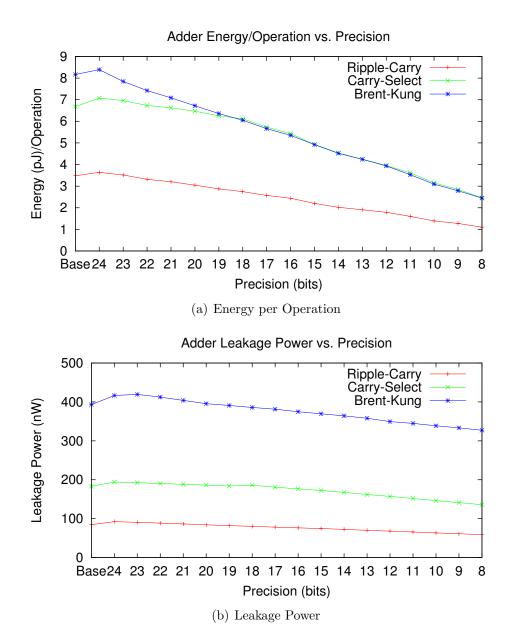

| 4.9  | Energy per operation and leakage power of the adder designs                    | 61 |

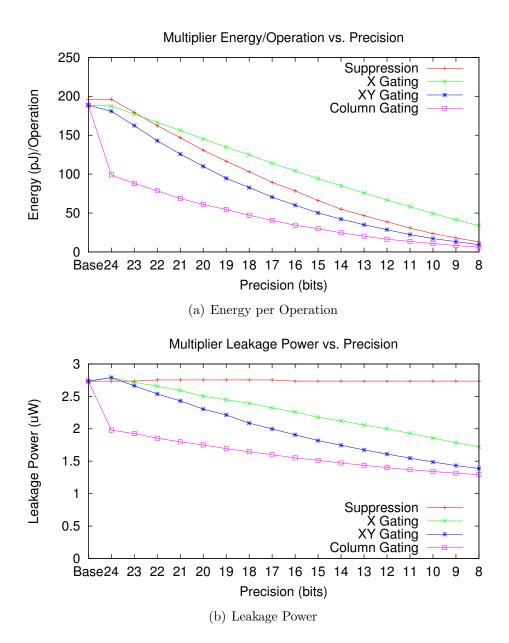

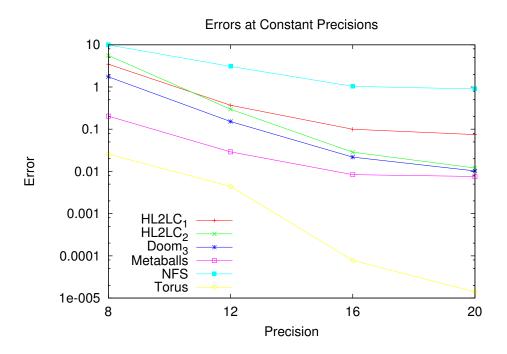

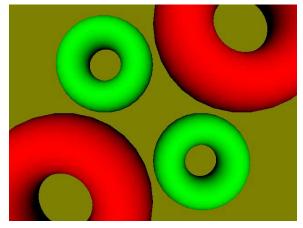

| 4.10 | Energy per operation and leakage power of the multiplier designs               | 62 |

| 5.1  | Reduced-precision vertex shading need not sacrifice image quality              | 68 |

| 5.2  | Two sources of errors in pixel shaders: arithmetic and texture coordinates.    | 71 |

| 5.3  | Pixel shaders have different errors at the same precision                      | 72 |

| 5.4  | Single frames simulated for error/energy relationships in vertex shaders.    | 83 |

|------|------------------------------------------------------------------------------|----|

| 5.5  | Developer-driven precision control test data sets                            | 84 |

| 5.6  | Data sets used to test my closed-loop precision control techniques           | 85 |

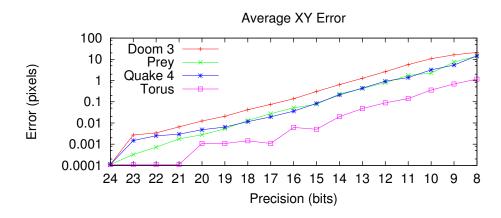

| 5.7  | Average screen-space vertex position error for several applications          | 87 |

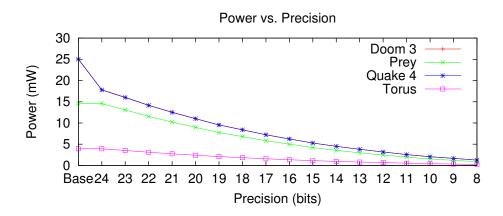

| 5.8  | Power consumption of vertex shaders as a function of precision               | 89 |

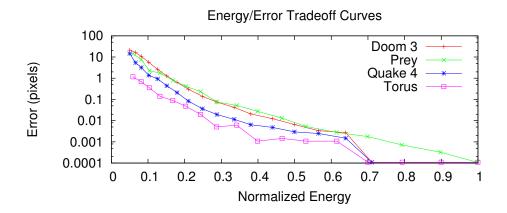

| 5.9  | Energy-error tradeoff curves for simulated vertex shaders at 640x480 pixels. | 89 |

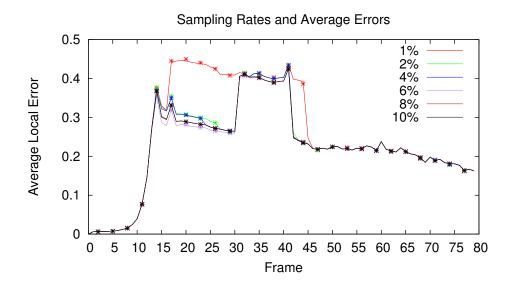

| 5.10 | Various sampling rates give different approximations of global errors.       | 91 |

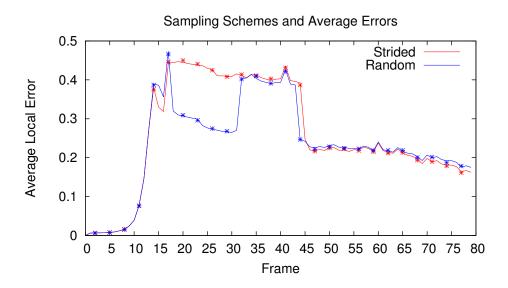

| 5.11 | Strided sampling performs as well as random sampling low sampling rates.     | 92 |

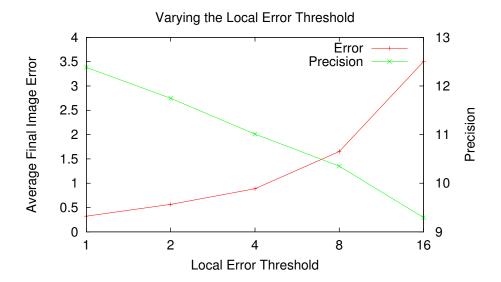

| 5.12 | Higher local error thresholds do not give significant savings. $\ldots$ .    | 92 |

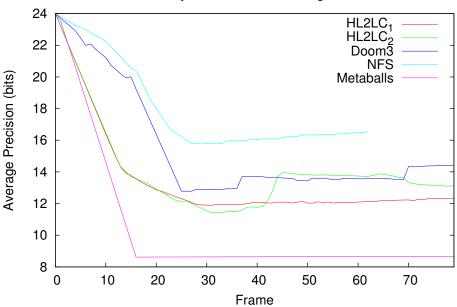

| 5.13 | As a program runs, dynamic precision selection changes its precisions        | 93 |

| 5.14 | A simple precision control scheme performs as well as a more complex one.    | 94 |

| 5.15 | Proper sampling parameters avoid noticeable errors                           | 96 |

| 5.16 | Energy savings in fragment shaders with variable-precision hardware          | 97 |

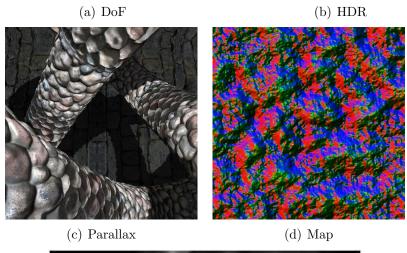

| 6.1  | Color buffers used to test my compression techniques                         | 15 |

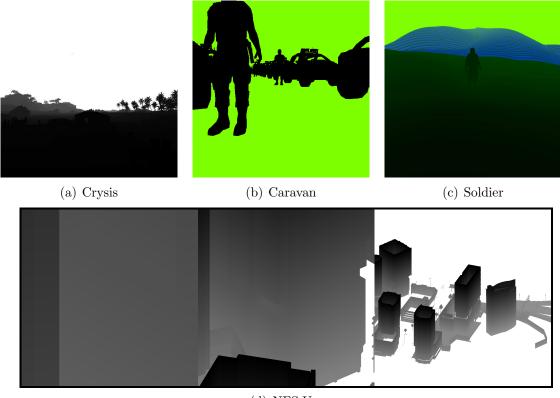

| 6.2  | Depth buffer data sets used to test my compression schemes 1                 | 16 |

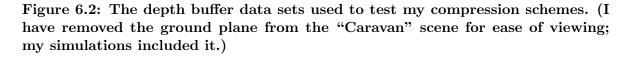

| 6.3  | Applications from which I extracted geometry buffers for compression 1       | 17 |

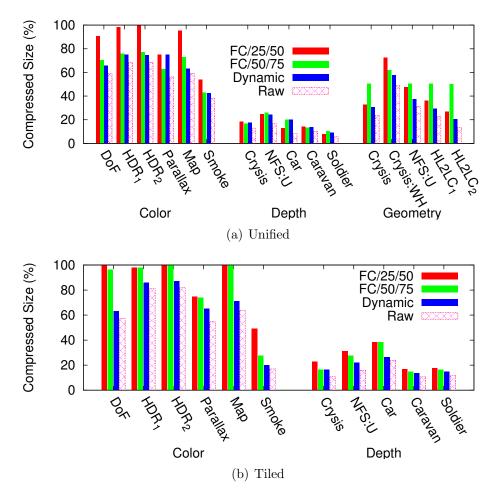

| 6.4  | Dynamic bucket selection leads to significant improvements 1                 | 18 |

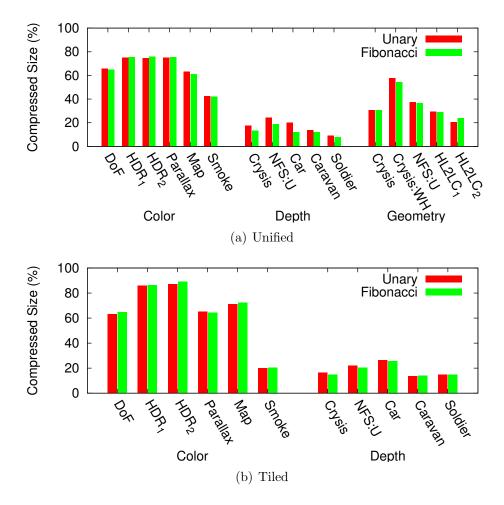

| 6.5  | Performance of a Golomb-Rice encoder with two schemes                        | 19 |

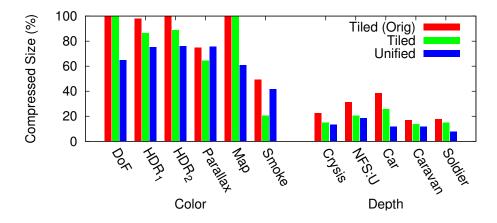

| 6.6  | State-of-the-art and proposed compressor comparison                          | 20 |

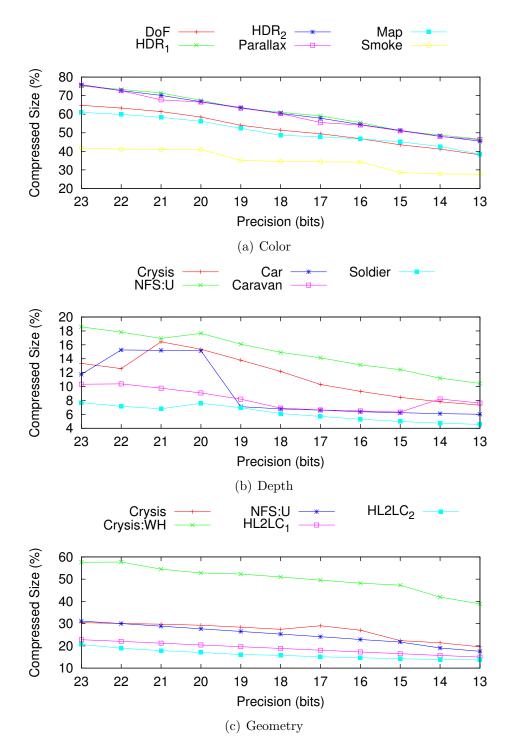

| 6.7  | Variable-precision general-purpose compression results                       | 21 |

| 6.8  | Dynamic range reduction with dynamic bucket selection 1                      | 22 |

| 6.9  | Energy savings in a local data path                                          | 26 |

# LIST OF ABBREVIATIONS

| $\mathbf{ALU}$  | arithmetic logic unit                                    |

|-----------------|----------------------------------------------------------|

| AMD             | Advanced Micro Devices                                   |

| BVH             | bounding volume hierarchy                                |

| CMOS            | complementary metal-oxide semiconductor                  |

| $\mathbf{CPU}$  | central processing unit                                  |

| CUDA            | Compute Unified Device Architecture                      |

| DCT             | discrete cosine transform                                |

| DRAM            | dynamic random-access memory                             |

| DVFS            | dynamic voltage and frequency scaling                    |

| fov             | field of view                                            |

| FPGA            | field-programmable gate array                            |

| FPS             | frames per second                                        |

| $\mathbf{FPU}$  | floating-point unit                                      |

| GPGPU           | general-purpose computation on graphics processing units |

| $\mathbf{GPS}$  | global positioning system                                |

| $\mathbf{GPU}$  | graphics processing unit                                 |

| $\mathbf{GUI}$  | graphical user interface                                 |

| HDR             | high dynamic range                                       |

| HPC             | high-performance computing                               |

| $\mathbf{LSBs}$ | least significant bits                                   |

| $\mathbf{LTF}$  | last texture fetch                                       |

| $\mathbf{PC}$   | personal computer                                        |

| PCI             | peripheral component interconnect                        |

| PSNR            | peak signal-to-noise ratio                               |

| SDK             | software development kit                                 |

| SIMD            | single-instruction multiple-data                         |

| $\mathbf{SoC}$  | system-on-a-chip                                         |

| SRAM            | static random-access memory                              |

## Chapter 1

## Introduction

## 1.1 Motivation

Graphics processing units (GPUs) in desktop computers have become very powerful in recent years, capable of creating nearly photo-realistic images by processing hundreds of millions of triangles and pixels every second. Similarly, graphics hardware has been used for general-purpose computation on graphics processing units (GPGPU) in applications to accelerate the solutions to problems such as molecular simulations, modeling large-scale crowds, and weather predictions. GPUs have been integrated into mobile devices, such as smart phones and tablets, to enrich the user experience and enable high-definition video applications. In all these domains—desktop graphics, GPGPU, and mobile devices—energy is a limiting factor in the performance of the GPU. While mobile devices are ultimately limited by the total energy available after a battery charge, desktop and server hardware also has to perform within the limits of their power supplies and heat dissipation solutions. Thus, energy consumption is directly related to performance! Decreasing the energy demands of the hardware will allow for both higher performance and longer battery lifetimes.

Nearly all computer graphics are based on the interaction of different types of light sources with different surfaces, which are well-understood natural phenomena. By simulating these interactions accurately, computers can render scenes that increasingly approach reality. As with any simulation, however, the results are approximate. Realtime graphics regularly employ many tricks to hide errors in these approximations, and even images generated by offline renderers are not exact replicas of scenes in real life. At the lowest level, the hardware used to render graphics has limited precision, and monitors can only display a finite number of different colors. Hao and Varshney first looked at variable-precision rendering for speed benefits when the vertex operations in the graphics pipeline were implemented in software and executed on the central processing unit (CPU) (Hao and Varshney, 2001). By reducing precision requirements, CPU rendering could be sped up. I take a similar approach, but my target is GPUs and my objective is saving energy consumption. My approach exposes a tradeoff between rendering precision and energy demands, which can equate to battery life improvement in mobile devices and performance increase in power-limited desktop units.

There are many approaches to reducing the energy used by hardware, from semiconductor manufacturing techniques, to reducing the voltage and/or frequency at runtime, to shutting down entire processing cores. My work is orthogonal to these techniques; the systematic reduction of precision throughout all levels of the pipeline can be used in tandem with these and other standard approaches to enable further savings. This work focuses on just the graphics pipeline, a single component of an overall system which typically has many other components using energy, such as some number of CPUs and display screens. While all these other components may use significant energy, the consumption of the GPU can often limit both the battery life and performance of the system. For example, a mobile device may deplete its battery much more quickly if the GPU is used for an extended period of time, and the performance of a GPU running a graphics or general-purpose application may be unnecessarily limited. For modern GPUs, power consumption is a significant issue that can cause performance bottlenecks and frustrate users.

## **1.2 Background: Graphics Pipeline**

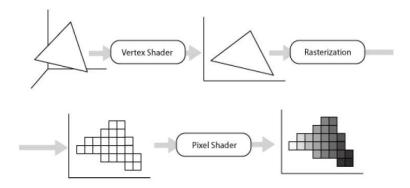

Before discussing specifics of how to save energy in the graphics pipeline, let me first briefly present a high-level view of graphics in general. Computer graphics is, at its heart, a series of similar computations performed on different data. These computations are performed in a pipeline, a simplified view of which is shown in Figure 1.1. The first stage is the transformation of input data—vertices from disparate coordinate frames into a unified "world-space" and then into "screen-space" (often combined into a single matrix multiplication). These transformed vertices are then assembled into triangles visible on the screen, possibly sharing a transformed vertex between several triangles. These triangles are sent through the rasterization stage, which generates a list of pixels that are wholly- or partially-covered by each triangle ("fragments"). These pixels are finally "shaded," or given a final color based on lighting and texture information. It is

Figure 1.1: A simplified view of the traditional graphics pipeline. Vertices enter the vertex shader, where they are transformed to screen space through a series of matrix multiplications. These transformed vertices are assembled, or "set up," into triangles. Next, these triangles are rasterized, creating lists of pixels covered by the on-screen triangles. These pixels are shaded, determining their final colors, before compositing them with geometry that has already been rendered to the final frame-buffer.

possible to discard (or "cull") data at any of these stages for reasons such as triangles existing entirely off-screen, or a set of pixels being entirely occluded behind opaque geometry that has already been drawn to the screen.

## 1.3 The Use of Graphics Hardware

The first dedicated graphics hardware was built to satisfy the demanding performance requirements of flight simulators. Strict requirements, such as real-time frame rates and low latency from user input to response on the screen, meant that general processors of the time period were not able to take on the job. The reader is referred to a survey of the topic for more information (Mueller, 1995).

In the personal computer (PC) market, these operations were, for a time, performed on a computer's CPU, the same general-purpose processor also responsible for executing all applications and operating system functions. However, as rendered scenes became increasingly complex, dedicated hardware (the GPU) that could be added to a PC was built to handle part of this load. At first, this hardware handled only rasterization and pixel operations; later it also performed vertex transformation and lighting operations. Early graphics hardware used a fixed-function implementation, which allowed for only minimal control by exposing different "modes" to the programmer, letting them change such parameters as lighting functions, blending modes, depth cueing, and backface culling.

In time, this fixed function hardware gave way to programmable hardware, letting the application programmer or artist dictate how to transform vertices and color pixels. This technology allowed for much more complex rendering techniques than were previously possible. At this point, scientists realized that these highly-parallel GPUs could also be exploited for general-purpose computations if they expressed these computations as graphics operations (early GPGPU). As programmability increased, the processing cores used for vertex transformations and pixel shading became progressively similar, eventually merging into a larger pool of "unified shaders" that can be allocated dynamically to adapt to varying workloads. This unification has allowed for new pipeline stages to emerge, such as geometry and tessellation shaders. Further, hardware vendors have made it easier to program the GPU as a general-purpose processor, allowing widespread use of the hardware for GPGPU and high-performance computing (HPC) applications in addition to the graphics workloads for which it was designed.

### **1.4 Contribution: Precision-Energy Tradeoff**

Nearly all of computer graphics is an approximation, even with all the processing power available in modern GPUs. Lighting equations are simplified to run in fractions of a second. Reflections on surfaces are, at times, not updated each frame. Research into the human visual system has led to lossy compression formats that are used to save memory and bandwidth. It is these approximations that lead to the key insight behind this thesis: reducing the precision of graphics operations need not have a negative effect on the application's usability and can save significant energy.

This tradeoff between the energy efficiency of a graphics application and the precision with which it computes the results can allow the user to choose an operating mode along the continuum connecting the two extremes. At one end, the user can enjoy a faithful reproduction of the application designer's vision at the expense of higher energy consumption. In mobile devices this will mean a shorter battery life, and in desktop and server settings, this will mean more heat that must be dissipated and higher energy costs. At the other end of the continuum is very long battery life (in a mobile device) with very noticeable errors. It is my intention that the user can choose a point in the middle that saves significant energy yet does not incur any noticeable errors.

This collection of ideas creates my thesis statement:

Figure 1.2: "Crysis," a popular video game, is an example of a class of applications that can benefit from my proposed techniques. The pictured scene's depth information was compressed by a factor of 7.7x, and the geometry data was compressed by a factor of 3.3x with my unified buffer compressor (see Chapter 6).

Reducing the work done in the modern graphics pipeline through novel communication and variable-precision computation techniques can enable a tradeoff between energy savings and image fidelity, leading to significant energy savings without perceptible loss of image quality.

## 1.5 Results

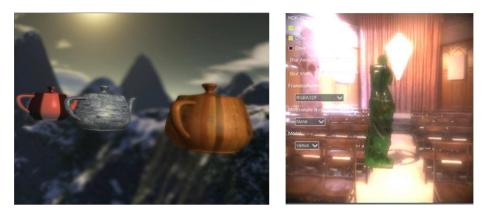

In order to defend this thesis, I approach the larger problem of energy savings in several parts, discussed independently, below. All of my proposed techniques apply to and have been tested on large-scale real-world applications, such as "Crysis" (Figure 1.2) (Crytek, 2007).

### 1.5.1 Energy Model

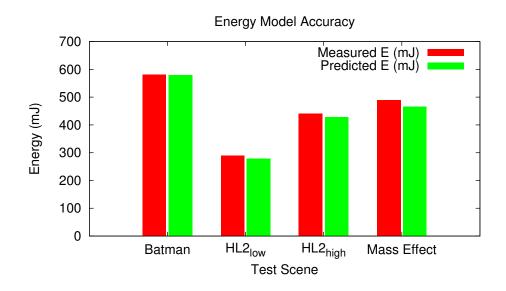

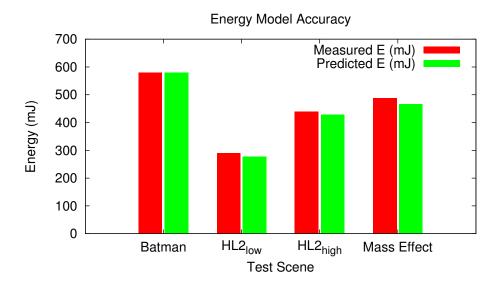

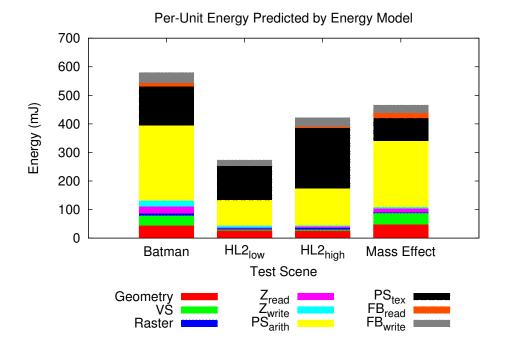

I first develop an instruction-level energy model for a GPU (Figure 1.3) by experimentally measuring the total energy used by a reference graphics card. For each operation (memory accesses, arithmetic, and fixed-function graphics operations), I measure the energy required for a directed microbenchmark. Then, I combine these individual energy per operation values to construct a model for any given workload. Accurate to within 10–15%, it allows programmers or architects to estimate the energy consumed by a particular graphics application on a particular architecture. By using the model's

Figure 1.3: The accuracy of my energy model for GPUs. The model is accurate to within 10-15% for the tested data sets, leading to very accurate predictions of energy consumption of the system as a whole, as well as different stages of the pipeline (see Chapter 3).

predictions for discrete sections of the hardware, I am able to estimate the impact of reducing the energy in a single part of the graphics pipeline on the overall energy consumption of the entire GPU. This, in turn, leads to an estimate of overall savings possible by putting the following techniques into practice.

### **1.5.2** Energy Savings in Computation

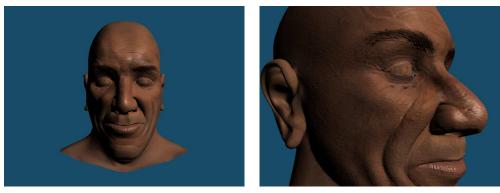

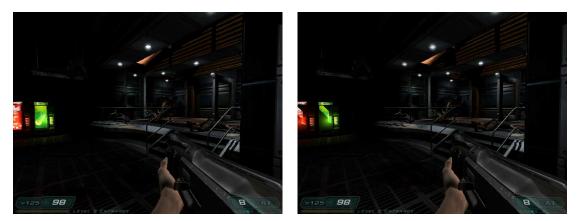

Due to the inherently approximate nature of computer graphics, the precision of floatingpoint numbers can be reduced significantly without noticeably affecting the final result, though the degree to which the precision can be reduced depends on the data used in the computations. Figure 1.4 shows an example of this: the dragon on the top was rendered with full-precision arithmetic (24 bits of precision) in the pixel shader, while the lower image used an average of only 12.5 bits of precision. Similar reductions are possible in the vertex shader stage, leading to average energy savings of 70% in the shaders' arithmetic (details in Chapter 5). I have also categorized the different types of errors that manifest themselves at different points in these shaders. Finally, I present several techniques for choosing a successful operating precision that saves energy without incurring intolerable error.

(a) Full Precision

(b) Reduced Precision

Figure 1.4: Figure 1.4(a) is the reference frame produced by full-precision computation (24 bits) throughout the pixel shader of a screen space ambient occlusion demo. Figure 1.4(b) shows the result when using an average of 12.5 bits of precision in the pixel shader. There are no perceptible differences between the two images, yet the reduced-precision image saved 71% of the energy in the pixel shader stage's arithmetic, or up to 20% of the GPU's overall energy.

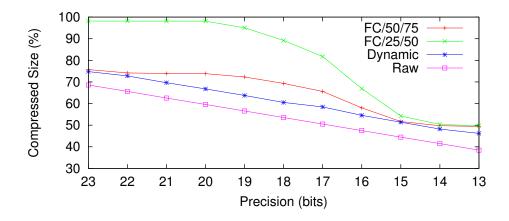

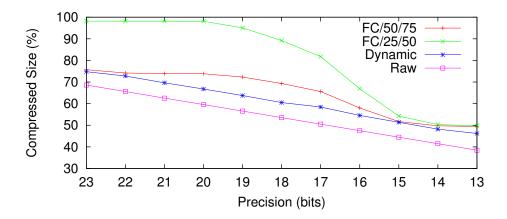

Figure 1.5: Range reduction of variable-precision prior to compression data is very effective when used with dynamic bucket selection (HDR<sub>1</sub> scene) (see Chapter 6). My approach ("Dynamic") leads to compressed data sizes closer to the ideally-compressed size ("Raw") than two different standard static bucket selections ("FC/50/75" and "FC/25/50").

#### **1.5.3** Energy Savings in Communication

I also save energy by reducing the number of bits that are necessary for communication, both on- and off-chip. First, I suggest two enhancements to a state-of-the-art compression scheme: dynamic bucket selection and using a Fibonacci encoder. These two techniques lead to an average improvement of 1.26x for an existing compressor.

Next, I describe a general-purpose compressor that is able to handle data from any source and of any layout without modification, which is a limitation of past work. It is clear that the GPU is a very general-purpose device; I feel the use of different specialized compressors for color, depth, etc., is not beneficial to the GPU's utility in a broad range of applications. Using this compressor, I estimate average bandwidth reductions of 1.5x, 7.7x, and 2.9x for color, depth, and geometry data, respectively.

Lastly in off-chip communication, I suggest a straightforward method that will take advantage of unused bits in compressing reduced-precision data, called "dynamic range reduction." Essentially, this technique treats reduced precision data in a similar manner to the computation: lower bits are simply ignored. The bandwidth savings will vary, depending on the data and precisions of the applications, but are expected to be between 5% and 20%. Figure 1.5 shows dynamic bucket selection and dynamic range reduction working in tandem to lower the bandwidth of reduced-precision data.

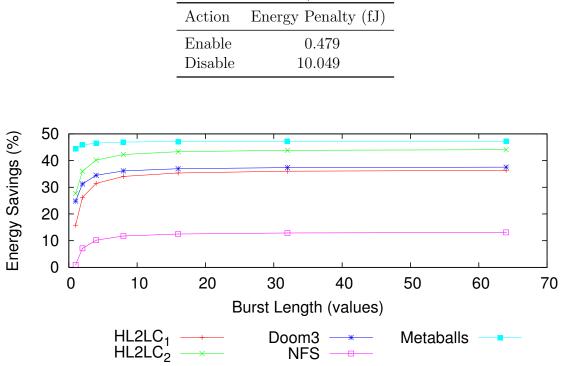

Saving energy in on-chip communication takes a different form; since compression is seldom used for sending data relatively short distances, I explore the use of signal gating on a bus from a processor's register file to its L1 cache. I have shown that the energy savings are nearly linear with bit width of the bus, so disabling 8 out of 32 bits will reduce the energy consumption by 25%. By simulating the data sent on this path for several applications, I have enabled savings between 13–48%, with an average energy savings of 36%. This technique requires only a minimal overhead, which is more than reclaimed for any "burst length" seen by the bus.

## 1.6 Outline of This Thesis

Following is the organization of this dissertation. Chapter 2 presents an overview of related work in the area of low-power graphics and hardware. Then, I present my energy model in Chapter 3. In Chapter 4, I develop and simulate several variable-precision arithmetic circuits whose energy-precision characteristics are used to estimate energy savings in later chapters. Chapters 5 and 6 detail my work in variable-precision computation and communication, respectively. Finally, Chapter 7 summarizes my findings and offers some conclusions.

## Chapter 2

## **Background and Related Research**

This chapter contains a short primer on power and energy, as well as common energysaving techniques, both in the computation and the communication of data. Also, I review existing variable-precision applications, specifically, work in graphics and physics simulations.

## 2.1 Power and Energy

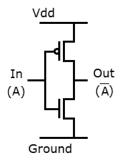

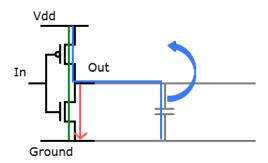

As discussed in Chapter 1, reducing the power and energy consumption of graphics hardware is an important task for modern architects, hardware designers, and software developers. The first step in reducing power is understanding exactly how the power is consumed on a chip. Let us start at a very low level: a simple complementary metaloxide semiconductor (CMOS) inverter, pictured in Figure 2.1. The function of the inverter is to transform a high signal (logical '1') on the input side to a low signal (logical '0') on the output side, or a low input signal to a high output signal, thereby inverting the input. This is accomplished by a single pair of NMOS and PMOS transistors that conduct in opposing situations. When the input is low, the PMOS transistor (on top in the figure) conducts, allowing the output to be pulled high. Similarly, the NMOS pulls the output low when the input is high. This seemingly simple idea can be extended to create any logical gate necessary, such as NAND and NOR gates. These gates, arranged in a particular fashion, can compose a basic circuit: an integer adder, for example. These basic circuits, in turn, can be combined to create more complex circuits and, eventually, a processing unit.

Stepping back to the inverter, I will discuss how it consumes power to perform its simple task. First, we should look at the inverter in the context of a larger circuit: the

Figure 2.1: A CMOS inverter.

Figure 2.2: A CMOS inverter with output capacitance and main sources of power use illustrated: dynamic power (blue), short circuit power (green), and leakage power (red).

inverter's input and output will be connected to other gates. The inverter's output, in particular, is said to "drive" the next element (just as the inverter itself is being driven by whatever came before it). A capacitive load is seen by this output, the magnitude of which is determined in part by the size of the driven element and the length of connecting wire. This capacitance is illustrated in Figure 2.2.

There are three main categories of power consumed during an inverter's operation. The first, *dynamic* (or *switching*) *power*, is highly dependent on the output capacitance. It is this capacitance that causes the transistor to have to work to change the output from one signal to another; the capacitance stores charge, and it must be either charged or discharged for the signal to change. The second, *short circuit power*, is due to the inability of transistors to switch on and off instantaneously. During a transition, there will be a brief moment when both the PMOS and NMOS transistors are conducting. At this point, current will have a direct path from the power supply to ground, creating a short circuit which consumes power without doing any useful work. Finally, there is *leakage power*, which is always present and not dependent on the activity of the gate. The transistors that make up the circuit are not perfect switches; some charge "leaks" through them even when they are disabled. These three sources of power consumption are illustrated in Figure 2.2.

Dynamic and leakage power are the two dominant consumers of power, so let us discuss them in more detail. Switching power is dependent on the capacitance: the larger the output capacitance, the more the gates have to work to change the output charge. Likewise, the higher the source voltage, the more the output has to change; this relationship is quadratic. Finally, the frequency with which the output changes directly affects the power consumed. This is determined by two quantities: the frequency at which the circuit is operating (or clock speed, f) and the *activity factor* ( $\alpha$ ) of the individual gates. The activity factor is an estimate of how often a given gate undergoes a transition and is a number between '0' (never) and '1' (every cycle). These various quantities are shown together in Equation 2.1.

$$P_{switching} = \frac{1}{2}CV^2 f\alpha \tag{2.1}$$

Leakage power does not depend on the frequency or activity factor of a circuit or gate. Instead, it is determined by the source voltage and the area of the gates. (This is a very high-level treatment that captures the most important aspects of leakage current; the reader is referred to a more in-depth analysis for further details (Yeap, 2002; Mukhopadhyay et al., 2003; Butzen et al., 2007; Rastogi et al., 2008).) The leakage power consumed by a circuit component is shown in Equation 2.2.

$$P_{leakage} \propto V * Area \tag{2.2}$$

Instantaneous power, in units of watts (W), is an important factor in the heat produced by high-performance hardware, so the effectiveness of the cooling (passive, fan, or even water-based) used on a circuit can often dictate how much power the circuit can handle. Further, the power supplies driving computational hardware have bounds on the amount of power they can deliver. These limits have recently become a bottleneck in GPUs; if graphics hardware used less power, it could run at a higher frequency. So, power efficiency is a concern to today's GPU designers.

Like power, energy is a consideration that designers must keep in mind. Energy, with units of joules (J) or kilowatt-hours (kWh), is instantaneous power over a period of time, shown in Equation 2.3. While energy consumption can be important for desktop

and server hardware, as energy cost directly impacts the total cost of operation, energy efficiency is even more crucial for mobile hardware. Batteries are limited by the amount of energy they can store; when that energy is depleted, the device powered by that battery is useless until the battery is replaced or recharged. While batteries do have limits on the instantaneous power they can deliver, the lifetime of the battery is often the more pressing concern to the consumer.

$$E = \int_0^T P(t) dt \tag{2.3}$$

## 2.2 Saving Energy in Computation

Saving energy in the computational phase of a program can come at all levels of the device: algorithmic, architectural, circuit, and even changes at the transistor level affect energy consumption. Though surveys of existing techniques exist (Benini et al., 2001; Hung et al., 2009), I will briefly mention and discuss common energy-saving approaches detailed in these surveys and refer the reader to them for more details.

### 2.2.1 Power, Clock, and Signal Gating

The most straightforward way to save energy is to attack the power term in Equation 2.3. In turn, there are two quantities in Equations 2.1 and 2.2 that can be changed at runtime: the voltage and frequency of the circuit. (The hardware's area, capacitance, and switching activity are tied to circuit- and architectural-level decisions.) Shutting off either the power or the clock that drives the circuitry will stop the circuitry from performing useful work but can drastically reduce the power, and therefore energy, consumed. Both techniques have their own benefits and caveats, however.

Power gating refers to completely turning off the supply voltage to some area of circuitry. Clearly, a circuit with no voltage will not function, so it is used on circuitry which is not currently needed, such as a floating-point unit (FPU) during an integer operation. Since a circuit's voltage plays a role in both its dynamic *and* its leakage power, power gating will reduce both of these quantities. Power gating can also apply to many levels of the hardware, from entire cores and partitions down to computational paths for individual bits. However, completely turning the voltage to a circuit on and off is not instantaneous—the hardware may take some time after it is re-enabled before it is usable again. Scheduling power events is a complicated problem, both for making sure the hardware is available for a task (Wang et al., 2010), as well as reducing noise in the power lines driving the hardware (Jiang and Marek-Sadowska, 2008).

Clock gating does not affect the supply voltage; rather, it eliminates switching activity in a component by changing the effective frequency to zero. As this frequency term is only found in the equation for dynamic power, clock gating does not affect leakage power; current still leaks through the transistors in the path to ground. However, re-enabling a clock-gated circuit is much faster than re-enabling a power-gated circuit, and there are no issues with noise on the power and ground rails. As with power gating, clock gating can be applied to many levels of the hardware's design.

One last type of gating does not change either the voltage or the frequency, but focuses on the activity factor ( $\alpha$ ) in Equation 2.1: signal gating. If it is known beforehand that the result of an operation (or sequence of operations) will not be used, then the inputs to the hardware can be "frozen," or held at a constant value. This value can be a logical '1' or '0' (which is simple in implementation, but can require a small amount of power to force the inputs to a particular value) or it can take the existing value as the constant value (which can be slightly more complicated in implementation, but requires no power to change the values). Signal gating can be applied to entire registers, or even just to individual computational paths (Huang and Ercegovac, 2001).

In Chapter 4, I use very fine-grained power gating to shut down sections of arithmetic circuits for energy savings, and I use signal gating in Chapter 6 to save energy in on-chip communication of reduced-precision data.

### 2.2.2 Dynamic Voltage and Frequency Scaling

While simply gating the voltage or clock signal to a circuit can save significant energy, it can sometimes be too heavy-handed; reducing the voltage and clock speed by some factor can often save energy while still allowing the circuitry to function as intended. Changing voltage and frequency at runtime, or dynamic voltage and frequency scaling (DVFS) (Benini et al., 2001), allows for a tradeoff between power or energy and performance. A simple example showing the effect of DVFS on a circuit's dynamic power should make this tradeoff clear.

Given a simple circuit that performs work at a voltage of 2V and a frequency of 100Hz, and expressing switching activity ( $\alpha$ ) and capacitance (C) (seen in Equation 2.1) as a single constant, k, the switching power is given in Equation 2.4. Equation 2.5 shows the power consumed by the same circuitry running at half the voltage and

half the frequency of the original. (Voltage and frequency do not necessarily scale with the same ratio; this is a contrived example!) Finally, Equation 2.6 shows the ratio of dynamic power consumed by the circuit operating at original and scaled voltage and frequencies; the circuit under DVFS uses only one-eighth the power.

100 1

= 50 \* k

$$P_{base} = k * 2^2 * 100 \tag{2.4}$$

$$= 400 * k$$

$$P_{scaled} = k * 1^2 * 50 \tag{2.5}$$

$$P_{scaled} = \frac{1}{8} P_{base} \tag{2.6}$$

There is one final step to find the energy savings. Since the frequency of the circuit was halved, the time spent in the computation was doubled, which, as we saw in Equation 2.3, will play a role in the energy. The energy consumed by the circuit (Equation 2.7) is reduced by using DVFS (Equation 2.8) to only one fourth of the original energy (Equation 2.9):

$$E_{base} = \int_{0}^{T} P_{base}\left(t\right) dt \tag{2.7}$$

$$E_{scaled} = \int_{0}^{2T} P_{scaled}(t) dt \qquad (2.8)$$

$$- \frac{1}{2} \int_{0}^{2T} P_{scaled}(t) dt$$

$$= \frac{1}{4} \int_{0}^{T} P_{base}(t) dt$$

$$= \frac{1}{4} \int_{0}^{T} P_{base}(t) dt$$

$$E_{scaled} = \frac{1}{4} E_{base}$$

(2.9)

The performance and power tradeoff should be clear. However, in some circumstances, there need not be a performance hit. With two similar units (be they simple adders or entire processors) and a sufficiently parallelizable workload, the same work can be done in the same time with much less energy by using both units at the same time. This is the approach taken by NVIDIA when motivating the use of multiple CPUs in their Tegra 3 system-on-a-chip (SoC) (NVIDIA Corporation, 2012).

### 2.2.3 Workload Reduction

A slightly different approach to saving energy is to simply do less work. If the work that is not performed was not necessary, or at least not noticeably important, then the larger application can save energy by not performing it. For instance, Lafruit et al. present a method for estimating the time necessary to render a frame based on input statistics and render states and reducing the workload gracefully if this time is too large (Lafruit et al., 2000). By reducing the render buffer (virtual screen) size, texture resolutions, and mesh resolutions, the authors have shown that rendering time can be (approximately) bounded with a "full" result, rather than truncating the rendering process in the middle of a frame. This allows for a quality/performance tradeoff, starting with a full-quality input scene and scaling down as desired.

Similarly, variable-precision techniques seek to do less work and arrive at approximate answers to computations, which, in many applications, are close enough to the correct answer. This is a broad topic, and I discuss it more fully in Section 2.4.

## 2.3 Saving Energy in Communication

Communication, not just computation, of data can also be a target for significant energy savings, and there have been studies detailing the power consumption in communication hardware (Lahiri and Raghunathan, 2004). Long-distance data communication consumes roughly an order of magnitude more energy than the computation performed on that data (Keckler et al., 2011), and this disparity is expected to increase in the future as transistors continue to shrink. There are many ways of approaching reducing the energy consumption of communication, which can target the amount of data, encoding of data, or even how the data is sent over long wires (Oh et al., 2006). Caches can reduce the amount of data that must be sent over a long distance, effectively increasing the bandwidth and energy efficiency of the hardware, but can hurt performance when handling poorly-behaved data access patterns (Bahar et al., 1998). Choosing different encodings for the data sent across a bus can reduce the transitions seen on long wires (the  $\alpha$  term in Equation 2.1) (Zhao et al., 2007; Lindkvist and Lofvenberg, 2005).

I look closely at compression of memory traffic on graphics hardware (Ström et al., 2008; Rasmusson et al., 2009). Compression can reduce redundancy within data, expressing the information contained within it more compactly and making it more efficient to send across wires. More information can be found in Chapter 6.

### 2.4 Variable-Precision Applications

Reducing the precision of the variables used for computation in an application can be seen as a reduction in workload. The results may no longer be as exact, but the computational effort can be greatly lessened. This type of tradeoff has been explored in many domains, which I discuss briefly below.

### 2.4.1 Graphics

#### Variable-Precision Rendering

Hao and Varshney looked in-depth at variable-precision rendering in the geometry transform and lighting stage to accelerate 3D graphics (Hao and Varshney, 2001). It is important to note that their work focused on CPU-side rendering, so they exploited the use of MMX (a single-instruction multiple-data (SIMD) instruction set designed by Intel) instructions and operated on integer and fixed-point representations. Further, they applied their work to the fixed-function pipeline, which has fallen to the wayside with the introduction of programmable shading. However, their work provides a foundation upon which to build a modern exploration. First, they present a breakdown of sources of error in data sets and computations for inputs with n bits, listing worst-case errors.

- 1. Representation error. These are statistical and observational uncertainties. At worst, the representation error is one half bit:  $\epsilon^{rep} \leq \frac{1}{2}$ .

- 2. Addition error. Propagation error leads to at most one bit of lost accuracy for each addition.

- 3. Multiplication error. Using 2n bits to store the intermediate result, the worst case error occurs when both operands are close to  $2^{n-1}$  and the representation error is  $\frac{1}{2}$ : one bit of accuracy can be lost during each multiplication.

- 4. Division error. Assuming the division is in the transformation from homogeneous coordinates to 3D image-space coordinates, the loss of accuracy is:

$$\left\lceil log_2(1 + \frac{distance of farplane from eye}{distance of scene vertex to eye}) \right\rceil$$

Finding the total error incurred is a linear combination of errors for each operation. Working backwards from, for example, 10 bits of precision in x and y for a 1024x1024 rendering window, one can find the necessary bits at the input to guarantee 10 output bits of precision. Sub-pixel accuracy is computed by artificially enlarging the window size.

Small objects in the distance do not need as much precision as a big object in the foreground. They propose an octree-based bounding volume hierarchy (BVH) to keep track of the position of rendered items in space to take advantage of this technique. If the near and far vertices in a cell need the same number of bits to be represented accurately, then this number can be used for every vertex in the cell; otherwise, it must be split.

Spatial coherence can be exploited in 3D models by encoding neighboring vertex positions as offsets from previous positions. Temporal coherence can be similarly exploited by expressing a transformed vertex as the sum of the originally transformed vertex and the original vertex transformed by the difference between the previous and current transformation matrices.

There are further sources of error in lighting operations that were not present in vertex transformations.

- 1. Operands with different accuracy. When two operands have different precisions, results always take on the precision of the lesser-precise operand.

- 2. Dot products (of unit vectors). For dot products of two three-component vectors, the results will lose one to two bits of precision.

- 3. Square roots. When implemented with a lookup table, the result will have nearly the same precision as the input (as long as the input is bigger than  $2^{2n-2}$ ).

- 4. Exponentiation. A step in the calculation of the specular component which will incur a loss of precision of 6 bits.

Lighting computations can be treated just like spatially-coherent geometry, calculating one vertex's lighting as an offset from a neighboring vertex's result.

#### Minimum Triangle Separation

A common problem that has plagued graphics applications for years is called z-fighting, and it occurs when two triangles are (nearly) co-planar. The limited precision of the

Figure 2.3: Z-fighting in the shoreline of a frame from "Grand Theft Auto: IV."

depth buffer cannot capture the correct rendering order across the entirety of the triangles. So, one triangle is rendered in front of the other triangle in some pixels, with the opposite ordering chosen for other pixels. The effect is exacerbated as the viewpoint moves, since the ordering is not spatially coherent. An example of z-fighting in the video game "Grand Theft Auto: IV" can be seen in Figure 2.3 (Rockstar Games, 2008). Apparent even when rendering a scene at full-precision, this problem can become worse as geometric precision is reduced.

Akeley and Su analyze the minimum triangle separation in object-space for correct occlusion given a viewing environment: camera position, field of view (fov), and window coordinate precision (Akeley and Su, 2006). By beginning with a minimum triangle separation, instead, an artist can calculate a final minimum necessary buffer and geometric transform precision to use when reducing the precision of an application that utilizes their 3D models.

Their method works as follows: an uncertainty cuboid is formed for each 3D location in window coordinates, the depth of which is the numeric distance between the representable z-buffer values nearest its location, and whose width and height (identical for all cuboids in a window) are determined by b, the precision of the window coordinates. Given a traditional z-buffer, cuboids near the near plane will be shallow; those near the far plane will be deep. Conversion to eye coordinates is done by inverting the projection and viewport transformations to reverse map the cuboids, which become frusta. Parallel triangles may swap order (fight) if and only if any of their uncertainty frusta overlap. The minimum distance,  $S_{min}$ , is the length of the frustum's longest diagonal.

A frustum in a screen corner will be highly sheared, meaning its diagonal will be longer than it would be at the center of the screen. This factor is labelled  $K_{fov}$  the ratio of corner-screen to center-screen diagonal length for uncertainty frusta on a given  $z_{eye}$  plane. The minimum separation depends on all these factors—simulations show that discounting any one of them will lead to an under-prediction and possible punch-through.

Finite-precision projection, viewport, and rasterization (mapping) arithmetic can further increase the minimum precision. The authors modeled the error in these operations by performing them in double precision. The contribution of this mapping error to  $S_{min}$  is minor due to the spatial-related error dominating the depth-related error; 10.8 fixed-point spatial precision used in the representation of window coordinates  $x_{win}$ and  $y_{win}$  is far below that of floating-point.

#### **Texture Mapping**

Textures, or pre-computed images, are often applied to triangles to add detail that is not captured by lighting equations alone. (While texture mapping can be performed at both the vertex and pixel shader stages, I will discuss texturing at the pixel level in particular.) These textures can represent color, normal, reflectance, and many other types of information. Special fixed-function hardware is used to determine what texture element, or *texel*, is to be applied to a particular pixel based on that pixel's texture coordinates, effectively an address into the texture memory. This address, though, is often a floating-point number that selects an element a fraction of the way through the data. If this address is greater than '1,' either the address is clamped or the texture is treated like a periodic signal.

Since floating-point addresses do not often land precisely on a single texel and a single pixel may cover several texels, the texture mapping hardware must decide what value to return. The simplest approach the hardware can take is to choose the nearest texel; this is seldom used in practice because of its poor quality and aliasing artifacts. Instead, filtering (i.e. interpolation) is often performed. By examining the four nearest texels to the pixel's center and performing a weighted average on their values, the texture hardware can enabled smoother gradients across texel boundaries. This is referred to as bilinear filtering. Trilinear filtering, on the other hand, performs bilinear filtering on two mipmap levels (Williams, 1983) and linearly interpolates between these two

values to find a single result. This inclusion of mipmapping leads to gentle transitions when a texture is applied to triangles of varying sizes. Finally, anisotropic filtering is the highest-quality filtering commonly used; it addresses cases in which a texture is applied to a triangle at a high relative angle to the camera, meaning it is much larger in one dimension than the other (*not* isotropic).

Chittamuru et al. present a method of trading off energy for quality in this texture mapping hardware (Chittamuru et al., 2003). They discuss two techniques for skipping certain MAC operations in texture filtering: weight-based and intensity-based techniques. If texel weights in the bilinearly or trilinearly sampled texels are small enough, they can be ignored. Similarly, if two neighboring texels are roughly equal, the two MAC operations can be transformed into an addition and a multiplication. This technique offers a tradeoff: comparing more bits of neighboring texels leads to more accurate results, and comparing fewer bits will lead to fewer MAC operations. The authors also present an architecture for efficiently evaluating texel and weight similarities, so that power spent in comparisons will not outweigh the savings realized. In total, the authors save 30–50% of the power and speculated that up to 80% could be saved with the use of multiple voltage supplies.

### 2.4.2 Physics

Yeh et al. explored error tolerance in physically based animation (Yeh et al., 2006; Yeh et al., 2009). Physics simulations are usually performed in several steps: broadphase and narrow-phase collision detection, island creation (grouping colliding objects together), and the simulation step (applying forces to simulated bodies). By injecting bounded random errors into these different phases, the authors determined acceptable limits. From a quantitative analysis of the errors, they choose the "knee" at which the system suffers a catastrophic failure as the last acceptable error threshold. Several tests confirmed this choice: visual inspection, comparison with a previous contrived system, comparison of the magnitude of observed errors to that seen in constraint reordering, and examining the effect of different timesteps on the errors. They observe that the overall energy in the system is a good indicator of whether or not a given simulation is well-behaved; if the total energy does not remain constant, then the simulation will likely explode into very implausible behavior. Finally, the authors present four case studies in trading off accuracy and performance.

1. Simulation timestep. It was shown that a frame rate of at least 34 frames per

second (FPS) is necessary to keep the simulation stable.

- 2. Iteration count. 11-30 solver iterations are result in a stable simulation at 60 FPS, but some iteration counts over 30 are *not* stable for only 30 FPS. So, iteration count can't be traded for frame rate.

- 3. Fast estimation with error control. Previously presented by Yeh (Yeh et al., 2006), this method creates a precise thread and an estimation thread for a given computation. The estimation thread completes first, allowing other components (rendering, AI) to begin working with this estimated result. The precise results are fed to the input of both threads for the next frame. Reducing the iteration count of the estimation thread led to stable simulations for iterations counts as low as 1, due to the precise input used for each frame.

- 4. Precision reduction. The precision of the computational steps is reduced, rather than range, because exponents are less tolerant of bit width reduction and the possible savings are lower. Precision thresholds derived numerically are much higher than thresholds arrived at through perceptual metrics. For the authors' tests, around 7 mantissa bits were the most ever needed by a phase of the simulation to remain stable.

## Chapter 3

## Energy Model

### 3.1 Motivation

Hardware designers and, recently, software designers, have gone to great lengths to reduce the power consumption of their hardware and applications. Hardware designers seek to minimize heat, keeping power and cooling requirements low in desktop units. In mobile GPUs, they go to great lengths to maximize battery life to make their solutions more attractive to buyers. Likewise, software designers know that their applications will likely see more use if they are not excessively power hungry. It is for this reason that mobile platforms, such as Apple's iOS, include tools for monitoring the power consumption of applications under development (Apple Inc., 2010).

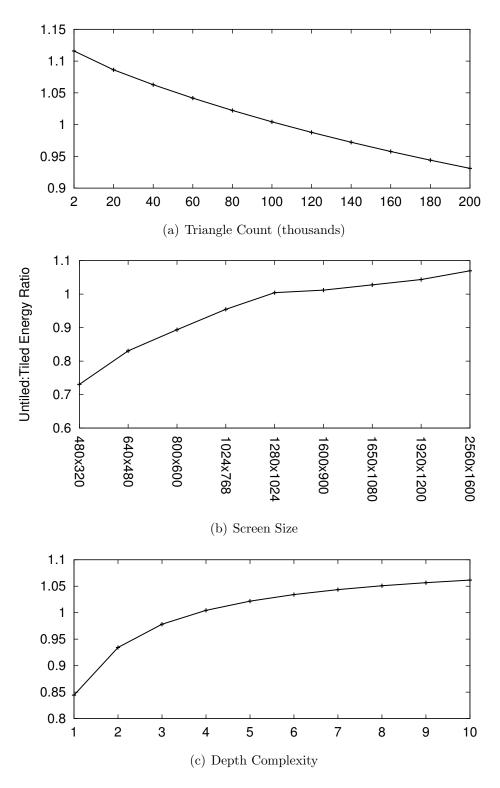

A validated energy model for GPUs would be helpful in predicting the impact of modifying applications on energy efficiency. For example, one could determine how the mix of operations performed in the hardware will change when using a different architecture (such as a tiled rendering scheme, similar to the popular POWERVR graphics solutions (Imagination Technologies Ltd., 2010)). Alternatively, one could look at the energy efficiency of different algorithms used for a graphical technique called bump-mapping (NVIDIA Corporation, 2004). With the energy model I introduce in this chapter, I am able to examine both these facets of hardware and software design.

### 3.2 Related Research

A commonly used solution for modeling the power consumption of computer hardware at the architectural level is Wattch (Brooks et al., 2000), which uses cycle-level simulation and parameterizable hardware power models to estimate power usage of different CPU architectures and compiler techniques to within around 10% of the actual reported value in most cases. Since then, there have been studies on the modeling of a single-core system at the architectural level, so that weeks of simulation are not necessary, with good results (Chen et al., 2001; Varma et al., 2008).

For multicore systems, perhaps the most promising work is an approach that maps the power consumption of the various cores to the power consumption on an analogous network model (Eisley et al., 2006). This model was simulated with LUNA, a highlevel network power analysis tool (Eisley and Peh, 2004), to give a reported 9% error in most cases. There have also been tools developed explicitly to measure the energy in high-performance systems (Ge et al., 2010), but they have not been adapted or used for modeling or prediction.

Power modeling for the GPU, in particular, is far less advanced. There have been multiple works published that advocate the use of GPUs for general-purpose computing from an energy standpoint, observing that though they require more power, their higher speeds reduce overall energy (Rofouei et al., 2008; Huang et al., 2009). A framework called PowerRed, which was designed for exploring power efficiency in GPUs, seems very promising, but it has not been validated or run on real-world graphics applications, only short tests (Ramani et al., 2007). QSilver, a GPU simulator with power analysis capabilities, can be a very powerful tool, but requires time to build a model and simulate existing application traces (Sheaffer et al., 2004). This tool remains, to my knowledge, unvalidated.

Recently, there have been several groups looking at statistical approaches for power and performance modeling of GPUs. Nagasaka et al. examine two NVIDIA graphics cards and use benchmarks in the Compute Unified Device Architecture (CUDA) software development kit (SDK) to develop a linear regression fit for a number of exposed performance counters (Nagasaka et al., 2010). Their model achieves an average of 4.7% relative error for a set of GPGPU kernels, but does not include many graphicsspecific operations, such as rasterization and texture fetches. Zhang et al. also looked at a statistical approach for finding performance and power characteristics of a GPU, though for a specific architecture made by Advanced Micro Devices (AMD), and discussed the relative importance and interdependence of various metrics (Zhang et al., 2011). They find that, for this particular architecture, making full use of special hardware for writing to the GPU's dynamic random-access memory (DRAM) is essential to achieving full performance. Further, they show that significant power can be saved by slightly under-utilizing the hardware, though the energy consumption increases due to the performance loss.

Hong and Kim take a different approach (very similar to mine), in which they measure the energy of different operations directly via micro-benchmarks and compute the cross-product of energy costs and operation frequencies to find the overall power consumed (Hong and Kim, 2010). However, like the above statistical models, they focus on GPGPU applications and do not integrate operations unique to graphics workloads.

## 3.3 Approach

Developing an energy model for graphics applications on a GPU is challenging because (i) many types of operations, both arithmetic and memory accesses, occur in a typical graphics pipeline; and (ii) while some parts of the pipeline are fixed-function, other parts are user-programmable. The mix of arithmetic versus memory accesses and fixed-function versus programmable hardware make it difficult to accurately predict what processing will occur for any given frame of an application. My methodology consists of carefully applying targeted tests to find the energy of arithmetic and memory operations, and that of the fixed-function and programmable stages. In particular, I use NVIDIA's CUDA—a framework for running general-purpose programs on GPUs—to determine the energy usage in the programmable stages. For the fixed-function units, I develop targeted graphics applications that stress only the unit in question, isolating its energy usage. For each of these tests, I measure the actual energy consumed by the GPU by measuring the current drawn by the hardware. I then use these measurements to develop my energy model.