## CASE STUDIES ON OPTIMIZING ALGORITHMS FOR GPU ARCHITECTURES

**Shawn Daniel Brown**

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the College of Arts & Sciences.

Chapel Hill 2015

Approved By: Anselmo Lastra Dinesh Manocha Lars Nyland Jan Prins Jack Snoeyink

© 2015 Shawn Daniel Brown ALL RIGHTS RESERVED

#### ABSTRACT

## SHAWN DANIEL BROWN: Case Studies on Optimizing Algorithms for GPU Architectures (Under the direction of Jack Snoeyink)

Modern GPUs are complex, massively multi-threaded, and high-performance. Programmers naturally gravitate towards taking advantage of this high performance for achieving faster results. However, in order to do so successfully, programmers must first understand and then master a new set of skills – writing parallel code, using different types of parallelism, adapting to GPU architectural features, and understanding issues that limit performance.

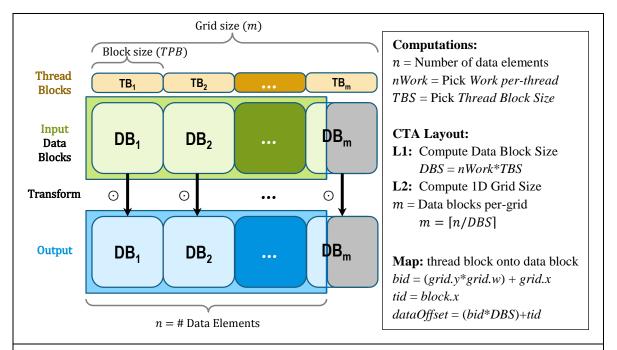

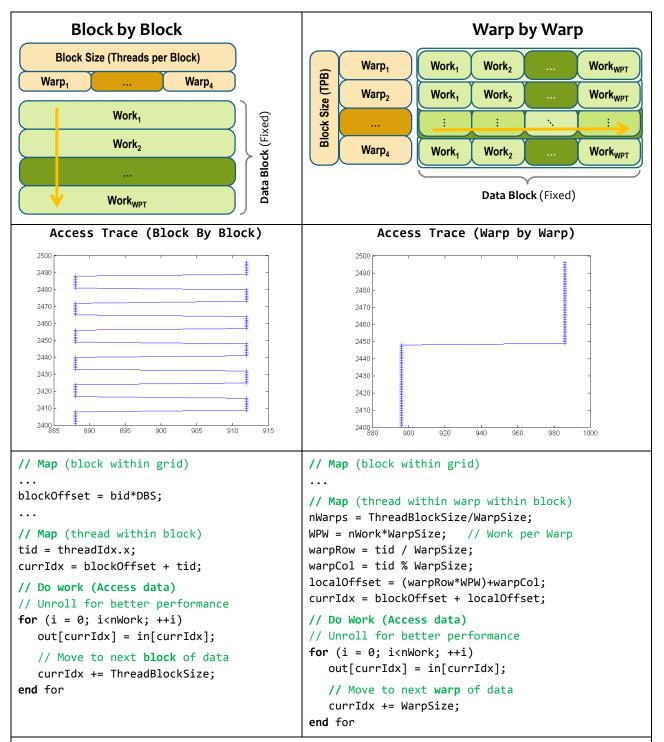

To help GPU programmers become productive more quickly, this dissertation introduces three *data access skeletons* (DASks) – Block, Column, and Row -- and two *block access skeletons* (BASks) – Block-By-Block and Warp-by-Warp. Each "skeleton" provides a highperformance implementation framework that partitions data arrays into data blocks and then iterates over those blocks. Programmers must still write "body" methods on individual data blocks to solve their specific problem. These skeletons provide efficient machine dependent data access patterns for use on GPUs. DASks group *n* data elements into *m* fixed size data blocks. These *m* data block are then partitioned across *p* thread blocks using a 1D or 2D layout pattern. Generic programming techniques are applied to the fixed size data blocks to enable performance experiments for different types of parallelism – instruction-level parallelism (ILP), data-level parallelism (DLP), and thread-level parallelism (TLP).

These different DASks and BASks are introduced using a simple memory I/O (Copy) case study. Three additional case studies – Reduce/Scan, Histogram, and Radix Sort -- demonstrate DASks and BASks in action on parallel primitives and also provide more valuable performance lessons.

To Helene, my love, my rock, my soul mate your love has helped support and guide me through these many tough years working on my PhD. You showed great wisdom, love, and courage during some turbulent times within our family.

### Proverbs 31:10-31

"Who can find a virtuous woman? For her price is far above rubies. ... She opens her mouth with wisdom; and in her tongue is the law of kindness. ... Her children arise up, and call her blessed; her husband also, and he praises her."

## ACKNOWLEDGMENTS

A PhD is a long hard struggle over many years. It takes a lot of support from others to make it through the many false starts, failures, and setbacks required to complete such a huge undertaking. I am very grateful to my mentor, Jack Snoeyink, for his patient guidance, amazing insights, and unwavering support.

# TABLE OF CONTENTS

| LIST OF TABLESxiv                           |

|---------------------------------------------|

| LIST OF FIGURES                             |

| LIST OF ABBREVIATIONSxx                     |

| LIST OF SYMBOLSxxiv                         |

| 1.0 Introduction                            |

| 1.1 The GPU Performance Challenge1          |

| 1.1.1 Good Algorithms                       |

| 1.1.2 Parallel Concepts                     |

| 1.1.3 GPU Architecture                      |

| 1.1.4 GPU Performance Issues5               |

| 1.2 Data Access Skeletons                   |

| 1.3 Case Studies7                           |

| 1.3.1 Memory I/O via Copy                   |

| 1.3.2 kd-tree for Nearest Neighbor Searches |

| 1.3.3 Reduce/Scan                           |

| 1.3.4 Histogram                             |

| 1.3.5 Radix Sort                            |

| 1.4 Summary12                               |

| 2.0 Parallelism                             |

| 2.1 Types of Parallelism                           | 13 |

|----------------------------------------------------|----|

| 2.1.1 Flynn's Taxonomy                             | 14 |

| 2.1.2 Machine Models                               | 16 |

| 2.1.3 Deriving a GPU core from a CPU core          | 21 |

| 2.2 GPU Architecture                               | 24 |

| 2.2.1 Hardware Processor and Memory Hierarchies    | 27 |

| 2.2.2 Warp Threading and Scheduling                | 32 |

| 2.2.3 Parallel Coordination                        |    |

| 3.0 Performance and issues Hindering Performance   | 41 |

| 3.1 Measuring Performance Throughput               | 41 |

| 3.1.1 Throughput Metrics                           | 42 |

| 3.1.2 Parallel Speedup and Work and Depth Analysis | 43 |

| 3.2 Parallel Performance Issues                    | 46 |

| 3.2.1 Scalability                                  | 46 |

| 3.2.2 Parallel Overhead                            | 46 |

| 3.2.3 Load Balancing                               | 46 |

| 3.3 GPU Architecture Issues                        | 47 |

| 3.3.1 CTA Partitioning                             | 47 |

| 3.3.2 GPU Scheduler – Stalls and Hazards           | 51 |

| 3.3.3 GPU Scheduler – Constraints on Occupancy     | 53 |

| 3.3.4 Multi-issue Dispatch                         | 55 |

| 3.3.5 Branch Divergence                                     | 56  |

|-------------------------------------------------------------|-----|

| 3.4 GPU Memory Issues                                       | 57  |

| 3.4.1 Memory Constraints                                    | 58  |

| 3.4.2 Register Spills                                       | 59  |

| 3.4.3 Coalescence                                           | 60  |

| 3.3.4 Bank Conflicts                                        | 61  |

| 4.0 Case Study: Memory I/O                                  | 62  |

| 4.1 How does one setup and launch a GPU Kernel?             | 63  |

| 4.2 How does one launch a kernel with thousands of threads? | 66  |

| 4.3 How does one map threads onto data?                     | 69  |

| 4.4 How can one write GPU data parallel code?               | 73  |

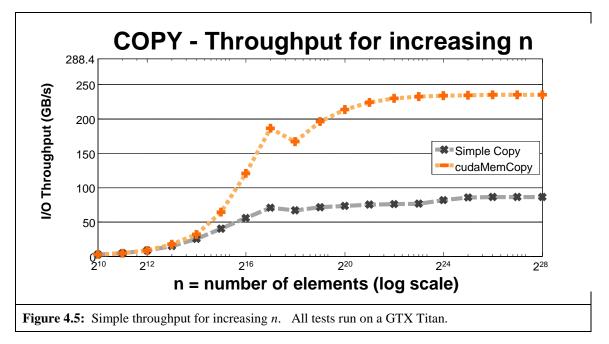

| 4.5 Simple Copy Results                                     | 79  |

| 4.6 Conclusion                                              | 80  |

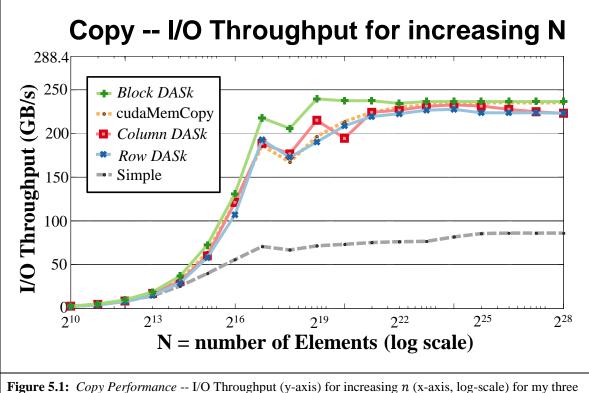

| 5.0 Data Access Skeletons (DASks)                           | 82  |

| 5.1 Block DASk                                              | 84  |

| 5.1.1 Block Access Skeletons (BASks)                        | 86  |

| 5.1.2 Amortized Range Checking                              | 90  |

| 5.1.3 Amortized Pointer Indexing                            | 92  |

| 5.1.4 Block DASK Code                                       | 94  |

| 5.1.5 Improving Copy Performance using ILP and TLP          | 96  |

| 5.1.6 Block DASk Conclusion                                 | 108 |

| 5.2 More MAP Primitives                                  |     |

|----------------------------------------------------------|-----|

| 5.3 Column DASk                                          | 111 |

| 5.3.1 Column DASk Code                                   | 112 |

| 5.3.2 Column DASk Conclusion                             | 116 |

| 5.4 <i>Row</i> DASk                                      | 117 |

| 5.4.1 Warp Alignment                                     | 119 |

| 5.4.2 (FIRST?) (MIDDLE*) (LAST?) Range Check Pattern     | 119 |

| 5.4.3 Load Balancing                                     |     |

| 5.4.4 Row DASk Conclusion                                | 126 |

| 5.5 Lessons Learned from the Memory I/O Case Study       | 127 |

| 6.0 Case Study: <i>Reduce</i> and <i>Scan</i> on the GPU | 130 |

| 6.1 Introduction                                         | 131 |

| 6.2 Issues affecting GPU Performance of Reduce and Scan  | 137 |

| 6.3 Related Work                                         |     |

| 6.4 Parallel Patterns                                    | 141 |

| 6.4.1 Reduce Parallel Patterns                           | 141 |

| 6.4.2 Scan Parallel Patterns                             | 143 |

| 6.5 Reduce and Scan Overview                             | 144 |

| 6.6 Reduce and Scan Implementation Details               | 147 |

| 6.6.1 RunLoad and RunStore Methods                       | 149 |

| 6.6.2 SerialReduce and SerialScan Methods                | 151 |

| 6.6.3 WarpReduce and WarpScan Methods                 |     |

|-------------------------------------------------------|-----|

| 6.6.4 RunUpdate Method                                | 158 |

| 6.6.5 BlockReduce and BlockScan Methods               | 158 |

| 6.6.6 GPU Reduce and GPU Scan Primitives              |     |

| 6.7 Reduce and Scan Implementation Issues             | 173 |

| 6.7.1 Conversion between Warp and Sequential Views    | 173 |

| 6.7.2 Mitigating Bank Conflicts                       | 174 |

| 6.7.3 Constraints on Occupancy                        | 177 |

| 6.8 Results                                           | 179 |

| 6.8.1 Throughput                                      | 179 |

| 6.8.2 Total Cycles                                    |     |

| 6.9 Conclusion                                        |     |

| 6.9.1 Limitations                                     |     |

| 6.9.2 Future Directions                               |     |

| 6.10 Lessons Learned from the Reduce Scan Case Study  |     |

| 7.0 Case Study: kd-tree for Nearest Neighbor Searches | 191 |

| 7.1 Nearest Neighbor Problem Definitions              | 192 |

| 7.2 Related Work                                      | 194 |

| 7.2.1 NN Solutions                                    | 194 |

| 7.2.2 kd-tree Review                                  |     |

| 7.2.3 Related NN work on the GPU                      |     |

| 7.3 The <i>k</i> d-tree Data Structure                              | 197 |

|---------------------------------------------------------------------|-----|

| 7.3.1 kd-tree Search Concepts                                       | 197 |

| 7.3.2 kd-tree NN Search                                             |     |

| 7.4 Hardware Limits and Design Choices                              | 198 |

| 7.4.1 GPU Hardware considerations                                   | 198 |

| 7.4.2 kd-tree Design Choices                                        | 201 |

| 7.5 Building the <i>k</i> d-tree                                    | 204 |

| 7.6 Searching the <i>k</i> d-tree                                   | 207 |

| 7.6.1 Point Location Problem                                        | 207 |

| 7.6.2 QNN and All-NN Search Algorithms                              |     |

| 7.6.3 kNN and All-kNN Search Algorithms                             |     |

| 7.6.4 GPU Resource constraints for <i>k</i> NN and All- <i>k</i> NN | 209 |

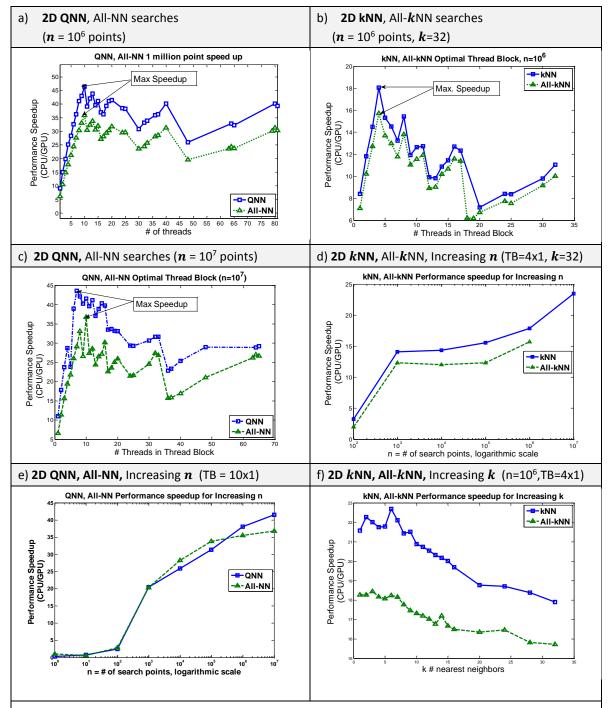

| 7.7 Performance Results                                             | 210 |

| 7.7.1 Building the kd-tree                                          | 211 |

| 7.7.2 Finding the optimal thread block size                         | 211 |

| 7.7.3 Performance for increasing <i>n</i> and <i>k</i>              | 213 |

| 7.8 Conclusion                                                      | 213 |

| 7.8.1 2D Performance Summary                                        | 214 |

| 7.8.2 3D Performance Summary                                        | 214 |

| 7.8.3 4D Performance Summary                                        | 214 |

| 7.9 Future Directions                                               | 215 |

| 8.0 Case Study: A GPU Histogram              |     |

|----------------------------------------------|-----|

| 8.1 Introduction                             | 216 |

| 8.1.1 Parallelism improves Performance       |     |

| 8.2 Related Work                             |     |

| 8.2.1 Podlozhnyuk's Histogram Method         |     |

| 8.2.2 Nugteren's Histogram Method            |     |

| 8.3 My TRISH Method                          |     |

| 8.3.1 Improving TLP                          |     |

| 8.3.2 Improving ILP                          |     |

| 8.3.3 Improving Bit-level Parallelism        |     |

| 8.3.4 Picking the best k value               |     |

| 8.3.5 TRISH method summary                   |     |

| 8.4 Performance Results                      |     |

| 8.4.1 Direct Comparison                      | 234 |

| 8.4.2 Degraded Self-Comparison               | 238 |

| 8.4.3 Profiler Results                       | 238 |

| 8.5 Conclusion                               |     |

| 8.5.1 Future Directions                      |     |

| 8.6 Acknowledgements                         |     |

| 9.0 Case Study: <i>Radix Sort</i> on the GPU |     |

| 9.1 Related Work                             |     |

| 9.2 Serial CPU Implementation         | 251 |

|---------------------------------------|-----|

| 9.2.1 Serial CPU Counting Sort        | 251 |

| 9.2.2 Serial CPU LSD Radix Sort       | 253 |

| 9.3 Parallel GPU Implementation       | 255 |

| 9.3.1 GPU_CountKeys Kernel            | 257 |

| 9.3.2 GPU_ScanRuns Kernel             | 265 |

| 9.3.3 GPU_DistributeKeys Kernel       | 268 |

| 9.4 Experiment Results                | 304 |

| 9.4.1 Data Throughput                 | 305 |

| 9.4.2 Total Cycles                    | 308 |

| 9.5 Conclusion                        | 311 |

| 9.6 Future Directions                 | 315 |

| 9.7 Lessons Learned                   | 316 |

| 10.0 Conclusion                       | 320 |

| 10.1 DASks and BASks                  | 321 |

| 10.1.1 Block Access Skeletons (BASks) | 325 |

| 10.1.2 Data Access Skeletons (DASks)  | 326 |

| 10.2 Summary and Lessons Learned      | 333 |

| APPENDIX A: GLOSSARY                  | 336 |

| BIBLIOGRAPHY                          | 431 |

## LIST OF TABLES

| Table 2.1 GPU Memory Types                                                                                                                                                                                                                                                                                                                     |                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

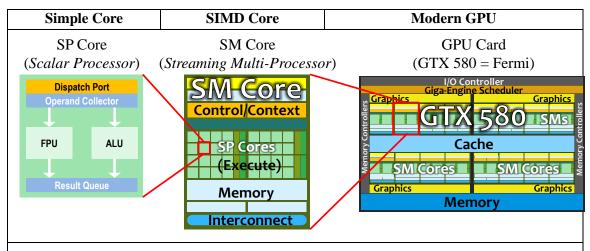

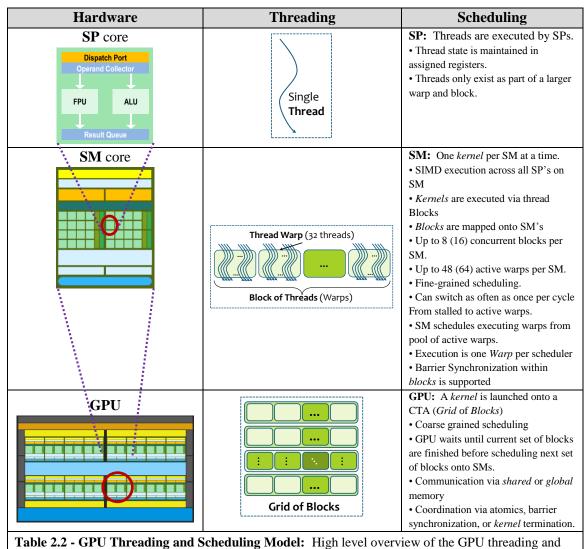

| Table 2.2 GPU Threading and Scheduling Model                                                                                                                                                                                                                                                                                                   | 33                                            |

| Table 3.1 Constraints on Occupancy (Fermi and Kepler)                                                                                                                                                                                                                                                                                          | 55                                            |

| Table 4.1 Mapping CTA parameters (Code Snippets)                                                                                                                                                                                                                                                                                               | 71                                            |

| Table 5.1 Loop Unrolling vs. Software Pipelining Performance                                                                                                                                                                                                                                                                                   | 103                                           |

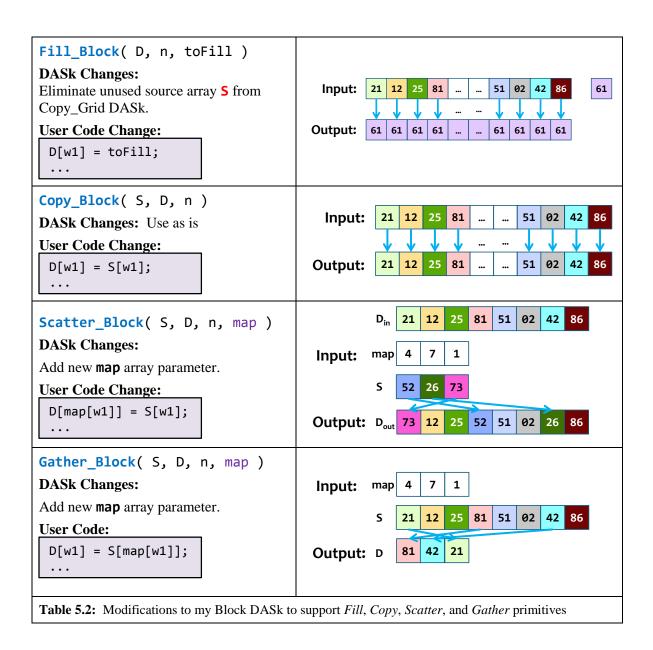

| Table 5.2 Modifications to the Block DASk to support Fill, Copy, Scatter, and Gather                                                                                                                                                                                                                                                           | 109                                           |

| Table 5.3 Load balancing data blocks for the <first?><middle*><last?> Pattern</last?></middle*></first?>                                                                                                                                                                                                                                       | 123                                           |

| Table 5.4 Batching vs. Interleaving Memory Accesses                                                                                                                                                                                                                                                                                            | 127                                           |

| Table 6.1 Common Associative Operators                                                                                                                                                                                                                                                                                                         | 132                                           |

| Table 6.2 Reduce Scan Nomenclature and Symbols                                                                                                                                                                                                                                                                                                 | 133                                           |

| Table 6.3 Serial Reduce and Inclusive/Exclusive Serial Scan                                                                                                                                                                                                                                                                                    | 134                                           |

| Table 6.4 Best Reduce / Scan Throughput Results                                                                                                                                                                                                                                                                                                | 135                                           |

| Table 6.5 Adder Summary                                                                                                                                                                                                                                                                                                                        | 139                                           |

| Table 6.6 GPU_Reduce / GPU_Scan Template Parameters                                                                                                                                                                                                                                                                                            | 170                                           |

| Table 6.7 GPU_Reduce / GPU_Scan Function Parameters                                                                                                                                                                                                                                                                                            | 171                                           |

|                                                                                                                                                                                                                                                                                                                                                |                                               |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters                                                                                                                                                                                                                                                                                                 |                                               |

|                                                                                                                                                                                                                                                                                                                                                | 171                                           |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters                                                                                                                                                                                                                                                                                                 | 171<br>173                                    |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters         Table 6.9 Convert between Warp and Sequential data views                                                                                                                                                                                                                                | 171<br>173<br>175                             |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters         Table 6.9 Convert between Warp and Sequential data views         Table 6.10 Padding for a given run length to avoid Bank Conflicts                                                                                                                                                      | 171<br>173<br>175<br>179                      |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters         Table 6.9 Convert between Warp and Sequential data views         Table 6.10 Padding for a given run length to avoid Bank Conflicts         Table 6.11 Reduce/Scan Experiment Environment                                                                                                | 171<br>173<br>175<br>179<br>180               |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters.         Table 6.9 Convert between Warp and Sequential data views         Table 6.10 Padding for a given run length to avoid Bank Conflicts         Table 6.11 Reduce/Scan Experiment Environment.         Table 6.12 Best Case Reduce/Scan Results.                                            | 171<br>173<br>175<br>179<br>180<br>180        |

| Table 6.8 GPU_Reduce / GPU_Scan CTA Parameters.         Table 6.9 Convert between Warp and Sequential data views         Table 6.10 Padding for a given run length to avoid Bank Conflicts         Table 6.11 Reduce/Scan Experiment Environment.         Table 6.12 Best Case Reduce/Scan Results.         Table 6.13 TLP Reduce/Scan Results | 171<br>173<br>175<br>179<br>180<br>180<br>181 |

| Table 6.17 Total Cycle Results                          | 184 |

|---------------------------------------------------------|-----|

| Table 7.1 Nearest Neighbor Search Types                 | 192 |

| Table 7.2 NN Search Experiment Environment              | 210 |

| Table 7.3 CPU Build Performance                         | 211 |

| Table 8.1 Histogram Test Environment                    | 234 |

| Table 8.2 CUDA Profiler Results                         | 239 |

| Table 9.1 GPU_CountKeys C++ Template Parameters         | 259 |

| Table 9.2 GPU_CountKeys Function Parameters             |     |

| Table 9.3 GPU_CountKeys CTA Parameters                  |     |

| Table 9.4 GPU_DistributeKeys C++ Template Parameters    | 271 |

| Table 9.5 GPU_DistributeKeys Function Parameters        | 272 |

| Table 9.6 GPU_DistributeKeys CTA Parameters             | 273 |

| Table 9.7 Bank Conflicts for Increasing run length      |     |

| Table 9.8 Coalesced I/O Efficiency (for increasing DBS) |     |

| Table 9.9 Radix Sort Experiment Environment             |     |

| Table 9.10 Maximum Data Throughput (on GTX 580)         |     |

| Table 9.11 Maximum Data Throughput (on GTX Titan)       |     |

| Table 9.12 Total Cycles (GPU_CountKeys Kernel)          |     |

| Table 9.13 Total Cycles (GPU_DistributeKeys Kernel)     |     |

## LIST OF FIGURES

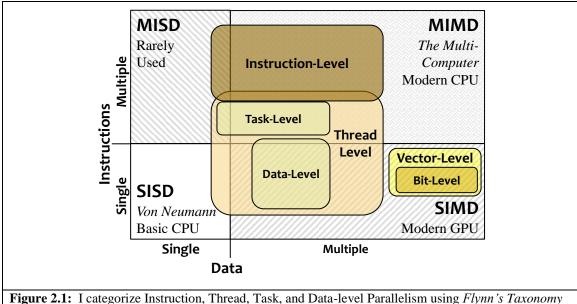

| Figure 2.1 Flynn's Taxonomy                                                         |

|-------------------------------------------------------------------------------------|

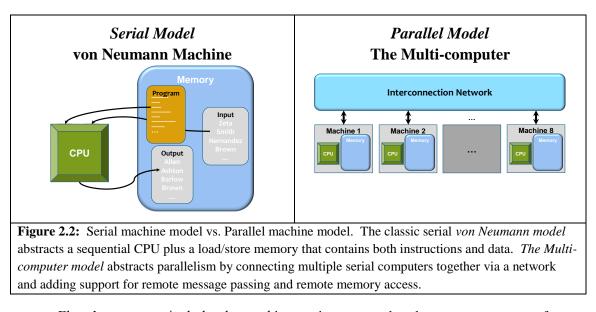

| Figure 2.2 Serial vs. Parallel Machine Models16                                     |

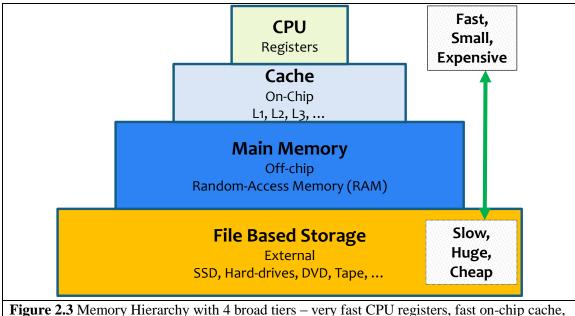

| Figure 2.3 Memory Hierarchy20                                                       |

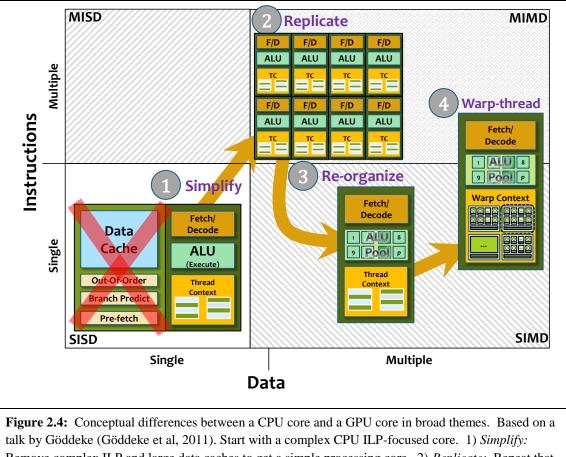

| Figure 2.4 CPU vs. GPU core in Broad Themes                                         |

| Figure 2.5 Modern GPU core layout25                                                 |

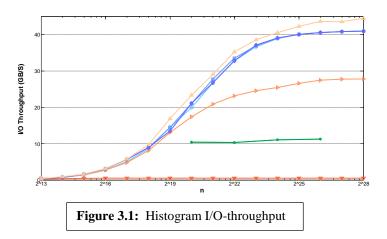

| Figure 3.1 Histogram I/O throughput43                                               |

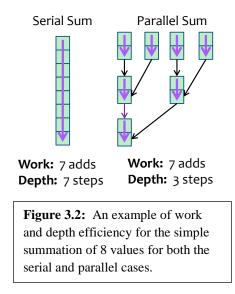

| Figure 3.2 Work and Depth Example45                                                 |

| Figure 3.3 Simple CTA mapping50                                                     |

| Figure 4.1 CPU Host Pattern Overview64                                              |

| Figure 4.2 CPU Host Pattern Example65                                               |

| Figure 4.3 Computing a CTA layout                                                   |

| Figure 4.4 Serial, Parallel, and GPU Copy programs76                                |

| Figure 4.5 Simple Copy Throughput for Increasing <i>n</i>                           |

| Figure 5.1 Copy Performance                                                         |

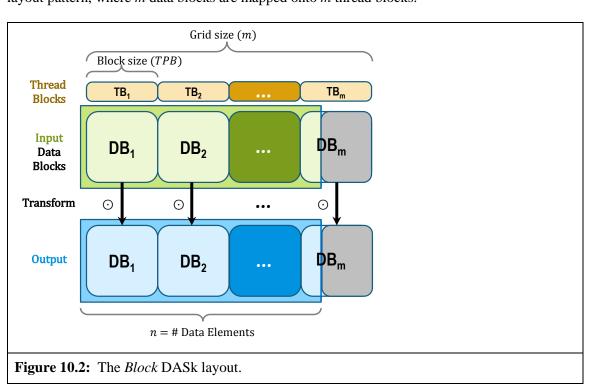

| Figure 5.2 The <i>Block</i> Data Access Skeleton (DASk)                             |

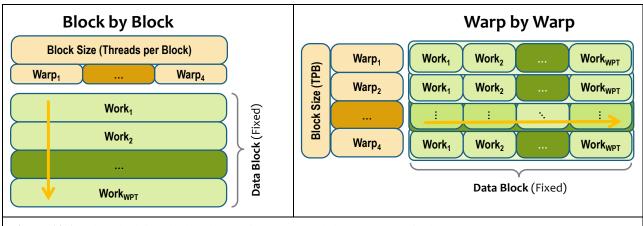

| Figure 5.3 Block Access Skeletons ( <i>Block-by-Block</i> vs. <i>Warp-by-Warp</i> ) |

| Figure 5.4 Amortized Range Checking (Block DASk)90                                  |

| Figure 5.5 Amortized Pointer Indexing                                               |

| Figure 5.6 Block DASk Code                                                          |

| Figure 5.7 Automatic Loop Unrolling Example                                         |

| Figure 5.8 Automatic Loop Unrolling vs. Manual Loop Unrolling Throughput            |

| Figure 5.9 Manual Loop Unrolling Example101                                         |

| Figure 5.10 Copy Throughput for Increasing <i>block size</i> 106                    |

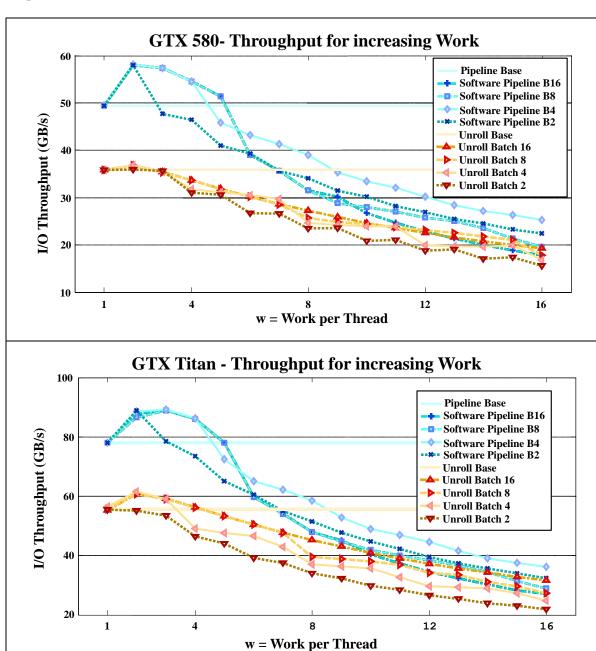

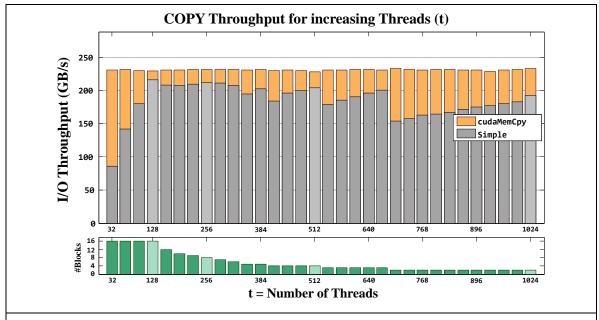

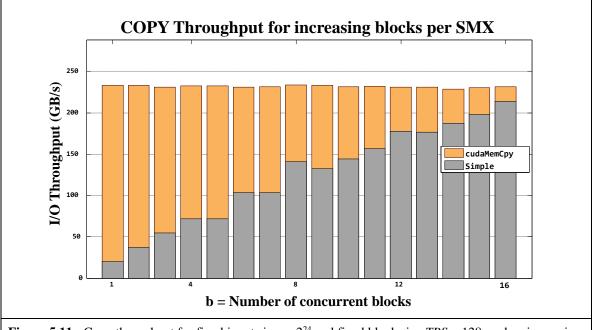

| Figure 5.11 Copy Throughput for an Increasing number of concurrent blocks per SM107 |

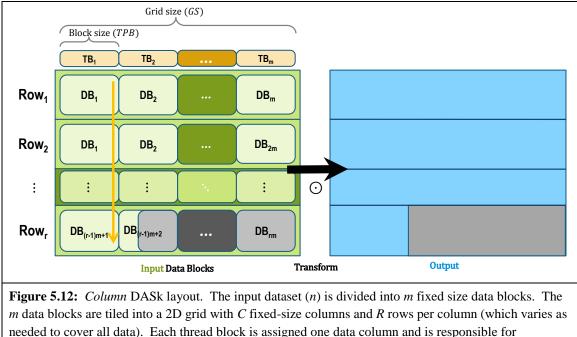

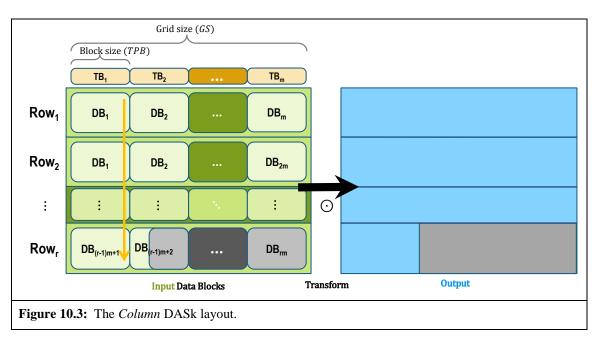

| Figure 5.12 The Column DASk112                                                      |

| Figure 5.13 Column DASk Code                                                      | 114-115 |

|-----------------------------------------------------------------------------------|---------|

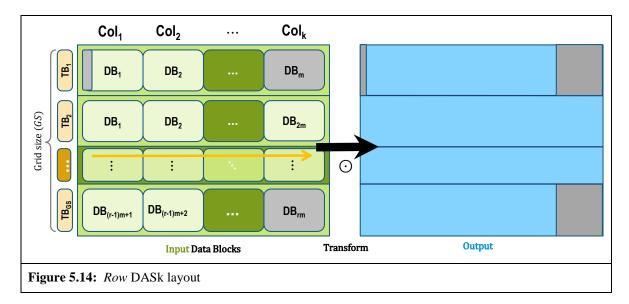

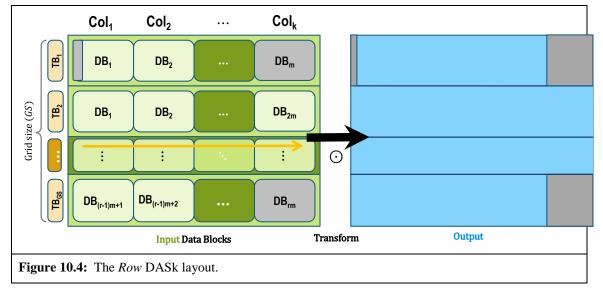

| Figure 5.14 The <i>Row</i> DASk                                                   | 118     |

| Figure 5.15 Warp Aligning Data Access                                             | 119     |

| Figure 5.16 <i>Row</i> DASk Code with the <i>(FIRST?)/MIDDLE*/(LAST?)</i> Pattern | 121-122 |

| Figure 5.17 Load Balancing Code for the Row DASk                                  | 124-125 |

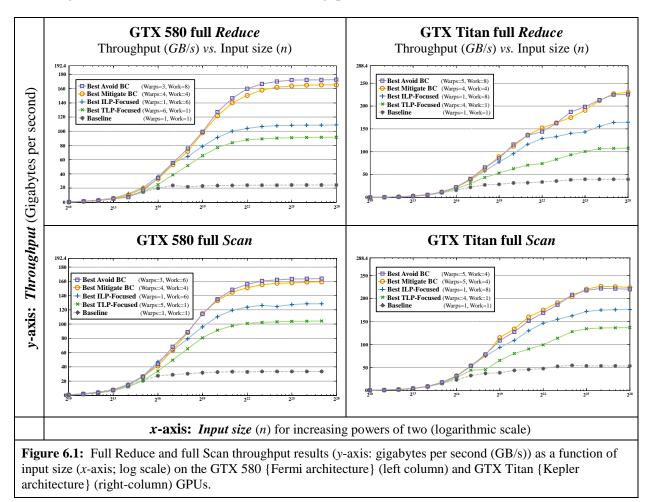

| Figure 6.1 Full Reduce/Scan Throughput Results                                    | 136     |

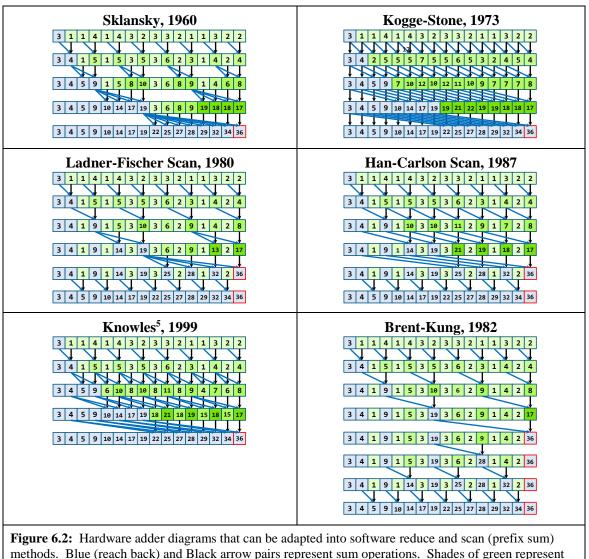

| Figure 6.2 Hardware Adder Diagrams                                                | 140     |

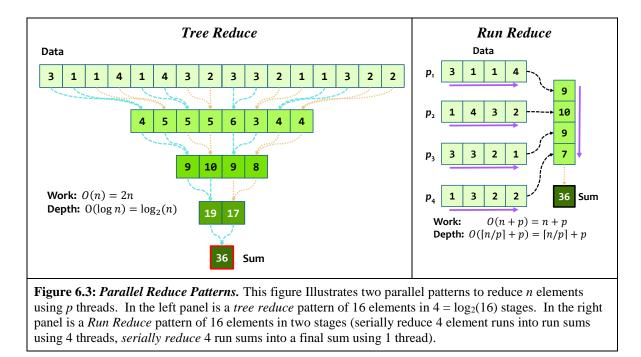

| Figure 6.3 Parallel Reduce Patterns (Tree-Reduce and Run-Reduce)                  | 142     |

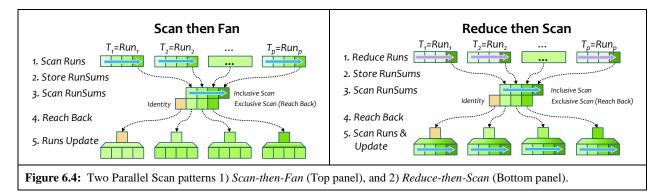

| Figure 6.4 Parallel Scan Patterns (Scan-then-Fan and Reduce-then-Scan)            | 143     |

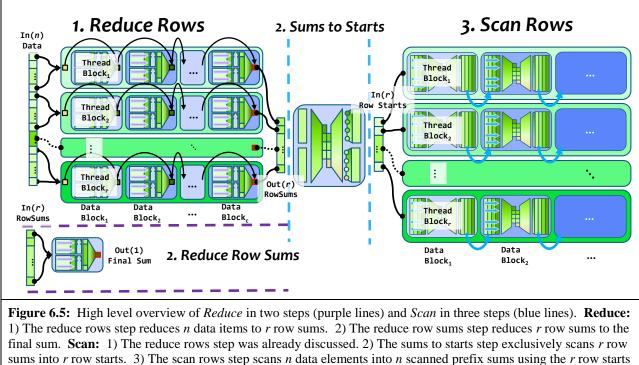

| Figure 6.5 GPU Reduce and Scan (High Level Overview)                              | 148     |

| Figure 6.6 RunLoad Method (Code)                                                  | 150     |

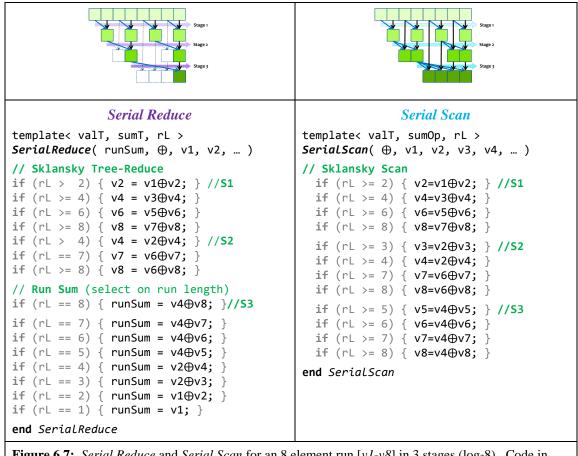

| Figure 6.7 SerialReduce and SerialScan Methods (Code)                             | 152     |

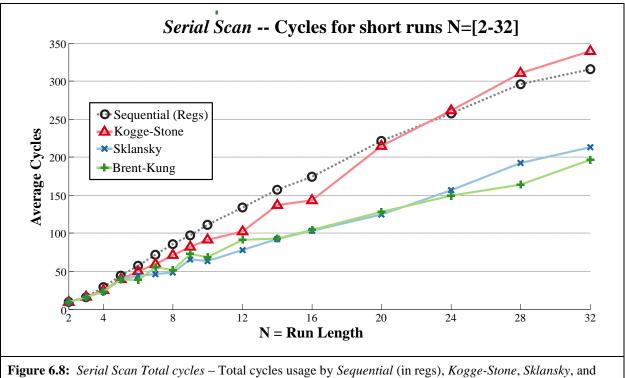

| Figure 6.8 SerialScan Total Cycles (Comparison)                                   | 153     |

| Figure 6.9 Overloaded Add Functors (CPU and GPU)                                  | 154     |

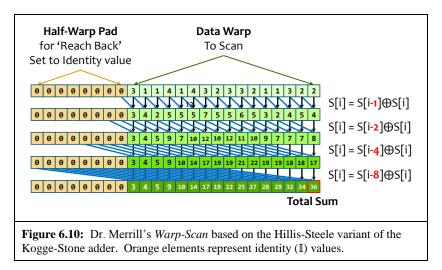

| Figure 6.10 WarpScan Layout Diagram                                               | 155     |

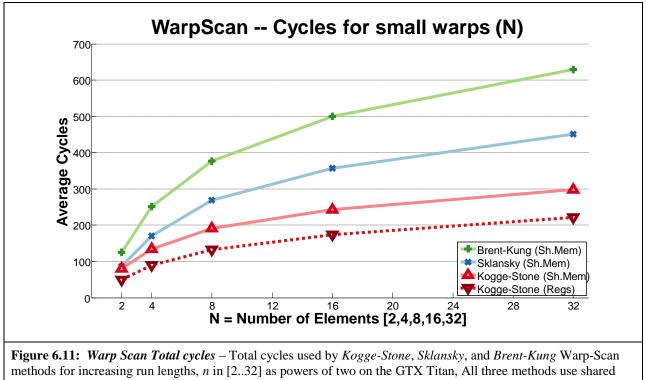

| Figure 6.11 WarpScan Total Cycles (Comparison)                                    | 156     |

| Figure 6.12 WarpReduce and WarpScan Methods (Code)                                | 157     |

| Figure 6.13 RunUpdate Method (Code)                                               | 158     |

| Figure 6.14 BlockReduce Method (Code)                                             | 161     |

| Figure 6.15 BlockScan Method (Code) plus Setup Hints                              | 162-163 |

| Figure 6.16 GPU_Scan Kernel (High level Code Overview)                            | 168-169 |

| Figure 6.17 Pad and Rake Technique (Overview)                                     | 176     |

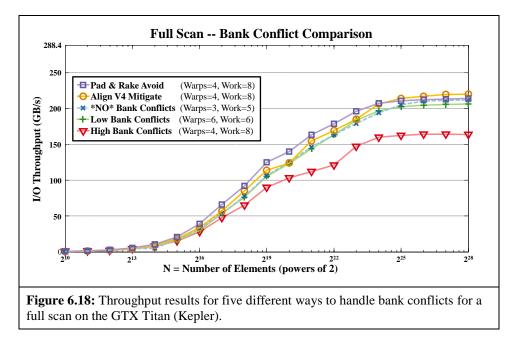

| Figure 6.18 Bank Conflict Comparison                                              |         |

| Figure 7.1 Brute Force Spatial Search                                             | 194     |

| Figure 7.2 Spatial Searches                                                       | 194     |

| Figure 7.3 A kd-tree                                                        |             |

|-----------------------------------------------------------------------------|-------------|

| Figure 7.4 A kd-tree Trim Test                                              | 197         |

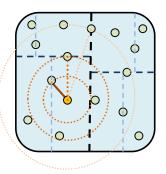

| Figure 7.5 kd-tree Search                                                   |             |

| Figure 7.6 kd-tree Build and Search Methods (Code)                          | 205         |

| Figure 7.7 kd-tree Search Results                                           | 212         |

| Figure 8.1 256-bin CPU Histogram Method (Code)                              | 218         |

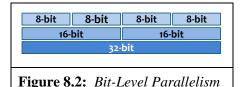

| Figure 8.2 Bit-Level Parallelism                                            | 219         |

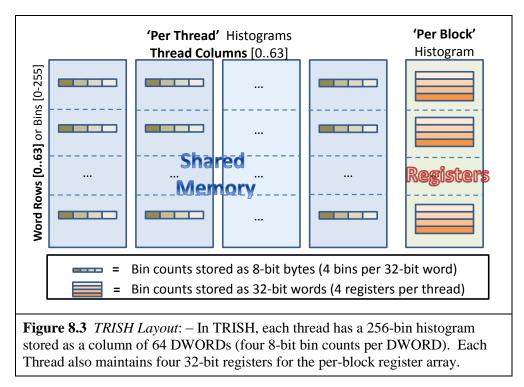

| Figure 8.3 TRISH Layout                                                     | 223         |

| Figure 8.4 Staggered Start / Circular Indexing (Code Snippets)              |             |

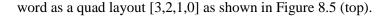

| Figure 8.5 BLP Optimization                                                 | 227         |

| Figure 8.6 Binning Code                                                     |             |

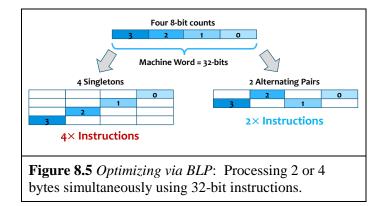

| Figure 8.7 Row-Sum Efficiency                                               | 230         |

| Figure 8.8 GPU_Count Kernel                                                 | 232         |

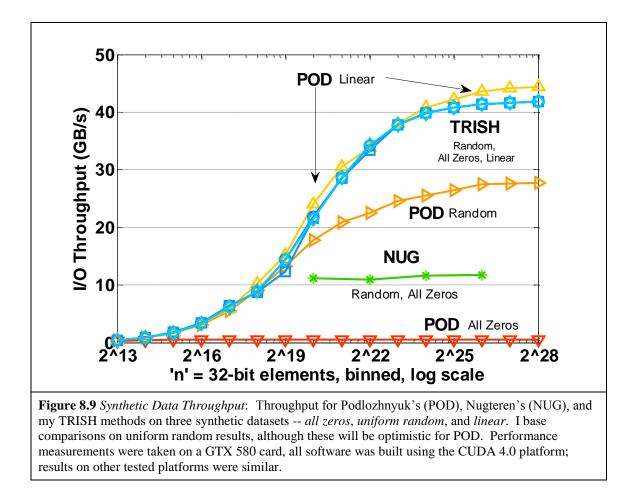

| Figure 8.9 Synthetic Data Throughput                                        | 235         |

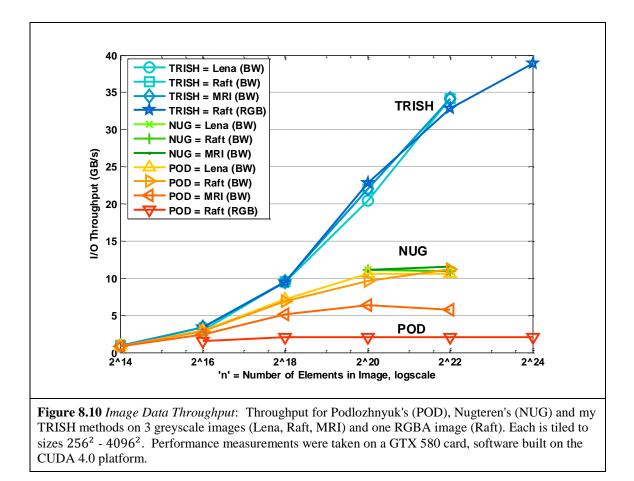

| Figure 8.10 Image Data Throughput                                           | 237         |

| Figure 9.1 Serial Counting Sort (Code)                                      |             |

| Figure 9.2 Serial LSD Radix Sort (Code)                                     |             |

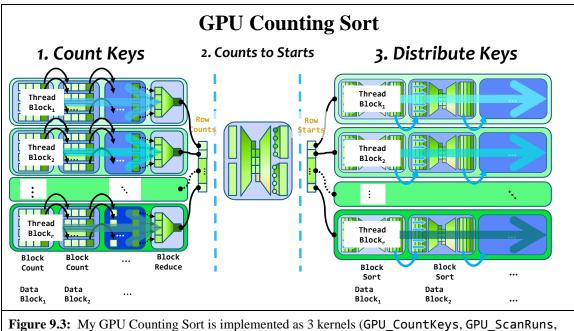

| Figure 9.3 GPU Counting Sort (3 Kernel Diagram)                             | 256         |

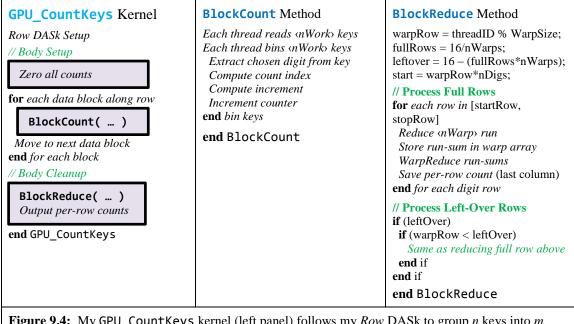

| Figure 9.4 GPU_CountKeys Kernel (Code Overview)                             |             |

| Figure 9.5 Sequential vs. Pipelined Counting Performance Bottleneck (Code S | nippets)262 |

| Figure 9.6 Handling Potential Overflow (Code Snippet)                       |             |

| Figure 9.7 GPU_ScanRuns Kernel (Code Overview)                              |             |

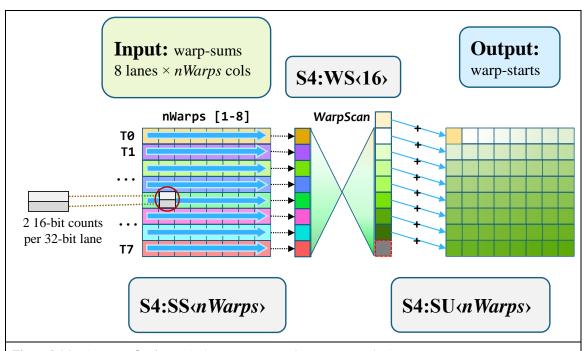

| Figure 9.8 GPU_DistributeKeys Kernel (Code Overview)                        |             |

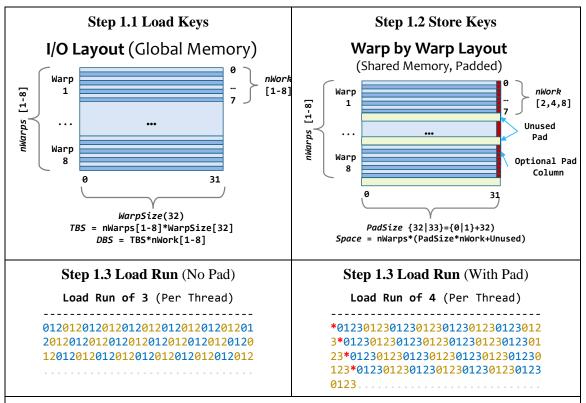

| Figure 9.9 Loading Keys Efficiently                                         |             |

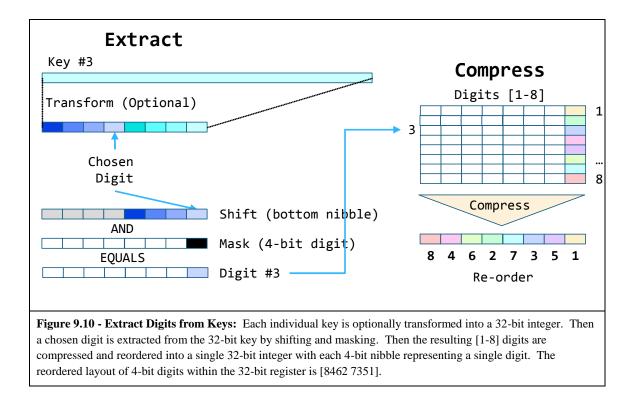

| Figure 9.10 Extract Digits from Keys                                        |             |

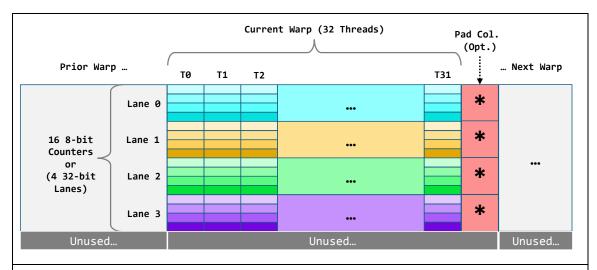

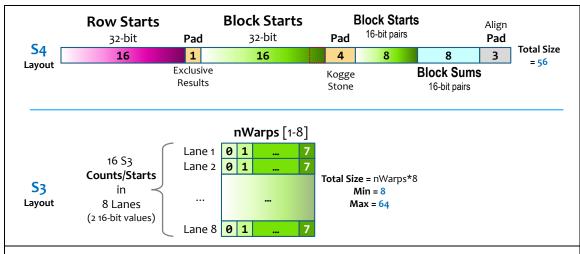

| Figure 9.11 CountDigits Memory Layout                                       |             |

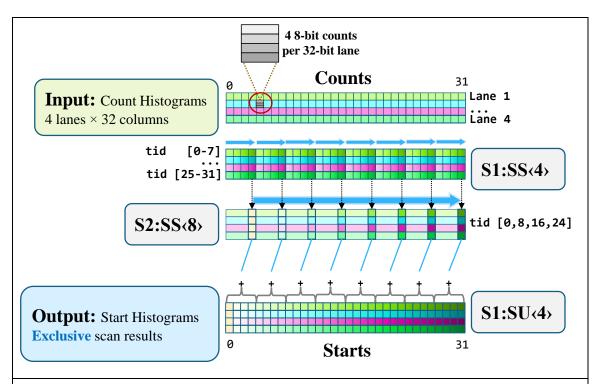

| Figure 9.12 ScanWarps Method Overview                           |         |

|-----------------------------------------------------------------|---------|

| Figure 9.13 ScanWarps Method (Code)                             |         |

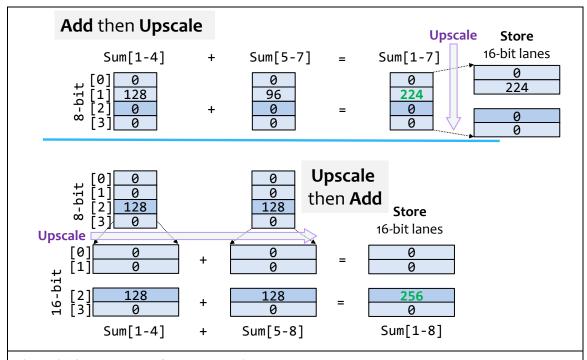

| Figure 9.14 Handle Overflow by Upscaling                        |         |

| Figure 9.15 ScanBlocks Memory Layout                            |         |

| Figure 9.16 ScanBlocks Overview                                 |         |

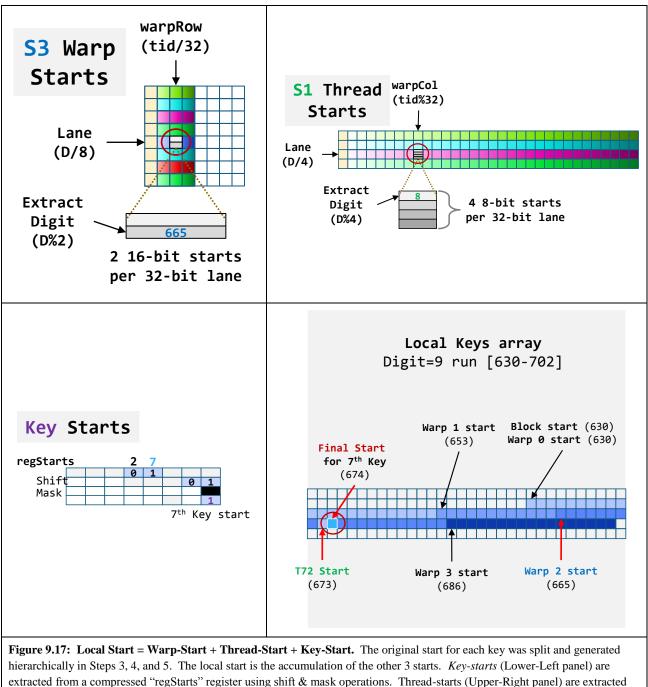

| Figure 9.17 Local Start = warp-start + thread-start + key-start |         |

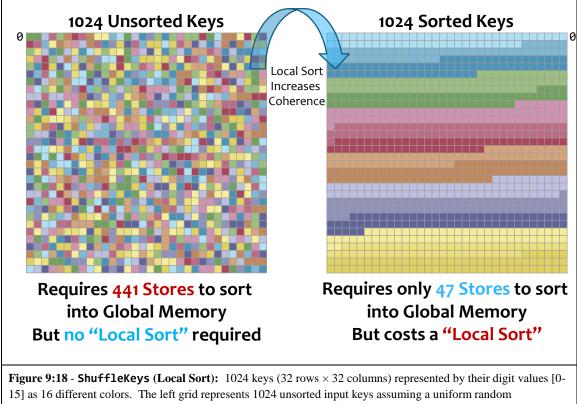

| Figure 9.18 ShuffleKeys (Sorting Increases Coherence)           |         |

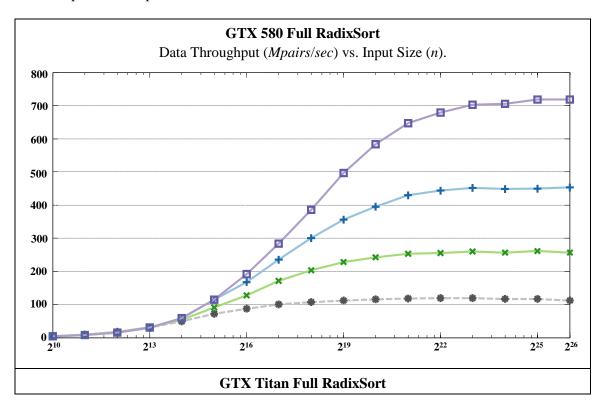

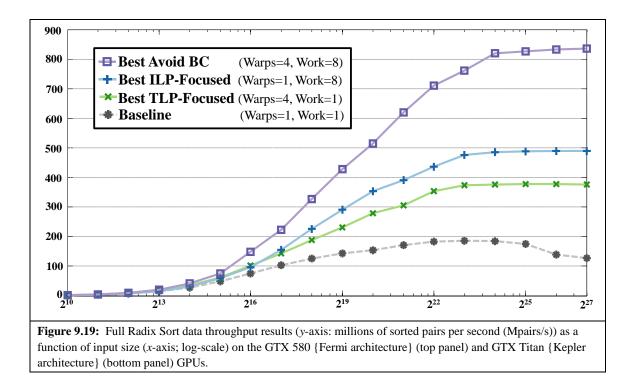

| Figure 9.19 Full Radix Sort Data Throughput Results             | 307-308 |

| Figure 10.1 BASks Review (Block-by-Block and Warp-by-Warp)      |         |

| Figure 10.2 The <i>Block</i> DASK Review                        |         |

| Figure 10.3 The Column DASK Review                              |         |

| Figure 10.4 The Row DASK Review                                 |         |

## LIST OF ABBREVIATIONS

| ALU     | Arithmetic Logic Unit                                                 |

|---------|-----------------------------------------------------------------------|

| All-kNN | All k Nearest Neighbor (search)                                       |

| All-NN  | All Nearest Neighbor (Search)                                         |

| AMP     | Accelerated Massive Parallelism (Microsoft)                           |

| ANN     | Approximate Nearest Neighbor (Search)                                 |

| API     | Application Program Interface                                         |

| b, B    | Bit or boolean {0 1} or { <i>true</i>   <i>false</i> }                |

| BASk    | Block Access Skeleton                                                 |

| BFS     | Breath First Search                                                   |

| bid     | block id (uniquely identifies thread block within grid)               |

| BLP     | Bit-Level Parallelism                                                 |

| BPS     | Bits Per Second                                                       |

| BSP     | Binary Space Partition (tree)                                         |

| BYTE    | Derived from 'bit' and 'bite' (8-bits of data)                        |

| CC      | Clock Cycle or Compute Capability                                     |

| CPI     | (average) Cycles Per Instruction (for entire algorithm)               |

| CPU     | Central Processing Unit                                               |

| СТА     | Cooperative Thread Array (Grid of Thread Blocks)                      |

| CUDA    | Compute Unified Device Architecture (NVIDIA)                          |

| DASk    | Data Access Skeleton                                                  |

| DBS     | Data Block Size                                                       |

| DDR     | <b>D</b> ouble <b>D</b> ata <b>R</b> ate memory type (as in DDR3-RAM) |

| DFS     | Depth First Search                                                    |

| DLP     | Data-Level Parallelism                                                |

| DMA     | Direct Memory Access                                                  |

| DWORD      | Double Word (32-bits of data, 4 bytes)               |

|------------|------------------------------------------------------|

| EX         | Execute cycle (classic MIPS pipeline)                |

| FMA        | Fused Multiply Add instruction (in ISA)              |

| FPU        | Floating Point Unit                                  |

| G          | Giga (one billion)                                   |

| GB         | Giga-Byte (one billion bytes)                        |

| GM         | Global Memory                                        |

| GPU        | Graphics Processing Unit                             |

| HPC        | High Performance Computing                           |

| ID         | Instruction Decode cycle (classic MIPS pipeline)     |

| IDE        | Interactive Development Environment                  |

| IF         | Instruction Fetch cycle (classic MIPS pipeline)      |

| II         | (total) Instructions Issued (for entire algorithm)   |

| ILP        | Instruction-Level Parallelism                        |

| IPC        | (average) Instructions (retired) Per Cycle           |

| ISA        | Instruction Set Architecture                         |

| Κ          | Kilo (one thousand)                                  |

| KB         | Kilo-Byte (one thousand bytes)                       |

| <i>k</i> d | k-Dimensional                                        |

| kd-tree    | A generalized binary tree used for spatial searching |

| kNN        | k Nearest Neighbor (search)                          |

| KSHS       | Kogge-Stone-Hillis-Steele prefix-sum (scan)          |

| LSD        | Least Significant Digit                              |

| М          | Mega (one million)                                   |

| MB         | Mega-Byte (one million bytes)                        |

| MEM        | Memory access cycle (classic MIPS pipeline)          |

| MISD                                                             | Multiple-Instruction, Single Data                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIMD                                                             | Multiple-Instruction, Multiple Data                                                                                                                                                                                                                                                    |

| MIPS                                                             | Microprocessor (without) Interlocked Pipeline Stages                                                                                                                                                                                                                                   |

| MPI                                                              | Message Passing Interface                                                                                                                                                                                                                                                              |

| MPMD                                                             | Multiple-Program, Multiple-Data                                                                                                                                                                                                                                                        |

| MSD                                                              | Most Significant Digit                                                                                                                                                                                                                                                                 |

| NN                                                               | Nearest Neighbor (Search)                                                                                                                                                                                                                                                              |

| NOP                                                              | No Operation                                                                                                                                                                                                                                                                           |

| octree                                                           | A 3D hierarchical spatial searching data structure                                                                                                                                                                                                                                     |

| OpenCL                                                           | Open Computing Language (Khronos Group)                                                                                                                                                                                                                                                |

| PTX                                                              | Parallel Thread Execution assembly code (NVIDIA)                                                                                                                                                                                                                                       |

| quadtree                                                         | A 2D hierarchical spatial searching data structure                                                                                                                                                                                                                                     |

| QNN                                                              | Query Nearest Neighbor (search)                                                                                                                                                                                                                                                        |

|                                                                  |                                                                                                                                                                                                                                                                                        |

| QWORD                                                            | Quad Word (64-bits of data, 8 bytes)                                                                                                                                                                                                                                                   |

| QWORD<br>RB                                                      | Quad Word (64-bits of data, 8 bytes)<br>Reach Back (convert inclusive to exclusive scan)                                                                                                                                                                                               |

| -                                                                |                                                                                                                                                                                                                                                                                        |

| RB                                                               | Reach Back (convert inclusive to exclusive scan)                                                                                                                                                                                                                                       |

| RB<br>RAM                                                        | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory                                                                                                                                                                                                               |

| RB<br>RAM<br>RAW                                                 | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)                                                                                                                                                                             |

| RB<br>RAM<br>RAW<br>RISC                                         | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer                                                                                                                                         |

| RB<br>RAM<br>RAW<br>RISC<br>RNN                                  | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer<br>Range (Nearest Neighbor) Query Search                                                                                                |

| RB<br>RAM<br>RAW<br>RISC<br>RNN<br>RAM                           | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer<br>Range (Nearest Neighbor) Query Search<br>Random Access Memory                                                                        |

| RB<br>RAM<br>RAW<br>RISC<br>RNN<br>RAM<br>SM                     | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer<br>Range (Nearest Neighbor) Query Search<br>Random Access Memory<br>Shared Memory                                                       |

| RB<br>RAM<br>RAW<br>RISC<br>RNN<br>RAM<br>SM<br>Sh. Mem.         | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer<br>Range (Nearest Neighbor) Query Search<br>Random Access Memory<br>Shared Memory<br>Shared Memory                                      |

| RB<br>RAM<br>RAW<br>RISC<br>RNN<br>RAM<br>SM<br>Sh. Mem.<br>SIMD | Reach Back (convert inclusive to exclusive scan)<br>Random-Access Memory<br>Read After Write (data hazard)<br>Reduced Instruction Set Computer<br>Range (Nearest Neighbor) Query Search<br>Random Access Memory<br>Shared Memory<br>Shared Memory<br>Single-Instruction, Multiple-Data |

| SMX   | Streaming Multi-core Extended (Multi-processor)          |

|-------|----------------------------------------------------------|

| SMP   | Simultaneous Multi-Processor (machine)                   |

| SMT   | Simultaneous Multi-Threading                             |

| SoC   | System on a Chip (Modern CPUs)                           |

| SP    | Scalar Processor (within SM)                             |

| SPMD  | Single-Program, Multiple-Data                            |

| SPMT  | Single-Program, Multi-Threaded                           |

| Т     | Tera (one trillion)                                      |

| ТВ    | Tera-Byte (one trillion bytes)                           |

| TBS   | Thread Block Size                                        |

| TC    | Total Cycles (for entire algorithm)                      |

| tid   | thread id (uniquely identifies thread within block)      |

| TLP   | Thread-Level Parallelism                                 |

| TRISH | Threaded Register Interleaved Strided Histogram (method) |

| VP    | Vector-level Parallelism (Vectorization,                 |

|       | or Vector Processing)                                    |

| WAR   | Write After Read (data hazard)                           |

| WAW   | Write After Write (data hazard)                          |

| WB    | Write-Back cycle (classic MIPS pipeline)                 |

| WORD  | Word (16-bits of data, 2 bytes)                          |

## LIST OF SYMBOLS

| $\odot$        | Unary Transform operator, $b = \bigcirc a = \bigcirc (a)$                                                                                                                                                                                                                                                                         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\oplus$       | Binary Transform operator, $c = a \oplus b = \oplus(a, b)$                                                                                                                                                                                                                                                                        |

| A <sub>n</sub> | Array of <i>n</i> data elements                                                                                                                                                                                                                                                                                                   |

| С              | Number of columns, if the number of rows ( <i>R</i> ) is fixed it can be computed as $C = [m/R]$                                                                                                                                                                                                                                  |

| Ci             | The $i^{\text{th}}$ bin counter, taken from [0, <i>d</i> ) bins in a count histogram (Radix Sort).                                                                                                                                                                                                                                |

| CTA layout     | Sizes and IDs of CTA grid and thread blocks respectively.<br>Even though the size parameters can be taken directly from<br>CTA runtime parameters they are usually indirectly set as<br>compile-time constants for improved performance and to<br>support generic programming. The position IDs are always<br>runtime parameters. |

| gw             | Grid Width, AKA gridDim.x                                                                                                                                                                                                                                                                                                         |

| gh             | Grid Height, AKA gridDim.y                                                                                                                                                                                                                                                                                                        |

| gl             | Grid Length, AKA gridDim.z (currently unused)                                                                                                                                                                                                                                                                                     |

| bw             | Block Width, AKA blockDim.x                                                                                                                                                                                                                                                                                                       |

| bh             | Block Height, AKA blockDim.y                                                                                                                                                                                                                                                                                                      |

| bl             | Block Length, AKA blockDim.z                                                                                                                                                                                                                                                                                                      |

| bx             | Position within [0, gw), AKA blockIdx.x                                                                                                                                                                                                                                                                                           |

| by             | Position within [0, <i>gh</i> ), AKA blockIdx.y                                                                                                                                                                                                                                                                                   |

| bz             | Position within [0, gl), AKA blockIdx.z                                                                                                                                                                                                                                                                                           |

| tx             | Position within [0, <i>bw</i> ), AKA threadIdx.x                                                                                                                                                                                                                                                                                  |

| ty             | Position within [0, bh), AKA threadIdx.y                                                                                                                                                                                                                                                                                          |

| tz.            | Position within [0, bl), AKA threadIdx.z                                                                                                                                                                                                                                                                                          |

| CTA<br>params  | Derived parameters from the CTA layout parameters, these are usually computed as runtime parameters.                                                                                                                                                                                                                              |

| b              | Block Size, assumes block is 1D and small ( $b \le 1024$ ),                                                                                                                                                                                                                                                                       |

|                | Typically taken directly from blockDim.x                                                                                                                                                                                                                                                                                          |

| g              | Grid Size, assumes grid is 1D and small ( $g \leq 1000$ ),                                                                                                                                                                                                                                                                        |

|           | Taken directly from either gridDim.x or *.y                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bid       | Unique 1D block ID (thread block within a grid), derived                                                                                                                 |

|           | (mapped) from $\langle gw, gh, 1 \rangle$ and $\langle bx, by, bz \rangle$                                                                                               |

| tid       | Unique 1D thread ID (thread within a thread block),                                                                                                                      |

|           | derived (mapped) from <i>(bw,bh,bl)</i> and <i>(tx,ty,tz)</i>                                                                                                            |

| warpCol   | Relative thread position within current thread warp in range                                                                                                             |

|           | [0, WarpSize) = [0, 31). Computed as                                                                                                                                     |

|           | <i>warpCol</i> = <i>tid</i> % <i>WarpSize</i> = <i>tid</i> % 32 or alternately as                                                                                        |

|           | warpCol = tid & (WarpSize-1) = tid & 31.                                                                                                                                 |

| warpRow   | Relative warp position within current thread block in range                                                                                                              |

|           | [0, <i>nWarps</i> ). Computed as                                                                                                                                         |

|           | <i>warpRow</i> = <i>tid</i> / <i>WarpSize</i> = <i>tid</i> /32 or alternately as                                                                                         |

|           | $warpRow = tid >> \log_2(WarpSize) = tid>>5.$                                                                                                                            |

| d         | Number of dimensions for <i>d</i> -dimensional points                                                                                                                    |

| d         | Digit, represents a small fixed-size numeric range $[0, d)$ . A number is represented by a string of digits (Radix Sort).                                                |

| d         | Number of bin counters (Count Histogram, Radix Sort)                                                                                                                     |

| D(n), D   | Depth, Steps, Number of parallel stages for $n$ data elements                                                                                                            |

| DBS       | Data Block Size, AKA Data (Work) per block, computed as                                                                                                                  |

|           | DBS = nWork*nWarps*WarpSize (= nWork*TBS).                                                                                                                               |

| dist(p,q) | A distance metric between two points, Euclidean distance as<br>$dist(p,q) = \sqrt{(q_1 - p_1)^2 + (q_2 - p_2)^2 + \dots + (q_d - p_d)^2}$                                |

| dv        | Digit value, specific number taken from range $[0, d)$ . A specific number is represented by a string of 1 or more specific digit values from most to least significant. |

| DWord     | 32-bit data-element (4 bytes, 2 words)                                                                                                                                   |

| f         | Fanout in a circuit (hardware adders)                                                                                                                                    |

| G         | Cycles to transfer data between global memory and registers (400-800 cycles on Fermi, 200-400 on Kepler)                                                                 |

| $h_i$     | The $i^{\text{th}}$ bin count (matching the sub-range $r_i$ )                                                                                                            |

| Ш            | Identity element, i.e., $\mathbb{I}$ is a data element under some binary operator $\oplus$ such that $a = a \oplus \mathbb{I} = \mathbb{I} \oplus a$ for all $a \in \mathbb{U}$         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IS           | The linear <i>ideal speedup</i> of a parallel computation, computed as $IS = W(n)/p$ .                                                                                                  |

| k            | Pipelined instruction-length (18-22 cycles on Fermi, 9-11 cycles on Kepler)                                                                                                             |

| k            | Number of nearest neighbors to find (kNN search)                                                                                                                                        |

| k            | Number of work items per-thread                                                                                                                                                         |

| k            | Number of thread collisions in a <i>k</i> -way bank conflict.                                                                                                                           |

| k            | Number of binning passes (Radix Sort)                                                                                                                                                   |

| k            | The maximum number of digits in a key (Radix Sort), computed as $k = \lceil \log_d m \rceil$                                                                                            |

| l            | Logic levels in a circuit (hardware adders)                                                                                                                                             |

| n            | Number of data elements in a run, warp, or array                                                                                                                                        |

| n            | Number of points (objects) in a search set (S)                                                                                                                                          |

| nWarps       | C++ parallelism parameter that tracks the number of thread<br>warps per thread block, typically set in the range [1-8] but<br>can go as large as 32 warps on current GPU architectures. |

| nWork        | C++ parallelism parameter that tracks the number of work-<br>items (data elements) assigned to each thread, typically set in<br>the range [1-8] but can go larger as needed.            |

| m            | Number of bins (frequency counts in histogram)                                                                                                                                          |

| т            | Number of data blocks, $m = \left[\frac{n}{DBS}\right]$                                                                                                                                 |

| m            | Number of points (objects) in a query set $(Q)$ .                                                                                                                                       |

| т            | Maximum number value taken from a large fixed-size numeric range $[0, m]$ .                                                                                                             |

| 0(n)         | Big "O" Notation, Asymptotic complexity of an algorithm                                                                                                                                 |

| $\mathbb{P}$ | Parallelism (work over depth), $\mathbb{P} = \frac{W(n)}{D(n)}$                                                                                                                         |

| p            | Number of parallel processors (multi-cores)                                                                                                                                             |

| p            | Number of parallel threads                                                                                                                                                              |

| point        | A <i>d</i> -dimensional point (optionally representing an object) as                                                                                                                    |

|                       | $\langle x, y, \ldots \rangle$                                                                                                                                                             |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q                     | Query set, set of points (objects) to find closest neighbors to                                                                                                                            |

| QR                    | <i>Query region</i> , a set of regions $QR_i$ (typically <i>d</i> -dimensional hyperboxes or hyperspheres) to find points (objects) that are contained in or covered by the query regions. |

| R                     | Range $R = [min, max]$ or $R = [min, max)$                                                                                                                                                 |

| R                     | Number of rows, if the number of columns ( <i>C</i> ) is fixed it can be computed as $R = [m/C]$                                                                                           |

| $r_i$                 | The <i>i</i> <sup>th</sup> sub-range, $r_i = [a_i, a_{i+1})$ from a larger range <i>R</i>                                                                                                  |

| r <sub>i</sub>        | The $i^{th}$ row from p rows in a partitioned data set                                                                                                                                     |

| $r_i$                 | The $i^{th}$ run from $p$ runs in a partitioned data block                                                                                                                                 |

| <i>r</i> <sub>i</sub> | The $i^{\text{th}}$ digit run, where the chosen digit from each key in the run matches the digit value <i>i</i> in the range [0, <i>d</i> ) (Radix Sort)                                   |

| rl                    | Run length, typically in range [1-8].                                                                                                                                                      |

| S                     | Cycles to transfer data between shared memory and registers (40-80 on Fermi, 20-40 on Kepler)                                                                                              |

| S                     | Search set, set of points (objects) to be searched                                                                                                                                         |

| S(n), S               | Steps, Number of parallel stages for $n$ data elements                                                                                                                                     |

|                       | Equivalent to concept of $Depth = D(n) = D$                                                                                                                                                |

| Si                    | The $i^{\text{th}}$ run start, taken from [0, <i>d</i> ) bins in a start histogram (Radix Sort).                                                                                           |

| Speedup               | Speedup, computed as $S = \frac{Time_{old}}{Time_{new}}$                                                                                                                                   |

| Serial                | Serial Speedup, computed as $SS = \frac{Time_{baseline}}{Time_{improved}}$                                                                                                                 |

| Parallel              | Parallel Speedup, computed as $SS = \frac{Time_{serial}}{Time_{parallel}}$                                                                                                                 |

| $SR\langle n \rangle$ | A Serial Reduce on a run of length n                                                                                                                                                       |

| $SS\langle n \rangle$ | A Serial Scan on a run of length n                                                                                                                                                         |

| SU(n)                 | A Serial Update on a run of length n (add prefix to run)                                                                                                                                   |

| t                     | Number of threads                                                                                                                                                                          |

| t                     | Number of search results (NN searches)                                                                                                                                                     |

| Т                     | Wire tracks in a circuit (hardware adders)                                                                                                                                                 |

|                       |                                                                                                                                                                                            |

| <i>T</i> <sub>1</sub> | Parallel running time on one processor for a parallel<br>algorithm, equivalent to the concept of $Work = W(n) = W$                                                                  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TBS                   | Thread Block Size, AKA threads per block, computed as <i>TBS=nWarps*WarpSize</i>                                                                                                    |

| ТС                    | Total Cycles, computed as $TC = II/IPC$ .                                                                                                                                           |

| $T_{CPU}$             | Serial running time on one processor for serial algorithm                                                                                                                           |

| $T_p$                 | Parallel running time for a fixed number of <i>p</i> processors<br>bounded by <b>Brent's Theorem:</b> $max\left(\frac{W}{p}, D\right) \le T_p \le \frac{W}{p} + D$                  |

| $T_{\infty}$          | Parallel running time for an infinite number of processors,<br>equivalent to the concept of $Depth = D(n) = D$                                                                      |

| WarpSize              | C++ parallelism parameter, used to track threads per thread<br>warp. This value is currently fixed at 32 on current GPU<br>architectures, but could change in future architectures. |

| W(n), W               | Work, Total parallel work across $p$ processors for $n$ elements                                                                                                                    |

|                       | Limit of running time for 1 processor                                                                                                                                               |

| WR <n></n>            | A Warp Reduce on a data run of length $n = [2, 4,, 32]$ .                                                                                                                           |

| WR <n></n>            | A Warp Scan on a data run of length $n = [2, 4,, 32]$                                                                                                                               |

### **1.0 Introduction**

Someone who wants to adapt a sequential program to a graphics processing unit (GPU) for better performance must learn to deal with a number of challenging problems quickly and without much training. In order to ease this process and help GPU programmers become productive more quickly, I have developed several skeletons that can be modified to fit their environment without having to come up with new code on their own. This thesis explains what these skeletons are and how they can be modified to solve real-life challenges. However, before I can explain how they help address those challenges, I must explain what those challenges are.

The next section attempts to explain in a nutshell why GPU programming is hard. New terminology employed in this section will be explained later on in context as this thesis unfolds.

### **1.1 The GPU Performance Challenge:**

**The Challenge:** GPU programmers are faced with several, complex challenges that directly affect performance. They must first understand and select serial algorithms that they can depend upon to solve their specific problems. They then must convert each single-threaded serial algorithm into an equivalent massively multi-threaded parallel algorithm<sup>1</sup> that is both correct and robust. They must carefully implement their multi-threaded solutions to prevent resource contention between threads that prevents problems such as race conditions, dead-lock, live-lock, starvation, etc. If the programmer is not careful, the overhead required to prevent resource contention can overwhelm the amount of useful work, bottlenecking performance.

<sup>&</sup>lt;sup>1</sup> Parallel algorithms are discussed in the following books and papers (Atallah et al, 2010; Blelloch and Maggs, 1996; Dongarra et al, 2003; Hillis and Steele, 1986; Hwu, editor, 2011 and 2012; Miller and Boxer, 2013; Rauber and Rünger, 2010)