# RUNTIME METHODS TO IMPROVE ENERGY EFFICIENCY IN SUPERCOMPUTING APPLICATIONS

Sridutt Bhalachandra

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2018

> Approved by: Allan K. Porterfield Jan F. Prins Stephen L. Olivier Robert J. Fowler Montek Singh

© 2018 Sridutt Bhalachandra ALL RIGHTS RESERVED

#### ABSTRACT

Sridutt Bhalachandra: Runtime Methods to Improve Energy Efficiency in Supercomputing Applications (Under the direction of Allan K. Porterfield and Jan F. Prins)

Energy efficiency in supercomputing is critical to limit operating costs and carbon footprints. While the energy efficiency of future supercomputing centers needs to improve at all levels, the energy consumed by the processing units is a large fraction of the total energy consumed by High Performance Computing (HPC) systems. HPC applications use a parallel programming paradigm like the Message Passing Interface (MPI) to coordinate computation and communication among thousands of processors. With dynamically-changing factors both in hardware and software affecting energy usage of processors, there exists a need for power monitoring and regulation at runtime to achieve savings in energy.

This dissertation highlights an adaptive runtime framework that enables processors with core-specific power control by dynamically adapting to workload characteristics to reduce power with little or no performance impact. Two opportunities to improve the energy efficiency of processors running MPI applications are identified - *computational workload imbalance* and *waiting on memory*. Monitoring of performance and power regulation is performed by the framework transparently within the MPI runtime system, eliminating the need for code changes to MPI applications. The effect of enforcing power limits (capping) on processors is also investigated.

Experiments on 32 nodes (1024 cores) show that in presence of workload imbalance, the runtime reduces Central Processing Unit (CPU) frequency on cores not on the critical path, thereby reducing power and hence energy usage without deteriorating performance. Using this runtime, six MPI mini-applications and a full MPI application show an overall 20% decrease in energy use with less than 1% increase in execution time. In addition, the lowering of frequency on non-critical cores reduces run-to-run performance variation and improves performance. For the full application, an average speedup of 11% is seen, while the power is lowered by about 31% for an energy savings of up to 42%. Another experiment on 16 nodes (256 cores) that are power capped also shows performance improvement along with power reduction. Thus, energy optimization can also be a performance optimization. For applications that are limited by memory access

times, memory metrics identified facilitate lowering of power by up to 32% without adversely impacting performance.

To my beloved family, the eternal source of my strength and inspiration.

#### ACKNOWLEDGMENTS

A dissertation is a culmination of the efforts and support of many individuals, and it is no different in my case. Many people have helped me along the way, and I would like to acknowledge and thank them for their contributions.

First and foremost, I would like to thank my advisor, Dr. Allan Porterfield for giving me the opportunity to work with him and guiding me through the process. Over the last six years, his faith and support in trying times have inspired and motivated me to put forth my best. I also had the privilege to be co-advised by Prof. Jan Prins who gave me the freedom to pursue my research with Allan, while at the same time providing invaluable support, feedback, and encouragement. I am grateful to Jan for doing everything he can to facilitate my research at the Renaissance Computing Institute (RENCI).

I thank Dr. Stephen Olivier, who has been a mentor to me since my summer internship at Sandia National Laboratories and served on my thesis committee. I am grateful to Stephen for his candid feedback and advice on both my research and professional career. I am thankful to Dr. Robert Fowler who showed faith and hired me as a Research Assistant with Allan at RENCI and provided continuous guidance. His constructive feedback as a committee member has greatly helped in improving the quality of this thesis. I also thank Prof. Montek Singh for agreeing to be on my thesis committee and for his advice and support since my first Preliminary Research Presentation and Exam (PRP).

I acknowledge and thank the countless professors, the non-teaching staff at CS department/UNC and colleagues at RENCI and other research groups and institutions. I also would like to call out the System Administrators at RENCI, Sandia, and UNC who facilitated access to various machines for experiments. I thank Dr. Barry Rountree for giving me the opportunity to be a summer intern at Lawrence Livermore National Laboratory. I acknowledge the contribution of various funding sources that have supported me – U.S. Department of Energy XPRESS project under Contract DE-SC0008704, Office of Science SciDAC SUPER Institute on grant DE-SC0006925, 2017 UNC Dr. Tom V. Morris Summer Fellowship and travel awards to conferences.

My graduate life has been enjoyable and purposeful because of the many amazing people I have met. They have contributed in different ways with some becoming friends, others mentors and a few both. I would like to thank Karthik Bangera, Ankur Bahri, Kishore Rathinavel, Diptorub Deb, Neha Gholkar, Wei Wang, Rajesh Reddy, Abhinav Golas, Anirban Mandal, Matthew Dosanjh, Noah Evans, Taylor Groves, Ryan Grant, Ronald Brightwell, Aniruddha Marathe, Tapasya Patki, Ravikiran Janardhana, Siddharth Padmanabhan, Praneeth Chakravarthula, Shubham Gupta and Ravish Mehra.

I would like to thank my family for all the love and support. My parents, Bhalachandra and Shakila, have given me more than I could have asked for. It was my father who first instilled in me the idea of pursuing a Ph.D. and gave me the freedom to chase my own dreams. My mother has always showered me with affection and helped me in every way. My mother-in-law, Pancharatna, a professor herself, empathized with the day-to-day of my graduate life and encouraged me to achieve my goals. Last but not the least, my wife, Apoorva has always been there for me and supported me in the toughest of times. It was due to her financial support and motivation that I completed my research and did not give up.

In the end, I thank my extended family and everyone else who might have contributed towards this thesis that I failed to mention.

# TABLE OF CONTENTS

| LI                  | LIST OF TABLES xiii |         |                                                             |     |  |  |

|---------------------|---------------------|---------|-------------------------------------------------------------|-----|--|--|

| LIST OF FIGURES xiv |                     |         |                                                             |     |  |  |

| LI                  | ST OF               | F ABBR  | EVIATIONS                                                   | xvi |  |  |

| 1                   | Intro               | duction |                                                             | 1   |  |  |

|                     | 1.1                 | Energy  | efficiency in High Performance Computing                    | 2   |  |  |

|                     | 1.2                 | Challer | nges and Goals                                              | 4   |  |  |

|                     | 1.3                 | Scope   | for improving energy efficiency                             | 5   |  |  |

|                     | 1.4                 | Thesis  | statement                                                   | 7   |  |  |

|                     | 1.5                 | Main F  | Results                                                     | 8   |  |  |

|                     |                     | 1.5.1   | Dynamic Duty Cycle Modulation in High Performance Computing | 9   |  |  |

|                     |                     | 1.5.2   | Adaptive Core-Specific Runtime for Energy Efficiency        | 10  |  |  |

|                     |                     | 1.5.3   | Memory-Metric Policy for Reducing Energy                    | 10  |  |  |

|                     | 1.6                 | Thesis  | Organization                                                | 11  |  |  |

| 2                   | Back                | ground  | and Previous Research                                       | 13  |  |  |

|                     | 2.1                 | Power   | consumption in a processor                                  | 13  |  |  |

|                     | 2.2                 | Proces  | sor power control                                           | 14  |  |  |

|                     |                     | 2.2.1   | Dynamic Voltage and Frequency Scaling                       | 14  |  |  |

|                     |                     | 2.2.2   | Dynamic Duty Cycle Modulation                               | 15  |  |  |

|                     |                     | 2.2.3   | Power capping                                               | 17  |  |  |

|                     |                     | 2.2.4   | Energy reduction with power controls                        | 17  |  |  |

|                     | 2.3                 | Metric  | s Measurement                                               | 19  |  |  |

|                     |                     | 2.3.1   | Running Average Power Limit                                 | 20  |  |  |

|   |      | 2.3.2   | RCRdae     | mon                                           | 20 |

|---|------|---------|------------|-----------------------------------------------|----|

|   |      | 2.3.3   | Effect of  | temperature on energy measurement             | 21 |

|   | 2.4  | Transp  | arent mon  | itoring and control of application            | 21 |

|   | 2.5  | Applic  | ations     |                                               | 21 |

|   |      |         | 2.5.0.1    | miniFE                                        | 22 |

|   |      |         | 2.5.0.2    | miniGhost                                     | 22 |

|   |      |         | 2.5.0.3    | miniAMR                                       | 22 |

|   |      |         | 2.5.0.4    | CloverLeaf                                    | 22 |

|   |      |         | 2.5.0.5    | HPCCG                                         | 22 |

|   |      |         | 2.5.0.6    | AMG                                           | 23 |

|   | 2.6  | Related | d Work     |                                               | 23 |

|   |      | 2.6.1   | Computa    | tion work-load imbalance                      | 23 |

|   |      | 2.6.2   | Waiting    | for a resource, mostly memory                 | 26 |

|   |      | 2.6.3   | Optimal    | resource utilization                          | 27 |

|   |      |         | 2.6.3.1    | Concurrency throttling                        | 27 |

|   |      |         | 2.6.3.2    | Operating under a power limit                 | 28 |

|   |      |         | 2.6.3.3    | Switching off components                      | 29 |

|   |      |         | 2.6.3.4    | Sub-section summary                           | 29 |

|   |      | 2.6.4   | Commur     | lication                                      | 30 |

|   |      | 2.6.5   | Resource   | e aware scheduling                            | 31 |

|   |      | 2.6.6   | Analysis   | , profiling and surveys                       | 32 |

|   |      | 2.6.7   | Summar     | y                                             | 33 |

| 3 | Usin | g Dynar | nic Duty ( | Cycle Modulation to improve Energy Efficiency | 36 |

|   | 3.1  | Introdu | iction     |                                               | 36 |

|   | 3.2  | Dynam   | nic Duty C | bycle Modulation in HPC                       | 37 |

|   | 3.3  | RENC    | I Workloa  | d Imbalance micro-benchmarks                  | 37 |

|   | 3.4  | The po  | licy       |                                               | 39 |

|   | 3.5  | Infrast  | ructure                                       | 42 |

|---|------|----------|-----------------------------------------------|----|

|   |      | 3.5.1    | Power Interface                               | 42 |

|   |      | 3.5.2    | MPI                                           | 43 |

|   |      | 3.5.3    | Experimental setup                            | 43 |

|   | 3.6  | Results  | 3                                             | 44 |

|   |      | 3.6.1    | Synthetic benchmarks                          | 44 |

|   |      |          | 3.6.1.1 Repeating Unequal                     | 44 |

|   |      |          | 3.6.1.2 Equally shifting load                 | 45 |

|   |      |          | 3.6.1.3 Randomly shifting load                | 46 |

|   |      | 3.6.2    | Standard benchmarks                           | 47 |

|   |      |          | 3.6.2.1 miniAMR                               | 47 |

|   |      |          | 3.6.2.2 Graph500                              | 48 |

|   |      | 3.6.3    | Platform Variation                            | 50 |

|   | 3.7  | DDCM     | l policy with full applications               | 52 |

|   |      | 3.7.1    | ADCIRC                                        | 52 |

|   |      | 3.7.2    | WRF                                           | 54 |

|   |      | 3.7.3    | LQCD                                          | 54 |

|   | 3.8  | Conclu   | sion                                          | 55 |

| 4 | An A | Adaptive | Core-specific Runtime for Energy Efficiency   | 57 |

|   | 4.1  | Introdu  | iction                                        | 57 |

|   | 4.2  | Adapti   | ng core frequency to workload characteristics | 59 |

|   |      | 4.2.1    | Working of policy with DDCM                   | 60 |

|   |      | 4.2.2    | Making the policy generic (per-core DVFS)     | 62 |

|   |      | 4.2.3    | Combined Policy                               | 62 |

|   |      | 4.2.4    | Adaptive Core-specific Runtime                | 63 |

|   | 4.3  | Infrast  | ructure                                       | 65 |

|   |      | 4.3.1    | System                                        | 65 |

|   |      | 4.3.2   | Measurement Techniques                              | 65 |

|---|------|---------|-----------------------------------------------------|----|

|   | 4.4  | Results | 3                                                   | 65 |

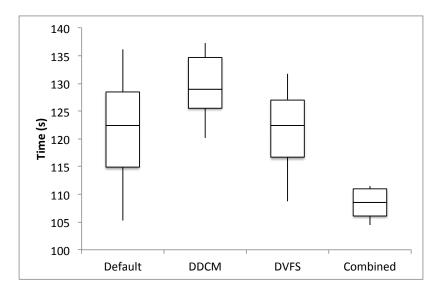

|   |      | 4.4.1   | Mini applications                                   | 66 |

|   |      | 4.4.2   | Impact of ACR user options                          | 67 |

|   |      | 4.4.3   | Mini-application Results                            | 68 |

|   |      |         | 4.4.3.1 miniFE                                      | 69 |

|   |      |         | 4.4.3.2 miniGhost                                   | 70 |

|   |      |         | 4.4.3.3 miniAMR                                     | 70 |

|   |      |         | 4.4.3.4 CloverLeaf                                  | 70 |

|   |      |         | 4.4.3.5 HPCCG                                       | 70 |

|   |      |         | 4.4.3.6 AMG                                         | 70 |

|   |      | 4.4.4   | Production applications - ParaDis                   | 71 |

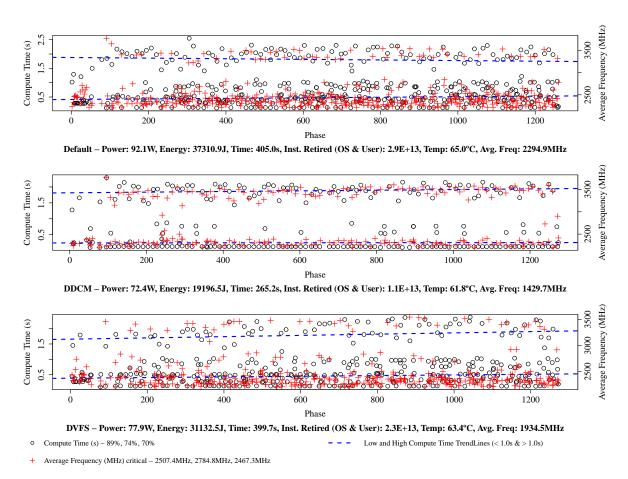

|   |      | 4.4.5   | Understanding performance improvement for ParaDis   | 72 |

|   | 4.5  | Discus  | sion                                                | 75 |

|   | 4.6  | Conclu  | sion                                                | 75 |

| 5 | Impr | oving E | nergy Efficiency in Memory-constrained Applications | 77 |

|   | 5.1  | Introdu | iction                                              | 77 |

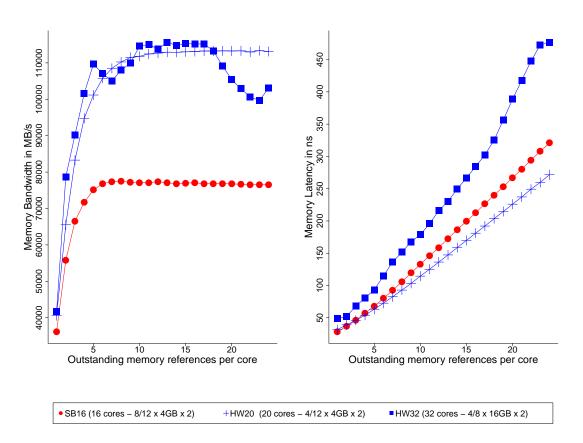

|   | 5.2  | Memor   | ry performance on modern HPC systems                | 78 |

|   |      | 5.2.1   | PCHASE Benchmark                                    | 78 |

|   |      | 5.2.2   | Experimental Setup                                  | 79 |

|   |      | 5.2.3   | Results                                             | 80 |

|   | 5.3  | Infrast | ructure                                             | 81 |

|   |      | 5.3.1   | System                                              | 82 |

|   | 5.4  | Charac  | terizing memory behavior                            | 82 |

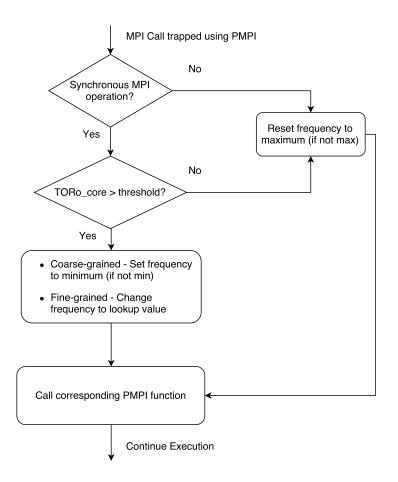

|   | 5.5  | Runtin  | ne Policy                                           | 84 |

|   |      | 5.5.1   | Coarse-grained application                          | 85 |

|   |      | 5.5.2   | Fine-grained application                            | 87 |

|    | 5.6   | Results                                                           | 88 |

|----|-------|-------------------------------------------------------------------|----|

|    |       | 5.6.1 Understanding the effects of FDP on application performance | 90 |

|    | 5.7   | Conclusion                                                        | 91 |

| 6  | Conc  | clusions                                                          | 92 |

|    | 6.1   | Summary of Results                                                | 93 |

|    | 6.2   | Limitations                                                       | 94 |

|    | 6.3   | Future Work                                                       | 94 |

| Ap | pendi | X A RENCI WORKLOAD IMBALANCE MICRO-BENCHMARKS CODES               | 96 |

| BI | BLIO  | GRAPHY                                                            | 99 |

# LIST OF TABLES

| 2.1 | Operational range of Dynamic Duty Cycle Modulation on Intel Sandy Bridge<br>micro-architecture and beyond. Older versions mostly support only eight levels |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | with a 12.5% transition step.                                                                                                                              | 16 |

| 2.2 | Classification of prior works aimed at improving energy-efficency in computing systems                                                                     | 24 |

| 3.1 | Mapping of levels to duty cycle as used in the DDCM policy                                                                                                 | 41 |

| 4.1 | Execution time and ACR parameters for all applications on 32 nodes                                                                                         | 66 |

| 4.2 | The best energy savings obtained for each application with ACR using either DDCM, DVFS or Combined.                                                        | 69 |

| 4.3 | Execution metrics for ParaDis while using ACR with DDCM, DVFS and both on 32 nodes (1024 cores)                                                            | 71 |

| 4.4 | Summary of energy savings and other metrics obtained with each policy for mini applications and <i>Paradis</i>                                             | 75 |

# LIST OF FIGURES

| 1.1  | Improving energy efficiency in a supercomputer                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Improving energy efficiency in system software                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3  |

| 1.3  | Problems addressed in this dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6  |

| 2.1  | Dynamic Duty Cycle Modulation in operation                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

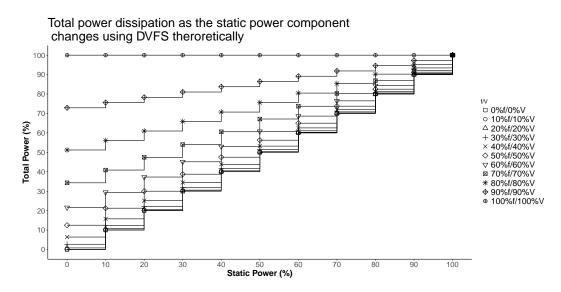

| 2.2  | Variation in total power consumption of a processor core as the static power component changes while using DVFS theoretically                                                                                                                                                                                                                                                                                                                                                      | 18 |

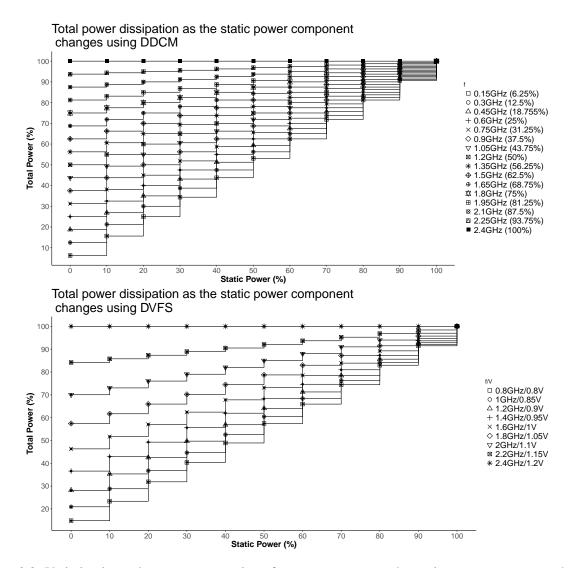

| 2.3  | Variation in total power consumption of a processor core as the static power component changes while using DDCM and DVFS                                                                                                                                                                                                                                                                                                                                                           | 19 |

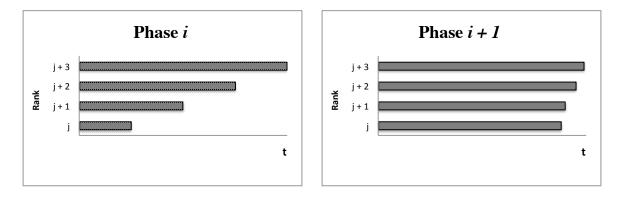

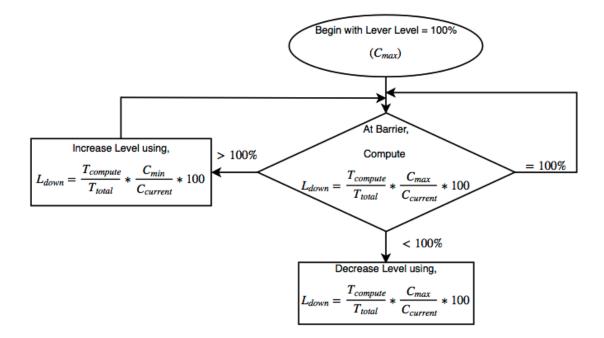

| 3.1  | (left) Each MPI process in an MPI application is observed to complete its phase $i$ in a fraction of the time in which all processes reach the barrier at the end of phase $i$ . The runtime uses this fraction to adjust the duty cycle for each process in phase $i + 1$ , according to eqns (1) and (2). (right) If the work per process is similar in phase $i + 1$ , the completion times will be more nearly equal, energy will be saved and perhaps time will be decreased. | 40 |

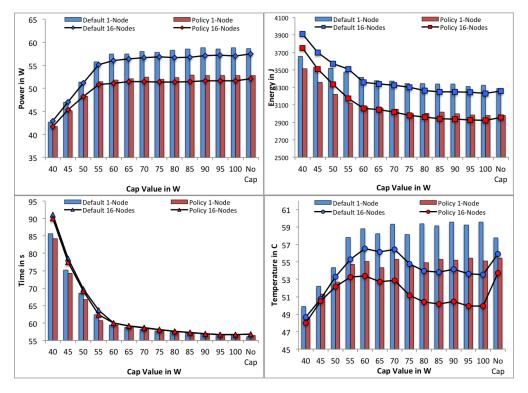

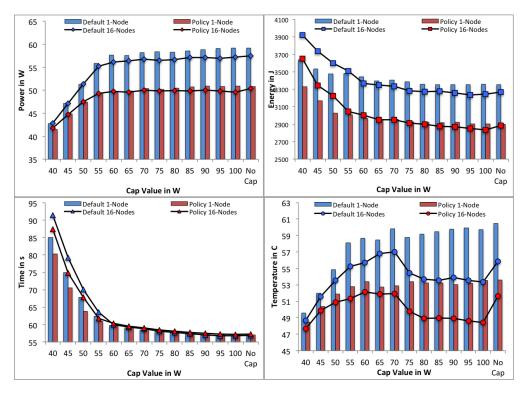

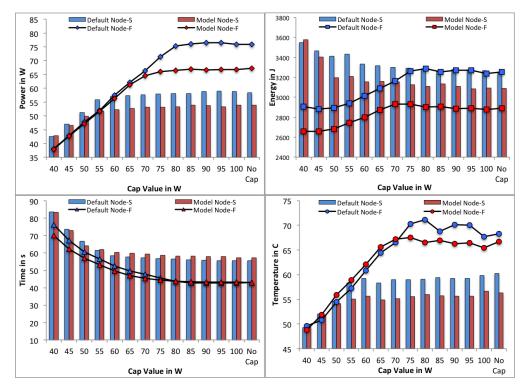

| 3.2  | Power, Energy, Time and Temperature for <i>Repeating Unequal</i> pattern                                                                                                                                                                                                                                                                                                                                                                                                           | 45 |

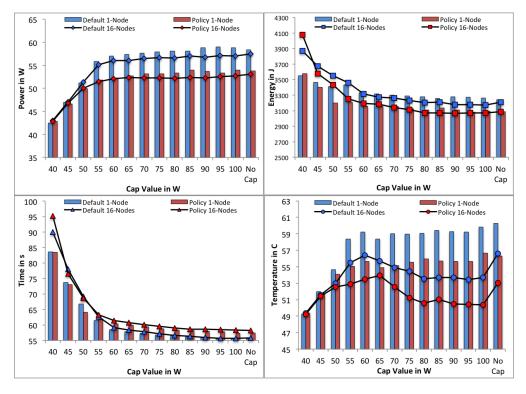

| 3.3  | Power, Energy, Time and Temperature for <i>Equally Shifting Load</i> pattern                                                                                                                                                                                                                                                                                                                                                                                                       | 46 |

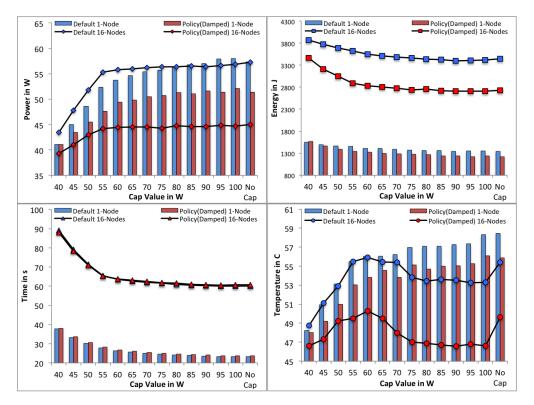

| 3.4  | Power, Energy, Time and Temperature for <i>Randomly Shifting Load</i> pattern                                                                                                                                                                                                                                                                                                                                                                                                      | 47 |

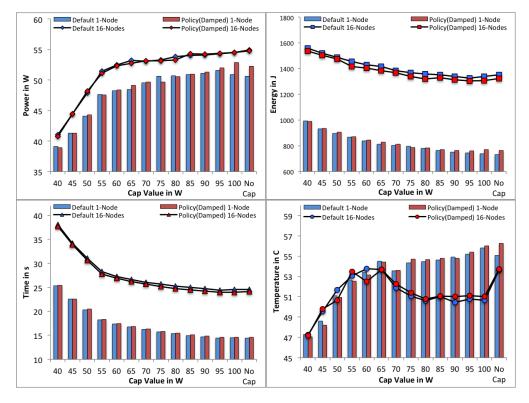

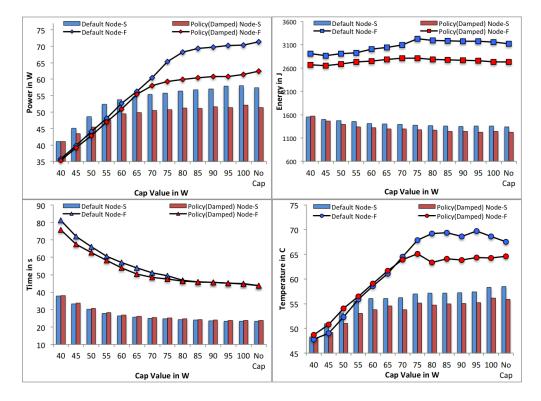

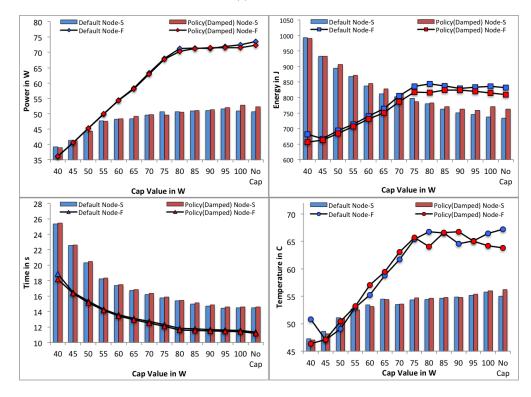

| 3.5  | Power, Energy, Time and Temperature for <i>miniAMR</i>                                                                                                                                                                                                                                                                                                                                                                                                                             | 48 |

| 3.6  | Power, Energy, Time and Temperature for <i>graph500</i>                                                                                                                                                                                                                                                                                                                                                                                                                            | 49 |

| 3.7  | The graphs show variation in power, energy and time for two different nodes while using DDCM with RMR synthetic benchmark.                                                                                                                                                                                                                                                                                                                                                         | 50 |

| 3.8  | The graphs show variation in power, energy and time for two different nodes while<br>using DDCM on mini-applications. It is observed that in every case the results<br>obtained using Node-F are superior to Node-S, suggesting the results obtained are<br>highly machine dependent and agnostic to the actual mechanism using DDCM                                                                                                                                               | 51 |

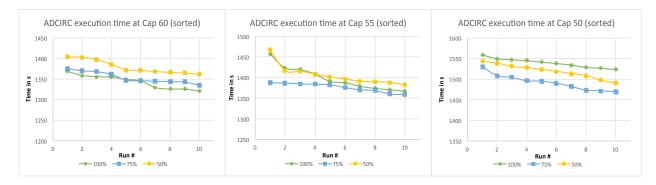

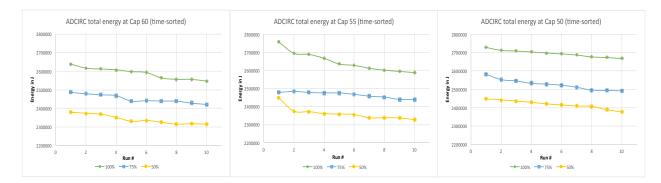

| 3.9  | Execution times for ADCIRC with combinations of power cap and minimum threshold duty cycle                                                                                                                                                                                                                                                                                                                                                                                         | 53 |

| 3.10 | Energy consumed by ADCIRC with combinations of power cap and minimum threshold duty cycle                                                                                                                                                                                                                                                                                                                                                                                          | 53 |

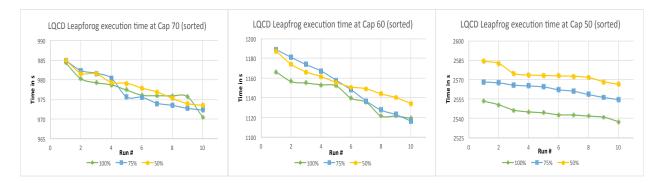

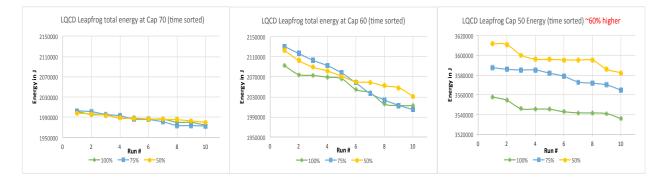

| 3.11 | Execution times for LQCD with combinations of power cap and minimum threshold duty cycle                                                                                                                                                                                                                                                                                                                                                                                           | 55 |

| Energy consumed by LQCD with combinations of power cap and minimum threshold duty cycle                                                                                                                                                                                              | 55             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

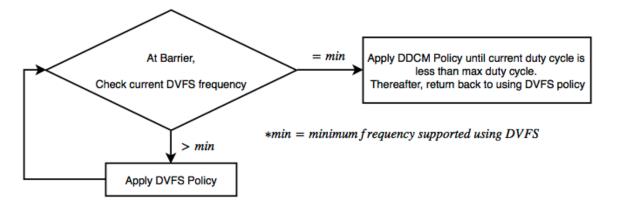

| Working of the generic core-specific adaptive runtime policy                                                                                                                                                                                                                         | 61             |

| Working of the Combined policy that uses both per-core DVFS and DDCM                                                                                                                                                                                                                 | 63             |

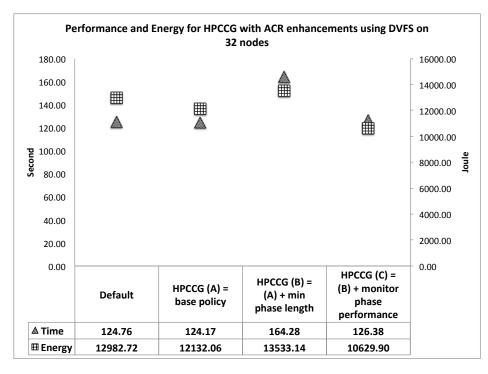

| Execution metrics showing improved effectiveness of the policy through options in ACR                                                                                                                                                                                                | 67             |

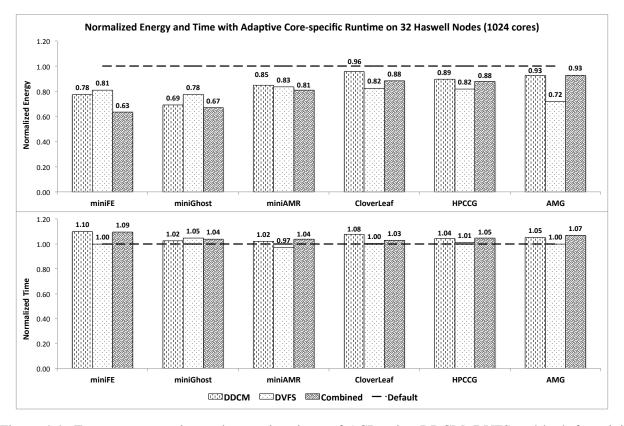

| Energy consumption and execution times of ACR using DDCM, DVFS and both for mini applications                                                                                                                                                                                        | 69             |

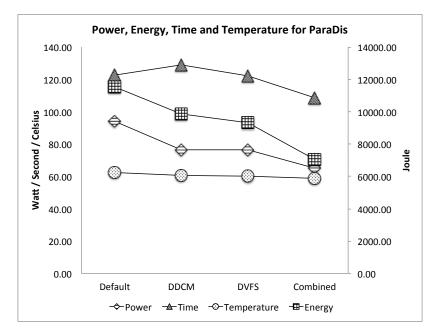

| Execution metrics for ParaDis while using ACR with DDCM, DVFS and both on 32 nodes (1024 cores). Note that the values are discrete with links only serving as visual cues.                                                                                                           | 72             |

|                                                                                                                                                                                                                                                                                      |                |

| Critical Path Behavior for <i>ParaDis</i> running on 24 nodes (768 cores)                                                                                                                                                                                                            |                |

| Memory Bandwidth & Latency using PCHASE on Sandy Bridge (SB16) and Haswell (HW20, HW32)                                                                                                                                                                                              | 80             |

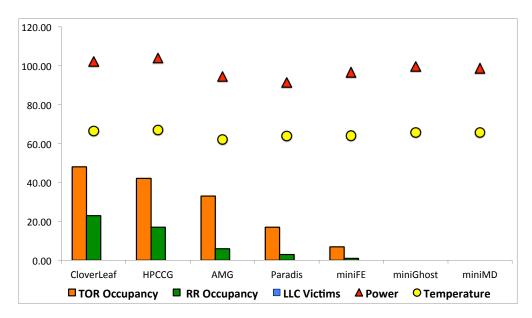

| Memory characterization of applications on 32 Haswell Nodes (1024 cores)                                                                                                                                                                                                             | 84             |

| Flowchart of the dynamic policy using TORo_core as the metric to throttle power using per-core DVFS                                                                                                                                                                                  | 85             |

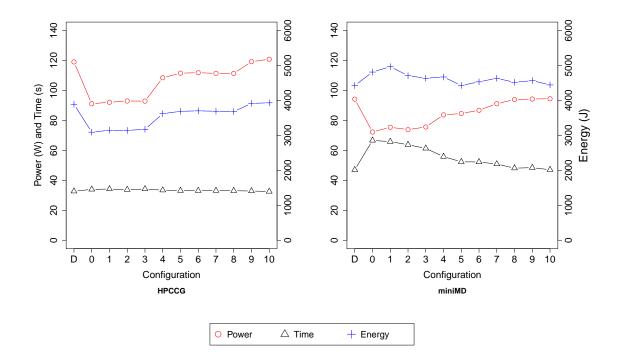

| Effect of using different TORo_core threshold values on HPCCG (memory con-<br>strained) and miniMD (compute bound) application energy and execution time<br>within coarse-grained dynamic policy (CDP). Note that the values are discrete with<br>links only serving as visual cues. | 86             |

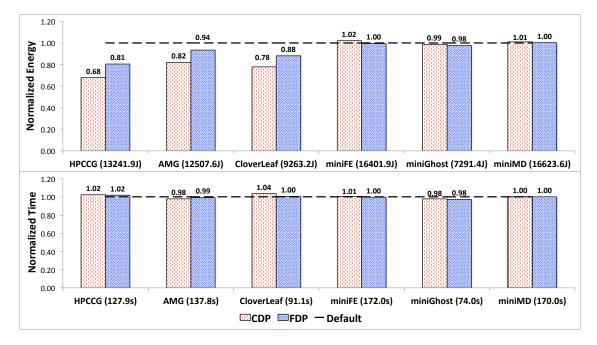

| Energy consumption and execution times using coarse (CDP) and fine-grained (FDP) dynamic policy for mini applications                                                                                                                                                                | 88             |

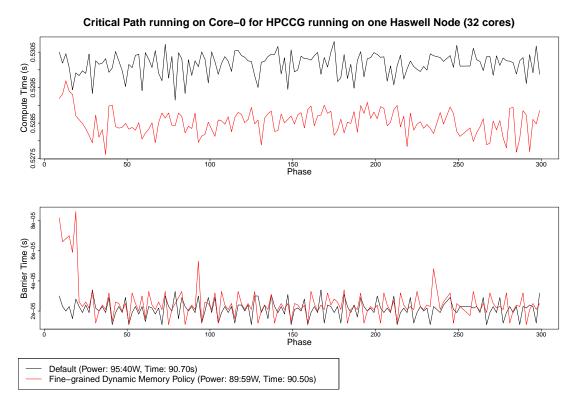

| Compute and barrier times for HPCCG using fine-grained dynamic policy (FDP) on one Haswell node (32 cores). Power consumption and total execution time for default and FDP are also shown.                                                                                           | 90             |

|                                                                                                                                                                                                                                                                                      | old duty cycle |

# LIST OF ABBREVIATIONS

| Adaptive Core-specific Runtime        |  |  |  |

|---------------------------------------|--|--|--|

| Adaptive Mesh Refinement              |  |  |  |

| Central Processing Unit               |  |  |  |

| Coarse-grained Dynamic Policy         |  |  |  |

| Dynamic Concurrency Throttling        |  |  |  |

| Dynamic Duty Cycle Modulation         |  |  |  |

| Dynamic Random Access Memory          |  |  |  |

| Dynamic Voltage and Frequency Scaling |  |  |  |

| Fine-grained Dynamic Policy           |  |  |  |

| High Performance Computing            |  |  |  |

| Last Level Cache                      |  |  |  |

| Message Passing Interface             |  |  |  |

| Model Specific Register               |  |  |  |

| Operating System                      |  |  |  |

| Profiling Message Passing Interface   |  |  |  |

| Resource Centric Reflection           |  |  |  |

| Running Average Power Limit           |  |  |  |

| Thermal Design Power                  |  |  |  |

| Table Of Request                      |  |  |  |

| Table Of Request Occupancy            |  |  |  |

|                                       |  |  |  |

#### **CHAPTER 1: Introduction**

In the past few decades advances in large-scale computing have revolutionized many basic fields of science. The impact of this progress however, has not been restricted to the fields originally intended, but has helped to lay the foundations of an age centered around information and technology. In a large-scale computer a massive number of parallel processors work together to solve a problem in a fraction of time it would take on a single processor. Suppose a processor takes at least time *t* to solve a problem (sequential solution), then a parallel solution utilizing *p* processors can improve the sequential solution by at most a factor of p – Fundamental Law of Parallel Computation (Gustafson, 1988).

Traditionally, the scientific and commercial problems that used large-scale computing were called compute-bound problems since I/O bound problems involving massive data were more conducive to better data transmission technology than processing capability. In recent times however, more and more scientific problems require the aid of efficient memory sub-systems and I/O capabilities to be solved with closer to peak performance on modern HPC systems. This makes achieving high performance even more challenging in current supercomputers as a poor provisioning can lead to very low percentages of peak performance attainable.

The compute-bound problems are generally superlinear, typically exhibiting sequential time complexity in the range  $O(n^2)$  to  $O(n^4)$  for problems of size n. The reason  $O(n^4)$  problems are common in science and engineering is that they often model physical systems with three spatial dimensions developing in time, for example a storm surge. A frequent challenge with these problems is not to solve a fixed-size instance of the problem faster, but rather to solve larger instances within a fixed time budget. Using this understanding along with the Fundamental Law of Parallel Computation, Lawrence Snyder (Snyder, 1986) observed that superlinear problems can be improved only sublinearly by parallel computation. Thus, parallel computation only offers modest potential benefit – Corollary of Modest Potential. This corollary along with the increasing complexity in current High Performance Computing (HPC) systems further mandates a need for efficiency in parallel systems as technological advancements are approaching their inevitable physical limits.

## 1.1 Energy efficiency in High Performance Computing

Advances in many branches of science and engineering increasingly depend on ever larger and more detailed numerical simulations performed on high performance computing (HPC) systems. The days of ever increasing single core performance have, however, come to an end as power dissipation and transistor scaling are reaching fundamental limits. With  $10^5$  parallel processors now present in top supercomputers, power consumption is increasingly becoming the limiting factor. These machines, with an aggregate performance of  $10^{15}$  (Peta) floating point operations per second (FLOPS), already consume in excess of 15MW (Fu et al., 2016), with energy costs of over \$10M dollars a year. To make the next generation of supercomputers feasible, the Exascale Computing study (Kogge et al., 2008) set a definitive power challenge to deliver exaFLOPS using just 20 MW. A commensurate increase in power is no longer feasible with the performance needing to improve over 10x, while power less than doubles.

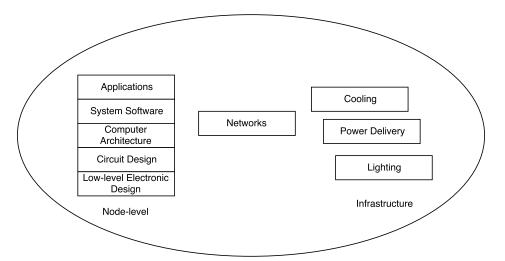

Figure 1.1: Improving energy efficiency in a supercomputer

The scope for improving energy efficiency of a supercomputer exists at many levels as shown in Figure 1.1. The hardware community is exploring alternative technologies like dark silicon to improve chip efficiency, while also investing time and energy to come up with better micro-architectures, interconnects, memory technologies among countless other improvements. The infrastructure research is focussing on designing energy-efficient buildings, power delivery infrastructure and cooling solutions to name a few. A lot can be achieved on the software side within a node to bridge the gap. HPC applications more often than not exhibit workload imbalances, wait on memory or poorly utilize the available resources like Central Processing

Unit (CPU), memory and network. These in-efficiencies present numerous opportunities to improve energy efficiency in system software.

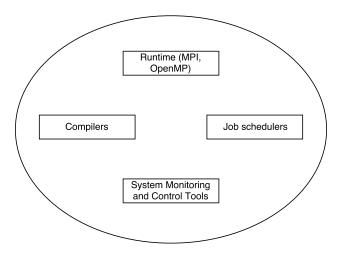

Figure 1.2: Improving energy efficiency in system software

In software (Figure 1.2), multiple hardware components like CPU, memory, storage and network interfaces can be targeted within a conventional compute node of a supercomputer to improve energy efficiency. Graphics Processing Units (GPU) too are making their way into newer systems and consume large portion of the energy budget. Network fabric, interconnects, switches and other components outside of a node too can be controlled through software. With more than 30% of energy being consumed in both idle and active operations (David et al., 2010), CPU is an ideal target for efforts involving software energy efficiency research.

With tighter power budgets likely in the near future, HPC researchers are searching for ways to improve performance with the available power budget. *Overprovisioning* of processor nodes (Patki et al., 2013; Sarood et al., 2014; Marathe et al., 2015; Gholkar et al., 2016) using hardware enforced power bounds is one likely alternative. An overprovisioned system is a system with more capacity (nodes), with the stipulation that we cannot simultaneously power all components at peak power because of strict power constraints. The maximum power budget is then met with additional nodes (with attendant memory and bandwidth) by constraining power for each node below the Thermal Design Power (TDP). This allows a greater number of nodes to be run than normally possible at peak power. In an overprovisioned system, improvements in energy efficiency increase performance by allowing more nodes or a higher effective power limit on actives node without exceeding the power cap. Increased power cap on the active nodes may also lead to improved performance as the cores can potentially run faster. The effect is improvement in the throughput of the system.

#### **1.2 Challenges and Goals**

Energy efficiency of computations can be improved by completing a computation in less time or by running the computation at lower power. The state-of-the-art of processor energy savings techniques mainly address problems arising from uneven work distribution, waiting on a resource, mostly memory and poor resource utilization. However, the techniques still faces many challenges:

**Static Analysis.** Many related studies (Feng et al., 2005; Kamil et al., 2008; Huang and Feng, 2009) make use of static analysis of programs/applications to determine optimal frequency for an application execution. Though these techniques provide useful insights, they are not always accurate as it is difficult to statically predict behavior of a running application as the system factors can change dynamically. As making actual test runs on production machines can be expensive, many a times synthetic benchmarks are used to obtain parameters for static analysis. Such benchmarks may not always be representative of actual application runtime conditions as energy usage of a processor depends both on physical and software factors that are dynamic. Physical variations arise during the fabrication process and induce variations in performance among otherwise identical processors (Rountree et al., 2012). Placement of components can induce variations are mainly due to varying data locality, compiler optimizations, and the number of threads utilized. These variations are 20% in general and in the extreme case over 2x (Porterfield et al., 2013b). External factors like cooling also contribute to the variation in energy consumed by an application. These variations suggest a need for dynamic power regulation to achieve savings in energy.

**Code instrumentation.** Many solutions (Ge et al., 2005; Wang et al., 2015) require changes in application code to support instrumentation. While feasible for small experimental codebases, this is a serious problem for production applications involving several decades of software development. Moreover, the addition of complex instrumentations and logic to an application code can affect the performance characteristics and program flow. This necessitates making the solution transparent to the application, and also simple.

**Simulation and synthetic benchmarks.** Many results (Hsu and Feng, 2005; Kandalla et al., 2010; Rountree et al., 2012; Livingston et al., 2014) are simulated or use synthetic benchmarks. Simulations provide extremely useful insights on systems that are not readily accessible and as a preliminary work pave the way for better solutions. The dynamic nature of HPC systems and applications however, make actual application run results not always conform to the results from simulation. The results from synthetic benchmarks like NAS are

useful as preliminary results, but are not always representative of actual HPC workloads. Therefore, there is a need for research that show results on mini-apps and real-world applications.

**Chip-wide effect of power control.** Most research (Kappiah et al., 2005; Rountree et al., 2009; Ge et al., 2007; Freeh and Lowenthal, 2005) to regulate energy and performance in CPU have revolved around chipwide Dynamic Voltage and Frequency Scaling (DVFS). Chip-wide DVFS is not used in production HPC because it is difficult to find applications where slowing the entire multi-core processor does not result in noticeable slowdowns. Until recently<sup>1</sup>, DVFS has only allowed frequency and voltage changes that applied to all the cores of a multi-core processor. Slowing the critical path slows execution. Thus, DVFS-centric research has focused on finding situations where the slowdown is greatly outweighed by the energy savings. This chip-wide effect limits the effectiveness of DVFS to be used for fine grained control. The use of chip-wide DVFS also restricts access to higher turbo frequencies for the critical core (core whose performance determines the performance of the application). Chip-wide DVFS can save energy but slows applications, a side-effect unacceptable for most HPC systems as the primary intent of these supercomputers is to improve performance.

#### **1.3** Scope for improving energy efficiency

With the introduction of core-specific voltage regulators in Intel Haswell microarchitecture, new options for software energy control are now available. Each physical core (or 2 logical cores if using Hyper-Threading) can be independently controlled allowing only non-critical threads to have their frequency reduced in software using runtimes like the one discussed in this dissertation. In addition to DVFS, core-specific Software Controlled Clock Modulation has been supported by Intel since Pentium. The effective core frequency is adjusted nearly instantaneously by gating only a fraction of the clock cycles to that core. We call this approach Dynamic Duty Cycle Modulation (DDCM), given that the objective is to match duty cycle of the core to its work dynamically. The fine-grained control allows DDCM to save power effectively for unbalanced applications. As voltage regulators are unaffected, changing clock frequency with DDCM requires less work (and time) than with DVFS (Wang et al., 2015).

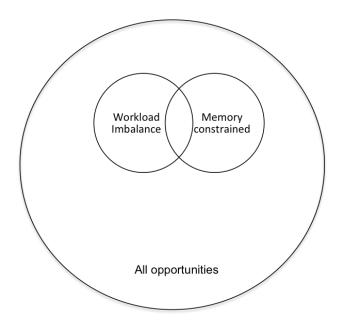

This dissertation identifies two opportunities (Figure 1.3) to improve energy efficiency in CPU - *computational workload imbalance* and *waiting for a resource, mostly memory*.

<sup>&</sup>lt;sup>1</sup>Intel Haswell architecture introduced core specific voltage regulators that allow per-core frequency control.

Figure 1.3: Problems addressed in this dissertation

**Computational workload imbalance:** Multi-core CPUs often have load imbalances between their cores. Applications can have fixed loads or the amount of work can vary between steps. Most HPC applications use parallel programming paradigms that use barriers. A processor that has been allocated less work may finish work faster, but still it has to wait for all other processors to proceed further. Nominally homogeneous computing elements exhibit heterogeneous performance and limiting power increases the performance variation (Porterfield et al., 2015). Transistor thresholds and leakage currents vary within and between wafers during fabrication, resulting in processor chips that require different supply voltages to operate at the design frequency and that therefore consume different amounts of power. Furthermore, the amount of cooling available to a chip depends on its position in the system, resulting in temperature differences that cause additional variations in power consumption in many air-cooled HPC systems. Power and thermal constraints will affect each chip differently causing on-chip mechanisms that control operating frequency to also vary. Performance will thus vary between sockets for even perfectly balanced parallel applications.

Waiting on memory: HPC applications need access to memory often, and sometimes even I/O. Disparity between CPU and memory speeds and the latency of accessing DRAM across the system bus contribute significantly to CPU cycling while waiting on memory and wasting power. Memory operations are not operating system (OS) visible and coarse-grained enough for the hardware circuitry to stall (or switch off) cores and reduce power as memory accesses are serviced without any information from runtime/application.

The hardware circuitry needs the core to idle for a certain amount of time (be coarse-grained enough) before it can be put into a sleep state. The amount of idle time required by the circuity is not always met in the case of HPC applications where the computation and memory sections are mostly alternating in bursts or could even overlap. However with smaller idle times too, there exist opportunities to slow down the CPU and reduce power in software using application-specific information. Also, for certain classes of HPC applications that are memory-bound, reducing the processor speed or using related approaches like CPU throttling for power savings has shown little adverse impact on performance, or in some cases slightly speeds up execution from reduced contention (Porterfield et al., 2013b; Wang et al., 2015).

In this research, the above two problems have been addressed in the Message Passing Interface (MPI) (Gropp et al., 1996) runtime from the available avenues shown in Figure 1.2. MPI includes protocols and semantic specifications for how its features must behave in any implementation. MPI is considered a *de facto* standard for communication among processes of a program that run on a distributed memory system. The following broad considerations have been made in our implementation for MPI:

- Only pure MPI applications with one process per core are targeted. The techniques presented have not be validated on hybrid programming models that use other shared-memory paradigms like OpenMP in addition to MPI (No MPI+X).

- 2. The runtime policies and framework have been tested and use features specific to Intel processors. Many of these techniques should be suited for processors from other vendors like IBM, AMD and others.

- 3. The techniques discussed have not been evaluated on hardware accelerators like Intel Xeon Phi, Fieldprogrammable gate arrays (FPGAs) or GPUs.

These considerations serve as basis for future work as we move towards exascale computing. Any other specific assumptions are addressed when relevant.

## 1.4 Thesis statement

Measurements and controls local to each core in a multi-core system can on average reduce power consumed by large supercomputing applications at runtime while having little or no adverse impact on execution times. To prove this thesis, we design and evaluate runtime methods that use measurements and controls local to each core to adapt the power consumption to the workload characteristics. The runtime methods dynamically identify scenarios exhibiting computational workload imbalance and/or memory-constrained behavior and improve energy-efficiency both on conventional and power-limited systems. The research in this dissertation differs from prior work by employing adaptive methods at runtime, and core-specific power controls that have not been readily applied to the above two scenarios. An adaptive runtime framework (MPI shim library) transparent to the application consisting of runtime techniques and user options is developed allowing processors to reduce power with little performance impact. Different core-specific power controls can be employed separately or combined to enhance effectiveness of the framework. In the view of strict power and energy budgets to control the operating costs of supercomputer centers in the future, the effect of enforcement of power limits by external agents on application performance is also studied. For applications with memory related issues, memory metrics that facilitate lowering of power without adversely impacting performance are identified.

# 1.5 Main Results

The goal of this research is to explore and evaluate methods that improve energy efficiency of HPC applications at runtime. Specifically, the focus is on using core-specific power controls available in recent processor architectures. The major work and ideas in this dissertation are as follows:

- Dynamic Duty Cycle Modulation in High Performance Computing: DDCM is shown to be an alternative to save energy, and improve performance in power-capped environments. The fundamental weaknesses of socket-wide DVFS can be overcome with DDCM as it has a per-core control with lower overheads allowing fine-grained core-specific clock frequencies. With power limits on a system, slowing non-critical cores in software is shown to increase the available thermal headroom to the critical core improving performance.

- Adaptive Core-Specific Runtime (ACR) for Energy Efficiency: The ACR showcased allows processors with core-specific power control to reduce power with little performance impact by dynamically adapting core frequencies to workload characteristics. Such a runtime could help alleviate heterogeneous processor loads that many future exascale applications will likely have. The MPI framework (shim

library) is transparent to application eliminating any code changes and allows use of multiple power controls (DDCM, per-core DVFS or both).

• Memory-Metric Policy for Reducing Energy: The presented characterization of HPC applications identifies a metric that conforms to the memory behavior exhibited by many HPC mini-apps and can be used to construct dynamic runtime polices improving energy efficiency.

We next summarize the results of the research presented in this thesis:

#### 1.5.1 Dynamic Duty Cycle Modulation in High Performance Computing

On Intel processors before Haswell, Dynamic Voltage and Frequency Scaling (DVFS) affects all cores of a multi-core processor. Slowing the critical path slows execution. DVFS-centric research has focused on finding situations where the slowdown is greatly outweighed by the energy savings. Intel also supports Dynamic Duty Cycle Modulation (DDCM) where the effective frequency of each core can be adjusted nearly instantaneously by only gating a fraction of the clock cycles to that core. We show DDCM as an alternative to improve energy-efficiency, and performance in power-capped environments. An adaptive runtime DDCM policy is developed to reduce power in unbalanced MPI applications (Bhalachandra et al., 2015).

On Sandy Bridge systems, the adaptive DDCM policy for MPI was run on synthetic benchmarks and mini-apps – *miniAMR* and *graph500* on single and 16-node configurations. DDCM saved up to 13.5% processor energy on one node and 20.8% (for *miniAMR* with slowdown of less than 1%) on 16 nodes. By applying a power cap, DDCM effectively shifts power consumption between cores and improves overall performance. Performance improvements of 6.0% and 5.6% on one and 16 nodes, respectively, were observed. Saving energy in power-limited systems is also seen to improve performance.

The policy was then validated with production applications like *ADCIRC*, *WRF and LQCD* (Porterfield et al., 2015). For *ADCIRC* on 16 nodes, energy savings of over 10% with only a 1-3% slowdown is obtained. With a power limit of 50W, one version of the policy executes 3% faster while saving 6% in energy, and a second version executes 1% faster while saving over 10% energy. The effectiveness of DDCM is also shown for OpenMP by *Wang et al., 2015*<sup>2</sup> with savings of 21% in energy and improvement of energy-delay product (EDP) by 16%. With encouraging results on both shared and non-shared memory as well as production applications, DDCM is seen to be a viable alternative to achieve energy efficiency in HPC.

<sup>&</sup>lt;sup>2</sup>Emphasized citations denote works including me as one of the authors, but not first author

#### 1.5.2 Adaptive Core-Specific Runtime for Energy Efficiency

With addition of core-specific voltage regulators in Intel Haswell, DVFS can now slow down only non-critical cores like DDCM. An Adaptive Core-specific Runtime (ACR) that allows processors with core-specific power control to reduce power with little performance impact by dynamically adapting core frequencies to workload characteristics is developed. A policy to combine the benefit of larger power reduction with DVFS owing to reduction in both voltage and frequency, and the ability of DDCM to lower the frequency beyond the operating range of DVFS is also presented (Bhalachandra et al., 2017a).

This work highlights a generic policy that effectively utilizes core-specific power controls. Our previous work (Section 1.5.1) aimed only at showing the efficacy of DDCM as an alternative to socket-wide DVFS. However, the present work offers a context for comparing DDCM (with its simple per-core hardware implementation and fast switching capability) and DVFS (more complex and costly to implement per-core but with potential for greater savings), and for showing how and when they can be used together. A transparent adaptive runtime framework (library) is implemented that throttles frequencies of cores not on the critical path of an MPI application using either DDCM, per-core DVFS or both.

The framework is validated using six mini-apps (*miniAMR*, *miniFE*, *CloverLeaf*, *HPCCG*, *AMG*, *miniGhost*), and a real world application, ParaDis. The evaluation shows an overall 20% improvement in energy efficiency with an average 1% increase in execution time on 32 nodes (1024 cores) using per-core DVFS. An improvement in energy efficiency of up to 39% is obtained with the real world application ParaDis through a combination of speedup (11%) and power reduction (31%). The average improvement in performance seen is a direct result of the reduction in run-to-run variation and running at turbo frequencies.

As Exascale deploys over-provisioned systems that use per core power-limits in day-to-day operations, energy optimizations will be more important. Runtimes such as ACR will either allow more work to be run at one time by using less power or allow single applications to be run faster by allowing a higher power cap on critical cores than non-critical.

# 1.5.3 Memory-Metric Policy for Reducing Energy

HPC would have been much easier if all the data required could fit in the cache of a processor, but rarely is this true. For certain classes of applications that heavily utilize the memory sub-system, slowing the processor speed or related approaches like CPU throttling has shown little impact on performance, with some cases showing performance improvement (Wang et al., 2015; Porterfield et al., 2013b). There exists a need for solutions that can dynamically identify such opportunities. Toward this end, we identify metrics to detect applications that are constrained by memory and build an adaptive runtime policy using one of these metric to reduce energy wastage (Bhalachandra et al., 2017b).

We present an experimental memory study on modern CPU architectures, Intel Sandy Bridge and Haswell, to identify opportunities to reduce CPU frequency. Since the Last Level Cache (LLC) is shared, each core has to create a request for a particular memory location that is not in its private cache into the Table of Requests (TOR). Using uncore performance monitoring hardware counters, we identify a metric, *TORo\_core*, that captures all valid requests in TOR. This metric detects bandwidth saturation and increased latency in the memory system, and is used in a dynamic policy to modulate per-core power controls.

The policy is evaluated when applied at coarse and fine-grained levels on six MPI mini-applications. The best energy savings with the coarse and fine-grained application of the dynamic policy is 32.1% and 19.5% respectively with a 2% increase in execution time in both cases. On average, the fine-grained dynamic policy yields a 1% speedup while the coarse-grained dynamic policy yields a 3% slowdown.

## 1.6 Thesis Organization

The rest of the dissertation is organized as follows:

- In **Chapter 2**, the fundamentals of power consumption and control in processor are provided along with a literature review of the prior energy-efficiency techniques, and existing work in the area of runtime optimization for energy.

- **Chapter 3** introduces the policy for using DDCM in presence of unbalanced workloads. The chapter discusses the different steps of the technique, provides implementation details, and presents the results and analysis. It also discusses the results on power-limited systems

- In **Chapter 4**, the DDCM policy is extended to work with core-specific DVFS. Further, a combined policy that uses both DDCM and core-specific DVFS is introduced. An adaptive core-specific runtime is showcased for integrating these policies with user options. It is also shown how optimizing for energy can improve performance

- **Chapter 5** starts with the memory performance study on modern HPC systems. Next, it discusses the characterization of memory activity using LLC counters and presents results for dynamic policies using a LLC metric to reduce power without adversely affecting performance.

- Chapter 6 concludes the thesis and discusses avenues for future work.

## **CHAPTER 2: Background and Previous Research**

This chapter provides background information about power and energy consumption and control, and introduces the tools and techniques used in this dissertation such as metric measurement tools, and energy control methods. Also, this chapter provides a literature review of the field of Energy Efficient HPC (EEHPC).

#### 2.1 Power consumption in a processor

The power consumption of a modern processor has two key components: static and dynamic (Brooks et al., 2000; Weste and Harris, 2015).

$$P_{total} = P_{static} + P_{dynamic} \tag{2.1}$$

Static power (Idle power) corresponds to the minimum amount of power that is required to turn on and run a processor without active computation/load. As a processor is made up of transistors, the static power dissipation depends on the voltage applied ( $V_{dd}$ ) and the leakage current ( $I_{leakage}$ ) in the transistors as

$$P_{static} = V_{dd} \times I_{leakage} \tag{2.2}$$

The leakages mainly occur at gates and junctions, with additional subthreshold leakage through OFF transistors. There is a small amount of static dissipation due to contention current.

When a computation is run on a processor, dynamic power is consumed due to the transistors constantly switching states. How often the transistors switch state depends on the frequency (f) at which the processor operates. While switching states, the transistors with capacitance, C are charged from a 0 to 1 or vice versa using the supply voltage, V. The dynamic power dissipation is given by

$$P_{dynamic} = ACV^2 f \tag{2.3}$$

A is known as the activity factor, denoting how often the transistors are active. In addition to above, there is a small contribution of short-circuit power in the circuit towards dynamic consumption.

#### 2.2 Processor power control

In this section, we look at the different power control mechanisms available.

# 2.2.1 Dynamic Voltage and Frequency Scaling

The processor power consumption as explained in Section 2.1 depends on the operating frequency (f) and the supply voltage (V) of the processor. Intuitively, one can control the processor power by controlling either the V, f or both. For reliable operation at a given frequency f however, there is a minimum voltage V that is required (varies by chip); making V not readily modifiable during operation without changing f. Therefore, the power consumption is controlling f and thereby, scaling V. This technique is commonly referred to as Dynamic Voltage and Frequency Scaling (DVFS).

For controlling power using DVFS on a Linux based system, the *acpi-cpufreq* or other applicable kernel modules requiring root privileges need to be loaded with only a limited set of frequency/volt-age pairs supported. To change or read the supported frequencies thereafter from the */sys/devices/sys-tem/cpu/cpu\*/cpufreq/scaling\_available\_frequencies* file no root permissions are needed, though the cpufreq governor needs to be set to *userspace*. The other governors generally supported are conservative, ondemand, powersave, and performance Users change the value of frequency by writing the desired frequency value to the */sys/devices/system/cpu/cpu\*/cpufreq/scaling\_setspeed* file. In case hyper-threads are enabled, both the threads need to be set to the same frequency for the DVFS to take effect.

DVFS has facilitated cubic reduction in the dynamic power dissipation with decrease in f taking advantage of Dennard scaling (Dennard et al., 1974) in the past. As the V depends on the current f

$$V \propto f$$

(2.4)

Using this in Equation 2.3 gives

$$P_{dynamic} \propto f^3$$

(2.5)

Because of hardware limitations to date, DVFS research has impacted all of the cores on a multi-core processor and potentially slowed the critical path. Thus, the research has focused on finding situations where the slowdown is greatly outweighed by the energy savings. Dennard scaling however, is running into limits as feature sizes and voltages decrease. As transistor sizes decrease, static losses become a significant fraction of the total power utilized and undermine the power savings, while lower voltages interfere with reliable operation (Esmaeilzadeh et al., 2011). This makes possible reduction in power using DVFS much lesser than theoretically possible. The chip-wide effect of DVFS also made effective fine-grain control of performance difficult. Therefore, there had been a need for core-specific implementation of DVFS.

With the introduction of per-core specific voltage regulators in Intel Haswell (Kurd et al., 2015; Hammarlund et al., 2014), DVFS has been made core-specific to facilitate new options for software energy control. Each physical core (or 2 logical cores if using Hyper-Threading) can be independently controlled allowing only non-critical threads to have their frequency reduced. Core-specific DVFS is also supported in IBM Power8 (Fluhr et al., 2014).

#### 2.2.2 Dynamic Duty Cycle Modulation

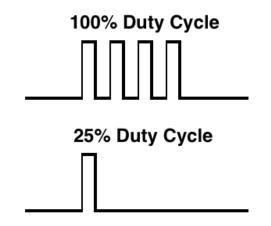

Dynamic Duty Cycle Modulation (DDCM) has been supported in Intel processors since Pentium as Software Controlled Clock Modulation, and is core-specific. For each core some percentage of the clock signals can be gated with rest of the hardware skipping that cycle. Figure 2.1 shows the working of DDCM.

Figure 2.1: Dynamic Duty Cycle Modulation in operation

The top sub-figure shows the normal operation where 100% of the cycles generated by the clock is applied to the CPU. The bottom half shows one out of four (25%) of clock cycles generated applied to the CPU.

Power is dissipated in the processor core only during the active cycles. As the clock pulse is the same width even when few of the cycles are gated, the voltage required remains same to ensure reliable operation. The power reduction is thus a function of only the number of cycles gated (effective frequency). The stop-clock duty cycle is controlled with the IA32\_CLOCK\_MODULATION Model Specific Register (MSR) found in /dev/cpu/cpu\*/msr file using rdmsr and wrmsr operations, and requires root access on a Linux system. The need for root access at application level can be overcome using libraries like msr-safe (Shoga et al., 2014). The MSR kernel module needs to be loaded however, to make any changes to the MSR file.

| Duty Cycle Level | Binary | Decimal | Hexadecimal | Effective Frequency |

|------------------|--------|---------|-------------|---------------------|

| 1                | 10001B | 17      | 11H         | 6.25%               |

| 2                | 10010B | 18      | 12H         | 12.50%              |

| 3                | 10011B | 19      | 13H         | 18.75%              |

| 4                | 10100B | 20      | 14H         | 25%                 |

| 5                | 10101B | 21      | 15H         | 31.25%              |

| 6                | 10110B | 22      | 16H         | 37.50%              |

| 7                | 10011B | 23      | 17H         | 43.75%              |

| 8                | 11000B | 24      | 18H         | 50%                 |

| 9                | 11001B | 25      | 19H         | 56.25%              |

| 10               | 11010B | 26      | 1AH         | 63.50%              |

| 11               | 11011B | 27      | 1BH         | 69.75%              |

| 12               | 11100B | 28      | 1CH         | 75%                 |

| 13               | 11101B | 29      | 1DH         | 81.25%              |

| 14               | 11110B | 30      | 1EH         | 87.50%              |

| 15               | 11111B | 31      | 1FH         | 93.75%              |

| 16               | 00000B | 0       | 00H         | 100%                |

Table 2.1: Operational range of Dynamic Duty Cycle Modulation on Intel Sandy Bridge micro-architecture and beyond. Older versions mostly support only eight levels with a 12.5% transition step.

On the Sandy Bridge architecture, the effective frequency of the clock can be reduced to 1/16th of the actual frequency. It is controlled by a 4-bit counter which allows clock rates evenly spaced between 6.25% and 100% (Table 2.1). The hardware implementation could be only a few instructions making the latency very low. Low latency facilitates dynamic fine-grain use. Since the actual clock rate is not changed, other hardware options like DVFS and TurboBoost are still operational, and can be combined with duty cycle modulation.

The duty cycle is set for a single clock domain, normally a single core. The major benefit of DDCM is that it allows each clock domain to be set to different duty cycle, thus a multi-core processor can have

different frequencies active on each core. Consequently, a critical thread can run faster than a waiting thread. Duty cycle modulation does not modify the voltage or the clock for shared regions of the processor. The energy savings are less than DVFS at the same clock rate, since less of the system is impacted. But, it can reduce the clock rate down to 6.25% which is much lower than the minimum frequency obtainable with DVFS.

#### 2.2.3 Power capping

Sandy Bridge and later architectures contain MSR\_PKG\_POWER\_LIMIT in the RAPL Interface (Section 2.3.1), that sets a hardware enforced power limit for the chip. The hardware enforces an adjustable chip-wide average power over a given time period and is used to set the power cap (Intel, 2015a). The user specifies a time window and a maximum average power for that window and the processor guarantees that it will not exceed this average by distributing the power budget across its cores. Two separate time windows can be programmed by the user in to the MRS. A higher power could be made available for shorter intervals, with a lower power limit enforced over longer periods to aid application performance.

The introduction of power capping capability has led researchers (Rountree et al., 2012; Patki et al., 2013; Sarood et al., 2014) explore the idea of *over-provisioning* future HPC systems. In an over-provisioned or power-limited system, for problems that benefit from higher number of processors, power capping could be used to run nodes at a low power bound allowing more processors to be operated at lower frequencies. For problems that perform best given a smaller number of faster processors, a smaller number of nodes running at higher power cap or no cap can be used.

In this work, a constant power limit is enforced across the length of the application run for power-limiting experiments.

#### 2.2.4 Energy reduction with power controls

In this section, the potential energy reduction obtainable with DVFS and DDCM is discussed.

Figure 2.2 shows variation in the total power consumption of a processor core as the static power component changes while using DVFS theoretically. When static power component is 100%, DVFS mostly has no effect. In contrast, when the static power component is 0%, the total power consumption is total dependent on the frequency set using DVFS and can be observed to change cubically with change in f as V scales commensurately. The static power component in modern systems constitutes an increasing fraction of

Figure 2.2: Variation in total power consumption of a processor core as the static power component changes while using DVFS theoretically

the total power and commonly contributes 10 to 30% or higher in extreme cases (Butts and Sohi, 2000; Goel and McKee, 2016). Given the contribution of static power to total power, Figure 2.2 gives a basic estimation of the total energy savings that can be achieved using DVFS. For example, if the static power component is 10% and the frequency is reduced by 10%, using Figure 2.2 the expected total energy consumption is 75.6% for a total energy reduction of 24.4% with no performance degradation for an application.

As discussed earlier in Section 2.2.1, the practical power reduction achievable with DVFS is at best quadratic. Figure 2.3 shows the variation in total power consumption of a processor core as the static power component changes while using DDCM and DVFS for a 2.4GHz processor core running at 1.2V by default. In comparison to the possible theoretical reduction of 75.6% seen above, reducing the frequency from 2.4GHz to 2.2GHz (8.3% reduction) gives an expected total energy consumption of 85.8% or reduction of 14.2% with no performance degradation and static power component as 10%. The reduction in energy consumption for DDCM is commensurate with the decrease in frequency, wherein a reduction of 12.5% in effective frequency reduces energy by 12.5%.

It can be seen that the power/energy reduction with DVFS at a particular frequency below default is much higher than DDCM. Thus, a core-specific implementation of DVFS is better for achieving greater power reduction within its operation range. DDCM on the other hand has larger operation range and can reach lower effective frequencies than DVFS at very low latency Experiments carried out on a Sandy Bridge machine show that the frequency transition latency for DVFS is about 30-40 microseconds and the latency for

Figure 2.3: Variation in total power consumption of a processor core as the static power component changes while using DDCM and DVFS

switching between 16 levels of clock modulation is less than 2 microseconds (Wang, 2016). Running at low frequency can do more harm than good, hence due caution needs to be exercised to avoid severe degradation of performance that may lead to increase in overall energy consumption of an application. Thus, choosing the right power control for energy reduction is a function of how fast and low the frequency transitions need to happen.

# 2.3 Metrics Measurement

This section takes a look at the various counters available in the Intel processor micro-architecture and how they can be used to monitor the characteristics of an application during execution.

#### 2.3.1 Running Average Power Limit

Starting with the Sandy Bridge implementation (Intel, 2015a), Intel extended the X86-64 architecture with the "Running Average Power Limit" (RAPL) interface. RAPL provides MSRs to measure and control microprocessor (PKG) energy/power utilization and also memory (DRAM). RAPL includes the MSR\_PKG\_-ENERGY\_STATUS counter which records the energy since boot in 15.3 nanojoule increments and can be accessed (read-only) using /dev/cpu/cpu\*/msr file through rdmsr operations. It is only 32-bit counter and rollover occurs frequently, but by counting the number of rollovers a very fine-grained measurement of chip power can be obtained. It provides the supervisor with energy measurements about 1000 times a second (1 millisecond). Temperature measurements are obtained from IA32\_THERM\_STATUS\_MSR.

On the Sandy Bridge architecture, our understanding is that the energy measurements are modeled. Any resulting skew (e.g., difference between measured power and power-limit setting) should be consistent between runs of the same application. The relative difference between runs should be approximately correct, even if there is error in the absolute values. This weakness seems to have been overcome with the introduction of core-specific voltage regulators in the Haswell architecture.

#### 2.3.2 RCRdaemon

Resource Centric Reflection (RCR) daemon (Porterfield et al., 2010), as the name suggests is a daemon that provides hardware performance counters to any program interested in how a system is performing. It focuses on counters for resources that are shared by more than one hardware core (e.g. energy consumption through RAPL, Last Level Cache performance or memory controller usage through Uncore Performance Monitoring). It can provide access to any counter available through PAPI (Mucci et al., 1999), PERF EVENTS (Per, 2008), or directly though hardware instructions. To provide access to some of the energy counters directly, traditionally RCRdaemon runs at root level for supervisor-privilege. This has been overcome by making RCRdaemon to use *msr-safe* (Shoga et al., 2014) to read counters that require root permissions. The RCRdaemon information is available to the programmer through a simple API that delineates a code region for measurement with a start and end call.

RCRdaemon writes the values into a shared memory region that can be shared with any other running application. To access the region the application only needs shm open a file in */dev/shm*. The shared memory region contains no pointers and access to it (after the first access) is accomplished with simple volatile loads

and stores. The counters tracked in the shared memory region is configured during RCRdaemon initialization and can be modified during daemon startup.

# 2.3.3 Effect of temperature on energy measurement

Temperature has a major effect on power used. Previous study (Porterfield et al., 2013a) has shown energy variation between nodes of an homogeneous cluster can be 10%. Also, power and time variations between consecutive executions of the same application can vary by 2+%. The runs on 'cold' processors can use up to 10% less energy compared to later runs with equivalent execution times. On several of the compute nodes used in the study, lower temperature correlated with reduced energy usage. Whether a cause or effect, hardware that is kept cooler uses less energy. To avoid energy variation with temperature, our experiments ignore results from the first several minutes until the system temperature is stable. Further, the values reported are generally averages taken over 10-12 runs.

## 2.4 Transparent monitoring and control of application