# Research Article Additional High Input Low Output Impedance Analog Networks

# Sudhanshu Maheshwari<sup>1</sup> and Bhartendu Chaturvedi<sup>2</sup>

<sup>1</sup> Department of Electronics Engineering, Z. H. College of Engineering and Technology, Aligarh Muslim University, Aligarh 202002, India

<sup>2</sup> Department of Electronics and Communication Engineering, Jaypee Institute of Information Technology, Noida 201304, India

Correspondence should be addressed to Bhartendu Chaturvedi; bhartendu.prof@gmail.com

Received 6 June 2013; Accepted 14 August 2013

Academic Editor: Jiun-Wei Horng

Copyright © 2013 S. Maheshwari and B. Chaturvedi. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

This paper presents some additional high input low output impedance analog networks realized using a recently introduced single Dual-X Current Conveyor with buffered output. The new circuits encompass several all-pass sections of first- and second-order. The voltage-mode proposals benefit from high input impedance and low output impedance. Nonideality and sensitivity analysis is also performed. The circuit performances are depicted through PSPICE simulations, which show good agreement with theory.

# **1. Introduction**

In the recent past, realization of configurable analog networks has assumed special significance for modern analogue signal processing applications. The feature is quite suited while designing analog blocks with easy configurability, so as to be employed in field programmable analog arrays (FPAAs). Simple analog blocks with this feature were reported earlier and further researched in most recent works [1–3]. Whereas configurability gives rise to the possibility of several electronic functions from a single topology, cascadability results in practical utility of analog blocks for designing more complex networks without additional coupling elements in form of buffers [4–6]. The most recent analog circuit topology benefits from these features by being suited for a number of first-order electronic functions and offering high input impedance and low output impedance [5]. The two features together are just another step towards reducing circuit components enabling portable high performance systems with ease for FPAA implementations [7, 8]. It may be noted that analog filters continue to appear in open literature as a potential analog block for larger subsystems [2-6, 9-12].

This paper presents additional first- and second-order allpass filters with the features of high input and low output impedance. State-of-the-art floating simulators have been employed to overcome the drawbacks of passive inductors [13]. It may be noted that floating inductor simulators using current conveyors have been researched well in the literature [14–17]. Transformation technique has further been employed to realize simpler alternative with lesser circuit complexity. Extensive simulations are performed to validate the proposed theory, which not only justify the proposed theory but also provide advancement to the existing knowledge.

### 2. Additional First-Order All-Pass Filters

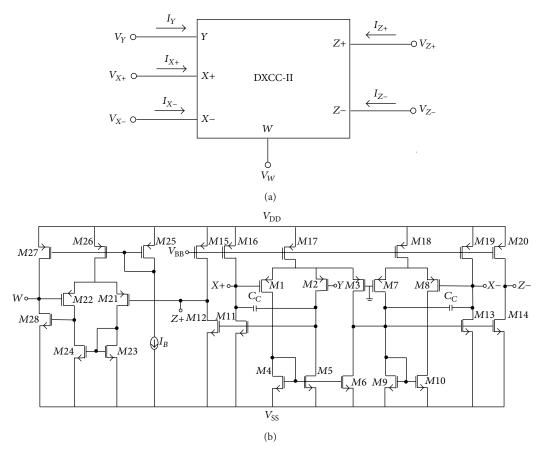

The symbol and CMOS implementation of newly developed second generation Dual-X Current Conveyor (DXCC-II) with buffered output are shown in Figure 1. A newly developed DXCC-II is characterized in matrix form by the following relationship:

$$\begin{bmatrix} I_{Y} \\ I_{Z^{+}} \\ I_{Z^{-}} \\ V_{X^{+}} \\ V_{X^{-}} \\ V_{W} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & -1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} I_{X^{+}} \\ I_{X^{-}} \\ V_{Y} \\ V_{Z} \end{bmatrix}.$$

(1)

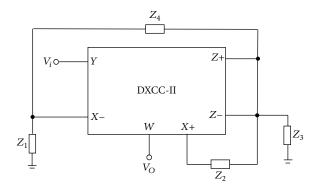

The new additional voltage-mode first-order all-pass filter topology is shown in Figure 2. It may be noted that interchanging the positions of X+ and X- yields the topology

FIGURE 1: (a) Symbol of DXCC-II with buffer, (b) CMOS implementation of DXCC-II with buffer [5].

FIGURE 2: Topology extension by interchanging *X* ports of a recent work [5].

of [5], a fact not mentioned therein. The given topology is characterized by the general transfer function for continual signals in "s" domain as

$$\frac{V_o(s)}{V_i(s)} = -\frac{Z_2 Z_3 Z_4 + 2Z_1 Z_2 Z_3 - 2Z_1 Z_3 Z_4}{Z_1 Z_2 Z_4 + 2Z_1 Z_2 Z_3 + 2Z_1 Z_3 Z_4}.$$

(2)

Specialization of the impedances in Figure 2 yields missing circuits of voltage-mode first-order all-pass filters as listed in Table 1. The circuits of Filter 1 and Filter 2 use two passive components. In the circuit of Filter 1,  $Z_2$  and  $Z_4$  are retained

with  $Z_2$  as a resistor and  $Z_4$  as a capacitor while opencircuiting  $Z_1$  and  $Z_3$ . In the circuit of Filter 2,  $Z_2$  and  $Z_4$ are retained with  $Z_2$  as a capacitor and  $Z_4$  as a resistor while open-circuiting  $Z_1$  and  $Z_3$ . No matching condition is required in both of the circuits of Filter 1 and Filter 2. In the last two circuits of Filter 3 and Filter 4 three components are used in each case. In the circuit of Filter 3,  $Z_1$ ,  $Z_2$ , and  $Z_3$ are retained with  $Z_1$ ,  $Z_3$  as capacitors and  $Z_2$  as a resistor while open-circuiting  $Z_4$ . In the circuit of Filter 4,  $Z_1$ ,  $Z_2$ , and  $Z_3$  are retained with  $Z_1$ ,  $Z_3$  as resistors and  $Z_2$  as a capacitor while open-circuiting  $Z_4$ . The circuits of Filter 1 and Filter 2 enjoy the advantage of single resistor control. The circuit of Filter 3 also enjoys the feature of single resistor control but is noncanonical. It also employs both capacitors in grounded form. The circuit of Filter 4 is canonical by employing single capacitor but requires matched grounded resistors. It is also to be noted that other useful first-order analog functions (e.g., lossy and loss less integrators, high pass filter, etc.) are also realizable from the modified general topology of Figure 2.

#### 3. Second-Order Filters

Selection of the impedances in Figure 2 yields a circuit of second-order voltage-mode all-pass filter by retaining all impedances  $Z_1, Z_2, Z_3$ , and  $Z_4$ . The selection of impedances is  $Z_1$  and  $Z_3$  as capacitive reactance ( $Z_1 = 1/sC_1$ ,

| Circuits     | Choice of passive components |            |              |              |                    | Filter type  |

|--------------|------------------------------|------------|--------------|--------------|--------------------|--------------|

| $\downarrow$ | $Z_1$                        | $Z_2$      | $Z_3$        | $Z_4$        | Matching condition | ritter type  |

| Filter 1     | Open circuit                 | $R_2$      | Open circuit | $1/sC_1$     | No                 | Inverting    |

| Filter 2     | Open circuit                 | $1/sC_{2}$ | Open circuit | $R_4$        | No                 | Noninverting |

| Filter 3     | $1/sC_1$                     | $R_2$      | $1/sC_3$     | Open circuit | $C_1 = C_3$        | Inverting    |

| Filter 4     | $R_1$                        | $1/sC_{2}$ | $R_3$        | Open circuit | $R_{1} = R_{3}$    | Noninverting |

TABLE 1: First-order voltage-mode all-pass filters.

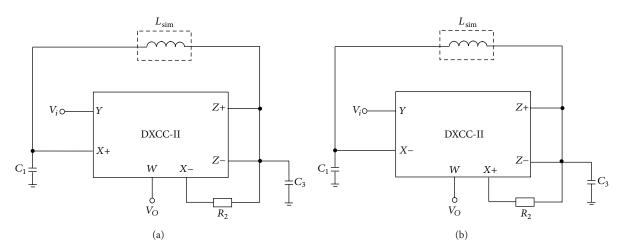

FIGURE 3: (a) Proposed second-order all-pass filter using simulated inductor. (b) Another circuit obtained by interchanging X ports.

$Z_3 = 1/sC_3$ , resp.)  $Z_2$  as resistive, and  $Z_4$  is taken as inductive reactance ( $Z_4 = sL_4$ ). It is a well-known fact that real inductors are not used in integrated analog systems due to their bulky size, which became a motivating factor for the introduction of active-RC networks long back. In the circuit proposed here, simulated floating inductor [13] is used in place of the real inductor. The DXCC-II based circuit of [13] realizes a resistor less floating inductor. The new proposed voltage-mode second-order all-pass filter using simulated inductance ( $L_4 \equiv L_{sim}$ ) is shown in Figure 3(a). Another circuit is obtained by interchanging the positions of the X+ and X- terminals and is shown in Figure 3(b). The transfer function of the proposed circuits of Figures 3(a) and 3(b) is given as

$$\frac{V_o(s)}{V_i(s)} = k \frac{s^2 L_{\rm sim} C_1 R_2 - 2s L_{\rm sim} + 2R_2}{s^2 L_{\rm sim} C_3 R_2 + 2s L_{\rm sim} + 2R_2},$$

(3)

where k = +1 for the circuit of Figure 3(a) and k = -1 for the circuit of Figure 3(b).

The expressions for pole- $\omega_0$  and Q are given in (4) and (5), respectively:

$$\omega_0 = \sqrt{\frac{2}{C_3 L_{\rm sim}}},\tag{4}$$

$$Q = R_2 \sqrt{\frac{C_3}{2L_{\rm sim}}}.$$

(5)

From (4) and (5), it is found that the Q can be tuned independent of  $\omega_0$  by adjusting the value of  $R_2$ .

Sensitivity figures for pole- $\omega_0$  and Q are given as follows:

$$S_{C_3}^{\omega_0} = S_{L_{\rm sim}}^{\omega_0} = -\frac{1}{2}, \qquad S_{R_2}^{\omega_0} = 0,$$

$$S_{R_2}^Q = 1, \qquad S_{C_3}^Q = -S_{L_{\rm sim}}^Q = \frac{1}{2}.$$

(6)

From (6), the sensitivity figures for the proposed circuits are found to be less than or equal to unity in magnitude which implies good sensitivity performance.

It is now to be emphasized that inductance simulator value is as  $L_{sim} = (C/g_{m1}g_{m2})$ , where  $g_{m1}$  and  $g_{m2}$  are transconductance of transistors used in simulated inductor, which can be controlled by the gate voltages of those transistors [13]. Here,  $g_{mi}$  (i = 1, 2) is the transconductance of the *i*th MOS transistor and is given as

$$g_{mi} = 2\mu C_{ox} \left(\frac{W}{L}\right)_i \left(V_{Gi} - V_{Ti}\right), \quad \text{where } i = 1, 2.$$

(7)

By substituting the value of  $L_{sim}$  in (3), the transfer function becomes

$$\frac{V_o(s)}{V_i(s)} = k \frac{s^2 C C_1 R_2 - 2sC + 2R_2 g_{m1} g_{m2}}{s^2 C C_3 R_2 + 2sC + 2R_2 g_{m1} g_{m2}}.$$

(8)

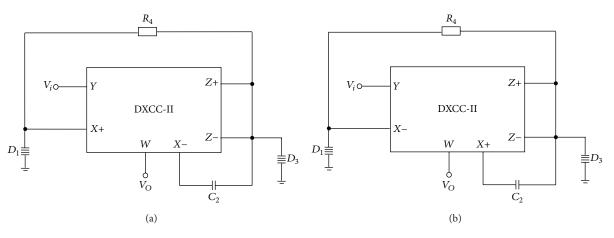

FIGURE 4: (a) Proposed second-order all-pass filter using frequency transformation. (b) Another circuit obtained by interchanging X ports.

The expressions for pole- $\omega_0$  and Q are also modified and given in (9) and (10), respectively:

$$\omega_0 = \sqrt{\frac{2g_{m1}g_{m2}}{C_3 C}},\tag{9}$$

$$Q = R_2 \sqrt{\frac{C_3 g_{m1} g_{m2}}{2C}}.$$

(10)

Sensitivity figures for pole- $\omega_0$  and Q are now given as follows:

$$S_{g_{m1},g_{m2}}^{\omega_0} = -S_{C_3}^{\omega_0} = -S_C^{\omega_0} = \frac{1}{2}, \qquad S_{R_2}^{\omega_0} = 0,$$

$$S_{R_2}^Q = 1, \qquad S_{C_3}^Q = S_{g_{m1},g_{m2}}^Q = -S_C^Q = \frac{1}{2}.$$

(11)

All the sensitivity figures given in (11) are still less than or equal to unity in magnitude, which suggests good sensitivity performance.

Another possible circuit design is to use frequency transformation method [18]. In frequency transformation, all the impedances are scaled by the frequency-dependent factor 1/s. Such an impedance-level scaling operation is quite appropriate, because this operation does not affect the transfer function. The motivation behind this scaling operation is that scaling inductive impedance sL by 1/s leaves the circuit with the resistor of the same value, R = L, and the inductor is eliminated. However, so as not to change the transfer function in the scaling operation, all components must be scaled by the same factor. Therefore, the three passive elements are, namely,

$$Z_R = R, \qquad Z_L = sL, \qquad Z_C = \frac{1}{(sC)}.$$

(12)

After transformation (1/s) yields the new components

$$Z'_{R} = \frac{R}{s}, \qquad Z'_{L} = L, \qquad Z'_{C} = \frac{1}{(s^{2}C)}.$$

(13)

Such scaling actually results in a transformation of the elements: a resistor (R) becomes a capacitor of value "1/R,"

an inductor (*L*) becomes a resistor of value "*L*," and a capacitor (*C*) becomes a frequency-dependent negative resistor (FDNR) and is denoted by "*D*" and symbolized as four parallel lines. The resulting circuit after frequency transformation is shown in Figure 4(a). Another circuit is obtained by interchanging the positions of the *X*+ and *X*- terminals and is shown in Figure 4(b). Here, the active realization of FDNR using DXCC-II may be used [19]. The active realization of FDNR has the advantage of using a single active element and tunability by means of control voltage. The impedance function [19] is given for the ideal case  $[Z] = 1/s^2 D_{eq} = 2/s^2 C^2 R$  for  $C_1 = C_2 = C$ .

The transfer function of the proposed circuits of Figures 4(a) and 4(b) is given as

$$\frac{V_o(s)}{V_i(s)} = k \frac{s^2 C_1^2 R_1 R_4 - 4s C_2 R_4 + 4}{s^2 C_2^2 R_3 R_4 + 4s C_2 R_4 + 4},$$

(14)

where k = +1 for the circuit of Figure 4(a) and k = -1 for the circuit of Figure 4(b).

The expressions for pole- $\omega_0$  and *Q* are given in (15) and (16), respectively:

$$\omega_0 = \frac{2}{C_3 \sqrt{R_3 R_4}},$$

(15)

$$Q = \frac{C_3}{2C_2} \sqrt{\frac{R_3}{R_4}}.$$

(16)

Sensitivity figures for pole- $\omega_0$  and Q are given as follows:

$$S_{C_3}^{\omega_0} = -1, \qquad S_{R_3}^{\omega_0} = S_{R_4}^{\omega_0} = -\frac{1}{2}, \qquad S_{C_2}^{\omega_0} = 0,$$

$$S_{C_2}^Q = -S_{C_3}^Q = -1, \qquad S_{R_3}^Q = -S_{R_4}^Q = \frac{1}{2}.$$

(17)

From (17), the sensitivity figures for the proposed circuits are all less than or equal to unity in magnitude which implies good sensitivity performance.

As an application of second-order voltage-mode all-pass filter, a sinusoidal oscillator producing two-phase signals is

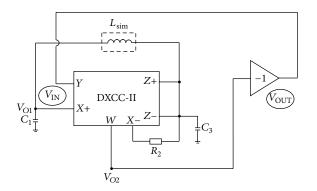

FIGURE 5: Proposed voltage mode sinusoidal oscillator.

next given. The circuit is shown in Figure 5; it consists of a voltage-mode second-order all-pass filter and a unity gain inverter, with the output of the inverter being fed back to the input of the first stage. It may be noted that the inverter (gain = -1) is realized using DXCC-II itself with input and output at Y and X-, respectively. The system loop gain (defined as  $V_{\rm OUT}/V_{\rm IN}$ , Figure 5) is given by

$$\frac{V_{\text{OUT}}(s)}{V_{\text{IN}}(s)} = (-1) \frac{s^2 L_{\text{sim}} C_1 R_2 - 2s L_{\text{sim}} + 2R_2}{s^2 L_{\text{sim}} C_3 R_2 + 2s L_{\text{sim}} + 2R_2}.$$

(18)

If loop gain is set to unity at  $s = j\omega$ , the circuit shown in Figure 5 can be set to provide two-phase sinusoidal oscillation with oscillation frequency as

$$f_0 = \frac{1}{\Pi \sqrt{2L_{\rm sim}C_3}}.$$

(19)

The circuit provides two voltage outputs  $V_{O1}$  and  $V_{O2}$ . The voltage outputs marked in Figure 5 are related as  $V_{O1} = -V_{O2}$ .

#### 4. Nonideal Analysis

A nonideal DXCC-II is characterized by the following port relationship:

$$\begin{bmatrix} I_{Y} \\ I_{Z+} \\ I_{Z-} \\ V_{X+} \\ V_{W} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ \alpha_{p} & 0 & 0 & 0 \\ 0 & \alpha_{n} & 0 & 0 \\ 0 & 0 & \beta_{p} & 0 \\ 0 & 0 & -\beta_{n} & 0 \\ 0 & 0 & 0 & \gamma \end{bmatrix} \begin{bmatrix} I_{X+} \\ I_{X-} \\ V_{Y} \\ V_{Z} \end{bmatrix}.$$

(20)

Here,  $\alpha_p$  and  $\alpha_n$  are the current transfer gains from X+ and X- terminals to Z+ and Z- terminals, respectively,  $\beta_p$ and  $\beta_n$  are the voltage transfer gains from Y input terminal to X+ and X- terminals, respectively, and  $\gamma$  is the voltage transfer gain from Z+ terminal to W terminal (buffered output). However, these transfer gains are close to unity up to very high frequencies [20]. Using (20), the proposed circuits of voltage-mode second-order all-pass filter using simulated inductor as shown in Figures 3(a) and 3(b) are reanalyzed so as to yield the following voltage transfer function:

$$\frac{V_o(s)}{V_i(s)} = k\gamma \frac{s^2 \alpha_p \beta_p L_{\rm sim} C_1 R_2 - s L_{\rm sim} \beta_n (1 + \alpha_n) + R_2 \beta_p (1 + \alpha_p)}{s^2 L_{\rm sim} C_3 R_2 + s L_{\rm sim} (1 + \alpha_n) + R_2 (1 + \alpha_p)},$$

(21)

where k = +1 for the circuit of Figure 3(a) and k = -1 for the circuit of Figure 3(b).

The expressions for pole- $\omega_0$  and Q are given as follows:

$$\omega_0 = \sqrt{\frac{1 + \alpha_p}{C_3 L_{\rm sim}}},$$

$$Q = \frac{R_2}{1 + \alpha_n} \sqrt{\frac{C_3 \left(1 + \alpha_p\right)}{L_{\rm sim}}}.$$

(22)

Active and passive sensitivity figures for pole- $\omega_0$  and Q are given as

$$S_{C_{3}}^{\omega_{0}} = S_{L_{\text{sim}}}^{\omega_{0}} = -\frac{1}{2}, \qquad S_{R_{2}}^{\omega_{0}} = 0,$$

$$S_{\alpha_{p}}^{\omega_{0}} = \frac{\alpha_{p}}{2\left(1 + \alpha_{p}\right)}, \qquad S_{\alpha_{n}}^{\omega_{0}} = 0,$$

$$S_{R_{2}}^{Q} = 1, \qquad S_{C_{3}}^{Q} = -S_{L_{\text{sim}}}^{Q} = \frac{1}{2},$$

$$S_{\alpha_{p}}^{Q} = \frac{\alpha_{p}}{2\left(1 + \alpha_{p}\right)}, \qquad S_{\alpha_{n}}^{Q} = -\frac{\alpha_{n}}{1 + \alpha_{n}}.$$

(23)

Using (20), the proposed circuits of voltage-mode secondorder all-pass filter using frequency transformation as shown in Figures 4(a) and 4(b) are reanalyzed so as to yield the following voltage transfer function:

$$\frac{V_{o}(s)}{V_{i}(s)} = k\gamma \frac{s^{2}\alpha_{p}\beta_{p}C_{1}^{2}R_{1}R_{4} - 2s\beta_{n}C_{2}R_{4}(1+\alpha_{n}) + 2\beta_{p}(1+\alpha_{p})}{s^{2}C_{3}^{2}R_{3}R_{4} + 2sC_{2}R_{4}(1+\alpha_{n}) + 2(1+\alpha_{p})},$$

(24)

where k = +1 for the circuit of Figure 4(a) and k = -1 for the circuit of Figure 4(b).

The expressions for pole- $\omega_0$  and *Q* are given as follows:

$$\omega_0 = \frac{1}{C_3} \sqrt{\frac{2\left(1+\alpha_p\right)}{R_3 R_4}},$$

$$Q = \frac{C_3}{C_2\left(1+\alpha_n\right)} \sqrt{\frac{R_3\left(1+\alpha_p\right)}{2R_4}}.$$

(25)

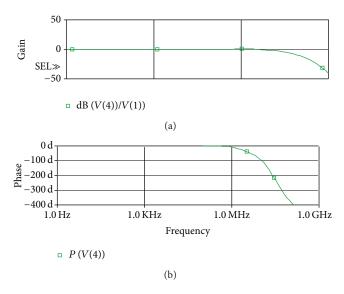

FIGURE 6: Gain (dB) and phase (deg) response of second-order voltage-mode all-pass filter of Figure 3(a).

Active and passive sensitivity figures for pole- $\omega_0$  and Q are given as

$$S_{C_{3}}^{\omega_{0}} = -1, \qquad S_{R_{3}}^{\omega_{0}} = S_{R_{4}}^{\omega_{0}} = -\frac{1}{2}, \qquad S_{C_{2}}^{\omega_{0}} = 0,$$

$$S_{\alpha_{p}}^{\omega_{0}} = \frac{\alpha_{p}}{2\left(1 + \alpha_{p}\right)}, \qquad S_{\alpha_{n}}^{\omega_{0}} = 0,$$

$$S_{C_{2}}^{Q} = -S_{C_{3}}^{Q} = -1, \qquad S_{R_{3}}^{Q} = -S_{R_{4}}^{Q} = \frac{1}{2},$$

$$S_{\alpha_{p}}^{Q} = \frac{\alpha_{p}}{2\left(1 + \alpha_{p}\right)}, \qquad S_{\alpha_{n}}^{Q} = -\frac{\alpha_{n}}{1 + \alpha_{n}}.$$

(26)

Equation (22) and (26) shows that the sensitivity figures are all less than or equal to unity in magnitude which implies good sensitivity performance. Sensitivity of filter parameters to current transfer gains will remain less than unity for the ideal value of current transfer gains which is equal to unity.

#### 5. Parasitic Considerations

The next study on the proposed circuits is carried out for the effect of parasitics involved with the used current conveyor. It assumes special significance for evaluating the real performance of any analog circuit. The various parasitics involved with a typical current conveyor [21] are well known to potential readers and will only be reviewed briefly. The various parasitics of the DXCC-II used in the proposed circuits are port *Z* parasitics in the form of  $R_Z//C_Z$ , port *Y* parasitic in the form of  $R_Y//C_Y$  and port *X* parasitics. The proposed circuits are re-analyzed by taking into account the above parasitic effects. A re-analysis of the proposed circuit of voltage-mode second order all-pass filter using simulated inductor as shown in Figure 3(a) yields:

$$\frac{V_o(s)}{V_i(s)} = -\frac{s^2 L_{\rm sim} C_1' R_2' - 2s L_{\rm sim} + 2R_2'}{s^2 L_{\rm sim} C_3' R_2' + 2s L_{\rm sim} + 2R_2'},$$

(27)

where  $R'_2 = R_2 + R_{X-}$ ,  $C'_1 = C_1 + C_{X+}$ , and  $C'_3 = (C_3 + C_{Z+} + C_{Z-})$ .

From (27), it is clear that the parasitic resistances/capacitances merge with the external value. Such a merger does cause slight deviation in circuit's parameters. It can be further observed from (27) that the order of transfer function of second-order all-pass filter is not changed. The modified expressions for pole- $\omega$ 0 and Q with parasitic effects are also given as

$$\omega_0 = \sqrt{\frac{2}{C_3' L_{\rm sim}}},\tag{28}$$

$$Q = R_2' \sqrt{\frac{C_3'}{2L_{\rm sim}}}.$$

(29)

Next, it is seen from (28) that the pole frequency would slightly be deviated (in deficit) because of these parasitics. The expression showing the effects of parasitics on pole-*Q* is also given in (29). The pole-*Q* would also deviate slightly because of the parasitics. The deviation is expected to be small for an integrated DXCC-II.

#### 6. Simulation Results

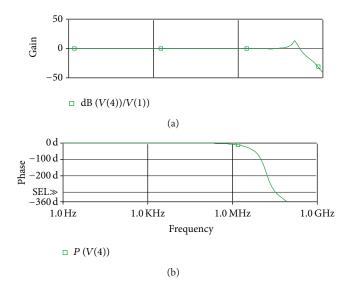

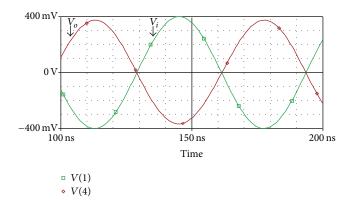

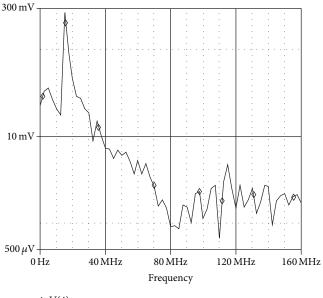

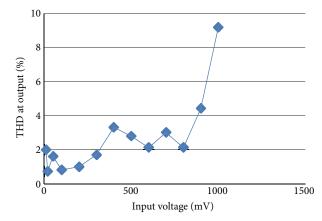

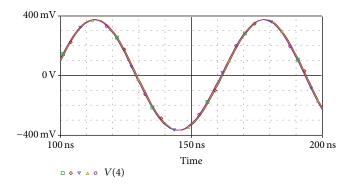

The new proposed circuits are verified through PSPICE simulations. The simulations are based on  $0.5 \,\mu m$ , TSMC, CMOS parameters. Table 2 shows the dimensions of MOS parameters which are used in CMOS implementation of DXCC-II of Figure 1(b). The supply voltages used are  $\pm 2.5$  V,  $V_{BB} = -0.6$  V,  $C_C = 0.06$  pF, and  $I_B = 25 \,\mu$ A. The proposed voltage-mode second-order circuit of all-pass filter using simulated inductor has been designed at the pole frequency of 15.92 MHz. For the circuit of voltage-mode second-order all-pass filter (Figure 3(a)) resistance used is  $R_2 = 20 \text{ K}\Omega$ , capacitors used are of values  $C_1 = C_3 = 1 \text{ pF}$ , and, for the resistor less floating simulated inductor, the dimensions of the NMOS transistors are  $W/L = 2 \mu m/0.5 \mu m$ . The bias voltages are selected to be 0.78 V so as to obtain a resistance of  $20 \text{ k}\Omega$ across each one of the MOS transistor. The capacitance C is set to 2 pF so as to realize a floating inductance of 0.2 mH. The gain and phase response of the circuit of Figure 3(a) are shown in Figure 6, which shows the pole frequency as 15.85 MHz with a percentage error of 0.44%. The usefulness of new circuits is to be especially emphasized keeping in view the design frequency which is quite high. The inputoutput waveforms for voltage-mode second-order all-pass filter are shown in Figure 7. The Fourier spectrum of output is shown in Figure 8. The THD is found to be 1.5% which is also moderately low. The plot of THD variation at output with the amplitude of the input voltage is shown in Figure 9. Furthermore, the circuit of second-order voltage-mode allpass filter using FDNR (Figure 4(a)) is also simulated.

FIGURE 7: Input/output waveforms at 15.92 MHz.

$\diamond V(4)$

FIGURE 8: Fourier spectrum of output waveform at 15.92 MHz.

The gain and phase response of the circuit of Figure 4(a) are given in Figure 10. The circuit of Figure 4(a) was designed using  $C_2 = 10 \text{ pF}$ ,  $R_4 = 4 \text{ k}\Omega$ , and, for the realization of resistor less FDNR, the dimensions of the NMOS transistor are selected as  $W/L = 4 \mu \text{m}/1 \mu \text{m}$ . The bias voltage is selected to be 1.2 V so as to obtain a resistance of 1.6 k $\Omega$  across the MOS transistor. The capacitances are set as  $C_{D11} = C_{D12} = 50 \text{ pF}$  and  $C_{D31} = C_{D32} = 50 \text{ pF}$  to realize FDNR1 ( $D_1$ ) and FDNR3 ( $D_3$ ), respectively. The theoretical pole frequency used in this design was 25.18 MHz. The simulated pole frequency was found to be 25 MHz, which is very close to the theoretical value and only 0.71% in error.

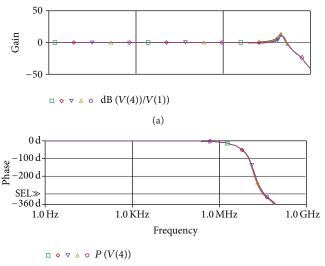

The Monte Carlo analysis of the second order voltagemode all-pass filter (Figure 3(a)) was next performed taking 5% Gaussian deviation in the each passive component ( $C_1$ ,  $R_2$ ,  $C_3$ , and  $L_{sim}$ ). The analysis was done for 5 runs. The gain and phase response with Monte Carlo analysis is shown in Figure 11 and time domain result for Monte Carlo analysis is

FIGURE 9: THD variation at output with signal amplitude at 15.92 MHz.

FIGURE 10: Gain (dB) and phase (deg) response of second-order voltage-mode all-pass filter of Figure 4(a).

TABLE 2: Dimensions of MOS transistors in DXCC-II of Figure 1(b).

| Transistors                                                        | $W (\mu m)/L (\mu m)$ |  |

|--------------------------------------------------------------------|-----------------------|--|

| <i>M</i> 1, <i>M</i> 2, <i>M</i> 4, <i>M</i> 5, and <i>M</i> 15–20 | 4/0.5                 |  |

| <i>M</i> 3, <i>M</i> 6–10                                          | 8/0.5                 |  |

| M11–14                                                             | 32/0.5                |  |

| M21, M22, M25, and M26                                             | 2.5/0.5               |  |

| M27                                                                | 10/0.5                |  |

| M23, M24                                                           | 50/0.5                |  |

| M28                                                                | 100/0.5               |  |

shown in Figure 12. As depicted from Monte-Carlo analysis results, the proposed filter has good sensitivity performances.

#### 7. Conclusion

This work presents four additional voltage-mode first-order all-pass filters and second-order all-pass filters with high

(b)

FIGURE 11: Monte Carlo analysis of Figure 3(a) showing gain (dB) and phase (deg) response.

FIGURE 12: Monte Carlo analysis of Figure 3(a) showing output for 5 runs.

input and low output impedance in each case. The circuits are based on the recently introduced active element, namely, Dual-X Current Conveyor with buffered output. As an application of the second-order voltage-mode all-pass filter, a voltage-mode oscillator configuration is given. Nonideal analysis of the proposed circuits is performed, and parasitic considerations are also discussed. The proposed circuits enjoy good active and passive sensitivities. Simulations results are given to confirm the presented theory.

#### Acknowledgments

The authors thank Academic Editor for recommending this paper. At the time of paper submission, the article processing charges for the Journal were waived off.

# References

P. Beg, I. A. Khan, S. Maheshwari, and M. A. Siddiqi, "Digitally programmable fully differential filter," *Radioengineering*, vol. 20, no. 4, pp. 917–925, 2011.

- [2] I. A. Khan and A. M. Nahhas, "Reconfigurable voltage mode first order multifunctional filter using single low voltage digitally controlled CMOS CCII," *International Journal of Computer Applications*, vol. 45, no. 5, pp. 37–40, 2012.

- [3] I. A. Khan, M. T. Simsim, and P. Beg, "Reconfigurable continuous time current mode first order multifunctional filter using low voltage digitally controlled CMOS CCII," in *Proceedings of the International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT '11)*, pp. 5–8, Aligarh, India, December 2011.

- [4] S. Maheshwari, "Analogue signal processing applications using a new circuit topology," *IET Circuits, Devices and Systems*, vol. 3, no. 3, pp. 106–115, 2009.

- [5] S. Maheshwari and B. Chaturvedi, "High-input low-output impedance all-pass filters using one active element," *IET Circuits, Devices and Systems*, vol. 6, no. 2, pp. 103–110, 2012.

- [6] S. Maheshwari, J. Mohan, and D. S. Chauhan, "Voltage-mode cascadable all-pass sections with two grounded passive components and one active element," *IET Circuits, Devices and Systems*, vol. 4, no. 2, pp. 113–122, 2010.

- [7] Y. Sun, Design of High Frequency Integrated Analogue Filters, vol. 14 of IEE Circuits, Devices and Systems, Institution of Electrical Engineers, Stevenage, UK, 2002.

- [8] Y. Sun, Wireless Communication Circuits and Systems, vol. 16 of IEE Circuits, Devices and Systems, Institution of Electrical Engineers, Stevenage, UK, 2004.

- [9] A. M. Soliman, "Generation of current conveyor-based allpass filters from op amp-based circuits," *IEEE Transactions on Circuits and Systems II*, vol. 44, no. 4, pp. 324–330, 1997.

- [10] T. Tsukutani, H. Tsunetsugu, Y. Sumi, and N. Yabuki, "Electronically tunable first-order all-pass circuit employing DVCC and OTA," *International Journal of Electronics*, vol. 97, no. 3, pp. 285– 293, 2010.

- [11] D. Biolek and V. Biolkova, "Allpass filter employing one grounded capacitor and one active element," *Electronics Letters*, vol. 45, no. 16, pp. 807–808, 2009.

- [12] D. Biolek and V. Biolkova, "First-order voltage-mode allpass filter employing one active element and one grounded capacitor," *Analog Integrated Circuits and Signal Processing*, vol. 65, no. 1, pp. 123–129, 2010.

- [13] R. A. Saad and A. M. Soliman, "On the systematic synthesis of CCII-based floating simulators," *International Journal of Circuit Theory and Applications*, vol. 38, no. 9, pp. 935–967, 2010.

- [14] K. Pal, "Novel floating inductance using current conveyors," *Electronics Letters*, vol. 17, no. 18, article 638, 1981.

- [15] A. S. Sedra and K. C. Smith, "A second generation current conveyor and its applications," *IEEE Transactions on Circuit Theory*, vol. 17, no. 1, pp. 132–134, 1970.

- [16] I. A. Khan and M. H. Zaidi, "A novel ideal floating inductor using translinear conveyors," *Active and Passive Electronic Components*, vol. 26, no. 2, pp. 87–89, 2003.

- [17] F. Kacar and A. Yesil, "Novel grounded parallel inductance simulators realization using a minimum number of active and passive components," *Microelectronics Journal*, vol. 41, no. 10, pp. 632–638, 2010.

- [18] R. Schaumann and M. E. Valkenburg, *Design of Analog Filters*, Oxford University Press, New York, NY, USA, 2005.

- [19] F. Kacar, B. Metin, and H. Kuntman, "A new CMOS dual-X second generation current conveyor (DXCCII) with an FDNR circuit application," *International Journal of Electronics and Communications*, vol. 64, no. 8, pp. 774–778, 2010.

- [20] A. Zeki and A. Toker, "The dual-X current conveyor (DXCCII): a new active device for tunable continuous-time filters," *International Journal of Electronics*, vol. 89, no. 12, pp. 913–923, 2002.

- [21] E. Tlelo-Cuautle, C. Sánchez-López, and D. Moro-Frías, "Symbolic analysis of (MO)(I)CCI(II)(III)-based analog circuits," *International Journal of Circuit Theory and Applications*, vol. 38, no. 6, pp. 649–659, 2010.