# IMPROVING THE RELIABILITY OF MICROPROCESSORS UNDER BTI AND TDDB DEGRADATIONS

by

# Lin Li

BS, Beihang University, 2005MS, Beihang University, 2007

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

PhD in Computer Engineering

University of Pittsburgh

2014

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Lin Li

It was defended on

October 18, 2013

and approved by

- Jun Yang, Ph. D., Associate Professor, Department of Electrical and Computer Engineering Youtao Zhang, Ph. D., Associate Professor, Department of Computer Science

- Steven P. Levitan, Ph. D., Professor, Department of Electrical and Computer Engineering Sangyeun Cho, Ph. D., Associate Professor, Department of Computer Science

Jingtao Wang, Ph. D., Assistant Professor, Department of Computer Science

Dissertation Director: Jun Yang, Ph. D., Associate Professor, Department of Electrical and Computer Engineering Copyright © by Lin Li2014

# IMPROVING THE RELIABILITY OF MICROPROCESSORS UNDER BTI AND TDDB DEGRADATIONS

Lin Li, Ph.D.

University of Pittsburgh, 2014

Reliability is a fundamental challenge for current and future microprocessors with advanced nanoscale technologies. With smaller gates, thinner dielectric and higher temperature microprocessors are vulnerable under aging mechanisms such as Bias Temperature Instability (BTI) and Temperature Dependent Dielectric Breakdown (TDDB). Under continuous stress both parametric and functional errors occur, resulting compromised microprocessor lifetime. In this thesis, based on the thorough study on BTI and TDDB mechanisms, solutions are proposed to mitigating the aging processes on memory based and random logic structures in modern out-of-order microprocessors.

A large area of processor core is occupied by memory based structure that is vulnerable to BTI induced errors. The problem is exacerbated when PBTI degradation in NMOS is as severe as NBTI in PMOS in high- $\kappa$  metal gate technology. Hence a novel design is proposed to recover 4 internal gates within a SRAM cell simultaneously to mitigate both NBTI and PBTI effects. This technique is applied to both the L2 cache banks and the busy function units with storage cells in out-of-order pipeline in two different ways. For the L2 cache banks, redundant cache bank is added exclusively for proactive recovery rotation. For the critical and busy function units in out-of-order pipelines, idle cycles are exploited at per-buffer-entry level.

Different from memory based structures, combinational logic structures such as function units in execution stage can not use low overhead redundancy to tolerate errors due to their irregular structure. A design framework that aims to improve the reliability of the vulnerable functional units of a processor core is designed and implemented. The approach is designing a generic function unit (GFU) that can be reconfigured to replace a particular functional unit (FU) while it is being recovered for improved lifetime. Although flexible, the GFU is slower than the original target FUs. So GFU is carefully designed so as to minimize the performance loss when it is in-use. More schemes are also designed to avoid using the GFU on performance critical paths of a program execution.

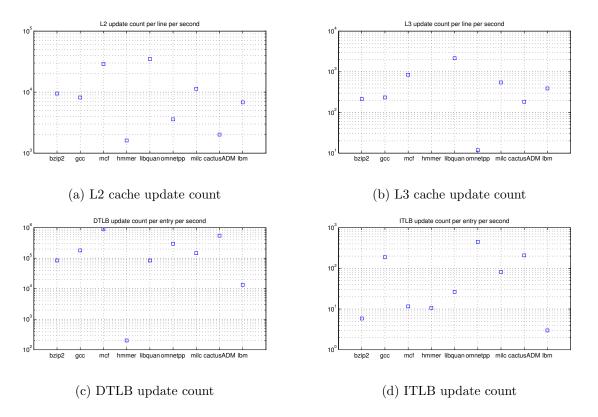

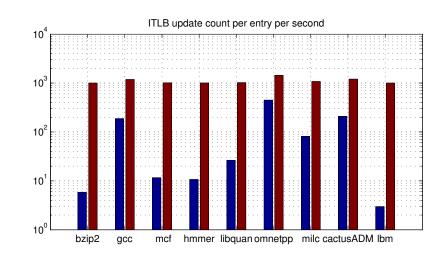

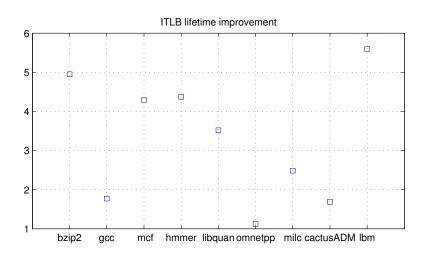

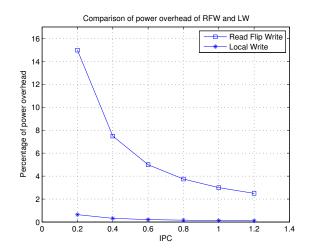

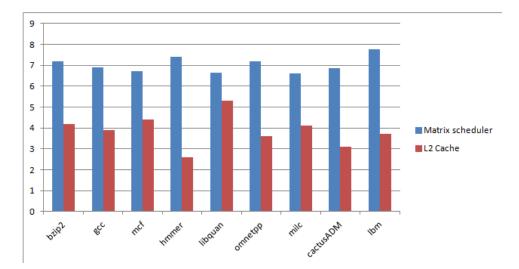

Then finally the TDDB reliability issues are analyzed and bit flipping technique is designed in addition to voltage scaling to improve TDDB reliability in memory based and combinational logic structures, leveraging TDDB's dependence on bit flipping frequency. The update counts in multiple units include matrix scheduler, caches and TLBs indicate significant potential of utilizing bit flipping circuit to mitigate TDDB stress. Although applying bit flipping technique on entry update improves the reliability under TDDB stress in most units, ITLB is the only unit that lacks natural frequent update activity. The local write circuit is a effective and light weight design to proactively boost the bit flipping frequency.

## TABLE OF CONTENTS

| AC  | KN  | OWLEDGEMENT                                               | xiii |

|-----|-----|-----------------------------------------------------------|------|

| 1.0 | IN  | <b>FRODUCTION</b>                                         | 1    |

|     | 1.1 | Thesis Topic                                              | 1    |

|     | 1.2 | Microprocessor Reliability Research Overview              | 2    |

|     |     | 1.2.1 Memory based Structure Reliability Improvement      | 3    |

|     |     | 1.2.2 Logic Structure Reliability Improvement             | 3    |

|     |     | 1.2.3 Aging Induced Reliability Issues                    | 5    |

|     |     | 1.2.4 Reliability Design Challenges for Future Technology | 6    |

|     | 1.3 | Reliability Design in State-of-Art Microprocessor         | 6    |

|     | 1.4 | Chapter Overview                                          | 7    |

| 2.0 | DE  | GRADATION MECHANISMS                                      | 10   |

|     | 2.1 | Bias Temperature Instability: BTI                         | 10   |

|     |     | 2.1.1 NBTI and PBTI                                       | 10   |

|     |     | 2.1.2 BTI Recovery Modes                                  | 12   |

|     |     | 2.1.3 BTI Modeling                                        | 14   |

|     | 2.2 | Time Dependent Dielectric Breakdown: TDDB                 | 15   |

|     |     | 2.2.1 Frequency Dependent Stress                          | 16   |

|     |     | 2.2.2 TDDB Modeling                                       | 16   |

|     | 2.3 | Summary                                                   | 17   |

| 3.0 | PR  | OACTIVE RECOVERY AND 4PR FOR BTI IN SRAM CELLS .          | 18   |

|     | 3.1 | Effect of both NBTI and PBTI                              | 18   |

|     | 3.2 | 4PR Recovery Circuit                                      | 22   |

|     |            | 3.2.1 Existing approach                                                                                                                                 | 22 |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |            | 3.2.2 4T proactive recovery for SRAM cells                                                                                                              | 23 |

|     |            | 3.2.3 Further discussions                                                                                                                               | 26 |

|     | 3.3        | Summary                                                                                                                                                 | 29 |

| 4.0 | 4 <b>P</b> | R ON L2 CACHE AND OUT-OF-ORDER ENTRIES                                                                                                                  | 30 |

|     | 4.1        | Using a spare bank for $4PR$ in L2 Cache                                                                                                                | 30 |

|     | 4.2        | $4PR$ opportunity for Busy FUs $\ldots \ldots \ldots$ | 31 |

|     |            | 4.2.1 FU Activities                                                                                                                                     | 31 |

|     |            | 4.2.2 Idle Cycle Analysis                                                                                                                               | 33 |

|     |            | 4.2.3 Recovery Opportunities with Latency Overhead                                                                                                      | 34 |

|     |            | 4.2.4 Hardware Design for $4PR$ in Busy FUs $\ldots$                                                                                                    | 36 |

|     | 4.3        | Overhead Analysis                                                                                                                                       | 39 |

|     |            | 4.3.1 Recovery Control Logic                                                                                                                            | 39 |

|     |            | 4.3.2 L2 Cache Recovery Logic                                                                                                                           | 40 |

|     | 4.4        | Simulation and Results                                                                                                                                  | 41 |

|     |            | 4.4.1 Simulation Setup                                                                                                                                  | 41 |

|     |            | 4.4.2 Reliability model                                                                                                                                 | 42 |

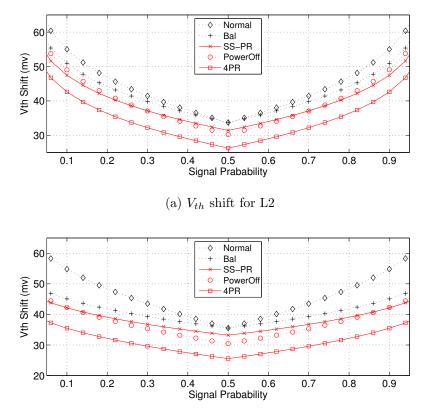

|     |            | 4.4.3 $V_{th}$ shift comparison                                                                                                                         | 43 |

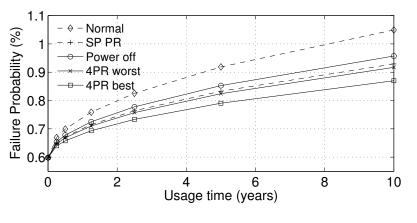

|     |            | 4.4.4 Cell failure probability analysis                                                                                                                 | 45 |

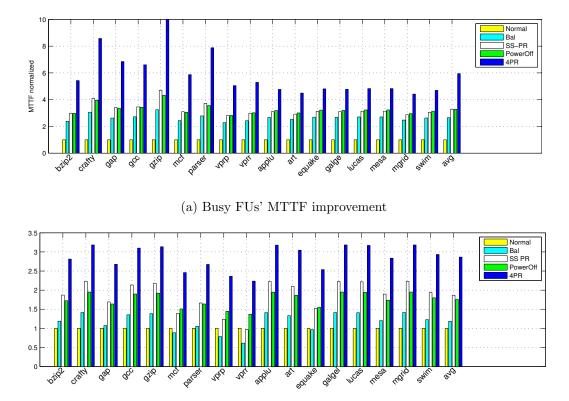

|     |            | 4.4.5 MTTF improvement                                                                                                                                  | 47 |

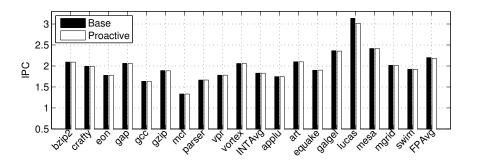

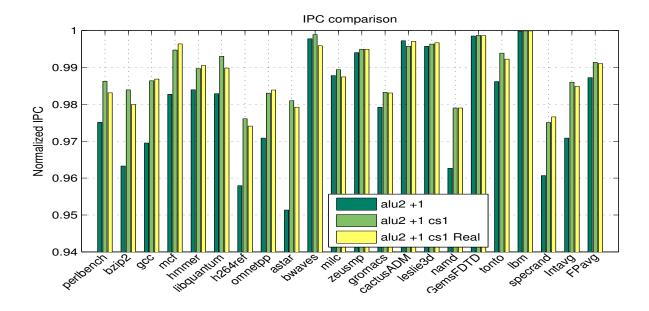

|     |            | 4.4.6 IPC                                                                                                                                               | 48 |

|     | 4.5        | Summary                                                                                                                                                 | 49 |

| 5.0 | GE         | NERIC FUNCTION UNIT                                                                                                                                     | 50 |

|     | 5.1        | Challenges of Function Unit Reliability                                                                                                                 | 50 |

|     | 5.2        | GFU: Generic Functional Unit                                                                                                                            | 51 |

|     |            | 5.2.1 The Overview of GFU Design                                                                                                                        | 51 |

|     |            | 5.2.2 GFU/m: A Macro-based GFU                                                                                                                          | 54 |

|     |            | 5.2.3 GFU/d: A Replication based GFU                                                                                                                    | 57 |

|     |            | 5.2.4 GFU/s: A STT-based Reconfigurable GFU                                                                                                             | 58 |

|     |            | 5.2.5 Integrating GFU in the Execution Stage                                                                                                            | 59 |

|     | 5.3 | Reliability-aware Scheduling                          | 61 |

|-----|-----|-------------------------------------------------------|----|

|     |     | 5.3.1 Step 1: Determine the FU to Recover             | 61 |

|     |     | 5.3.2 Step 2: Minimize Performance Degradation        | 62 |

|     |     | 5.3.2.1 Handling GFU/s based Recovery                 | 62 |

|     |     | 5.3.2.2 Handling GFU/m based Recovery                 | 63 |

|     |     | 5.3.3 Discussion on OS/Compiler reliability scheduler | 71 |

|     | 5.4 | Experimental Methodology                              | 71 |

|     |     | 5.4.1 Architecture Modeling                           | 71 |

|     |     | 5.4.2 GFU/m Circuit Modeling                          | 72 |

|     |     | 5.4.3 Reliability Modeling                            | 72 |

|     | 5.5 | Experimental Results                                  | 73 |

|     |     | 5.5.1 Hardware Overhead                               | 73 |

|     |     | 5.5.2 GFU-introduced Performance Degradation          | 75 |

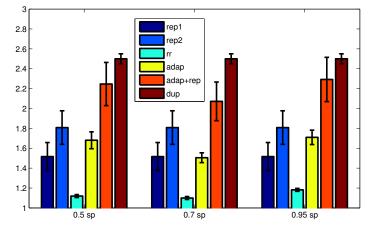

|     |     | 5.5.3 Instruction Steering                            | 79 |

|     |     | 5.5.4 Lifetime Improvement                            | 80 |

|     | 5.6 | Summary                                               | 83 |

|     | 5.7 | Related Work                                          | 83 |

|     |     | 5.7.1 Processor Core Logic Reliability                | 83 |

|     |     | 5.7.2 Reconfigurable Function Unit                    | 85 |

| 6.0 | BI  | Γ FLIPPING IN TDDB RELIABILITY IMPROVEMENT            | 87 |

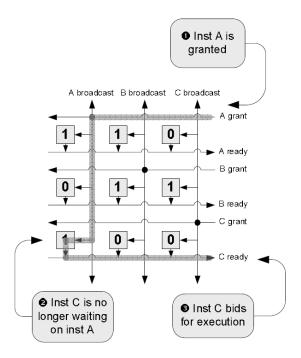

|     | 6.1 | Matrix-based Scheduler                                | 88 |

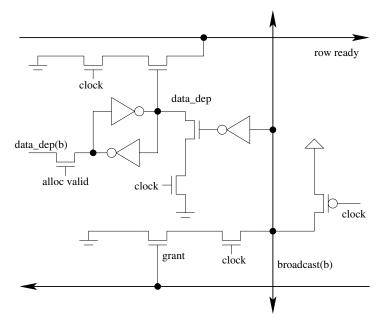

|     | 6.2 | Bit flipping Circuit                                  | 91 |

|     | 6.3 | Bit Flipping Frequency in Multiple Units              | 92 |

|     |     | 6.3.1 Matrix Scheduler                                | 93 |

|     |     | 6.3.2 Cache and TLB                                   | 93 |

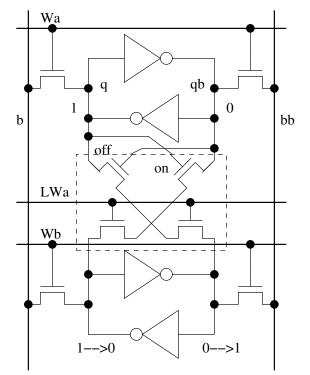

|     | 6.4 | Local Write Circuit for ITLB                          | 94 |

|     | 6.5 | Results                                               | 96 |

|     |     | 6.5.1 Analysis of Local Write Circuit                 | 96 |

|     |     | 6.5.2 LWC Overhead Evaluation                         | 97 |

|     |     | 6.5.3 MTTF improvement for Scheduler and L2 Cache     | 99 |

|     | 6.6 Summary         | • | • |  | • | • |  | • | • | <br>• |  |  | • | <br>• |  | • | • | • | • | • | • | 99  |

|-----|---------------------|---|---|--|---|---|--|---|---|-------|--|--|---|-------|--|---|---|---|---|---|---|-----|

| 7.0 | CONCLUSION          | • | • |  |   | • |  | • | • | <br>• |  |  |   |       |  | • | • | • |   |   |   | 101 |

| BIE | <b>BLIOGRAPHY</b> . |   |   |  |   |   |  |   |   |       |  |  |   |       |  |   |   |   |   |   |   | 104 |

### LIST OF TABLES

| 1  | Overview of Solutions for BTI and TDDB                     | 7  |

|----|------------------------------------------------------------|----|

| 2  | Recovery Comparison                                        | 28 |

| 3  | Energy for test 128_bit $\times$ 256 SRAM bank             | 40 |

| 4  | Processor configurations.                                  | 42 |

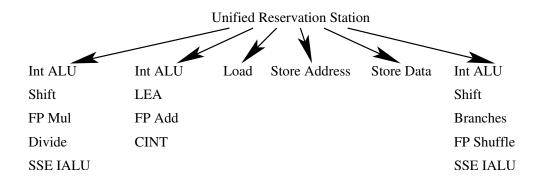

| 5  | Detailed FUs in Super-FU block in Fig. 19 from [26]        | 52 |

| 6  | Control Signals and Added Overhead for Reconfiguring GFU/m | 56 |

| 7  | The extra latency of GFU/m                                 | 57 |

| 8  | Simulation configuration.                                  | 72 |

| 9  | GFU/m Hardware Area/Delay Evaluation                       | 73 |

| 10 | Evaluation of DIV, CRC and AES                             | 75 |

## LIST OF FIGURES

| 1  | Three NBTI modes                                                                               | 11 |

|----|------------------------------------------------------------------------------------------------|----|

| 2  | Vth shift rise/drop in stress/recovery                                                         | 12 |

| 3  | TDDB failure distribution                                                                      | 16 |

| 4  | Standard 6T SRAM Cell                                                                          | 19 |

| 5  | Cell stability                                                                                 | 20 |

| 6  | Proactive recovery circuits                                                                    | 22 |

| 7  | Mode control design                                                                            | 24 |

| 8  | Transition between PR and Normal mode                                                          | 25 |

| 9  | BTI proactive recovery strength                                                                | 27 |

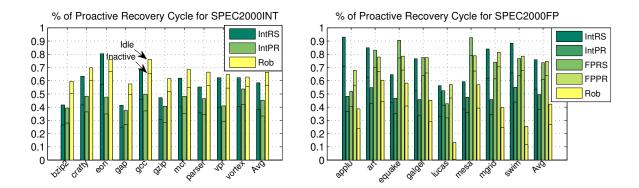

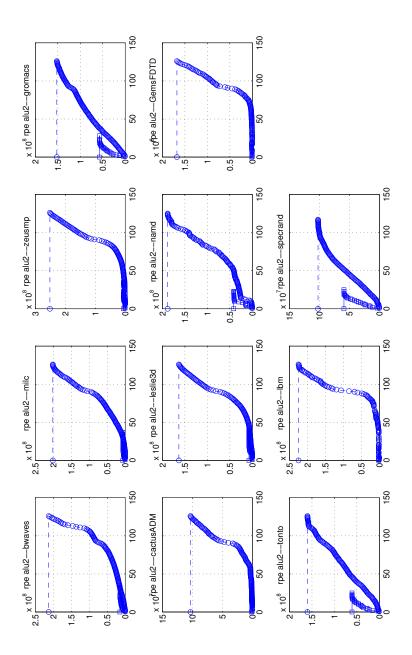

| 10 | Idle time percentages for SPEC2000 INT and FP benchmarks                                       | 33 |

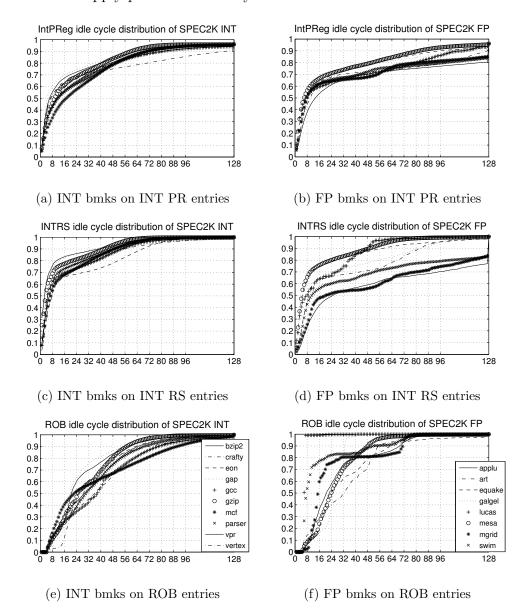

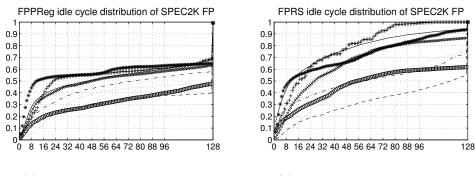

| 11 | Idle time distribution                                                                         | 34 |

| 12 | Idle time distribution                                                                         | 35 |

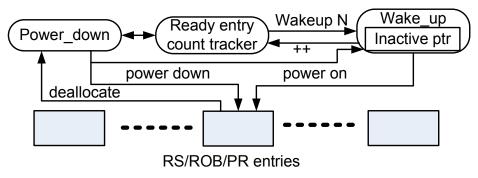

| 13 | Per-entry based recovery control logic.                                                        | 37 |

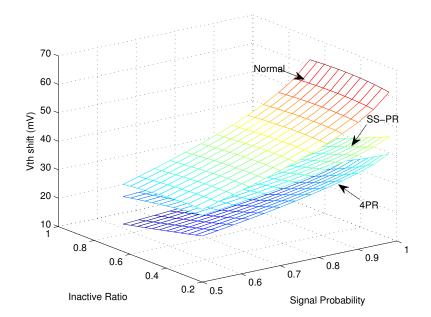

| 14 | $V_{th}$ shift for varying signal probability and inactive ratio $\ldots \ldots \ldots \ldots$ | 43 |

| 15 | $V_{th}$ degradation for L2 and FU                                                             | 44 |

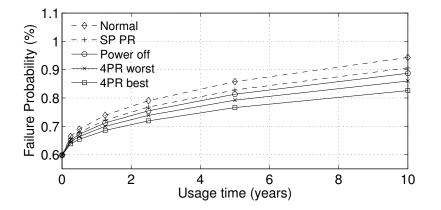

| 16 | Failure probability analysis.                                                                  | 46 |

| 17 | MTTF Improvement                                                                               | 47 |

| 18 | Impact of proactive recovery on IPC.                                                           | 49 |

| 19 | Intel Nehalem-like core execution units from [11]                                              | 52 |

| 20 | FU usage examples in 3 groups.                                                                 | 53 |

| 21 | GFU/m Structure                                                                                | 55 |

| 22 | Integrating GFU in the execution stage                                                         | 60 |

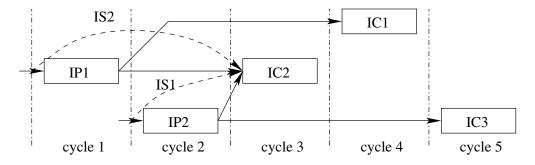

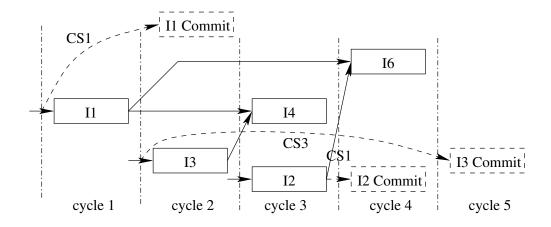

| 23 | A simple instruction dependency graph                                          | 64 |

|----|--------------------------------------------------------------------------------|----|

| 24 | Issue Slack                                                                    | 65 |

| 25 | Commit Slack                                                                   | 66 |

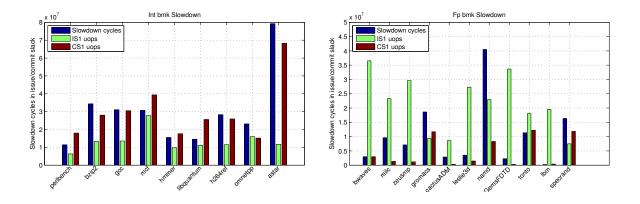

| 26 | Comparisons of Slowdown Cycles and IS1 CS1 Instructions                        | 67 |

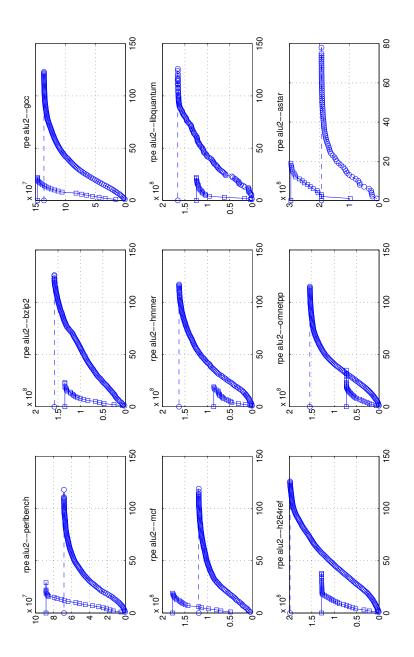

| 27 | $\rm CS1/\rm CS2+$ instruction count vs distance to ROB tail (INT bmk) in ALU2 | 68 |

| 28 | CS1/CS2+ instruction count vs distance to ROB tail (FP bmk) in ALU2 $$         | 69 |

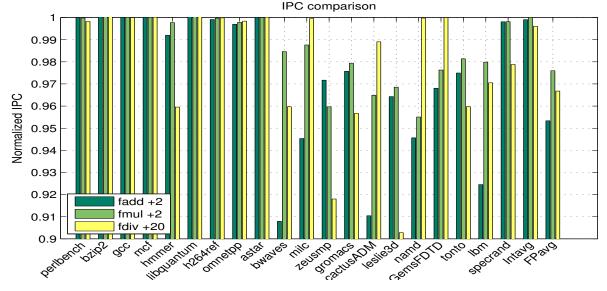

| 29 | Normalized IPC when FP Add/Mul/Div gets replaced respectively                  | 76 |

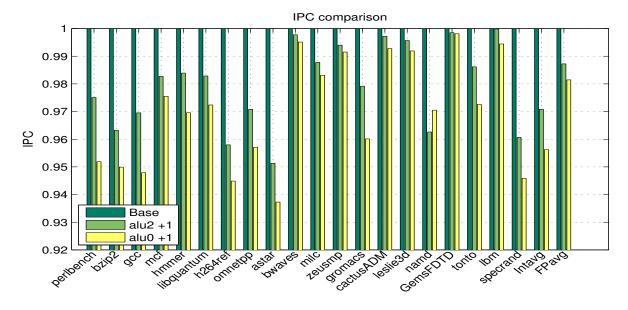

| 30 | Normalized IPC when ALU2/0 gets replaced respectively.                         | 77 |

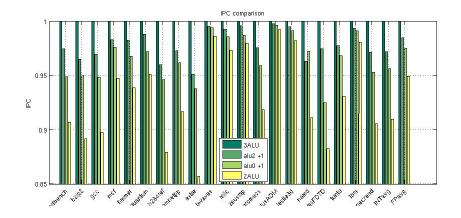

| 31 | 2 ALUs vs 3 ALUs                                                               | 79 |

| 32 | Performance overhead reduction of using instruction steering                   | 80 |

| 33 | MTTF improvement                                                               | 81 |

| 34 | Wakeup Matrix in [63]                                                          | 89 |

| 35 | Wakeup Matrix Circuit in [63]                                                  | 90 |

| 36 | Bit Flipping Support in Wakeup Matrix Circuit                                  | 92 |

| 37 | Signal Probability in Wakeup Matrix                                            | 93 |

| 38 | Update Count for Multiple Structures                                           | 94 |

| 39 | Local Write Circuit                                                            | 95 |

| 40 | Update Activity of ITLB with Local Write Circuit                               | 96 |

| 41 | ITLB MTTF with Local Write Circuit                                             | 97 |

| 42 | Comparison of RFW and LW Power in ITLB                                         | 98 |

| 43 | MTTF Improvement for Scheduler and L2 Cache                                    | 99 |

#### ACKNOWLEDGEMENT

I'm holding my breath writing these words since it's after years of dedicated work in computer architecture research. This thesis is not possible without generous support from my advisors, as well as professors in committee and others from the Department of Electrical and Computer Engineering. Doing research in Ph.D study is a long and lonely journey. It's long because one has to master both the breadth of literature and depth of certain field before truly understand the important problems and whether they are low hanging fruits (usually they are not since other smart and competitive researchers already took them). It's lonely because the further one search and ponder, he will find himself the only one crawling in tunnel with uncertainties. He has be creative to figure ways out so he is making contribution at the end of journey.

Thanks to all supports from my advisor Prof. Yang and co-advisor Prof. Zhang who relentlessly devote their time and effort in guiding me researching frontiers of computer architecture. Prof. Yang always trusts her students' potential and gives invaluable advice in all respects to encourage them to achieve fully, since she is a perfect role model of diligence and endless pursuit for perfection. In 1:1 and group meetings I learned how to think and work like a researcher. Prof. Zhang has endless sharp insights and rigorous investigations in discussions. Without their support this thesis is nowhere close to existence.

I owe my gratitude to professors in committee. Prof. Cho introduced the computer architecture foundation in my early Ph.D study and has always been very constructive and nice in all seminars I attend. Prof. Levitan set high standards and guides my work to be solid and at high level. Prof. Wang shared valuable perspective and suggested revision for easier access. Their advice and suggestions are essential to this thesis. Also I learned a lot from Prof. Levitan, Prof. Jones, Prof. Mickle and Prof. Yang with which I spent many hours in teaching undergraduate students in labs and lecture classes. They showed the passion when sharing knowledge as well as the way of thinking to students. I must thank my colleagues and friends that I have been working with in my course of my Ph.D study, Xiuyi Zhou, Ping Zhou, Bo Zhao, Yi Xu, Lei Jiang, Vicky Li and Yu Du. I enjoyed the time spent together discussing research as well as relaxing. I also get a lot of help from them. With them I'm not lonely any more.

At last and most importantly, many thanks to my wife, Xi Yang and our little son, Austin. You are always supportive in everyday life for my decision to pursue the Ph.D. I'm not alone, and this thesis is for also you.

#### 1.0 INTRODUCTION

#### 1.1 THESIS TOPIC

As technology scales, computer hardware is increasingly susceptible to both soft and hard errors. Soft errors are transient malfunctions (bit flip in memory and timing error in execution path) due to external random disturbance such as high energy particle strike, temperature and voltage fluctuations. Soft errors are more likely to happen in smaller gates: it takes less energy to flip one bit in smaller gates with lower voltage and there are even more multi-bit soft errors [68], as observed in both memory and execution units. Hard errors are hardware defects induced both in manufacture and in-field aging. Smaller gates with thinner oxide are stressed under stronger electrical field and higher power density. Together with temperature, voltage and process variations, both yield loss and aging problems become increasingly severe. Consequently, reliability caused by both soft and hard errors becomes more important than ever.

The soft error detection and correction have been studied extensively in past. The random nature of soft errors makes them correctable by re-execution from checkpoints once errors are detected [12] in execution path, or by ECC in memory. Although expensive, checkpointing and re-execution circuits are used in high-end mission critical microprocessors. The techniques for soft errors are well established and not the topic of this thesis.

The hard error detection and correction are becoming more challenging in scaling technology. Hard errors include both function faults and parametric faults, and both may occur in manufacture and in-field use. Defects in manufacture are inevitable and the root cause of yield loss. Besides function faults, process variation in manufacture also incurs parametric faults: although circuits are functional, parameters such as performance and power fail to meet target. Both functional and parametric faults in manufacture reduce effective yield and increase chip cost.

At runtime, circuits degrade under stress of multiple aging mechanisms on gates during in-field use. Bias Temperature Instability (BTI), Time Dependent Dielectric Breakdown (TDDB), Hot Carrier Injection (HCI), etc (discussed further in Section 2) are such mechanisms. Some mechanisms (TDDB) introduce permanent functional faults, while others (TDDB and BTI) exacerbate parametric faults, jeopardizing the lifetime of a processor. New generations of technology with stronger electric field due to thinner dioxide and higher operating temperature exacerbate the reliability across the entire processor including both memory and logic structures.

This thesis focuses on aging induced parametric hard errors (BTI) and functional hard errors (TDDB and BTI). Soft errors and manufacturing time hard errors are not covered. Based on the unique characteristics of BTI and TDDB, circuit and architectural level techniques are designed to alleviate circuit aging process and improve microprocessor lifetime. A brief overview of current status in academia and industry is discussed to map the thesis contribution in general picture of microprocessor reliability.

#### 1.2 MICROPROCESSOR RELIABILITY RESEARCH OVERVIEW

The microprocessor reliability problem has attracted extensive efforts in past decades for tackling soft and hard errors. Different designs are proposed in memory based and random combinational units due to different structure and complexity by incorporating redundancy. Memory based structures are generally regular and it is straight forward to apply minor redundancy to improve reliability. Random combinational structures such as function units in execution stage are irregular and low overhead redundancy is generally not practical or available. This section briefly discusses existing methods that mitigate aging induced errors in memory based and random combinational circuits.

#### 1.2.1 Memory based Structure Reliability Improvement

Memory based structures such as on-chip caches, branch predictors, register files, TLBs are critical since they store important state information. They occupy large chip area (over 50%) and are more vulnerable to soft/hard errors. Due to the regular and repetitive structure in data array, memory units are typically protected by Error Correction Code (ECC) and simple redundancy (spare bits, lines) from hard errors (both induced in manufacture and in-field again) and soft errors, at minor to moderate overhead in chip area.

Error correction code (ECC) is widely used to detect and correct soft/hard errors in memory structures. Single Error Correction Double Error Detection (SECDED) Hamming code is light weight and effective to detect at most 2 errors and correct 1 error. The SECDED encoding and decoding add extra cycles in data access, and were traditionally used in lower memory hierarchy such as L2/L3 and main memory where extra latency is amortized in overall longer access latency than L1 cache.

Recently, many variants of ECC are proposed in different scenarios. 2-D ECC [34] uses ECC in columns as well as rows to tolerate more bits in one row or column. Multi-bit ECC [76] use stronger BCH code such that up to 5 bit errors are correctable in eDRAM with lower refresh frequency. [84] claims error detection is critical and more frequent but error correction is less likely and proposes splitting error detection on chip and error correction off chip.

Besides ECC, another approach to improve memory reliability is adding light weight redundancy such as extra bits, columns, and rows as backup or spare. The spare components are reconfigured to replace defective ones in test stage to improve yield. [77] proposes one method to combine multiple defective lines to form one functional logic line. All above techniques take advantage of regular memory structure and lightweight error detection and correction to tolerate errors with minor overhead.

#### 1.2.2 Logic Structure Reliability Improvement

Contrary to the regular memory based structure with mild and effective redundancy, irregular, non-memory core logic structures impose obstacles to detect and correct errors. They cannot be protected using ECC, as errors manifest as faulty execution rather than faulty stored bits. Tremendous efforts for improving core logic reliability can be coarsely grouped to 2 categories: handling soft errors and handling hard errors.

Soft errors in core logic are tolerable by check-pointing and re-execution that is first proposed in Razor [12]. Shadow latch is used to detect timing errors in execution path, and the stage with error is re-executed from checkpoints after the pipeline is stalled and flushed. Although the recovery is expensive in terms of performance due to the pipeline flush and check-pointing, as long as timing errors are rare, the performance degradation is tolerable while the performance improvement is significant by eating-up conservative guard-bands and aggressively running microprocessor faster than specification with increasing minor risk of errors. Hence, Razor uses minor time redundancy to improve reliability and it usually works well for soft errors which occur randomly.

However, for hard errors, re-execution does not work since the error tends to happen again on the faulty hardware and even infinite re-execution could not make it correct. For timing related parametric errors, reducing the frequency is a remedy by trading off performance. While for functional hard errors, redundancy of different granularity (core, function unit) is necessary to improve reliability.

The present multi-core processors provide natural redundancy at the core level. A core can be disabled if errors are found post fabrication, resulting better yield than abandoning the entire chip. Considering throwing away faulty cores is too expensive, [55] and [3] try to salvage and use faulty cores: [55] observes some faulty function units are not frequently used and it's safe to run applications that do not utilize the faulty FU on the core; [3] observes a faulty core is likely to be an animator core in sufficient long period and provides useful hints to accelerate the execution of normal cores.

In a similar vein, a coarse-grained replication using Triple Module Redundancy (TMR) is adopted for highly reliable and mission critical systems [2, 6]. Although core-level or coarse-grained redundancy achieves high fault coverage, they are often over-designed and unnecessary, as a fault may occur in only one functional unit (FU) and it is unlikely that all FUs are faulty. Replicating a large area of logic is hence not cost-effective. However, fine-grained redundancy at the FU level is also challenging as it is difficult to determine which

FU is most vulnerable at design time, and which FU is stressed most online. Protecting irregular logic structure with redundant is not trivial task in terms of complexity and cost.

#### 1.2.3 Aging Induced Reliability Issues

Previous study on microprocessor reliability focus on soft errors and manufacture time hard errors. Recently with technology scaling aging mechanisms receive a lot of attention and become emerging sources for reliability problems. Multiple aging mechanisms discussed in Section 2 stress circuits and finally cause parametric and function errors and compromised lifetime.

Although existing methods in above discussions could be used to tolerate aging induced hard errors as well as other errors, they are not quite effective in extending lifetime if only used after hard errors occur. Many research works take a promising path that proactively mitigates the degradation on circuits to slow down aging mechanisms, which is also the key topic of this thesis.

Since aging mechanisms (BTI and TDDB) are highly dependent on voltage and temperature (more details in Chapter 2), circuit level voltage tuning and architectural level scheduling are straight forward and effective approaches. [70] tried to hide and slow down aging by 1) steering hot jobs on faster cores and cold jobs on slower cores; 2) changing voltage by adaptive scaling voltage (ASV) and threshold voltage by adaptive body bias (ABB). [32] uses finnier granularity dynamic voltage scaling to slow down NBTI aging in core logic.

Besides circuit level methods, architectural level methods for mitigating NBTI are proposed since threshold voltage degradation caused by NBTI depends on signal probability: alternating "0" and "1" on PMOS is stressed less than always "0" on PMOS. [1] utilizes idle cycles to recover NBTI induced degradations by balancing signal probabilities on gates, which is be quite effective. [16] studies NBTI stress in context of process variation (PV). Due to PV, some FUs are inherently weaker, slower and vulnerable to NBTI stress. By using the vulnerable FU less and the robust FU more, the vulnerability difference initially introduced by PV is evened out in field use and the lifetime is greatly improved.

#### 1.2.4 Reliability Design Challenges for Future Technology

Although this thesis focuses on current 28nm technology (High-k and bulk), the 20nm SOC and 14nm FinFET are coming in following years. [35] discusses the design challenges due to reliability on VMIN/VMAX, wires and CMOS devices. BTI is still a problem and gets worse in limiting the VMIN. Also the TDDB is worse since the new effect of TDDB that increases the sensitivity of 1x BEOL metal pitch to bias-temperature stress finally limits VMAX. For wires the electro-migration (EM) is also a worse problem with smaller interconnect cross-sections and higher current. Although the next generation fully-depleted FinFET devices improve performance at lower voltages, the FinFET device quantization poses challenges for 6T embedded SRAM memory in that it's more difficult to balance both write and read margins. With technology advancing, the reliability keeps challenging for processor designers.

#### 1.3 RELIABILITY DESIGN IN STATE-OF-ART MICROPROCESSOR

Not only in academia, many microprocessor manufactures also become aware of the increasing challenging reliability issues, and reliability features are added in core logic and memory although more complexity and cost are incurred. In IBM zEnterprise CPU [75], extensive parity and residue error checking are employed against soft errors, which adds roughly 20 to 25% to core logic area. In Intel Itanium Poulson [60], residue protection and radiation hardened sequential latches are implemented on key logic and data-path. Despite large area is devoted to recovery circuits, it is necessary for these high-end processors to guarantee top level reliability.

Stronger ECCs are also implemented in high-end microprocessors. In Intel Westmere CPU [64], heavy portion of area is dedicated to ECC. The L3 cache data arrays are strengthened with Double Error Correcting, Triple Error Detecting codes (DECTED), and tag arrays are protected using Single Error Correcting, Double Error Detecting (SECDED) codes. In Intel Itanium Poulson microprocessor, L3 cache are protected by DECTED, MLI/MLD data are protected by SECDED code. Even the register file have extensive parity and interleav-

| Degradation | Memory based Structure        | Combinational Logic Structure |

|-------------|-------------------------------|-------------------------------|

| BTI         | 4PR and application           | GFU                           |

| TDDB        | Voltage↓, Bit Flip Frequency↑ | Voltage↓, GFU                 |

#### Table 1: Overview of Solutions for BTI and TDDB

ing parity. Niagara T4 use ECC on register files, coherency states and all cache hierarchies. Although stronger ECCs incur higher complexity, area and cost, it is worthy to implement to overcome the reliability problems.

State-of-art high-end mission critical processors require reliability aware design and recovery, while it's not common practice yet for commercial processors. With the technology scaling and increasingly worsen reliability issues, a lightweight and effective reliability aware design technique is required for commercial processors.

#### 1.4 CHAPTER OVERVIEW

The literature study shows extensive efforts have been invested to mitigating aging in both memory based and random combinational structures. However, most existing techniques only target NBTI induced degradation and only natural recovery (to be discussed shortly in Chapter 2) is exploited to enhance reliability. The recently surfaced and equally important PBTI becomes another important reliability issue and should be addressed properly. Moreover the faster, more effective proactive BTI recovery is left unnoticed and hardly exploited. Besides BTI, another important degradation mechanism, TDDB, although a hot topic in device community, hasn't received enough attention in circuit and architecture community so far. This thesis targets in solving the emerging aging induced reliability issues in both memory based and random combinational structures in modern complex out-of-order cores.

Table 1 illustrates the overview of solutions for BTI and TDDB degradations on memory based and combinational logic structures. For the BTI stress on memory based structure, 4PR, an innovative BTI proactive recovery mode for SRAM cell is implemented in Chapter 3. And the application of 4PR in cache banks and storage entries of function units in out-oforder core is elaborated in Chapter 4. For combinational logic units, GFU is carefully designed and implemented to replace the vulnerable logic unit under recovery with minimal overhead and it works for both BTI and TDDB stress. The bit flipping technique is designed to mitigate the TDDB stress on memory based structures.

Chapter 2 studies the characteristics of two dominating aging mechanisms, BTI and TDDB. A favorable feature of BTI (both PBTI and NBTI) is its recovery mode, i.e, when the gate is off its shifted threshold voltage induced by BTI stress is partially recovered which we denote as natural recovery mode. A faster and more effective recovery mode (proactive recovery) is achieved when reverse bias is applied based on which Chapter 3 further develops 4PR to be used in Chapter 4. For TDDB, the bit flipping frequency dependence makes the reliability improvement possible: under faster bit switching the TDDB stress is less. This feature provides the clue to tackle TDDB problem in memory based structure in Chapter 6. When such features are not practical to use, Chapter 5's GFU framework resort to shutting down the FU for natural recovery or stopping stress.

In Chapter 3, an innovative proactive recovery mode, 4PR, is designed. The 4PR is motivated by the fact that both NBTI and PBTI are important in high-k metal gate technology. The effect of both NBTI and PBTI on read flip failure, write failure and access time failure are discussed. Results show PBTI dominates the most likely access time failure and a 4PR address the requirement by proactively recovering all 4 gates in a 6T SRAM cell. HSpice simulation shows 4PR is an effective and low overhead circuit technique to improve BTI reliability.

In Chapter 4, 4PR mode is applied in cache and storage cells in Out-of-Order pipeline. A spare bank is added in L2 cache to replace the bank under 4PR. However, applying 4PR in storage cells in pipeline is hard since re-routing the busy function units as register files and reorder buffers incurs large performance overhead. Inspired by [1], per-entry level idle cycles are exploited to apply 4PR. Results show there are abundant idle cycles, and combining effective 4PR, significant reliability improvement is achieved.

In Chapter 5, Generic Function Unit (GFU) is designed to utilize natural recovery and stopping stress to improve the reliability of function units in execution stage. 4PR can not be easily used for function units due to the irregular structure of combinational logic. Instead an extra GFU is added to provide fine-grain function unit level redundancy to facilitate using natural recovery for BTI and stopping stress for TDDB. GFU has high fault coverage due to its flexibility: it can be configured as most FUs. Depending on different usage FUs are partitioned into 3 groups and GFU is accordingly designed to cover most FUs in 3 groups. Also GFU has low area overhead since it only targets 1 or 2 FUs at a time instead of using spare copies for all FUs which incurs 100% area overhead. An important design issue is how to reduce the performance overhead when the generally slower GFU is introduced. Evaluation shows performance overhead is small and further reduced by steering less critical instructions to GFU. The reliability lifetime improvement is significant for the combinational logic units.

In Chapter 6, reliability loss due to TDDB stress in processor core is studied with focus on memory based structures. Although voltage scaling can be applied on many less busy units to mitigate TDDB stress, some structures on critical path that is used in every cycle can not use voltage scaling. Scheduler, ITLB and L1 cache are identified to be such structures that voltage scaling is not feasible due to potentially significant performance overhead. Based on the frequency dependent TDDB stress, the bit flipping circuit is implemented to increase the bit flipping frequency as an essential alternative to mitigate TDDB stress. Results show in many units the entry update activity is sufficiently frequent to utilize the bit flipping circuit. However, one exception is ITLB in which the natural bit flipping frequency is extremely slow. Then the local write circuit is designed to enable proactive bit flipping, although the area overhead is not non-negligible. Evaluations show promising lifetime improvement in scheduler, cache and ITLB.

#### 2.0 DEGRADATION MECHANISMS

In scaled technologies, although transistors are smaller, faster and consume less power, they tend to suffer intense and severe stress due to thinner gate oxide, stronger electric field, and higher temperature. Bias Temperature Instability (BTI) and Time Dependent Dielectric Breakdown (TDDB) are two such degradation mechanisms. BTI stress increases threshold voltage and hence propagation delay is larger and memory cell is less stable. TDDB stress gradually increases leakage current and finally gate oxide breaks down such that gates fails to control channels conductivity. In this chapter we discuss unique characteristics of BTI and TDDB that are to be used in circuit or micro-architectural level techniques in following chapters to slow down aging and improve reliability. Although there are other degradation mechanisms such as Hot Carrier Injection (HCI, not as severe as BTI [49]) and Fowler-Nordheim tunneling (FN, stress floating gate in FLASH), due to less severity, they are not discussed further in the thesis.

#### 2.1 BIAS TEMPERATURE INSTABILITY: BTI

#### 2.1.1 NBTI and PBTI

BTI includes NBTI (Negative BTI) on PMOS transistors and PBTI (Positive BTI) on NMOS transistors. For traditional SiO2 dielectric technology, NBTI has been identified as the dominant stress mechanism while PBTI is negligible. Efforts have been taken to study NBTI intensively. These include NBTI modeling [72], studying its impact on circuits [30, 37], and designing mitigation methods [37] for PMOS gates.

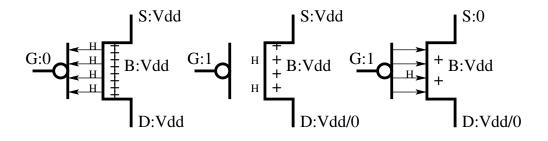

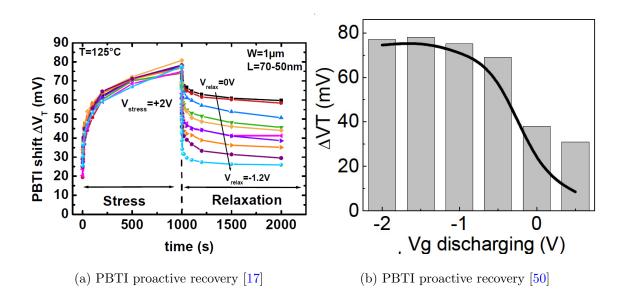

Figure 1: Three NBTI modes: Stress (left), Natural Recovery (middle), Proactive Recovery (right). PBTI has similar 3 modes. Proactive recovery is both faster and stronger than Natural Recovery

In sub-45nm technologies, high- $\kappa$  metal-gate stack is widely used to gain high speed and low leakage. For example, Intel Westmere-EX Xeon and Itanium Poulson use 32nm high-k technology. Instead of using silicon dioxide  $(SiO_2)$  as the dielectric and poly-silicon gate, the new stack is composed of high- $\kappa$  material dielectric and the metal gate, with a very thin layer of  $SiO_2$  in between. The high- $\kappa$  material has higher relative dielectric constant than that of  $SiO_2$ . The metal gates are used on top of the high- $\kappa$  dielectric. With the new stack structure, scaled gates are less leaky while keeping high performance.

In high- $\kappa$  metal gate stack, the NBTI occurs in PMOS transistors when the input of the gate is "0" at elevated temperature, as shown in the leftmost case in Fig. 1. Similarly, the PBTI occurs in NMOS transistors with the gate input "1". In short, the gates are stressed under BTI when ON, for both PMOS and NMOS. Under BTI stress (negative/positive gate-source bias i.e.,  $V_{gs} = -/+V_{dd}$  for PMOS/NMOS), a series of physical-chemical processes are triggered such that 1) positively charged traps are created in interface of  $SiO_2$  and SI near the gate oxide [85] for NBTI; 2) negatively charged traps are created in the added high- $\kappa$  dielectrics for PBTI. These traps raise the threshold voltage, which gradually slows down the gate transition speed and reduces the noise margin of the circuit. Eventually the circuit will fail as the transistors become too slow to meet the timing or stability requirement. Studies showed that BTI-induced failure becomes more severe under higher temperature and stronger electric field [67].

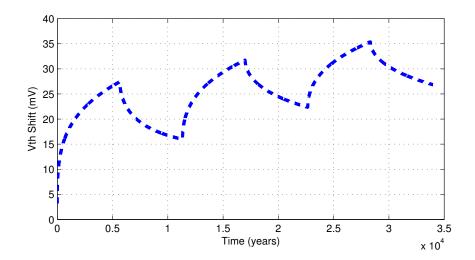

Figure 2: Vth shift rise/drop in stress/recovery in 3 iterations with 50% signal probability. This is also called AC stress, compared to continued stress called DC stress

However, the reliability of the high- $\kappa$  metal gate stack is yet to be solved. For  $SiO_2$  dielectric, NBTI in PMOS has been identified as the limiting reliability issue, while the effect of PBTI in NMOS is negligible. For high- $\kappa$  metal-gate stack, recent measurements [86] on  $V_{th}$  shift show that NBTI in PMOS is as severe as that in  $SiO_2$ /poly-silicon. Moreover, the effect of PBTI in NMOS is now comparable to NBTI in PMOS. While there are works on PBTI measurements and modeling [86, 28], only limited attempts have been conducted to studying the impact of PBTI on circuits and its mitigation methods for high- $\kappa$  material.

#### 2.1.2 BTI Recovery Modes

Besides stress mode, one key characteristic of BTI is two recovery modes, which have been investigated to increase the lifetime of transistors. We use NBTI on PMOS as example. The first recovery mode, referred as *Natural Recovery*, is shown in the middle case of Fig. 1. It happens when the input of the gate is "1" with normal  $V_{dd}$ . This is the mild recovery used in [1]. When the input changes to "1", the negative bias stress is removed, the traps in the gate oxide near the interface are healed, and the NBTI degradation on the  $V_{th}$  of PMOS can be recovered partially. Note that when the input switches between logic "0" and "1" on the gate, the PMOS transistor undergoes an alternation of stress and recovery, as shown in Fig. 2.

A stronger and faster recovery mode for PMOS transistors, referred as *Proactive Recovery*, is shown in the last case of Fig. 1. It uses positive voltage bias, i.e.,  $V_{gs} = V_{dd}$  [45] and forces the gate input to be "1" and S terminal to be "0". The MOS transistor cannot enter the strong recovery mode in normal operation since (1) the S terminal of the PMOS is connected to physical  $V_{dd}$ ; (2) even if S terminal can be driven to ground, the gate voltage is discharged through the preceding PMOS and cannot be kept at "1". Therefore the cell circuit needs to be revised properly to enable proactive recovery.

The recovery mechanisms of NBTI used to mitigate the degradation are also observed for PBTI in high- $\kappa$  dielectrics in experimental conditions. For example,  $V_{th}$  shift under PBTI is naturally healed after removing the stress and making  $V_{gate}$ , or  $V_g = 0V$  [29, 28], which is same as "Natural Recovery" in NBTI. Stronger and accelerated recovery is achieved when an inverse bias (discharge bias in [28, 50]) is applied to  $V_g$ .

Thus, the impact of NBTI is determined by the operation of the circuits, and varies with different applications, or diffident phases in one application. An early analytical study [38] showed that the NBTI progress is determined by the signal probability of the input signal being "0", temperature and supply voltage, but independent of how frequently the transistor switches between "0" and "1". As a result, having sustained recovery span is as equally effective as having interrupted recovery periods as long as their accumulated recovery cycles are the same.

Both NBTI and PBTI are caused by high temperature, strong electric field, and most importantly, high stress duty cycles. Typical recovery schemes for NBTI exploit the opportunity to maximize the recovery cycles for PMOS gates [16]. However, in the presence of both NBTI and PBTI, the duty cycles for NMOS and PMOS are complementary: a gate input of "1" incurs stress on an NMOS and recovery on PMOS, while a gate input of "0" incurs recovery on NMOS and stress on PMOS. Therefore, maximizing (natural) recovery cycles for one type of gate could stress the other gate even more. For SRAM cells, [4, 5] showed that PBTI has a larger impact than NBTI on the degradation of a SRAM cell under the worst case BTI stress. This has made previously designed NBTI-oriented mitigating techniques inadequate, and calls for the development of new schemes for high- $\kappa$  based circuits.

#### 2.1.3 BTI Modeling

Although detailed and accurate BTI modeling and search the root of BTI mechanism are continued efforts in device and reliability research community, circuit level modeling often use a simplified model, which just describes the relationship of resulting threshold voltage shift and parameters such as temperature, voltage and signal probability.

A BTI model [43] shows the relationship of time to failure due to BTI  $(TF_{BTI})$  and parameters such as temperature and voltage in Equation 2.1([43]).  $A_{NBTI}$  is transistor's gate-oxide area, T is temperature,  $V_{gs}$  is gate-to-source voltage. Details of temperature functions  $B_1(T)$  and other parameters are discussed in [43].

$$TF_{BTI} = A_{NBTI} V_{gs}^{-\frac{1}{\beta_1}} B_1(T)$$

$$(2.1)$$

Although reducing temperature and voltage [70] has been demonstrated to be effective to slow down BTI aging, our techniques focus on proactive recovery during idle cycles. Thus, we use a more accurate model proposed in [31], in which the  $V_{th}$  shift under AC NBTI stress is calculated by Eqn (2.2).

$$\Delta V_{t,AC} = K_{AC} \cdot t^n = \alpha(S, f) \cdot K_{DC} \cdot t^n \tag{2.2}$$

Here  $K_{DC}$  is the technology dependent constant.  $\alpha(S)$  is the AC factor determined by the signal probability of the cell S (extracted from architectural simulations), independent of operating frequency f.  $\alpha(S)$  is calculated using the multiple cycle stress and recovery model: the stress phase is modeled by the popular accepted power-law model with the exponent n = 0.16 for P/NMOS [28, 19]; the recovery phase is modeled according to [72]:

Stress:

$$V_{th}(t) = \sqrt{K^2(t-t_0)^{\frac{1}{2}} + V_{th}(0)^2}$$

(2.3)

Recovery:

$$V_{th}(t) = V_{th}(0)(1 - \sqrt{\eta(t - t_0)/t})$$

(2.4)

The  $V_{th}(t)$  is  $V_{th}$  at time t when the stress or recover mode begins at  $t_0$  with the  $V_{th}(0)$ . The parameters  $\eta$  for P/NBTI under natural and proactive recovery are individually calibrated to match the experiment data in [58]. This model would be used in evaluations in following chapters.

#### 2.2 TIME DEPENDENT DIELECTRIC BREAKDOWN: TDDB

Gate-oxide breakdown is another important failure mechanism in CMOS technologies [43]. TDDB stress experiences 3 stages: soft break down (SBD), wear out (WO) and finally hard bread down (HBD). When gate is on, SBD happens when two-trap perlocation cluster is created due to tunneling current flow though gates. SBD could be detected as an abrupt current increase. Although gate leakage current due to SBD is negligible, it starts the WO process on percolating path. At operating conditions where the gate leakage current increase due to SBD is negligible, the WO phase becomes the dominant factor in degradation. At the end of WO, HDB happens. The gate-voltage controllability is lost which further results in excessive dissipated energy or even thermal runaway.

In high- $\kappa$  metal gate technology, TDDB degradation is much worse than traditional poly-Si technology [61]. In high- $\kappa$  technology, the runaway phase in WO is much faster than that in poly-Si technology, resulting greatly reduced reliability margin. Ultra-thin gates with high- $\kappa$  dielectric, high temperature and high voltage accelerate the TDDB failure rate and hence TDDB is also a serious degradation mechanism.

Although TDDB is at least as important as BTI, it received much less attention than BTI. Unlike the interesting characteristics such as signal probability dependence and proactive recovery in BTI, people conceived that TDDB is only highly dependent on temperature and voltage, and circuit techniques to reduce temperature/voltage suffices are used to slow down aging. However, recent research shows an interesting characteristic of TDDB, Frequency Dependent Stress, which is to be exploited in this thesis to improve TDDB reliability.

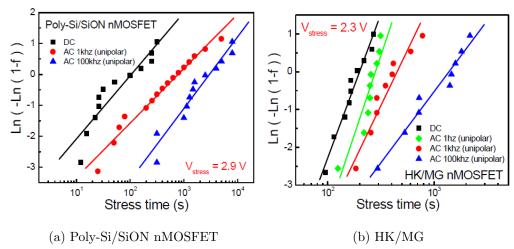

#### 2.2.1 Frequency Dependent Stress

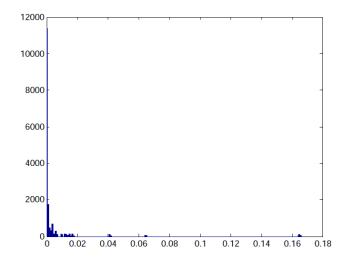

Recent experiments [41] show TDDB degradation depends on bit flipping frequency. In Fig. 3(a) and Fig. 3(b), both poly-Si/SiON and HK/MG suffer less TDDB degradation under unipolar AC stress over DC stress in accelerated test with 2.9V and 2.3V stress. The degradation is further reduced when higher AC stress frequency used. For example in HK/MG, the lifetime improvement is 1.8x/3.5x when frequency increase from 0 to 1Khz and to 100KHz. According to [41], the frequency dependency is due to that trapped charges in HK can easily be detrapped once a relaxation bias is applied. This new interesting and favorable finding motivates circuit and micro-architectural level designs to slow down TDDB degradation.

Figure 3: TDDB failure distribution under DC and unipolar AC stress for poly-Si/SiON (a) and HK/MG (b) [41]. In both cases the unipolar AC conditions exhibit longer time to breakdown than DC conditions.Vertical axis is accumulative failure probability in Weibull distribution.

#### 2.2.2 TDDB Modeling

Extensive researches show SBD is Weibull distributed and voltage acceleration accords to a power law. The time to failure due to TDDB  $(TF_{TDDB})$  under different temperature, voltage gate area is calculated in Eqn 2.5.  $A_{TDDB}$  are transistor's gate-oxide area, T is temperature,  $V_{gs}$  is gate-to-source voltage. Details of temperature functions  $B_1(T)$ ,  $B_2(T)$ and other parameters are discussed in [43].

$$TF_{TDDB} = A_{TDDB} (\frac{F}{A})^{-\frac{1}{\beta_2}} V_{gs}^{a+bT} B_2(T)$$

(2.5)

Eqn. 2.5 with the parameters in [43] shows the strong and sensitive dependence of TDDB lifetime on supply voltage: reducing 0.1V supply voltage improves the TDDB lifetime by 100x, as confirmed in [61]. Hence less frequently used or less critical function units such as last level cache would enjoy extended TDDB lifetime by just reducing supply voltage. However, for frequently used and busy function unit where reducing voltage incurs intolerable performance loss and temperature is usually high, the bit flipping technique could be used to improve TDDB lifetime.

However, the frequency dependency is not modeled in Eqn. 2.5 and no available such models are proposed so far. In evaluations in following chapters we treat Eqn. 2.5 as baseline lifetime estimations, and use calibrated parameters in Fig. 3 ([41]) to evaluate the benefit of increasing bit flipping frequency.

#### 2.3 SUMMARY

This chapter discusses BTI and TDDB degradation mechanisms in traditional poly-Si and latest high- $\kappa$  technology. BTI, TDDB that were tolerable in traditional technology become a more serious threat to device, circuit, chip and system reliability. Accurate models show that temperature, voltage, stress patterns play important role in degradation. Properly adjusting temperature, voltage, and stress patterns paves a way to alleviate degradation and improve lifetime of microprocessors. The BTI natural and proactive recovery modes are exploited in chapter 3 and 4 to improve the SRAM cell based structures, both in cache and in entries in pipeline such as register file, reservation stations and robs. Increasing bit flipping frequency is exploited in chapter 6 to improve scheduler and itlb reliability.

#### 3.0 PROACTIVE RECOVERY AND 4PR FOR BTI IN SRAM CELLS

In this chapter, a novel design is proposed that mitigates both NBTI and PBTI at the same time in all 4 transistors of SRAM cell in high- $\kappa$  technology with which PBTI is as severe as NBTI. In Section 3.1, it's identified that for a SRAM cell, while NBTI on PMOS shows degradations to read static noise margin and read's statistical stability [31], PBTI on NMOS is more critical to the cell's access failure and/or read flip failure. Existing NBTI-only approaches [65] recover some but not all transistors. Then in Section 3.2, we devise a proactive recovery technique that recovers all four transistors in a cell simultaneously. A new recovery mode, 4PR, is introduced in which the inverse bias is created for all four MOS gates and the voltage level of the internal gate inputs is approximately  $0.5V_{dd}$ . 4PR helps to recover all four MOS gates proactively at the same time, with a medium strength but 100% effective recovery time during the recovery period.

#### 3.1 EFFECT OF BOTH NBTI AND PBTI

The direct consequence of BTI stress is the MOS  $V_{th}$  increase due to the generated traps. The increased  $V_{th}$  then causes the performance and the reliability of both combinational circuits and SRAM cells to degrade.

For combinational circuits, the  $V_{th}$  increase in the PMOS/NMOS slows down the lowto-high/high-to-low transition due to a weaker drive strength. If  $V_{th}$  increases too high, the transition may fail to meet the timing requirement of the circuit. Previous study has shown that although the increased delay caused by NBTI is significant for a single gate, its impact on a combinational circuit is relatively low(3.3% in 3 years [30]). However, considering both NBTI and PBTI, their impact is doubled and a re-evaluation is needed, which is not covered in this thesis. On the other hand, NBTI in combination with process variation can severely degrade the reliability of memory cells [30]. Such degradation can greatly reduce the statistical read stability and read static noise margin of the cell [31]. Therefore, we target the on-chip SRAM cells and mitigate both their NBTI and PBTI degradations in this work.

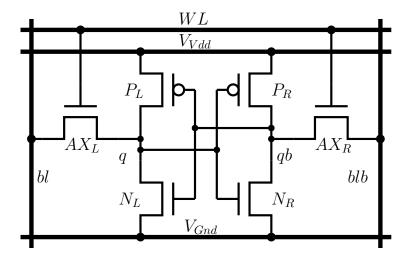

Figure 4: Standard 6T SRAM Cell

Fig. 3.1 shows a conventional 6T SRAM cell. When "1" is stored (q = 1, qb = 0),  $P_R$ and  $N_L$  are under natural recovery, and  $P_L$  and  $N_R$  are under stress. When "0" is stored,  $P_R$  and  $N_L$  are under stress, and  $P_L$  and  $N_R$  are under natural recovery. As we can see, the signal probability of the cell determines the  $V_{th}$  shift of the  $P_R$ - $N_L$  pair and  $P_L$ - $N_R$  pair. We ignore the stress on the access transistor due to its average low duty/busy ratio. We will assume a cell storing value 0 with q = 0, qb = 1 for the ease of discussion in the remainder of this section.

$V_{th}$  variation on gates can lead to the following 3 failure mechanisms in a SRAM cell [51]: write failure, access failure, and read flip failure. The write failure happens when writing an inverse value to the SRAM cell cannot finish before the word-line closes and the transaction rewinds. The access failure happens when the bit-line does not discharge below the sense amplifier's trigger threshold such that it fails to sense the correct data. The read flip failure happens when an inverse value is written in the cell during a normal read operation, since

Figure 5: Cell stability under 1. NBTI only (surface plot) 2. Both NBTI and PBTI (mesh plot)

the voltage at q (storing a "0") is driven too high by the pre-charged bit-line and shoots over the trip point, initiating the flipping process. The SRAM cell fails if any of the above 3 failures occurs. We do not include the hold failure analysis since it is for special operations. Note that process variations (PV) during fabrication can also lead to  $V_{th}$  shifts which are additive to BTI degradation induced shifts. We will first discuss BTI effects without PV for clarity, and later present experimental evaluations with PV for completeness.

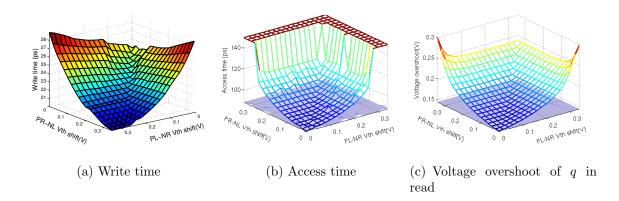

To evaluate failures caused by  $V_{th}$  shifts, we measured the write time, access time and voltage overshoot magnitude at q during a read (which can cause read flip failure) for an SRAM cell while  $V_{th}$  increases, shown in Figure 5. The dynamic simulation-based failure criteria is used instead of static criteria such as SNM and WSNM, since RSNM tends to overestimate the dynamic read failure and WSNM underestimates the dynamic write failure [33]. In simulating one cell, we used equivalent resistance and capacitance load extracted from a 128\_bit×256\_word SRAM bank, to obtain reasonably accurate timing and expedite the simulation. We will also compare our observations with [4, 5].

In Figure 5, the mesh plot shows results when only NBTI induced  $V_{th}$  shift is considered, and the surface plot shows the results when both NBTI and PBTI are considered. We do not put any timing constraints on read or write to show clearer trends with extreme  $V_{th}$  ranges  $(0\sim300mV)$  in the figure and no variations on access transistors) for a clear comparison. Note that in reality,  $V_{th}$  is in a much smaller region, e.g.  $0 \sim 100 mV$ , but its impact on those failures still complies with the observations we make.

Fig. 5(a) shows write time variations with  $V_{th}$  increases. The lower the better. The mesh and surface plots almost overlap since with or without PBTI, the write times only differ by 2ps at most, indicating that PBTI does not have significant impact on write time. In other words, the NBTI effect on PMOS dominates the write time. Also, the weakened PMOS due to NBTI further weakens the pull-up strength, which makes the pull-down relatively easier. This is because the PMOS in an SRAM cell is designed weaker than the NMOS, and is more sensitive to  $V_{th}$  shifts. As a result, the write time even improves when  $V_{th}$  shifts becomes larger. This is also observed in [5]: writability is improved under symmetric degradation; only in worst case write time degrades marginally with PBTI.

Fig.5(b) shows the access time changes. Similar to Fig. 5(a), the lower the value the better the reliability. The plot clearly shows that when both NBTI and PBTI are considered (the mesh plot), access time increases quickly. However, if only the NBTI stress is considered (the surface plot), the changes in access time is not noticeable. This is because the access time is mainly determined by the driving capability of the pull-down path of the cell which does not involve the two PMOS. Hence, the degradation in the PMOS has little effect on the access process. In [4], the read access time is more sensitive to PBTI which plays an more important role. As we can see, when considering the PBTI stress on NMOS gates, the access failure becomes a serious reliability problem, which was not surfaced when NBTI was considered only.

Fig.5(c) shows the voltage overshoot of q in a read operation with respect to  $V_{th}$ . The higher the worse. Again, we see that the mesh plot rises above the surface plot, meaning that the read flip failure is more likely to happen when PBTI is counted. Besides PBTI affecting read stability by raising the voltage overshoot, the NBTI also degrades the read stability by reducing the flip trip point. In [5], read SNM is more sensitive to PBTI compared to NBTI. Hence, PBTI worsens the read flip failure that is already threatened by NBTI.

To summarize, the NBTI plays an important role in write time, while the PBTI plays an important role in access time. The read stability is both affected by NBTI and PBTI. Among all the failures, the access time failure dominates other SRAM cell failures [51] (in Monte-Carlo simulation). Without considering PBTI, the access reliability would be treated overly optimistically. Hence, considering both NBTI and PBTI are mandatory to evaluate the reliability of high- $\kappa$  metal-gate stack technology.

#### 3.2 4PR RECOVERY CIRCUIT

In this section, we elaborate the 4PR design and compare it with pure natural recovery (a simple approach that simply turns off the circuit and let all MOS transistors recover) and the existing approach [65] that proactively recovers NBTI-introduced degradation.

#### 3.2.1 Existing approach

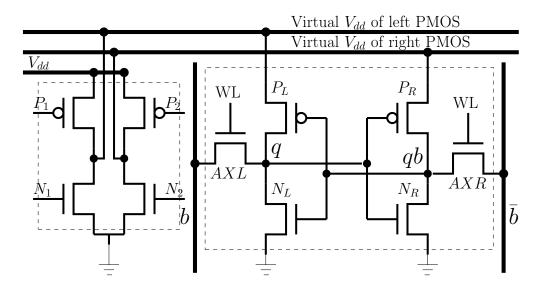

Figure 6: Proactive recovery circuits (left dash line box) for SRAM cells [65](right dash line box)

Under normal condition, a SRAM cell only stresses one PMOS-NMOS pair (source = drain = 1, gate = 0 for PMOS) while having the other pair under natural recovery (source = gate = 1 for PMOS). The proactive recovery technique proposed in [65] turns natural recovery into strong recovery (source = 0, gate = 1) to suppress PMOS  $V_{th}$  shift.

This is achieved by forcing the virtual power  $(VV_{dd})$  to ground for the PMOS that is being recovered. Since the other PMOS is still under stress, the proactive recovery needs to be applied to two PMOS transistors alternatively, which requires two virtual power lines to separate the two sides.

To mitigate both NBTI and PBTI, a simple extension of the above scheme is to apply proactive recovery to one PMOS-NMOS pair, instead of just one PMOS. Take  $P_L$ - $N_R$  pair as an example: besides driving the virtual power of  $P_L$  to ground, the virtual ground of  $N_R$  is also driven to  $V_{dd}$ . Two virtual ground lines are necessary to separate  $N_R$  and  $N_L$ . Hence, the gate is positively/negatively biased to the source for  $P_L/N_R$ , resulting in proactive recovery on  $P_L$ - $N_R$  pair. We refer this technique as "Single Pair PR" ("SP PR" for short). Since PBTI stress on NMOS cannot be neglected when using high- $\kappa$  technology, we will compare our scheme to the extended proactive recovery "SP PR" instead of the original one in [65] in the rest of the discussion.

"SP PR" has two limitations. First, the recovery mode recovers one PMOS-NMOS pair but stresses the other. Thus, its improvement over pure natural recovery is limited. Second, this approach connects sources of 4 MOS to 4 virtual source/ground wires, resulting in increased wiring overhead.

# 3.2.2 4T proactive recovery for SRAM cells

In this subsection, we discuss the design to recover all 4 transistors in one SRAM cell simultaneously (not counting the 2 access transistors), as opposed to only 1 or 2 transistors ([65] or "SP PR"). In a regular SRAM cell storing a "0",  $P_L$  and  $N_R$  are under natural recovery while  $P_R$  and  $N_L$  are under NBTI and PBTI stress respectively. Storing a "1" incurs the mirror effect of recovery and stress. By turning all four transistors into a stronger recovery mode, we tackle both NBTI and PBTI degradation in those 4 transistors, achieving much higher reliability improvement.

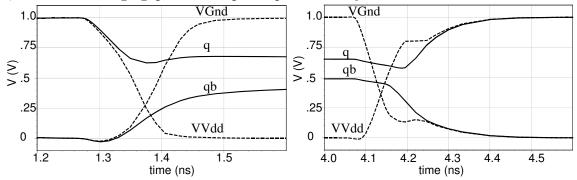

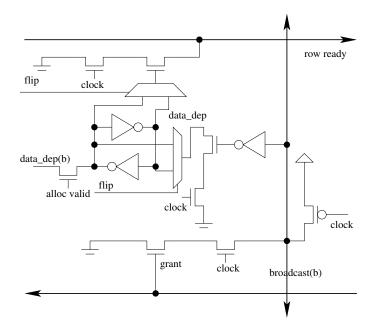

We refer to the new recovery mode as 4T-Proactive-Recovery (4PR) mode. It pulls the source terminals of the 2 PMOS gates down to ground while pulling the ground terminals of the 2 NMOS gates up to  $V_{dd}$ . As shown in Fig. 7, the power and ground terminals of

Figure 7: Mode control design: "Normal" when T1 and T4 are on; "4PR" when T2 and T3 are on.

all SRAM cells in a cache bank are connected to virtual power  $(VV_{dd})$  and virtual ground  $(VG_{nd})$ . We add a mode control circuit including  $T_3$ - $T_4$ , for  $VG_{nd}$ , and  $T_1$ - $T_2$ , for  $VV_{dd}$ . We also add drivers to drive  $T_1$ - $T_4$ . The area overhead of these drivers is small since only one such control circuit is needed per cache bank. Our evaluation also shows that the drivers and virtual power/ground wires have negligible impact on write time (0.56%), access time (0.33%) and read stability (0.36%) when  $V_{th}$  degrades from 0 to 100mV. Here we did not consider PV of drivers since they are less sensitive to PV due to the large size.

By setting different inputs to  $T_1$ - $T_4$ , the SRAM cell can switch between Normal mode and 4PR mode as follows.

- Normal mode:  $T_1$  and  $T_4$  are on,  $T_2$  and  $T_3$  are off, virtual power/ground connects to physical power/ground.

- $4PR \ mode: T_2 \ and \ T_3 \ are \ on, \ T_1 \ and \ T_4 \ are \ off, \ virtual \ power/ground \ connects \ to \ physical ground/power.$

The 4PR mode is intuitively errant since in SRAM cell the pull-up PMOS is connected to ground and pull-down NMOS is connected to power. Fig.8 (left figure) shows the transient analysis when entering from the Normal mode to the 4PR mode. The Normal mode control signal "normal" is connected to  $T_1$  and  $T_4$ , and 4PR mode control signal "pr" is connected to  $T_2$  and  $T_3$ . Initially, the SRAM cell is in Normal mode, storing a "1". When "normal" and "pr" commands flip, the cell enters the 4PR mode. With falling "normal" signal, both  $VV_{dd}$  and q drop. With rising "pr" signal, both  $VG_{nd}$  and qb rise. When q falls and qb rises such that  $q - qb < V_{th}$  is approached,  $P_L$  and  $N_R$  are off, and the cell enters the 4PR mode. Note that  $N_L$  and  $P_R$  are always off during this process. After all 4 transistors are turned off, the q and qb slowly approach to approximate  $0.5V_{dd}$ , due to the sub-threshold leakage discharge of q by  $P_L$ , and charge of qb by  $N_R$ . Thus, in the 4PR mode, all the 4 gates are off, and the internal q and qb reach about  $0.5V_{dd}$ . Note that we used 45nm high performance model [8] (lower  $V_{th}$  for MOS) in this study. If the low power model (higher  $V_{th}$  for MOS) is used, there is a voltage gap between q and qb when they stabilize.

Figure 8: Entering (left) and exiting (right) 4PR mode from the Normal mode. The transitions are fast enough.

Note that we have been using "off" to indicate that the gates are not in the saturation mode. However, they are not entirely off. In fact, all 4 gates are in the *proactive recovery* mode. The "S" and "G" terminals of the two PMOS are 0 and ~  $0.5V_{dd}$ , forming a positive bias (inverse) of  $V_{gs}$ . The "S" and "G" terminals of the two NMOS are 1 and ~  $0.5V_{dd}$ , forming the negative bias (inverse) of  $V_{gs}$ . Positive  $V_{gs}$  on PMOS and negative bias  $V_{gs}$ on NMOS (all are inverse bias) result faster and stronger recovery than natural recovery  $(V_{gs} = 0)$  [29, 28, 50]. Although this recovery strength is weaker than using full inverse bias  $(V_{gs} = V_{dd} \text{ in } [65] \text{ and } V_{gs} = -1V \text{ in } [50])$ , the measured results in [50] indicate that we can still achieve 89% of  $V_{th}$  shift recovery compared to using full positive bias, while the natural recovery can only achieve 50%. Moreover, since there are no transistors under stress in our 4PR mode, we can double the recovery time that was achieved in [65]. Also, the concurrent recovery simplifies the circuit design.

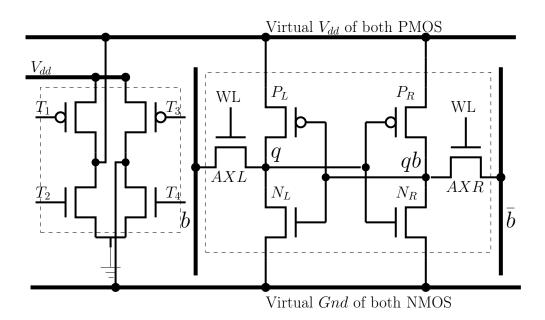

### 3.2.3 Further discussions

To evaluate the effectiveness of our 4PR, we need to closely examine the recovery characteristics under different magnitudes of discharge bias in real SRAM cell. As mentioned earlier, in multiple experiments [28, 58, 50, 29] the recovery is accelerated under inverse bias of  $V_g$  with source, drain and substrate terminals grounded. Although the settings (temperature, stress time, stress voltage, measurement method) of these experiments vary, it is clear that the inverse bias accelerates the PBTI recovery significantly. In [28], at 10<sup>4</sup> seconds, applying  $V_g$ of -1.2V results in 43% recovered  $V_{th}$  shift, comparing to 8% for grounded gate. In [58], the final degradation is reduced by 31%, compared to that after same cycles of alternating stress and natural recovery. In [50], applying -1.5V bias achieves full recovery, while applying -0.5V achieves 87% recovery and natural recovery only achieves 48%.

However, in real SRAM cell circuits both the natural recovery and proactive recovery under 4PR mode differ from those in previous experiments. In natural recovery, inverse bias occurs at the gate-drain overlap (for NMOS,  $V_g = V_s = 0, V_d = V_{dd}$ ), contrary to the setting of natural recovery in experiments without any bias (for NMOS,  $V_g = V_s = V_d = 0$ ). In 4PR, a mild inverse bias is forced at the original gate-source overlap (for NMOS,  $V_g = V_d =$  $0.5V_{dd}, V_s = V_{dd}$ ), which is different from the mild/full inverse bias on both gate-drain and gate-source ends.

For natural recovery, in [58], the inverse bias at the gate-drain end shows negligible impact on recovery strength: even raising the  $V_{ds}$  from 1.2V to 1.6V only results in limited improvement of recovered  $V_{th}$  from 3% to 10%. The great diminish is due to the reduced electrical field in the channel where there is no inverse bias for  $V_{gs}$  or  $V_{gb}$  and consequent

Figure 9: BTI proactive recovery strength

reduced electron tunneling current for charge neutralisation. Although inverse  $V_{gd}$  marginally accelerates recovery, it might be hasty to assume the inverse  $V_{gs}$  bias in 4PR has more impact on recovery strength than  $V_{gd}$ . Since there are no experiments performed under varying gate-source bias for authors' best knowledge, it is hard to quantify the individual impact of 2 inverse biases ( $V_{gs}, V_{gd}$ ) on the detrapping process and the recovery strength. Since 4PRputs gates into a new recovery state, we conservatively studied two extreme cases to include possible scenarios where  $V_{gd}$  might play a role.

- 1. 4PR-best. The first case is that  $V_{gd}$  has little impact on the gate recovery, so only  $V_{gs}$  dominates the recovery strength, as with all previous researches. The 4PR can achieve strongest recovery in this case.

- 2. 4PR-worst. The second case is that  $V_{gd}$  has the same impact on gate recovery, so combined  $V_{gs}$  and  $V_{gd}$  should be used to determine the recovery strength. The 4PR can achieve weakest recovery in this case.

However, even under the worst case, it is expected that more  $V_{th}$  shift is recovered when the inverse  $V_{gs}$  bias is applied in experiment of [58] after multiple cycles of stress and natural recovery. Since in real circuits the gate-drain has the inverse bias while the gate-source has only 0 bias, the recovery on gate-drain is always stronger than gate-source. Therefore, the accumulated trapped charge in dielectrics at the gate-source end is denser than that at the gate-drain end. As a result, periodically applying inverse  $V_{gs}$  effectively removes the charges, compared to the saturated recovery at the gate-drain end.

We list  $V_{gs}$ ,  $V_{gd}$ , recovery strength and recovery time for different modes of P/NMOS in Table 2. Take the NMOS as an example: in the stress mode,  $V_{gs} = V_{gd} = V_{dd}$ . In the natural recovery mode,  $V_{gs} = 0$  and  $V_{gd} = -V_{dd}$ . In the "SP PR" mode,  $V_{gs} = V_{gd} = -V_{dd}$ . Previous study [50] has shown that a full inverse bias to the gate results in full recovery of  $V_{th}$  while a zero bias results in a 50% of recovery. Hence, the recovery strength ratio of Natural vs. SP PR is 1:2. Regarding recovery time, the SP PR mode dedicates certain percentage of time for recovery on SRAM cache bank. Within this recovery time, only one PMOS is recovered, so the total effective recovery time for PMOS gates is 50%. Outside of the proactive recovery interval, the PMOS still enjoys the natural recovery opportunities. For natural recovery, the recovery time of any gate in a cell depends on the cell's signal probability x. Since the recovery time is limited by the weakest gate in the cell, the effective recovery time is always less than 50%.

| Table 2: Recovery Comparison: the magnitude of $V_{gs}$ , $V_{gd}$ , recovery strength and time under |

|-------------------------------------------------------------------------------------------------------|

| different modes. P represents PMOS. N represents NMOS.                                                |

| condition | $V_{gs}$ (P/N) | $V_{gd}$ (P/N) | strength | time           |

|-----------|----------------|----------------|----------|----------------|

| Stress    | $-/+V_{dd}$    | $-/+V_{dd}$    | N/A      | 1-x            |

| Natural   | 0              | $+/-V_{dd}$    | 0.5      | $\min(x, 1-x)$ |

| SP PR     | $+/-V_{dd}$    | $+/-V_{dd}$    | 1        | 50%            |

| 4PR-best  | $+/-0.5V_{dd}$ | 0              | 0.89     | 100%           |

| 4PR-worst | $+/-0.5V_{dd}$ | 0              | 0.52     | 100%           |

The recovery strengths of 4PR-best and 4PR-worst are shown in Table 2. The full recovery under SP PR mode is normalized as 1. In 4PR mode of an NMOS,  $V_g = V_d = 0.5V_{dd}$ and  $V_s = V_{dd}$ . Hence,  $V_{gs} = -0.5V_{dd}$  and  $V_{gd} = 0$ . In 4PR-best,  $V_{gd}$  can be ignored and  $V_{gs}$ is half of that in SP PR mode. Hence, 4PR can achieve 89% of the recovery strength of SP PR mode, for all 4 gates. The 4PR-worst mode might be weaker than the Natural mode but due to the effective recovery on gate-source end, the recovery score is 52%.

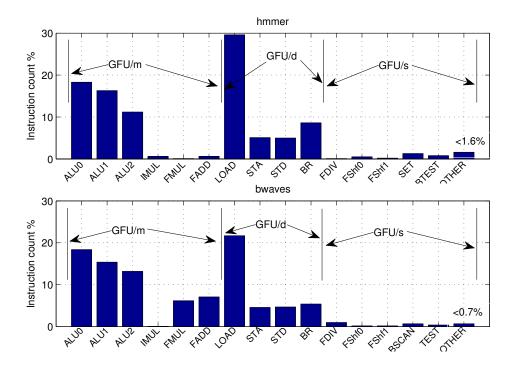

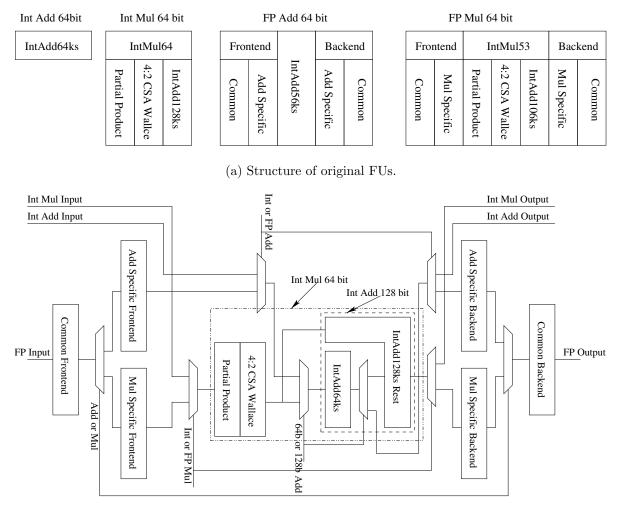

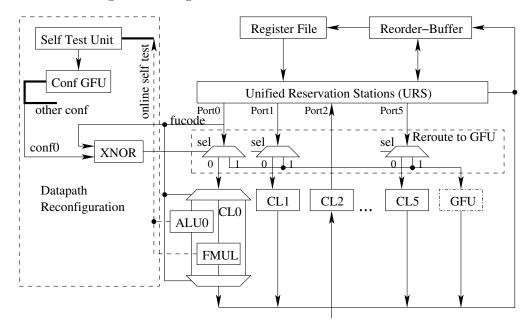

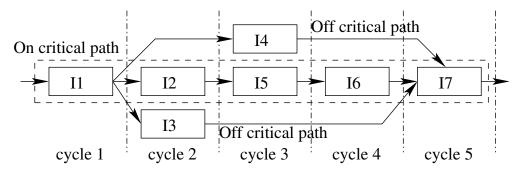

When it comes to recovery time, the 4PR mode has a clear advantage over all other modes. As we will explain later, both 4PR and SP PR modes have the same dedicated time for SRAM bank recovery. During this time, 4PR ensures recovery for all 4 gates while SP PR provides recovery for only one PMOS gate. Outside this recovery time, both schemes enjoy natural recovery opportunities.