Department of Electronic & Electrical Engineering UNIVERSITY COLLEGE LONDON

# Resistive Switching in Silicon-rich Silicon Oxide

Adnan MEHONIĆ

Supervisor : Dr Anthony KENYON

Dissertation submitted for the degree of Doctor of Philosophy

December, 2013

I, Adnan Mehonic confirm that the work presented in this thesis is my own. Where information has been derived from other sources, I confirm that this has been indicated in the thesis.

## Abstract

Over the recent decade, many different concepts of new emerging memories have been proposed. Examples of such include ferroelectric random access memories (FeRAMs), phase-change RAMs (PRAMs), resistive RAMs (RRAMs), magnetic RAMs (MRAMs), nano-crystal floating-gate flash memories, among others. The ultimate goal for any of these memories is to overcome the limitations of dynamic random access memories (DRAM) and flash memories.

Non-volatile memories exploiting resistive switching – resistive RAM (RRAM) devices – offer the possibility of low programming energy per bit, rapid switching, and very high levels of integration – potentially in 3D. Resistive switching in a silicon-based material offers a compelling alternative to existing metal oxide-based devices, both in terms of ease of fabrication, but also in enhanced device performance.

In this thesis I demonstrate a redox-based resistive switch exploiting the formation of conductive filaments in a bulk silicon-rich silicon oxide. My devices exhibit multi-level switching and analogue modulation of resistance as well as standard two-level switching. I demonstrate different operational modes (bipolar and unipolar switching modes) that make it possible to dynamically adjust device properties, in particular two highly desirable properties: non-linearity and self-rectification. Scanning tunnelling microscopy (STM), atomic force microscopy (AFM), and conductive atomic force microscopy (C-AFM) measurements provide a more detailed insight into both the location and the dimensions of the conductive filaments.

I discuss aspects of conduction and switching mechanisms and we propose a physical model of resistive switching.

I demonstrate room temperature quantisation of conductance in silicon oxide resistive switches, implying ballistic transport of electrons through a quantum constriction, associated with an individual

silicon filament in the  ${\rm SiO}_{\rm x}$  bulk.

I develop a stochastic method to simulate microscopic formation and rupture of conductive filaments inside an oxide matrix. I use the model to discuss switching properties – endurance and switching uniformity.

## Contents

| 1 | Introduction to Digital Memories                             | 7  |

|---|--------------------------------------------------------------|----|

|   | Memory Devices                                               | 8  |

|   | Classification of Matrix-based Memories                      | 9  |

|   | Read Only Memory                                             | 10 |

|   | Random Access Memory                                         | 11 |

|   | Static Random Access Memory and Dynamic Random Access Memory | 12 |

|   | Ferroelectric Random Access Memory                           | 14 |

|   | Nano-electro-mechanical Random Access Memory                 | 15 |

|   | Magnetoresistive Random Access Memory                        | 16 |

|   | Phase Change Random Access Memory                            | 17 |

|   | Organic Random Access Memory                                 | 18 |

|   | Flash Memory                                                 | 19 |

|   | Ferroelectric FET Memory                                     | 20 |

|   | The Memristor                                                | 21 |

|   | Memristor Model                                              | 22 |

|   | The HP Memristor                                             | 25 |

|   | Redox Based Random Access Memories                           | 27 |

|   | Phenomenological Description of ReRAM                        | 27 |

|   | Requirements for ReRAM as Non-volatile Memory                | 31 |

|   | Electrochemical Metallization Cell Memory                    | 36 |

|   | Valence Change Memory                                        | 37 |

|   | Thermochemical Memory Cells                                  | 39 |

|   | Introduction to Resistive Switching in Silicon Oxide         | 40 |

| 2 | Experimental Techniques and Sample Preparation               | 44 |

|   | Electrical Characterisation                                  | 44 |

|   | Electrical Probe Station                                     | 44 |

|   | Impedance Spectroscopy                                       | 45 |

|   | Structural Characterisation                                  | 46 |

|   | Scanning Tunnelling Microscopy                                     | 46  |

|---|--------------------------------------------------------------------|-----|

|   | Atomic Force Microscopy                                            | 48  |

|   | Transmission Electron Microscopy                                   | 51  |

|   | Sample Preparation                                                 | 53  |

|   | 1st, 2nd and 3rd Generation                                        | 53  |

|   | 4th Generation                                                     | 55  |

| 3 | Resistive Switching in Active Silicon Oxide                        | 56  |

|   | Electrical Characterisation                                        | 56  |

|   | Current-voltage Characteristics                                    | 57  |

|   | Bipolar Switching Mode                                             | 57  |

|   | Unipolar Switching Mode                                            | 63  |

|   | Multi-level and Gradual Switching                                  | 66  |

|   | Temperature Dependence                                             | 68  |

|   | Current-time Characteristics                                       | 70  |

|   | Impedance Spectroscopy                                             | 70  |

|   | Nonlinearity and Self-rectification                                | 71  |

|   | Structural Characterisation                                        | 72  |

|   | AFM and STM Characterisation                                       | 72  |

|   | C-AFM Characterisation                                             | 74  |

|   | TEM Characterisation                                               | 78  |

| 4 | Quantum Conductance in Silicon Oxide ReRAM Devices                 | 81  |

|   | Mesoscopic Electron Transport                                      | 81  |

|   | Introduction to Quantum Conductance                                | 82  |

|   | Introduction to Quantum Conductance in RRAM Devices                | 82  |

|   | Conduction Quantisation in Silicon Oxide RRAM                      | 83  |

|   | Reproducibility of G-V Curves                                      | 88  |

|   | Nonlinear Components of the Conductance                            | 88  |

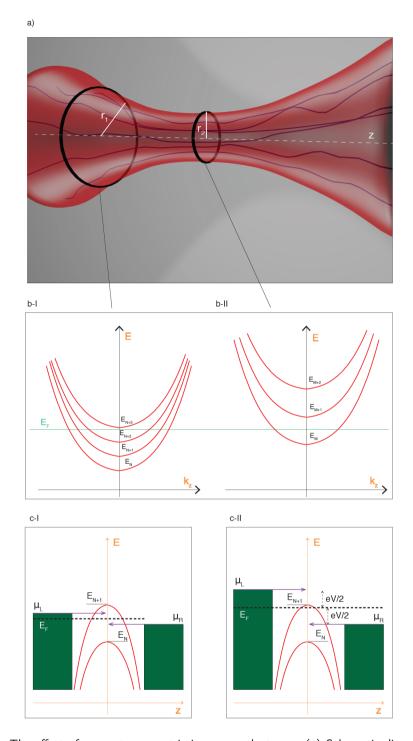

|   | Theoretical Model – Nonlinear Quantum-Point Transport Mode         | 93  |

|   | Distinction between the Half-integer and Integer Quantisation RRAM |     |

|   | Systems                                                            | 96  |

|   | Conclusion                                                         | 100 |

| 5 | Phenomenological Model of Resistive Switching in Silicon Oxide     | 101 |

|   | Introduction                                                       | 101 |

|   | Conduction Mechanism                                               | 101 |

|   | Fowler-Nordheim Tunnelling                                     |

|---|----------------------------------------------------------------|

|   | Poole-Frenkel Conduction Mechanism                             |

|   | Trap-assisted Tunnelling                                       |

|   | Conduction Mechanism Results                                   |

|   | Switching Model                                                |

|   | Multi-channel Conduction Using Quantum Point Contact           |

|   | Theory                                                         |

|   | Model Description and Fitting Results                          |

| 6 | Stochastic Simulation of Resistive Switching in Oxide RRAM 130 |

|   | Introduction to the Stochastic Model                           |

|   | Model Description                                              |

|   | Simulation Results                                             |

|   | Electroforming                                                 |

|   | Reset Process                                                  |

|   | Set Process                                                    |

|   | Endurance Testing                                              |

|   | Resistive Switching without an External Oxygen Ion Source      |

|   | Unipolar Switching                                             |

|   | Bipolar Switching                                              |

|   | Resistive Switching with Unlimited Oxygen Vacancies Source     |

| 7 | Conclusion and Future Plans 146                                |

## Acknowledgements

I would like to use this opportunity to thank everybody who supported me during my doctorate.

Firstly, I am deeply grateful to my supervisor Dr Tony Kenyon. His continuous support, advice and knowledge have made my time at UCL one of the best experiences of my life – both academically and personally. His understanding and patience have made the whole process very enjoyable. For all this time I felt very lucky that I have had not only an ideal professional mentor but also a friend.

I am also grateful to all my collaborators who have made a big contribution to my work and from whom I have learnt a lot. I thank Dr Sébastien Cueff, Dr Christophe Labbé, Prof Richard Rizk and Prof Enrique Miranda who have been great collaborators from the start of the project. I would like to thank Dr Vasillios Albanis and UCLb who greatly helped my work through our strategic and financial partnership.

Special thank you goes to my parents for all their kind support, love and understanding. I thank my sister Aida for sharing the ups and downs during this period. I thank Nejra for being the best support I could ask for.

Finally I thank all my friends in Bosnia and the UK for their love and support.

### Chapter 1

## Introduction to Digital Memories

This chapter provides an overview of digital memories. Different memory concepts are classified into several groups. The basic physical principles governing the processes of different memory types are briefly discussed. Typical memory properties of each type are compared.

The special focus is on resistive random access memories (RRAM) and, more specifically, on redoxbased resistive random access memories (ReRAM).

RRAM is often seen as a special case of a general class of technologies that exhibit memristance[1] – a resistance that depends on the past history of the device (a "memristor"[2]). There is some controversy over the definition of memristor. RRAM is classified as a type of memristive system rather than a memristor. This is discussed later in the chapter. Memristors can be non-volatile memory elements, novel logic gates, or elements in neural networks.

There is therefore considerable interest in memristor/RRAM commercialisation as replacement for flash memory and other non-volatile memory systems.

As successive generations of NAND technology strive to boost performance, processing and physical limitations make it increasingly difficult to shrink device size and increase bit-count per cell without encountering power dissipation and speed problems.

RRAM offers a promising solution, requiring far fewer mask steps than existing flash technologies, with far higher areal densities. The International Technology Roadmap for Semiconductor (ITRS)

International Roadmap Committee report into emerging post-NAND memory technologies (2010) states: "... incentives for developing RRAM technologies include their low cost-per-bit, low-voltage (and low power dissipation) operation, high endurance, and their plausible suitability for integration in crossbar arrays stacked in multiple levels in 3D."[3]

Several RRAM technologies are currently under investigation, including phase-change materials (chalcogenides, perovskites, Ge sulphide and selenide), and, currently most promising, metal oxides (NiO, TiO, HfO<sub>2</sub>) in which resistance is switched through the formation and destruction of conductive filaments. Work is moving rapidly from fundamental research to development. However, issues around understanding the switching mechanism, device reliability and processing remain critical. The consensus is that switching is predominantly due to the migration of oxygen vacancies under the application of external fields, although Joule heating plays an important role too. Much of the microscopic detail of the switching process is largely conjecture.

#### **Memory Devices**

Information storage represents a crucial step in passing human experience and knowledge in time and space. Number tracking evolved from the system of counting using small clay tokens to impressing a stylus into clay to first pen writings to printing via moveable parts and finally electronic printing. Similar scenarios occurred for sound and picture recording. In 2011 it was estimated that humankind has stored more than 295 billion gigabytes of data since 1986[4].

Generally speaking, electronic storage systems are classified into two groups – random access devices and mass storage devices. This is shown in Table 1.1 [5].

|                    | Mass Storage Devices                                  | Random Access Devices                                      |

|--------------------|-------------------------------------------------------|------------------------------------------------------------|

| System             | Access unit<br>Storage medium                         | Matrix of conductor lines<br>Storage elements are at nodes |

| Addressing of Data | Positioning of the read/write unit and storage medium | Application of address signals<br>(columns and rows)       |

| Data exchange      | Mechanical<br>Optical<br>Magnetic<br>Electric         | Electronic access via matrix                               |

Table 1.1: Classification of electronic storage systems

Random access devices are controlled in a parallel way, providing a faster access. They have a matrix organisation. Every memory cell is addressed by appropriately addressing two address lines – bit line and word line.

Mass storage devices are more suitable for storing larger amounts of data. In this case, access of data is sequential. This means that the operational speed is slower and it depends on the physical position of accessed data.

There is a clear trade-off between the operational speed and the overall storage capacity. Different types of memories are used for different purposes – from very fast, low capacity cache memories to much slower higher capacity permanent memories like hard disk drives.

Although there is a very clear difference between these two types there are many memory concepts sharing the properties of both. For example, solid-state memories (SSD) are addressed in the same way as hard-disk drives (HDD), but they have an internal matrix organisation like flash memories (an example of random access memory).

#### **Classification of Matrix-based Memories**

Different memory states are represented by different physical states of a memory unit. In most cases, these physical states are either different charge states or different resistance states.

Matrix-based memories are further classified into two types – random access memories (RAM) and read only memories (ROM). The first type is used as a main memory in semiconductor devices such as personal computers, mobile phones, portable electronics. The second type is used when the access time needs to be as short as possible. Memory capacity of ROM is lower compared to RAM. ROM is typically used for the instruction storage.

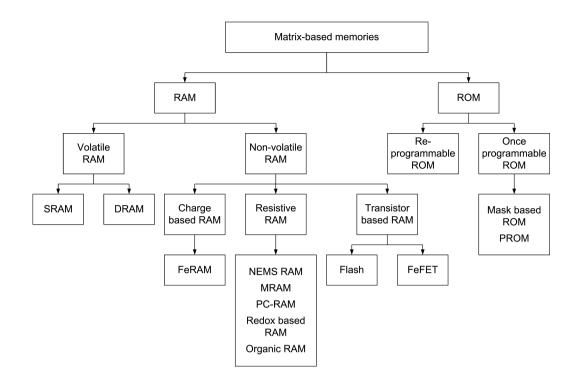

These two types of memories are further divided in several categories as shown in Figure 1.1.

Figure 1.1: Classification of Matrix-based memories. After [5].

#### **Read Only Memory**

Read only memory (ROM) is classified into two groups – re-programmable ROM and once programmable ROM.

In the case of once programmable ROM, the state of the memory is defined during the first programming step or the last fabrication step. In either case these states are permanent and they cannot be changed. When defining the memory state during the first programming step, the metal bridges at the nodes of the matrix are fused. Therefore either fused or intact nodes represent "0s" and "1s". The matrix can also be defined during the last fabrication step – different mask layouts represent different states (mask-based ROM).

In case of re-programmable ROM the matrix's configuration can be changed. The process of reprogramming can be done either electrically – electrically erasable PROM (EEPROM), or by application of UV light that discharges all units – erasable PROMs (EPROM).

#### **Random Access Memory**

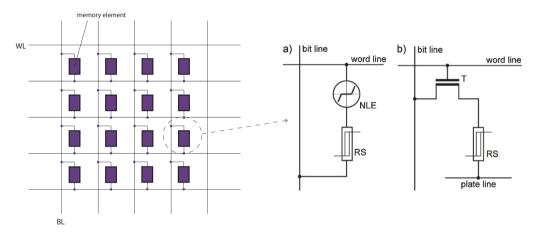

When it comes to random access memory (RAM) there are two types of matrix organisation – passive matrix organisation and active matrix organisation.

Matrix memory organisation is shown in Figure 1.2. The rows of address lines (called word lines – WL) are perpendicular to the columns of address lines (called bit lines – BL). At the node of every intersection there is a memory unit/resistive switch (RS). In case of passive organisation there is no additional active switch. However the nonlinear element (NLE), usually a diode, in series to RS is used.

Figure 1.2: Memory crossbar array. (a) Passive memory matrix. (b) Active memory matrix. After [6].

Selecting a different WL and BL line accesses a single memory unit. Every cell that is located in the same WL or BL experiences a fraction of the addressing signal – even non-selected cells. To prevent an unintentional switching event (switching between two logic states – "1" and "0"), a well-defined method (threshold values) is required. Furthermore, during the reading process the occurrence of many parasitic current sneak paths is possible. If system is not well adapted, a faulty reading will occur.

A passive memory matrix allows a high device density (which is only limited by the size of a memory unit), low fabrication costs and the possibility of 3D architectures – stacking of multi layers in a 3D configuration. However, in the case of RRAM with passive matrix ogranisation, sneak currents through non-selected cells limit the maximum size of the matrix.

Active memory matrix, as an addition to a memory cell, includes an active switch. This active

switch is a selector device, usually a transistor (T), that overcomes the problem of sneak paths and fractional stressing of non-selected cells. Although this greatly helps in respect of the maximum size of an individual matrix, it comes at the cost of an additional element.

RAM is further classified into two groups - volatile RAM and non-volatile RAM.

In the case of volatile RAM the memory state is lost once the power supply is removed. For continuous retention of data an external power supply is required. There are two types of volatile RAM – static RAM (SRAM) and dynamic RAM (DRAM).

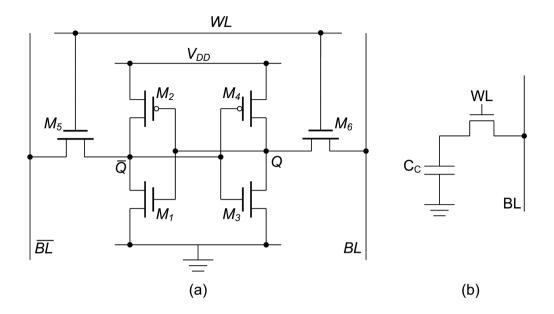

#### Static Random Access Memory and Dynamic Random Access Memory

SRAM uses a bistable latch configuration. The two stable states represent logical "1" or "0". In contrast to dynamic RAM static RAM does not require a periodical refreshment of data. Still, data is lost when the power supply is removed – therefore SRAM is still classified as a volatile type of memory.

The typical cell consists of 6 MOSFET transistors, and has two stable states. The states are stored in four transistors – 2 cross-coupled inverters formed by transistors  $M_1 - M_4$  as shown in Figure 1.3(a). Transistors  $M_5$  and  $M_6$  provide an access to the inverters.

In the case of DRAM, a capacitor charge is used to represent a memory state. Every bit state (zero or one) is represented by the charge of the capacitor (charged or discharged capacitor). To prevent loss of data caused by the constant discharging of capacitor (through the leakage current), the states of capacitors are periodically refreshed. This requirement for a refresh process defines DRAM as a dynamic type of memory. DRAM is very simple compared to other types of memories – it requires only one transistor and one capacitor per bit. Consequently the density of DRAM is very high – billions of bits can be fitted on a single chip.

Figure 1.3: (a) SRAM memory cell. (b) DRAM memory cell.

DRAM is much faster than non-volatile types of memory (e.g. flash) – it operates on the nanosecond scale (to write or read a bit state), while flash requires at least tens of microseconds.

Although DRAM uses much smaller space than equivalent SRAM (capacitor and selector in the case of DRAM, compared to six transistors in the case of SRAM), SRAM is still used for fast memory like cache. The access time of SRAM is shorter than the access time of DRAM (approximately 50ns in case of DRAM and 10ns in case of SRAM).

Non-volatile RAM does not require a power supply for the retention of data. The most used type of non-volatile RAM is a flash memory.

There are still a few drawbacks of flash memory despite it being one of the most used memory types. These include slow access times compared to volatile RAM – either DRAM or SRAM, limited number of write-erase cycles (normally around 100,000), and in some cases limited random addressability. Due to these intrinsic drawbacks of a flash, many alternative approaches are being developed. Although the early results are promising (compared to flash or even SRAM), they are still not mainstream.

Non-volatile ROM can be classified into three groups based on main physical principle of data storage: charge-based RAM, resistive RAM and transistor-based RAM.

The operation of charge-based RAM relies on different levels of charge stored in the memory cell. These states are non-volatile, as they do not require a power supply. A typical example is ferroelectric RAM (FeRAM).

#### Ferroelectric Random Access Memory

FeRAM uses a typical MOSFET structure. The main difference compared to a typical MOSFET is that the insulator between the gate and the transistor body is a ferroelectric. Different polarisation states of the ferroelectric represents different memory states. The amount of charge flowing into the device depends directly on the polarisation state. When an external electric field is applied dipoles inside the ferroelectric align themselves with the field that is produced by small shifts of electronic charge in the crystal structure. The dipoles retain their state even after the charge is removed.

During the reading process the ferroelectric is forced into a particular state. If the forced state is the same state as the ferroelectric was before, nothing will happen. If there is a change of the state a short current pulse will be generated due to re-orientation of atoms. The reading process is destructive and it is required to re-write the state after reading. These states are non-volatile. The switching speeds (around 150 ns) are much faster than the ones of typical flash. Although data retention is significantly improved in the last few years, the main issue with FeRAM is lower storage density and higher cost compared to high volume memories that are already on the market.

Figure 1.4: Schematic representation of the conventional floating gate transistor – (a) Flash memory cell. (b) FeRAM cell. After[7].

#### Nano-electro-mechanical Random Access Memory

Resistance-based RAM relies on different resistance states of the memory cell. There are many different types of RRAM. These include nano-electro-mechanical RAM (NEMS RAM or NRAM), magnetoresistive random-access memory (MRAM), phase change RAM (PC-RAM or PRAM), redox-based RAM (ReRAM), and organic RAM.

The memory state in nano-electro-mechanical RAM (NRAM) is represented by the position of carbon nanotubes (CNT). When nanotubes are in contact the resistance state is low, which represents the logic state "1" and when there is no contact the resistance is much higher, representing logic state "0".

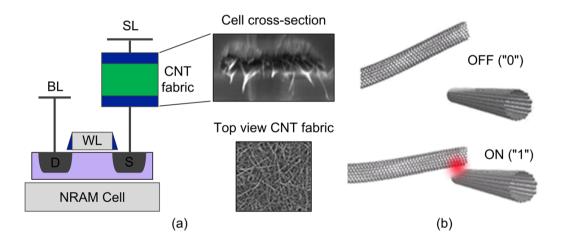

An NRAM memory cell is shown in Figure 1.5(a).

Figure 1.5: (a) Basic memory cell structure. (b) Representation of memory state – OFF state (CNT are not in contact), ON state (CNT in contact). After[8].

The carbon nanotubes are sandwiched between two metal electrodes. A small electric pulse is used to bring the nanotubes in contact or to separate them – as shown in Figure 1.5(b).

When two nanotubes are separated a short pulse greater than the read pulse will cause an electrostatic attraction between the CNTs, and they will be brought into contact. This represents the set operation (the transition from "0" to "1"). The nanotubes stay in contact due to Van der Waals forces. For the reset process (the transition from "1" to "0" state) a short reset pulse is used to generate a phonon energy high enough to separate them.

The density of NRAM is defined by the feature size of the electric contacts. The size of the CNT

is much smaller than this and does not contribute to the overall cell size. Consequently, only the lithography process limits the memory density. Theoretically, this means that NRAM density can surpass the density of DRAM while being non-volatile and performing similarly to SRAM (in terms of speed and power). The technology is still in development by company Nantero.[8]

#### Magnetoresistive Random Access Memory

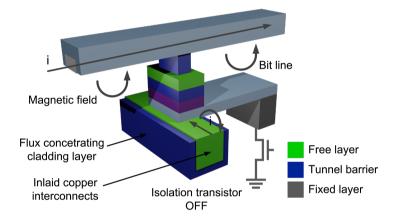

A magnetisation state is used to represent the memory states of magnetnoresistive RAM (MRAM). The basic cell structure is shown in Figure 1.6.

Figure 1.6: The structure of an MRAM cell with bit and word lines. After[9].

The memory cell consists of two ferromagnetic plates separated by an insulating layer. One of the plates is fixed and the magnetic moment of the plate is permanently set. The magnetic moment of the second plate can be changed by an external magnetic field. The magnetic moments of the two plates can be either in parallel or in anti-parallel to each other.

These two cases represent the two memory states - "1" and "0".

Every memory cell is sandwiched between two lines – BL and WL. An induced magnetic field is generated at the junction when a current passes through the lines. This field can change the polarisation state of the cell. The state of the cell is read by means of electrical resistance of the cell. An anti-parallel arrangement of two magnetic moments will provide a higher resistance of the cell.

MRAM is still in the early stage of its development, but initial results indicate that MRAM can be as fast as SRAM. Since the 1990s MRAM has been a continuous subject of both industry and academic research. It is often seen as a "universal memory" to replace not only flash but also SRAM and DRAM.

#### Phase Change Random Access Memory

Many materials can be found in two distinct phases – amorphous and crystalline. They are commonly fabricated in either one or other phase, but there are some particular materials which exhibit fast transitions from one phase to the other. These materials exhibit a large electrical and optical contrast between these two phases with high stability in either of them, which makes them very interesting for memory-like applications.

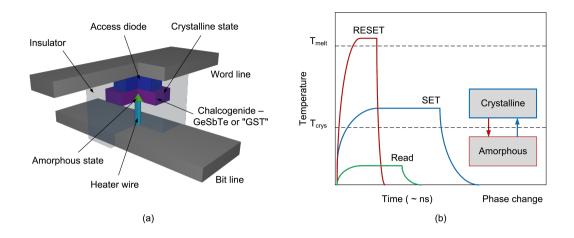

The idea of media storage in phase-changing materials dates back to the 1960s with the preposition that chalcogenides might be used as the storage media. But this idea became more technologically viable only with the discovery of fast crystallisation in certain materials. The best results have been reported for  $Ge_2Sb_2Te_5$  (GST), which is still the most used phase changing material[10, 11]. Optical data storage based on these materials already had a great success (e.g. Blu-Ray disks and other rewritable optical disks).

A Phase Change Memory (PCM) consists of cells which could either pass current, when they are in the ON state (crystalline state), or block the current when in the OFF state (amorphous state). By heating the cell via a tiny heather/resistor it is possible to change state either to amorphous or crystalline. Different voltage pulses control the material crystallisation – either to allow crystals to grow from the melted mass, or to prevent the growth. These processes happen at the localised area and they are very fast – a few nanoseconds. A schematic of a typical PCM cell is shown in Figure 1.7(a). Intense heating and abrupt cooling afterwards turns the material into the amorphous phase. Longer, weaker heating turns the material into the crystalline phase, as shown in Figure 1.7(b).

Although PCRAM can already be found in volume production[12] several challenges are still present.

High temperature sensitivity of PCM is still the main drawback. Moreover, the existing commercial memories are proving to be more economical. Nevertheless due to other excellent properties (in particular the scaling prospect) it is expected that PCM will play an important role in the general memory market in the near future.

Figure 1.7: (a) Cross-point PCM memory cell. (b) Typical T-t curves of PCM element.

#### **Organic Random Access Memory**

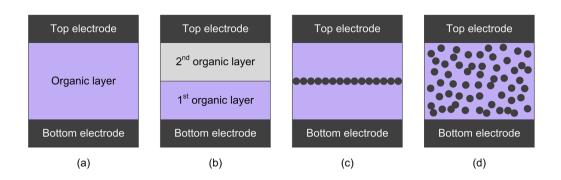

Another type of RRAM is organic RAM. The basic unit cell is an organic material sandwiched between two electrodes. Organic RAM has already shown good memory properties. At least two stable memory states, good endurance, good retention, fast switching, good ON/OFF ratio have been reported[13, 14].

The main issue with organic RRAM is the still quite unclear physical picture of the switching process. Various organic materials have shown resistive switching when a voltage bias is applied[15]. These materials include small molecules, polymers and composites containing nanoparticles.

A few structures have been explored:

- Single organic layer sandwiched between the contacts;

- Multi-layer structures containing at least two types of organic material;

- Spin-cast polymer nanoparticles embedded in host material.

The main advantage of organic RRAM is its low fabrication cost, scalability and flexibility, while poor reliability is the main issue.

Once the physics behind the switching is better understood this particular technology might find its place in non-volatile memory market – especially in new flexible memory applications. At the moment organic RRAM is still in its early stages of development.

Figure 1.8: Typical structures of organic memory cells: (a) a single-layer structure without nanoparticles (NPs), (b) a bilayer structure containing two kinds of polymers, (c) a structure with nano-traps buried in the middle of an organic layer, and (d) a polymer-NP composite with NP traps randomly distributed throughout the entire host polymer. After[16].

#### Flash Memory

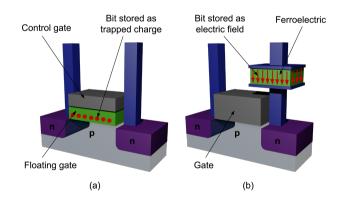

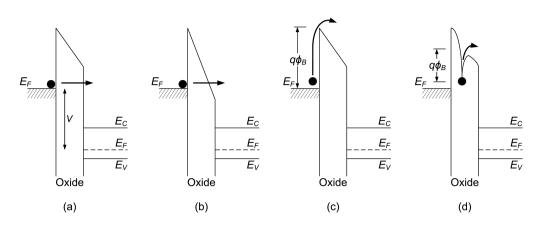

Data is stored in the gate of a selecting transistor in the case of transistor based RAM. Typical examples are flash memory and ferroelectric field effect transistors (FeFETs).

Flash memory, based on floating gate transistors, still dominates the non-volatile memory market. The basic flash memory unit is the floating-gate MOSFET transistor.

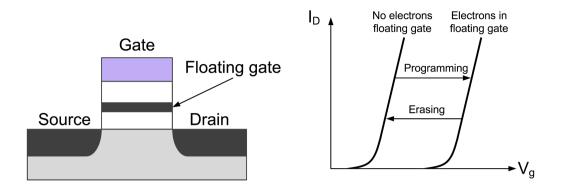

A schematic of a MOSFET transistor is shown in Figure 1.9. The floating gate (FG) is electrically isolated from the external control gate and drain and source. As there is no resistive connection between FG and the control gate, the charge stored in the FG remains the same for long periods of time. To modify the charge stored in the FG a high voltage is applied to the control gate. Charging or discharging of the FG occurs through Fowler-Nordheim tunnelling and hot-carrier injection mechanisms. Different amounts of charge stored in FG modify the threshold voltage and this represents different memory states.

Figure 1.9: Floating gate transistor and the basic working principle of flash memory.

#### Ferroelectric FET Memory

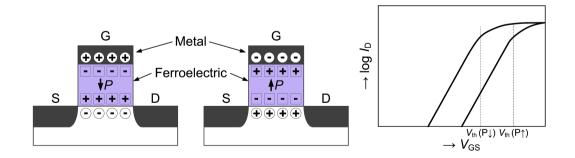

Ferroelectric FET, similarly to ferroelectric RAM, uses ferroelectric material instead of the gate dielectric of a MOSFET.

In contrast to FeRAM, the reading process in a FeFET is not destructive. By application of an external field the polarisation of the ferroelectric can be changed. Two different polarisations represent two logic states, and different polarisation states yield different threshold voltages of the FET.

The FeFET is much faster, and operates at significantly lower voltages, than flash. A disadvantage of FeFET is low data retention – the 10 years limit, required for non-volatile memories, is still not reached.

Figure 1.10: Schematic of FeFET cell and corresponding  $I_D$ -V<sub>GS</sub> characteristics.

#### The Memristor

Although Leon Chua first introduced the name "Memristor" in 1971, the concept of electrically variable resistance is much older. In a recent commentary publication[?] Leon Chua (with other authors) states: "The memristor is not an invention. Rather it is a description of a basic phenomenon of nature that manifests itself in various dissipative devices, made from different materials, internal structures and architectures. We end this historical narrative by noting that even though the memristor has seen its light of joy only recently in 2008, and has been recognized as the fourth circuit element along with the resistor, capacitor and inductor, it actually predates the resistor, which was formally published by Ohm in 1827, and the inductor, which was formally published by Faraday in 1831".

Here is a brief historical background:

- In 1960, the device called the "Memistor" was introduced by Bernard Widrow from Stanford University. His device had three terminals and the conductance between the two terminals was controlled by the time integral of the current that goes into third terminal.

- In 1968, three years before Chua's paper on "Memristors The Missing Circuit Element", a paper entitled "Switching phenomena in titanium oxide thin films" [?] was published reporting similar results to these of the HP memristor work that came 40 years after, in 2008.

- In 1971, Leon Chua defined a "Fourth Circuit Element" calling it the "Memristor" [2].

- In 1976, Leon Chua published another paper giving the mathematical generalisation of the model of the Memristor[17].

- In 1990, variable resistance was observed in tungsten oxide that can be electrically programmable[18].

- In 2000, research group from IBM's Zurich Research Laboratory reported reproducible resistive switching in oxide thin films[19].

- In 2008, HP reported a direct link between resistive switching in their titanium oxide device and Chua's model [20].

Between the initial work of Chua in 1971 and the HP report on titanium oxide based memristor in 2008 many papers have reported memristor-like behaviour, but only the HP report found a direct link between resistive switching in their device and Chua's model. They found a link between the

resistance switching in two-terminal device and Chua's mathematical model. Since this announcement, the number of reports of memristors has increased dramatically. Globally, the number of publications on memristors has jumped from  $\approx$ 49 in 2008 to  $\approx$ 2400 in 2013.

#### **Memristor Model**

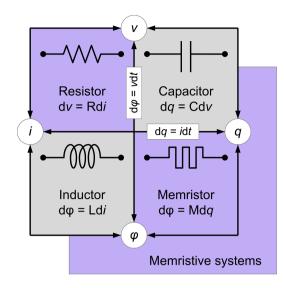

In circuit theory there are three basic circuit elements and four circuit variables. The fundamental circuit variables are current i, voltage v, flux  $\phi$  and charge q.

Five well-understood relations relate these four fundamental variables, but there are six possible combinations. Three basic circuit elements are defined as two-terminal devices relating the two fundamental variables. In that respect, there is the resistor R, the capacitor C and the inductor L. They are defined by the following relations:

$$dV = Rdi \tag{1.1}$$

$$dq = Cdv \tag{1.2}$$

$$d\phi = Ldi \tag{1.3}$$

Variables are also related as

$$i = \frac{dq}{dt} \tag{1.4}$$

$$v = \frac{d\phi}{dt} \tag{1.5}$$

Looking at symmetry in Figure 1.11 it is immediately obvious that there is one missing circuit element to complete the symmetry. This element should relate charge q and flux  $\varphi$ . Chua predicted that such element exists and he called it a memristor.

Figure 1.11: Relations between fundamental circuit variables.

The memristor gives a functional relation between the flux and charge. The commonly used definition of a memristor is that it is a two-terminal circuit element in which the flux between the two terminals is a function of the amount of electric charge that has passed through the device [10].

The derivation of memristance is given by:

$$\phi = f(q) \tag{1.6}$$

$$\frac{d\phi}{dt} = \frac{df(q)}{dq}\frac{dq}{dt}$$

(1.7)

Voltage is given by:

$$v(t) = \frac{d\phi}{dt} \tag{1.8}$$

so

$$v(t) = M(q)i(t) \tag{1.9}$$

where

$$M(q) = \frac{df(q)}{dq} \tag{1.10}$$

where M stands for memristance and its unit is the same as for resistance. This value linearly relates voltage and current if the charge does not change. Consequently, memristance M becomes resistance in the case that it does not change.

Memristance is the fundamental property of the memristor. Resistance of a memristor decreases if the charge flows in one direction, and it increases if it flows in the opposite direction. When the charge flow stops, the memristor "remembers" the last resistance and it resides in that state until the charge flow starts again.

There are many physical systems that exhibit the same phenomenological behaviour as the memristor. These are not restricted on electrical systems only. The mechanical example of a memristor is a water pipe whose shape depends on direction of water's flow.

Memristive systems are generally described by two equations:

$$v = M(w, i)i \tag{1.11}$$

and

$$\frac{dw}{dt} = f(w, i) \tag{1.12}$$

where w is a set of state variables, M and f are function of time, and v and i are voltage and current [17].

The memristor is a passive circuit element, meaning it can only dissipate energy; it cannot store any energy. As a consequence, memristance must be non-negative. The  $\Phi$ -q curve needs to be monolithically increasing and the slope of the curve gives the memristance.

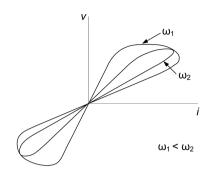

The main fingerprint of a memristor is the "pinched hysteresis curve" in the I-V characteristics. This pinched loop shrinks when the frequency of the input voltage increases. The memristor becomes a resistor once the frequency approaches infinity. When the input voltage is zero, the current passing through memristor has to be zero too (Figure 1.12). It is often said that "if a system exhibits such behaviour it is a memristor" [21], although there is some ongoing debate over this claim.

There is some controversy if certain types of devices exhibiting variable resistance are indeed memristors. Chua in his recent paper states: "Resistance switching memories are memristors" and "All 2-terminal non-volatile memory devices based on resistance switching are memristors, regardless of the device material and physical operating mechanisms. They all exhibit a distinctive "fingerprint" characterized by a pinched hysteresis loop confined to the first and the third quadrants of the v-i plane whose contour shape in general changes with both the amplitude and frequency of any periodic "sine-wave-like" input voltage source, or current source. In particular, the pinched hysteresis loop

Figure 1.12: The pinched hysteresis loop and the loop shrinking with the increase in frequency.

shrinks and tends to a straight line as frequency increases. Though numerous examples of voltage  $v_s$ . current pinched hysteresis loops have been published in many unrelated fields, such as biology, chemistry, physics, etc., and observed from many unrelated phenomena, such as gas discharge arcs, mercury lamps, power conversion devices, earthquake conductance variations, etc., we restrict our examples in this tutorial to solid-state and/or nano devices where copious examples of published pinched hysteresis loops abound. In particular, we sampled arbitrarily, one example from each year between the years 2000 and 2010, to demonstrate that the memristor is a device that does not depend on any particular material, or physical mechanism. For example, we have shown that spintransfer magnetic tunnel junctions are examples of memristors. We have also demonstrated that both bipolar and unipolar resistance switching devices are memristors."[19].

In a recent publication, Valov et al put a special emphasis on the distinction between memristors, memristive systems and resistive memories: "*Recently, the serendipitous discovery of the link between redox-based nanoionic-resistive memory cells and memristors and memristive devices has further intensified the research in this field. Here we show on both a theoretical and an experimental level that nanoionic-type memristive elements are inherently controlled by non-equilibrium states resulting in a nanobattery. As a result, the memristor theory must be extended to fit the observed non-zero-crossing I-V characteristics." [22]. In other words this brings the necessity for the revision of the original memristor theory to include the ReRAM. Demonstration of the internal voltage within the ReRAM clearly violates the memristor postulate as a passive circuit element.*

#### The HP Memristor

In 2008, a research group working in HP Labs published the paper entitled "The missing memristor found". Stanley Williams and his group were working on thin titanium oxide films. It was an MIM

structure consisting of a thin (a few nanometres in thickness) titanium dioxide film rich with oxygen vacancies sandwiched between two platinum electrodes.

Titanium dioxide is intrinsically an insulator, meaning it has a very high resistance. Making the oxide richer with oxygen vacancies increases the conductivity. Engineering the stoichiometry of the film, during the fabrication process, produces different profiles of oxygen vacancies. The oxygen vacancies behave as positively charged species. By applying an external voltage bias it is possible to drift the oxygen vacancies.

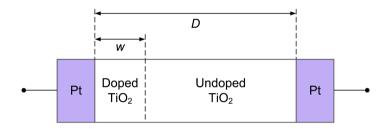

Figure 1.13: Schematic of the HP memristor. After[23].

In a simplified model, the whole oxide structure can be described as if it consists of two parts. One part is pure  $TiO_2$ , while the second part is titanium dioxide rich with oxygen vacancies,  $TiO_{2-x}$ . Rearrangement of oxygen vacancies defines the position of boundary between these two regions.

The first part  $TiO_2$  is highly resistive while the second part  $TiO_{2-x}$  is more conductive due to the presence of oxygen vacancies. When an external voltage is applied, positively charged oxygen vacancies will drift towards the negatively biased electrode changing the position of the boundary between two regions. The resistance of the whole film will change. If the oxygen vacancies are moving towards the left electrode the overall resistance will increase, as the boundary will be pushed further towards the left electrode. Similarly, if the vacancies are moving in the opposite direction the resistance will decrease.

The direction of vacancy drift is controlled by the external voltage, thus the resistance of the device is controlled by voltage. When the external voltage is turned off the device keeps the same resistance, as the boundary between the two parts does not move.

The HP device can be mathematically described as:

$$M(q) = R_{off} \left( 1 - \frac{R_{on}}{\beta} q(t) \right)$$

(1.13)

where  $\beta = \frac{D^2}{\mu_D}$ ;  $\mu_D$  is the average drift velocity, D is the thickness of the oxide film,  $R_{off}$  and  $R_{on}$  are two states of ON and OFF resistance and q(t) is the charge passing through the device.

#### **Redox Based Random Access Memories**

A local redox process governs the resistive switching in redox based RAM (ReRAM).

This redox process is triggered by an external voltage bias. Depending on whether the process is thermally or electrically driven there are several different types of ReRAM.

Both thermal and electrical effects are always acting simultaneously, but typically only one of them dominates. The three main types of redox RRAM are: electrochemical metallization cells (or conductive bridge) ReRAMs (ECM), valence change ReRAMs (VCM) and thermochemical ReRAMs (TCM).

#### Phenomenological Description of ReRAM

Resistive switching is the main phenomenon seen in these devices. A thin insulating film can reversibly change its electrical properties – from an insulating state to a conducting state under the application of an external electrical stimulus. At least two stable states are achievable – normally called the high resistive state (HRS), or OFF state, and the low resistive state (LRS), or ON state. In many cases more than two stable states are observed[24, 25].

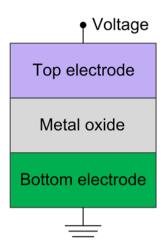

The basic memory unit is a two-terminal device consisting of two conducting electrodes and the switching thin film sandwiched inbetween. This is shown in Figure 1.14.

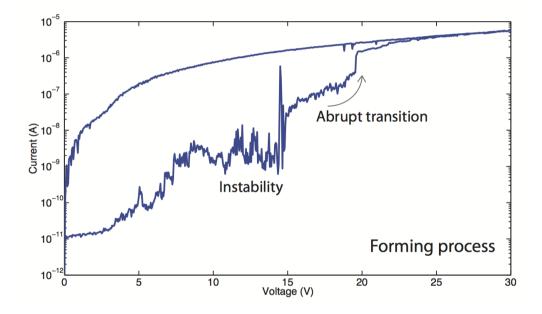

When the two electrodes are biased, the thin film can change its resistance. This change of resistance can be very large – typically several orders of magnitude. The initial transition from the insulating to the conducting state is called electroforming. After electroforming, the device can be cycled between the two stable states (LRS and HRS). This is achieved by applying appropriate voltage pulses. The pristine device, device before the electroforming, is typically more resistive than the HRS.

In many cases electroforming a requires higher voltage than the switching process. This process can

Figure 1.14: Schematic of ReRAM cell.

be seen as the controlled breakdown of an insulator.

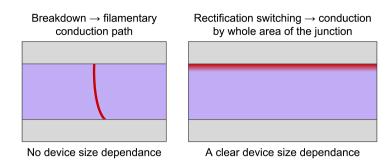

During the electroforming, a conductive filament is produced inside the insulating film (in case of filamentary ReRAM). The formation of the filament is demonstrated by in situ transmission electron microscopy measurements[26] and conductive atomic force microscopy measurements[27]. Also it is found that the conductivity of the LRS does not scale with the electrode size. Typically, there is only one dominant filament and the switching affects only that single filament[28]. During the switching process, only a small fraction of the filament is changing.

The voltage level required for the electroforming process depends on the thickness of the film[29]. This is expected, as the electroforming is (in principle) a soft breakdown of the film. Breakdown occurs when the threshold electric field is achieved, thus it is thickness dependent.

The further growth of the formed filament is thermally driven due to the high local Joule heating. External current compliance is generally required during electroforming to prevent an extensive local heating and permanent damage to the film. The following switching process is not thickness dependent, as the switching, after the initial electroforming, occurs at localised point on the filament.

Another, less common type is interface-type switching. In this case the conductivity of LRS depends on electrode size. The switching is driven by the formation of a tunnel barrier or Schottky barrier across the whole interface between the contact and the switching layer[30, 31].

Figure 1.15: LHS: Filamentary resistive switching. RHS: Interface resistive switching.

Transitional metals such as  $TiO_x[32]$ ,  $VO_x[33]$ ,  $NiO_x[34]$ , CuOx[35],  $ZnO_x[36]$ ,  $ZrO_x[37]$ ,  $HfO_x[38]$ ,  $TaO_x[39]$ ,  $WO_x[40]$ , and  $SrTiO_x[41]$  are the most used switching materials, though other materials including organic materials have also been used. Even  $SiO_x[42, 43]$ , which is best known for its good insulating properties, has shown good resistive switching properties.

We can differentiate two types of switching regarding if the electrodes play an active role in the switching events. If the electrodes play an active role in the switching process it is the extrinsic type of switching and the ECM is the typical example of this type. If the electrodes do not play an active role in switching (but they can still affect the switching properties) is reffered to as intrinsic switching. VCM and TCM are two typical examples of this type.

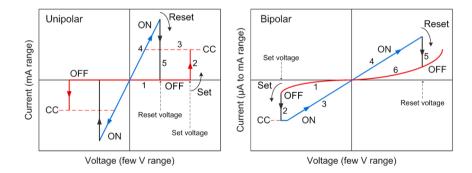

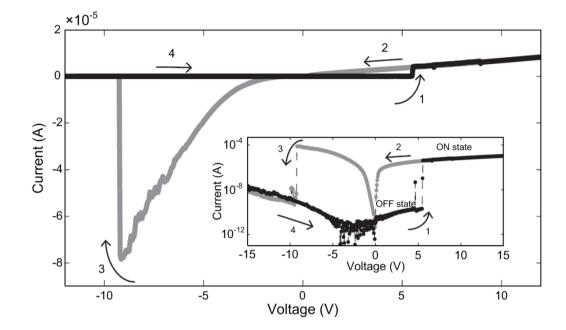

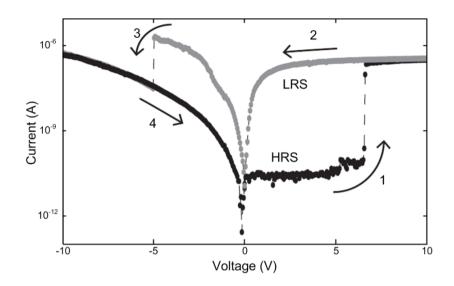

In oxide ReRAM devices, there are two commonly reported switching modes: unipolar and bipolar mode. This is shown in Figure 1.16.

Figure 1.16: LHS: Unipolar switching mode. RHS: Bipolar switching mode. Current compliance (CC) is used to prevent the hard breakdown (permanent damage) during the set process.

In case of the unipolar mode, the resistance change occurs irrespective of bias polarity, whereas in the case of bipolar mode it is necessary to use opposite polarities. Certain materials have shown the coexistence of both types of switching[44].

The transition from one state to the other is commonly called the set process if the transition is from the OFF to the ON state, and the reset process if the transition is from the ON to the OFF state.

In the case of unipolar switching a current compliance is used during the set process to prevent the hard breakdown. During the reset process the current compliance is removed (to allow the high current to pass at the lower voltages) and a transition to the HRS is achieved. In some cases the reset voltage is higher than the set voltage (though the opposite is more typically observed) and therefore the current compliance is not required.

Figure 1.16(LHS) shows the sequence of device operation in the unipolar mode. For this mode only one polarity is used. I will focus on positive polarity in this description. Starting from the higher resistance state (OFF state), there is a very low current passing through the device (part of the I-V curve noted with the part "1"). After the threshold voltage (set voltage) is reached there is a sudden current jump to the level of current compliance (part "2"). Sweeping the device back to the origin does not switch the device back to the higher resistance state, but device stays in the lower resistance state (ON state) (I-V curve would follow the part "3" which is the level of current compliance). To reset device back to the higher resistance state the current compliance is removed and device is swept from the origin. After the certain current level is reached (at the reset voltage) device switches back to the higher resistance state (part "4" and "5"). This sequence can be repeated many times and device can be switched from one to the other resistance state.

In the case of bipolar switching the set and the reset are obtained in the opposite polarities and a certain device asymmetry is required. This asymmetry can occur during the electroforming process, or it can be achieved by using different materials for the two electrodes. The current compliance is still typically required during the set process (to prevent the hard breakdown).

Again starting from the higher resistance state, device is swept in the negative bias (part "1" in Figure 1.16(RHS)). Similarly to unipolar switching, after certain threshold voltage is achieved, device switches to the lower resistance state and current jumps to the current compliance level (part "2"). Sweeping the device back to origin does not switch the device back to the higher resistance state (part "3"). In the case of bipolar switching to switch the device back to the higher resistance state the opposite polarity (compared to the polarity of the set process) is used. In this case that is the positive polarity. Device is swept to the set voltage in the positive polarity without the current compliance (part "4"). After the reset voltage is achieved, device switches back to the higher resistance state the imper state (part "5" and "6"). To switch the device back to the lower resistance state the

sequence is the same (begining with the parts "1").

In practical applications of the resistive switching memories, transitions are induced with the short pulses rather than with the voltage sweeps.

Two different processes dominate these two types of switching. If the electric field is the dominant factor in the switching process, it can be described as an electrochemical. Electric field causes the drift of the charge species (oxygen ions and vacancies) inside the switching film. In this case bipolar switching is observed. If the Joule heating (generated by the passing current) is the dominant factor of the switching process, it can be described as a thermochemical. Oxygen ions and oxygen vacancies move along a temperature gradient. In this case unipolar switching is observed. Three voltage pulses are used for the device operation in either case. A read voltage pulse is used to read the device state; a set voltage pulse is used for the transition from HRS to LRS; a reset voltage pulse is used for the transition form LRS to HRS.

#### Requirements for ReRAM as Non-volatile Memory

There are a few general requirements for all non-volatile memories, and this includes ReRAM as well. The requirements are resistance ratio between the states, endurance and retention.

- The set voltage should be in the range of a few hundred mV to a few V. It should not be too low (less than 100mV) in order to be compatible with scaled CMOS. The upper limit of set voltage gives ReRAM an advantage over other non-volatile memory types. Flash normally operates at much higher voltages (>10V) compared to typical ReRAM (a few V).

- The set process should be fast enough to outperform flash. The typical set pulse is shorter than 30ns. This is on a par with DRAM and much faster than flash (typically around  $10\mu$ s). Very fast set processes of around 300ps have been demonstrated[45].

- Ideally, reading voltage should be 10 times lower than the writing voltage to prevent an unintentional change of the memory state and to still be appropriate for the circuit design (detection by sense amplifiers). Reading current should not be less than 100nA for easy and fast detection. Reading time should be at least fast as the set time, and preferably faster.

- The resistance ratio between the states should be at least 10. This allows a cost-effective design of the reading amplifiers.

- Endurance should be on a par with flash typically at least 10<sup>3</sup>, although higher endurance is normally required. Higher endurance on a par with DRAM or SRAM (10<sup>12</sup>) has already been reported[39].

- Data retention of 10 years under a thermal stress of 85°C is a typical requirement for non-volatile memories.

- High density is needed to be competitive with the aggressive scaling of the present memory technologies.

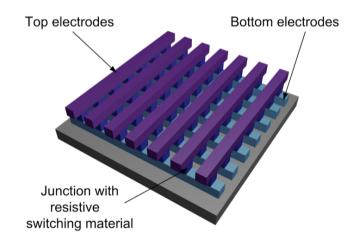

A crosspoint (crossbar) structure provides the best scaling prospect. Passive crossbar memories consist of two layers of the perpendicular electrodes with the active switching material between the crosspoint. This is shown in Figure 1.17.

Any memory unit can be addressed by applying an appropriate voltage across the two perpendicular arrays.

In the ON state the selected unit gives enough current to be read/sensed by the current amplifier. To obtain a non-destructive reading two lines are biased with the total voltage difference smaller than the threshold set voltage. Lines are typically biased with opposite polarities and the same voltage level. During the reading perpendicular lines are biased with  $-V_{red}/2$  and  $+V_{red}/2$ , where  $V_{red}$  is the reading voltage ( $0>V_{red}>V_{set}$ , where  $V_{set}$  is the set voltage).

A similar process is used in case of writing and only selected cell is affected while common-line cells remain in the same state.

In conventional active memories a selector device is integrated together with the memory cell. The selector is usually a transistor and the scaling of the whole structure is limited by the transistor scaling. In contrast to transistor scaling, where two critical dimensions are present and an aggressive scaling is not possible, ReRAM systems provide scaling in just one dimension (the thickness of the switching layer). The whole structure can be stacked in the third dimension providing much higher density if a high temperature process is not required during the fabrication.

Nonlinearity of the ReRAM unit is crucial for implementation of passive crossbar memories; it decreases sneak currents passing through the semi-selected devices. Nonlinearity is typically achieved by putting a diode in the series with the memory unit.

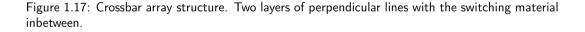

Apart from these solutions (integration of an external diode or engineering some nonlinearity of the active material), an interesting approach not requiring nonlinearity in the ON state is proposed. This approach is called complementary resistive switching (CRS) and the main idea is to use two bipolar resistive units connected in anti-series[46].

Four different states are possible: both units are in the HRS; both units are in the LRS; the first unit is in the LRS and the second unit is in the HRS; the first unit is in the LRS and the second unit is in the HRS. To prevent a leakage current one of the memory units is always in the HRS. The drawback of this approach is higher complexity and the destructive manner of the reading process.

Logical state "0" is represented by the state in which the first unit is in the HRS and the second unit is in the LRS. Logical state "1" is represented by the state in which the first unit is in the LRS and the second unit is in the HRS.

In order to write the state "0", positive voltage bias larger than  $V_{th,2}$  is applied ( $V_{th,2} = |V_{th,set}| + |V_{th,reset}|$ , where  $V_{th,set}$  is the set volage and  $V_{th,reset}$  is the reset voltage of the individual unit). If the CRS is already in the state "0", nothing will happen. The first unit is in the HRS and the negative bias (note that the first unit is inverted with respect to the second unit) does not change its state, while the second unit is in the LRS, and thus the positive bias does not change its state either. If the CRS is in the state "1", positive voltage larger than  $V_{th,1}$  will switch the second unit to the LRS and the CRS will temporarily be in an all-ON state (both units are in the LRS). When the voltage increases above  $V_{th,2}$ , the first unit switches to the HRS so the CRS changes its state to the state "0".

Writing the state "1" is equivalent to writing the state "0" by applying the negative voltage bias larger than  $V_{th,4}$  (where  $|V_{th,4}| = |V_{th,2}|$ ).

In order to read the state, positive bias bias larger than  $V_{th,1}$  (where  $V_{th,1} = V_{th,set}$ ) and smaller than  $V_{th,2}$  is applied. If CRS is in the state "0", a small current at the output is detected as the first unit is in the HRS and the states do not change. If CRS is in the state "1", positive voltage bias larger than  $V_{th,1}$  and smaller than  $V_{th,2}$  switches the second unit to the LRS and a large current is detected (as both units are in the LRS). This indicates the logical state "1" for CRS. It is necessary to recover CRS to the state "1" because the state of the second unit is changed. Negative voltage bias larger than  $V_{th,4}$  is applied and CRS is recovered to the state "1". This approach is shown in Figure 1.18.

Figure 1.18: (a) Bipolar memristive element A with a Pt/solid electrolyte/Cu stack. (b) I-V characteristic of memristive element A. The resistance can be toggled between the LRS and HRS by exceeding  $V_{th,SET}$  and  $V_{th,RESET}$ . (c) Bipolar memristive element B with a Cu/solid electrolyte/Pt stack. (d) I-V characteristic of memristive element B. (e) CRS resulting from the combination of memristive element A and B. (f) I-V characteristic of a CRS. (g) Measured I-V curve. After[46].

ReRAM has the potential to become not just the alternative to flash or DRAM but to become a universal memory. Universal memory would need to combine all the good characteristics of all types of memories including non-volatility, high endurance (higher than 10<sup>12</sup> cycles), sub-nanosecond writing speed, long retention time (>10 years) and nanometre dimensions. Although most of these characteristics are already reported, high-density memory requires high yield and small variation in switching behaviour. The required level is still not achieved.

#### **Electrochemical Metallization Cell Memory**

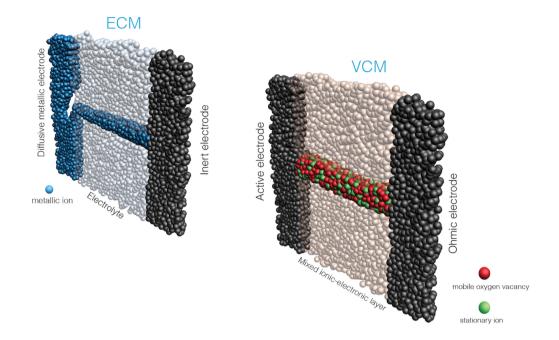

Electrochemical metallization cell (ECM) memories are also called Conductive Bridge RRAMs.

The main part of the memory cell is electrochemically active metal electrode, usually Ag or Cu. The other electrode is chemically inert – such as Pt, Ir, TiN, Au, W. Thin insulating layer is sandwiched between two electrodes. This layer is typically either a solid electrolyte such as  $Ag_2S$ ,  $Cu_2S$  or an insulator such as  $WO_3$ , GeS, SiO<sub>2</sub>. The thickness of the insulating layer is typically a few tens of nm, but can range from 5nm to several hundreds of nm. The basic principle of operation is shown in Figure 1.19.

In the pristine state the cell shows high resistivity. There is no metallic material from the active electrode present in the insulating layer. During the forming and the SET process a positive voltage is applied to the active electrode. After the application of an electrical bias the process of anodic oxidation occurs. Metallic cations are formed at the site of the active electrode and they begin to propagate into the insulating layer under the electric field. When cations reach the passive electrode the chemical reduction takes place and the filament growth starts. The filament grows from the passive electrode towards the active electrode. Once the filament bridges the two electrodes the low resistive state is reached as much higher current can pass through the conductive filament. Further growth of the filament is controlled by the external current compliance.

Typically, only one complete filament is produced as the voltage immediately drops when the first contact is made and current compliance is reached. Nevertheless, the formation of several filament seeds is possible during the formation process. The presence of grain boundaries and accumulated defects within the insulating layer serves to facilitate the formation of a filament. The radial growth of the filament is controlled by the current compliance and different resistivity levels can be achieved. This means that multi-level operation is possible by controlling the filament growth.

Many different processes can occur during the reset. Once the electric conduction is sufficiently high a large current passes through the narrow filament producing local Joule heating. This Joule heating will be most pronounced at the narrowest point – presumably near the active electrode. High Joule heating leads to the rupture of the filament through temperature assisted atom diffusion. Once the rupture occurs and a gap is produced the electrochemical process dominates the rest of the reset process.

Figure 1.19: Typical I-V curve and basic principle of operation of ECM. (a) OFF-state; (b), (c) Set process; (d) ON-state; (e) Reset process. Taken from [5].

#### Valence Change Memory

A VCM memory cell consists of an active electrode, a mixed ionic-electronic layer and an Ohmic passive electrode. In the case of VCM the active electrode does not provide a diffusion of metallic ions to form the filament, but rather provides an active site where the switching takes place.

Material with low oxygen affinity is used for the active electrode (e.g. TiN, Ir, Pt). Transition metal oxides like  $TaO_x$ ,  $TiO_x$ ,  $WO_x$ ,  $HfO_x$  are the most popular choice for the switching layer. These transition oxides are typically non-stoichiometric and oxygen deficient. Fully oxidised layers can also

be used and an electroforming process is used to produce an oxygen deficient conduction channel. Low work function materials with high oxygen affinity are used for the Ohmic electrode.

The basic principle of operation, together with a characteristic I-V curve, is shown in Figure 1.20.

Figure 1.20: Typical I-V curve and basic principle of operation of VCM. (a) OFF-state; (b) Set process; (c) ON-state; (d) Reset process. Taken from [5].

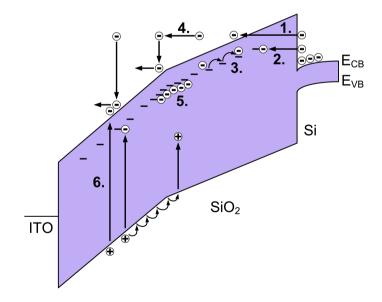

The electroforming step is crucial for most VCM systems. The forming voltage is typically significantly higher than the set voltage. Electroforming is a local reduction of the insulating layer. Both voltage polarities can be used. During the forming a high local temperature is generated due to the significant currents and large voltages. This temperature can cause local morphological changes or a phase transition of the material (e.g. formation of oxygen deficient Magnéli phase in case of  $TiO_2$ ).

After electroforming, a conductive n-type channel is produced. The following switching process takes place near the active electrode (the electrode with the lower oxygen affinity). A tunnelling barrier is typically present between the conductive filament and the active electrode. By varying the barrier height it is possible to achieve different resistance states. During the set process oxygen ions are removed from this region - consequently tunnelling and thermionic current is increased and

barrier height is reduced. During the reset process oxygen ions are moved back into the region. This increased the barrier height and the overall resistance of the VCM cell.

#### **Thermochemical Memory Cells**

The thermochemical memory cell (TCM) is dominated by the thermochemical process in contrast to ECM and VCM where the electrochemical process is the dominant one. Another difference to ECM and VCM is that TCM is operated in the unipolar mode – the polarity of both set and reset is the same. A temperature gradient affects the local stoichiometry through a local redox processes.

Many different materials are used for the switching layer, most often NiO,  $Al_2O_3$ , CoO, CuO, TiO<sub>x</sub>, Fe<sub>2</sub>O<sub>3</sub>, ZrO<sub>x</sub>. Even SiO<sub>2</sub> is used as the switching material in TCM. The same material is used for both electrodes as there is no need for asymmetry as in case of ECM and VCM. The reason for this is that oxygen ions and oxygen vacancies diffuse along the temperature gradient and the position of the switching point can be at the arbitrary place along the filament – not necessary near the interface. A typical I-V curve with physical principle of switching is shown in Figure 1.21.

A dramatic current increase is observed due to thermionic breakdown. An increase in the local temperature leads to permanent material change and formation of a conductive filament.

Current compliance is required to prevent the hard breakdown and nonreversible transition to LRS. Current compliance is removed in the reset process. This allows a higher current to pass at much lower voltages, leading to a partial rupture of the filament and recovery of the HRS. The conductivity of the HRS is usually larger than the conductivity of the pristine device as the filament is not completely dissolved and current can still flow through the part of the filament.

The set process is similar to the electroforming process, but it typically occurs at lower voltages. Current compliance is needed to prevent the hard breakdown just as in case of the electroforming. During the forming/set process a reduction of oxidation states occurs. Most transition metal oxides show much lower resistivity in the lower oxidation states.

Figure 1.21: Typical I-V curve and basic principle of operation of TCM. (a) Electroforming process; (b) ON-state; (c) Reset process; (d) OFF-state; (e) Set process. Taken from [5].

#### Introduction to Resistive Switching in Silicon Oxide

Silicon dioxide (silica) is one of the most abundant materials on the planet Earth – silicon and oxygen together account for 75% of earth's crust. In nature it can be found in crystalline or amorphous form – sandy areas are a good source of silicon dioxide (e.g. beaches, deserts). Also it can be found as quartz in the Earth's crust.

Silicon dioxide has a very wide spectrum of applications, especially in electronics and photonics, such as in manufacturing of semiconductor devices. In its quartz form, silicon dioxide has piezoelectric properties and it is used in the TV and radio industry for reception and transmission of signals. Silica is used for production of all kinds of glass. It is used in the food industry as an additive to powdered food as a flow agent.

The native oxide of silicon is an extremely stable compound, stable both in water and at elevated

temperatures. It is an excellent electrical insulator, and for many years it has been used as insulating layer in MOSFETs. Silicon dioxide forms a very good electrical interface with its silicon substrate. Silicon dioxide is one of the most widely used materials in the CMOS industry.

Reports of resistive switching in defective  $SiO_2$  date back to the 1960s[47], and the so-called soft breakdown of silicon oxides has been of interest for some time as a model to understand oxide failure in silicon microelectronics. However, the underlying physics of resistive switching in silicon oxide is relatively poorly understood.

Although one of the earliest reports of resistive switching in thin films is about resistive switching in thermally grown silicon dioxide, silicon dioxide is not the most popular choice for resistive switching material. Far more popular are transition metal oxides such as  $HfO_x$ ,  $TiO_x$ ,  $Ta_2O_5$ , NiO.

Silicon dioxide (or silicon oxide) was regarded as a passive, insulating element and for applications in RRAMs it is used either in ECM systems or doped with metallic species during the fabrication process. When used in ECM systems it supports the diffusion of metallic ions from the active electrode and does not play an active role in switching. Only recently has the idea of using silicon oxide as an active material for resistive switching been reinvestigated.

Typically, a Cu active electrode is used in silicon oxide based ECM. The switching is attributed by the formation and dissolution of a Cu filament within the silicon dioxide matrix[48]. An Ag active electrode is used in the case of amorphous silicon[49]. Similarly, amorphous silicon supports the diffusion of Ag ions to form the conductive filament. The silicon dioxide matrix may itself be doped with metallic ions, the diffusion of which can modify the resistivity of the matrix[50].

However, in CMOS processing diffusion of metallic ions is undesirable, as this could potentially endanger the operation of surrounding electronics. The intrinsic resistive switching of silicon oxide is therefore a more appealing mechanism. Such a system was first demonstrated by Yao et al.[51] in 2010, who reported a switchable silicon conductive path formed on the vertical surface of a silicon-rich silica pillar. No metals were present in the device, and the authors reported intrinsically unipolar switching. The switching process was attributed to the voltage-driven formation of silicon nano-crystals (NCs) in the surface of the silicon oxide. These nano-crystals will eventually produce a conductive filament that is able to support current flow. Very promising switching properties were reported: high ON/OFF ratios (>10<sup>5</sup>), fast switching (sub-100 ns), and good endurance (10<sup>4</sup> write-erase cycles). Figure 1.22[51] shows device schematics and characteristic I-V curves together with programming pulsing.

Figure 1.22: Device structures and electrical characterisations. (a) Schematics of the poly-Si/SiO<sub>x</sub>/poly-Si devices (50 $\mu$ m diameter) and the electrical characterisation setup. (b) An optical top-view image of the device arrays (top panel) and a scanning electron microscope (SEM) image of the cross section (bottom panel). (c) Characteristic I-Vs in a formed device: (blue curve) starting from an OFF state, the conductance of the device suddenly increases at +3.5V and drops at +8V. During a subsequent reverse voltage sweep (gray curve), the conductance goes back to a higher value at +8V, producing a current hysteresis. Corresponding "read", "set", and "reset" regions are defined based on these conductance changes. The vertical dashed line indicates the ON/OFF ratio at 1V. Inset: device resistance changes after +6 and +13 V programming voltage pulses. (d) (Top panel) A series of voltage pulses of +13, +1 (5 times), and +6 V serve as reset, read (5 times), and set operations, respectively. (Bottom panel) currents corresponding to each voltage pulse in the top panel. Taken from [51].

Interestingly, I-V curves are different to typical I-V curves reported either in the case of bipolar or unipolar switching. Switching is intrinsically unipolar but current compliance is not used and the reset voltage is higher than the set voltage, in contrast to more conventional unipolar switching. These early results are very promising as they fulfil many of the requirements for non-volatile memories.

However, the operation of such a device is possible only under vacuum due to the oxidation of silicon conductive pathways on the device surface under ambient conditions. The authors reported no evidence of high contrast controllable resistive switching in continuous films of silicon oxide: instead, silicon nano-filaments at vertical surfaces of mesa structures were proposed as the switching elements and any exposure to oxygen leads to oxidation and rupture of conductive filament.

In this thesis, resistive switching in the bulk silicon oxide is examined. This switching is not restricted to vacuum operation or to the surface of the active material.

# Chapter 2

# Experimental Techniques and Sample Preparation

This chapter provides an overview of the experimental techniques and the sample preparation procedure.

## **Electrical Characterisation**

#### **Electrical Probe Station**

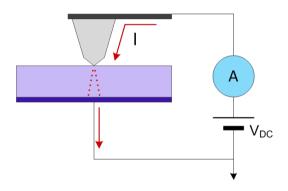

The equipment that we used for the I-V characterisation is the Keithley 4200-SCS Semiconductor Characterisation System. It consists of a characterisation probe station, an analyser module and the appropriate software (Keithley Interactive Test Environment). The characterisation probe station has four probes and a highly conductive sample platten. Two probes were used to generate I-V and I-t curves. Electrical characterisation was done in ambient conditions.

#### Impedance Spectroscopy

Impedance spectroscopy is a technique used to characterise electrical properties of materials. The sample is biased with an alternating voltage source, and the sample impedance is measured as a function of source frequency.

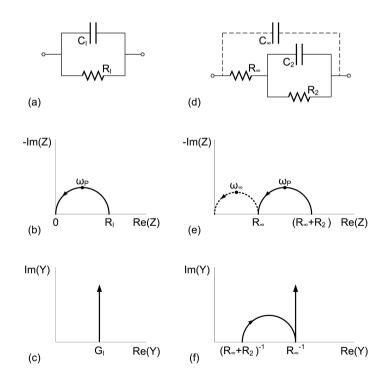

Impedance, in general terms, is defined as a complex ratio of the applied alternating (AC) voltage and the passing current. Impedance (Z) as a function of input frequency is plotted in the complex plane, called Cole-Cole plot. These are impedance plane plots (see Figures 2.1(b) and (e)). Admittance (inverse of impedance) plane plots are commonly used together with Cole-Cole plots (see Figures 2.1(c) and (f)). These plots can be related to the microstructure properties of the measured material. The overall resistivity can be modelled as an equivalent circuit consisting of resistors and capacitors connected in series and parallel (see Figures 2.1(a) and (d)). When plotted on a Cole-Cole plot, the curve shape of impedance can consist of several semi-circles indicating different equivalent circuits. By fitting the curve shape with a particular model it is possible to obtain the values for resistors and capacitors in the circuit. This is used to determine if there is only one or several conduction paths. This can be further related to bulk or grain boundary properties of the material.

Figure 2.1: Parts (a) and (d) show two common RC circuits. Parts (b) and (e) show their impedance plane plots and (c) and (f) their admittance plane plots. Arrows indicate the direction of increasing frequency. After [52].

#### Structural Characterisation

#### Scanning Tunnelling Microscopy

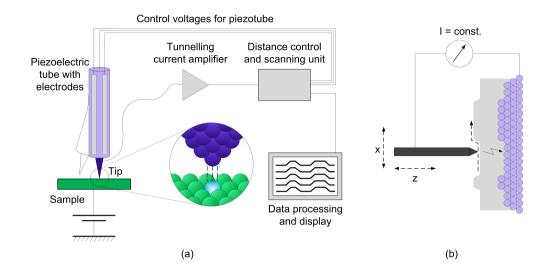

In 1986 the Nobel Prize in physics was awarded to Gerd Binning and Heinrich Roher for their invention of scanning tunnelling microscopy (STM) in 1981. Since its innovation, STM was an important tool for characterisation of surface structures. The breakthrough of this technique is its ability to study surface properties with atomic resolution.

The basic concept of the STM is quantum tunnelling of electrons between a sharp microscope tip and the investigated surface (the tip that we used is a platinum-rhodium or tungsten needle). The scanned surface must be conductive. A voltage is applied between the surface and the tip. When the needle tip is sufficiently near to the surface the electrons are able to tunnel through the vacuum (ambient - air in our case) barrier in between (typical distances are around 1nm). This current is called tunnelling current and it is based on quantum-mechanical tunnel effect. When the tunnelling current starts to flow and a tunnelling contact is established, the tip is moved across the surface by piezoelectric scanning unit. The scanning unit is typically capable to scan the areas in range of a few nm up to several µm. The scan provides a microscopic image of the spatial variation of the tunnel current.

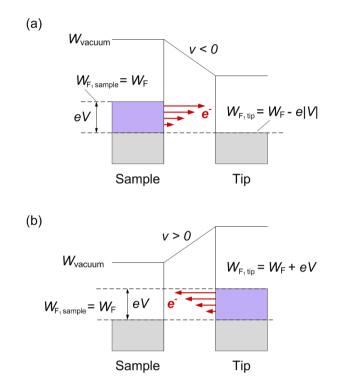

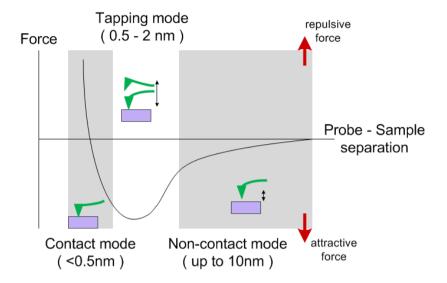

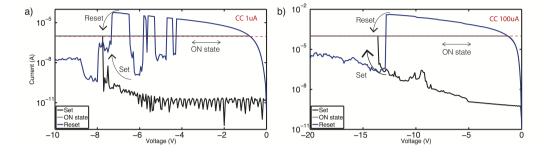

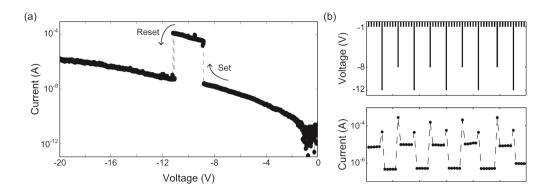

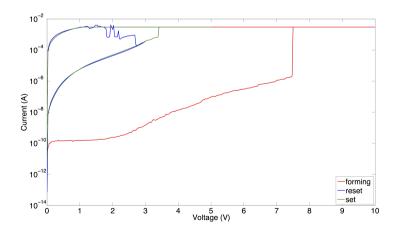

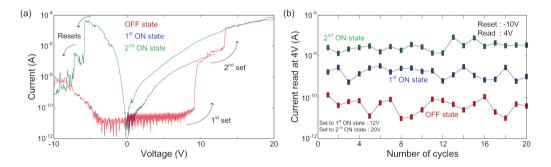

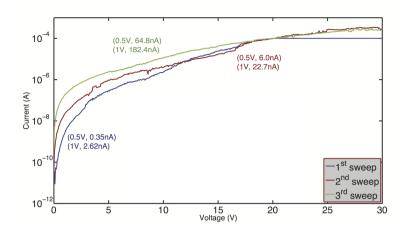

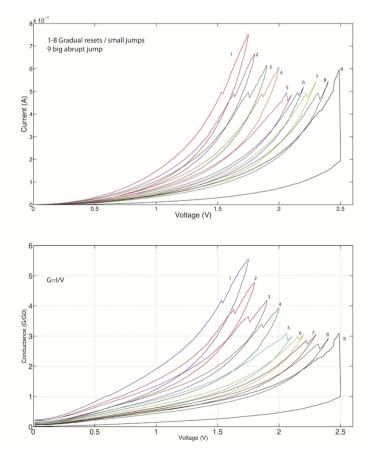

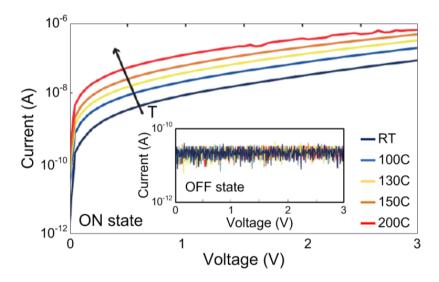

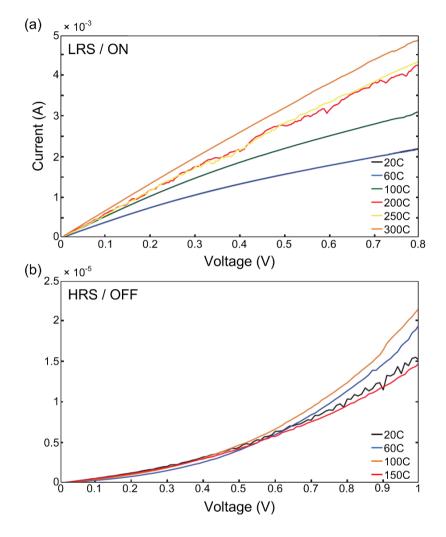

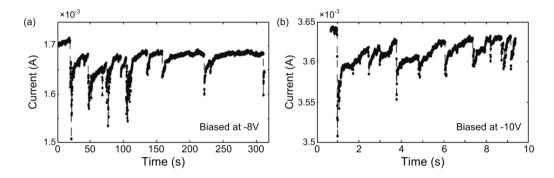

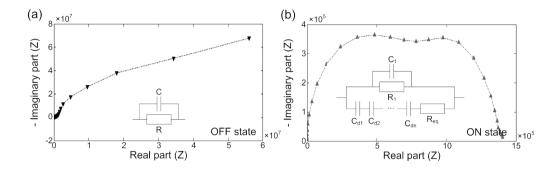

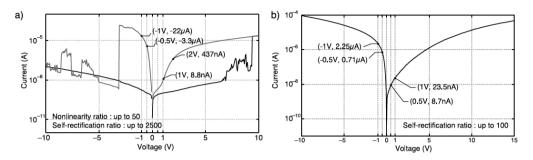

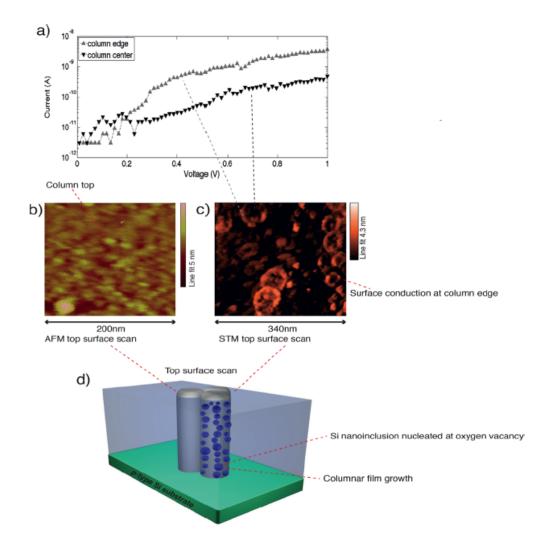

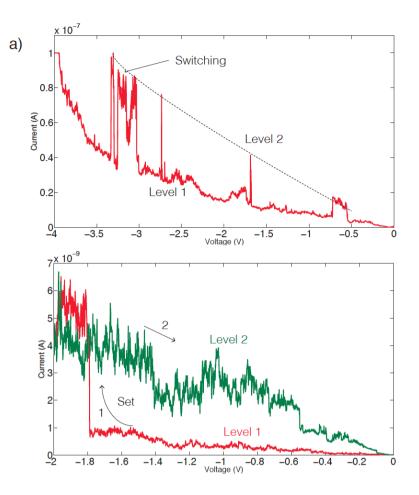

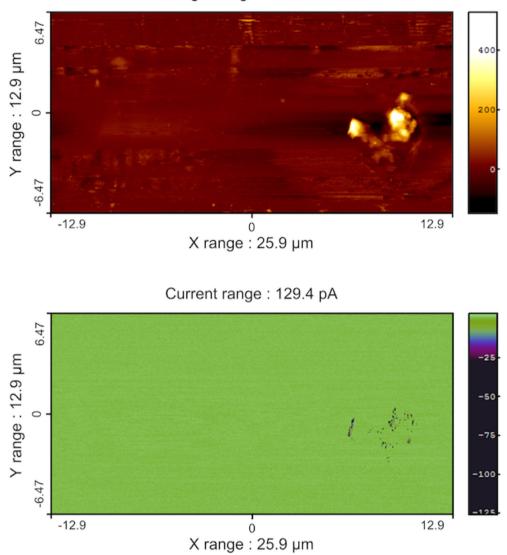

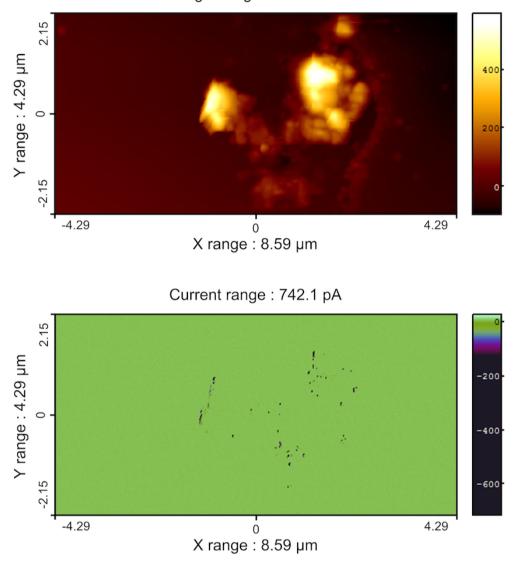

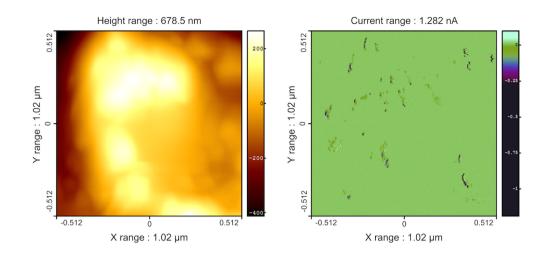

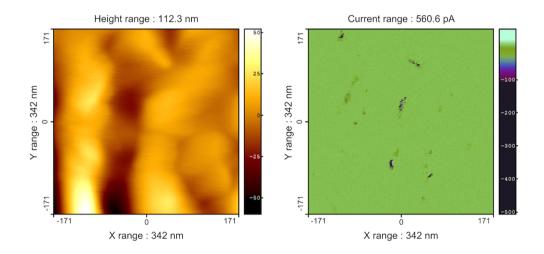

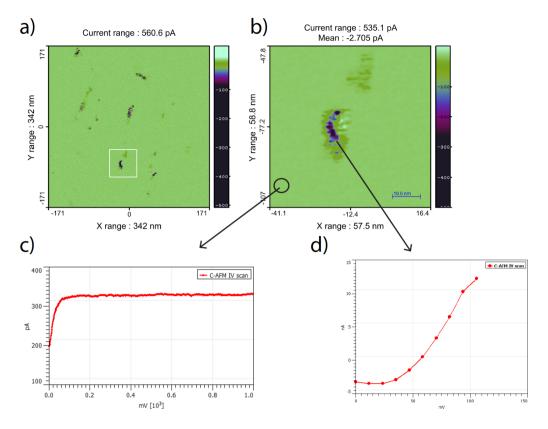

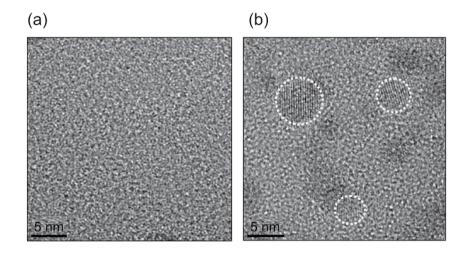

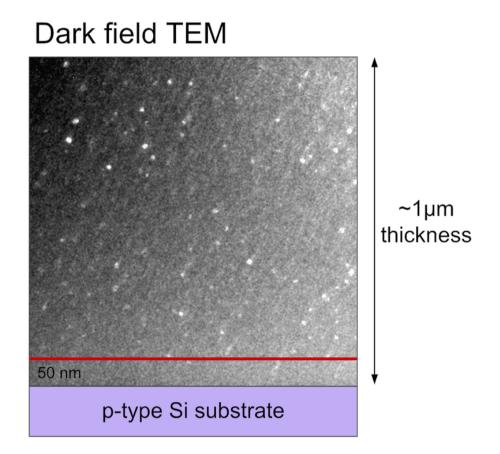

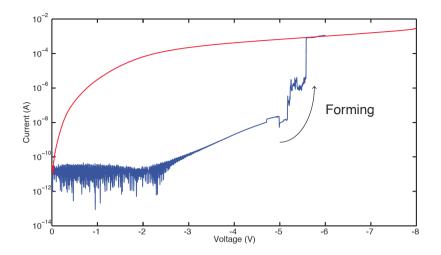

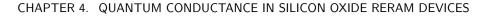

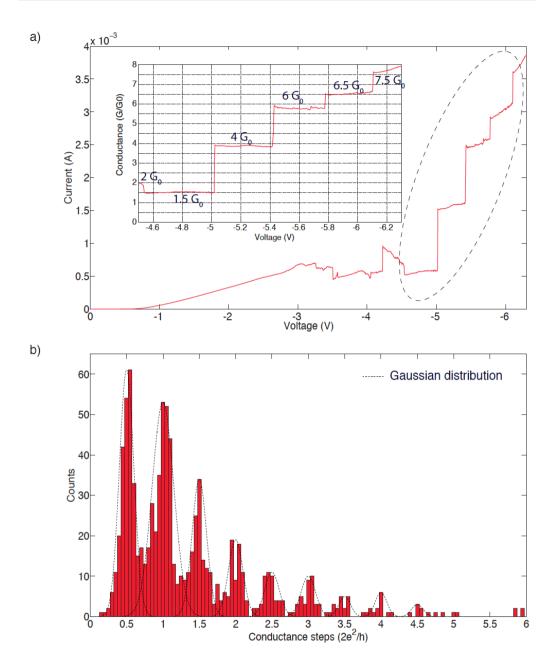

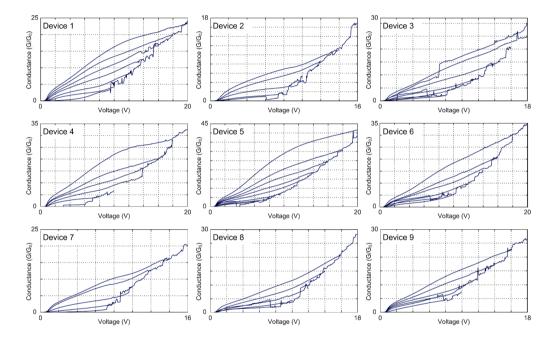

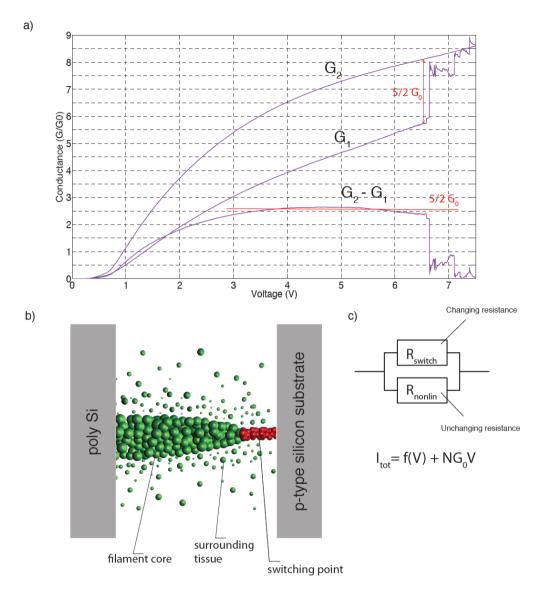

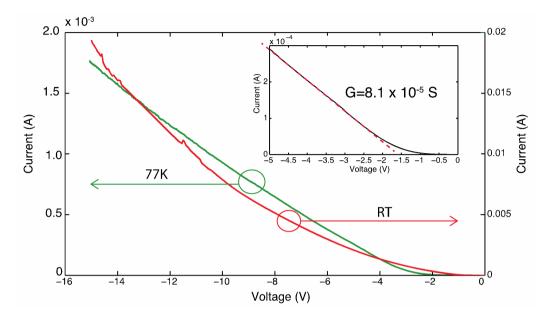

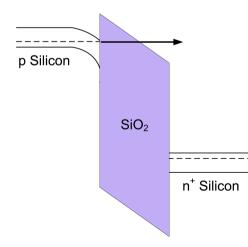

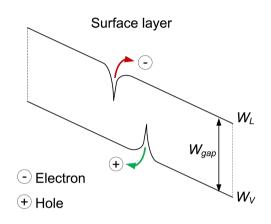

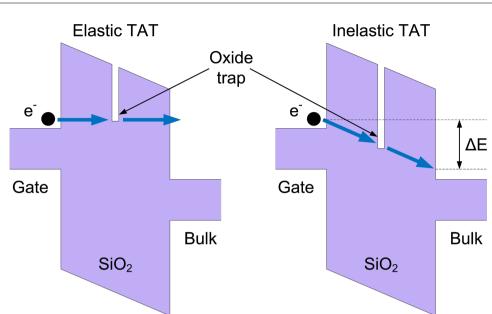

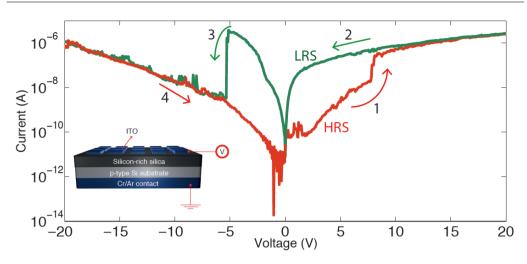

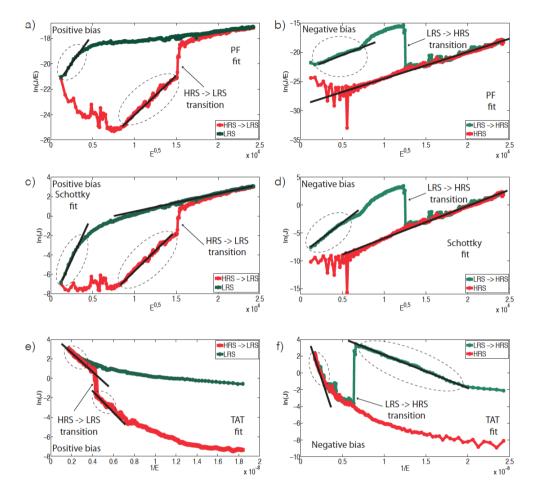

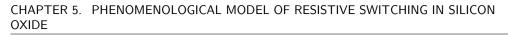

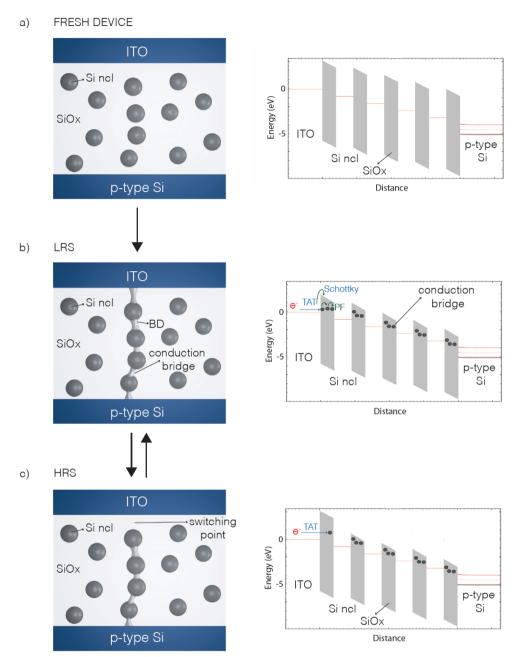

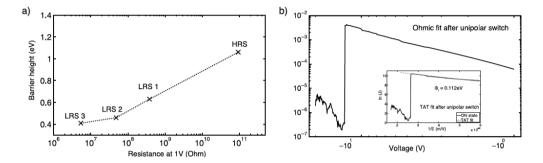

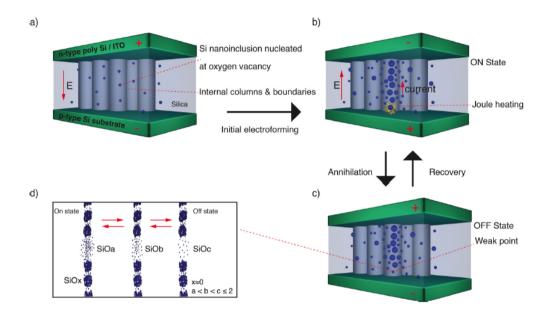

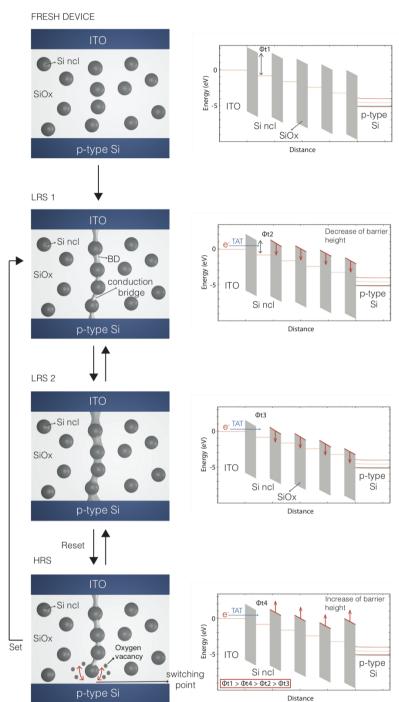

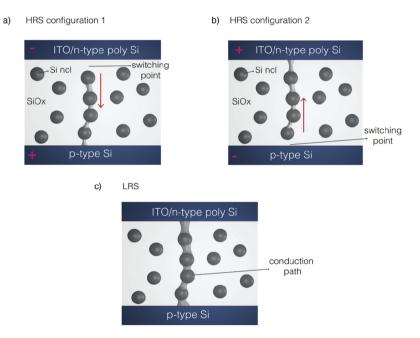

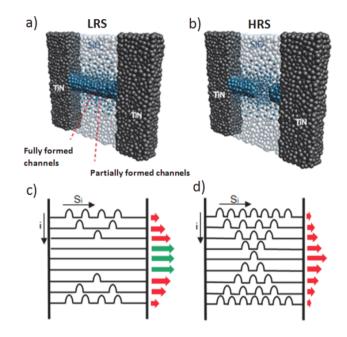

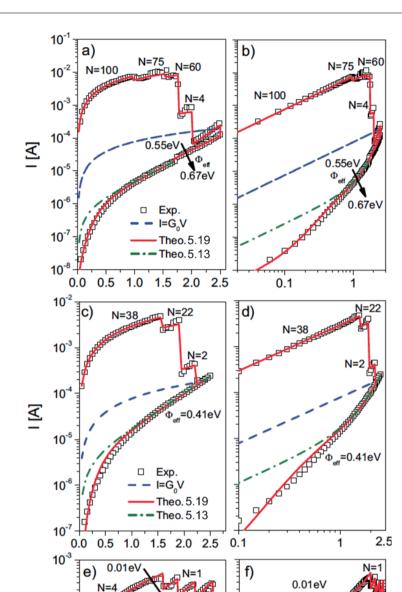

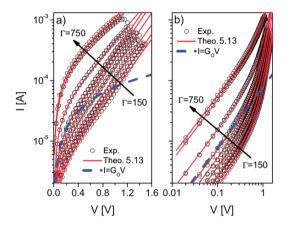

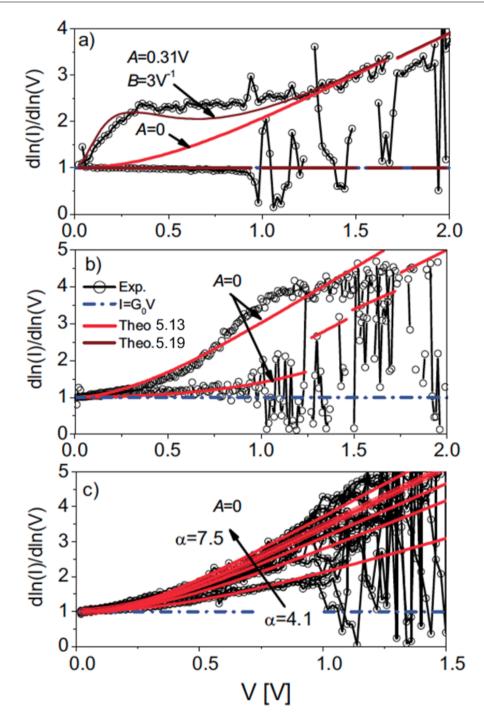

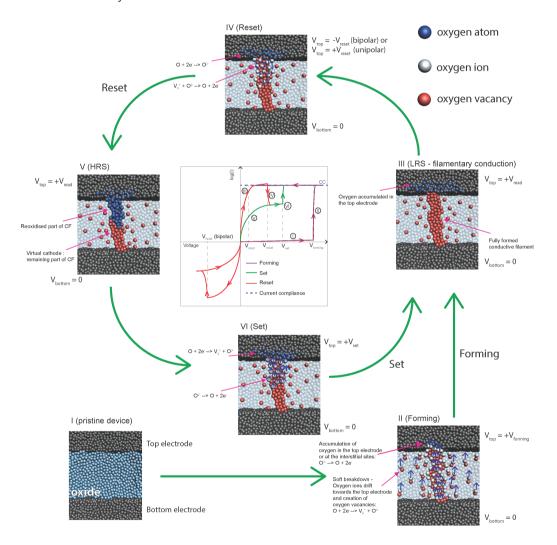

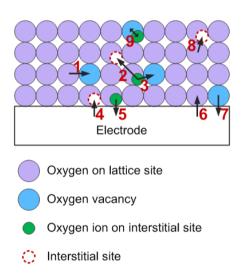

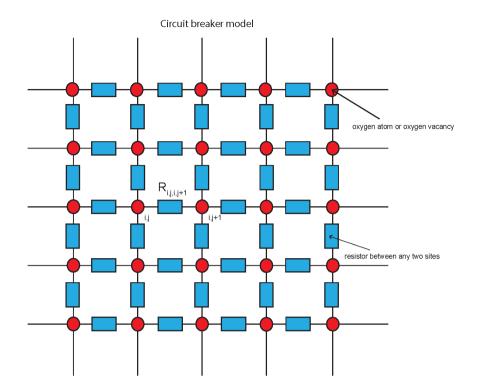

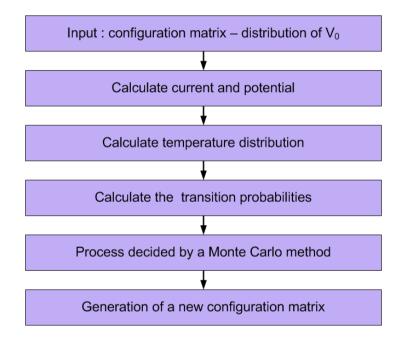

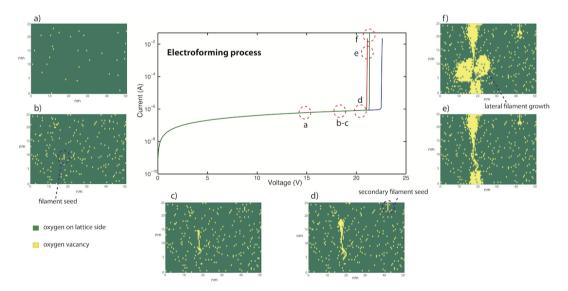

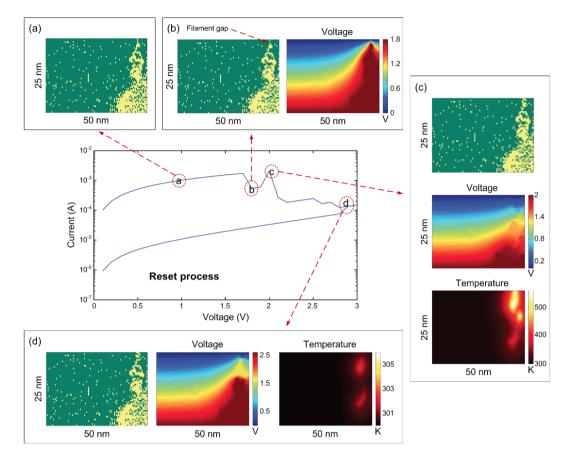

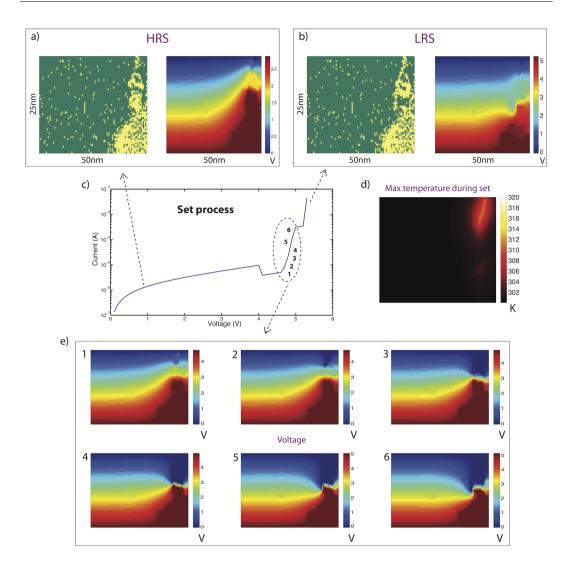

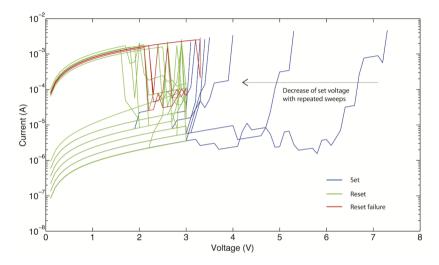

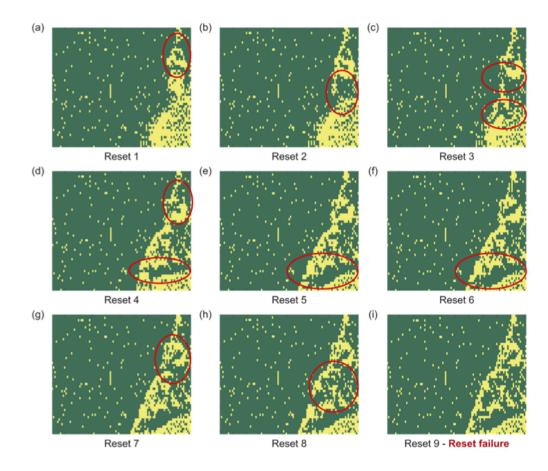

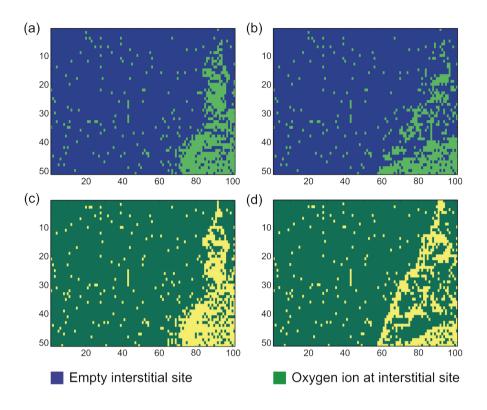

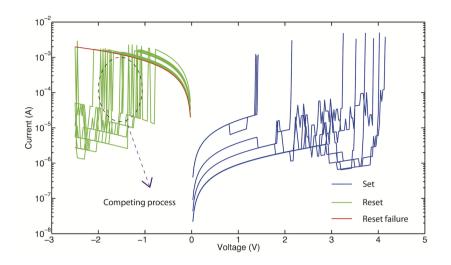

STM can reveal informations about the atomic-scale structures that must correspond to electrical states. These are the states from which electrons can tunnel into the tip or into which the electrons can tunnel from the tip. The electrons can tunnel across the potential barrier (between the tip and the sample) even when the electron's energy is lower than the barrier height. The corresponding tunnelling probability is proportional to  $e^{-kz}$ , where z is the tip-sample distance and k is a decay constant. Furthermore  $k = [2m(W_b - W)/\hbar]^{0.5}$ , where m is electron mass,  $W_b$  is the potential barrier and W is the energy of the tunnelling electron.