## NOVEL DESIGN TECHNIQUES AND CONTROL SCHEMES FOR HIGHER EFFICIENCY SWITCHED-MODE POWER CONVERTERS

CHI WA TSANG

Thesis submitted to the Department of Electronic and Electrical Engineering in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

Supervised by Dr. Martin P. Foster and Prof. David A. Stone

June 2014

#### **Summary**

This thesis details novel control schemes and design techniques with the aim of improving the performance of several switched-mode power converter topologies. These improvements include higher steady-state and transient efficiencies for hard-switching converters and the automatic current limiting provision for LLC resonant converters.

The thesis initially attempts to use linear closed-loop controllers to improve the transient response of synchronous buck converters, enabling them to be designed with a lower open-loop bandwidth so that the system can achieve higher efficiency. Three types of controllers were investigated viz: the PID, the state-feedback and the predictive controller. All three controllers exhibit similar step responses, which are the maximum transient responses achievable by the linear controllers with the given requirements.

The thesis then examines the parallel converter (i.e. a converter with two parallel connected power modules (PMs)) in detail with a view to improve the efficiency and to minimise the current ripple experienced by the output capacitor. Two control schemes and a design technique for the parallel converter are proposed, to simultaneously improve its efficiency and power density. The parallel converter in this research consists of two non-identical rated PMs (termed main PM and auxiliary PM), with the transient response requirement allocated to the auxiliary PM, thereby allowing the main PM to operate at a lower frequency for higher steady-state efficiency.

The first control scheme activates the auxiliary PM only when a pre-determined deviation in load/output voltage is exceeded under a load step. Thus, eliminating the losses contributed by the low efficiency auxiliary PM for small load step changes. The second control scheme shapes the auxiliary PM inductor current to be equal and opposite to the main PM current ripple, which when combined reduce the current ripple as experienced by the output filter capacitor, thereby allowing a lower value (and hence physically smaller) capacitor to be selected for higher power density. In order to improve the converter's steady-state efficiency further, the minimum load condition is

allocated to the auxiliary PM in the new design technique. These allow both the main PM inductance and its switching frequency to be lower for higher efficiency.

In recent years, the LLC has received much attention owing to its favourable operating characteristics including high efficiency and high power density. Usually one chooses to operate at or very close to the load independent point (LIP) since very little control effort is required to regulate the converter's output voltage in response to changes in the load. However under fault conditions where the load tends towards a short circuit, excessive currents can flow and thus control action need to be taken to protect both the converter and the load. The final topic of the thesis hence studies the characteristics of an LLC resonant converter with current-limiting capacitor-diode clamp and develops a new equivalent circuit model to predict the behaviour under overload conditions. A detailed analysis of the converter is presented using the proposed model, from which a design methodology is derived allowing the optimum circuit components to be selected to achieve the required current limiting/protection characteristics.

### **Publications**

Some of the work contained in this thesis has been disseminated at the following international conferences and in learned society journals:

- [P1] C.-W. Tsang, M.P. Foster and D.A. Stone, 'Parallel buck converter with non-identical power module for improved transient efficiency', Power Control and Intelligent Motion (PCIM) 2013.

- [P2] C.-W. Tsang, M.P. Foster and D.A. Stone, 'New design approach for higher energy efficiency with parallel converter', IET PEMD conf., 2012, pp 1-6.

- [P3] C.-W. Tsang, M.P. Foster, D.A. Stone and D. Gladwin, 'Active current ripple cancellation in parallel connected buck converter modules', IET Power Electron., 2013, 6, pp 721-731.

- [P4] C.-W. Tsang, M.P. Foster, D.A. Stone and D. Gladwin, (In Press) 'Analysis and design of the LLC resonant converter with capacitor-diode clamp current-limiting', IEEE Trans. Power Electron., accepted April 2014.

#### Acknowledgements

First, I would like to thank my supervisors Martin Foster and Dave Stone for their valuable support and guidance throughout the work, particularly, their patience and tolerance. I am indebted to you for all that I have learned.

I would like to acknowledge the EPSRC for providing funding to this research.

Many thanks all members for the Electrical Machines and Drives group for making the Mappin Building a friendly environment to conduct research in. In particular, Dan Gladwin, James Green, Andrew Fairweather, Daniel Schofield, Daniel Rogers, and those who have helped proof read my work.

Special thanks to Dalil Benchebra, Jonathan Davidson, David Hewitt, Sami Saad Abuzed, Huw Price, Jonathan Gomez, Shahab Nejad, Glynn Cooke and Rui Zhao for their constructive feedback and for helping me to prepare for the viva.

Finally, I would like to thank my parents and colleagues for all their support.

## **Table of Contents**

|    | Summ         | ary                                                                           | ii   |

|----|--------------|-------------------------------------------------------------------------------|------|

|    | Publica      | ations                                                                        | iv   |

|    | Acknow       | wledgements                                                                   | v    |

|    | Nomenclature |                                                                               |      |

|    | List of      | figures                                                                       | .xv  |

|    | List of      | tables                                                                        | xvii |

| 1. | Intro        | oduction                                                                      | 1    |

|    | 1.1.         | Background                                                                    | 1    |

|    | 1.2.         | Switched-mode power converters                                                | 2    |

|    | 1.2.1.       | Non-isolated converter                                                        | 3    |

|    | 1.2.2.       | Isolated power converter                                                      | 7    |

|    | 1.2.3.       | Load resonant converters                                                      | 9    |

|    | 1.2.4.       | Design considerations and challenges                                          | 12   |

|    | 1.3.         | Thesis outline                                                                | 13   |

|    | 1.4.         | Contribution                                                                  | 15   |

| 2. | Con          | trol schemes and switched-mode power converter topologies for high efficiency | 16   |

|    | 2.1.         | Introduction                                                                  | 16   |

|    | 2.2.         | Mathematical modelling                                                        | 16   |

|    | 2.3.         | Closed-loop controllers                                                       | 18   |

|    | 2.4.         | Transient efficiency of a parallel converter                                  | 20   |

|    | 2.5.         | Steady-state efficiency of a parallel converter                               | 22   |

|    | 2.6.         | Active current ripple cancellation schemes                                    | 22   |

|    | 2.7.         | LLC resonant converter with capacitor-diode clamp                             | 24   |

|    | 2.8.         | Summary                                                                       | 25   |

| 3. | Clos         | ed-loop controllers for buck converters                                       | 27   |

|    | 3.1.         | Introduction                                                                  | 27   |

|    | 3.2.         | Circuit operation and component selection                                     | 27   |

|    | 3.3.         | Equivalent circuit model                                                      | 32   |

|    | 3.4.         | Controller design                                                             | 39   |

|    | 3.4.1.       | Performance indices                                                           | 40   |

|    | 3.4.2.       | Robust PID control                                                            | 42   |

|    | 3.4.3.       | State feedback control                                                        | 44   |

|    | 3.4.4. | Predictive control                                                        | 46  |

|----|--------|---------------------------------------------------------------------------|-----|

|    | 3.4.5. | Digital implementation                                                    | 49  |

|    | 3.5.   | Design examples and experimental results                                  | 49  |

|    | 3.5.1. | Robust PID controller                                                     | 50  |

|    | 3.5.2. | State feedback controller                                                 | 52  |

|    | 3.5.3. | Predictive controller                                                     | 54  |

|    | 3.5.4. | Converter prototype                                                       | 56  |

|    | 3.6.   | Summary                                                                   | 61  |

| 4. | . Imp  | rovements in transient response with parallel converters                  | 63  |

|    | 4.1.   | Introduction                                                              | 63  |

|    | 4.2.   | Circuit configuration and components selection                            | 63  |

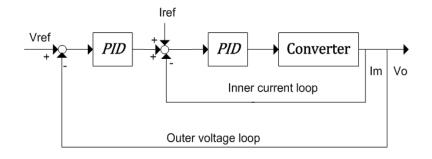

|    | 4.3.   | Control schemes for transient condition                                   | 66  |

|    | 4.3.1. | FRDB scheme                                                               | 68  |

|    | 4.3.2. | SCM-PCM scheme                                                            | 70  |

|    | 4.3.3. | Proposed FRHE scheme                                                      | 72  |

|    | 4.4.   | Controller design                                                         | 74  |

|    | 4.5.   | Design example and experimental results                                   | 76  |

|    | 4.5.1. | Settling time and on-duration characteristics                             | 77  |

|    | 4.5.2. | Converter prototype                                                       | 80  |

|    | 4.6.   | Summary                                                                   | 82  |

| 5. | . Imp  | rovements in steady-state efficiency with parallel connected converters   | 83  |

|    | 5.1.   | Introduction                                                              | 83  |

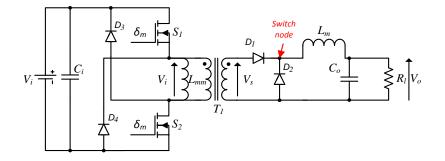

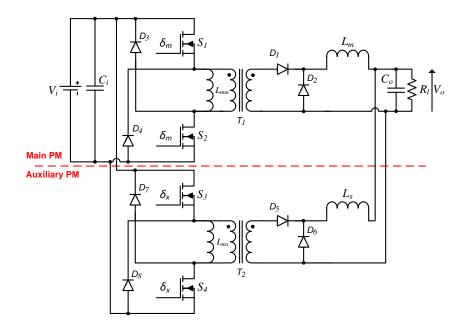

|    | 5.2.   | Two-switch forward converter (2SFC)                                       | 83  |

|    | 5.2.1. | Circuit operation                                                         | 84  |

|    | 5.3.   | Design techniques for parallel converter                                  | 87  |

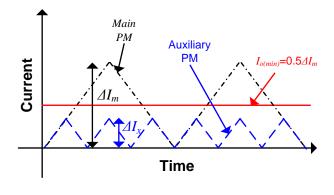

|    | 5.3.1. | Proposed (HSSE) design technique                                          | 88  |

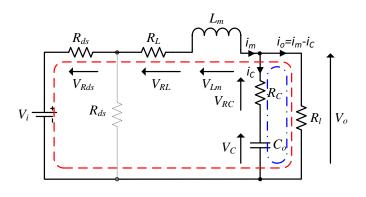

|    | 5.4.   | Loss analysis                                                             | 90  |

|    | 5.5.   | Design examples and experimental results                                  | 94  |

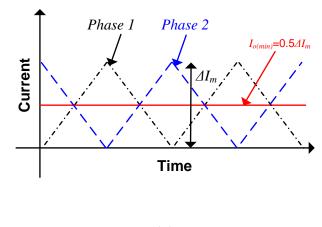

|    | 5.5.1. | Interleaved converter design                                              |     |

|    | 5.5.2. | Converter designed by the proposed HSSE technique                         | 95  |

|    | 5.5.3. | Prototype converters                                                      | 99  |

|    | 5.6.   | Summary                                                                   | 102 |

| 6  | Acti   | ve current ripple cancellation using a high frequency auxiliary converter | 103 |

|    | 6.1.   | Introduction                                                              | 103 |

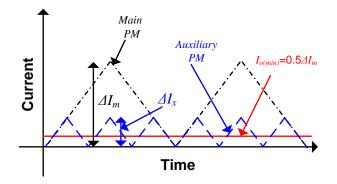

|    | 6.2.     | Active current ripple cancellation                  | 103 |

|----|----------|-----------------------------------------------------|-----|

|    | 6.2.1.   | Theory of operation                                 | 104 |

|    | 6.2.2.   | Inductor current ripple and rate of change          | 105 |

|    | 6.2.3.   | Generation of the cancellation current              | 108 |

|    | 6.3.     | Design consideration                                | 110 |

|    | 6.3.1.   | Auxiliary PM inductor and duty cycle selection      | 110 |

|    | 6.3.2.   | Ripple reduction ratio                              | 114 |

|    | 6.3.3.   | Efficiency comparison                               | 114 |

|    | 6.3.4.   | Practical consideration                             | 116 |

|    | 6.4.     | Design example and experimental results             | 117 |

|    | 6.4.1.   | Switching frequencies and component value selection | 118 |

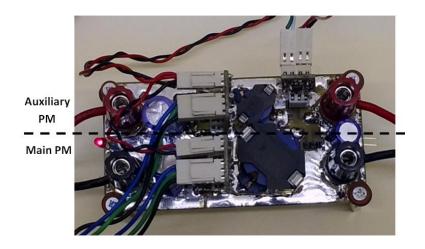

|    | 6.4.2.   | Prototype converter                                 | 122 |

|    | 6.5.     | Summary                                             | 126 |

| 7. | LLC      | resonant converter with capacitor-diode clamp       | 127 |

|    | 7.1.     | Introduction                                        | 127 |

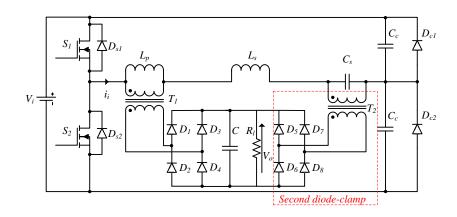

|    | 7.2.     | Circuit operation                                   | 127 |

|    | 7.3.     | Equivalent circuit model                            | 133 |

|    | 7.3.1.   | Diode-clamp inactive                                | 133 |

|    | 7.3.2.   | Diode-clamp active                                  | 135 |

|    | 7.3.3.   | Diode-clamp conduction point                        | 138 |

|    | 7.3.4.   | Nominalised gain with active diode-clamp            | 139 |

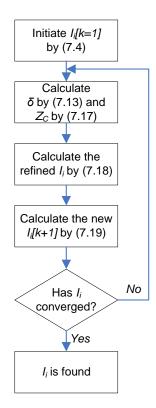

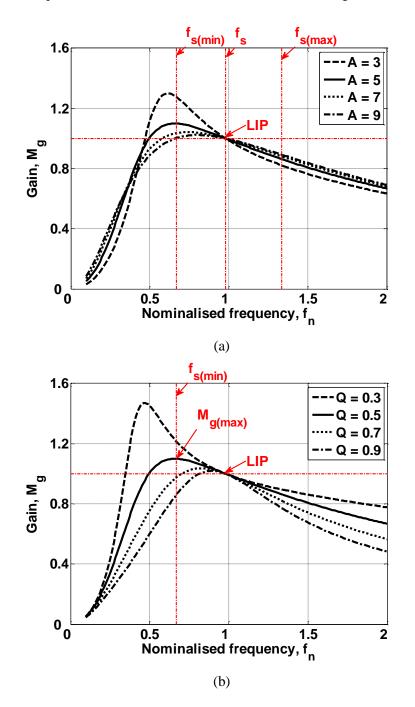

|    | 7.4.     | Analysis of converter operating characteristic      | 140 |

|    | 7.4.1.   | Capacitor diode-clamp characteristics               | 142 |

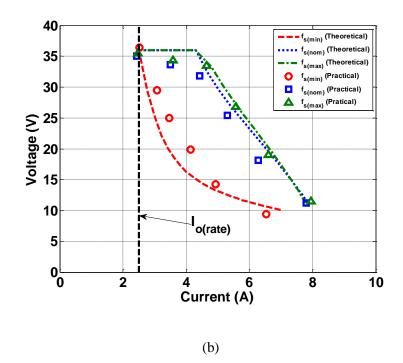

|    | 7.4.2.   | Converter Voltage-Current (VI) characteristics      | 145 |

|    | 7.5.     | Design example                                      | 148 |

|    | 7.6.     | Summary                                             | 153 |

| 8. | Con      | clusion and future work                             | 154 |

|    | 8.1.     | Conclusion                                          | 154 |

|    | 8.2.     | Future work                                         | 155 |

| R  | eference | 2                                                   | 158 |

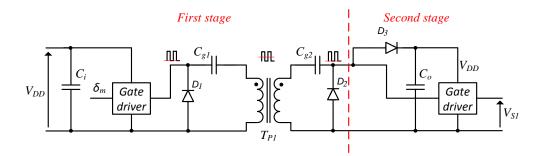

| A  | ppendix  | A - Isolated MOSFET gate driver                     | 169 |

| A  | ppendix  | B - rms current                                     | 169 |

| A  | ppendix  | C - Calorimeter for efficiency measurement          | 171 |

## Nomenclature

Subscript m, x and i are also used with the list of symbol above to distinguish the parameters for the main PM, auxiliary PM and interleaved converter PMs (e.g.  $\delta_m$ ,  $\delta_x$  and  $\delta_i$  are the duty cycles for the main PM, auxiliary PM and interleaved PM respectively).

| A, B, C, D, E, K                                        | matrices, bold font represents vector                       |

|---------------------------------------------------------|-------------------------------------------------------------|

| A <sub>c</sub>                                          | inductor core area                                          |

| $A_s$                                                   | resonant tank inductor ratio $(= L_p/L_s)$                  |

| $A_w$                                                   | winding cross-sectional area                                |

| BW                                                      | system bandwidth                                            |

| $B_f$                                                   | flux density                                                |

| B <sub>peak</sub>                                       | peak flux density                                           |

| B <sub>s</sub>                                          | capacitance sharing ratio $(= C_r/C_s)$                     |

| <i>B</i> ′                                              | augmented input vector, bold font represents vector         |

| ССМ                                                     | continuous conduction mode                                  |

| СМС                                                     | current mode control                                        |

| $C_c, C_s$                                              | resonant tank capacitors                                    |

| $C_{gs}, C_{rss}, C_{oss}$                              | parasitic capacitors of MOSFET                              |

| $C_i$                                                   | input capacitor                                             |

| Co                                                      | output capacitor                                            |

| $C_r$                                                   | equivalent resonant capacitance (with inactive diode-clamp) |

| DT                                                      | dead-time                                                   |

| $D_k$                                                   | predictive controller's control gain                        |

| $D_{c1}, D_{c2}$                                        | diode-clamp diode                                           |

| $D_1, D_2, D_3, D_4$                                    | diodes                                                      |

| $\frac{d}{dt}I_m, \frac{d}{dt}I_x, \frac{d}{dt}I_{m+x}$ | rate of inductor currents                                   |

| $\frac{d}{dt}I_{m(+)}$ , $\frac{d}{dt}I_{x(+)}$         | rate of rise of inductor currents                           |

| $\frac{d}{dt}I_{m(-)}, \frac{d}{dt}I_{x(-)}$            | rate of fall of inductor currents                           |

| $\frac{d}{dt}I_{m(net)}, \frac{d}{dt}I_{x(net)}$        | net rate of inductor currents                               |

| $\frac{d}{dt}I_{x(net+)}$                               | net rate of rise of inductor current                        |

| $\frac{d}{dt}I_{x(net-)}$                               | net rate of fall of inductor current                        |

| ESR                                  | equivalent series resistance                            |

|--------------------------------------|---------------------------------------------------------|

| е                                    | error signal, $e = r - y$                               |

| e <sub>ss</sub>                      | steady-state error                                      |

| FHA                                  | fundamental harmonic approximation                      |

| FRDB                                 | fast response double buck scheme                        |

| FRHE                                 | fast recovery with high transient efficiency scheme     |

| $f_{sm}, f_{sx}, f_{si}$             | switching frequencies                                   |

| $f_{s(min)}$                         | minimum switching frequency                             |

| $f_{s(max)}$                         | maximum switching frequency                             |

| $f_n$                                | nominalised frequency $(f_n = f_s/f_0)$                 |

| fo                                   | resonant frequency                                      |

| HSSE                                 | high steady-state efficiency design technique           |

| IAE                                  | integral of the absolute magnitude of the error         |

| ISE                                  | integral of the squared of the error                    |

| ITAE                                 | integral of time multiplied by absolute error           |

| ITSE                                 | integral of time multiplied by the squared error        |

| Ι                                    | identity matrix                                         |

| I <sub>co</sub>                      | current reference                                       |

| $I_{(dc)}$                           | dc current                                              |

| I <sub>i</sub>                       | input current                                           |

| $I_{m(rms)}, I_{x(rms)}, I_{i(rms)}$ | rms currents                                            |

| I <sub>ref</sub>                     | current reference                                       |

| In                                   | normalised output current $(= I_{o(over)}/I_{o(rate)})$ |

| $I_m, I_x$                           | inductor current                                        |

| Io                                   | output current                                          |

| I <sub>o(rate)</sub>                 | maximum rated output current                            |

| I <sub>o(over)</sub>                 | overloading output current                              |

| I <sub>peak</sub>                    | peak current                                            |

| I <sub>r</sub>                       | compensation ramp                                       |

| Is                                   | current step                                            |

| J                                    | cost function                                           |

| k <sub>im</sub>                      | imaginary component used in $M_{g(clmp)}$               |

| k <sub>re</sub>                      | real component used in $M_{g(clmp)}$                    |

| KVL                                  | Kirchhoff's voltage law                                 |

| KCL                                  | Kirchhoff's current law                                 |

| K <sub>c</sub>                       | input voltage compensation gain                         |

|                                      |                                                         |

| 17                    | Eulor's advation gain                                       |

|-----------------------|-------------------------------------------------------------|

| K <sub>e</sub>        | Euler's equation gain                                       |

| K <sub>g</sub>        | instrumentation amplifier gain                              |

| $K_P, K_{Pm}, K_{Px}$ | proportional gains of PID controller                        |

| $K_I, K_{Im}, K_{Ix}$ | integral gains of PID controller                            |

| $K_D, K_{Dm}, K_{Dx}$ | derivative gains of PID controller                          |

| $K_1, K_2, K_i$       | state feedback controller gains                             |

| K <sub>PWM</sub>      | PWM gain                                                    |

| K <sub>Id</sub>       | discrete-time equivalent of integrator gain                 |

| K <sub>s</sub>        | system gain                                                 |

| LIP                   | load independent point                                      |

| $L, L_m, L_x, L_i$    | inductors                                                   |

| $L_p, L_s$            | resonant tank inductors                                     |

| $L_{mm}, L_{mx}$      | magnetising inductors                                       |

| l                     | legth of wire                                               |

| $M_g$                 | nomalised gain (with inactive diode-clamp)                  |

| $M_{g(max)}$          | maximum nomalised gain (with inactive diode-clamp)          |

| $M_{g(min)}$          | minimum normalised gain (with inactive diode-clamp)         |

| $M_{g(clmp)}$         | nomalised gain (with activated diode-clamp)                 |

| m                     | number of auxiliary PM cycles with respect to main PM cycle |

| $m_n$                 | number of phases                                            |

| $N_k$                 | predictive controller's feedback gain                       |

| $N_L$                 | inductor number of turns                                    |

| $N_p$                 | transformer primary number of turns                         |

| N <sub>s</sub>        | transformer secondary number of turns                       |

| n                     | transformer turn ratio                                      |

| $n_y$                 | predictive controller's output horizon                      |

| $n_u$                 | predictive controller's input horizon                       |

| РСМ                   | peak current mode                                           |

| РМ                    | power module                                                |

| PWM                   | pulse-width modulation                                      |

| P <sub>gm</sub>       | gate drive loss                                             |

| P <sub>cm</sub>       | MOSFET conduction loss                                      |

| P <sub>sm</sub>       | MOSFET switching loss                                       |

| P <sub>cL</sub>       | inductor conduction loss                                    |

| P <sub>sL</sub>       | inductor switching loss                                     |

| P <sub>cd</sub>       | diode conduction loss                                       |

| P(n)                  | total loss ratio                                            |

|                       |                                                             |

| $P_c(n)$          | conduction loss ratio                                |

|-------------------|------------------------------------------------------|

| $P_s(n)$          | switching loss ratio                                 |

| $P_{gm}(n)$       | gate drive loss ratio                                |

| $P_{cm}(n)$       | MOSFET conduction loss ratio                         |

| $P_{sm}(n)$       | MOSFET switching loss ratio                          |

| $P_{cL}(n)$       | inductor conduction loss ratio                       |

| $P_{SL}(n)$       | inductor switching loss ratio                        |

| $P_{cd}(n)$       | diode conduction loss ratio                          |

| P <sub>cm</sub>   | MOSFET conduction loss                               |

| P <sub>r</sub>    | predictive controller feedforward gain               |

| p                 | ripple reduction ratio                               |

| Q                 | quality factor $\left(=\sqrt{L_s/C_r}/R_{eq}\right)$ |

| $Q_g$             | MOSFET gate charge                                   |

| $Q_n$             | normalised Q-factor (= $Q_{over}/Q_{rate}$ )         |

| Qover             | Q-factor at overloading                              |

| $Q_r$             | charge due to current ripple                         |

| Q <sub>rate</sub> | Q-factor at maximum rated load                       |

| Q <sub>rr</sub>   | reverse recovery charge                              |

| $Q_{us}$          | charge due to load step                              |

| R                 | real component of $Z_c$                              |

| R <sub>C</sub>    | parasitic capacitor resistance                       |

| R <sub>ds</sub>   | MOSFET on-state resistance                           |

| R <sub>eq</sub>   | equivalent load resistance                           |

| $R_g$             | instrumentation amplifier gain resistor              |

| $R_L$             | parasitic inductor resistance                        |

| R <sub>l</sub>    | load resistance                                      |

| R <sub>w</sub>    | winding resistance                                   |

| r                 | reference signal                                     |

| SBC               | synchronous buck converter                           |

| SCM               | sensorless current mode                              |

| SCM – PCM         | sensorless and peak current mode scheme              |

| SMPC              | switched-mode power converter                        |

| SSA               | state-space averaging                                |

| $S_1, S_2$        | MOSFETs                                              |

| S                 | complex frequency $(= j\omega_s)$                    |

| $T, T_s$          | switching period                                     |

| $T_D$             | derivative time constant                             |

|                   |                                                      |

| $T_I$                          | integral time constant                                         |

|--------------------------------|----------------------------------------------------------------|

| $T_f$                          | MOSFET fall time                                               |

| $T_r$                          | MOSFET rise time                                               |

| $T_p$                          | time period                                                    |

| T <sub>set</sub>               | settling time                                                  |

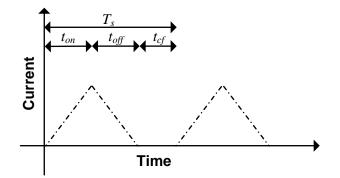

| $T_{x}$                        | auxiliary PM switching period                                  |

| $T_1$                          | transformer                                                    |

| t                              | time                                                           |

| $t_{m(on)}, t_{x(on)}$         | on-periods                                                     |

| $t_{m(off)}, t_{m(off)}$       | off-periods                                                    |

| $t_{m(cf)}$                    | cut-off period                                                 |

| u                              | intput signal                                                  |

| VMC                            | voltage mode control                                           |

| VR                             | voltage regulator                                              |

| V <sub>C</sub>                 | voltage across capacitor $C_o$                                 |

| V <sub>c</sub>                 | voltage across capacitor $C_c$                                 |

| $V_f$                          | diode forward voltage drop                                     |

| $V_{gs}$                       | MOSFET gate-source voltage                                     |

| $V_{g}$                        | MOSFET gate drive voltage                                      |

| $V_i$                          | input voltage                                                  |

| V <sub>i(min)</sub>            | minimum input voltage                                          |

| V <sub>i(max)</sub>            | maximum input voltage                                          |

| V <sub>i(norm)</sub>           | nominal input voltage                                          |

| $V_{L_m}$                      | voltage across inductor $L_m$                                  |

| $V_n$                          | normalised output voltage $(= V_{o(over)}/V_{o(rate)})$        |

| $V_{R_C}, V_{R_L}, V_{R_{ds}}$ | voltage across parasitic components $R_c$ , $R_L$ , $R_{ds}$ . |

| Vo                             | output voltage                                                 |

| Vos                            | voltage overshoot                                              |

| V <sub>o(rate)</sub>           | maximum rated output voltages                                  |

| V <sub>o(over)</sub>           | overloading output voltage                                     |

| V <sub>ref</sub>               | voltage reference                                              |

| $V_{th}$                       | MOSFET threshold voltage                                       |

| V <sub>us</sub>                | voltage undershoot                                             |

| v <sub>co</sub>                | control signal                                                 |

| $v_{ds}$                       | MOSFET drain-source voltage                                    |

| vs                             | sawtooth signal                                                |

|                                |                                                                |

| Х                                 | imaginary component of $Z_c$                              |

|-----------------------------------|-----------------------------------------------------------|

| x                                 | state vector, bold font represents vector                 |

| <i>x</i> ′                        | augmented state equation                                  |

| ż                                 | $(d/dt)\mathbf{x}$                                        |

| х́′                               | (d/dt)x'                                                  |

| ĩ                                 | state vector x with disturbance                           |

| <i>x</i>                          | $(d/dt)\widetilde{x}$ with disturbance                    |

| у                                 | output signal                                             |

| ŷ                                 | output signal y with distribute                           |

| $Z_1$                             | resonant tank impedance (with inactive diode-clamp)       |

| Z <sub>2</sub>                    | resonant tank impedance (with activated diode-clamp)      |

| Z <sub>c</sub>                    | equivalent clamping capacitance impedance (with activated |

|                                   | diode-clamp)                                              |

| α                                 | load sharing ratio                                        |

| $\alpha_c, \ \beta_c, \ k_c$      | inductor core loss constants                              |

| $lpha_d$                          | damping factor                                            |

| β                                 | frequency ratio $f_{sm}/f_{si}$                           |

| γ                                 | frequency ratio $f_{sx}/f_{si}$                           |

| δ                                 | diode-clamp non-conduction angle                          |

| $\delta_{(+)}$                    | desired duty cycle for $t_{(on)}$                         |

| $\delta_{(-)}$                    | desired duty cycle for $t_{(off)}$                        |

| $\delta_m,\delta_x,\delta_i$      | duty cycles                                               |

| $	ilde{\delta}_m$                 | duty cycle $\delta_m$ with distribute                     |

| $\delta_{m(ss)},  \delta_{x(ss)}$ | steady-state duty cycles                                  |

| $\delta'_m$                       | complemented main PM duty cycle                           |

| ζ                                 | damping ratio                                             |

| θ                                 | angle                                                     |

| λ                                 | weighting function                                        |

| ρ                                 | wire resistivity                                          |

| $\omega_n$                        | system natural frequency                                  |

| $\omega_s$                        | angular switching frequency (= $2\pi f_s$ )               |

| Δ                                 | tolerant                                                  |

| $\Delta V_o$                      | output voltage ripple                                     |

| $\Delta I_m$                      | current ripple                                            |

| 2SFC                              | two-switch forward converter                              |

|                                   |                                                           |

## List of figures

| Fig. 1.1 Schematic of a linear DC power supply.                                                | 1   |

|------------------------------------------------------------------------------------------------|-----|

| Fig. 1.2 Schematic of main connected power supply with SMPC                                    | 2   |

| Fig. 1.3 The three most basic SMPC. (a) Buck converter (b) Boost converter (c) Buck-boost      |     |

| converter                                                                                      | 4   |

| Fig. 1.4 Inverting and non-inverting step up/down converters. (a) Cuk converter (a) SEPIC      |     |

| converter (b) Zeta converter                                                                   |     |

| Fig. 1.5 Isolated step down converter. (a) Forward converter (b) Push-pull converter (c) Half- |     |

| bridge converter (d) Full-bridge converter                                                     |     |

| Fig. 1.6 Flyback isolated step up/down converter                                               | 9   |

| Fig. 1.7 Half-bridge resonant converter. (a) Series resonant converter (b) Parallel resonant   | 4.0 |

| converter                                                                                      |     |

| Fig. 1.8 Two-switch forward converter.                                                         |     |

| Fig. 3.1 Circuit diagram of the synchronous buck converter                                     |     |

| Fig. 3.2 MOSFETs drive signals with dead-times.                                                |     |

| Fig. 3.3 Circuit diagram of SBC under the dead-time period.                                    |     |

| Fig. 3.4 Circuit diagrams showing the two subintervals. (a) on-period (b) off-period           |     |

| Fig. 3.5 Steady state inductor current and output voltage waveforms.                           |     |

| Fig. 3.6 Equivalent circuit model under different subintervals. (a) on-period (b) off-period   |     |

| Fig. 3.7 Block diagram of system in state-space form.                                          |     |

| Fig. 3.8 Block diagram of system in transfer function form.                                    |     |

| Fig. 3.9 Block diagram of closed-loop system                                                   |     |

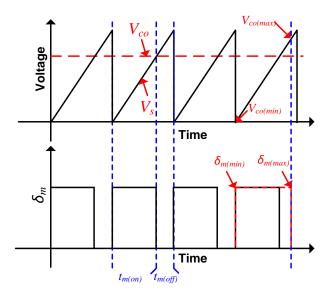

| Fig. 3.10 Operation of PWM, $u = 1$ if vs < vco otherwise $u = 0$                              |     |

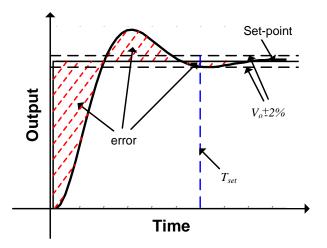

| Fig. 3.11 Example of a system step response.                                                   | 41  |

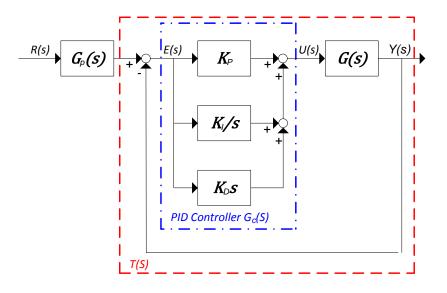

| Fig. 3.12 Block diagram of system with robust PID controller.                                  | 42  |

| Fig. 3.13 Block diagram of system with state feedback with integral control                    | 44  |

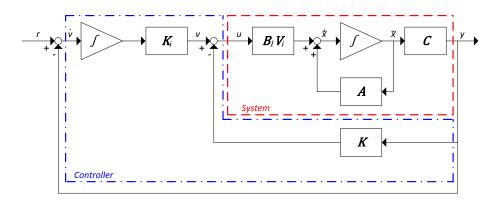

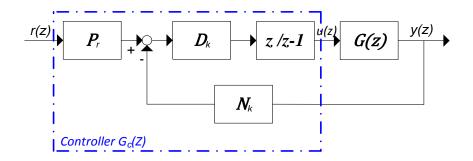

| Fig. 3.14 Block diagram of system with predictive controller                                   | 46  |

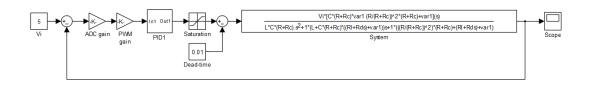

| Fig. 3.15 Simulink model of system with the robust PID controller                              | 51  |

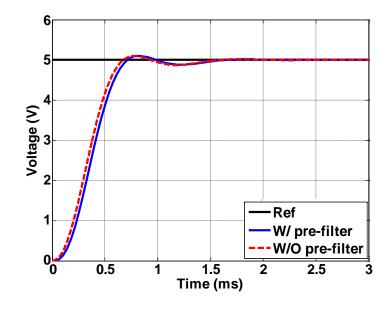

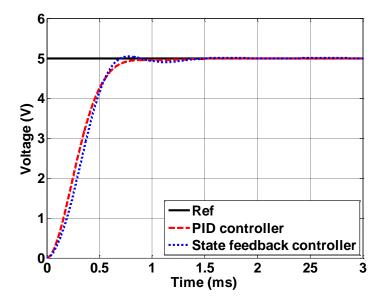

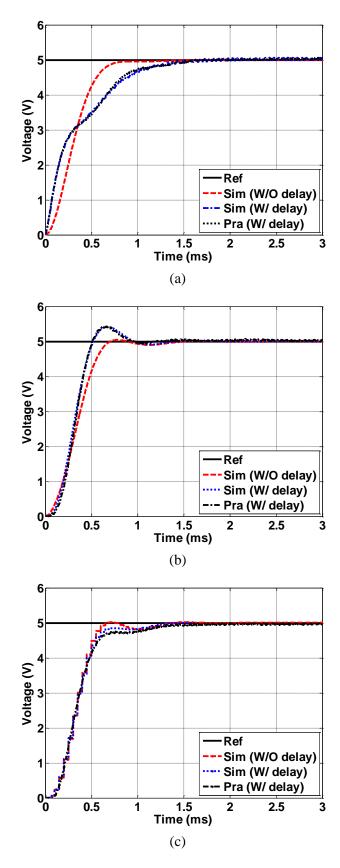

| Fig. 3.16 Simulated system step responses with PID controller                                  | 52  |

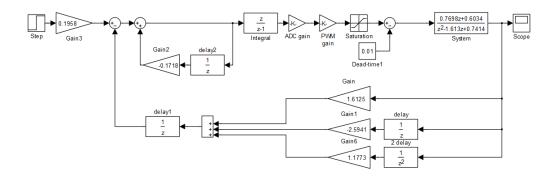

| Fig. 3.17 Simulink model of system with the state feedback control with integral control       | 53  |

| Fig. 3.18 Simulated system step response with state feedback controller.                       | 53  |

| Fig. 3.19 Simulink model of system with predictive controller                                  | 54  |

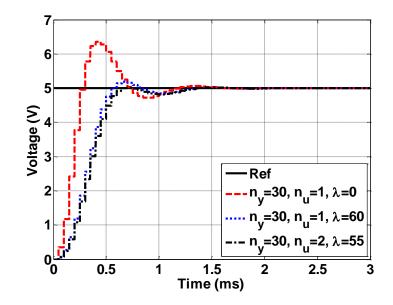

| Fig. 3.20 Simulated system responses with predictive controllers.                              | 55  |

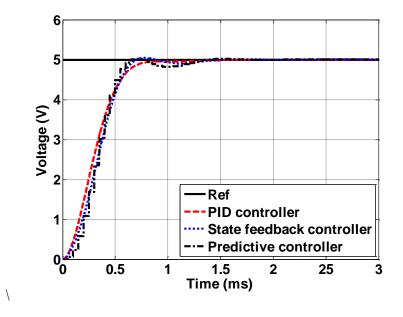

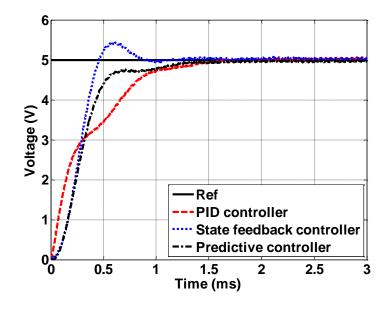

| Fig. 3.21 Simulated system step responses with the three controllers.                          | 56  |

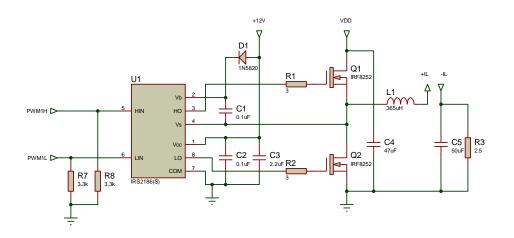

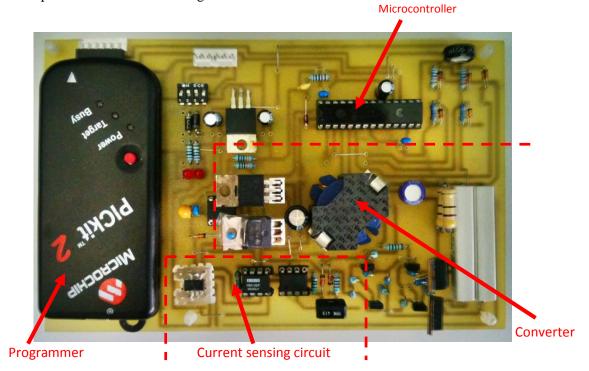

| Fig. 3.22 Schematic of the prototype converter. (a) synchronous buck converter and (b) curren  | nt  |

| sensing circuit.                                                                               |     |

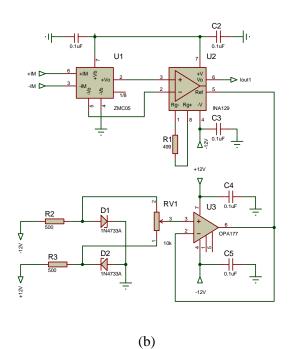

| Fig. 3.23 Schematic of the microcontroller in the prototype converter.                         | 58  |

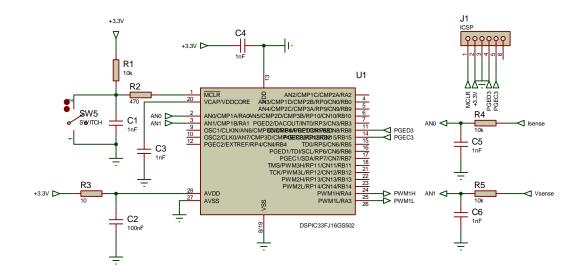

| Fig. 3.24 Image of the prototype converter                                                     |     |

| Fig. 3.25 Simulated and practical system responses. (a) PID controller (b) State feedback      |     |

| controller (c) Predictive controller                                                           | 60  |

| Fig. 3.26 Practical system responses with different controller with time delay                 |     |

| Fig. 4.1 Parallel converter with two parallel connected SBC.                                   |     |

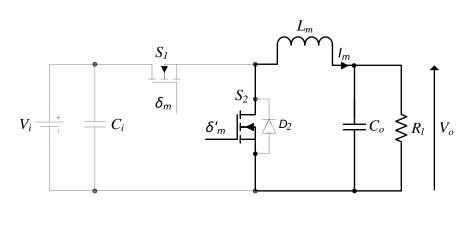

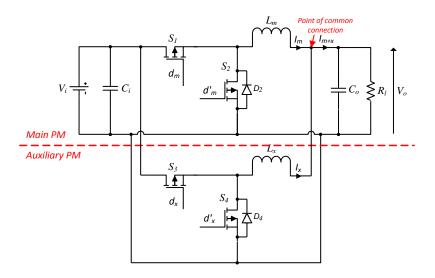

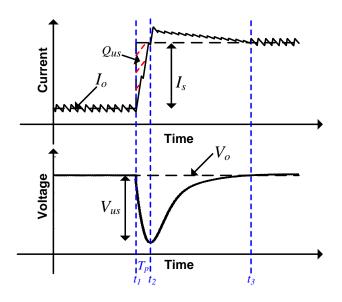

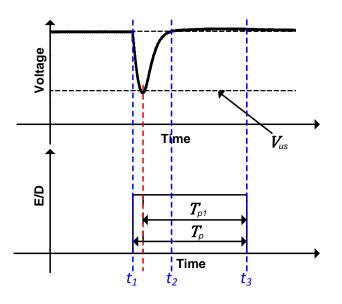

| Fig. 4.2 Current and voltage waveforms of converter subjected to load step.                    |     |

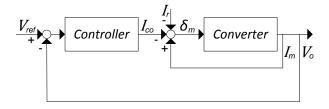

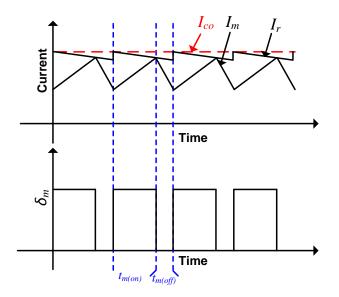

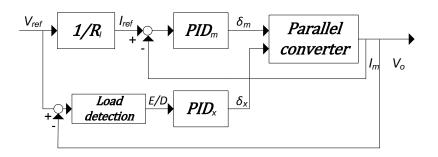

| Fig. 4.3 Block diagram of closed-loop current mode control.                                    |     |

| Fig. 4.4 Current mode control current and PWM waveforms                                                                      | 67    |

|------------------------------------------------------------------------------------------------------------------------------|-------|

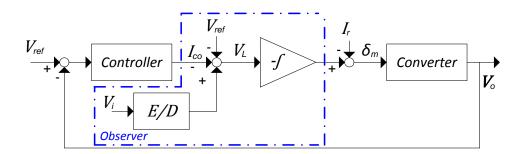

| Fig. 4.5 Block diagram of a converter with the SCM control                                                                   | 68    |

| Fig. 4.6 Auxiliary PM with nonlinear hysteretic control.                                                                     | 69    |

| Fig. 4.7 Block diagram of the converter with FRDB.                                                                           | 69    |

| Fig. 4.8 Voltage waveform and auxiliary PM timing diagram with FRDB                                                          | 70    |

| Fig. 4.9 Block diagram of the converter with SCM-PCM.                                                                        | 71    |

| Fig. 4.10 Voltage waveform with SCM-PCM.                                                                                     | 72    |

| Fig. 4.11 Block diagram of the converter with the proposed control scheme                                                    | 73    |

| Fig. 4.12 Voltage waveform and auxiliary PM timing diagram with the proposed scheme                                          | 74    |

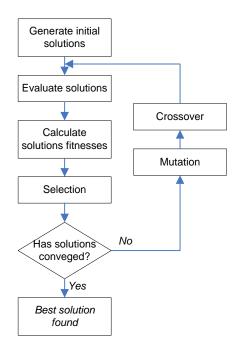

| Fig. 4.13 Flow chart of the GA tuning process                                                                                | 75    |

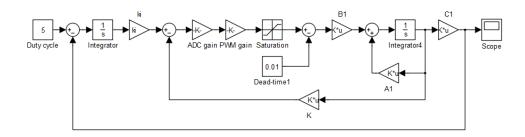

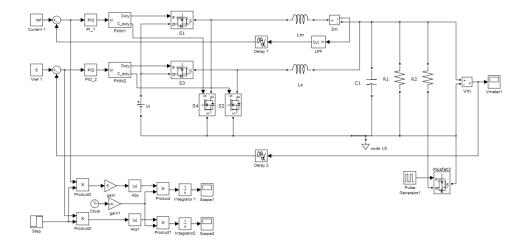

| Fig. 4.14 Simulink model of the converter with the proposed control schemes                                                  | 77    |

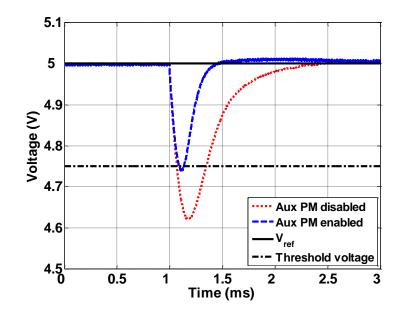

| Fig. 4.15 Simulated transient responses with auxiliary PM enabled and disabled                                               | 78    |

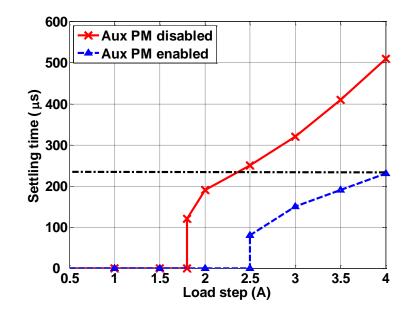

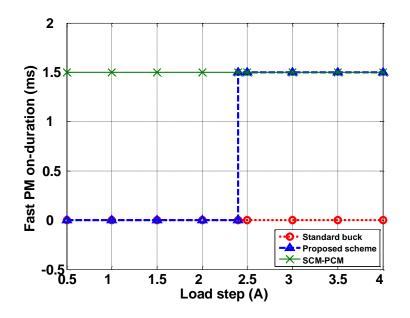

| Fig. 4.16 Converter settling times with the auxiliary PM enabled and disabled                                                | 79    |

| Fig. 4.17 On-duration of the auxiliary PM with the different control schemes.                                                | 79    |

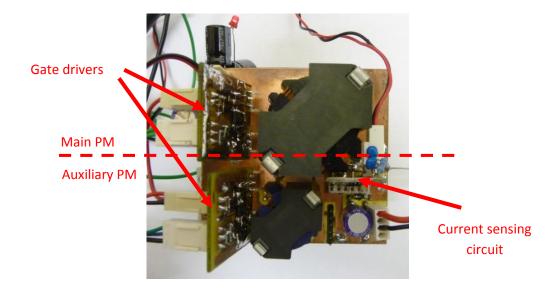

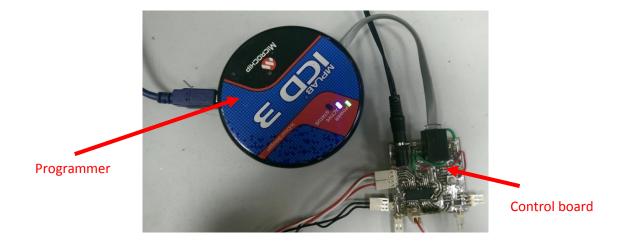

| Fig. 4.18 Image of the prototype converter                                                                                   | 80    |

| Fig. 4.19 Image of the control board and programmer.                                                                         | 80    |

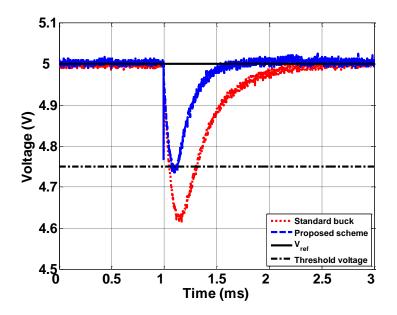

| Fig. 4.20 Practical transient responses under different schemes                                                              | 81    |

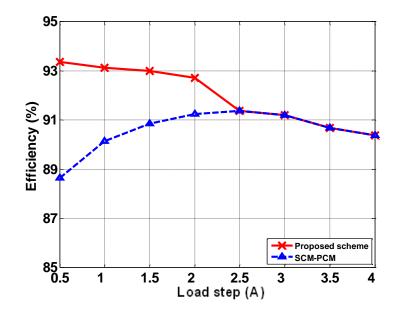

| Fig. 4.21 Practical converter efficiency under different schemes                                                             | 82    |

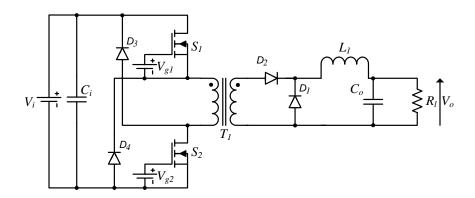

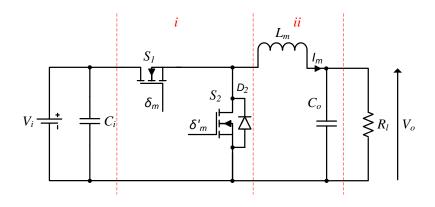

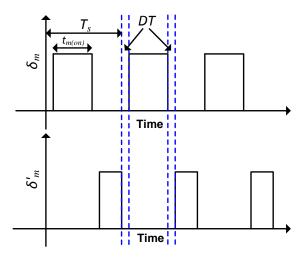

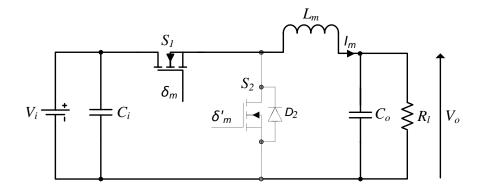

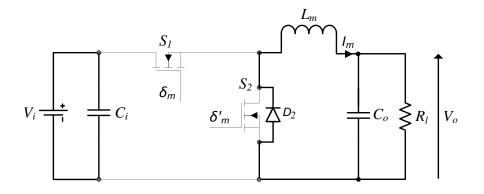

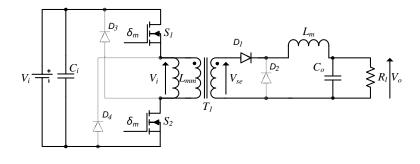

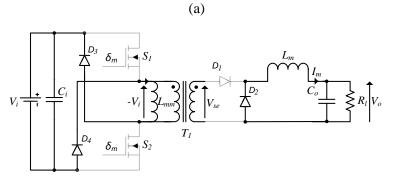

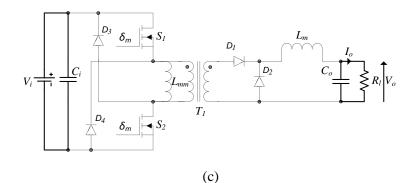

| Fig. 5.1 Circuit diagram of two-switch forward converter (2SFC)                                                              | 84    |

| Fig. 5.2 Circuit diagrams of a parallel converter with two parallel connected 2SFC. (a) on-                                  |       |

| period (b) off-period (c) cut-off period                                                                                     | 85    |

| Fig. 5.3 Inductor current waveform in DCM.                                                                                   | 86    |

| Fig. 5.4 Parallel connected two-switch forward converters                                                                    | 86    |

| Fig. 5.5 Current waveforms of the parallel converter. (a) non-identical PM (b) identical PM.                                 | 88    |

| Fig. 5.6 Current waveforms of converter with the proposed design technique                                                   | 89    |

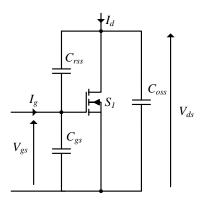

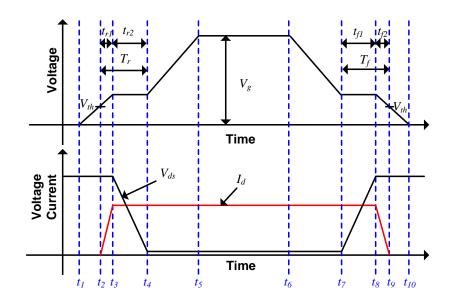

| Fig. 5.7 Circuit diagram of MOSFET with the three parasitic capacitors                                                       | 91    |

| Fig. 5.8 MOSFET switching waveforms                                                                                          | 92    |

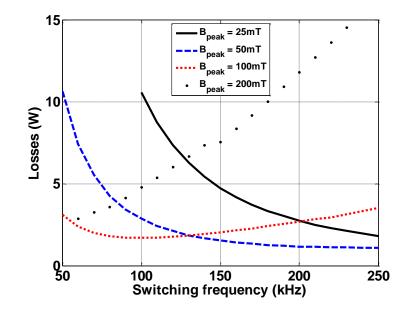

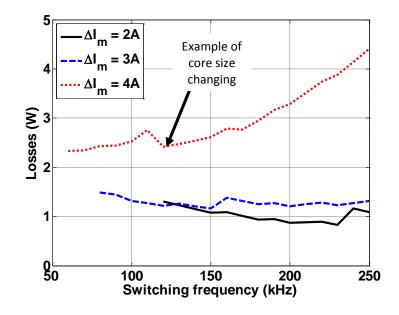

| Fig. 5.9 Main PM transformer losses under different Bpeak.                                                                   |       |

| Fig. 5.10 Main PM inductor losses under different $\Delta I$ m                                                               | 97    |

| Fig. 5.11 Main PM components losses.                                                                                         | 98    |

| Fig. 5.12 Prototype of the 2SFC (proposed HSSE design technique)                                                             | . 100 |

| Fig. 5.13 The calculated efficiency curves for the two converters.                                                           | . 101 |

| Fig. 5.14 Measured efficiency curves of the two converters.                                                                  | . 102 |

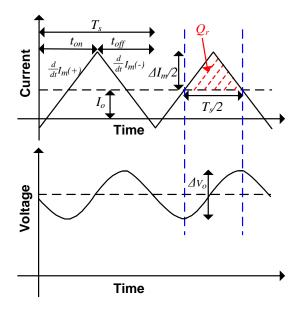

| Fig. 6.1 Active current ripple cancellation with identical PMs                                                               | . 104 |

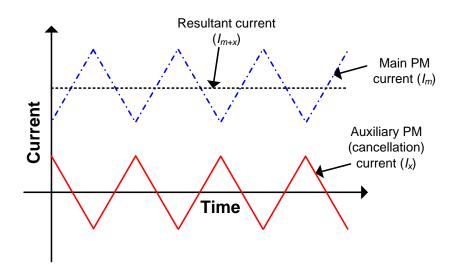

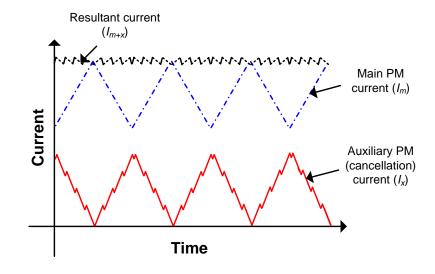

| Fig. 6.2 Main PM, auxiliary PM and resultant current waveforms                                                               | . 105 |

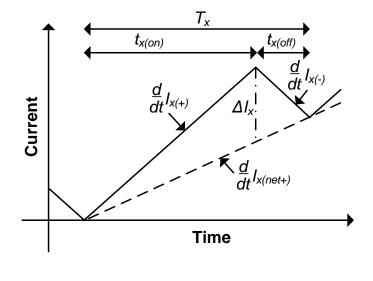

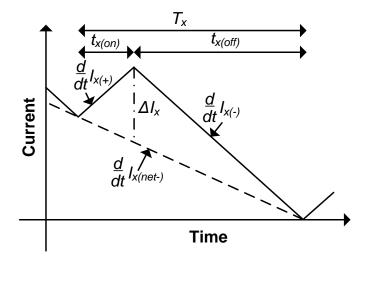

| Fig. 6.3 Current waveforms of the auxiliary PM under one auxiliary PM cycle. (a) $\delta x = 0.7$                            | 5     |

| (b) $\delta x = 0.25$                                                                                                        | . 107 |

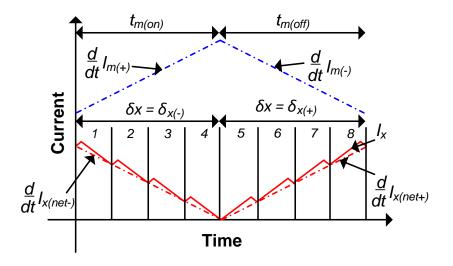

| Fig. 6.4 Current waveforms of the main and auxiliary PMs over one main PM cycle                                              | . 109 |

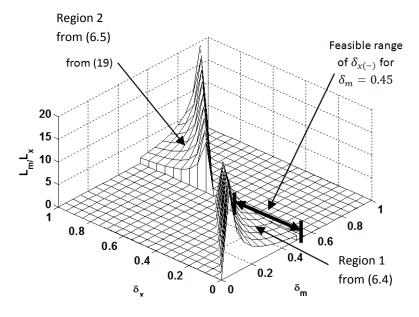

| Fig. 6.5 Ratio of the two inductors against $\delta m$ and $\delta x$                                                        | . 110 |

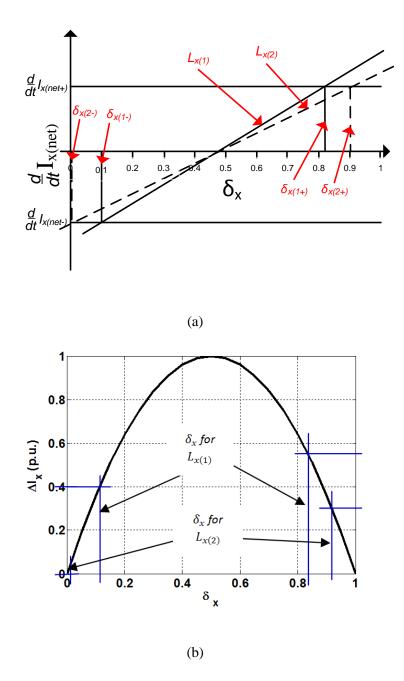

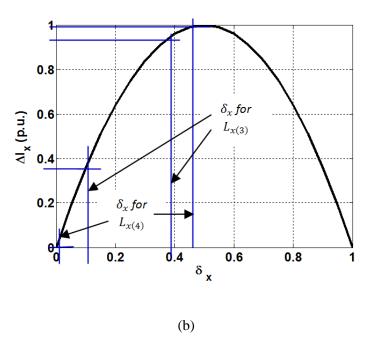

| Fig. 6.6 Effect on $\delta x$ and $\Delta I x$ with different $L x$ at $\delta xss = 0.48$ . (a) $\delta x$ (b) $\Delta I x$ | . 112 |

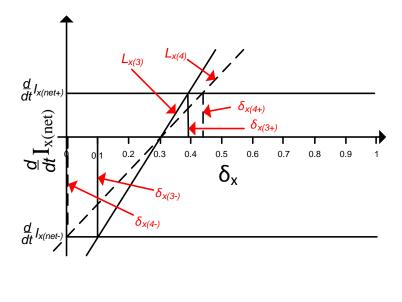

| Fig. 6.7 Effect on $\delta x$ and $\Delta I x$ with different $L x$ at $\delta xss = 0.3$ . (a) $\delta x$ (b) $\Delta I x$  | . 113 |

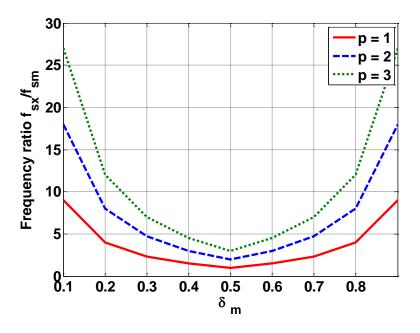

| Fig. 6.8 Frequency ratios of the two PMs under different $\delta$ m and $p$                                                  | . 114 |

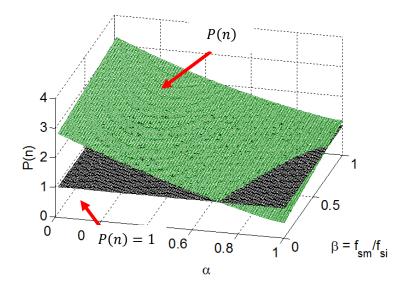

| Fig. 6.9 Loss ratio between the propose converter and interleaved converter                                                  | . 117 |

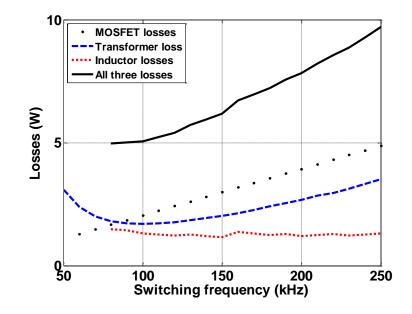

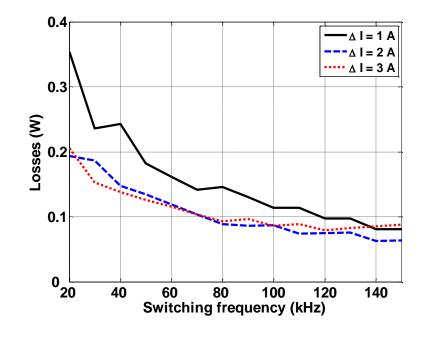

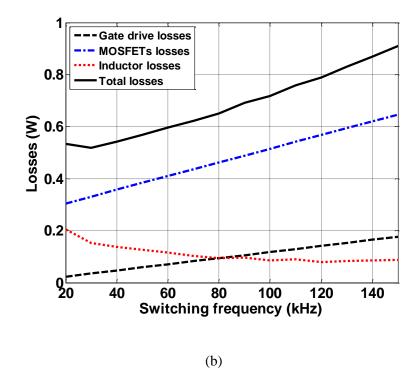

| Fig. 6.10 Main PM calculated losses. (a) Inductor losses (b) Total losses                                                    | . 119 |

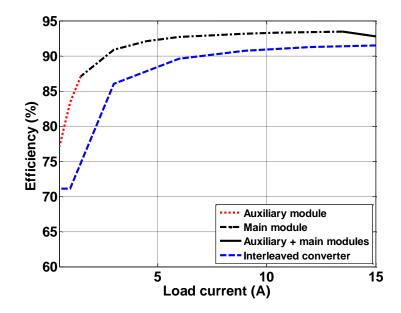

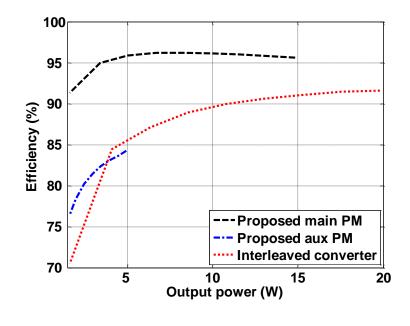

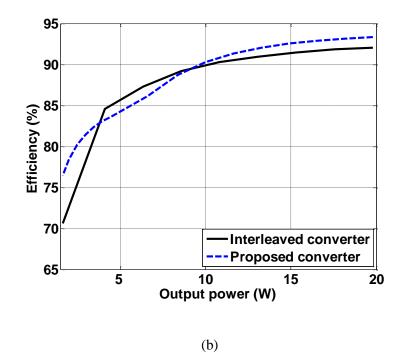

| Fig. 6.11 Calculated efficiencies. (a) Efficiencies of the different PMs (b) Efficiencies of the                       |      |

|------------------------------------------------------------------------------------------------------------------------|------|

| proposed converter and interleaved converter                                                                           | 121  |

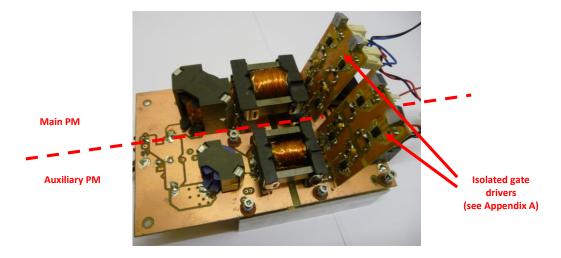

| Fig. 6.12 Prototype of the converter with the proposed scheme                                                          | 122  |

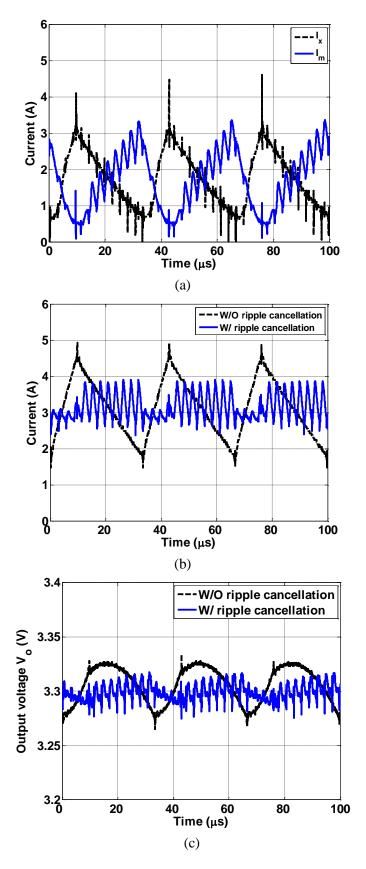

| Fig. 6.13 Prototype output current and voltage waveforms with and without ripple cancellation                          | on.  |

| (a) Main and auxiliary PMs current waveforms (b) Output current waveforms (c) Output volt                              | tage |

| waveforms                                                                                                              | 124  |

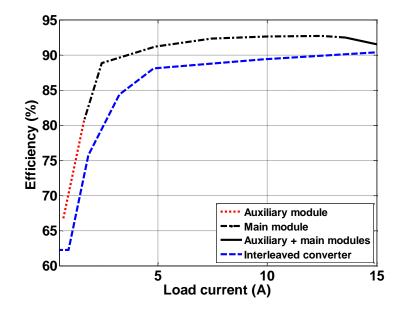

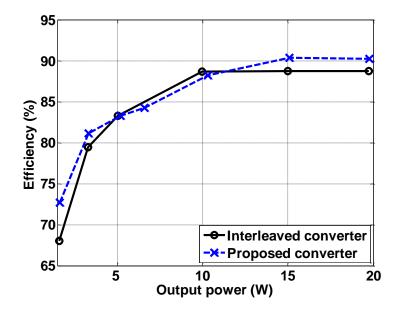

| Fig. 6.14 Measured efficiency of the proposed and interleaved converters                                               | 126  |

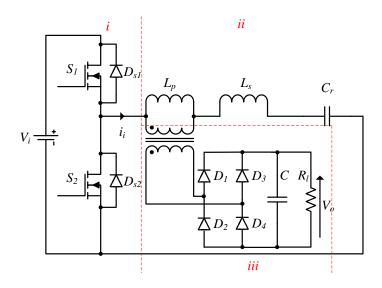

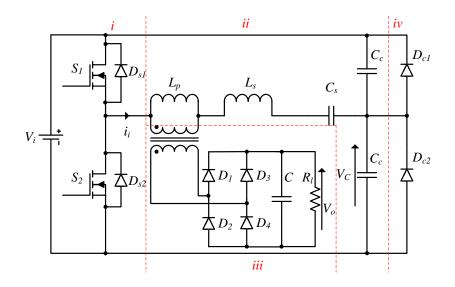

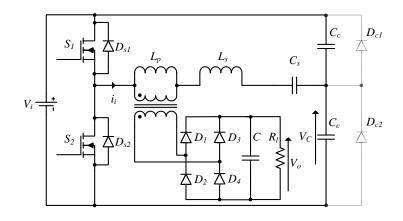

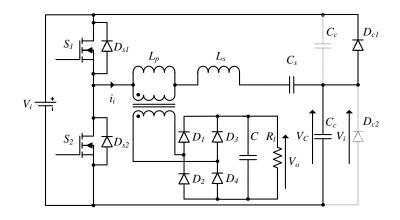

| Fig. 7.1 Half-bridge LLC resonant converter                                                                            | 128  |

| Fig. 7.2 Gain characteristics of LLC converter under different conditions                                              | 128  |

| Fig. 7.3 Half-bridge LLC resonant converter with capacitor-diode clamp                                                 | 129  |

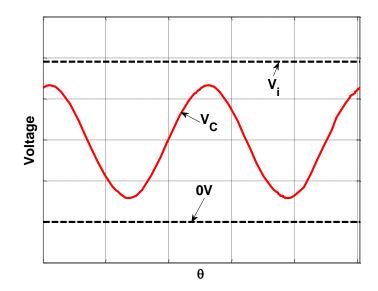

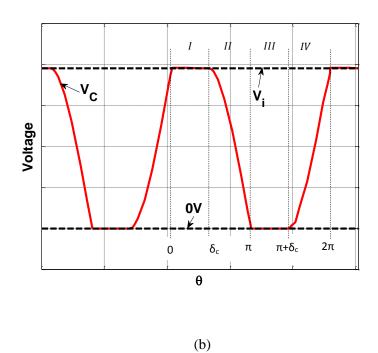

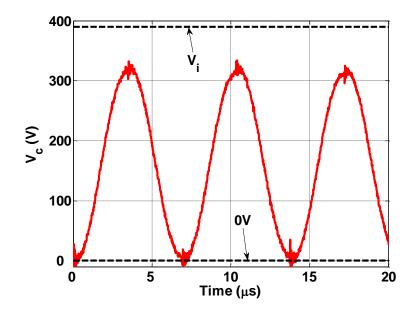

| Fig. 7.4 Resonant capacitor voltage waveforms. (a) normal operation and (b) overloading                                |      |

| operation                                                                                                              | 131  |

| Fig. 7.5 Equivalent circuit under different diode-clamp conduction states. (a) diode clamp                             |      |

| inactive (b) conduction state 1 $\delta c < \theta \le \pi$ (c) conduction state 2) $\pi + \delta c < \theta \le 2\pi$ | 132  |

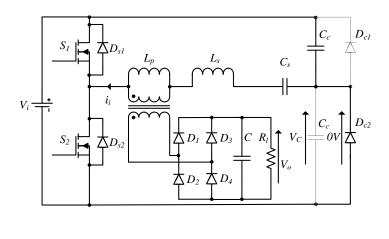

| Fig. 7.6 Flowchart describing the interactive procedure for finding the load current during                            |      |

| overloading conditions (i.e. <i>V</i> c > <i>V</i> i)                                                                  | 139  |

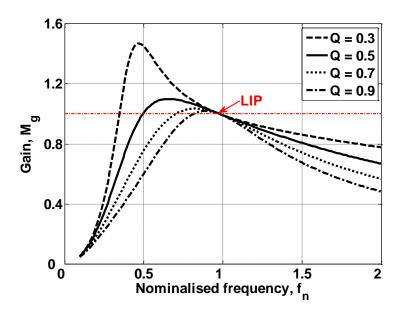

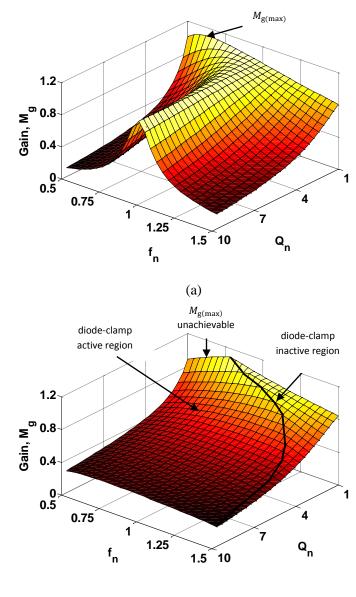

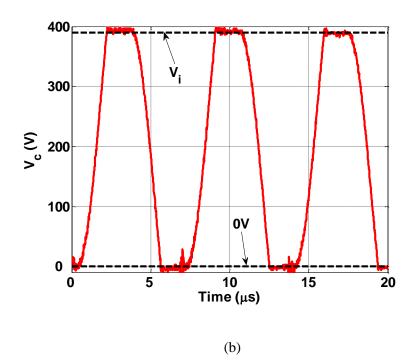

| Fig. 7.7 Converter gain characteristics. (a) $Q = 0.5$ , $3 \le As \le 9$ (b) $0.3 \le Q \le 0.9$ , $As = 5$           | 141  |

| Fig. 7.8 Converter gain characteristics with $As = 5$ and $Qrate = 0.5$ . (a) $Bs = 1$ and (b) $Bs = 0$                |      |

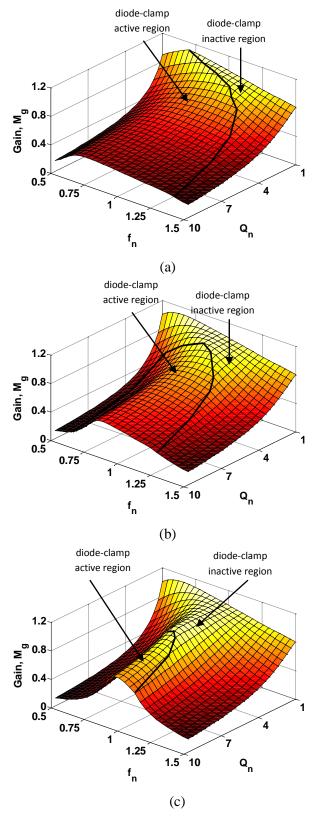

| Fig. 7.9 Converter gain characteristics with $As = 5$ and $Qrate = 0.5$ . (a) $Bs = 0.25$ (b) $Bs = 0.25$              |      |

| (c) $Bs = 0.75$                                                                                                        | 144  |

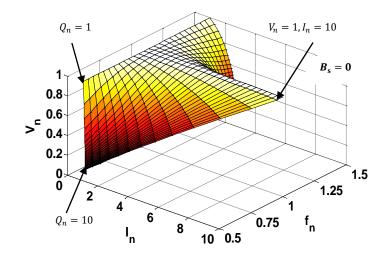

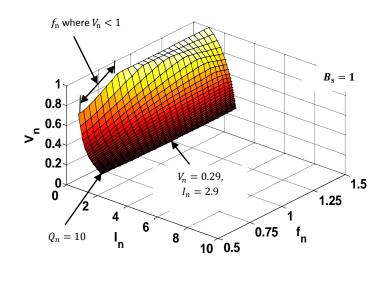

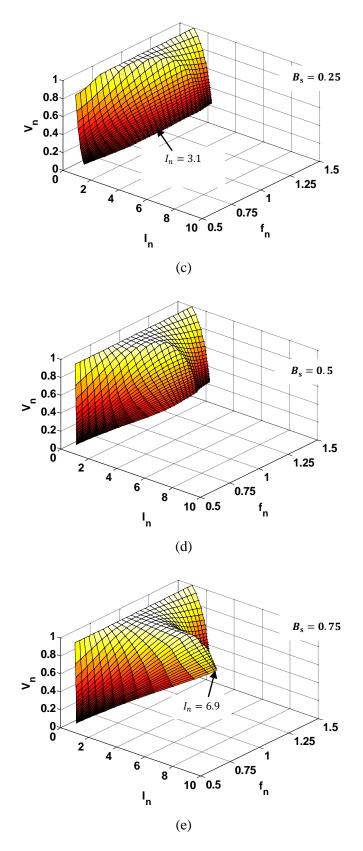

| Fig. 7.10 Converter VI characteristics. (a) $Bs = 1$ (b) $Bs = 0$ (c) $Bs = 0.25$ (d) $Bs = 0.5$ (e) $Bs = 0.5$        | s =  |

| 0.75                                                                                                                   | 147  |

| Fig. 7.11 Measured resonant capacitor voltage waveform $\nu c$ . (a) normal operation and (b)                          |      |

| overloading operation                                                                                                  | 150  |

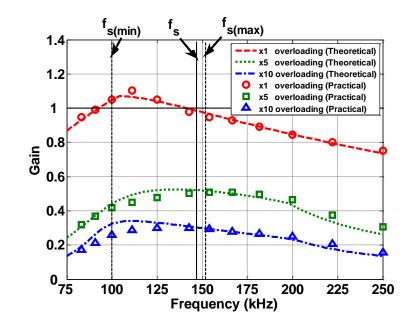

| Fig. 7.12 Comparison of the theoretical and practical results. (a) voltage gain characteristics                        | (b)  |

| VI characteristics                                                                                                     | 152  |

| Fig. 8.1 Block diagram of the converter with average current mode control                                              | 156  |

| Fig. 8.2 Circuit diagram of the proposed dual capacitor-diode clamp                                                    | 157  |

| Fig. A1 Circuit diagram of the two stages transformer coupled isolated gate driver                                     | 169  |

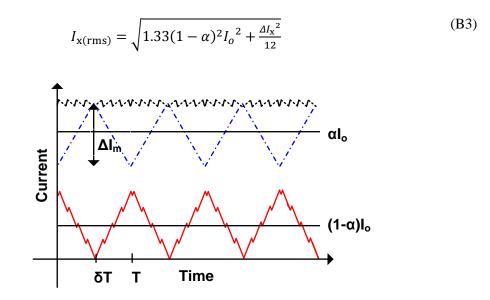

| Fig. B1 Current waveform of auxiliary PM in ripple cancellation mode                                                   | 170  |

|                                                                                                                        |      |

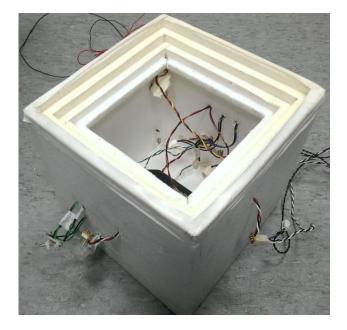

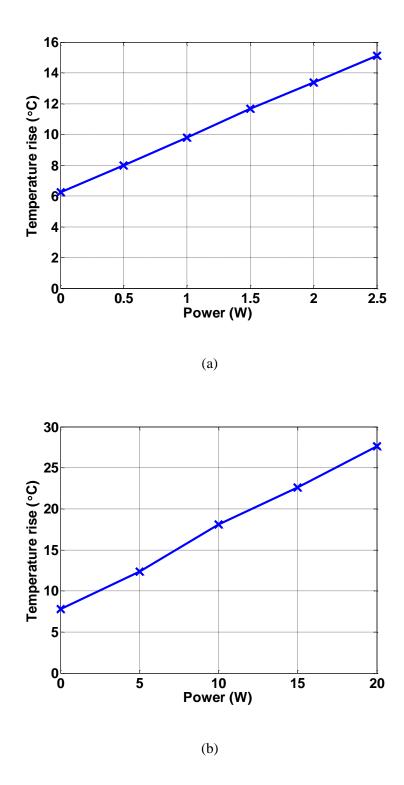

| Fig. C1 Bespoke calorimeter                                                                                            |      |

| Fig. C1 Bespoke calorimeterFig. C2 Calorimeter with fan for heat spread                                                | 172  |

## List of tables

| Table 1.1 Summary of the topologies characteristics.                                 | 11  |

|--------------------------------------------------------------------------------------|-----|

| Table 3.1 Predictive control laws with different tuning factors                      | 54  |

| Table 5.1 Interleaved PM transformer losses under different Bpeak.                   | 95  |

| Table 5.2 Auxiliary PM transformer losses under different Bpeak                      | 99  |

| Table 5.3 Summary of parameter for the interleaved and the proposed converters       | 99  |

| Table 6.1 Summaries of the duty cycles at different input voltages and load currents | 125 |

#### 1.1. Background

The proliferation of electrical systems in modern society has put an increasing emphasis on power supply (converter) design, owing to the growing requirement to interface a multitude of devices with different specifications to the standard mains utility supply. Some examples of these devices include televisions (TVs) and personal computers (PCs), which, in the year 2012, have worldwide shipments of 238 million and 341 million, respectively [1].

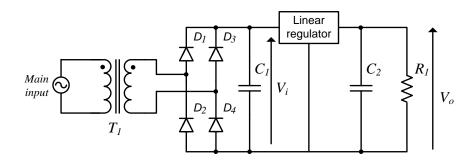

Classically, linear DC power supplies [2]-[4] such as those shown in Fig 1.1 were used for this purpose. In these cases, the AC mains input is first passed through a transformer to provide isolation and to step-down the voltage to the desired level, after which the output is rectified by diodes and smoothed by a capacitor to produce the DC voltage,  $V_i$ . The final step utilises a linear regulator to maintain the output at the desired output level,  $V_0$ .

Fig. 1.1 Schematic of a linear DC power supply.

Several issues are generally found with this type of power supply; firstly, the power density is low because the size of the transformer is large due to the low utility supply frequency (50 Hz in the UK). Secondly, the efficiency of the linear regulator is low because it regulates the output power by dissipating any excessive input power as heat. These issues become more problematic

in battery operated portable devices such as mobile phone and tablet computers, where efficient operation leads to longer battery life.

#### 1.2. Switched-mode power converters

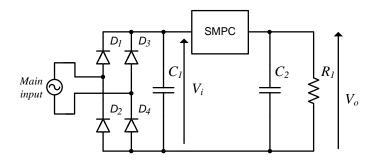

The above issues can be overcome by a switched-mode power converter (SMPC) where the AC mains input is first converted into DC by rectifiers and capacitors as shown in Fig. 1.2. The DC voltage,  $V_i$ , is then chopped by a DC chopper to produce a high frequency ac signal (e.g. at 300 kHz), after which it is smoothed by a low-pass filter to produce the desired DC output voltage,  $V_0$ . Due to the higher switching frequency (compared to the AC main frequency) of the pseudo ac signal, a smaller isolation transformer than is required in mains frequency applications can be used to achieve a higher power density. The efficiency of the SMPC is also higher when compared to the linear regulator, as only the required level of power is transferred to the output by controlling the on-period of the DC chopper. The higher efficiency also allows smaller heat-sinks to be used for higher power density and lower cost. These advantages have led a proliferation of SPMC within the consumer electronics industry. Indeed, the market value of SPMC technologies is expected to reach US\$4.3 billion by 2016 [5] and US\$9.7 billion by 2020 [6].

Fig. 1.2 Schematic of main connected power supply with SMPC.

Different types of SMPC have been developed over time. They are classified into three groups for the following discussion: these are the isolated converter, the non-isolated converter and the resonant converter.

#### 1.2.1. Non-isolated converter

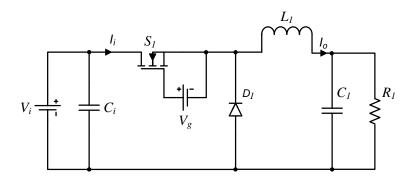

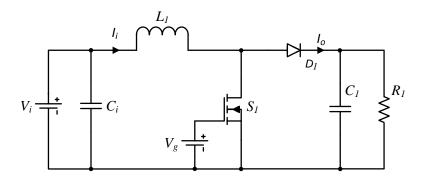

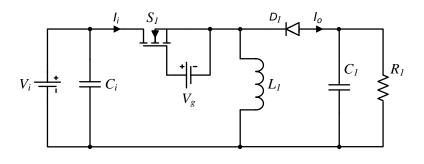

To use one of the six non-isolated topologies [7][8] in this section, the conversion ratios must be small (e.g. for a 5 V to 3.3 V step-down converter) with no isolation requirement, as these converters are either pre-regulated with an isolated converter (discussed in section 1.2.2) or are battery powered. The three most basic SMPCs—the buck converter [9], the boost converter [10] and the buck-boost converter [11]—are formed by four main components. These being a power electronic switch  $(S_1)$ , a diode  $(D_1)$ , an inductor  $(L_1)$  and a capacitor  $(C_1)$  as shown in Fig. 1.3. In the buck converter shown in Fig. 1.3 (a), power is transferred to the output from the input during the on-period of the switching device (MOSFET), and is cut-off during the off-period. The output voltage is proportional to the ratio of the on-period to the overall switching period. This ratio is always smaller than unity and so the output voltage is always lower than the input voltage in a practical system (i.e. this is a step-down converter). The inductor stores energy during the onperiod which is then released during the off-period to smooth the pulsated (discontinuous) input current,  $I_i$ , forming a DC (continuous) output current,  $I_o$ , perturbed by a small ripple (n.b.  $D_1$  is commonly replaced by a MOSFET to reduce the converter's loss. The buck converter with this modification is called the synchronous buck converter (SBC), for which more detail will be given in chapter 3). The boost converter in Fig. 1.3 (b) stores energy in the inductor during the on-period which is then released together with power directly from the input during the off-period, producing an output voltage that is always greater than the input voltage (i.e. this is a step-up converter). With the inductor in series with the input source, the input current is continuous while the output current is discontinuous. The operation of the buck-boost converter in Fig. 1.3 (c) is similar to the boost converter, where the inductor stores energy during the on-period and releases it during the off-period. However since the input is not connected to the load during the off-period, the output voltage can both be lower or higher than the input voltage (i.e. this can operate in either step-down or step-up mode) dependent on the amount of energy stored. Both the input and output current of the buck-boost topology are discontinuous and the output voltage is inverted.

(a)

(b)

(c)

Fig. 1.3 The three most basic SMPC. (a) Buck converter (b) Boost converter (c) Buck-boost converter

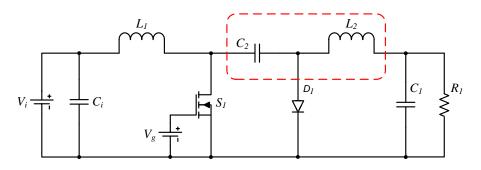

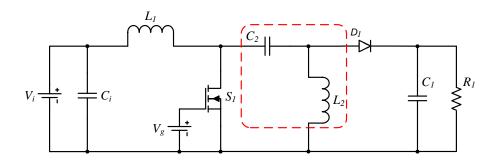

By cascading the boost converter with the buck converter and removing any superfluous components, the Cuk converter in Fig 1.4 (a) is obtained [12]. This topology contains two additional components from the above three topologies—these being the inductor,  $L_2$ , and

capacitor,  $C_2$ —which make this topology more complicated. The capacitor  $C_2$  acts as an energy transfer medium, charging up from the input and  $L_1$  during the off-period and releasing energy to  $L_2$  during the on-period. By controlling the amount of energy stored in  $C_2$ , both step-up and step-down conversion can be achieved. The output voltage of this topology is also inverted. The advantage of this topology is that the two inductors are in series with the input and output; both the input and output currents are continuous. As the output polarity in most applications is non-inverted, two further topologies with the same components as in the Cuk converter were developed. These are the SEPIC [13] and ZETA [14] converters shown in Fig. 1.4 (b) and (c) respectively. The operation of these converters is similar to the Cuk converter with the capacitor acting as the transfer medium. The output voltage can both be higher or lower than the input by virtue of controlling the charge to the capacitor. The configurations of the SEPIC and ZETA converters are identical to the boost and buck converters respectively, without the two additional components enclosed by a dashed box in the figures, hence they have the same input and output current characteristics respectively.

(a)

(b)

(c)

Fig. 1.4 Inverting and non-inverting step up/down converters. (a) Cuk converter (a) SEPIC converter (b) Zeta converter.

#### 1.2.2. Isolated power converter

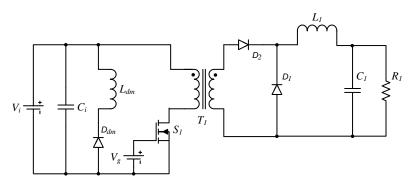

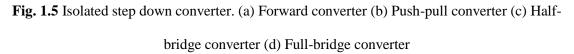

In applications where isolation is required (e.g. to prevent electrical shock) and the output voltage is always significantly lower than the input voltage, a transformer can be added to the buck converter topology to form the four isolated step-down converters [7][8] shown in Fig. 1.5: the forward, push-pull, half-bridge and full-bridge converters (n.b. step-up conversion can be achieved with a greater than unity transformer turns ratio). The forward converter shown in Fig. 1.5 (a) operates in a similar manner to the buck converter where power is only transferred during the on-period. The additional demagnetising winding,  $L_{dm}$  and the diode  $D_{dm}$  in parallel with the transformer primary, are needed to reset the transformer core by removing stored flux in each cycle. The additional diode  $D_2$  ensures the transformer secondary is cut-off from the output during the off-period of the switching device. This topology is only suitable for applications of up to 100 W [8] due to the high voltage stress seen by the switch.

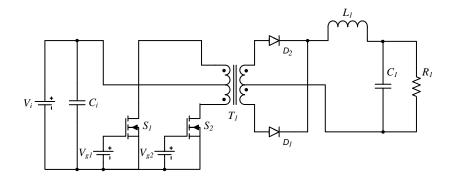

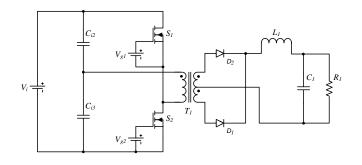

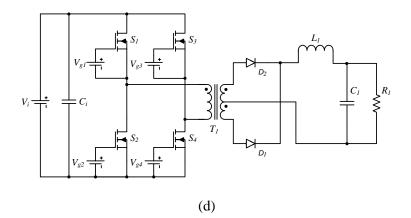

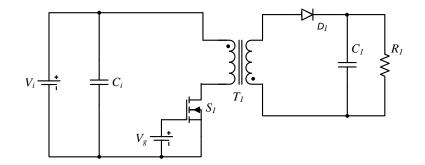

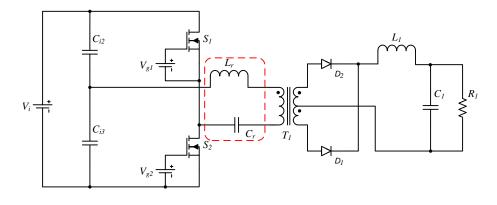

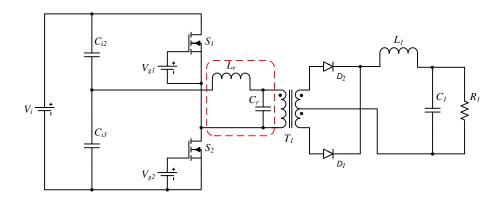

In the push-pull converters, Fig. 1.5 (b), a demagnetising winding is not required as a flux balance in the transformer primary is achieved with an 'ac' excitation signal through a centre-tapped transformer. Since this converter only uses half of the primary winding at any one time, the utilisation of the transformer is low which makes it only suitable for application with power rating of up to 500 W [8]. In the half-bridge converter in Fig. 1.5 (c), an 'ac' signal in the transformer primary is formed by taking the mid-point input voltage as a reference. With the elimination of the need for two primary windings, transformer utilisation has increased, however as only half of the input voltage is available, the required input current is twice as large for the same output power requirement, which makes it also only suitable for application of up to 500 W [8]. In the full-bridge converter shown in Fig. 1.5 (d), the two capacitors in half-bridge are replaced by two switches. By switching the diagonal legs of the bridge in pairs, the full input voltage,  $V_i$ , is made available across the transformer primary, making it suitable for use in applications of up to and above 5 kW [8].

(b)

(c)

In applications where isolation and both step-up and step-down conversions are needed, the flyback converter, shown in Fig. 1.6, can be used. This converter operates as the buck-boost converter; however, its output is non-inverted because the primary and secondary windings are wound in opposite directions. This converter is only suitable for application of up to 100 W [8] as the magnetic core has to store all the load energy during the on-period of the switching device.

Fig. 1.6 Flyback isolated step up/down converter.

#### 1.2.3. Load resonant converters

Converters mentioned up to this point are classified as hard-switching converters as the current and voltage across the switches (MOSFETs) are non-zero each time a switching event occurs, thereby inducing switching losses, stress and EMI. The load resonant converter overcomes this by ensuring the switching event occurs at either zero current (ZCS) or the zero voltage (ZVS). The resonant converter is formed by adding a resonant tank (with the resonant inductor  $L_r$  and capacitor  $C_r$  enclosed in Fig. 1.7) to either the half-bridge or full-bridge converters in Fig. 1.5 (c) and (d). The two most basic resonant converters, the series and parallel resonant converters [15], are formed by placing the resonant tank in series or in parallel with the load as shown in Fig. 1.7 (a) and (b) respectively. The regulation of this type of converter is achieved by changing the resonant tank impedance with the switching frequency.

(b)

Fig. 1.7 Half-bridge resonant converter. (a) Series resonant converter (b) Parallel resonant

converter

The characteristics and limitations of all these basic topologies are summarised in Table 1.1.

| Topology              | Power rating<br>(W) | Voltage conversion    | Output<br>voltage<br>polarity | Input current | Output current |

|-----------------------|---------------------|-----------------------|-------------------------------|---------------|----------------|

| Buck                  | > 1M                | Step-down             | · +                           | Continuous    | Discontinuous  |

| Boost                 | > 1000              | Step-up               |                               | Discontinuous | Continuous     |

| Buck-boost            | > 100               |                       | -                             | Discontinuous | Discontinuous  |

| Cuk                   |                     | Step-down/            |                               | Continuous    | Continuous     |

| SEPIC                 |                     | Step-up               |                               | Continuous    | Discontinuous  |

| ZETA                  |                     |                       |                               |               |                |

| Forward               | < 100               | -<br>Stan dawn        |                               |               |                |

| Push-pull             | < 500               |                       |                               |               |                |

| Half-bridge           | < 500               | Step-down             |                               |               |                |

| Full-bridge           | > 5000              |                       | +                             |               |                |

| Flyback               | < 100               | Step-down/<br>Step-up | - +                           | Discontinuous | Continuous     |

| Series-<br>resonant   |                     | Step-down             |                               |               |                |

| Parallel-<br>resonant |                     | Step-down/<br>Step-up |                               |               |                |

Table 1.1 Summary of the topologies characteristics.

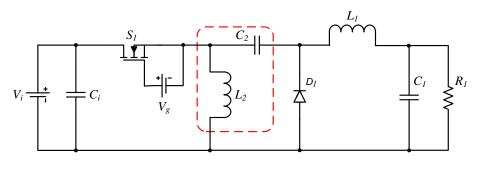

The limitations as summarised in Table 1.1 can, however, be overcome with a small modification to the topologies. For example, a higher power rating version of the forward converter (for up to 1 kW), called the 2-switches forward converter [16], is formed by replacing the demagnetising circuit by two diodes as shown in Fig. 1.8.

Fig. 1.8 Two-switch forward converter.

#### 1.2.4. Design considerations and challenges

The design of a converter starts by selecting a suitable topology based on the application's specifications, which can be achieved with the help of Table 1.1. Other factors affecting the topology selection include engineer expertise, available literature, design guidelines, compatibility to the existing product portfolio, converter complexity and reliability, to name but a few.

Having selected the topology, the engineer can then focus on the design and selection of the converter's components to meet the steady-state and the transient response requirements of the application. Attention must also be paid tosize, weight, cost and efficiency. For certain applications, the implications of these requirements are contradictory and, therefore, a suitable compromise must be found. For example, a computer voltage regulator (VR) must provide excellent transient response, whilst achieving high efficiency. The fast transient response in buck converters can be achieved by selecting its low-pass filter with a higher bandwidth (corner frequency), this however requires the converter to operate at a higher switching frequency, leading to a reduction in efficiency due to the increase in switching losses in the semiconductor switching device and magnetic components. Even through some of the losses in the semiconductors can be mitigated to a certain extent by employing resonance (as in the resonant converters or the resonant switch converter [17]), these converters require a different set of design and control techniques. Solutions utilising the same set of design and control techniques as the original converter are a more attractive alternative. Some of these solutions include connecting multiple converters in series [18], in parallel [19], or both in series and parallel [20].

With energy efficiency becoming more important in recent years due to rising energy prices and tightening regulations from environmental protection agencies, this thesis primary focuses on identifying control schemes and design techniques to improve the efficiency of the converter. These control schemes and design techniques utilise the same set of design and control techniques as the original converter, similar to the approach in [18]-[20]. Step-down converters (i.e. buck and forward converters) are selected for the investigation as the majority of applications have a step-

down conversion ratio. These new control schemes and design techniques also work with step-up converters. Resonant converters, like the LLC resonant converter, are becoming increasingly popular, due to their low switching losses. One of the issues that prevents this converter from being widely adapted is the low impedance around the operating frequency, allowing excessive current to flow under overload or short circuit conditions. This thesis also develops an equivalent circuit model to predict the overloading issue experienced in the LLC resonant converter which allows the desired clamping capacitor to be selected.

#### 1.3. Thesis outline

The work in this thesis is divided into eight chapters:

Chapter 1 introduces the characteristics and applications of the most commonly used converters. The research focus, thesis outline and contribution are also presented.

Chapter 2 reviews the different modelling techniques and the design and control techniques that have been developed to improve the efficiency of step-down converters. New design and control techniques that could lead to higher converter efficiency and power density are identified. Also included in the review is the overloading issue of LLC resonant converters.

Chapter 3 explores the use of closed-loop controllers to improve the transient performance of synchronous buck converters (SBCs). The full derivation of the converter's equivalent circuit models (in both the state-space and the transfer function forms) and the complete design procedures for the three types of controllers (the PID, the state feedback and the predictive controllers) are presented. The step responses of the converter with the three different types of controllers are compared to identify the best controllers.

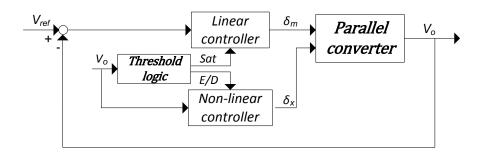

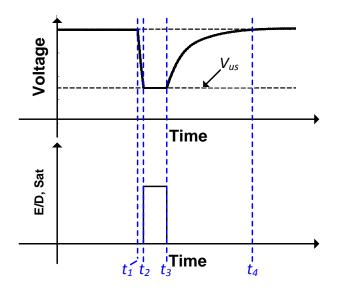

Chapter 4 investigates the characteristics of the two control schemes developed to improve the transient performance of the parallel converter, the fast response double buck (FRDB) scheme and sensorless and peak current mode control (SCM-PCM) scheme. By combining the advantages of the two schemes, a new control scheme—the fast recovery with high transient efficiency (FRHE)

scheme—is proposed to improve the converter efficiency during transient operation without unduly increasing the transient response time.

Chapter 5 studies the effects of the different system requirements on the parallel converter's efficiency to assist the development of a new design technique, the high steady-state efficiency (HSSE) technique. In HSSE, the design specifications and requirements that prevent the main power module (PM) from having high steady-state efficiency are conveniently allocated to an auxiliary PM, to allow the main PM be optimised for conduction loss for high steady-state efficiency.

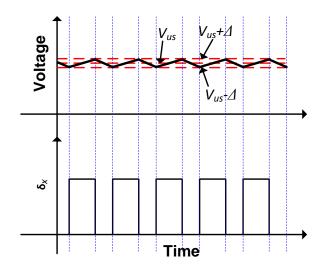

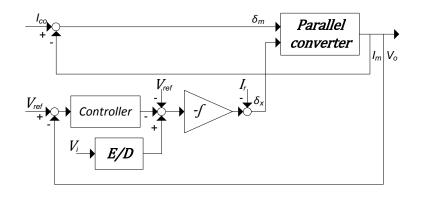

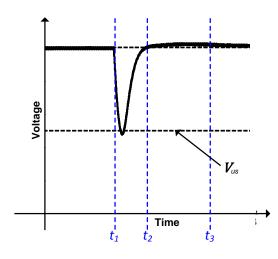

Chapter 6 demonstrates a new active current ripple cancellation (ACRC) scheme, which shapes the auxiliary PM current to reduce the main PM current ripple and hence reduce the current ripple seen by the output capacitor, allowing a lower value output capacitor to be selected. The selection of the auxiliary PM components and duty cycle under different operating conditions are also given.

Chapter 7 presents a design methodology for LLC resonant converters with a capacitor-diode clamp. A new fundamental harmonic approximation (FHA) based equivalent circuit model is obtained through the application of describing function techniques by examining the fundamental behaviour of the capacitor-diode clamp. The current limiting performance of the converter under overload condition is studied and design guidelines are given.

Chapter 8 concludes the thesis and details any further work.

#### **1.4. Contribution**

This thesis proposes novel control and design techniques to improve both the steady-state and transient efficiencies of the parallel converter and addresses the overload issue of the LLC resonant converter. In particular, the work presented herein has been disseminated in internationally recognised journals and conferences. The main contribution are summarised below:

- A novel fast recovery with high transient efficiency (FRHE) scheme [P1] is proposed to improve the transient efficiency of the converter with two parallel connected SBCs. By activating the auxiliary PM only when the threshold voltage or settling time are to be exceeded, the transient efficiency of the prototype converter is improved by as much as 4.7% under continuous load step.

- A novel high steady-state efficiency (HSSE) design technique [P2] is proposed to improve the steady-state efficiency of the converter with two parallel connected 2SFCs. By allocating both the transient response requirement and the minimum load condition to the auxiliary PM, the main PM can then be optimised for steady-state operation. The steady-state efficiency of the prototype converter is improved by up to 12%.

- A novel active current ripple cancellation (ACRC) scheme [P3] is proposed to reduce the current ripple as seen by the output capacitor. Through shaping of the current waveform of the auxiliary PM, the current ripple of the prototype converter is reduced by 67% and the efficiency is also improved under most load conditions.

- A new equivalent circuit model for a LLC resonant converter with the capacitor-diode clamp [P4] is developed to predict the overload current. By extracting the fundamental behaviour of the capacitor-diode clamp using a describing function technique, the converter current limiting characteristic under different operating frequency and overload conditions are predicted, allowing the optimum clamping capacitors to be selected.

# 2. Control schemes and switched-mode power converter topologies for high efficiency

#### 2.1. Introduction

The previous chapter introduced different switched-mode power converter topologies usually employed within industry, and highlighted the focus of the thesis. This chapter provides a thorough review of different types of modelling techniques, control schemes and design and control techniques developed and employed by power supply designer for SMPCs. It also proposes new control schemes and design techniques that allow higher efficiency, higher power density and overload protection to be achieved. From the review of existing literatures, five areas are identified as suitable for further research:

- 1) Effect on the converter's transient responses with different feedback controllers

- 2) Control schemes that provide lower losses under transient conditions.

- 3) Design techniques that improve the efficiency under steady-state conditions.

- 4) Reduction in current ripple for higher power density

- 5) Overload characteristics of an LLC converter with capacitor-diode clamp.

This chapter commences by examining the mathematical modelling techniques employed to predict both the steady-state and the transient behaviour of converters before applying some of the techniques to the analysis and design of converters and their feedback controllers.

#### 2.2. Mathematical modelling

In order to study the converter's behaviour, system (converter) mathematical models are essential. As the buck converter is a nonlinear system due to the switching action in each period, equivalent LTI models must be obtained in order to design suitable feedback controllers using linear control systems theory. Dependent on whether the system is to be controlled in either voltage mode (VMC)

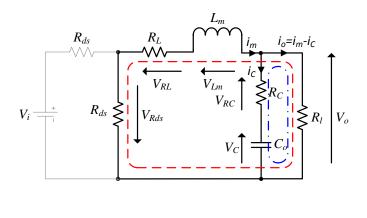

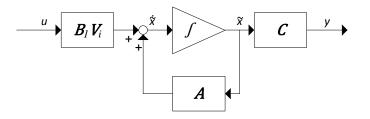

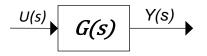

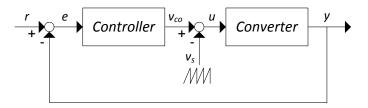

#### 2. Control schemes and switched-mode power converter topologies for high efficiency