© 2014 by Osman Sarood. All rights reserved.

## OPTIMIZING PERFORMANCE UNDER THERMAL AND POWER CONSTRAINTS FOR HPC DATA CENTERS

BY

OSMAN SAROOD

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 2014

Urbana, Illinois

Doctoral Committee:

Professor Laxmikant V. Kalé, Chair Professor Tarek Abdelzaher Professor Maria Garzaran Doctor Bronis de Supinski, Lawrence Livermore National Laboratory

### Abstract

Energy, power and resilience are the major challenges that the HPC community faces in moving to larger supercomputers. Data centers worldwide consumed energy equivalent to 235 billion kWh in 2010. A significant portion of that energy and power consumption is devoted to cooling. This thesis proposes a scheme based on a combination of limiting processor temperatures using Dynamic Voltage and Frequency Scaling (DVFS) and frequency-aware load balancing that reduces cooling energy consumption and prevents hot spot formation. Recent reports have expressed concern that reliability at the exascale level could degrade to the point where failures become a norm rather than an exception. HPC researchers are focusing on improving existing fault tolerance protocols to address these concerns. Research on improving hardware reliability has also been making progress independently. A second component of this thesis tries to bridge this gap and explore the potential of combining both software and hardware aspects towards improving reliability of HPC machines. Finally, the 10MW consumption of present day HPC systems is certainly becoming a bottleneck. Although energy bills will significantly increase with machine size, power consumption is a hard constraint that must be addressed. Intel's Running Average Power Limit (RAPL) toolkit is a recent feature that enables power capping of CPU and memory subsystems on modern hardware. The ability to constrain the maximum power consumption of the subsystems below the vendor-assigned Thermal Design Point (TDP) value allows us to add more nodes in an overprovisioned system while ensuring that the total power consumption of the data center does not exceed its power budget. The final component of this thesis proposes an interpolation scheme that uses an application profile to optimize the number of nodes and distribution of power between CPU and memory subsystems that minimizes execution time under a strict power budget. We also present a resource management scheme including a scheduler that uses CPU power capping, hardware overprovisioning, and job malleability to improve the throughput of a data center under a strict power budget.

To my parents and wife for their continuous support.

### Acknowledgments

Both of you can not do PhD and raise kids. This is what most people told my wife and I when we started doing PhD and had kids. My super-wife is the sole reason behind my PhD. How many wives have completed a PhD, took care of a husband and raised 2 kids all at the same time? I remember her taking care of our new born and our 2 year old daughter immediately after her C-section while I had to go for work. I would never be able to repay her for that!

It was my parents determination that brought me to the US to pursue higher studies. I still remember their kind words that made me believe in myself. My father sacrificed his career in order to spare time for me, while my mother would spend her nights praying to Allah (God) for my success. I still remember her standing with me on my PhD defense and saying: 6 saal sey iss din ka intezar kiya (I have waited 6 years for this day). My grand father, Prof. Anjum Roomani, also played a very vital role in my studies and upbringing. May he rest in peace. I would also thank my brother, Omer Sarood, for supporting me to go for graduate studies. I also owe a lot to my sister, Amna Sarood, who has been praying for both my wife and I throughout our PhD. I like to thank my friends Musa, Rana, and Ghufran for taking care of my parents while I was in the US.

I thank Prof. Laxmikant Kalé for being a generous and helping advisor. He taught me so many things from paper writing to exploring groundbreaking ideas. His emphasis on experimental work is something that greatly contributed to the quality of my work. Besides my advisor, I thank Prof. Bronis de Supinski and Prof. Maria Garzaran for serving on my doctoral committee and providing valuable perspectives on improving the dissertation.

I would like to thank my internship supervisor Barry Rountree, who played a key role towards the end of my thesis. Barry introduced me to the wonderful world of mathematical modeling and linear programming which facilitated the latter part of my research.

I would sincerely like to thank Prof. Tarek Abdelzaher for allowing us to use the Power

and Energy clusters. Without getting access to these clusters this thesis would not have been possible.

I am privileged to have worked with some of the most competent people in the world, i.e. my lab mates. I spent hours talking to most of them and learnt a lot from them. Esteban is a very good team player and I loved discussing my work with him. Some of our discussions led to very good projects. Akhil is a very smart person and would point out problems that most people would fail to identify. I owe a lot of credit to Phil for helping me out with my experimental work. Jonathan and Nikhil are both very competent and wonderful people to interact with. I enjoyed co-authoring a lot of papers with Abhishek due to his reliability. Lukasz, Dave, Abhinav, Eric, Isaac, and Pritish helped me during my initial days at the PPL. Harshitha and Ram were gentle colleagues with whom I had a lot of discussions about raising kids. I will miss discussing my power related work with Ehsan. The new generation of PPLers, Mike, Ronak, Bilge remind me of my early days. I would like to thank JoAnne for writing all those numerous HR related letters for me.

During my stay at Urbana-Champaign I was blessed to have the company of some amazing people. This town won't have been so much fun for me without Azeem *bhai* and Qazi *bhai*. I would miss all those night-long discussions we had. Syed Usman Ali is the most lively person I have ever met. I would miss playing cricket in the South Quad, especially alongside Ahmad Qadir.

Last but not least, I would like to thank everyone I met at Urbana during my stay. I may not remember their names but they made a difference in one of the most exciting adventures of my life.

### Grants

This work was partially supported by the following sources:

- HPC Colony II. This project is funded by the US Department of Energy under grant DOE DE-SC0001845. The Principal Investigator of this project is Terry Jones.

- Simplifying Parallel Programming for CSE Applications using a Multi-Paradigm Approach. This project is funded by the National Science Foundation (NSF) under grant NSF ITR-HECURA-0833188. It is a collaborative work between Prof. Laxmikant Kalé, Prof. David Padua and Prof. Vikram Adve.

- **Power/Energy Cluster**. This project is funded by the National Science Foundation (NSF) under grant NSF CNS 09- 58314. The Principal Investigator of this project is Prof. Tarek Abdelzaher.

### Table of Contents

| List of I | igures                                            |

|-----------|---------------------------------------------------|

| List of 7 | Tables                                            |

| List of A | Algorithms                                        |

| СНАРТ     |                                                   |

| 1.1       | Thesis Organization                               |

| CHAPT     | ER 2 Thermal Restraint Using Migratable Objects   |

| 2.1       | Related Work         6                            |

| 2.2       | Limiting Temperatures                             |

| 2.3       | Charm++ and Load Balancing 10                     |

| 2.4       | 'Cool' Load Balancer                              |

| 2.5       | Experimental Setup                                |

| 2.6       | Constraining Core Temperatures and Timing Penalty |

| 2.7       | Energy Savings                                    |

| 2.8       | Tradeoff in Execution Time and Energy Consumption |

| CHAPT     | ER 3 Thermal Restraint and Reliability            |

| 3.1       | Related Work                                      |

| 3.2       | Implications of Temperature Control               |

| 3.3       | Approach                                          |

| 3.4       | Experiments                                       |

| 3.5       | Projections                                       |

| СНАРТ     | ER 4 Optimizing Performance Under a Power Budget  |

| 4.1       | Related Work                                      |

| 4.2       | Approach                                          |

| 4.3       | Setup                                             |

| 4.4       | Case Study: Lulesh                                |

| 4.5       | Results                                           |

| CHAPTER 5 Job Scheduling Under a Power Budget | 79  |

|-----------------------------------------------|-----|

| 5.1 Related work                              | 80  |

| 5.2 Data Center and Job Capabilities          | 81  |

| 5.3 The Resource Manager                      | 82  |

| 5.4 Strong Scaling Power Aware Model          | 87  |

| 5.5 Experimental Results                      | 90  |

| 5.6 Large Scale Projections                   | 97  |

| CHAPTER 6 Concluding Remarks                  | 107 |

| 6.1 Thermal Restraint                         | 107 |

| 6.2 Power Constraint                          | 109 |

| APPENDIX A Machine Descriptions               | 112 |

| APPENDIX B Benchmark Descriptions             | 114 |

| REFERENCES                                    | 117 |

# List of Figures

| 1.1        | Mean Time Between Failures (MTBF) for different numbers of sockets<br>using different MTBF per socket.                                         |   |   | 2                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-----------------------------------------|

| 1.2        | Power consumption and theoretical peak performance for supercomputers<br>from the Top500 (blue circles). The proposed Exascale machine under a |   |   | _                                       |

|            | power budget of 20MW (red square)                                                                                                              |   |   | 3                                       |

| 2.1        | Average core temperatures and maximum difference of any core from the average for <i>Wave2D</i>                                                |   |   | 9                                       |

| 2.2        | Execution time and energy consumption for <i>Wave2D</i> running at different CRAC set-points using DVFS                                        |   |   | 10                                      |

| 2.3        | Our DVFS and load balancing scheme successfully keeps all processors within the target temperature range of 47°–49° C, with a CRAC set-point   |   |   |                                         |

| 2.4        | of 24.4° C                                                                                                                                     | • | • | 18                                      |

| 2.5        | Balancing                                                                                                                                      | • | • | 19                                      |

| 2.6        | for <i>Wave2D</i>                                                                                                                              | • | • | 20                                      |

| 2.7        | $24.4^{\circ}$ C                                                                                                                               | • | • | 21                                      |

| 2.8        | $24.4^{\circ}$ C                                                                                                                               |   |   | $\begin{array}{c} 21 \\ 22 \end{array}$ |

| 2.8<br>2.9 | Utilization of processors for Jacobi2D using <i>TempLDB</i>                                                                                    |   |   | $\frac{22}{22}$                         |

| 2.10       | Frequency sensitivity of the various applications                                                                                              |   |   | 23                                      |

| 2.11       |                                                                                                                                                |   |   |                                         |

|            | set-point and various <i>TempLDB</i> runs                                                                                                      |   |   | 25                                      |

| 2.12       | Savings in cooling energy consumption with and without Temperature                                                                             |   |   |                                         |

|            | Aware Load Balancing (higher is better)                                                                                                        |   |   | 27                                      |

| 2.13       | Change in machine energy consumption with and without Temperature                                                                              |   |   |                                         |

| 0.1.4      | Aware Load Balancing (values less than 1 represent savings)                                                                                    | • | • | 28                                      |

| 2.14       | Normalized machine energy consumption for different frequencies using                                                                          |   |   | 90                                      |

|            | 128 cores                                                                                                                                      | · | • | 30                                      |

|                                   | The time $Wave2D$ spent in different frequency levels $\ldots$ $\ldots$ $\ldots$ Total power draw for the cluster using $TempLDB$ at CRAC set-point of 24.4 °C                                                                |   | $\frac{30}{31}$  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|

| 2.17                              | of 24.4 °C                                                                                                                                                                                                                    | • |                  |

| 2.18                              | pared to naive DVFS                                                                                                                                                                                                           | • | 31<br>32         |

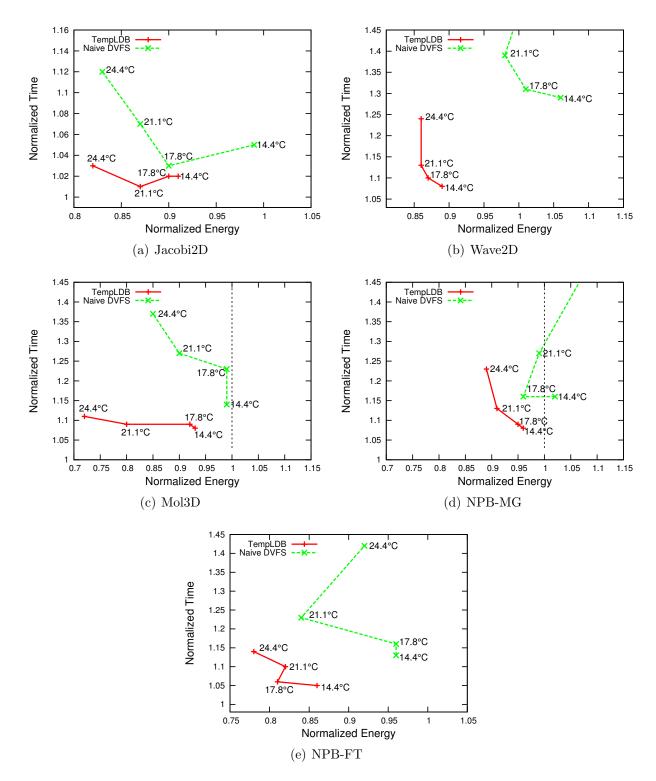

| 2.19                              | Normalized time against normalized total energy for a representative sub-<br>set of applications                                                                                                                              |   | 33               |

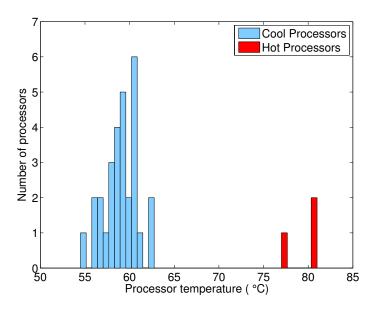

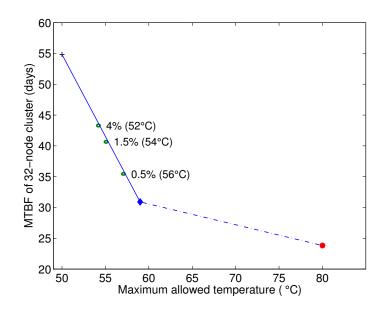

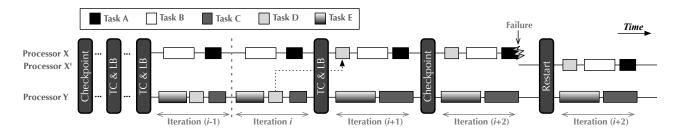

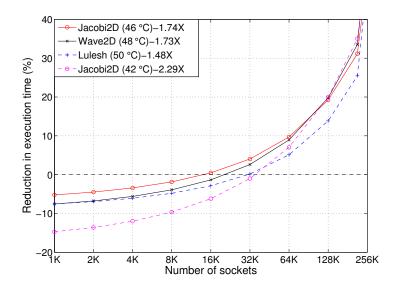

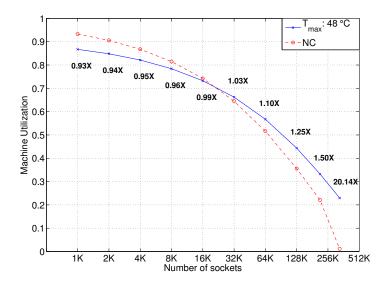

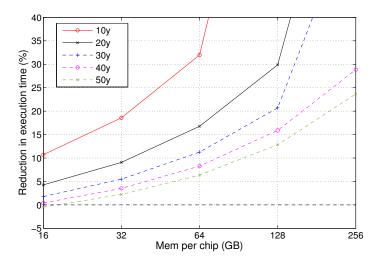

| 3.1<br>3.2<br>3.3                 | Histogram of max temperature for each node of the cluster using <i>Wave2D</i><br>Effect of cooling down processors on MTBF of the system                                                                                      |   | $38 \\ 39 \\ 47$ |

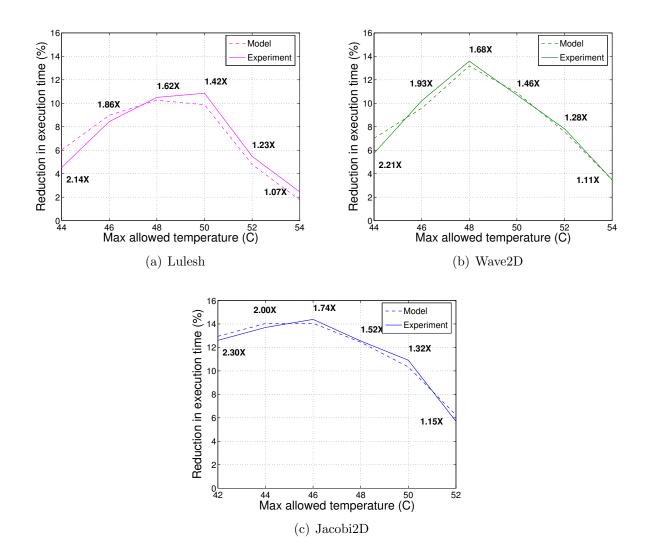

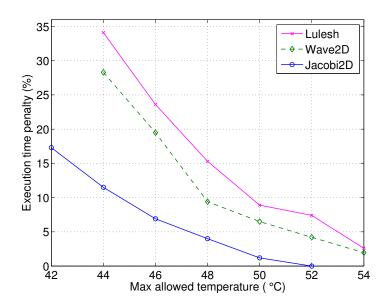

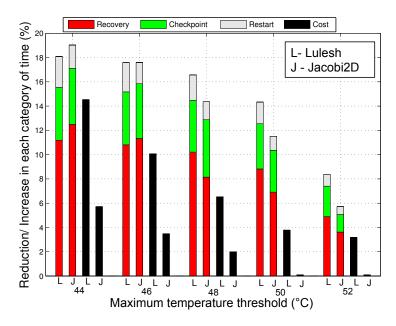

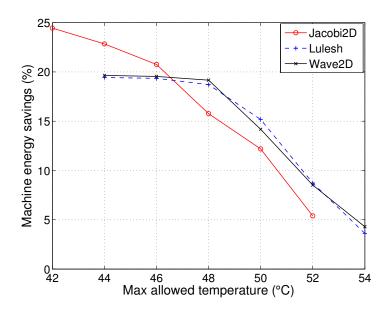

| $3.4 \\ 3.5$                      | Reduction in execution time for different temperature thresholds Execution time penalty for DVFS                                                                                                                              |   | $50\\53$         |

| 3.6<br>3.7<br>3.8                 | Gains/cost of increasing reliability for different temperature thresholds Reduction in machine energy consumption for all applications Execution time reduction for all applications at large scale                           |   | 54<br>56<br>57   |

| 3.9<br>3.10                       | Projected efficiency for <i>Wave2D</i>                                                                                                                                                                                        |   | 58               |

|                                   | exascale machine                                                                                                                                                                                                              |   | 59               |

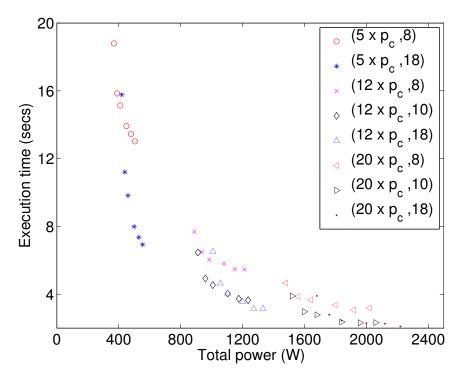

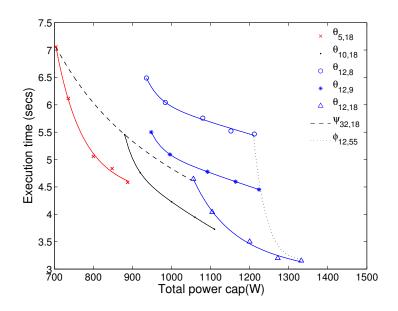

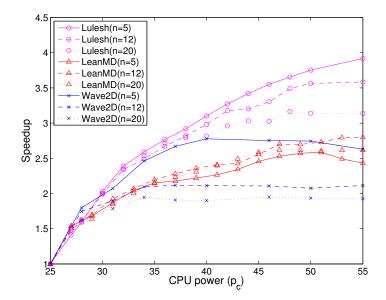

| 4.1<br>4.2<br>4.3                 | Average time per step of Lulesh for configurations selected in Step $1 \ldots$ .<br>Average time per step of Lulesh after interpolation (Step 2) $\ldots$<br>Speedups obtained using CPU and memory power capping in an over- |   | 66<br>68         |

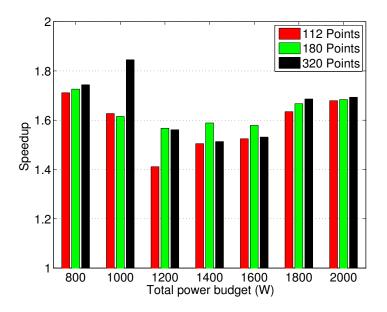

| 4.4                               | provisioned system                                                                                                                                                                                                            |   | 69<br>79         |

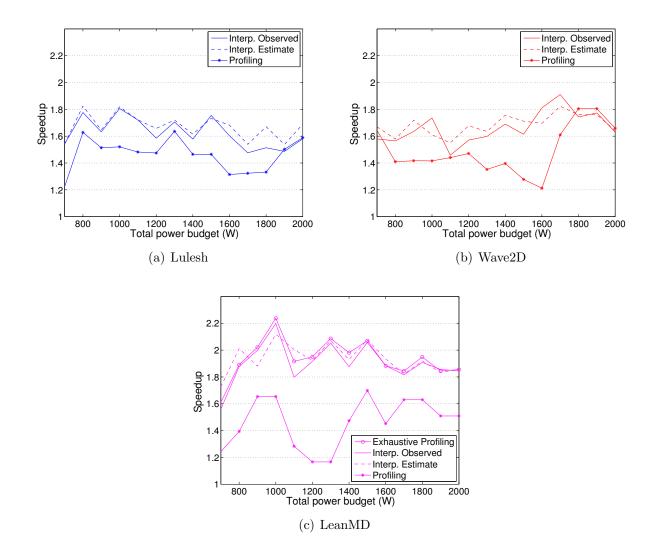

| 4.5                               | as input to our interpolation scheme                                                                                                                                                                                          | • | 72               |

| 4.6<br>4.7                        | experiments                                                                                                                                                                                                                   |   | 73<br>74<br>74   |

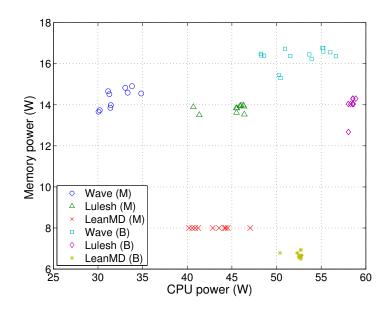

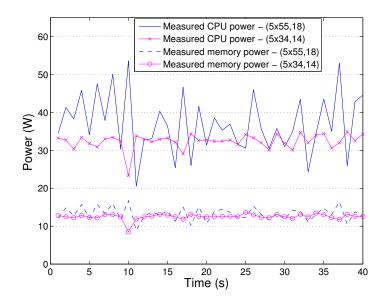

| <ul><li>4.8</li><li>4.9</li></ul> | Measured CPU and memory power for two different configurations with significantly different power allocations but similar execution time Speedups for power capping both CPU and memory (C&M) compared to                     | • | 76               |

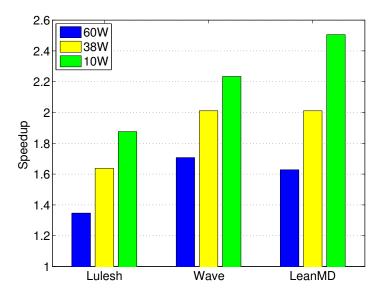

| 4.10                              | CPU (C) only $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ Estimated speedups for different base powers in case of $P=800W$ $\ldots$ $\ldots$                                                       |   | 77<br>77         |

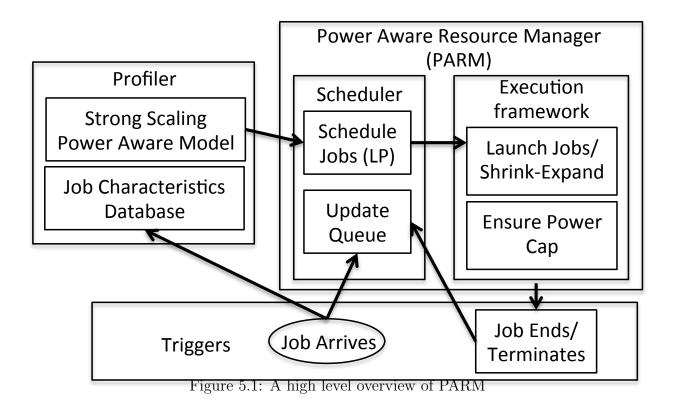

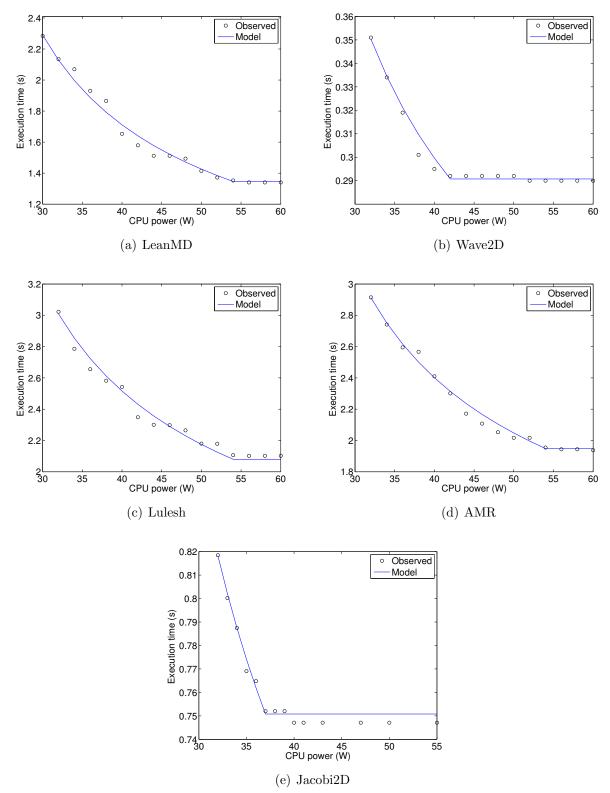

| $5.1 \\ 5.2 \\ 5.3$               | A high level overview of PARM                                                                                                                                                                                                 |   | 83<br>85         |

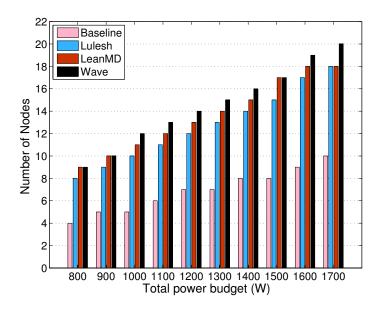

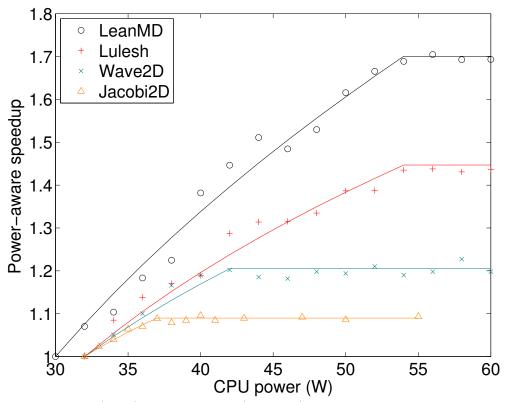

|                                   | speedups for all applications (f)                                                                                                                                                                                             |   | 92               |

| 5.4  | Modeled (lines) and observed (markers) power aware speedups for four                                                               | 93  |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

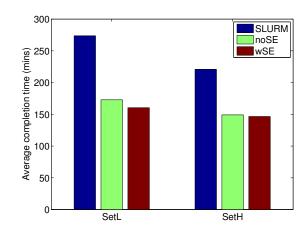

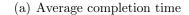

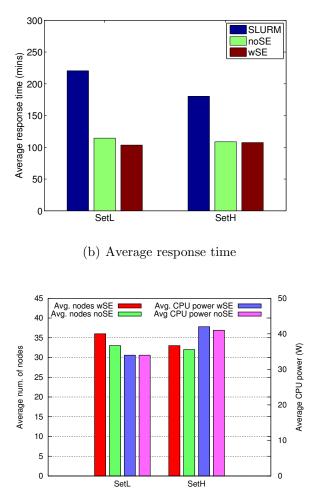

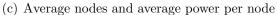

| 5.5  | applications                                                                                                                       | 95  |

|      | and SetH with SLURM and noSE, wSE versions of PARM. (c) Average number of nodes and average CPU power in the wSE and noSE versions |     |

|      | of PARM.                                                                                                                           | 96  |

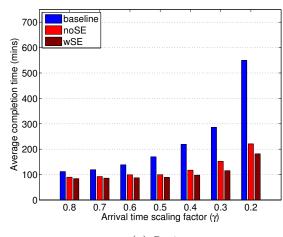

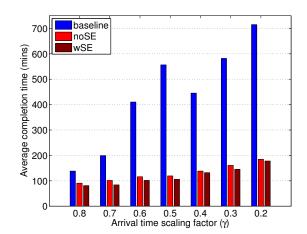

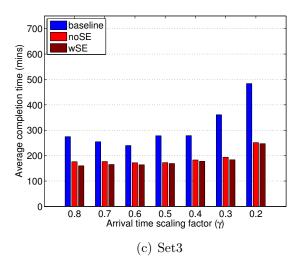

| 5.6  | Average completion times of baseline, $noSE$ and $wSE$ . Job arrival times in                                                      |     |

|      | all the sets (Set1, Set2, Set3) were scaled down by factor $\gamma$ to get diversity                                               | 100 |

|      | in job arrival rate                                                                                                                | 100 |

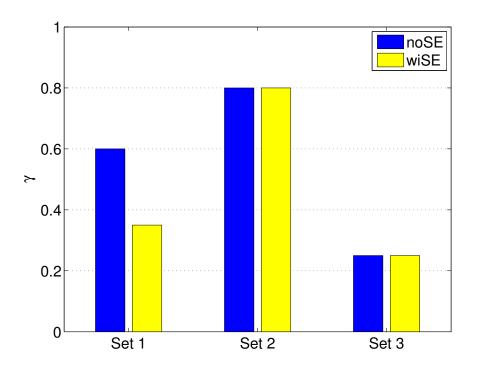

| 5.7  | Reduction in job arrival times while maintaining the same QoS as the                                                               |     |

|      | baseline scheduler                                                                                                                 | 103 |

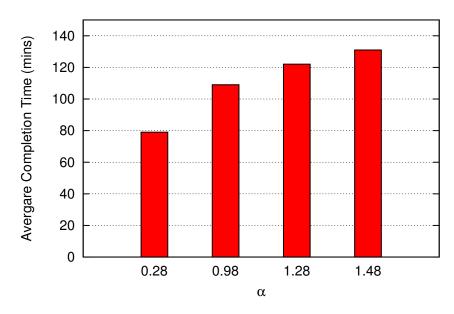

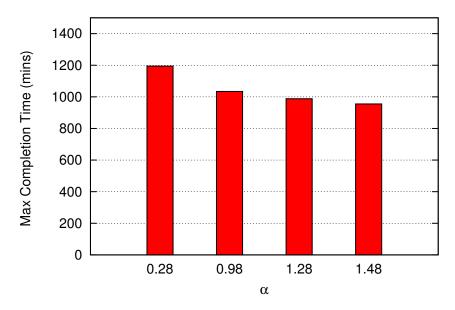

| 5.8  | Average completion times for Set 1 for different values of $(\alpha)$                                                              | 104 |

| 5.9  | Maximum (worst) completion times for Set 1 for different values of $(\alpha)$                                                      | 104 |

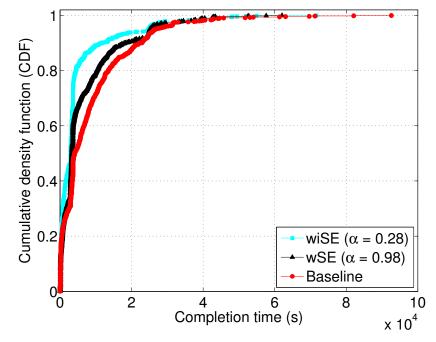

| 5.10 | CDF for completion times for baseline and wiSE for different $\alpha$ using SET1 .                                                 | 105 |

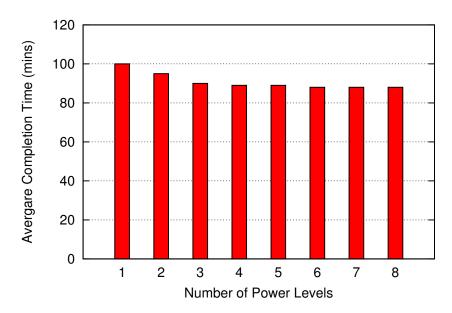

| 5.11 | Effect of increasing the number of power levels $( P_i )$ on the average com-                                                      |     |

|      | pletion time of Set 1 ( $\gamma = 0.5$ ).                                                                                          | 106 |

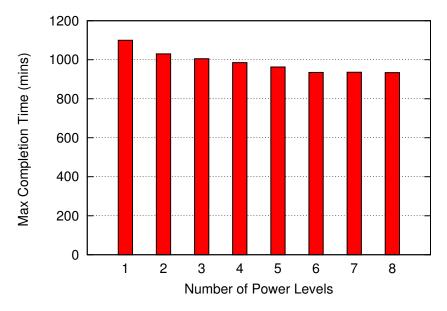

| 5.12 | Effect of increasing the number of power levels $( P_j )$ on the maximum                                                           |     |

|      | completion time of Set 1 ( $\gamma = 0.5$ )                                                                                        | 106 |

|      |                                                                                                                                    |     |

### List of Tables

| 2.1 | Description for variables used in Algorithm 1                                                                                                                               | 13  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Performance counters for Charm++ applications on one core                                                                                                                   | 21  |

| 3.1 | Parameters of the performance model                                                                                                                                         | 41  |

| 3.2 | Description for variables used in Algorithm 2 and Algorithm 3                                                                                                               | 43  |

| 3.3 | Application parameters for $NC$ case $\ldots \ldots \ldots$ | 49  |

| 3.4 | MTBF (sec) for different temperature thresholds (42° C - 54° C)                                                                                                             | 51  |

| 4.1 | Terminology                                                                                                                                                                 | 63  |

| 5.1 | Integer Linear Program Terminology                                                                                                                                          | 84  |

| 5.2 | Obtained model parameters                                                                                                                                                   | 94  |

| 5.3 | Comparison of the baseline, wSE and noSE scheduling policies for different                                                                                                  |     |

|     | data sets.                                                                                                                                                                  | 101 |

| 5.4 | Comparison of $wSE$ with the baseline scheduler running on an overprovisioned system (at different CPU power caps) using Set 2 ( $\gamma = 0.5$ )                           | 102 |

| A.1 | Summary of features of clusters used in this thesis                                                                                                                         | 112 |

# List of Algorithms

| 1 | Temperature Aware Refinement Load Balancing | 14 |

|---|---------------------------------------------|----|

| 2 | Temperature Control                         | 45 |

| 3 | Communication Aware Load Balancing          | 46 |

### CHAPTER

### Introduction

Computational scientists are among the leading users of high performance computing (HPC). These scientists usually run codes that simulate physical processes. Such simulation codes have an everlasting demand for computational power. In order to satisfy the demands for running these computational models, the HPC community will need to keep advancing their quest for larger machines. Soaring energy consumption, accompanied by declining reliability, together loom as the biggest hurdles for the next generation of supercomputers. As we approach the exascale era, both hardware and software designers will need to account for power, energy, and reliability of the machine while optimizing performance.

The combined energy consumption for data centers worldwide totaled 235 billion kWh in 2010 [1]. Most HPC researchers have been primarily focussing on energy minimization in the past decade [2,3]. The majority of this work is concentrated on reducing machine energy consumption. In this dissertation, we first attack the 'other' side of the problem i.e., cooling energy consumption, which can account for up to 50% of the total energy consumption of a data center [4–7]. Chip manufacturers have ceased to increase processor frequency and have resorted to adding more cores on a chip to keep up with the ever increasing demand for faster computers. This stagnation in processor frequency has been caused by a sharp increase in the heat density of chip. Earlier studies show a connection between the operating temperature of a processor and its reliability [8–10]. These studies mention the existence of an exponential relationship between a processor's temperature and its Mean Time Between Failures (MTBF). Most HPC research focused on energy optimization and machine reliability does not consider the impact of processor temperature. Although thermal considerations have not been a primary concern for recent supercomputers, it can significantly improve MTBF and hence, performance of future supercomputers. An exascale machine is predicted to have more than 200,000 sockets [11]. Recent studies also show that supercomputers can

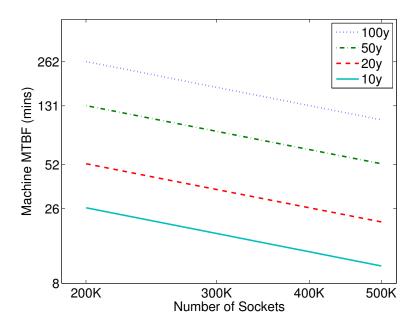

Figure 1.1: Mean Time Between Failures (MTBF) for different numbers of sockets using different MTBF per socket.

have a per socket MTBF as low as 5 years [12]. The implications of such large numbers of sockets coupled with the existing MTBF values per socket are depicted in Figure 1.1. This figure shows the MTBF of large supercomputers for different numbers of sockets and different MTBF per socket. Figure 1.1 shows that with a per socket MTBF of 5 years, a 200K socket machine is likely to fault every 26 mins. Such a high fault rate could have a dramatic effect on machine utilization. On the other hand, a per socket MTBF of 100 years can improve the machine reliability and increase the machine MTBF to 262 mins for a 200K socket machine. This thesis makes an attempt at improving the per socket MTBF of a large machine by using Dynamic Voltage and Frequency Scaling (DVFS) in conjunction with an adaptive runtime system.

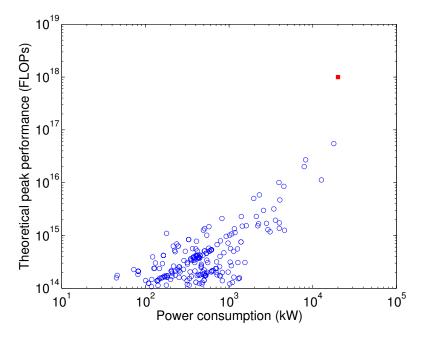

Although energy minimization and thermal control are major challenges, in order to reach exascale computing within the 20MW power envelope proposed by the DOE, data centers would have to significantly improve their performance per watt. Figure 1.2 shows the power consumption and the theoretical peak performance of all the supercomputers from the Top500 [13] for which power consumption data is available (blue circles). It also plots the power consumption bound (20MW) set by the DOE for the exascale machine (red box). Given the trend of current supercomputers, it is unlikely that the HPC community will achieve exascale computing within the 20MW power budget. Looking at the data from Figure 1.2, 100MW seems to be a more realistic target to achieve an exaflop. Although

Figure 1.2: Power consumption and theoretical peak performance for supercomputers from the Top500 (blue circles). The proposed Exascale machine under a power budget of 20MW (red square).

hardware advances will be needed to build an exascale machine, efficient runtime techniques are necessary to make the best use of what the hardware will provide.

#### 1.1 Thesis Organization

This thesis is organized in three major parts. Part one contains Chapter 2 and Chapter 3. This part demonstrates techniques for controlling core temperature and their impact on performance and reliability. Chapter 2 describes how Dynamic Voltage and Frequency Scaling (DVFS) can restrain processor temperatures and our scheme that uses object migration to minimize the timing penalty associated with DVFS. Chapter 2 further presents the experimental results for restraining processor temperatures using different applications, and demonstrates the reduction in timing penalty as well as energy consumption. It includes a comprehensive discussion about application reaction to thermal restraint. Chapter 3 introduces a novel technique that combines fault tolerance with thermal restraint to improve system reliability. It demonstrates how restraining core temperatures can eventually benefit application performance as a result of improved machine reliability. It also presents the estimated benefits in machine reliability and application performance of using temperature restraint for massively parallel machines running different types of applications. We thank Esteban Meneses for his interest in the research on improving reliability using thermal restraint (Chapter 3). We had a lot of discussions which helped improve the quality of our work. In particular, Esteban's incisive comments and his mathematical modeling background helped us a great deal.

Part two of the thesis tackles the imminent problem of data center operation under a strict power budget. It contains Chapters 4 and Chapters 5. Operating under a power constraint is a challenging problem as it poses a constraint rather than a restraint which is a less stricter limiting condition. While restraining, we try to apply a limit whereas in case of a constraint that limit is strictly enforced. In this part, we use Intel's Running Average Power Library (RAPL) to cap processor and memory power for overprovisioned systems [14] to improve application performance. Chapter 4 uses RAPL to improve application performance for a single application executing in an overprovisioned system. Chapter 5 proposes a resource management strategy that maximizes job throughput by intelligently scheduling applications with different resource configurations. This chapter also proposes a detailed strong scaling power aware model that can estimate the execution time of an application based on its characteristics for any resource configuration. We thank Akhil Langer for his interest in the research on optimization under strict power budget (Chapter 4 and 5). We had numerous productive discussions during which we gave direction to this work. In particular, his insightful comments, his linear programming background, his work on the SLURM simulator, and clear presentation of the ideas (including writing of the papers) helped us a great deal.

Chapter 6 contains the last part of the thesis which summarizes the contributions of this thesis and possible directions for future work. We outline multiple directions in which we plan to extend our thesis work. The first idea relates to improving machine reliability by taking into account the effects of thermal throttling. The second idea explores the possibility of operating a data center under strict power *and* thermal constraints.

# $_{\rm chapter} 2$

### Thermal Restraint Using Migratable Objects

Energy consumption has emerged as a significant issue in modern high-performance computing systems. Some of the largest supercomputers draw more than 10 megawatts, leading to millions of dollars per year in energy bills. What is perhaps less well known is the fact that 40% to 50% of the energy consumed by a data center is spent in cooling [4], [5], [6], to keep the computer room running at a lower temperature. How can we reduce this cooling energy?

Increasing the thermostat setting on the computer room air-conditioner (CRAC) reduces the cooling power. But the increase in the thermostat will also increase the ambient temperature in the computer room. The reason the ambient temperature is kept cool is to keep processor cores from overheating. If they run at a high temperature for a long time, the processor cores may be damaged. Additionally, cores consume more energy per unit of work when run at higher temperatures [15]. Further, due to variations in the air flow in the computer room, some chips may not be cooled as effectively as the rest. Semiconductor process variation will also likely contribute to variability in heating, especially in future processor chips. So, to handle such 'hot spots', the ambient air temperature is kept at a low temperature to ensure that no individual chip overheats.

Modern microprocessors contain on-chip temperature sensors that can be accessed by software with minimal overhead. Further, they also provide means to change the frequency and voltage at which the chip runs, known as *dynamic voltage and frequency scaling*, or DVFS. Running processor cores at a lower frequency (and correspondingly lower voltage) reduces the thermal energy that they dissipate, leading to a cool-down.

This suggests a method for keeping processors cool while increasing the CRAC set-point (i.e. the thermostat setting). A component of the application software can periodically check the temperature of the chip. When it exceeds a pre-set threshold, the software can reduce the frequency and voltage of that particular chip. If the temperature is lower than a threshold, the software can correspondingly increase the frequency.

This technique will ensure that no processors overheat. However, in HPC computations, and specifically in tightly-coupled science and engineering simulations, DVFS creates a new problem. Generally, computations on one processor are dependent on the data produced by the other processors. As a result, if one processor slows down to half its original speed, the entire computation can slow substantially, in spite of the fact that the remaining processors are running at full speed. Thus, such an approach will reduce the cooling *power*, but increase the execution time of the application. Running the cooling system for a longer time can also *increase* the cooling energy.

We aim to reduce cooling power without substantially increasing execution time, and thus reduce cooling energy. We first describe the temperature sensor and frequency control mechanisms, and quantify their impact on execution time mentioned above (Section 2.2). Our solution leverages the adaptive runtime system underlying the Charm++ parallel programming system (Section 2.3). In order to minimize *total* system energy consumption, we study an approach of limiting CPU temperatures via DVFS and mitigating the resultant timing penalties with a load balancing strategy that is conscious of these effects (Section 2.4). We show the impact of this combined technique on application performance (Section 2.6) and *total* energy consumption (Section 2.7).

#### 2.1 Related Work

Cooling energy optimization and hot spot avoidance have been addressed extensively in the literature of non-HPC data centers [16–19], which shows the importance of the topic. As an example, job placement and server shut down have shown savings of up to 33% in cooling costs [16]. Many of these techniques rely on placing jobs that are expected to generate more heat in the cooler areas of the data center. Such job placement schemes can not be directly applied to HPC applications because different nodes are running parts of the same application with similar power consumption. As an example, Rajan et al [20] use system throttling for temperature-aware scheduling in the context of operating systems. Given their assumptions, they show that keeping temperature constant is beneficial with their theoretical models. However, their assumption of non-migratability of tasks is not true in HPC applications by turning the machines on and off and consequently reduce total energy consumption by 18%. However, most of these techniques, cannot be applied to HPC applications as they are

not practical for tightly-coupled applications.

Minimizing energy consumption has also been an important topic for HPC researchers. However, most of the work has focused on machine energy consumption rather than cooling energy. Freeh et al. [2] show machine energy savings of up to 15% by exploiting the communication slack present in the computational graph of a parallel application. Lim et al [22] demonstrate a median energy savings of 15% by dynamically adjusting the CPU frequency/voltage pair during the communication phases in MPI applications. Springer et al. [3] generate a frequency schedule for a DVFS-enabled cluster that runs the target application. This schedule tries to minimize the execution time while staying within the power constraints. The major difference of our approach to the ones mentioned is that our DVFS decisions are based on saving cooling energy consumption by constraining core temperatures. The *total* energy consumption savings that we report represent both machine and cooling energy consumption.

Huang and Feng describe a kernel-level DVFS governor that tries to determine the poweroptimal frequency for the expected workload over a short time interval that reduces machine energy consumption up to 11% [23]. Hanson et al. [24] devise a runtime system named PET for performance, power, energy and thermal management. They consider a more general case of multiple and dynamic constraints. However, they just consider a serial setting without the difficulties of parallel machines and HPC applications. Extending our approach for constraints other than temperature is an interesting future work.

Banerjee et al. [25] try to improve the cooling cost in HPC data centers by an intelligent job placement algorithm yielding up to 15% energy savings. However, they do not consider the temperature variations inside a job. Thus, their approach can be less effective for data centers with a few large-scale jobs rather than many small jobs. They also depend on job pre-runs to get information about the jobs. In addition, their results are based on simulations and not experiments on a real testbed. Tang et al. [26] reduce 30% of cooling energy consumption by scheduling tasks in a data center. However, the benefits of their scheme for large-scale jobs are questionable.

Merkel et al. [27] discuss the scheduling of tasks in a multiprocessor to avoid hot cores. However, they do not deal with complications of parallel applications and large-scale data centers. Freeh et al. [28] exploit the varying sensitivity of different phases in the application to core frequency in order to reduce machine energy consumption for load balanced applications. This work is similar to ours, as it deals with load balanced applications. They reduce machine energy consumption by a maximum of 16%. However, our work is different as we achieve much higher savings in *total* energy consumption primarily by reducing cooling energy consumption.

#### 2.2 Limiting Temperatures

The design of a machine room or data center must ensure that all equipment stays within its safe operating temperature range while keeping costs down. Commodity servers and switches draw cold air from their environment, pass it over processor heatsinks and other hot components, and then expel it at a higher temperature. To satisfy these systems' specifications and keep them operating reliably, cooling systems in the data center must supply a high enough volume of sufficiently cold air to every piece of equipment.

Traditional data center designs treated the air in the machine room as a single mass, to be kept at an acceptable aggregate temperature. If the air entering some device was too hot, the CRAC's thermostat should be adjusted to a lower set-point. That adjustment would cause the CRAC to run more frequently or intensely, increasing its energy consumption. More modern designs, such as alternating hot/cold aisles [4] or in-aisle coolers, provide greater separation between cold and hot air flows and more localized cooling, easing appropriate supply to computing equipment and increasing efficiency.

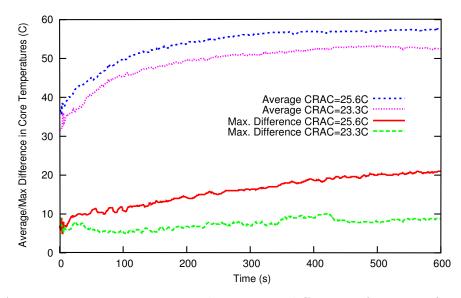

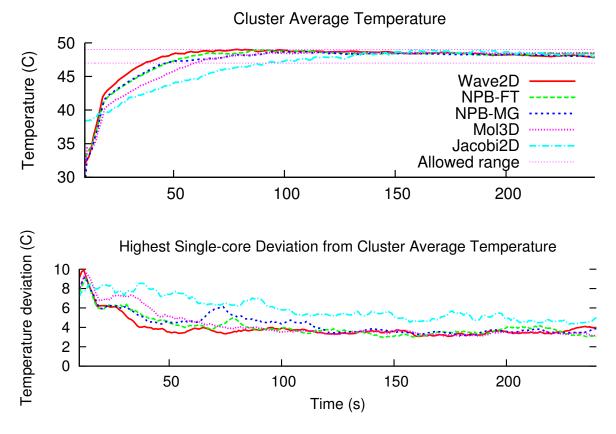

However, even with this tighter air management, variations in air flow, system design, manufacturing and assembly, and workload may still leave some devices significantly hotter than others. To illustrate this sensitivity, we run an intensive parallel (Wave2D) application on a cluster (Energy Cluster) with a dedicated CRAC unit. We changed the machine room's cooling by manipulating the CRAC set-point. The details of the application and our Energy Cluster are described in Appendix B and Appendix A respectively. Figure 2.1 shows two runs of Wave2D with different CRAC set-point temperatures. For each run, we plot both the average core temperature across the entire cluster, and the maximum deviation of any core from that average.

Unsurprisingly, observed core temperatures correlate with the temperature of the air provided to cool them. With a set-point increase of  $2.3^{\circ}$  C, the average temperature across the system increases by 6° C. More noteworthy is that this small shift creates a substantial hot spot, that worsens progressively over the course of the run. At the higher 25.6° C set-point, the temperature difference from the average to the maximum rises from 9° C to 20° C. In normal operations, this difference of 11° C would be an unacceptable result, and the CRAC set-point must be kept low enough to avoid it.

An alternative approach, based on DVFS, shows promise in addressing the issue of overcooling and hot spots. DVFS is already widely used in laptops, desktops, and servers in non-HPC data centers as a means to limit CPU power consumption. However applying DVFS naively to HPC workloads entails an unacceptable performance degradation. Many HPC applications are tightly-coupled, such that one or a few slow cores would effectively

Figure 2.1: Average core temperatures and maximum difference of any core from the average for Wave2D

slow down an entire job. This *timing penalty* implies decreased throughput and increased time-to-solution.

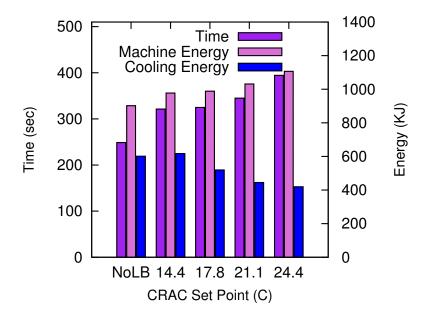

To demonstrate the impact of DVFS, we repeat the earlier experiment with a temperature constraint. We fix a threshold temperature of 44° C that we wish to keep all CPUs below. We sample temperatures periodically, and when a CPU's average temperature is over this threshold, its frequency is lowered by one step, i.e., increase the P-state by a level. If it is more than a degree below the threshold, its frequency is increased by one step i.e. decrease its P-state by a level. We repeat this experiment over a range of CRAC settings, and compute their performance in time and energy consumption relative to a run with all cores working at their maximum frequency and the CRAC set to 12.2° C. As shown in Figure 2.2, DVFS alone in this setting hurts performance and provides minimal savings in *total* energy consumption. Most of the savings from cooling energy consumption are offset by an increase in machine energy consumption. This effect arises because the decreased energy consumption of the slower cores is more than offset by the additional machine energy consumed by all the cores, including some at higher frequencies, running for the extended time. Not only that, the slower cores can sometimes add such a large timing penalty that even they start consuming more energy  $(24.4^{\circ} \text{ C CRAC set-point case})$  due to the extra time they have to run while parts outside the CPUs keep consuming the same power. Nevertheless, our results in Figure 2.3 (described in detail in Section 2.6) show that DVFS effectively limits both overall temperatures and hot spots.

More radical liquid-cooling designs mitigate some of the hot spot concerns, but they are

Figure 2.2: Execution time and energy consumption for *Wave2D* running at different CRAC set-points using DVFS

not a panacea. Equipment must be specifically designed to be liquid-cooled, and data centers must be built or retrofit to supply the coolant throughout the machine room. The present lack of commodity liquid-cooled systems and data centers means that techniques to address the challenges of air-cooled computers will continue to be relevant for the foreseeable future. Moreover, our techniques for limiting core temperatures can actually reduce the overall thermal load of an HPC system, leading to energy savings even for installations using liquid cooling.

#### 2.3 Charm++ and Load Balancing

Charm++ is a general-purpose C++-based parallel programming system designed for productive HPC programming [29]. It is supported by an adaptive runtime system that automates resource management. It relies on techniques such as processor virtualization and over-decomposition (having more work units than the number of cores) to improve performance via adaptive overlap of computation and communication and data-driven execution. The automated resource management implies that the developer does not need to program in terms of the physical cores, but instead divides the work into pieces with a suitable grain size to let the system manage them easily.

A key feature of Charm++ is that the units of work decomposition are *migratable objects*.

The adaptive runtime system can assign these objects to any processor and move them around during program execution, for purposes including load balancing, communication optimization, and fault tolerance. To enable effective load balancing, it tracks statistics of each object's execution, including its computation time and communication volume [30].

The runtime system provides a variety of plug-in *load balancing strategies* that can account for different application characteristics. Through a simple API, these strategies take the execution statistics from the runtime and generate a set of migration instructions, describing which objects to move between which processors. Application developers and users can provide their own strategy implementations as desired. Load balancing strategies can be chosen at compilation or run-time. The majority of these strategies are based on the heuristic 'principle of persistence', which states that each object's computation and communication loads tend to persist over time. The principle of persistence holds for a large class of iterative HPC applications. In this study, we have developed a new load balancing strategy that accounts for the performance effects of DVFS-induced heterogeneity. The new strategy is described in detail in Section 2.4.

At small scales, the cost of the entire load balancing process, from instrumentation through migration, is generally a small portion of the total execution time, and less than the improvement that it provides. For cases where load balancing costs can be significant, a strategy must be chosen or adapted to match the application's needs [31]. Our approach can be easily adapted to available hierarchical schemes, which have been shown to scale to the largest machines available [32]. By limiting the cost of decision-making and scope of migration, we expect these schemes to offer similar energy benefits.

#### 2.3.1 AMPI

The Message Passing Interface (MPI) is a standardized communication library for distributedmemory parallel programming. MPI has become the dominant paradigm for large-scale parallel computing. Thus, techniques for addressing the energy consumption of large parallel systems must be applicable to MPI applications.

Charm++ provides an implementation of MPI known as Adaptive MPI (AMPI). AMPI makes the features of the Charm++ runtime system available to MPI programs. Common MPI implementations implement each unit of parallel execution, or *rank*, as a separate process. Pure MPI applications run one rank per CPU core, while others use fewer ranks and gain additional shared-memory parallelism via threading.

In contrast, AMPI encourages running applications with several ranks per core. AMPI

implements these ranks as light weight user-level threads, many of which can run in each process. The runtime schedules these threads non-preemptively, and switches them when they make blocking communication calls. Internally, these threads are implemented as migratable objects, enabling the same benefits for MPI programs as for native Charm++. In particular, AMPI allows us to apply the Charm++ load balancing strategies without intrusive modifications to application logic.

#### 2.4 'Cool' Load Balancer

In this section, we introduce a novel approach that reduces energy consumption of the system with minimal timing penalty. It is based on limiting core temperatures using DVFS and task migration. Because our scheme is tightly coupled to task migration, we chose Charm++ and AMPI as our parallel programming frameworks as they allow easy task (object) migration with low overhead. All implementations and experiments were done using Charm++ and AMPI. However, our techniques can be applied to any parallel programming system that provides efficient task migration.

The steps of our temperature-control scheme can be summarized as applying the following process periodically:

- 1. Check the temperatures of all cores

- 2. Apply DVFS to cores that are hotter or colder than desired

- 3. Address the load imbalance caused by DVFS using our load balancer, *TempLDB*:

- (a) Normalize task and core load statistics to reflect old and new frequencies

- (b) Identify overloaded or underloaded cores

- (c) Move work from overloaded cores to underloaded cores

The remainder of this section describes this process in detail.

Our temperature control scheme is periodically triggered after equally spaced intervals in time, referred to as *steps*. Other DVFS schemes [23] try to react directly to the demands of the application workload, and thus must sample conditions and make adjustments at intervals on the order of milliseconds. In contrast, our strategy only needs to react to much slower shifts in chip temperature, which occur over intervals of seconds. At present, DVFS is triggered as part of the runtime's load balancing infrastructure at a user-specified period.

| Variable                                   | Description                                     |

|--------------------------------------------|-------------------------------------------------|

| n                                          | number of tasks in application                  |

| р                                          | number of cores                                 |

| $T_{max}$                                  | maximum temperature allowed                     |

| k                                          | current load balancing step                     |

| $C_i$                                      | set of cores on same chip as core $i$           |

| $taskTime_i^k$                             | execution time of task $i$ during               |

|                                            | step $k$ (in ms)                                |

| $coreTime_i^k$                             | time spent by core $i$ executing tasks          |

|                                            | during step $k$                                 |

| $egin{array}{c} f_i^k \ m_i^k \end{array}$ | frequency of core $i$ during step $k$ (in Hz)   |

| $m_i^k$                                    | core number assigned to task $i$                |

|                                            | during step $k$                                 |

| $\{task, core\}Ticks_i^k$                  | num. of clock ticks taken by $i^{th}$ task/core |

|                                            | during step $k$                                 |

| $t_i^k$                                    | average temperature of chip $i$ at start of     |

| U                                          | step $k$ (in °C)                                |

| over Heap                                  | heap of overloaded cores                        |

| underSet                                   | set of underloaded cores                        |

Table 2.1: Description for variables used in Algorithm 1

Our control strategy for DVFS is to let the cores work at their maximum frequency as long as their temperature is below a threshold parameter. If a core's temperature crosses above the threshold, it is controlled by decreasing the voltage and frequency using DVFS. When the voltage and frequency are reduced, power consumption will drop and hence the core's temperature will fall. Our earlier approach [33] raised the voltage and frequency as soon as temperatures fell below the threshold, causing frequent changes and requiring effort to load balance in every interval. To reduce overhead, our strategy now waits until a chip's temperature is a few degrees below the threshold before increasing its frequency.

The hardware in today's cluster computers does not allow reducing the frequency of each core individually and so we must apply DVFS to the whole chip. This raises the question: what heuristic should we use to trigger DVFS and modulate frequency? In our earlier work [15], we conducted DVFS when *any* of the cores on a chip were considered too hot. However, our more recent results [33] show that basing the decision on *average* temperature of the cores in a chip results in better temperature control.

Another important decision is how much a chip's frequency should be reduced (respectively, raised) when it gets too hot (is safe to warm up). Present hardware only offers discrete frequency and voltage levels built into the hardware, the 'P-states'. Using this hardware, we observed that reducing the chip's frequency by one level at a time is a reasonable heuristic because it effectively constrains the core temperatures in the desired range (Figure 2.3). Lines 1–6 of Algorithm 1 apply DVFS as we have just described. The description of the variables and functions used in the algorithm is given in Table 2.1.

When DVFS adjusts frequencies differently across the cores in a cluster, the workloads on those cores change relative to one another. Because this potential for load imbalance occurs all at once, it makes sense to react to this load balance immediately. The system responds by rebalancing the assignment of work to cores according to the strategy described by lines 7–32 of Algorithm 1.

| Algorithm 1: Temperature Aware Refinement Load Balancing                                                                                                             |                                   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| 1: On every node $i$ at start of step $k$                                                                                                                            |                                   |  |  |  |

| 2: if $t_i^k > T_{max}$ then                                                                                                                                         |                                   |  |  |  |

| 3: decreaseOneLevel $(C_i)$                                                                                                                                          | $\triangleright$ increase P-state |  |  |  |

| 4: else if $t_i^k < T_{max} - 2$ then                                                                                                                                |                                   |  |  |  |

| 5: increaseOneLevel $(C_i)$                                                                                                                                          | $\triangleright$ decrease P-state |  |  |  |

| 6: end if                                                                                                                                                            |                                   |  |  |  |

| 7: On Master core                                                                                                                                                    |                                   |  |  |  |

| 8: for $i \in [1, n]$ do                                                                                                                                             |                                   |  |  |  |

| 9: $taskTicks_i^{k-1} = taskTime_i^{k-1} \times f_{m_i^{k-1}}^{k-1}$                                                                                                 |                                   |  |  |  |

| 10: $totalTicks += taskTicks_i^{k-1}$                                                                                                                                |                                   |  |  |  |

| 11: end for                                                                                                                                                          |                                   |  |  |  |

| 12: for $i \in [1, p]$ do                                                                                                                                            |                                   |  |  |  |

| 13: $coreTicks_i^{k-1} = coreTime_i^{k-1} \times f_i^{k-1}$                                                                                                          |                                   |  |  |  |

| 14: $freqSum += f_i^k$                                                                                                                                               |                                   |  |  |  |

| 15: end for                                                                                                                                                          |                                   |  |  |  |

| 16: createOverHeapAndUnderSet()                                                                                                                                      |                                   |  |  |  |

| 17: while over Heap NOT NULL do                                                                                                                                      |                                   |  |  |  |

| 18: $donor = deleteMaxHeap(overHeap)$                                                                                                                                |                                   |  |  |  |

| $19: \qquad (bestTask, bestCore) =$                                                                                                                                  |                                   |  |  |  |

| 20: $getBestCoreAndTask(donor, underSet)$                                                                                                                            |                                   |  |  |  |

| 21: $m_{bestTask}^k = bestCore$                                                                                                                                      |                                   |  |  |  |

| 21: $m_{bestTask}^{k} = bestCore$<br>22: $coreTicks_{donor}^{k-1} - = taskTicks_{bestTask}^{k-1}$<br>23: $coreTicks_{bestCore}^{k-1} + = taskTicks_{bestTask}^{k-1}$ |                                   |  |  |  |

| 23: $coreTicks_{bestCore}^{k-1} + = taskTicks_{bestTask}^{k-1}$                                                                                                      |                                   |  |  |  |

| 24: updateHeapAndSet()                                                                                                                                               |                                   |  |  |  |

| 25: end while                                                                                                                                                        |                                   |  |  |  |

| 26:                                                                                                                                                                  |                                   |  |  |  |

| 27: procedure $isHeavy(i)$                                                                                                                                           |                                   |  |  |  |

| 28: return $coreTicks_i^{k-1} > (1 + tolerance) * totalTicks$                                                                                                        |                                   |  |  |  |

| 29: $*(f_i^k/freqSum)$                                                                                                                                               |                                   |  |  |  |

| 30:                                                                                                                                                                  |                                   |  |  |  |

| 31: procedure isLight(i)                                                                                                                                             |                                   |  |  |  |

| 32: return $coreTicks_i^{k-1} < totalTicks * f_i^k / freqSum$                                                                                                        |                                   |  |  |  |

The key principle in how a load balancer must respond to DVFS actuation is that the

load statistics must be adjusted to reflect the various different frequencies at which load measurements were recorded and future work will run. At the start of step k, our load balancer retrieves load information for step k-1 from Charm++'s database. This data gives the total duration of work executed for each task in the previous interval  $(taskTime_i^{k-1})$  and the core that executed it  $(m_i^{k-1})$ . Here *i* refers to task *id* and k-1 represents last step. We normalize the task workloads by multiplying their execution times by the old frequency values of the core that hosted them. We then sum these normalized task workloads to compute the total load, as seen in lines 8–11. This normalization is an approximation to the performance impact of different frequencies. However, different applications might have different characteristics (e.g., cache hit rates at various levels, instructions per cycle) that determine the sensitivity of their execution time to core frequency. We plan to incorporate more detailed load estimators in our future work. The scheme also calculates the work assigned to each core and sum of frequencies for all the cores to be used later (lines 12-15).

Once the load normalization is done, we create a max heap for overloaded cores (overHeap) and a set for the underloaded cores (underSet) on line 16. The cores are classified as overloaded and underloaded by procedures isHeavy() and isLight() (lines 26–30), based on how their normalized loads from the previous step, k-1, compare to the frequency-weighted average load for the coming step k. We use a tolerance in identifying overloaded cores to focus our efforts on the worst instances of overload and minimize migration costs. In our experiments, we set the tolerance to 0.07, empirically chosen for the slight improvement that it provided over the lower values used in our previous work.

Using these data structures, the load balancer iteratively moves work away from the most overloaded core (*donor*, line 18) until none are left (line 17). The moved task and recipient are chosen as the heaviest task that the *donor* could transfer to any underloaded core such that the underloaded core does not become overloaded (line 19, implementation not shown). Once the chosen task is reassigned (line 20), the load statistics are updated and the data structures are updated accordingly (lines 21–23).

#### 2.5 Experimental Setup

To evaluate our approach to reducing energy consumption, we must be able to measure and control core frequencies and temperatures, air temperature, and energy consumed by computer and cooling hardware. All experiments were run on real hardware and this chapter does not include any simulation results.

We tested our scheme on the Energy Cluster hosted by the Computer Science department

at University of Illinois Urbana Champaign (see Appendix A). Its cooling design is similar to the cooling systems of most large data centers. We were able to vary the CRAC set-point across a broad range as shown in our results (following sections).

Because the CRAC unit exchanges machine room heat with chilled water supplied by a campus-wide plant, measuring its direct energy consumption (i.e., with an electrical meter) would only include the mechanical components driving air and water flow, and would miss the much larger energy expenditure used to cool the water. To capture the machine room's cooling energy, we use a model [21] based on measurements of how much heat the CRAC actually expels. The instantaneous power consumed by the CRAC to cool the temperature of the exhaust air from  $T_{hot}$  down to the cool inlet air temperature  $T_{ac}$  can be approximated by:

$$P_{ac} = c_{air} * f_{ac} * (T_{hot} - T_{ac}) \tag{2.1}$$

In this equation,  $c_{air}$  is the heat capacity constant and  $f_{ac}$  is the constant rate of air flow through the cooling system. We use temperature sensors on the CRAC's vents to measure  $T_{hot}$  and  $T_{ac}$ . During our experiments, we recorded a series of measurements from each of these sensors, and then integrated the calculated power to produce total energy figures.

By working in a dedicated space, the present work removes a potential source of error from previous data center cooling results. Most data centers have many different jobs running at any given time. Those jobs dissipate heat, interfering with cooling energy measurements and increasing the ambient temperature in which the experimental nodes run. In contrast, our cluster is the only heat source in the space, and the CRAC is the primary sink for that heat.

We investigate the effectiveness of our scheme, using five different applications, of which three are Charm++ applications and two are written in MPI. These applications have a range of power profiles and are described in Appendix B.

Most of our experiments were run for 300 seconds as it provided ample time for all applications to settle to their steady state frequencies. All results that we show are averaged over three identically configured runs, with a cool-down period before each. All normalized results are reported with respect to a run where all 128 cores were running at the maximum possible frequency with Intel Turbo Boost in operation and the CRAC set to  $12.2^{\circ}$  C. To validate the ability of our scheme to reduce energy consumption for longer execution times, we ran *Wave2D* (the most power-hungry of the five applications we consider) for 2.5 hours. The longer run was consistent with our findings, with the temperature being constrained well within the specified range and we were able to reduce cooling energy consumption for the entire 2.5 hour period.

#### 2.6 Constraining Core Temperatures and Timing Penalty

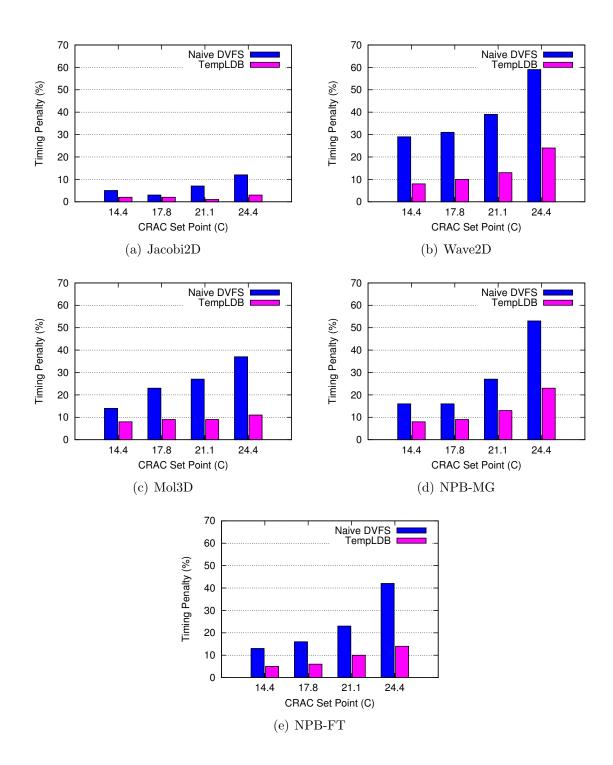

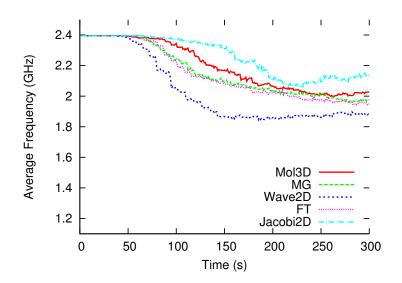

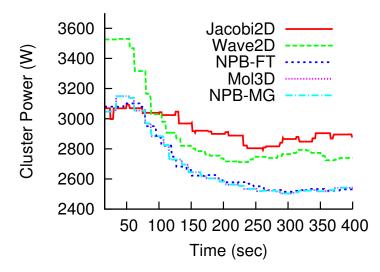

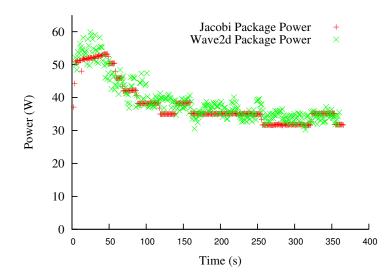

The approach that we have described in Section 2.4 constrains processor temperatures with DVFS while attempting to minimize the resulting timing penalty. Figure 2.3 shows that all of our applications when using DVFS and *TempLDB*, settle to an average temperature that lies in the desired range (the two horizontal lines at 47 °C and 49 °C on Figure 2.3). As the average temperature increases to its steady-state value, the hottest single core ends up no more than 6° C above the average (lower part of Figure 2.3) as compared to 20° C above average for the run where we are not using temperature control (Figure 2.1).

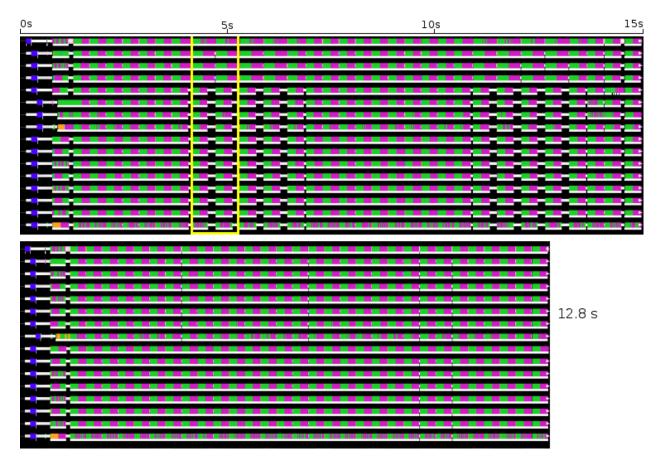

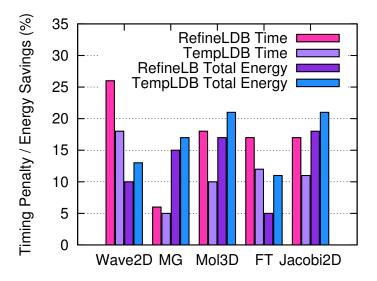

Figure 2.4 shows the timing penalty incurred by each application under DVFS, contrasting its effect with and without load balancing. The effects of DVFS on the various applications are quite varied. The worst affected, Wave2D and NAS MG, see penalties of over 50%, which load balancing reduces to below 25%. Jacobi2D was the least affected, with a maximum penalty of 12%, brought down to 3% by load balancing. In all cases, the timing penalty sharply decreases when load balancing is activated, generally by greater than 50%. Before analyzing the timing penalty for individual applications we first see how load balancing helps in reducing timing penalty compared to naive DVFS.

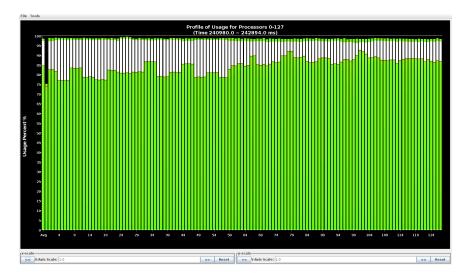

To illustrate the benefits of load balancing, we use Projections [34], which is a multipurpose performance visualization tool for Charm++ applications. Here, we use processor timelines to see the utilization of the processors in different time intervals. For ease of comprehension, we show a representative 16-core subset of the 128-core cluster. The top part of Figure 2.5 shows the timelines for execution of Wave2D with the naive DVFS scheme. Each timeline (horizontal line) corresponds to the course of execution of one core visualizing its utilization. The green and pink colored pieces show different computation but white ones represent idle time. The boxed area in Figure 2.5 shows some of the cores have significant idle time. The top 4 cores in the boxed area take much longer to execute their computation than the bottom 12 cores which is why the pink and green parts are longer for the top 4 cores. However, the other 12 cores execute their computation quickly and stay idle waiting for the rest of cores. The idle time is caused because DVFS decreased the frequency of the first four cores and so they are slower in their computation. It means that the timing penalty of naive DVFS is dictated by the slowest cores. The bottom part of Figure 2.5 shows the same temperature control but using our *TempLDB*. In this case, there is no significant idle time because the scheme balances the load between slow and fast processors by taking their frequencies into account. Consequently, the latter approach results in much shorter total execution time, as reflected by shorter timelines (and figure width) in the bottom part of Figure 2.5. Now we try to understand the timing penalty differences amongst different

Figure 2.3: Our DVFS and load balancing scheme successfully keeps all processors within the target temperature range of  $47^{\circ}$ – $49^{\circ}$  C, with a CRAC set-point of 24.4° C.

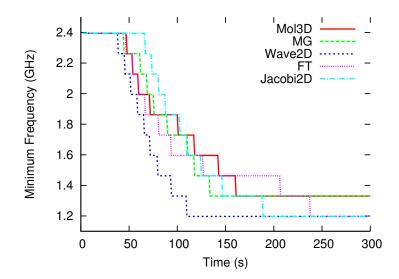

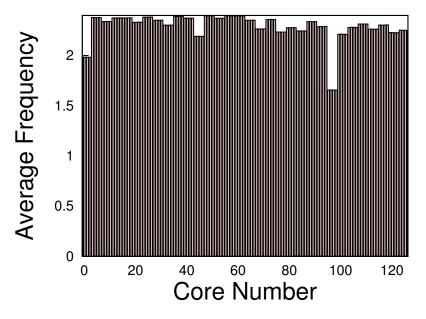

applications by examining more detailed data. Jacobi2D experiences the lowest impact of DVFS, regardless of load balancing (Figure 2.4(a)). The small timing penalty for Jacobi2D occurs for several interconnected reasons. From the high level, Figure 2.3 shows that it takes the longest of any application to increase temperatures to the upper bound of the acceptable range, where DVFS activates. This slow ramp-up in temperature means that its frequency does not drop until later in the run, and then falls relatively slowly, as seen in Figure 2.6 which plots the minimum frequency at which any core was running (Figure 2.6(a)) and the average frequency (Figure 2.7(a)) for all 128 cores. Even when some processors reach their minimum frequency, Figure 2.7(a) shows that its average frequency decreases more slowly than any other application, and does not fall as far. The difference in the average frequency and the minimum frequency explains the difference between TempLDB and naive DVFS, as the execution time for TempLDB is dependent on average frequency whereas the execution time for naive DVFS depends on the minimum frequency at which any core is Another way to understand the relatively small timing penalty of Jacobi2D is running. to compare its utilization and frequency profiles. Figure 2.8(a) depicts each core's average

Figure 2.4: Execution timing penalty with and without Temperature Aware Load Balancing

Figure 2.5: Execution timelines before and after Temperature Aware Load Balancing for Wave2D

frequency over the course of the run. Figure 2.9(a) shows the utilization of each core while running Jacobi2D. In both figures, each bar represents the measurement of a single core. The green part of the utilization bars represents computation and the white part represents idle time. As can be seen, utilizations of the right half cores are roughly higher than the left half. Furthermore, the average frequency of the right half processors is roughly lower than the other half. Thus, lower frequency has resulted in higher utilization of those processors without much timing penalty. The reason this variation can occur is that the application naturally has some slack time in each iteration, which the slower processors dip into to keep pace with faster ones.

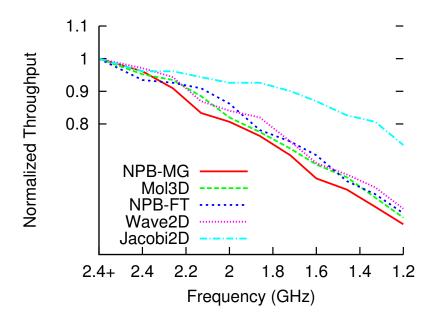

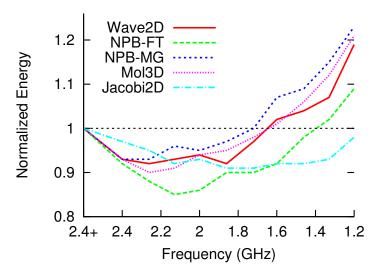

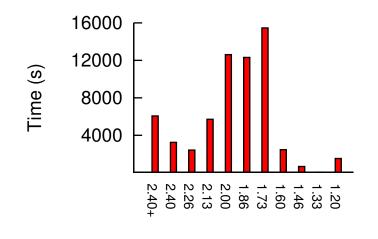

To examine the differences among applications at another level, Figure 2.10 shows the performance impact of running each application with the processor frequencies fixed at a particular value (the marking 2.4+ refers to the top frequency plus Turbo Boost). All applications slow down as CPU frequency decreases. However, Jacobi2D incurs the smallest timing penalty compared to other applications. This marked difference can be better understood in light of the performance counter-based measurements shown in Table 2.2.

Figure 2.6: Minimum core frequencies produced by DVFS for different applications at 24.4° C

Figure 2.7: Average core frequencies produced by DVFS for different applications at 24.4°  $\rm C$

| Counter Type         | Jacobi2D | Mol3D | Wave2D |

|----------------------|----------|-------|--------|

| MFLOP/s              | 373      | 666   | 832    |

| Traffic L1-L2 (MB/s) | 762      | 1017  | 601    |

| Cache misses to DRAM | 663      | 75    | 402    |

| (millions)           |          |       |        |

Table 2.2: Performance counters for Charm++ applications on one core

Figure 2.8: Average frequency of processors for Jacobi2D using *TempLDB*

Figure 2.9: Utilization of processors for Jacobi2D using TempLDB

measurements were taken in equal-length runs of the three Charm++ applications using the PerfSuite toolkit [35]. Jacobi2D has a much lower computational intensity, in terms of FLOP/s, than the other applications. It also retrieves much more data from main memory, explaining its lower sensitivity to frequency shifts. Its lower intensity also means that it consumes less power and dissipates less heat in the CPU cores than the other applications, explaining its slower ramp-up in temperature, slower ramp-down in frequency, and higher steady-state average frequency. In contrast, the higher FLOP counts and cache access rates of Wave2D and Mol3D explain their high frequency sensitivity, rapid core heating, lower steady-state frequency, and hence the large impact DVFS has on their performance.

Figure 2.10: Frequency sensitivity of the various applications

# 2.7 Energy Savings

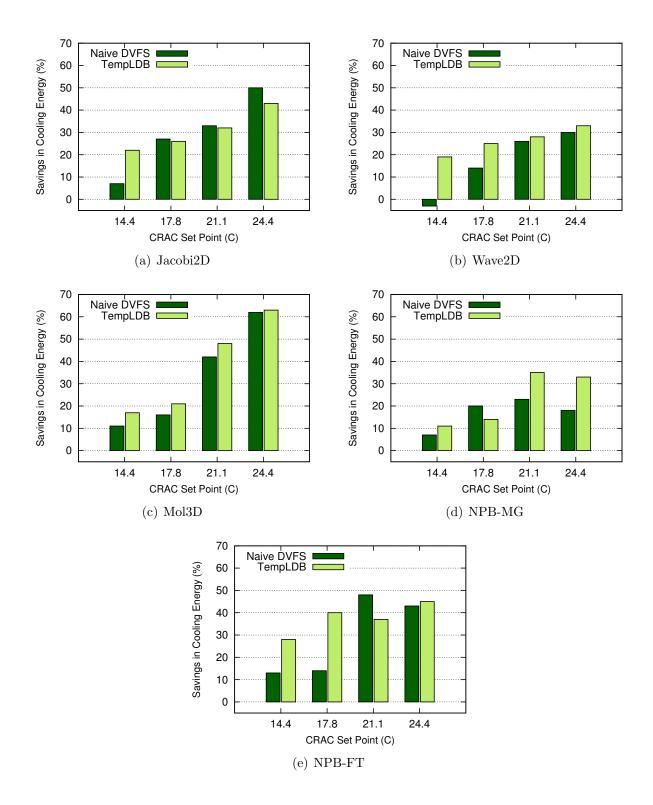

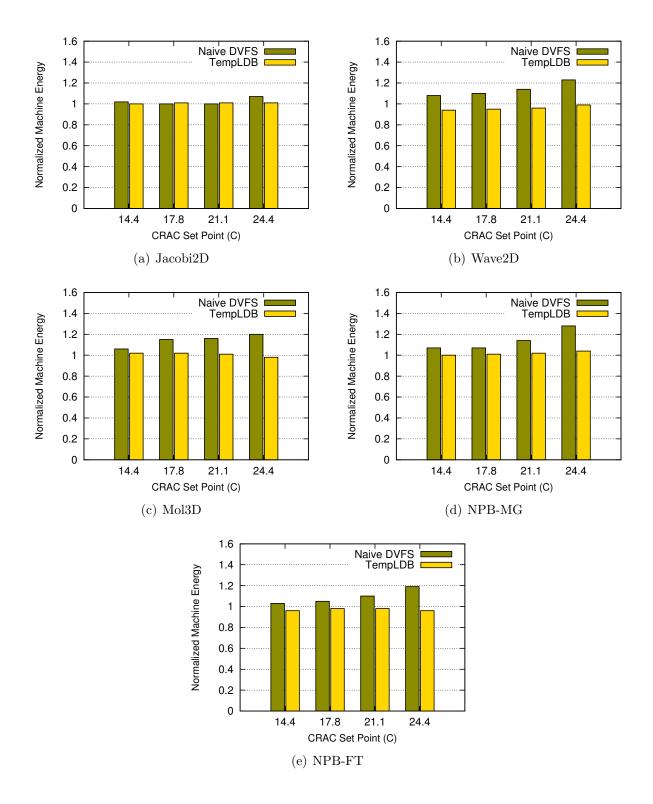

In this section, we evaluate the ability of our scheme to reduce *total* energy consumption. Our current load balancing scheme with the allowed temperature range strategy resulted in less than 1% time overhead for applying DVFS and load balancing (including the cost of object migration). Due to that change, we now get savings in both cooling energy consumption as well as machine energy consumption, although savings in cooling energy consumption constitute the main part of the reduction in total energy consumption. In order to understand the contribution for both cooling energy consumption and machine energy consumption, we look at them separately.

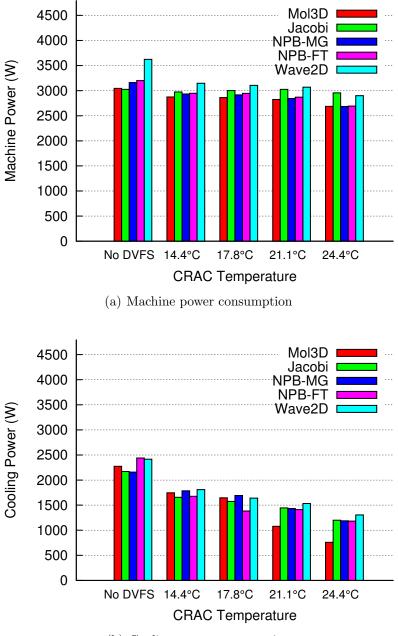

## 2.7.1 Cooling energy consumption

The essence of our work is to reduce cooling energy consumption by constraining core temperatures and avoiding hot spots. As outlined in Equation 2.1, the cooling power consumed by the air conditioning unit is proportional to the difference between the hot air and cold air temperatures going in and out of the CRAC respectively. As mentioned in earlier work [4–6], cooling cost can be as high as 50% of the total energy budget of the data center. However, in our calculation, we take it to be 40% of the total energy consumption of a baseline run with the CRAC at its lowest set-point, which is equivalent to 66.6% of the measured machine energy during that run. Hence, we use the following formula to estimate the cooling power by feeding in actual experimental results for hot and cold air temperatures:

$$P_{cool}^{LB} = \frac{2 * (T_{hot}^{LB} - T_{ac}^{LB}) * P_{machine}^{base}}{3 * (T_{hot}^{base} - T_{ac}^{base})}$$

(2.2)