Università di Pisa

DIPARTIMENTO DI INGEGNERIA DELL'INFORMAZIONE Laurea Magistrale in Ingegneria Informatica

### Exploiting Partial Dynamic Reconfiguration for On-Line On-Demand Detection of Permanent Faults in SRAM-based FPGAs

Master's Thesis

Supervisors: Prof. Cinzia BERNARDESCHI Prof. Andrea DOMENICI

> Candidate Domenico SORRENTI

Academic Year 2012/2013

### Acknowledgements

I would like to thank those who have helped me during the development of this thesis, making it clear that I take the blame for each mistake, which could be found in this work.

First of all, thanks to my supervisors Prof. Cinzia Bernardeschi and Prof. Andrea Domenici for their support and valuable advice.

I thank the Cognitronics and Sensor Systems Group for allowing me to develop my thesis and join the group, in particular Prof. Mario Porrmann, Dario Cozzi, Jens Hagemeyer and Sebastian Korf for their continuing help and useful suggestions.

I would like to thank Luca Cassano for his constant assistance before, during and after my visiting period in Germany.

I also thank Lydia Ntokou, Anna Isakova and Luca Santangelo for keeping me company during my period in Germany.

Finally, I would like to thank my family, Laura and her family for their support. This work is dedicated to them.

### Contents

| In       | trod | uction                                                    | i  |

|----------|------|-----------------------------------------------------------|----|

| 1        | Bac  | kground                                                   | 1  |

|          | 1.1  | Field Programmable Gate Array                             | 1  |

|          |      | 1.1.1 FPGA Architecture                                   | 2  |

|          |      | 1.1.2 Programming an FPGA                                 | 6  |

|          |      | 1.1.3 Configuring an FPGA                                 | 7  |

|          |      | 1.1.4 FPGA testing                                        | 15 |

|          |      | 1.1.5 Testing approaches: External and Built-in-Self-Test | 23 |

|          | 1.2  | Xilinx Description Language                               | 27 |

|          |      | 1.2.1 DHHarMa                                             | 27 |

|          | 1.3  | Dynamically Reconfigurable Processing Module (DRPM)       | 28 |

|          |      | 1.3.1 RAPTOR-X64                                          | 28 |

|          |      | 1.3.2 DB-V4                                               | 28 |

|          |      | 1.3.3 DB-SPACE                                            | 30 |

|          | 1.4  | Thesis Statement                                          | 32 |

| <b>2</b> | Rel  | ated Work                                                 | 34 |

|          | 2.1  | Introduction                                              | 34 |

|          | 2.2  | Logical resources testing                                 | 34 |

|          | 2.3  | Routing resources testing                                 | 35 |

|          | 2.4  | The proposed approach                                     | 35 |

| 3        | Tes  | ting Circuits                                             | 37 |

|          | 3.1  | Introduction                                              | 37 |

|          |      | 3.1.1 Test Pattern Generator                              | 38 |

|          |      | 3.1.2 Output Response Analyzer                            | 38 |

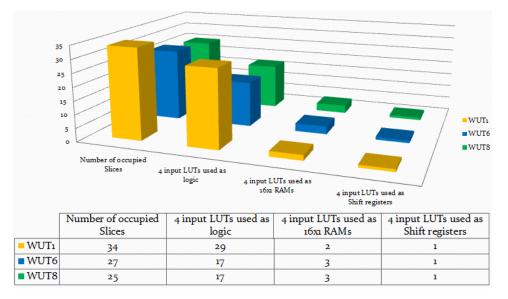

|          | 3.2  | 6WUTs and 8WUTs testing circuits                          | 39 |

|          |      | 3.2.1 6WUTs and 8WUTs planning                            | 40 |

|          |      | 3.2.2 6WUTs implementation                                | 42 |

|          |      | 3.2.3 8WUTs implementation                                | 45 |

|          |      | 3.2.4 Auxiliary logic                                     | 47 |

|          | 3.3  | 1WUT planning                                             | 52 |

| 55          |

|-------------|

| 60          |

| 60          |

| 60          |

| 62          |

| 64          |

| 65          |

| 66          |

| 67          |

| 67          |

| 68          |

| 70          |

| 71          |

| 73          |

| 73          |

| 73          |

| 75          |

| ·<br>·<br>· |

# List of Figures

| FPGA common architecture                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtex-4 CLB                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Virtex-4 Slice L part G                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A configuration bit determines the state of a PIP | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Cross Point PIP                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Break Point PIP                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Multiplexer PIP                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Compound PIP                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Xilinx design implementation                      | $\overline{7}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

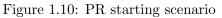

| PR starting scenario                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

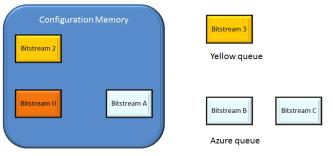

| PR bitstream 1 replacing                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

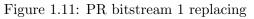

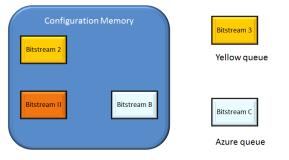

| PR bitstream A replacing                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Full bitstream example                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Frame address format                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FAR Top/Bottom                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FAR Row Address                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FAR Column Address                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FAR Minor Address                                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Failure rate: bathtub curve                       | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Effect propagation chain                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Switch matrix with no faulty PIPs                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Open PIP case 1                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Open PIP case 2                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Conflict PIP                                      | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

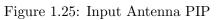

| Input Antenna PIP                                 | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

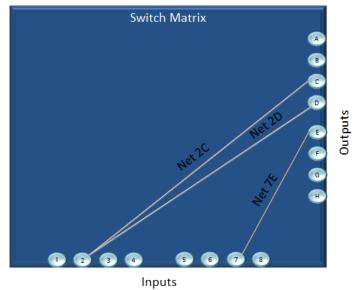

| Output Antenna PIP                                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bridge PIP                                        | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BIST approach scheme                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Comparison-Based BIST approach                    | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Parity-Based BIST approach                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cross-Couple Parity BIST approach                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

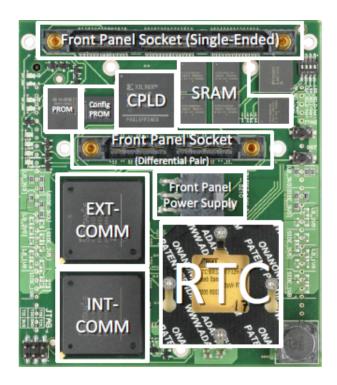

| The RAPTOR-X64 baseboard                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The DB-V4 daughterboard                           | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                   | Virtex-4 CLBVirtex-4 Slice L part GA configuration bit determines the state of a PIPCross Point PIPBreak Point PIPMultiplexer PIPCompound PIPCompound PIPXilinx design implementationPR starting scenarioPR bitstream 1 replacingPR bitstream A replacingFull bitstream exampleFrame address formatFAR Top/BottomFAR Row AddressFAR Column AddressFallure rate: bathtub curveEffect propagation chainSwitch matrix with no faulty PIPsOpen PIP case 1Output Antenna PIPOutput Antenna PIPBridge PIPBitsT approachComparison-Based BIST approachCross-Couple Parity BIST approachThe RAPTOR-X64 baseboard |

| 1.34       | The PR-FPGA module                                                                                              | 30 |

|------------|-----------------------------------------------------------------------------------------------------------------|----|

| 1.35       | The DB-SPACE daughterboard                                                                                      | 31 |

| 1.36       | Example of interaction between Leon2-FT and MicroBlaze                                                          |    |

|            | processors without fault detection                                                                              | 33 |

| 1.37       | Example of interaction between Leon2-FT and MicroBlaze                                                          |    |

|            |                                                                                                                 | 33 |

|            |                                                                                                                 |    |

| 3.1        | I                                                                                                               | 41 |

| 3.2        | I I I I I I I I I I I I I I I I I I I                                                                           | 41 |

| 3.3        |                                                                                                                 | 42 |

| 3.4        |                                                                                                                 | 43 |

| 3.5        |                                                                                                                 | 43 |

| 3.6        | I V V                                                                                                           | 44 |

| 3.7        | The second se | 45 |

| 3.8        |                                                                                                                 | 45 |

| 3.9        |                                                                                                                 | 46 |

|            |                                                                                                                 | 46 |

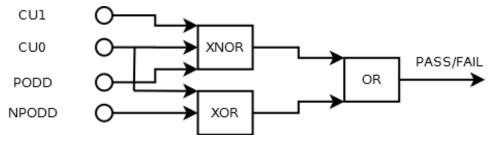

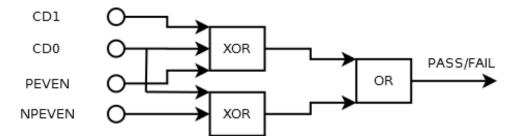

| 3.11       | 8WUTs EVEN parity ORA                                                                                           | 47 |

|            | - · · · · · · · · · · · · · · · · · · ·                                                                         | 47 |

|            | - 8                                                                                                             | 47 |

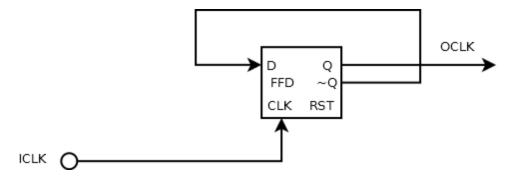

| 3.14       | Frequency divider element                                                                                       | 48 |

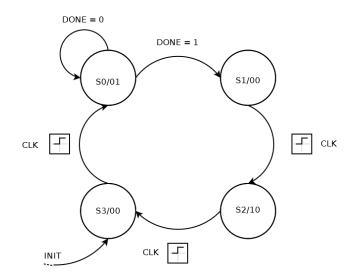

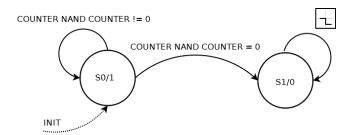

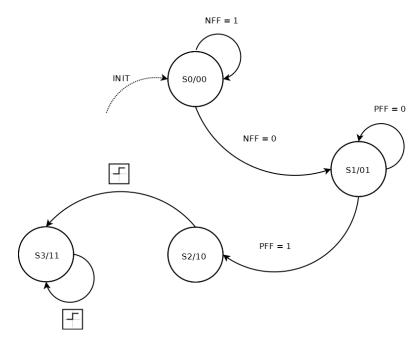

| 3.15       | TPG_SU state transition diagram                                                                                 | 49 |

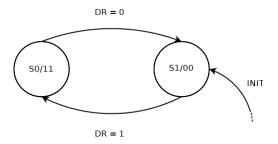

| 3.16       | ORA_SU state transition diagram                                                                                 | 49 |

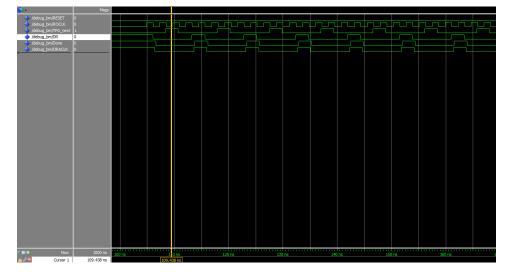

| 3.17       | FSMs ModelSim simulation                                                                                        | 50 |

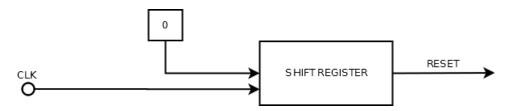

| 3.18       | Reset generator circuit                                                                                         | 50 |

|            | 1                                                                                                               | 52 |

| 3.20       |                                                                                                                 | 52 |

| 3.21       |                                                                                                                 | 53 |

| 3.22       |                                                                                                                 | 54 |

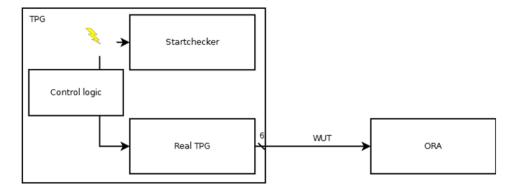

| 3.23       | 1WUT high level "CLK Approach" scheme                                                                           | 55 |

|            |                                                                                                                 | 56 |

|            | 0                                                                                                               | 56 |

|            |                                                                                                                 | 57 |

| 3.27       | 1WUT "CLK Approach" ORA                                                                                         | 57 |

| 3.28       | 1WUT "CLK Approach" ORACU                                                                                       | 58 |

| 3.29       | 1WUT OCU state transitions diagram                                                                              | 59 |

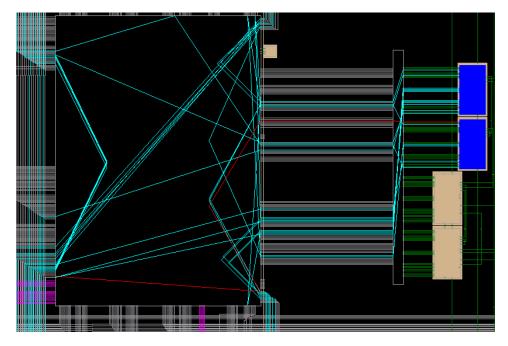

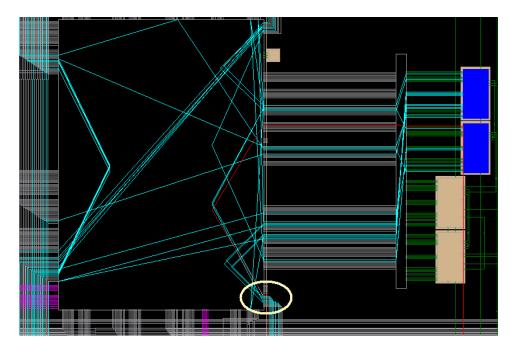

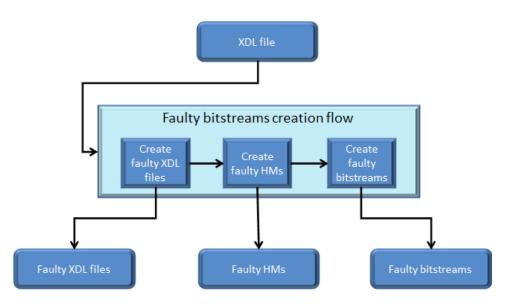

| 4.1        | No faulty bitstream                                                                                             | 61 |

| 4.2        | •                                                                                                               | 61 |

| 4.3        |                                                                                                                 | 62 |

| 4.4        |                                                                                                                 | 63 |

| 4.5        |                                                                                                                 | 64 |

| 4.6        |                                                                                                                 | 64 |

| 4.0<br>4.7 |                                                                                                                 | 66 |

| 1.1        |                                                                                                                 | 50 |

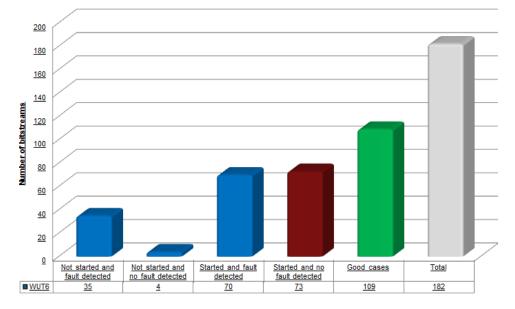

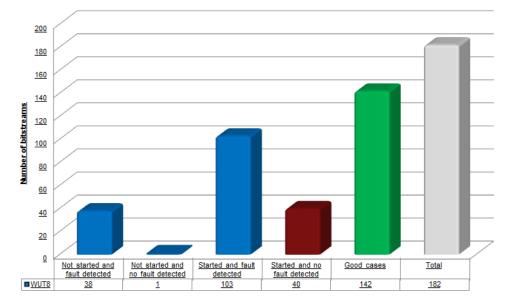

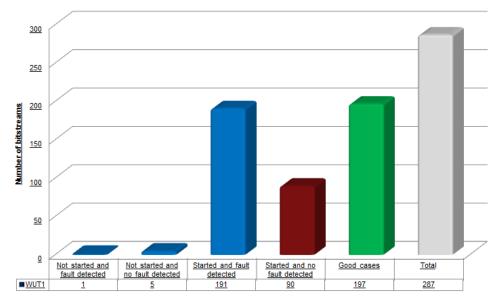

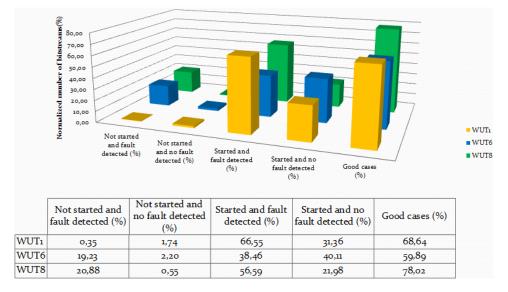

| 4.8  | 8WUTs verification results                 |

|------|--------------------------------------------|

| 4.9  | 1WUT verification results                  |

| 4.10 | Verification results                       |

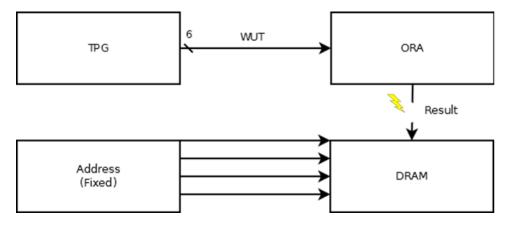

| 4.11 | Not started and no fault detected scenario |

| 4.12 | Bad cases: masking faults case             |

| 4.13 | Undetectable fault on addressing wires     |

| 4.14 | HMs sizes summary 70                       |

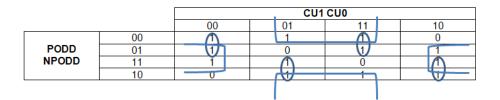

| 1    | ODD parity ORA Karnaugh's map              |

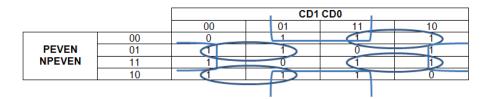

| 2    | EVEN parity ORA Karnaugh's map             |

## List of Tables

| 1.1              | Bitstream lengths                                                                                                                            | 10                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.1              | TPG signals configurations                                                                                                                   | 38                   |

| 3.2              | ORA expected configurations                                                                                                                  | 39                   |

| 3.3              | 8WTUs TPG signals configurations                                                                                                             | 39                   |

| 3.4              | 8WTUs ORA expected configurations                                                                                                            | 40                   |

| 3.5              | Result configurations                                                                                                                        | 51                   |

| 3.6              |                                                                                                                                              | 57                   |

| 1                | ODD parity ORA truth table                                                                                                                   | 73                   |

| T                |                                                                                                                                              | 10                   |

| 2                |                                                                                                                                              | 73<br>74             |

|                  | ODD parity ORA proof table 1                                                                                                                 |                      |

| 2                | ODD parity ORA proof table 1ODD parity ORA proof table 2                                                                                     | 74                   |

| $2 \\ 3$         | ODD parity ORA proof table 1                                                                                                                 | 74<br>74             |

| 2<br>3<br>4      | ODD parity ORA proof table 1                                                                                                                 | 74<br>74<br>75       |

| 2<br>3<br>4<br>5 | ODD parity ORA proof table 1ODD parity ORA proof table 2ODD parity ORA proof table 3EVEN parity ORA truth tableEVEN parity ORA proof table 1 | 74<br>74<br>75<br>75 |

### Abstract

FPGAs become ever more popular thanks to their features, such as reconfigurability and short time to market. When FPGAs operate in harsh environments, like in space, soft faults can occur (SEU) due to radiation, as well as permanent faults (TID, Aging). Testing of logic resources has already been widely considered in literature, on the other hand this work aims at detecting permanent faults which can affect the interconnection infrastructure. In modern FPGAs the routing resources represent up to 80% of the whole chip area. Few works consider permanent faults and none of them deals with on-line testing of permanent faults with independent test circuits. In this work a first approach is presented, where different circuits have been developed and tested on a DB-V4 daughterboard of the RAPTOR prototyping system.

### Introduction

FPGAs are increasingly being used in safety-related and critical applications, for this reason testing of these devices is gaining importance. Unfortunately, existing testing techniques developed for other devices, such as ASICs, are not adequate, therefore new techniques have been and are still being developed.

Around twenty years ago, permanent faults were the main problem, then with the transistors industry progress, that is smaller transistors, they have lost importance with respect to transient ones. Nowadays, the new devices employ small transistors, but in a really high number, and hence permanent faults are gaining importance again. Testing the interconnection infrastructure, which in modern devices can reach up to 80% of the chip area, is gaining importance although many works are focused only upon logical resources. Sometimes it is the application or the operating environment that requires fault detection, for example, the Adaptive Computing Systems (ACSes) rely on reconfigurable hardware for adapting the system to changes of the external environment, exploiting hardware sharing, to increase the functional density and reduce power consumption, and reusing modules for different applications. Where a direct human intervention is not possible, such as in space, fault detection and fault tolerance mechanisms are essential. Various fault tolerance techniques exist, but these are not always suitable, for example, redundancy and voting algorithms are expensive in terms of space, weight and power for these systems, which are typically subject to strict constraints.

The goal of this work is to conceive, develop and verify a mechanism which permits permanent faults in routing resources of FPGAs to be detected. The thesis is organized as follows:

- 1. **Background** (Chapter 1), which provides a brief description about FPGAs, architecture and configuration, the more common testing approaches, the Xilinx Description Language and the Dynamically Reconfigurable Processing Module;

- 2. **Related Work** (Chapter 2), which reports some works associated to FPGA testing;

- 3. **Testing Circuits** (Chapter 3), in which the developed mechanism is shown in detail;

- 4. **Testing Circuits Verification** (Chapter 4), in which the developed mechanism is verified and related results are shown;

- 5. Conclusions and Future Work (Chapter 5), in which final remarks and possible improvements are reported.

### Chapter 1

### Background

#### 1.1 Field Programmable Gate Array

Field Programmable Gate Arrays (FPGAs) are integrated circuits, which feature the capability to be reconfigured via software more times; as consequence of this flexibility, these devices present some advantages with respect to other technologies, such as ASICs (Application Specific Integrated Circuits).

ASICs require high investments during the design phase, in particular about non-recurring expenses (NRE), whereas FPGA functionalities are not fixed by the vendor, which can fabricate them in large scale lowering the price. Then end users can adapt an FPGA to their own need by means of a configuration. This leads to a sizeable decrease of the TTM (Time To Market), which is quite important from an economic point of view. But probably the most important advantage with respect to ASICs is the possibility to correct errors without further costs and any time. Thanks to this feature FPGAs were initially largely used for prototyping and exactly this represents the reason of the starting diffusion of these devices.

There are also some disadvantages, such as a higher cost for unit in high volume designs and a bigger size with respect to ASICs, which are realized custom. In particular, FPGAs can take up an area 10 times bigger and be at least 3 times slower than ASICs, the latter aspect is the consequence of replacing metal tracks (ASICs) with programmable blocks containing active elements (FPGAs), which introduce propagation delay. A more complete treatise can be found in [1].

Another possible comparison is with general purpose processors, which feature a high flexibility like FPGAs, but they have typically a higher power consumption and a lower elaboration time. For further information see [2]. With time passing FPGAs cost is decreasing, whereas their performance is increasing, therefore nowadays FPGAs can be used for digital signal processing, hardware acceleration, cryptography and so on; because of their flexibility they are suitable for several fields of application.

#### 1.1.1 FPGA Architecture

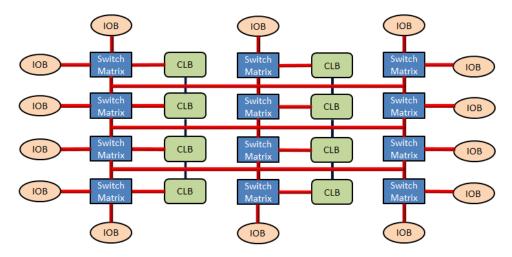

In this section a brief description about FPGA architecture is given. FPGA architecture is vendor dependent, but the most common consists in a matrix of configurable logic blocks (CLBs) connected through a routing infrastructure.

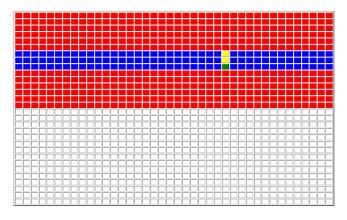

An FPGA is made of three essential blocks (Figure 1.1):

- CLB, in which the logic functions are implemented;

- Input-Output Block (IOB), which represents connection with outside;

- Switch matrix (INT), by which is possible to drive signals inside an FPGA. Routing is obtained by means of Programmable Interconnection Points (PIPs), which are CMOS transistors that can be activated and deactivated in order to get a custom path within a switch matrix. Switch matrices are linked together by fixed wires.

Figure 1.1: FPGA common architecture

**CLB** The CLB structure depends on vendors and FPGA families, for example a Xilinx Virtex-4 CLB consists of 4 slices (Figure 1.2), whereas in a Virtex-5 CLB there are 2 slices.

Figure 1.2: Virtex-4 CLB

Focusing on Virtex-4, a slice is split in part F and G. Each part consists, from a simplified viewpoint, in a 4-input Look Up Table (LUT) and a Flip-Flop (FF). There are two types of slice:

- Slice L (Figure 1.3);

- Slice M.

Figure 1.3: Virtex-4 Slice L part G

In a slice M, LUTs can operate as a ROM, shift register or distributed RAM.

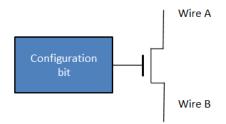

**PIP** Regarding an FPGA architecture the programmable routing infrastructure consists of a set of wire segments, which can be interconnected

by means of programmable elements: PIPs. A PIP is a switched element, whose state is determined by the value contained in a configuration cell (see Figure 1.4).

Figure 1.4: A configuration bit determines the state of a PIP

Several types of PIPs are used:

- Cross Point PIP (Figure 1.5), which connects wire segments placed in different plans, that is a horizontal segment with a vertical one or vice versa;

- Break Point PIP (Figure 1.6), which connects wire segments placed in a same plan, that is two horizontal or vertical segments;

- Multiplexer PIP (Figure 1.7), which in turn is split in:

- **Decoded multiplexer**, which is made of  $2^k$  Cross Point PIPs connected to a common output wire segment. It is driven by k configuration bits;

- Non-Decoded multiplexer, which differs from a Decoded one because it consists of a single configuration bit for each CMOS transistor, in other words k wire segments are controlled by k configuration bits.

- **Compound PIP** (Figure 1.8), which is made of four Cross Point and two Break Point PIPs.

For further information see [3].

Figure 1.5: Cross Point PIP

$\bigcirc$

\_

Figure 1.7: Multiplexer PIP

Figure 1.8: Compound PIP

#### 1.1.2 Programming an FPGA

FPGAs are programmable devices, for this reason their behaviour has to be defined by the end user, which can do that by means of either a hardware description language (HDL) or a schematic design. The former should be preferred when the design is rather big and the most used HDLs are Verilog and VHDL.

By the time in which the behaviour has been defined, using a design automation tool, typically supplied free of charge by vendors, a technology-mapped netlist is generated. A netlist is a textual description of a circuit diagram, which provides a map of how its elements are interconnected. Then a process, called Place-and-Route, can be performed in order to adapt a netlist to an actual FPGA architecture. On the result of the previous process, several verification methodologies, such as timing analysis and simulation, can be performed. Once that the result is verified, a binary file, called bitstream, is generated and loaded into the device in order to configure or reconfigure it.

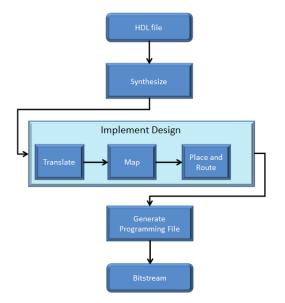

In Xilinx language *design implementation* is the process of translating, mapping, placing, routing and generating a bitstream file for a given design. All these tools are included and integrated in the Xilinx® ISE® Design Suite.

Figure 1.9 depicts the whole flow:

- the HDL file represents the input;

- **Synthesize**, which generates a supported netlist type (EDIF or NGC) for the Xilinx implementation tools;

- **Implement design**, which is made of:

- Translate, which converts input design netlists and creates a single NGD netlist;

- Map, which maps the design into CLBs and IOBs;

- Place and Route, which places the design and calculates routes for the nets.

- Generate Programming File, which generates the bitstream which is loaded into the device.

For further information about the Xilinx design automation tool see [4].

Figure 1.9: Xilinx design implementation

#### 1.1.3 Configuring an FPGA

Once that a bitstream is ready, it has to be loaded into a device. This section presents how a bitstream can be loaded and in which way an FPGA can be reconfigured, as well as a short description about the configuration memory and the bitstream format.

#### Partial reconfiguration

FPGAs feature a high flexibility due to the possibility to be reprogrammed via software; with the **Partial Reconfiguration** (PR) they have reached an even higher flexibility level, inasmuch as the PR permits to reconfigure a specified part of the device, without affecting the others.

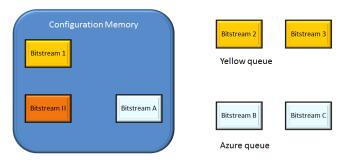

An example of how PR works is depicted in Figure 1.10, 1.11 and 1.12.

Figure 1.10 shows a scenario where there are three bitstreams in the configuration memory and two bitstream queues, which involve different parts of the device.

In Figure 1.11 the bitstream 1 has been replaced without affecting the part of the device where other bitstreams are currently operating.

Finally, in Figure 1.12 the bitstream A has been replaced with the bitstream B, without affecting other device parts.

**PR groups** Two groups of PR exist:

• **dynamic** PR, which permits to reconfigure some parts of the device, without disrupting applications which are currently operating on the

Figure 1.12: PR bitstream A replacing

rest of the device;

• **static** PR, in which, during a reconfiguration, the rest of the device is stopped until the reconfiguration has been accomplished.

**PR styles** There are two different styles of PR:

- module-based, where a modular design conceived for reconfiguring large logic blocks is used (for further information see [5]);

- **difference-based**, which is foreseen for dealing with small changes in a design.

Two different ways exist for obtaining these small changes:

- a *front-end approach*, where it is needed to re-synthesize and re-implement the design in order to get a NCD (Native Circuit Description) file and thence a partial bitstream, for instance, using Xilinx® ISE® Design Suite;

- a *back-end approach*, where changes are directly made with FPGA Editor, a Xilinx tool used for displaying and configuring FPGAs.

#### Why use the PR?

There are several benefits using a partial reconfiguration in place of a full one, such as:

**Application** A requirement of various applications is the capability to adapt their own behaviour on the basis of different events which can occur, in particular in the space or aerospace field, but not only. These changes could be, for instance, the adoption of a different protocol or algorithm, basing on collected or observed data. These applications were plainly not supported by previous architectures, for the reason that a full configuration is not suitable.

**Performance** The PR permits to reconfigure a specified part of the device, without affecting the others, that means that the system continues to operate without service interruption.

**Resource sharing** The PR allows more applications to run at the same time on a single device and hence this leads to a better utilization of hardware resources, and therefrom a reducing power consumption and decreasing cost.

**Configuration time** Although it could seem an almost worthless benefit, with the possibility of loading only a partial bitstream, therefore reprogramming only a part of the device, in contrast to a full bitstream, which reconfigures the whole device, the configuration time has undergone a sizeable lowering. Table 1.1 reports the length of some full bitstreams, related to the Virtex devices, and it notes that a full reconfiguration can take a considerable amount of time to be performed.

| Family   | Device    | Size(MiB) |

|----------|-----------|-----------|

| Virtex-4 | XC4VFX100 | 3.94      |

| Virtex-5 | LX330T    | 9.86      |

| Virtex-6 | XC6VLX760 | 22.03     |

| Virtex-7 | 7V2000T   | 53.33     |

Table 1.1: Bitstream lengths

#### How perform a partial reconfiguration?

There are four interfaces which can be used for loading a bitstream:

- 1. Serial interface;

- 2. SelectMAP interface;

- 3. ICAP interface;

- 4. JTAG interface.

Some information about these interfaces are here reported, for full details see [6].

**Serial interface** With the use of this interface an FPGA is configured by loading one configuration bit for each CLK cycle.

**SelectMap interface** This interface provides a bidirectional 8, 16 and 32bit bus and can be used both for configuration and readback, that is the process of reading back data from an FPGA, initially conceived to verify whether the design was loaded properly.

**ICAP interface** The Internal Configuration Access Port (ICAP) permits the access to the configuration data in a way similar to the SelectMap interface. It can be used to perform both PR and readback operation, but not a full configuration.

**JTAG interface** The use of this interface was standardized by IEEE in 1990 (IEEE 1149.1 standard) and the Virtex-families are fully compliant with it.

#### **Configuration Memory Architecture Overview**

The configuration memory in Virtex-4 FPGA is frame-based, that is it is arranged in frames. With respect to the previous Virtex families, these frames have a fixed length: 41 words (for further information [7], [8]).

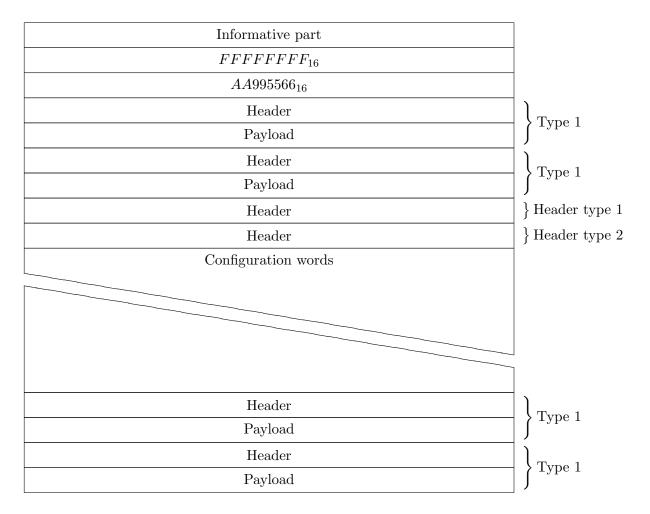

**Bitstream structure overview** A full bitstream may be thought as made of five parts:

- an informative part, with information such as design name, generating time and so on;

- a dummy word  $FFFFFFF_{16}$  and a synchronize word  $AA995566_{16}$ , for alignment issues;

- a sequence of packets, each one consists of a header and a payload;

- configuration words;

- another sequence of packets.

An example of full bitstream is exhibited in Figure 1.13.

Figure 1.13: Full bitstream example

**Packets** The packet header specifies what operation has to be performed, the address of the register in which to write and the word count, that is the number of data words which follow the header and that have to be written in a specified register. There are two packet types: *type 1* and *type 2*. The former is far more common than the second one, indeed the latter has been created only to bypass the case in which the number of words, which are specified in the word count field in the packet 1's header, are too much with respect to the field size. In this particular case a packet 2 is used, which has not an address field in his header, but only the word count field, whereas the address has to be specified by a previous packet 1 with count word field equals to 0. In other words, a packet 2 is always preceded by a packet 1.

**Configuration registers** Some fundamental registers, which are involved during the configuration process, are hereinafter reported.

- Cyclic Redundancy Check (CRC). Inside the bitstream there is a precalculated 16 bit checksum, if no disabled, which is written in the CRC register. The configuration logic calculates the checksum during the configuration process and compares it with what is written in the CRC register. This option allows checking whether the transferring data succeeds or not, in this last case an error is signalled;

- **IPCODE**. In this particular register a word has to be written, which is unique for each device. The configuration logic compares the IPCODE's content with a hard-wired unique word and in case of mismatch an error is signalled;

- Frame Address Register (FAR). This register takes a fundamental role in loading the configuration frames, it represents the place where the address of the first frame is written. For a full bitstream this is always  $0_{16}$  and the configuration logic is in charge of incrementing it for every frame which is received.

#### Frame Address Format

The frame address, whose format is shown in Figure 1.14, is a 32 bit word and consists of several parts:

- 9 bits are not used;

- Top/Bottom (1 bit)

- Block Type (3 bits)

- Row Address (5 bits)

- Column Address (8 bits)

- Minor Address (6 bits)

| 31 | 30 | 29 | 28  | 27 | 26  | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10  | 9  | 8 | 7 | 6 | 5 | 4 | 3  | 2   | 1 | 0 |

|----|----|----|-----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|---|---|---|---|---|----|-----|---|---|

|    |    | N  | Jot | U  | Jse | d  |    |    | Т  | Т  | yp | e  |    | F  | lo | W  |    |    |    | С  | olı | ım | n |   |   |   | l | Mi | noi | r |   |

#### Figure 1.14: Frame address format

The various parts which make up a frame address are described below.

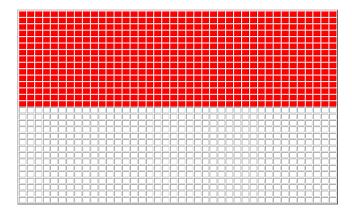

**Top/Bottom** Virtex-4 devices have been designed as separated in two halves: *top* and *down* half. When a full bitstream is loaded, the FAR address is written with  $0_{16}$ , which represents the upper-center and left-most column of the device. In Figure 1.15 the top half is selected with the top/bottom bit.

Figure 1.15: FAR Top/Bottom

**Block Type** This part of the address specifies what kind of resources will be configured by that frame. It can assume the following value:

- 000<sub>2</sub>: CLB, IO, DSP, CLK, MGT;

- 001<sub>2</sub>: block RAM interconnect;

- 010<sub>2</sub>: block RAM content;

- $011_2$ : it is reserved;

- $100_2$ : it is reserved;

- 101<sub>2</sub>: it is reserved;

- 110<sub>2</sub>: block RAM data integrity.

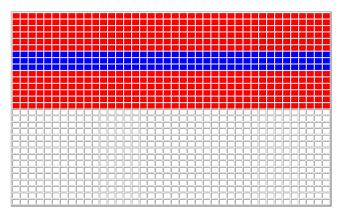

**Row Address** It is used to select a row of frames and has been introduced with the Virtex-4 family. Its number increases with the distance from the center of device, both in top and bottom half. In Figure 1.16 a row in the top half is selected with the row address.

**Column Address** This field selects one column of frames in the row which is specified by the Row Address field, obviously in the half of device which has been specified by the Top/Bottom field. It starts with  $0_2$  and is incremented moving toward right in the device. In Figure 1.17 one column in the row is selected with the column address.

Figure 1.16: FAR Row Address

Figure 1.17: FAR Column Address

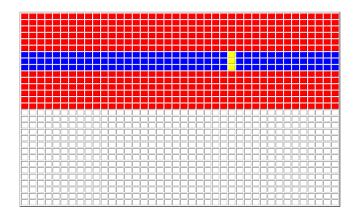

Minor Address It selects one frame inside a column of frames, in fact a frame represents the smallest addressable part in a device and a way for indicating directly a word within a frame does not exist. Finally, in Figure 1.18 one frame in the column is selected with the minor address.

#### 1.1.4 FPGA testing

FPGAs are suitable for many fields of application. In particular, the growing use of FPGAs in safety-critical systems requires that the system does not fail because of faults and that it features a gradual degradation of performance due to aging. Moreover nowadays the testing has acquired a lead role in the life cycle of these devices, due, again, to their increasing use in critical applications.

This section briefly introduces possible causes of faults, which can affect these devices, a first fault classification based on duration of their effect, and a description about faults which can occur in the PIPs of the interconnection

Figure 1.18: FAR Minor Address

infrastructure.

#### Fault causes

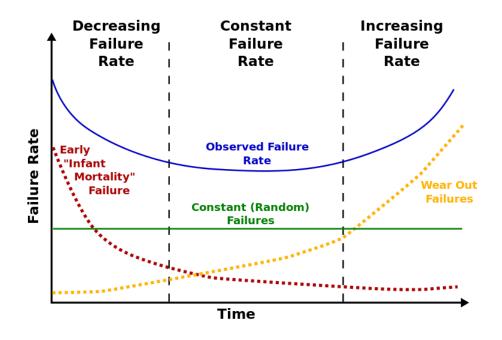

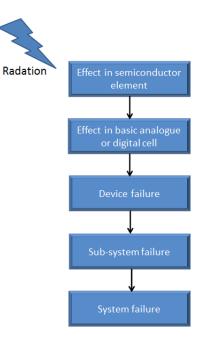

FPGAs are electronic devices and hence prone to an unavoidable aging of their own components, with a consequent degradation in terms of performance, which can lead to a failure. Figure 1.19 depicts the "bathtub" curve which is typically used for indicating the failure rate evolution with respect to time.

In addition, FPGAs can operate in harsh environments, for example in space, where radiations can affect the device causing even a failure. Figure 1.20 depicts how the radiation effect can propagate itself throughout the system and can lead to a failure.

Figure 1.19: Failure rate: bathtub curve

Figure 1.20: Effect propagation chain

#### Fault classification

An FPGA can be affected by:

- Single Event Upset (SEU), that is the effect of a particle on a memory element, such as a LUT or a register, which causes a change of the stored value;

- Total Ionizing Dose (TID), that is an accumulation of charge in the silicon injected by radiations; when the charge reaches a sizeable value, a transistor is not no longer able to switch between state on and off.

As SEU belongs to the *soft* error type [9], on the other hand, TID belongs to the *permanent* one. For a more complete classification see [3]. Some works on SEU and TID are here reported:

- SEU

- In [10] a prover of SEUs unexcitability based on a model checker tool is shown;

- In [11] an automatic test pattern generation tool for detection of SEUs is presented; it is based on the use of Genetic Algorithms (GAs);

- In [8] Xilinx proposes how dealing with SEU using a combination of PR and readback.

- TID

- In [12] a complete testing and diagnosing flow is proposed; it consists of several available tools.

#### PIPs behaviour in presence of fault

As previously said, a fault can affect the configuration memory, in particular a configuration bit which controls a PIP. Consequences can be different:

- Open;

- Conflict;

- Input Antenna;

- Output Antenna;

- Bridge;

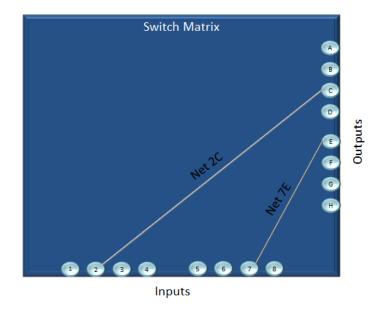

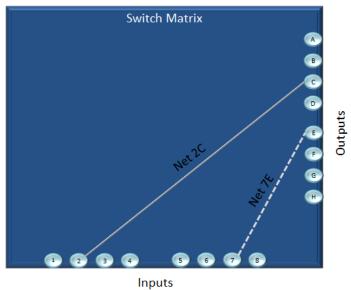

Figure 1.21 depicts a switch matrix, whose PIPs are not affected by faults.

Figure 1.21: Switch matrix with no faulty PIPs

**Open** There are two possible cases of open:

- Figure 1.22, where the net 7*E* is deleted, because the PIP is no longer programmed;

- Figure 1.23, where the net 7E is deleted and a new net, for example, 5E, between an unused input node 5 and the previously used ouput node E, is created.

Figure 1.22: Open PIP case 1

Figure 1.23: Open PIP case 2

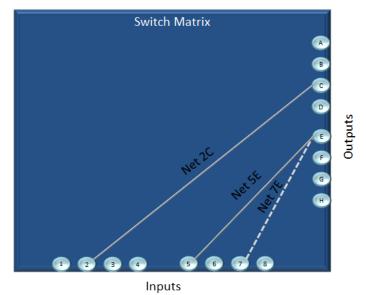

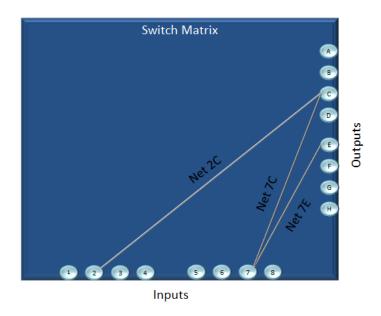

**Conflict** Figure 1.24, where a new PIP is added between two previously used input and output nodes (net 7C is created).

Figure 1.24: Conflict PIP

Antenna Two types of antenna are possible:

- Input: Figure 1.25, where a new PIP is programmed creating a new net, for example, 4C between an unused input node 4 and a used output node C;

- *Output*: Figure 1.26, where a new PIP is programmed creating a new net, for example, 2D between a used input node 2 and an unused output node D.

Inputs

Figure 1.26: Output Antenna PIP

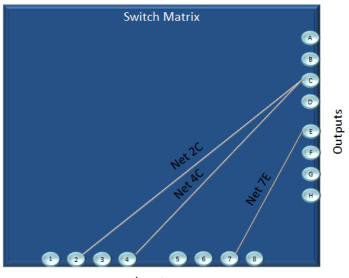

**Bridge** Figure 1.27, where the net 7E is deleted and a new net, for instance, 2E, between a used input node and the output node of the net 7E, is created.

Figure 1.27: Bridge PIP

For further information and more details see [3].

#### 1.1.5 Testing approaches: External and Built-in-Self-Test

There are various testing methodologies and they can be classified in two big families:

- Application-independent testing, in which the goal is to detect every structural defect because of the manufacturing process in the whole FPGA;

- **Application-dependent testing**, in which the aim is to detect defects only in resources actually used by the design.

In order to perform whatever test, the following items are needed:

- 1. a mechanism to provide a set of input stimuli;

- 2. a circuit under test (CUT);

- 3. a mechanism to analyse responses in order to discriminate whether the CUT is fault-free or not.

Amongst various methodologies the most common are the external and the **Built-in-Self-Test** (BIST) approach.

The former approach was the first utilized and consists in considering the circuit under test like a black box, providing input stimuli from outside the device through IOBs or JTAG interface, for example. Then responses are collected by means of IOBs or a readback and they are externally assessed. On the other hand, the BIST approach, which is currently the most utilized, allows a device to test itself without acting from outside. This approach is faster, simpler, inexpensive and does not require external test equipment, whereas its disadvantages are additional design requirements and area overhead. The advent of the PR has helped to diffuse the BIST approach, because it allows a device to test its own parts without disrupting applications which are currently running.

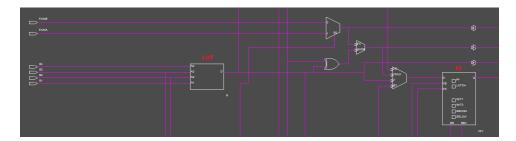

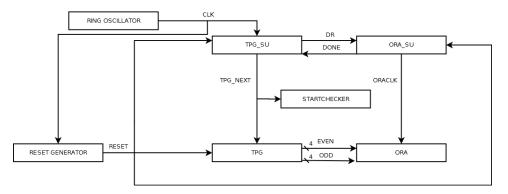

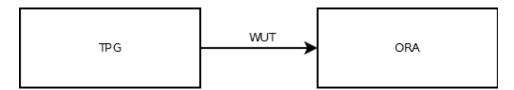

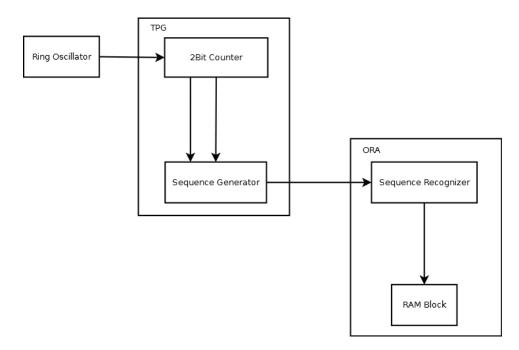

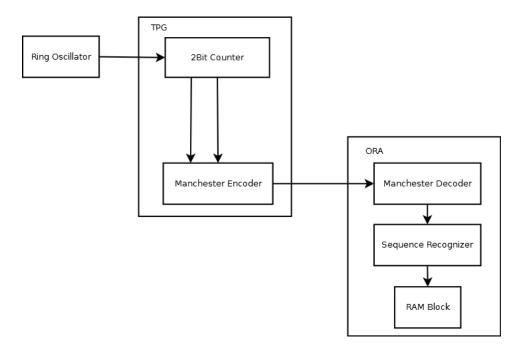

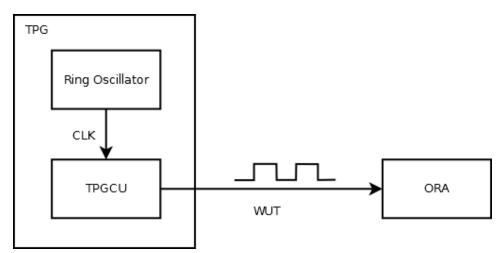

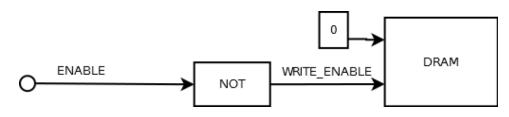

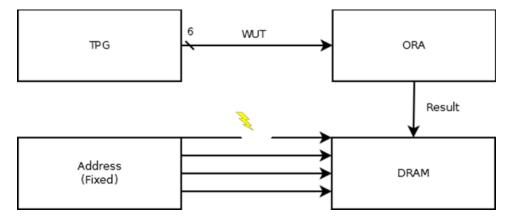

The idea on which the BIST approach is based is to configure some CLBs as **Test Patter Generator** (TPG), which is in charge of generating input stimuli, and some others as **Output Response Analyzer** (ORA), which is in charge of assessing responses of the CUT and giving a related result, that is whether the CUT is faulty or not. Figure 1.28 depicts a simple BIST scheme, where the CUT is represented by a **wire under test** (WUT). With the term wire a set of PIPs and physical wire segments is meant.

Figure 1.28: BIST approach scheme

In [13] the first BIST approach for testing the interconnection infrastructure in an FPGA is reported.

**BIST approach evolution** From its first definition the BIST approach is passed through various improvement steps:

- Comparison-Based;

- Parity-Based;

- Cross-Coupled Parity Based.

**Comparison-Based** This was the initial stage, in which the name derives from the fact that the ORA compares responses received on the WUTs. It represents the most simple BIST approach, where the TPG generates identical signals on the WUTs, which are received by the ORA. A problem with this approach is that equivalent faults (that is faults with the same effects) are not detected. In addition, if, for example, the TPG is faulty and provides same signals on the WUTs, the ORA is not able to detect the fault. Figure 1.29 depicts the Comparison-Based approach with two WUTs.

Figure 1.29: Comparison-Based BIST approach

**Parity-Based** This version was introduced for the first time in [14]. It consists in realizing the TPG with a n-bit counter, therefore the input stimuli are  $2^n$ , and using a parity bit, which is transmitted on fault-free routing resources. This version is affected by the fact that if the parity remains correct even in presence of a fault (for example if the TPG is frozen to a fixed input), the fault is not detected by the ORA. With respect to the Comparison-Based approach, now the ORA is able to detect equivalent faults on the WUTs, and sometimes if the TPG is faulty, this can be detected through a readback of the state of the counter. Figure 1.30 depicts the Parity-Based approach with two WUTs and the parity bit.

Figure 1.30: Parity-Based BIST approach

**Cross-Coupled Parity Based** This version is the most recent, it aims to outdo the too rigid constraint of transmitting the parity on fault-free

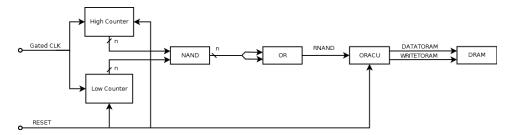

routing resources. It is realized through the use of two n-bit counters, which compose the TPG, whose parity bits are exchanged and sent to two different ORAs (see Figure 1.31); in this way if a TPG is faulty the ORA is able to detect the fault, without needing to resort to a readback of the state of the counters. It was proposed in [15] for Virtex-4 devices.

Figure 1.31: Cross-Couple Parity BIST approach

## **1.2** Xilinx Description Language

The Xilinx Description Language (XDL) is a human-readable format compatible with the more known and used Netlist Circuit Description (NCD). Both these languages have been created by Xilinx for describing and representing FPGA designs.

With the XDL it is possible to obtain a full description about:

- 1. the available resources in an FPGA. This report can occupy from a few MiBs (smaller or older devices) up to several GiBs (newer devices);

- 2. FPGA netlists, such as complete systems, hard macros or modules.

Notwithstanding the same language is used for both cases, descriptions differ in both syntax and structure [16].

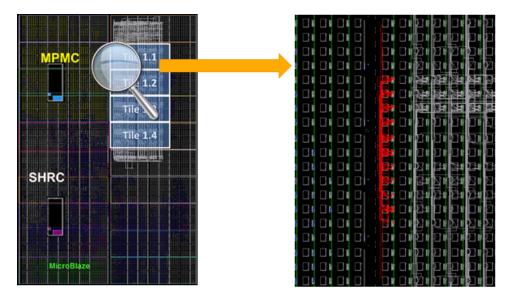

What is a hard macro? A hard macro is a pre-placed and pre-routed design block. If a hard macro is moved along an FPGA, all its elements maintain the same position within it.

#### 1.2.1 DHHarMa

DHHarMa[17] is a software flow which exploits the XDL, in particular it can be used for the automatic generation of homogeneous HMs and it offers the possibility to constrain both placing and routing phases.

## 1.3 Dynamically Reconfigurable Processing Module (DRPM)

The project in [18], under ESA contract, is aimed at designing, developing and validating a DRPM demonstrator. The system updates and adapts its functionalities through a dynamically exchange of processing modules at run-time. Because of the harsh environment in which the system operates, that is in space, particular attention was paid about mitigation of radiations and recovery mechanisms in case of failure. The DRPM is particular indicated for space mission in which there is the need to adapt data processing algorithms basing on the collected data.

The DRPM consists in three fundamental components:

- **RAPTOR-X64** baseboard;

- **DB-V4** daughterboard;

- **DB-SPACE** daughterboard.

## 1.3.1 RAPTOR-X64

It is a rapid prototyping system based on a modular approach: the base system provides the communication infrastructure and some management facilities, which can be used by various extension modules. Figure 1.32 depicts the RAPTOR-X64 baseboard.

Figure 1.32: The RAPTOR-X64 baseboard

## 1.3.2 DB-V4

It is a RAPTOR-X64 extension module and hosts:

• Xilinx Virtex-4 FX100 FPGA;

## • 4 GiB DDR2 RAM.

Figure 1.33 depicts the DB-V4 daughterboard.

Figure 1.33: The DB-V4 daughterboard

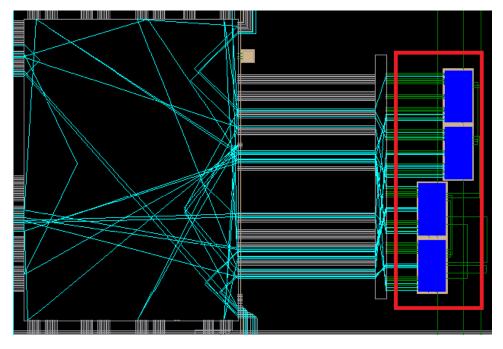

### **PR-FPGA**

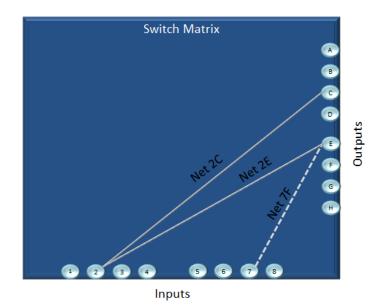

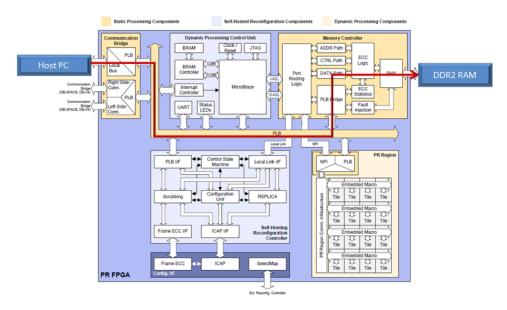

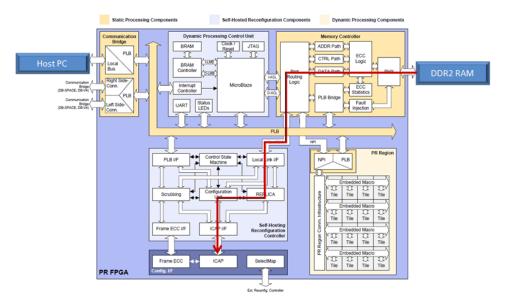

It is the main payload processing module of the system. The FPGA consists in three essential parts:

- Static processing components part, which includes a memory controller, which is connected to a DDR2 RAM, and several communication bridges;

- Self-hosting reconfiguration (SHR) components part, which includes a MicroBlaze processor and is in charge of carrying out the PR through the ICAP interface;

- **Dynamic processing** components part, which can be dynamically reconfigured in order to adapt the system to changed environment situations or to perform on-demand operations.

Figure 1.34 depicts the PR-FPGA module. The Host PC is the backplane for the RAPTOR-X64 baseboard.

Figure 1.34: The PR-FPGA module

## 1.3.3 DB-SPACE

This daughterboard is conceived for space missions, in fact it hosts a Leon2-FT core, which is the SEU fault tolerant (FT) version of the Leon2 processor, in particular FFs are protected with *triple modular redundancy* (TMR), while internal and external memories with *Error Detection And Correction* (EDAC) mechanisms. Figure 1.35 exhibits the DB-SPACE daughterboard.

Figure 1.35: The DB-SPACE daughterboard

## 1.4 Thesis Statement

Critical operations are processed on the DB-SPACE daughterboard, where the various components are fault tolerant, but there are cases in which some important operations are performed elsewhere, in fact the PR-FPGA is typically used on-demand by the Leon2-FT processor, which delegates some operations to it.

For example, the Leon2-FT processor has to take some decisions about moving and, for some reasons, it may need to calculate a Fast Fourier Transform (FFT), therefore it delegates this operation to the PR-FPGA. The MicroBlaze processor loads a bitstream from the DDR2-RAM, through the memory controller, into the SHR controller for performing the PR. The loaded bitstream is relative to a hard macro which is able to perform the FFT. Supposing the chosen empty space, in which the hard macro has been placed, is in somehow faulty and hence the hard macro could not work or worse could give a wrong result.

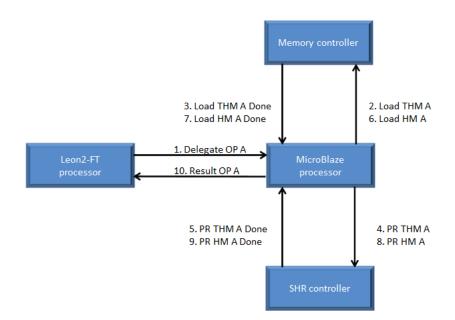

The aim of this thesis is to provide some mechanisms, in particular hard macros (HMs), which allow the MicroBlaze processor to detect faults in the chosen space. The processor could decide whether launching testing periodically, during idle time, or just before to execute a new PR, that is on-demand.

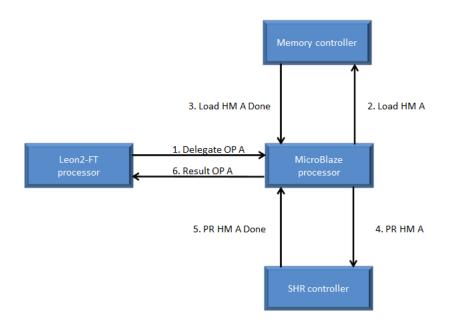

Figure 1.36 depicts a scheme in which fault detection is not carried out, the scenario is that the Leon2-FT processor delegates an operation A to the MicroBlaze processor, which performs all the due steps to obtain the operation A results. On the other hand, when fault detection mechanisms are available, the previous scenario can be changed as depicted in Figure 1.37, where before loading the hard macro related to the operation A, the MicroBlaze processor may decide of verifying the chosen space with one or a set of testing HMs.

Figure 1.36: Example of interaction between Leon2-FT and MicroBlaze processors without fault detection

Figure 1.37: Example of interaction between Leon2-FT and MicroBlaze processors with fault detection

## Chapter 2

# **Related Work**

## 2.1 Introduction

FPGA testing occupies an important part in the literature pertaining to FPGAs, above all as a result of their increase of popularity and use in safety-related and space applications.

At the beginning most of the works were addressed to the Off-Line testing, that is where possible running applications are stopped and the device is then tested. This service interruption is not feasible in continuous operating contexts. Recently, in particular with the introduction of the PR, the focus was moved on performing On-Line testing, allowing running applications to continue their elaborations.

In the following sections some works related to the FPGA testing are presented. Finally, the approach object of this thesis is briefly introduced.

## 2.2 Logical resources testing

Works in this section are focused on logical resources testing:

- 1. [19], where only faults in memory elements are addressed, supposing that IOBs and interconnections have already been tested;

- 2. [20], where testing integration in a runtime reconfigurable system is emphasized. Logical resources are divided in containers and the logic, within the container under test, is tested through a comparison-based BIST approach, utilizing TPG and ORA placed in different containers;

- 3. [21], where the use of testing HMs and the constraint of using only some columns for each testing session are introduced, in particular five columns are considered:

- one contains two TPGs;

- two contain ORAs;

- two contain Blocks Under Test (BUTs).

The approach is a comparison-based BIST, where each ORA compares two responses, which come from two different BUTs, driven by different TPGs. Finally, columns are shifted on the next testing session.

4. [22], where a comparison-based BIST is used and columns are shifted in each testing session; in particular this work is focused on Xilinx Virtex-4 devices and uses the PR for keeping the testing time low, because it mainly depends on the reconfiguration time.

## 2.3 Routing resources testing

Works in this section are aimed at detecting faults in routing resources.

- 1. [23], where an external approach is used, rather than a BIST. It exploits the JTAG interface for providing input stimuli and retrieving results;

- 2. [24], where a comparison-based BIST approach is used, in particular test vectors are stored in LUTs and then subsequently applied to CUTs;

- 3. [25], where a comparison-based BIST approach is used and it exhibits the feature of moving the part under test in every testing session for both logical and routing resources. Input stimuli for routing resources are generated as in [23] with a *Walking-0* or *Walking-1* approach;

- 4. [26], where the cross-coupled parity BIST and registers for storing test results are used. This work represents the starting point for the approach proposed in this thesis.

## 2.4 The proposed approach

All the aforementioned works feature interesting properties, but no one combines:

- Hard macros utilization, these pre-built blocks can be stored in the DDR2 RAM and loaded on-demand by the MicroBlaze;

- **Cross-coupled parity approach**, which outdoes limitations of the comparison-based and single parity approaches;

- Interconnection infrastructure testing, which, as previously said, by now occupies up to 80% of whole chip area;

- Focus on permanent faults, which nowadays, with really bigger devices, are gaining importance again;

- **PR and readback**, which represent the key for an On-Line testing approach as well as for keeping the testing time low;

- **On-Line testing**, which permits the use of these mechanisms even in situations where a service interruption is not feasible, such as in ACSes operating in space.

The proposed approach aims at combining all these elements, with a reasonable tradeoff between simplicity and effectiveness.

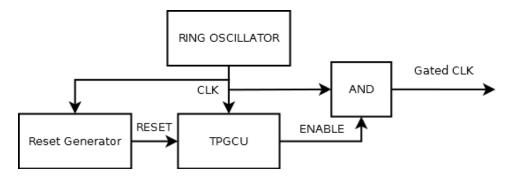

In order to realize easy placeable testing hard macros, the use of the following elements must be avoided:

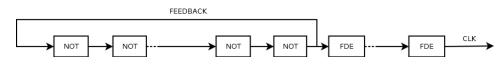

- global signals, as clock and reset, therefore they should be internally generated;

- particular resources, as the CAPTURE unit, which is used when the content of registers is read through a readback, for example where results are stored in registers as in [26].

Moreover, the quantity of the used logical resources has to be kept small in respect to the total available and the approach has to be optimized for Xilinx Virtex-4 devices, the same with which the DB-V4 daughterboard is equipped.

## Chapter 3

# **Testing Circuits**

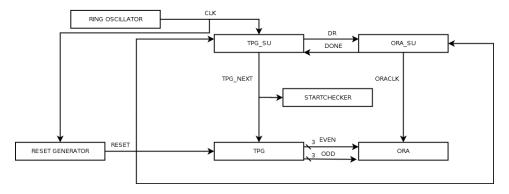

## 3.1 Introduction

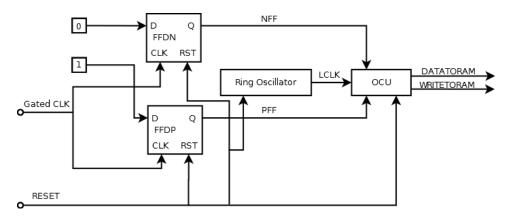

Three different testing circuits have been developed, each has different characteristics and features a diverse granularity level in terms of number of WUT. More precisely they are:

- A version with 6WUTs, which thanks to a feedback mechanism is able to detect transient faults, as well permanents;

- A version with 8WUTs, which is a variation of the previous version, it has no longer the feedback mechanism, but is able to test eight wires at the same time;

- A version with 1WUT, which represents the higher reachable granularity level, it employs a completely new approach because of the constraint of having only a wire between TPG and ORA.

There are actually two variants for the first two circuits, one without and one with a clock cycle counter. This counter could be used to check if there is performance degradation, for instance due to aging.

As previously said, in order to ease the placement of the hard macros inside an FPGA, the planning phase of these circuits has to eliminate, and where it is not possible, to reduce:

- global signals, e.g. Clock and Reset;

- using specific resources, e.g. the CAPTURE unit;

- used logical resources.

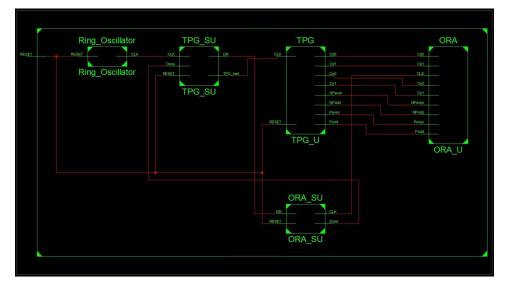

Consequently, it has also been necessary to develop other logic, as a ring oscillator for generating a clock signal and a circuit for generating a reset signal.

The results of the ORA assessment task are stored in distributed RAM and in due time these will be read by means of a readback operation.

Before presenting the developed testing circuits in details, some useful information about TPG and ORA are given in the following section.

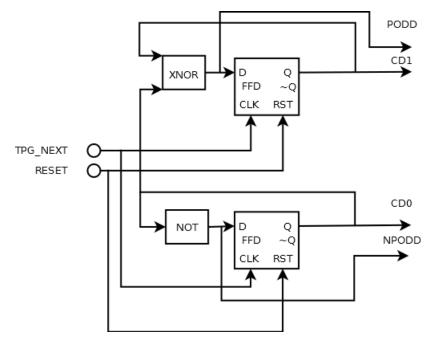

#### 3.1.1 Test Pattern Generator

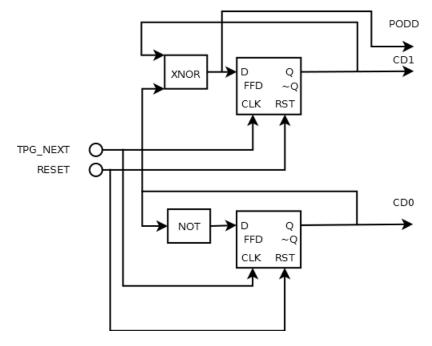

The function of this component is to generate some specific signals, which are propagated on the wires under test, thereby testing their status. The testing signals derive from [26], representing the starting point for 6WUTs and 8WUTs circuits. There are overall four configurations of these signals, which are shown in Table 3.1.

| Num | Ι | II | III | IV | V | VI |

|-----|---|----|-----|----|---|----|

| 1   | 0 | 0  | 0   | 1  | 1 | 1  |

| 2   | 0 | 1  | 1   | 1  | 0 | 0  |

| 3   | 1 | 0  | 1   | 0  | 1 | 0  |

| 4   | 1 | 1  | 0   | 0  | 0 | 1  |

Table 3.1: TPG signals configurations

In reality, the TPG is made of two internal TPGs (up and down counting TPG) and for that reason in the Table 3.1 the columns have been highlighted with different colours, in particular, each colour represents a different internal TPG.

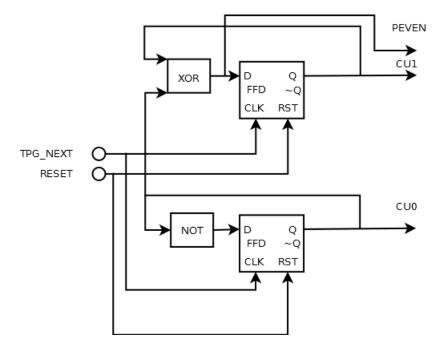

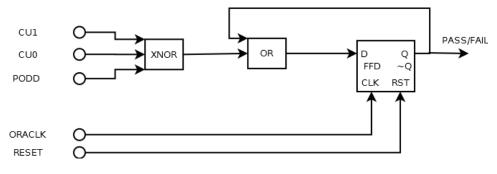

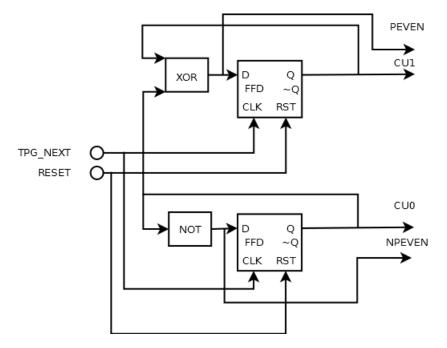

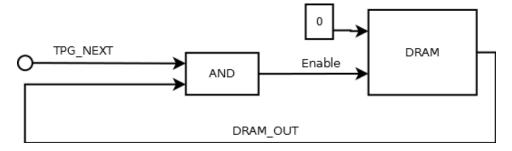

## 3.1.2 Output Response Analyzer

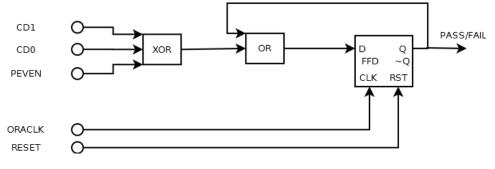

Functions of this component are essentially two:

- 1. Assessing if the received signals, by means of the WUTs, are what it is expected;