# PIEZOTRONIC DEVICES AND INTEGRATED SYSTEMS

A Dissertation Presented to The Academic Faculty

by

Wenzhuo Wu

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Materials Science and Engineering

Georgia Institute of Technology May, 2013

## PIEZOTRONIC DEVICES AND INTEGRATED SYSTEMS

## Approved by:

Dr. Zhong Lin Wang, Advisor School of Materials Science and Engineering Georgia Institute of Technology

Dr. David McDowell School of Materials Science and Engineering/Woodruff School of Mechanical Engineering Georgia Institute of Technology

Dr. Yulin Deng School of Chemical & Biomolecular Engineering Georgia Institute of Technology Dr. Preet Singh School of Materials Science and Engineering Georgia Institute of Technology

Dr. Russell D. Dupuis School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: December 5, 2012

#### **ACKNOWLEDGEMENTS**

Neither my life in these past four years, nor myself, nor this thesis would be the same without the help and company of many people.

First of all, I would like to thank my advisor, Prof. Zhong Lin Wang, for his scientific vision in conducting pioneering research, his encouragement and guidance during my PhD study, and his constant, generous and unreserved support for my life. I have learnt a lot from Prof. Wang during the past four years, both professionally and personally. Whenever I feel depressed and frustrated, the inspiring encouragements from Prof. Wang always lead me to the right direction with his unique foresight. I also sincerely thank Prof. Wang and his family for their care of me, not only in my academic research and study, but also in my personal life, which means a lot to me. Without these supports, guidance and care, I could not have gone thus far.

I would also like to express my sincere appreciation to members of my dissertation committee, Prof. David McDowell, Prof. Yulin Deng, Prof. Russell D. Dupuis and Prof. Preet Singh for the precious time, patience and invaluable advices which they generously offer. I also thank the professors from different departments who have instructed the courses I took.

I am also very fortunate to receive help from a lot of people during my PhD endeavors. My group members helped me a lot during the past four years. Special thanks to Dr. Yong Ding, Mr. Tiejun Zhang, Ms. Yolande, Ms. Karen Mayo, Ms. Susan Bowman and others for kindly providing technical support and assistance. Dr. Jinhui Song and Dr. Yaguang Wei acted as my immediate mentors during the first two years of

my PhD study and have been providing invaluable advice since then. I have learned a lot from both of them. We also have several collaboration work crystallized. Sincere thanks go to Dr. Wei, Dr. Song and Dr. Rusen Yang as well as their families for their kindly care of me. Many thanks to Drs. Xudong Wang, Wenjie Mai, Jin Liu, Melanie Kirkham, Ben Weintraub, Chen Xu, Yong Qin, Youfan Hu, Minbaek Lee, Sangmin Lee and others for the precious discussions on research and various other aspects. I would like to mention my appreciation to my fellow graduate students and alumni of Prof. Wang's group, Fengru Fan, Fan Bai, Yifan Gao, Cheng Li, Xiaonan Wen, Long Lin, Hao Fang, Su Zhang, Yue Shen, Yi Xi, Ken Pradel and others for the wonderful company and friendship they have provided. Among many others, I have been enjoying your company in a social setting just as much as your scientific input in the lab.

I am appreciative of the constant encouragement and company from all my good friends. Thanks for being such good friends and being there for me, when I need it.

Thanks to those who I have left out unintentionally but have helped in any way or contributed to my life and study.

Finally and most importantly, I want to thank my family for always quietly watching out for me, patiently loving me, and sparing advice and support, when I need them most. I would like to especially thank my mother, for the care and the love which she has given unconditionally with her persistence and aspiration. I would not be who I am if it wasn't for you.

# TABLE OF CONTENTS

|                                                                          | Page |

|--------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                         | iv   |

| LIST OF TABLES                                                           | ix   |

| LIST OF FIGURES                                                          | X    |

| LIST OF ABBREVIATIONS                                                    | xix  |

| SUMMARY                                                                  | XX   |

| <u>CHAPTER</u>                                                           |      |

| 1 INTRODUCTION                                                           | 1    |

| 1.1 Complementing device miniaturization with functional diversification | on 1 |

| 1.2 Interface between electronics and human/ambient                      | 2    |

| 1.3 Thesis outline                                                       | 4    |

| 2 PIEZOPOTENTIAL AND PIEZOTRONIC EFFECT                                  | 6    |

| 2.1 Piezopotential                                                       | 6    |

| 2.1.1 Piezopotential distribution in transversely deflected NW           | 9    |

| 2.1.2 Piezopotential distribution in axially strained NW                 | 13   |

| 2.1.3 Piezopotential distribution in doped semiconductor NW              | 15   |

| 2.2 Piezotronic effect                                                   | 18   |

| 2.2.1 Effect of piezopotential on metal-semiconductor contact            | 18   |

| 2.2.2 Effect of piezopotential on p-n junction                           | 22   |

| 2.3 Summary                                                              | 27   |

| 3 RATIONAL SYNTHESIS OF ZINC OXIDE NANOWIRE AND ARRAY                    | 28   |

| 3.1 Physical-vapor-deposition (PVD) method                               | 29   |

| 3.1.1 Vapor-solid (VS) process                                           | 29   |

|   | 3.1.2 Vapor-solid-solid (VSS) process                                                    | 32         |

|---|------------------------------------------------------------------------------------------|------------|

|   | 3.1.3 Pulsed laser deposition (PLD) method                                               | 36         |

|   | 3.2 Solution-phase hydrothermal (HT) method                                              | 39         |

|   | 3.2.1 General growth mechanism                                                           | 39         |

|   | 3.2.2 Wafer-scale high-throughput ordered growth of vertically align ZnO NWs array       | ed<br>40   |

| 4 | STRAIN-GATED PIEZOTRONIC LOGIC NANODEVICES                                               | 55         |

|   | 4.1 Background                                                                           | 56         |

|   | 4.2 Strain-gated transistor (SGT)                                                        | 56         |

|   | 4.2.1 Calculation of strain for ZnO strain gated logic devices                           | 58         |

|   | 4.2.2 Characteristics of SGT                                                             | 58         |

|   | 4.2.3 Working principle of SGT                                                           | 59         |

|   | 4.2.4 Comparison between SGT and traditional field-effect-transis (FET)                  | stor<br>64 |

|   | 4.3 Strain-gated inverter (SGI)                                                          | 66         |

|   | 4.3.1 Fabrication and operation of SGI                                                   | 66         |

|   | 4.3.2 Characterization of SGI                                                            | 67         |

|   | 4.4 Strain-gated universal logic gates                                                   | 71         |

|   | 4.5 Summary                                                                              | 74         |

| 5 | PIEZOTRONIC NANOWIRE BASED RESISTIVE SWITCHES AS PROGRAMMABLE ELECTROMECHANICAL MEMORIES | 76         |

|   | 5.1 Background                                                                           | 80         |

|   | 5.2 Structure and fabrication of piezoelectrically-modulated resistive memory            | 77         |

|   | 5.3 Characterization of PRM                                                              | 79         |

|   | 5.3.1 Electro-mechanical characterization                                                | 79         |

|   | 5.3.2 Effect of plasma pre-treatment                                                     | 81         |

| 5.3.3 Temperature-dependent <i>I-V</i> measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3.4 Stain-modulated hysteretic switching of PRM cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 90  |

| 5.3.5 Operation of PRM cell as electromechanical memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 95  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _   |

| 6.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

| 6.2 Materials, working principles and design strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |

| 6.2.1 Fabrication of SGVPT array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102 |

| 6.2.2 Structure characterization of SGVPT array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 103 |

| 6.3 Single-channel and full array response characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107 |

| 6.3.1 Single-channel response characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107 |

| 6.3.2 Full-array response characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111 |

| 6.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113 |

| 7 CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 115 |

| 5.3.4 Stain-modulated hysteretic switching of PRM cell 5.3.5 Operation of PRM cell as electromechanical memory  6 PIXEL-ADDRESSABLE TRANSPARENT-AND-FLEXIBLE MATRIX OF VERTICAL-NW PIEZOTRONIC TRANSISTORS FOR TACTILE IMAGIN  6.1 Background  6.2 Materials, working principles and design strategies  6.2.1 Fabrication of SGVPT array  6.2.2 Structure characterization of SGVPT array  6.3 Single-channel and full array response characterization  6.3.1 Single-channel response characterization  6.3.2 Full-array response characterization  6.4 Summary  7 CONCLUSION  APPENDIX A: PROCESSING SCHEME FOR FABRICATING 3D VERTICAL PIEZOTRONIC TRANSISTORS ARRAY  11  12  13  14  15  16  17  17  18  18  18  18  19  19  19  10  10  10  10  10  10  10 | 119 |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 121 |

| VITA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 140 |

#### LIST OF TABLES

Page

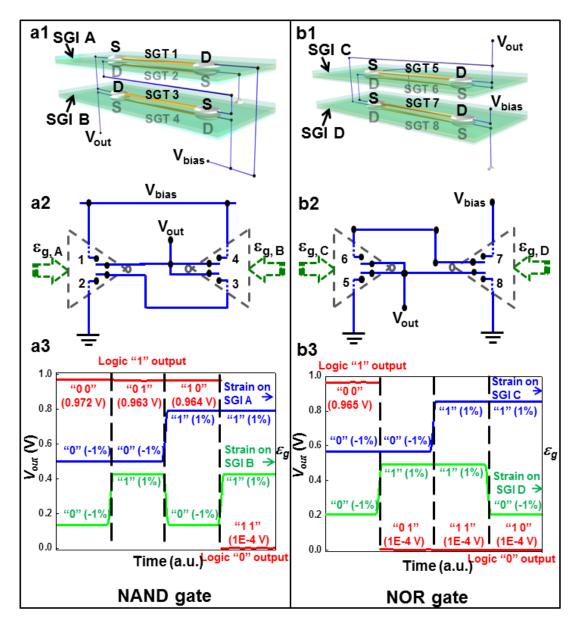

- Table 1: One kind of transition changes the on/off status for all four SGTs, such as the case happening in the first two columns of Table S1 (with purple color). The other kind of transition changes the on/off status for only two SGTs, like the cases happening in the last four columns of Table S1 (with bluish color). The two numbers in the quotation marks represent the logic levels for strain inputs on the SGIs in a ZnO NW strain gated NAND gate.

- Table 2: One kind of transition changes the on/off status for all four SGTs, such as the case happening in the first two columns of Table S2 (with purple color). The other kind of transition changes the on/off status for only two SGTs, like the cases happening in the last four columns of Table S2 (with bluish color). The two numbers in the quotation marks represent the logic levels for strain inputs on the SGIs in a ZnO NW strain gated NOR gate.

## LIST OF FIGURES

Page

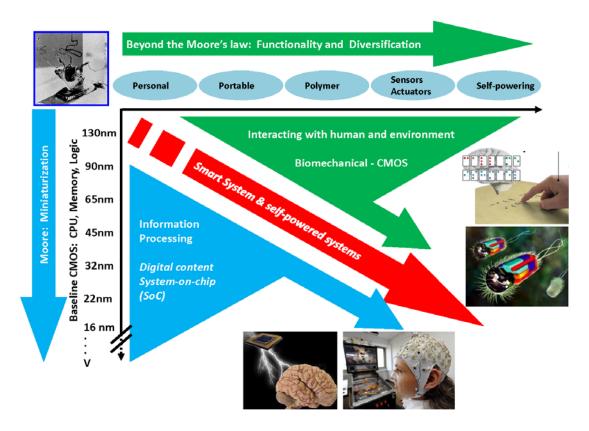

- Figure 1: Future perspective of electronics beyond Moore's law. The vertical axis represents a miniaturization and increase of device density, CPU speed and memory capacity. The horizontal axis represents the diversity and functionality for personal and portable electronics. The future of electronics is an integration of CPU speed and functionality.

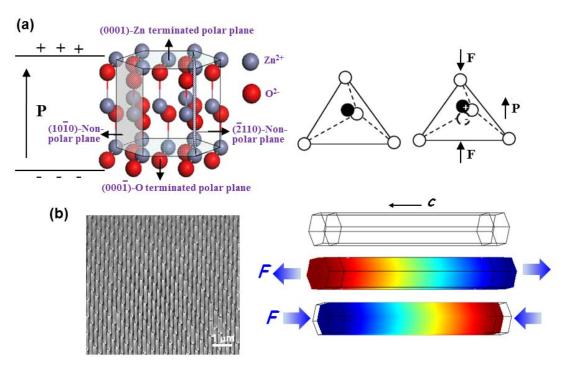

- Figure 2: Piezopotential in Wurtzite crystal. (a) Atomic model of the Wurtzite-structured ZnO. (b) Left, large-scale aligned ZnO nanowire (NW) arrays by solution based hydrothermal approach. Right, distribution of piezopotential along a ZnO NW under axial strain calculated by numerical methods. The growth direction of the NW is along c-axis.

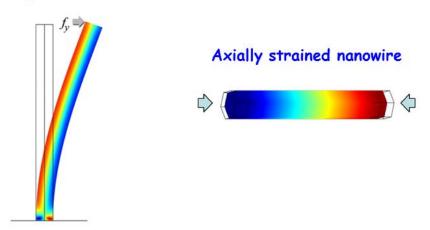

- Figure 3: Distribution of piezopotential in two typical configurations of NW devices. The color gradient represents the distribution of piezopotential in which red indicates positive piezopotential and blue indicates negative piezopotential. 8

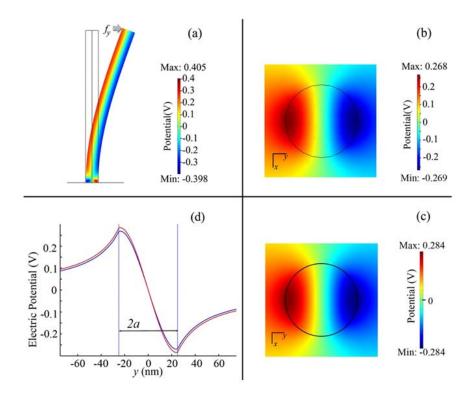

- Figure 4: Potential distribution for a ZnO NW with d = 50 nm and l = 600 nm experiencing a lateral bending force of 80 nN. (a) and (b) are the side and top cross-sectional (at z0 = 300 nm) piezopotential output in the NW obtained by finite element calculation using fully coupled equations (1-4), while (c) is the cross-sectional piezopotential output calculated by analytical equation (8). (d) gives a comparison of the line-scan profiles from both (b) and (c), showing the accuracy of equation (8) and approximations applied for deriving it (blue line is for result obtained from full finite element method (FEM) and red line is for result given by equation (8)).

- Figure 5: Numerical calculation results of the piezopotential distribution in a ZnO NW without considering the doping. (Top) An unstrained ZnO NW grown along *c*-axis. (Middle) Distribution of piezopotential together with deformed shape for the NW by stretching force and (Bottom) by a compressing force of same magnitude.

- Figure 6: Numerical calculation results of the piezopotential distribution in a ZnO NW considering finite doping with donor concentration of  $1\times10^{17}$  cm<sup>-3</sup>. The dimension of the NW is: a=25 nm, l=600 nm and the external force is  $f_y=80$  nN. (a) Piezopotential distribution of the cross section at x=0. (b) Cross section plot of the piezopotential at z=400 nm. (c and d) Calculation results for the case without considering the doping inside ZnO NW. (c) shows the cross section plot of piezopotential at z=0. (d) shows the cross section plot of the piezopotential at z=400 nm.

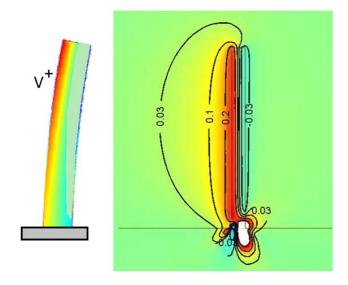

- Figure 7: Calculated distribution of piezopotential in a *p*-type ZnO NW when transversely deflected.

- 17

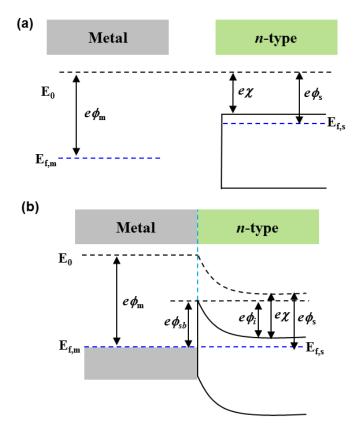

- Figure 8: Schematic of an ideal metal/semiconductor contact. (a) Before forming the contact. (b) Creation of Schottky barrier after metal and semiconductor form close contact.

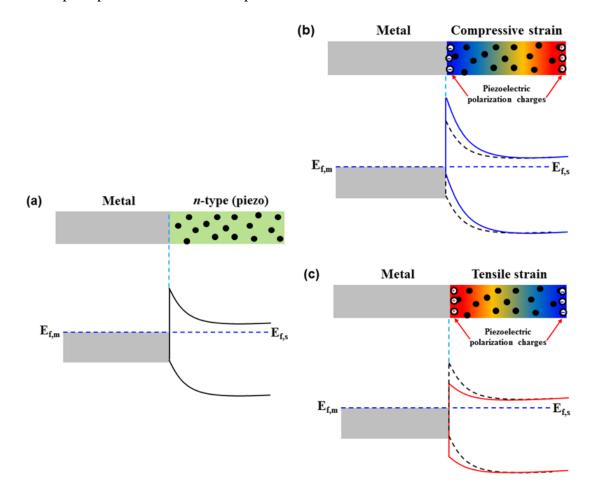

- Figure 9: Schematic of energy diagram illustrating the effect of piezopotential on modulating the metal-semiconductor characteristics. (a) Schottky barrier induced at the interface between metal and n-type piezoelectric semiconductor material, without strain applied. Black dots represent the free charge carriers in the bulk semiconductor. (b) With compressive strain applied, the negative piezoelectric polarization ionic charges induced near the interface (symbols with "-") increases the local SBH. (c) With tensile strain applied, the positive piezoelectric polarization ionic charges induced near the interface (symbols with "+") decreases the local SBH. The color gradients in (b) and (c) indicate the distribution of piezopotential, with red representing positive piezopotential and blue representing negative piezopotential. The band diagrams for the M-S contact with and without the presence of piezotronic effect are shown using red solid and black dashed curves, respectively.

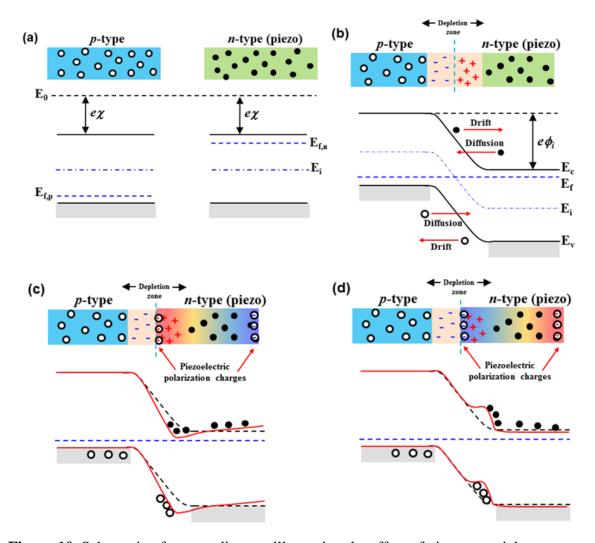

- Figure 10: Schematic of energy diagram illustrating the effect of piezopotential on modulating characteristics of *p-n* homojunction. (a) Before the contact/junction is formed. Black dots and empty circles represent the free charge carriers in semiconductor.  $E_{f,n}$  and  $E_{f,p}$  are the Fermi levels in *n*-type and *p*-type materials respectively.  $E_0$  and  $E_i$  are the vacuum level and intrinsic Fermi level. (b) Charge depletion regions forms when thermal equilibrium of the system is reached. Symbols "+" and "-" represent the ionized donors and acceptors in respective regions. (c) and (d) With strain applied, the piezoelectric polarization ionic charges are induced near the junction interface. The color gradients in (c) and (d) indicate the distribution of piezopotential, with red representing positive piezopotential and blue representing negative piezopotential. The band diagrams for the *p-n* junction with and without the presence of piezotronic effect are shown using red solid and black dashed curves, respectively.

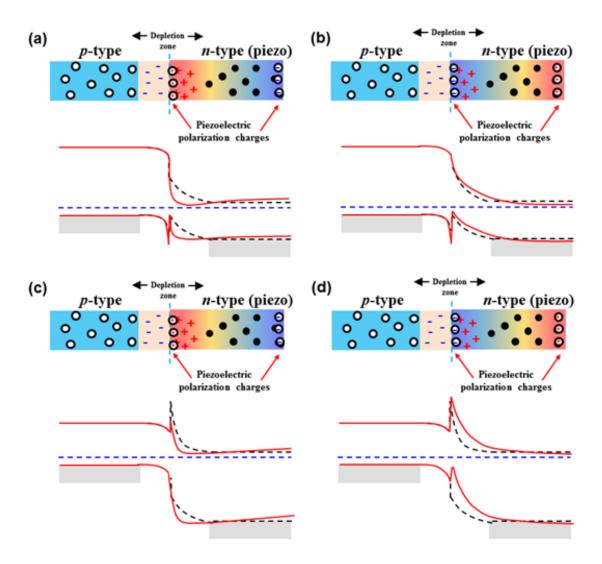

- Figure 11: Schematic of energy diagram illustrating the effect of piezopotential on modulating characteristics of *p-n* heterojunction. In (a) and (b), *p*-type semiconductor material has larger bandgap than n-type piezoelectric semiconductor material. (a) Positive piezoelectric polarization charges are induced near the junction interface and (b) negative piezoelectric polarization charges are induced near the junction interface. In (c) and (d), *p*-type semiconductor material has smaller bandgap than *n*-type piezoelectric semiconductor material. (c) Positive piezoelectric polarization charges are induced near the junction interface and (d) negative piezoelectric polarization charges are induced near the junction interface. The band diagrams for the *p-n* junction with and without the presence of piezotronic effect are shown using red solid and black dashed curves, respectively.

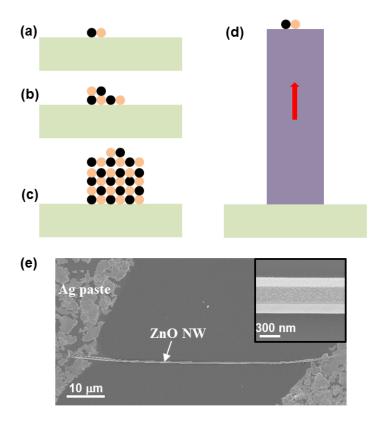

- Figure 12: (a-d) A proposed growth mechanism for ZnO nanostructure via VS process. Adapted from <sup>89</sup>. (e) A single-NW device fabricated by forming contacts between the as-synthesized ZnO NW and metal electrodes (Ag paste). Inset: magnified view of the ZnO NW, which clearly shows the facets of the asgrown hexagonally structured NW. Scale bars: 10 μm for (e) and 300 nm for the inset.

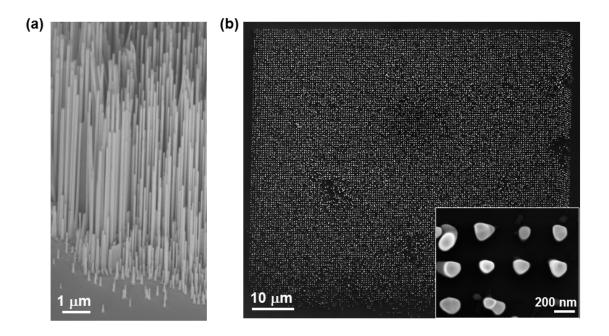

- Figure 13: (a) Tilted-view (30 °) of vertically-aligned ZnO NWs array grown via VSS process. (b) Top view of site-specific growth of vertically-aligned ZnO NWs array via VSS process. Inset: zoom-in view of the as-grown samples. Images in (b) by courtesy of Dr. Y. G. Wei.

- Figure 14: (a) Left: Tilted view of the as-grown NWs. The corresponding growth parameters are 795 °C, 4.5 Torr, Ar = 40 sccm, O2 = 6 sccm, deposition time = 40 minutes, laser repetition frequency = 5 Hz. Right: PL spectra obtained for this sample. (b) Left: Tilted view of the as-grown NWs. The corresponding growth parameters are 795 °C, 4.1 Torr, Ar = 30 sccm, O2 = 10 sccm, deposition time = 40 minutes, laser repetition frequency = 3 Hz. Right: PL spectra obtained for this sample. Images by courtesy of Dr. S. S. Lin.

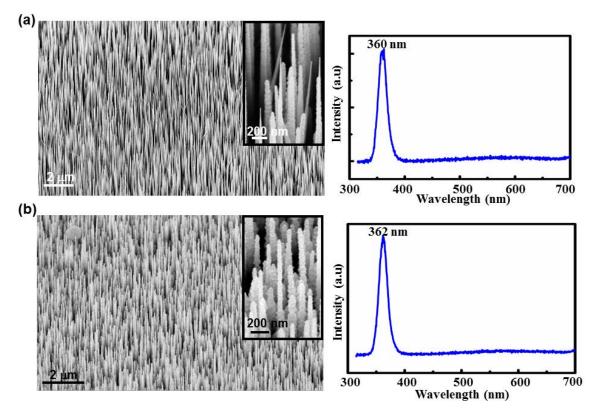

- Figure 15: (a) Schematics of experimental setup for the laser interference patterning. (b) The interference between beam 1 and beam 2 forms a grating pattern on the photoresist layer under a single laser pulse (10 ns) irradiation. (c) The sample is then rotated for 90 o or at an arbitrary angle with a second exposure, and patterns of periodic nanodot arrays are formed on the photoresist layer or the substrate. The grating and nanodot patterns in b and c are fabricated on SU 8 via LIL approach and acquired by scanning probe microscope (SPM, Veeco Dimension 3100).

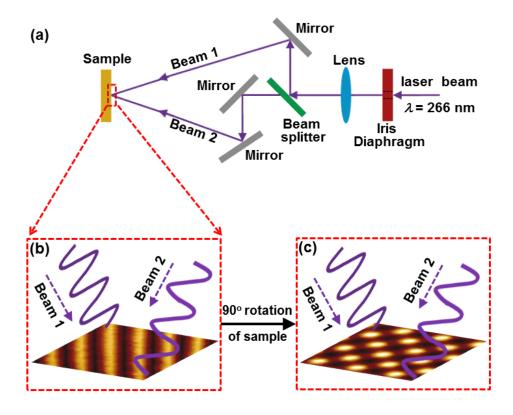

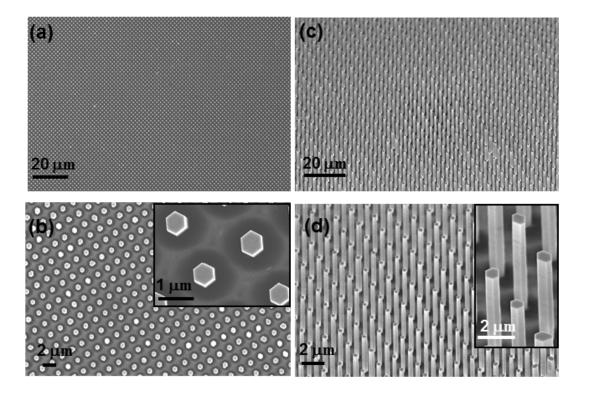

- Figure 16: Schematics of the fabrication sequences of vertically aligned ZnO NW arrays using laser interference techniques. (a) Fabrication sequence using LIL approach for large-scale patterned vertically aligned ZnO NW arrays. (b) Optical image of a 2-inch Si wafer with SU 8 open-hole pattern over the whole surface area. The iridescence dispersion demonstrates the excellent periodicity over the entire wafer surface.(c) Top-view SEM image of patterned SU-8 film. Inset, zoom in top-view SEM image of patterned SU-8 film. (d) 45°-tilted-view SEM image of patterned SU-8 film.

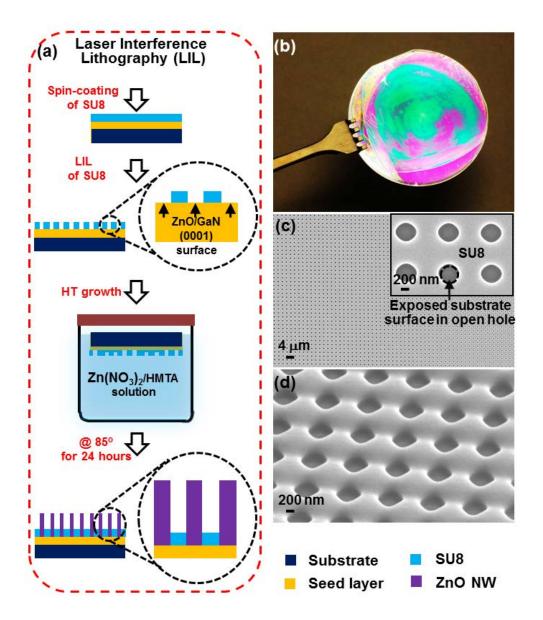

- Figure 17: The heteroepitaxial growth of vertically aligned ZnO NW arrays on GaN substrate via LIL approach. (a) and (b) Top-view SEM images of vertically aligned ZnO NW arrays on GaN substrate in large-scale uniform pattern at different magnifications. (c) and (d) 45°-tilted-view SEM images of vertically aligned ZnO NW arrays on GaN substrate in large-scale uniform pattern at different magnifications.

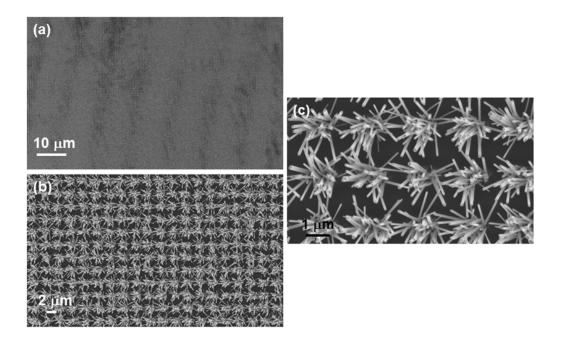

- Figure 19: The homoepitaxial growth of randomly aligned ZnO NWs array on a silicon wafer covered with a polycrystalline ZnO seed layer via LIL approach. (a), (b) and (c) Top-view SEM images of randomly aligned ZnO NWs array on Si substrate in large-scale uniform pattern at different magnifications.

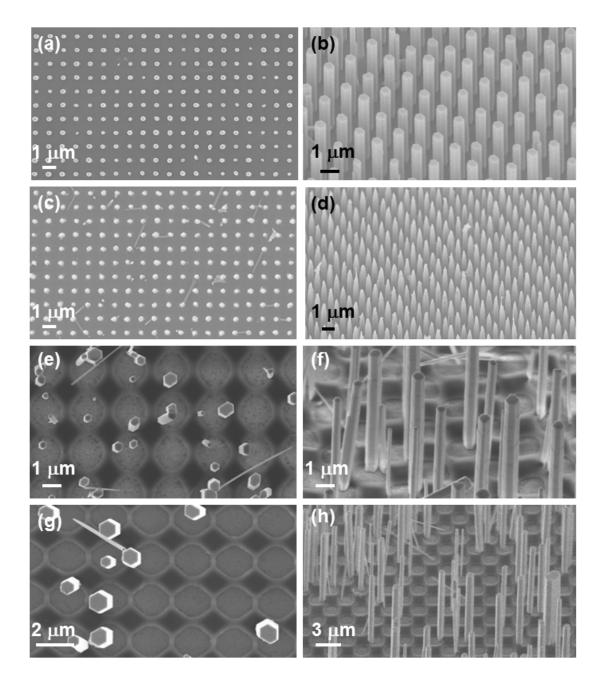

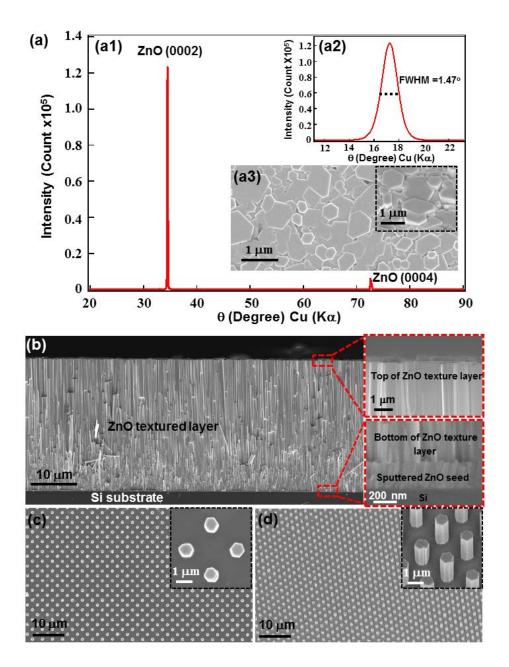

- Figure 20: The homoepitaxial growth of large-scale vertically aligned ZnO NWs array via LIL approach on textured ZnO seed layer. (a) X-ray diffraction (XRD) measurements investigating the crystal structure and orientation as well as SEM image of the as-grown textured ZnO seed layer. (b) Cross-section of the as-grown dense textured ZnO layer. (c), (d) and insets, Top-view and 45°-tilted-view SEM images of vertically aligned ZnO NWs array on silicon substrate with textured ZnO layer in large-scale uniform pattern at different magnifications.

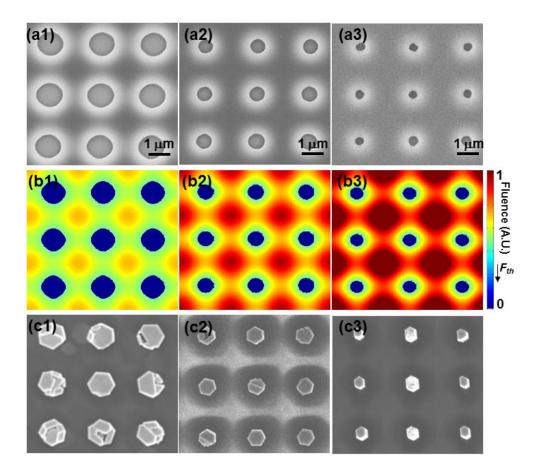

- Figure 21: (a1-a3) Top-view SEM images of SU-8 patterns of different hole-opening sizes on Si substrate with textured ZnO seed layer, and the interference light fluence is 1.6, 3.2 and 6.0 mJ/cm<sup>2</sup>, respectively. (b1-b3) Simulated laser fluence distribution in SU-8 using the same laser fluencies as those in a1-a3. (c1-c3) Top-view SEM images of vertically aligned ZnO NW arrays, which follow the pre-defined pattern of SU-8 layer with high-fidelity.

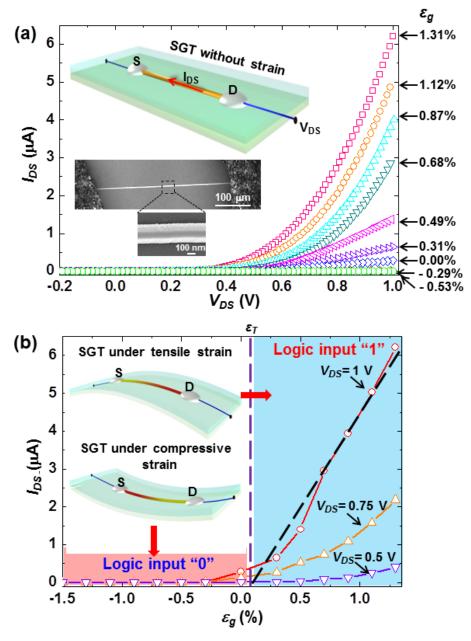

- Figure 22: Single ZnO NW strain-gated transistor (SGT). a)  $I_{DS}$ - $V_{DS}$  output characteristic for a ZnO SGT device. b)  $I_{DS}$ - $\varepsilon_g$  transfer characteristic for the same ZnO SGT device under three different  $V_{DS}$  bias values: 1 V, 0.75 V and 0.5 V.

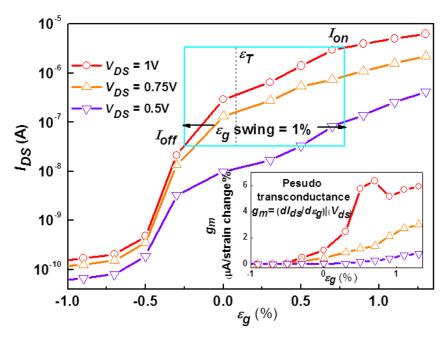

- Figure 23:  $I_{DS}$ - $\varepsilon_g$  transfer characteristic for the ZnO SGT device under three different  $V_{DS}$  bias values: 1 V, 0.75 V and 0.5 V, respectively. The blue square defines the 1% gate strain window. (Inset) Pseudo transconductance for this ZnO NW SGT with VDS bias values of 1 V, 0.75 V and 0.5 V, respectively, from top to bottom.

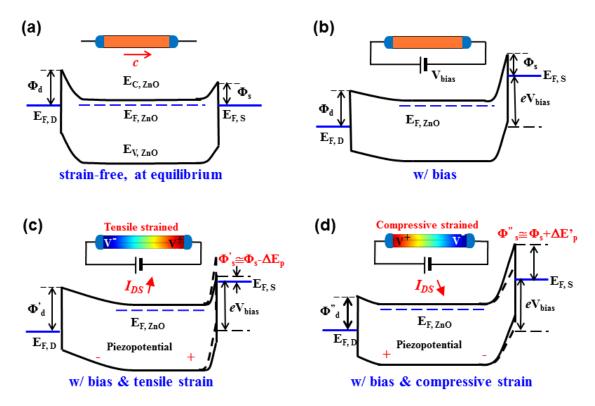

- Figure 24: The band structures of the ZnO NW SGT under different conditions for illustrating the mechanism of SGT. a) The band structure of a strain-free ZnO NW SGT at equilibrium with different barrier heights of  $\Phi_S$  and  $\Phi_D$  at the source and drain electrodes, respectively. b) The quasi-Fermi levels at the source  $(E_{F,S})$  and drain  $(E_{F,D})$  of the ZnO SGT are split by the applied bias voltage  $V_{bias}$ . c) With tensile strain applied, the SBH at the source side is reduced from  $\Phi_S$  to  $\Phi'_S \cong \Phi_S \Delta E_P$ . d) With compressive strain applied, the SBH at the source side is raised from  $\Phi_S$  to  $\Phi''_S \cong \Phi_S + \Delta E'_P$ .

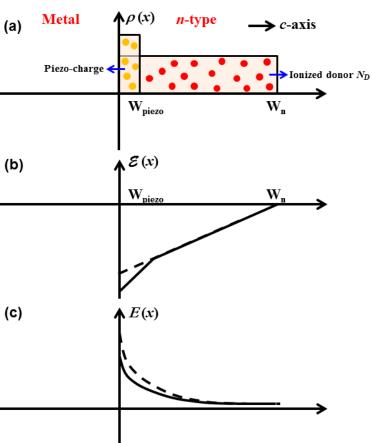

- Figure 25: (a) Space charges distribution; (b) electric field and (c) energy band diagram for ideal metal-semiconductor Schottky contacts with the presence of piezoelectric polarization charges at applied voltage V = 0 (thermal equilibrium). Dashed lines indicate electric field and energy band with the absence of piezoelectric charges. Adapted from 63

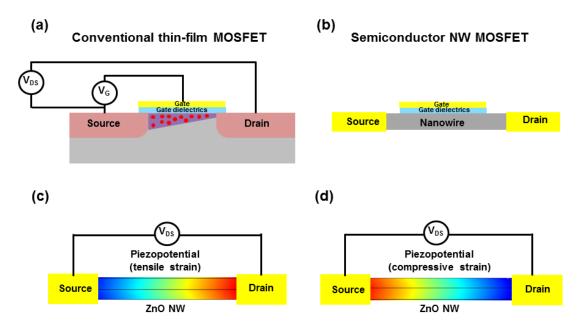

- Figure 26: Schematics of (a) conventional thin-film based MOSFET and (b) a semiconductor NW based FET; Schematics of a SGT under tensile strain (c) and compressive strain (d), where the gate voltage which controls the channel width in MOSFET is replaced by a piezopotential that modulates the transport across the MS interface<sup>21</sup>.

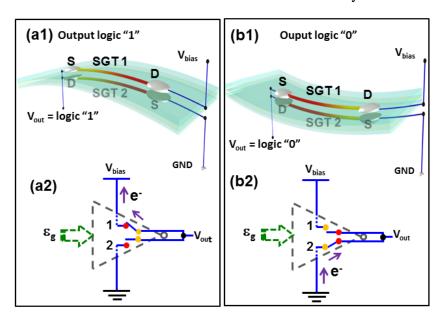

- Figure 27: Schematics and corresponding symbols of a ZnO NW strain-gated inverter (SGI) performing logic operations on corresponding input strain.

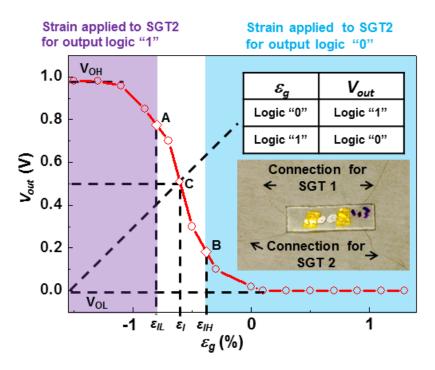

- Figure 28: The strain-voltage transfer characteristic (SVTC) and noise margins of the ZnO NW SGI with  $V_{DS} = 1$  V. Inset, optical picture of a ZnO NW SGI, with two SGTs and four connecting wires.

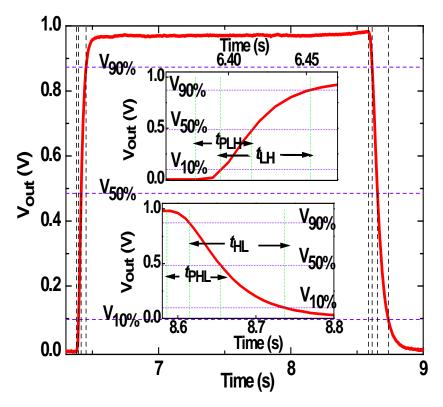

- Figure 29: Transient analysis of the ZnO NW SGI. Low-to-high time  $t_{LH}$  and high-to-low time  $t_{HL}$  represent the minimum response time of the NW SGI.  $t_{LH}$  and  $t_{HL}$  for a typical ZnO-NW SGI are determined as 0.06s and 0.11s respectively. The maximum switching frequency is hence computed from  $f_{max} = 1/(t_{HL} + t_{LH}) = 5.88$  Hz. The propagation delay  $t_P$  for the gate is the average time required for a change in the gate input strain to be reflected at the output, which is computed using the time intervals  $t_{PHL}$  and  $t_{PLH}$  from  $t_P = (0.5)(t_{PHL} + t_{PLH}) = 0.249$  s. 69

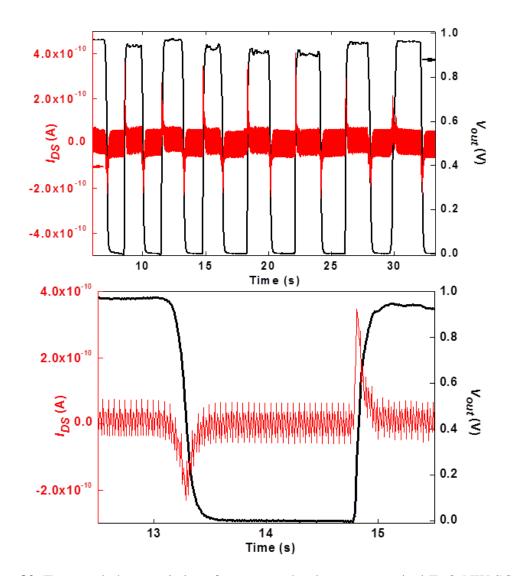

- Figure 30: Temporal characteristics of current and voltage on a typical ZnO-NW SGI. The absolute charges for the two current spikes in the magnified part are  $1.99 \times 10^{-11} C$  (negative spike) and  $2.97 \times 10^{-11} C$  (positive spike), respectively. The current spikes resulted from current generating process in the NWs can be negative or positive here depending the sign of straining rate, while the spikes of  $I_{dp}$  should be all positive. Therefore,  $I_{dp}$  can be determined as around 50 pA using simple superposition calculation.

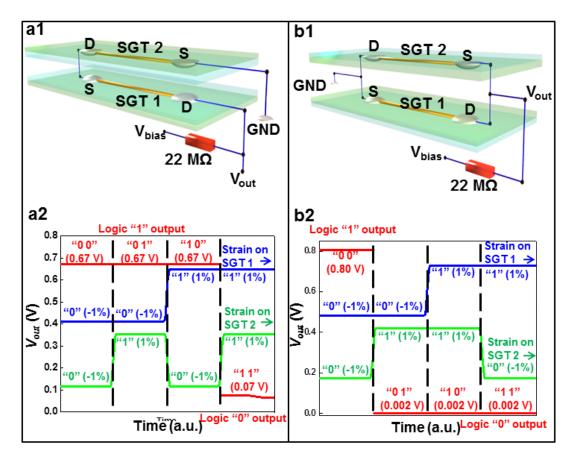

- Figure 31: Schematics and operations of ZnO NW strain-gated NAND and NOR logic gates. a1-a3) ZnO NW strain-gated NAND gate. b1-b3) ZnO NW strain-gated NOR gate. a.u., arbitrary units.

- Figure 32: a1) Schematic of a resistive-load ZnO NW NAND gate constructed from serial connection of two ZnO NWs. a2) Logic operations and experimental truth table of the resistive-load ZnO NW NAND logic gate. b1) Schematic of a resistive-load ZnO NW NOR gate constructed from parallel connection of two ZnO NWs. b2) Logic operations and experimental truth table of the resistive-load ZnO NW NOR logic gate.

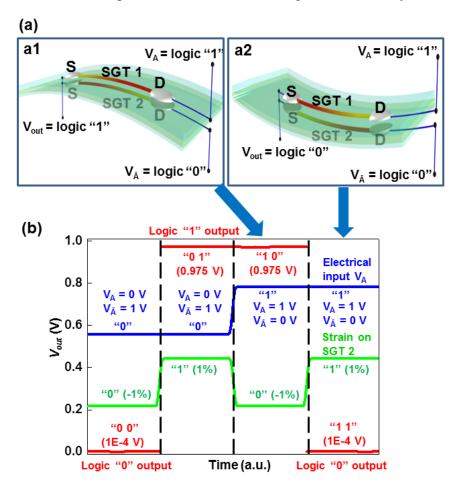

- Figure 33: ZnO NW strain-gated XOR logic gate. a1-a2) Schematics of a ZnO NW XOR logic gate performing logic operations on strain and electrical inputs. b) Logic operations and experimental truth table of the ZnO NW strain-gated XOR logic gate.

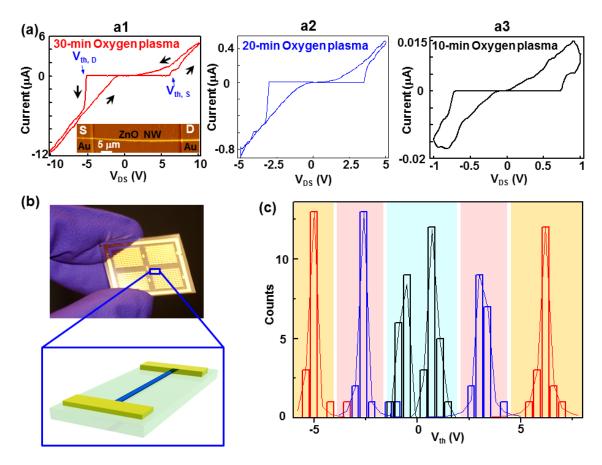

- Figure 34: Effects of oxygen plasma treatment on electrical properties of ZnO PRM cells.

(a) a1-a3 *I-V* characteristics of ZnO PRM cells after 30, 20 and 10 minutes oxygen plasma treatment. a1 Inset, Atomic force microscopy (AFM) image of one ZnO PRM cell. (b) Optical image of the large-scale as-fabricated PRM cells after printing transfer of ZnO NWs and lithography patterning of metal electrodes. (c) Statistical distributions of the V<sub>th,S</sub> and V<sub>th,D</sub> peaks for PRM cells with different periods of oxygen plasma treatment. Red, blue and black lines are for PRM cells with 30, 20 and 10 minutes oxygen plasma treatment, respectively.

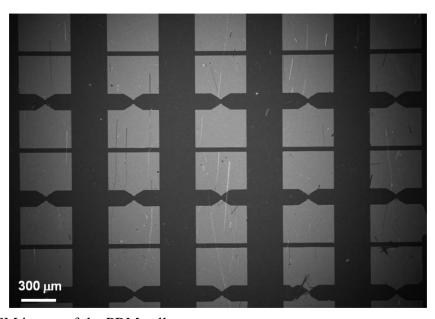

- Figure 35: SEM image of the PRM cells array.

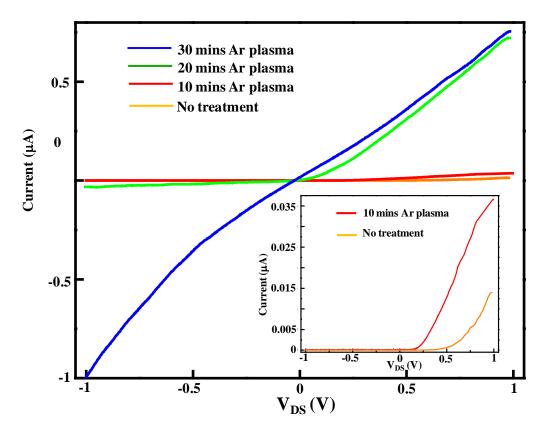

Figure 36: *I-V* curves of PRM cells with argon plasma treatment. For PRM cells treated with argon plasma, the threshold voltages decreased and the conductance increased with respect to the pristine one, as the treatment time increased. The rectification disappeared in the *I-V* curve for PRM cell treated with 30 minute argon plasma. Inset, magnified plot for pristine PRM cell and cell with 10-minute argon plasma treatment.

80

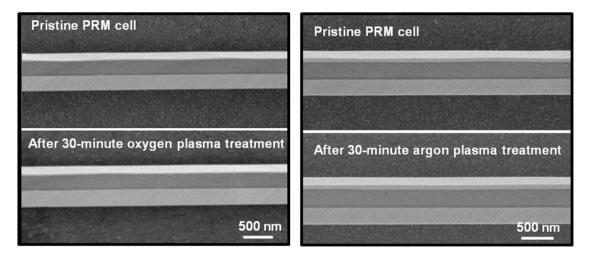

Figure 37: Morphology of ZnO NWs before and after plasma treatment. No obvious variations can be observed in morphology for ZnO NWs before and after plasma treatments.

83

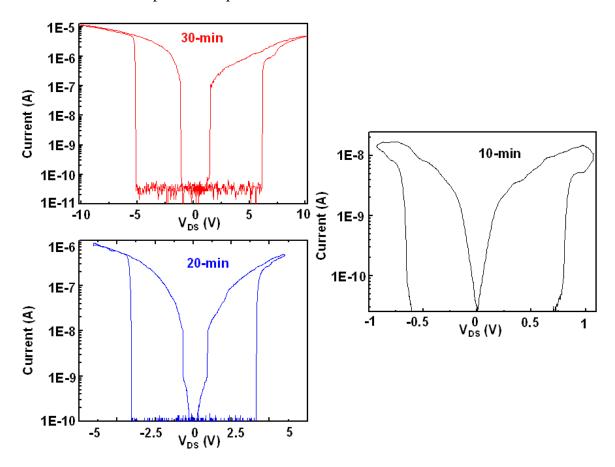

| Figure 3 | 8: <i>I-V</i> characteristics of ZnO PRM cells after 30, 20 and 10 minutes oxygen                                                                                                                                                                                                                    | n  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| rigare 3 | plasma treatment.                                                                                                                                                                                                                                                                                    | 84 |

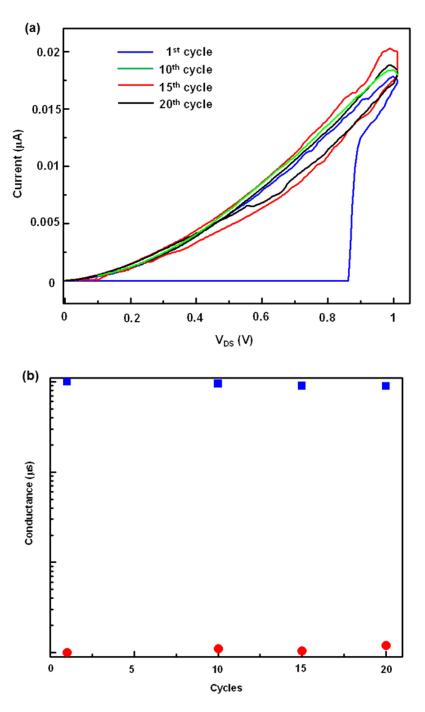

| Figure 3 | 9: (a) <i>I-V</i> characteristics of ZnO PRM cell (10-minute oxygen plasma treat for 20 cycles. The non-volatile characteristic of the ZnO PRM cell with 1 minute oxygen plasma treatment can be seen here. (b) Retention cycle test ZnO PRM cell (10-minute oxygen plasma treatment) for 20 cycles. | 0- |

| Figure 4 | 0: Temperature-dependent <i>I-V</i> measurements of PRM cells at strain-free                                                                                                                                                                                                                         |    |

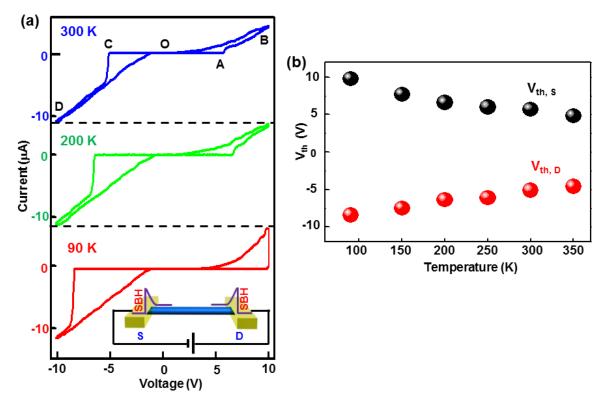

- Figure 40: Temperature-dependent *I-V* measurements of PRM cells at strain-free condition. (a) *I-V* characteristics of ZnO PRM cells at 300 K, 200 K and 90 K, respectively. (b) Dependence of threshold voltages on temperature. Both V<sub>th,S</sub> (in black) and V<sub>th,D</sub> (in red) increased in magnitudes almost linearly with the decreasing temperature.

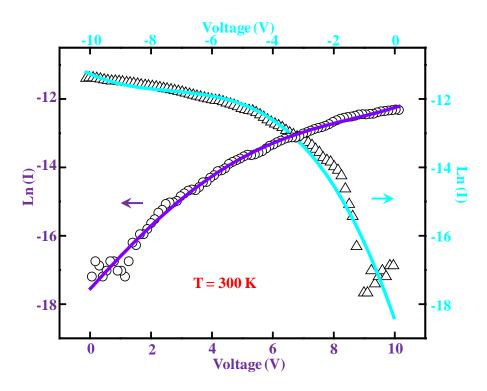

- Figure 41: I-V characteristic for PRM cell in region O-B and D-O in Figure 40. The numerical fitting curves show ln(I) linearly depends on  $V^{1/4}$ , which indicate thermionic emission-diffusion dominates the transport at the reverse-biased barriers.

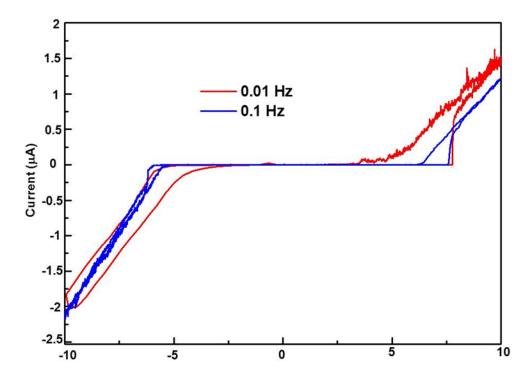

- Figure 42: *I-V* characteristics of PRM cell under sweeping of different rates. 90

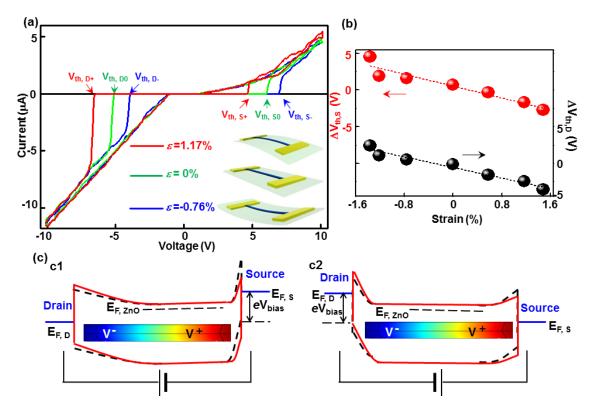

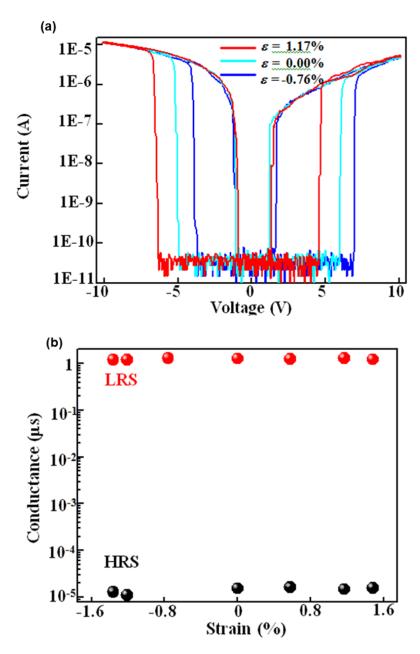

- Figure 43: Stain-modulated hysteretic switching of PRM cell. (a) *I-V* characteristics of ZnO PRM cells under tensile, zero and compressive strains respectively. (b) Dependence of threshold voltages on applied strains. (c) Schematic of banddiagram of PRM cell under tensile strain. c1, Schottky barrier at drain side is forward biased. c2, Schottky barrier at drain side is reversely biased. Red solid lines represent band-diagrams after tensile strain is applied. Black dashed lines represent band-diagrams under strain free condition.

- Figure 44: (a) Stain-modulated hysteretic switching curves of PRM cell in a semilogarithmic current scale. (b) Ratio of conductance at LRS and HRS for the PRM cell under different strains. The ratio of conductance at LRS and HRS remain steady at high values (~ 10<sup>5</sup>) under different strains, demonstrating the stable performance of the PRM cell.

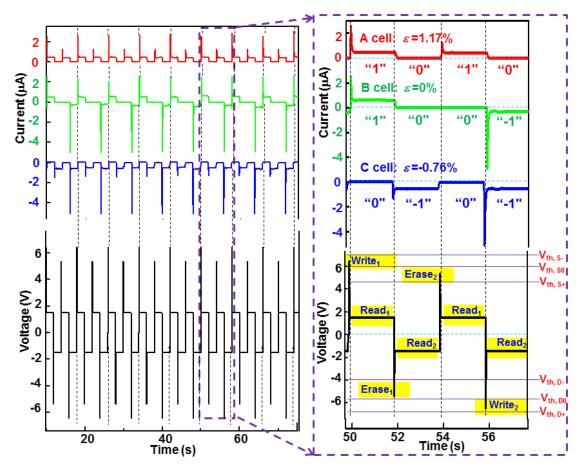

- Figure 45: Write/read access of PRM cell as an electromechanical memory.

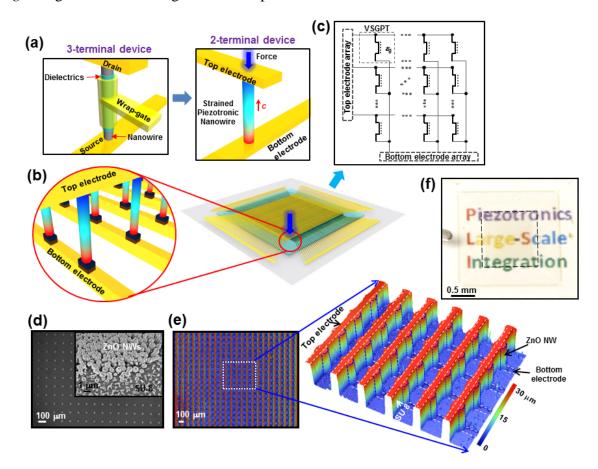

- Figure 46: Schematic illustration, optical and SEM images, and topological profile image of 3D SGVPT array assembly. (a) Structural transformation from three-terminal configuration of wrap-gate 3D NW FET (left) into two-terminal configuration of SGVPT (right). (b) Schematic illustration of a 3D SGVPT array with pixel density of 92 x 92 and scheme for spatial profile imaging of local stress. (c) Equivalent circuit diagram of the 3D SGVPT array. (d) SEM image of SGVPT array taken after etching-back the SU 8 layer and exposing top surfaces of the ZnO NWs. Inset, 30°-tilt view of the exposed ZnO NWs for single pixel. (e) Topological profile image of the SGVPT array (Top view). Inset, 3D perspective view of the topological profile image reveals the vertical hierarchy of the SGVPT assembly in which the color gradient represents different heights. (f) Optical image of the transparent 3D SGVPT array on flexible substrate.

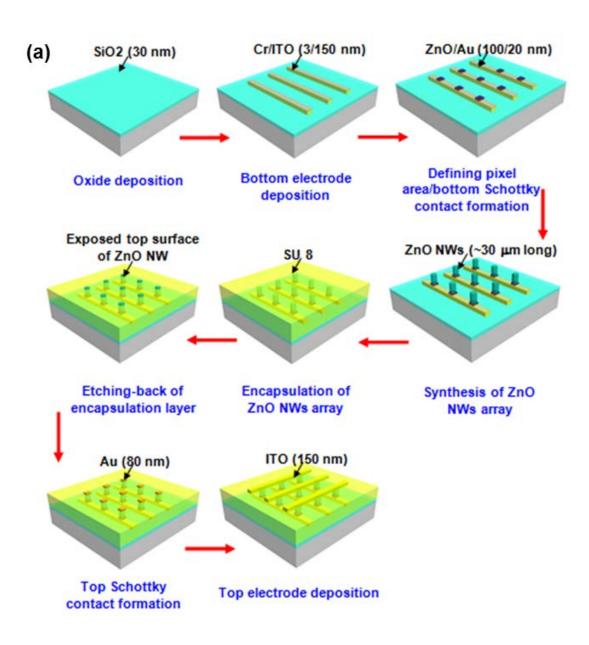

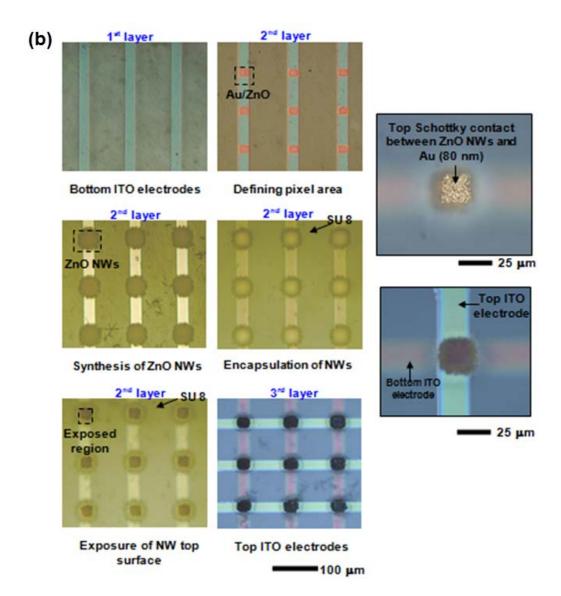

- Figure 47: (a) Schematic illustration of processing steps for fabricating 3D vertical piezotronic transistors array on a PET substrate. (b) Optical micrographs of 3D vertical piezotronic transistors array on a PET substrate. Inset (right) shows magnified image of top Schottky contacts and single pixel after 3<sup>rd</sup> layer processing.

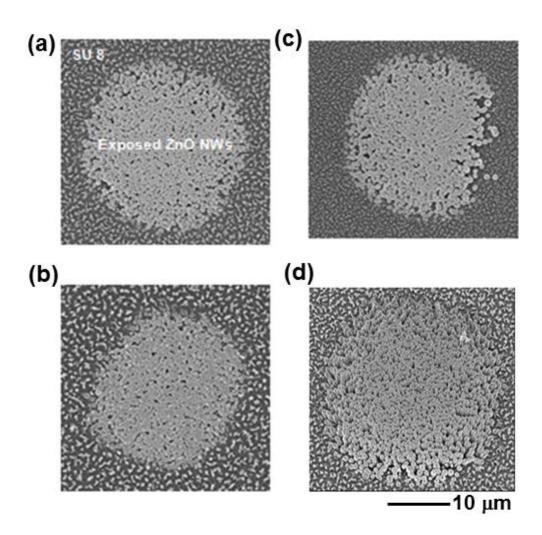

- Figure 48: (a-d) Scanning electron micrographs of 3D vertical piezotronic transistors array encapsulated by SU 8, with top surfaces of ZnO NWs exposed. (a-c): Top views of three selected pixels with SU 8 etched back. (d): 30° tilted view of single pixel with top surfaces of ZnO NWs exposed.

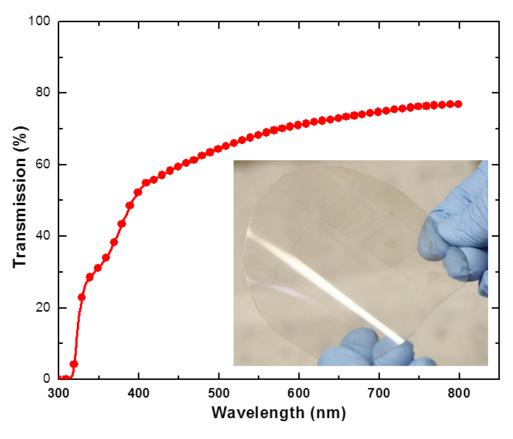

- Figure 49: Measured normal incidence transmission (T) spectra of 3D vertical piezotronic transistors array on a PET substrate. Inset: Optical image of 3D vertical piezotronic transistors arrays on a 4-inch PET substrate.

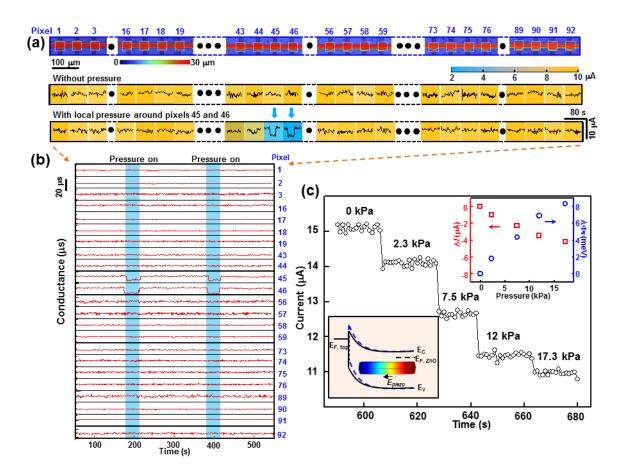

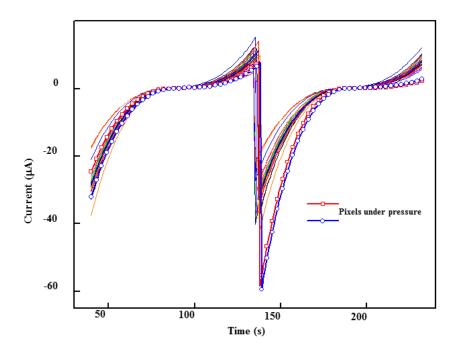

- Figure 50: Single-channel line-scan (1 x 92) electrical measurement for SGVPT array device. (a) Topological profile images (top view) and the current response from these 23 pixels under 1 V bias with and without external stress applied to certain localized region. (b) Single-channel conductance measurement in temporal domain with and without pressure applied. (c) Current responses for pixel 46 under different pressures. Top right inset, current variations (red squares) and derived changes in SBHs (blue circles) for the reversed biased top contact, both versus the applied pressures. Bottom left inset, schematic band-diagram illustrating the change in SBH of the reversed biased top contact due to the modulation effect of strain-induced piezopotential.

- Figure 51: Single-channel measurement confirming the piezotronic rather than piezoresistive characteristics of the conductivity change for SGVPT pixels under strain.

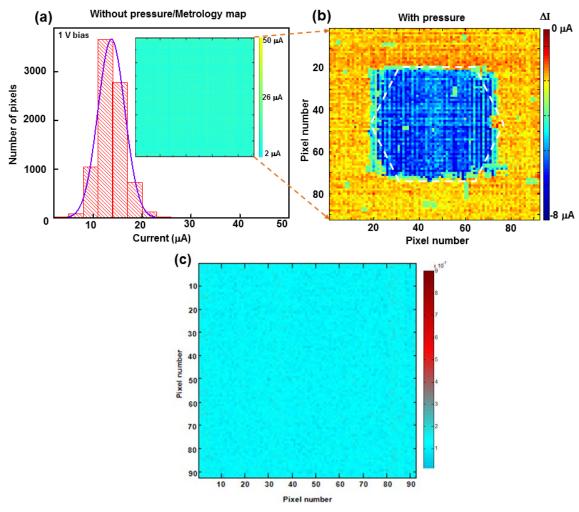

Figure 52: Tactile imaging by fully-integrated 92 x 92 SGVPT array. (a) Metrology mapping (Inset) and statistic investigation of the fully integrated SGVPT array without applying stress. (b) Current responses contour plot illustrating the capability of SGVPT array for imaging the spatial profile of applied stress. (c) Background noise test for the measurement system under 1 V bias.

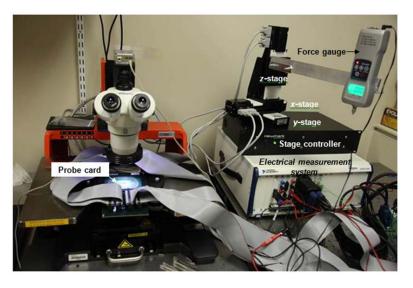

Figure 53: Experimental setup for multichannel multiplexed measurement and programmed mechanical inputs. 113

## LIST OF ABBREVIATIONS

CPU central processing unit

CMOS complementary metal-oxide-semiconductor

SEM scanning electron microscope

MOSFET metal-oxide-semiconductor-field-effect-transistor

PLD pulse laser deposition

HMTA hexamethylenetetramine

MEMS/NEMS micro/nano-electromechanical-system

AFM atomic force microscopy

FEM finite element method

PDMS polydimethylsiloxane

LED light-emitting-diode

SBH Schottky-barrier height

SGT strain-gated transistor

SGI strain-gated inverter

SVTC strain-voltage transfer characteristic

PRM piezotronic resistive memory

ITO Indium tin oxide

#### **SUMMARY**

Novel technology which can provide new solutions and enable augmented capabilities to CMOS based technology is highly desired. Piezotronic nanodevices and integrated systems exhibit potential in achieving these application goals. By combining laser interference lithography and low temperature hydrothermal method, an effective approach for ordered growth of vertically aligned ZnO NWs array with high-throughput and low-cost at wafer-scale has been developed, without using catalyst and with a superior control over orientation, location/density and morphology of as-synthesized ZnO NWs. Beyond the materials synthesis, by utilizing the gating effect produced by the piezopotential in a ZnO NW under externally applied deformation, strain-gated transistors (SGTs) and universal logic operations such as NAND, NOR, XOR gates have been demonstrated for performing piezotronic logic operations for the first time. In addition, the first piezoelectrically-modulated resistive switching device based on piezotronic ZnO NWs has also been presented, through which the write/read access of the memory cell is programmed via electromechanical modulation and the logic levels of the strain applied on the memory cell can be recorded and read out for the first time. Furthermore, the first and by far the largest 3D array integration of vertical NW piezotronic transistors circuitry as active pixel-addressable pressure-sensor matrix for tactile imaging has been demonstrated, paving innovative routes towards industrial-scale integration of NW piezotronic devices for sensing, micro/nano-systems and humanelectronics interfacing. The presented concepts and results in this thesis exhibit the potential for implementing novel nanoelectromechanical devices and integrating with MEMS/NEMS technology to achieve augmented functionalities to state-of-the-art CMOS technology such as active interfacing between machines and human/ambient as well as micro/nano-systems capable of intelligent and self-sufficient multi-dimensional operations.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Complementing device miniaturization with functional diversification

There has been an increasing demand in developing micro/nano-systems (MNS) for wireless and personal applications and it is predicted that the market for wireless sensor network (WSN) will grow rapidly from \$0.45 billion in 2011 to \$2 billion in 2021<sup>1</sup>. In addition to the conventional technology trajectory of miniaturizing components dimensions for enhanced operation performance as per Moore's law, which has been the principal roadmap that drives and directs the advancement of information technology in the last few decades, enormous efforts have been recently focused on integrating individual micro/nano-devices with diversified functionalities into multi-functional MNS and further into large-scale networks for potential applications in ultrasensitive chemical sensing<sup>2</sup>, remote and mobile environmental monitoring<sup>3</sup>, structural health monitoring<sup>4</sup>, homeland security<sup>5</sup>, portable/wearable biomedical devices and personal electronics <sup>6,7</sup>. In order to fulfill these application promises, each device/system node within the network should consist of low power microcontroller unit, high-performance data processing/storage components, wireless signal transceiver, ultrasensitive micro/nanoelectromechancial system (MEMS/NEMS) based sensors, and embedded energy powering units<sup>8-12</sup>.

Integration of these discrete devices with dedicated functionality toward self-powered smart systems is prospected to be one of the major roadmaps for electronics<sup>13</sup>. The miniaturized dimensions of nanomaterials together with the capability of modulating their compositions and obtaining unprecedented properties compared to bulk counterparts in well-controlled manners not only exhibit the potential for addressing some of the critical challenges faced by silicon-based microelectronics as technology node advances,

but also enable the possibility of incorporating diversified functionalities which do not necessarily scale as per Moore's Law into the systems to complement digital signal/data processing with augmented functional capabilities, such as interactions between machine and human/environment (Figure 1). Numerous nodes of such device/system can be spatially distributed and embedded virtually anywhere ranging from remote field, civil structures, to even human body for fulfilling respective purposes.

**Figure 1**. Future perspective of electronics beyond Moore's law. The vertical axis represents a miniaturization and increase of device density, CPU speed and memory capacity. The horizontal axis represents the diversity and functionality for personal and portable electronics. The future of electronics is an integration of CPU speed and functionality<sup>14</sup>.

#### 1.2 Interface between electronics and human/ambient

As the complement of digital signal/data processing, the aforementioned diversified functionalities include interaction between the device and ambient through appropriate transduction mechanism as well as embedded energy scavenging/storage

components for powering the device operations. In prospective applications such as prosthetics, artificial intelligence and robotics, electronic systems need to directly interface the ambient environment like the human body itself, which is abundant with activities and "signals" such as mechanical actions and electrical signals <sup>13</sup>. Transmission of electrical signals via neuron system inside human body have been investigated for decades and various approaches have been developed for interfacing neuron activities with silicon based electronics <sup>15-18</sup>. Mechanical actions, whereas, is not easy to be directly interfaced with silicon electronics without innovative design and approaches.

Traditionally, signals from transducers sensitive to strain variation can be probed and acquired by electronic devices. These signals, however, cannot be directly utilized to control silicon electronics.

One major focus in current research of flexible electronics is to minimize and eliminate the effect of strain introduced by the substrate on the performance of the electronic components built on a substrate, which can be termed as the passive flexible electronics. On the other hand, the deformation introduced by the substrate can be utilized to induce electrical signals that can be used directly for controlling Si based electronics. A "mediator" or "translator" is needed for the conjunction of bio-mechanical action and operation of silicon based electronics. The piezotronics and piezo-phototronics are invented for such purposes, and they are considered as the active flexible electronics or bio-driven electronics<sup>19-21</sup>, which enables novel approach for directly generating digital signals and electronic control using mechanical actions.

The role anticipated to be played by piezotronics is similar to the mechanosensation in physiology<sup>22</sup>. Mechanosensation is a response mechanism to mechanical stimuli. The physiological foundation for the senses of touch, hearing and balance, and pain is the conversion of mechanical stimuli into neuronal signals; the former is mechanical actuation and the latter is electrical stimulation. For instance,

mechanoreceptors of the skin are responsible for touch while tiny cells in the inner ear are responsible for hearing and balance.

#### 1.3 Thesis outline

This thesis consists of seven chapters. Following this introduction chapter is a discussion on the fundamental physics and concepts, such as piezopotential and piezotronic effect, in the field of piezotronics and related applications. The modulation effect of piezopotential on transport of charge carriers in metal-semiconductor contact and p-n junction, both of which are the essential building blocks for modern electronics, are also addressed and discussed in details in Chapter 2. Chapter 3 investigates the various synthesis processes for growing one-dimensional ZnO nanostructures for piezotronic applications. Synthesis methods based on vapor-solid (VS) and solution phase hydrothermal (HT) processes are discussed with more emphasis, since ZnO NWs obtained from VS process constitute the majority materials for fabricating single-NW based piezotronic applications, and ZnO NW arrays derived from HT process provide the material platform for realizing large-scale piezotronic array applications, particularly on flexible substrates. Other synthesis methods such as vapor-solid-solid (VSS) and pulsed laser deposition (PLD) processes are also discussed in Chapter 3 and their potential in realizing ZnO NWs array with high crystallinity, adjustable dopant type, doping levels and controllable bandgap engineering is also investigated. Chapter 4 demonstrates for the first time the piezotronic logic operations by utilizing the gating effect produced by piezopotential in a ZnO NW under externally applied deformation. Universal strain-gated logic operations such as NAND, NOR and XOR gates have been implemented by integration of ZnO NW based strain-gated transistors (SGTs). In contrast to the conventional CMOS logic units, the SGT based logic units are driven by mechanical agitation and rely only on *n*-type ZnO NWs without the presence of *p*-type semiconductor components. The mechanical-electronic logic units can be integrated with

NEMS technology to achieve advanced and complex functionalities in nanorobotics, microfluidics and micro/nano-systems, in which mechanical actions such as the movement of robots, fluidic flow and hydrostatic pressure induced in the micro-channels or micro-valves might be utilized for performing electromechanical logic operations for controlling and processing purposes. In Chapter 5, a novel nanoelectromechanical memory device has been presented. By utilizing the strain-induced polarization charges created at the semiconductor/metal interface under externally applied deformation as a result of piezotronic effect, the switching characteristics of the ZnO NW resistive switching devices can be modulated and controlled. It is further demonstrated that the logic levels of the strain applied on the memory cell can be recorded and read out for the first time utilizing the piezotronic effect, which has the potential for implementing novel nanoelectromechanical memories and integrating with NEMS technology to achieve micro/nano-systems capable of intelligent and self-sufficient multi-dimensional operations such as tactile sensing and imaging. As a critical step towards practical applications, Chapter 6 presents the first and by far the largest 3D array integration of vertical NW piezotronic transistors circuitry as active pixel-addressable pressure-sensor matrix for tactile imaging. The demonstrated highest spatial resolution and tactile sensitivity with the smallest pixel dimension and pitch size present the landmark breakthrough in implementing 3D piezotronic transistor arrays and pave innovative routes towards industrial-scale integration of NW piezotronic devices for sensing, micro/nano-systems and human-electronics interfacing. Finally, Chapter 7 concludes this thesis and provides discussions and prospects on potential future work in related field.

#### **CHAPTER 2**

#### PIEZOPOTENTIAL AND PIEZOTRONIC EFFECT

In order to realize augmented capabilities such as interfacing between machine and human/ambient, a direct control over the operation of electronic devices by mechanical action is highly desired. Since silicon-based CMOS devices operate via electrically-modulated charge transport process, it is necessary to utilize electric signal which can be generated by mechanical action.

#### 2.1 Piezopotential

Piezoelectricity is a phenomenon which produces electrical potential in the material upon variations of applied pressure/stress. The piezoelectric effect can be interpreted as the linear electromechanical coupling/interaction between mechanical and electrical state in materials which lack inversion symmetry<sup>23</sup>. Piezoelectricity has been observed in a wide range of materials from ceramics, synthetic polymers to biological materials in response to applied mechanical stress. The most well-known piezoelectric material is Perovskite -structured Pb(Zr<sub>x</sub>Ti<sub>1-x</sub>)O<sub>3</sub> (PZT), which has numerous applications in electromechanical sensing, actuating and energy harvesting <sup>24-26</sup>. Traditionally, investigation and application of piezoelectric materials have been largely carried out by the ceramics community. PZT, however, is electrically-insulating and hence less useful for building electronic devices. In addition, the extremely brittle nature of ceramic PZT films and existence of lead impose issues such as reliability, durability and safety for long term sustainable operations and hinder its applications in areas such as biomedical devices.

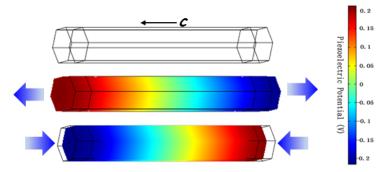

**Figure 2**. Piezopotential in Wurtzite crystal. (a) Atomic model of the Wurtzite-structured ZnO. (b) Left, large-scale aligned ZnO nanowire (NW) arrays by solution based hydrothermal approach<sup>27</sup>. Right, distribution of piezopotential along a ZnO NW under axial strain calculated by numerical methods<sup>28</sup>. The growth direction of the NW is along *c*-axis.

On the other hand, semiconductor materials with Wurtzite structures such as ZnO, GaN, InN and ZnS also possess piezoelectric properties but are not as extensively utilized in piezoelectric sensors and actuators as PZT due to their relatively small piezoelectric coefficients<sup>29</sup>. ZnO, for example, has a crystal structure with non-central symmetry, which naturally produces piezoelectric effect upon strained. The unique properties of ZnO, such as photo-excitation, biocompatibility and degradability<sup>30</sup>, in addition to its semiconductor, pyroelectric and piezoelectric characteristics, enable the wide utilizations and applications of ZnO nanomaterials in sensing<sup>31</sup>, energy conversion and scavenging<sup>32</sup>, light-emitting diodes<sup>33</sup> and piezotronics<sup>11,29</sup>.

Wurtzite ZnO crystal has a hexagonal structure with a large anisotropic property in c-axis direction and perpendicular to the c-axis. The  $Zn^{2+}$  cations and  $O^{2-}$  anions are tetrahedrally coordinated and the centers of the positive ions and negatives ions overlap

with each other. If a stress is applied at an apex of the tetrahedron, the centers of the cations and anions are relatively displaced, inducing a dipole moment (Figure 2a). A constructive addition of all the dipole moments within all of the units in the crystal results in a macroscopic potential drop along the straining direction in the crystal. This is the piezoelectric potential (*piezopotential*) (Figure 2b)<sup>29</sup>.

## Transversely deflected nanowire

**Figure 3**. Distribution of piezopotential in two typical configurations of NW devices. The color gradient represents the distribution of piezopotential in which red indicates positive piezopotential and blue indicates negative piezopotential.

Piezopotential is the strain-induced inner crystal field, which is created by non-mobile and non-annihilative ionic charges. Therefore piezopotential exists as long as the applied strain maintains. Piezopotential can also drive the flow of electrons in the external load when the materials are subjected to mechanical deformation, which is the fundamental of the nanogenerator<sup>34,35</sup>. The distribution of piezopotential has been investigated based on two typical configurations of NW devices: transversely deflected NW and axially strained NW (Figure 3). The transversely deflected NWs are normally utilized in nanogenerator applications<sup>32</sup>, while the axially strained NWs are used in piezotronic applications on flexible substrates<sup>30</sup>. The following sections will briefly discuss the fundamental theory for calculating the distribution of piezopotential in nanostructures without and with considering the presence of finite doping. The finite

conductivity possessed by the material can partially screen the regional piezopotential accordingly, but cannot completely cancel the effect of polarization charge due to the dielectric property of the material and the moderate doping level.

#### 2.1.1 Piezopotential distribution in transversely deflected NW

Numerous efforts have been put into investigating piezoelectricity in one-dimensional nanostructures, including first-principle calculations<sup>36,37</sup>, molecular dynamics (MD) simulations<sup>38</sup> and modeling based on continuum theory<sup>39</sup>. However, it is rather cumbersome to implement first-principle theory and MD simulation for studying piezoelectricity in nanoscale system due to the huge number of atoms incorporated in these systems (typical dimension of a nanoscale system is ~ 50 nm in diameter and ~2 micron in length). The continuum model, however, is insightful since it provides the criterion for distinguishing between mechanically dominated regime and electro-statically dominated regime<sup>39</sup>. Wang's group previously established a continuum model for evaluating the electrostatic potential in a laterally bent NW<sup>40</sup>.

The configuration of laterally bent NW is commonly utilized in nanogenerator and potential novel piezotronic applications<sup>41-43</sup>. The theoretical objective is to derive the relationship between the piezopotential distribution in a laterally bent NW and the dimensionality of the NW as well as the magnitude of the applied force at the tip. The governing equations for a static piezoelectric material include mechanical equilibrium equation (Equations 1), constitutive equation (Equations 2), geometrical compatibility equation (Equation 3) and Gauss equation of electric field (Equation 4)<sup>40</sup>. The mechanical equilibrium condition when there is no body force  $\vec{f}_e^{(b)} = 0$  acting on the nanowire is:

$$\nabla \cdot \sigma = \vec{f}_e^{(b)} = 0 \tag{1.1}$$

Here  $\sigma$  is the stress tensor, which is related to strain  $\varepsilon$ , electric field E and electric displacement D by constitutive equations:

$$\begin{cases}

\sigma_p = c_{pq} \varepsilon_q - e_{kp} E_k \\

D_i = e_{iq} \varepsilon_q + \kappa_{ik} E_k

\end{cases}$$

(1.2)

Here  $c_{pq}$  is the linear elastic constant,  $e_{kp}$  is the linear piezoelectric coefficient, and  $k_{ik}$  is the dielectric constant. The contribution of spontaneous polarization resulting from the polar charges on the  $\pm (0001)$  polar surfaces, which are the top and bottom ends of the NW, are not taken into consideration here in equation  $1.2^{44}$ . By considering the  $C_{6v}$  symmetry of Wurtzite-structured ZnO crystal,  $c_{pq}$ ,  $e_{kp}$  and  $k_{ik}$  can be expressed in the following reduced forms:

$$c_{pq} = \begin{pmatrix} c_{11} & c_{12} & c_{13} & 0 & 0 & 0\\ c_{12} & c_{11} & c_{13} & 0 & 0 & 0\\ c_{13} & c_{13} & c_{33} & 0 & 0 & 0\\ 0 & 0 & 0 & c_{44} & 0 & 0\\ 0 & 0 & 0 & 0 & c_{44} & 0\\ 0 & 0 & 0 & 0 & 0 & \frac{(c_{11} - c_{12})}{2} \end{pmatrix}$$

(2.1)

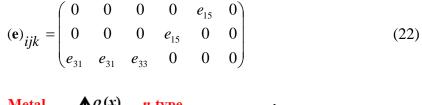

$$e_{kp} = \begin{pmatrix} 0 & 0 & 0 & 0 & e_{15} & 0 \\ 0 & 0 & 0 & e_{15} & 0 & 0 \\ e_{31} & e_{31} & e_{33} & 0 & 0 & 0 \end{pmatrix}$$

(2.2)

$$\kappa_{ik} = \begin{pmatrix} \kappa_{11} & 0 & 0 \\ 0 & \kappa_{11} & 0 \\ 0 & 0 & \kappa_{33} \end{pmatrix}$$

(2.3)

Meanwhile, strain  $\varepsilon_{ij}$  must also satisfy the geometrical constraint set by the compatibility equation:

$$e_{ilm}e_{jpq}\frac{\partial^2 \varepsilon_{mp}}{\partial x_l \partial x_q} = 0 \tag{3}$$

Here  $e_{ilm}$  and  $e_{jpq}$  are Levi-Civita anti-symmetric tensors<sup>40</sup>.

Finally, for simplicity of derivation, Gauss equation must be satisfied by assuming no free charge  $\rho_e^{(b)}$  in the NW:

$$\nabla \cdot \vec{D} = \rho_e^{(b)} = 0 \tag{4}$$

This indicates that the governing equation (4) only applies to insulating piezoelectric materials, while in reality, piezoelectric materials such as ZnO is intrinsically *n*-type doped due to the unavoidable native defects<sup>45</sup>. More sophisticated models considering finite doping in ZnO NWs will be discussed later.

The above governing equations (1-4) together with appropriate boundary conditions will give the complete description of a static piezoelectric system. However, solution to these equations is rather complex, and analytical solution does not exist in many cases. In order to derive an approximate solution to these equations for providing the basic physical picture, Gao *et al* carried out perturbation expansion of the linear equations to simplify the analytical solution<sup>40</sup>. The NW is assumed to have a uniform cylindrical shape with diameter 2a and length l. The strain and stress relation is thus given by<sup>40</sup>:

$$\begin{pmatrix}

\mathcal{E}_{xx} \\

\mathcal{E}_{yy} \\

\mathcal{E}_{zz} \\

2\mathcal{E}_{yz} \\

2\mathcal{E}_{zx} \\

2\mathcal{E}_{xy}

\end{pmatrix} = \sum_{q} a_{pq}^{isotropic} \sigma_{q} = \frac{1}{E} \begin{pmatrix}

1 & -v & -v & 0 & 0 & 0 \\

-v & 1 & -v & 0 & 0 & 0 \\

-v & -v & 1 & 0 & 0 & 0 \\

0 & 0 & 0 & 2(1+v) & 0 & 0 \\

0 & 0 & 0 & 0 & 2(1+v) & 0 \\

0 & 0 & 0 & 0 & 0 & 2(1+v)

\end{pmatrix} \begin{pmatrix}

\sigma_{xx} \\

\sigma_{yy} \\

\sigma_{zz} \\

\sigma_{yz} \\

\sigma_{zx} \\

\sigma_{xy}

\end{pmatrix} (5)$$

where *E* is Young's modulus and v is Poisson ratio.

In the configuration of transversely deflected NW, the lateral force  $f_y$  is assumed to be applied uniformly on the top surface of NW so that there is no effective torque which twists the NW<sup>40</sup>. By applying Saint-Venant principle to simplify the boundary condition, the maximum potential on the surface (r = a) of the NW at the tensile (T) side  $(\theta = -90^{\circ})$  and the compressive (C) side  $(\theta = 90^{\circ})$  has been obtained in the following expression:

$$\varphi_{\text{max}}^{(T,C)} = \pm \frac{1}{\pi} \frac{1}{\kappa_0 + \kappa_\perp} \frac{f_y}{E} [e_{33} - 2(1 + \nu)e_{15} - 2\nu e_{31}] \frac{1}{a}$$

(6)

Here  $\kappa_{\perp} = \kappa_{11} = \kappa_{22}$  and  $\kappa_0$  is the permittivity in vacuum. Furthermore, by applying fundamental elastic theory, the lateral force  $f_y$  is related to maximum deflection of the NW tip  $v_{max} = v$  (z = l) under small deflection by:

$$v_{\text{max}} = \frac{f_{y}l^{3}}{3EI_{yy}} \tag{7}$$

Consequently, the maximum potential at the NW surface can be expressed as  $^{40}$ :

$$\varphi_{\text{max}}^{(T,C)} = \pm \frac{3}{4(\kappa_0 + \kappa_\perp)} [e_{33} - 2(1+\nu)e_{15} - 2\nu e_{31}] \frac{a^3}{l^3} v_{\text{max}}$$

(8)

Since Saint-Venant principle is applied to simplify the boundary condition, equation (8) is valid only for regions far away from the fixed end of the NW. Subsequent full numerical calculation shows the above equation is feasible when the distance from the fixed end is larger than twice the NW diameter<sup>40</sup>. Equation (8) indicates that electric potential (in cylindrical coordinates) is independent of vertical height z, which suggests that the potential is uniform along z direction except for regions very close to the fixed end of the NW. Moreover, electrostatic potential is directly related to the aspect ratio of the NW instead of its absolute dimensionality. For a NW with a fixed aspect ratio, the induced piezopotential is proportional to the maximum deflection at the NW tip.

The validity of derived analytical equation (8) in describing the piezopotential distribution in transversely deflected NW has also been verified by comparing results obtained from equation (8) and finite element method (FEM) calculation for a fully coupled electro-mechanical system using equations (1-4)<sup>40</sup>. Figure 4 shows the comparison between results given by both methods and it reveals that the difference between results derived from analytical equation and those from full numerical calculation is only 6%.

**Figure 4.** Potential distribution for a ZnO NW with d = 50 nm and l = 600 nm experiencing a lateral bending force of 80 nN. (a) and (b) are the side and top cross-sectional (at  $z_0 = 300$  nm) piezopotential output in the NW obtained by finite element calculation using fully coupled equations (1-4), while (c) is the cross-sectional piezopotential output calculated by analytical equation (8). (d) gives a comparison of the line-scan profiles from both (b) and (c), showing the accuracy of equation (8) and approximations applied for deriving it (blue line is for result obtained from full finite element method (FEM) and red line is for result given by equation (8))<sup>40</sup>.

#### 2.1.2 Piezopotential distribution in axially strained NW

Another commonly encountered configuration for ZnO NW based nanoelectronic device incorporates the horizontally placed Wurtzite ZnO NW, with its two ends and regions close to the ends fully covered by metal electrodes on the substrate (normally flexible material). The dimension of NWs is orders of magnitude smaller than that of the supporting substrates so that the mechanical behavior of the entire device is dictated by the substrate. In reality, various kinds of forces, including tensile, compression, twisting and combinations of them, might act on the NW during operation<sup>28</sup>. The fully coupled

equations (1-4) can be solved with finite element method (FEM) and corresponding distribution of piezopotential throughout the NW under these forces can then be obtained<sup>28</sup>. For simplicity and concentrating on how the piezopotential would vary under different strains, it is assumed that there is no body force and no free charge carriers in the NW. Figure 5 (top) shows a ZnO NW without any applied force. The total length of the NW is 1200 nm with a 100 nm length of contact domain at each end, and the side length of the hexagon is 100 nm. When an axial stretching force of 85 nN uniformly acts on the NW in the direction parallel to c-axis, as shown in Figure 5 (middle), a potential drop of approximately 0.4 V is induced between the two ends of the NW. When the applied force changes to compressive type, the magnitude of the induced piezopotential remains at 0.4 V while its polarity reverses (Figure 5, bottom)<sup>28</sup>. It can be seen clearly that piezopotential continuously drops from one side of the NW to the other, indicating that electron energy also continuously increases from one end of the NW to the other. Meanwhile, the Fermi level remains flat all over the NW at equilibrium. Consequently, the electron energy barrier between ZnO and metal electrodes will be raised at one side and lowered at the other side, which should lead to experimentally observable asymmetric I-V characteristics for the NW device. This is the governing principle for understanding the experimental results presented in later sessions of this thesis.

**Figure 5.** Numerical calculation results of the piezopotential distribution in a ZnO NW without considering the doping. (Top) An unstrained ZnO NW grown along *c*-axis. (Middle) Distribution of piezopotential together with deformed shape for the NW by stretching force and (Bottom) by a compressing force of same magnitude<sup>28</sup>.

The effect of piezoelectricity on transport properties of metal-ZnO NW device contains two parts: one is the spontaneous polarization charge effect induced by the Zn<sup>2+</sup> and O<sup>2-</sup> terminating layers at the +*c* and -*c* end surfaces of NW structure<sup>44</sup>; the other is the piezopotential effect introduced by piezoelectric polarization charges. Strain will not only induce piezoelectric effect in ZnO, but also cause variations in band structure. The induced deformation potential can also change the height of Schottky barrier formed between ZnO and metal electrodes: under tensile strain the barrier will be lowered, and under compressive strain the barrier will be raised. However, variations at the two ends of NW caused by change in band structure are identical, which cannot switch the I-V characteristics of the device from linear Ohmic type to nonlinear rectifying type. This is the conventionally-known piezoresistive effect<sup>46</sup>.

#### 2.1.3 Piezopotential distribution in doped semiconductor NW

It is also important to point out that the above results are all based the assumption that there are no free charge carriers in the materials<sup>28</sup>. The as-synthesized ZnO nanostructures are, however, intrinsically n-type with a typical donor concentration of  $1\times10^{17}$  cm<sup>-3</sup> <sup>47</sup>. Taking into account the statistical electron distribution, the distribution of piezopotential in a bent ZnO NW (of which the dimension is not too small) with moderate charge carrier density can be calculated, showing that free electrons tend to accumulate at the positive piezopotential side of the NW at thermal equilibrium<sup>48</sup>. Therefore, the effect of negatively charged carriers is partially, if not all, screening the positive piezopotential, while no change to the negative piezopotential can be observed. Figure 6 shows the calculated piezopotential when the donor concentration in the ZnO NW is  $1\times10^{17}$  cm<sup>-3</sup>, which clearly presents the screening effect of finite donor concentration on the distribution of piezopotential<sup>48</sup>. The piezopotential maximum in the positive side is significantly reduced from ~0.3 V in Figure 6d, which corresponds to the case when ZnO in assumed to be insulating, to less than 0.05 V in Figure 6b, which

considers the moderate doping in ZnO. Meanwhile it can be seen clearly that the induced piezopotential in negative side is very well preserved<sup>48</sup>. This is also consistent with the experimental observation that only negative pulses can be observed in an AFM based nanogenerator experiment using *n*-type ZnO NWs and the output negative potential peak appears only when the AFM tip touches the compressed side of the NW<sup>32</sup>. For even smaller systems, strong confinement effect requires quantum mechanical considerations due to discrete bound states in the materials. In such a case, an elaboration in theory similar to two-dimensional-electron-gas (2DEG) in GaN/AlGaN high-electron-mobility-transistors (HEMTs) is necessary for investigating the effect of piezopotential<sup>49</sup>.

In addition to the n-type doping normally observed for as-synthesized ZnO NWs, it is also possible to receive stable p-type ZnO NWs<sup>50-52</sup>. The stability of p-type doping in ZnO NWs is possible due to the dislocation free volume and the presence of high concentration of vacancies near the surface of the NWs<sup>53</sup>. The distribution of piezopotential in a bent p-type ZnO NW has also been theoretically investigated previously. With a finite p-type doping, the holes tend to accumulate at the negative piezopotential side. The negative side is thus partially screened by holes while the positive side of the piezopotential preserves. For a typical ZnO NW with diameter of 50 nm, length of 600 nm and acceptor concentration of  $1 \times 10^{17} \text{cm}^{-3}$  under a bending force of 80 nN, the piezopotential in the negative side is  $\sim$  -0.05 V and is  $\sim$  0.3 V at the positive side (Figure 7). This suggests that the piezopotential in p-type ZnO NW is dominated by the positive piezopotential at the tensile side of surface<sup>50</sup>.

**Figure 6.** Numerical calculation results of the piezopotential distribution in a ZnO NW considering finite doping with donor concentration of  $1 \times 10^{17}$  cm<sup>-3</sup>. The dimension of the NW is: a = 25 nm, l = 600 nm and the external force is  $f_y = 80$  nN. (a) Piezopotential distribution of the cross section at x = 0. (b) Cross section plot of the piezopotential at z = 400 nm. (c and d) Calculation results for the case without considering the doping inside ZnO NW. (c) shows the cross section plot of piezopotential at z = 0. (d) shows the cross section plot of the piezopotential at z = 400 nm<sup>-48</sup>.

**Figure 7.** Calculated distribution of piezopotential in a p-type ZnO NW when transversely deflected<sup>50</sup>.

#### 2.2 Piezotronic effect