# Optimizing Implementations of Lightweight Building Blocks

Jérémy Jean<sup>1</sup>, Thomas Peyrin<sup>2</sup>, Siang Meng Sim<sup>2</sup> and Jade Tourteaux<sup>1,3</sup>

<sup>1</sup> Agence nationale de la sécurité des systèmes d'information (ANSSI) Crypto Lab, Paris, France Jeremy.Jean@ssi.gouv.fr

<sup>2</sup> Nanyang Technological University, Singapore, Singapore Thomas.Peyrin@ntu.edu.sg,crypto.s.m.sim@gmail.com <sup>3</sup> Paris Diderot University, Paris, France Jade.Tourteaux@gmail.com

**Abstract.** We study the synthesis of small functions used as building blocks in lightweight cryptographic designs in terms of hardware implementations. This phase most notably appears during the ASIC implementation of cryptographic primitives. The quality of this step directly affects the output circuit, and while general tools exist to carry out this task, most of them belong to proprietary software suites and apply heuristics to any size of functions. In this work, we focus on small functions (4- and 8-bit mappings) and look for their optimal implementations on a specific weighted instructions set which allows fine tuning of the technology.

We propose a tool named LIGHTER, based on two related algorithms, that produces optimized implementations of small functions. To demonstrate the validity and usefulness of our tool, we applied it to two practical cases: first, linear permutations that define diffusion in most of SPN ciphers; second, non-linear 4-bit permutations that are used in many lightweight block ciphers. For linear permutations, we exhibit several new MDS diffusion matrices lighter than the state-of-the-art, and we also decrease the implementation cost of several already known MDS matrices. As for non-linear permutations, LIGHTER outperforms the area-optimized synthesis of the state-of-the-art academic tool ABC. Smaller circuits can also be reached when ABC and LIGHTER are used jointly.

**Keywords:** LIGHTER  $\cdot$  Implementation  $\cdot$  ASIC  $\cdot$  Lightweight Block Ciphers  $\cdot$  Boolean function  $\cdot$  Meet-in-the-Middle  $\cdot$  Sbox  $\cdot$  MDS Matrix

## 1 Introduction

Pervasive computing is becoming increasingly important in many applications of our daily life. Lightweight devices such as RFID tags and wireless sensor nodes might manipulate sensitive data and thus usually require some security. Yet, classical cryptographic algorithms may not be very suitable for this type of applications, especially for very constrained environments. As a consequence, lightweight cryptography has become an extremely active research topic in the recent years, with several new lightweight symmetric-key primitives being proposed, e.g., [BJK<sup>+</sup>16, SIH<sup>+</sup>11, BKL<sup>+</sup>07, SMMK13, BSS<sup>+</sup>13]. In this context, there have been many advances in finding the best possible and in particular the most lightweight building bricks to design a symmetric-key primitive. In particular, diffusion matrices [KPPY14, SKOP15, LS16, LW16, BKL16] and Sboxes [UDCI<sup>+</sup>11, Osv00, Saa12, Can05, CDL16] were thoroughly scrutinized as they are considered classical components of modern SPN ciphers.

(CC) BY

What criterion to optimize for lightweight applications might significantly vary depending on the exact application (area, throughput, energy, power), but compact implementations, i.e. minimizing the area required by the hardware implementation, is generally considered of major importance as it represents a direct constraint in practice (even though the technology evolved since then, it was for example expected in 2005 that an RFID tag could spend at most 2000 GE for its security [JW05]), and also indirectly affect energy and power consumptions. Usual figures of area reported for cryptographic implementations usually contain the cost of storage – the registers that hold the key and the internal state – as well as the combinatorial logic, which implements the actual operations. Therefore, minimization of storage cost and combinatorial logic cost (by the means of reducing the number of operations required to apply the cryptographic function) is a very desirable goal. This can be achieved by design (for example by selecting a sparse diffusion matrix in a hope to reduce the total number of XORs required to compute it), but the study of their actual implementation can have a significant impact as well, and is often overlooked.

There are many different types of hardware implementations (serial, round-based, fully unrolled, and other variations) and many different technologies available, each having its own set of logic operations costs for example. All of these dimensions offer countless opportunities for optimization and it is not trivial for a researcher or an engineer to find the optimal hardware implementation for his own particular scenario. One can even extend this observation to other platforms and other criteria than area: How can I optimize this cipher on software since the logical operations' costs are very different than for hardware? How can I optimize the implementation of this lightweight cipher when I care about the delay and not the area? An optimized implementation from the designers might not be optimized for other use-cases, as we will see later.

For symmetric-key primitives, it is therefore interesting to study given an Sbox or given a certain linear diffusion layer what is the best possible (or at least a very good) implementation for a particular environment and how it can be obtained. Most of the time, this work is performed by synthesizers that convert small lookup tables (LUT) to boolean circuits: the implementer will design the general architecture of the cipher, but will leave the optimization of the small components to automated tools. While these tools do an excellent job at improving performances for generic functions, their output might not be optimal.

**Our Contributions.** In this article, we propose a new automated tool, LIGHTER, <sup>1</sup> that can either search for new lightweight cryptographic components or find optimized implementations of lightweight components, such as Sboxes or diffusion matrices. This tool is based on several advances.

First, we introduce a graph-based meet-in-the-middle (MITM) search algorithm that can generate an efficient implementation of a small (linear or non-linear) function given a certain set of available instructions and their corresponding costs. This algorithm is simple yet extremely generic and can be used for many purposes. The most obvious utilization is to compute the smallest implementation of lightweight encryption building blocks, by encoding the logical instruction area costs inside the algorithm's input costs. This allows an implementer to easily obtain very good implementations that exactly match his hardware configuration. The algorithm can also be used to optimize for delay instead of area, or to compute the best software implementation (by simply setting all the logic operations to the same cost). Another example would be to minimize the amount of linear or non-linear operations of a given function by setting the operations cost accordingly, which would be very useful for multi-party computation, zero-knowledge proofs, masking against side-channel attacks or fully homomorphic encryption schemes [ARS+15]. More utilizations are probably possible.

$<sup>^{1} \</sup>verb|http://jeremy.jean.free.fr/pub/fse2018_layer_implementations.tar.gz|$

The time and memory complexities of this first algorithm are directly related to the number of instructions considered in the implementation, which can therefore grow beyond practical ranges for high numbers of instructions. Thus, we propose in a second part another algorithm that computes good (but not-necessarily optimal) implementations of small functions, without specific limitation on the number of instructions. The idea is to perform a divide-and-conquer approach and improve locally sub-parts of a given starting implementation. This approach can therefore be seen as a tradeoff between optimality of the output and tractability of the computation.

Combining both algorithms leads to very good results. Namely, we first examine the area-optimized implementation of finite field multiplications over  $GF(2^4)$  and  $GF(2^8)$  and show that many multiplication coefficients are actually much cheaper than originally thought. This allowed us not only to find new best diffusion matrices (for example the new best  $4 \times 4$  involutory diffusion matrix over  $GF(2^4)$ ), but also to improve the implementation of many existing ones (the diffusion matrices of the AES block cipher, the WHIRLPOOL or Grøst1 hash functions being some of them).

Linear layers are not the only components that can be handled. We apply LIGHTER to search for area-optimized implementations of several 4-bit Sboxes and we show that our tool outperforms the state-of-the-art synthesis tool ABC almost all the time. Besides, when given the output from our tool, ABC improves over its own implementation obtained from the lookup table of the Sbox. We note that due to legal reasons, we only compare our algorithms to the academic tool ABC and not with other proprietary widely-used algorithms, whose usage are restricted by non-disclosure agreements. However, we are confident that similar conclusions could be drawn with such tools.

LIGHTER does have some limitations. For example, it does not always guarantee that a given implementation is optimal according to the constraints provided as input. This is particularly true for non-linear layers, as we need to combine several operations to ensure that the instructions used are invertible. Besides, unlike for general synthesizers, LIGHTER will mainly work for small functions (like 4-bit Sboxes) since for larger sizes, the tool will require too much memory and computation. Yet, this limitation does not apply to most lightweight designs for which small cryptographic components are a requirement. Finally, we emphasize that LIGHTER is currently not handling the case of optimizing FPGA implementations, which requires a very different optimization strategy.

**Organization of the Paper.** In Section 2, we first recall some previous works on the implementation of linear and non-linear layers and we introduce some preliminary notions. Then, in Section 3, we introduce two algorithms that search for efficient implementations of small functions, the core of our tool LIGHTER. In Section 4, we propose several heuristics to further help the efficient implementations search, and in Section 5 several implementation improvements of known matrices, but also new efficient matrix candidates. Eventually, we provide further results by application of the tool on non-linear layers in Section 6.

## 2 Preliminaries

## 2.1 Previous Work

In the past few years, there has been an important focus on lightweight cryptography with several new research directions. Among them, we can distinguish two main dimensions, which are the search/implementation of linear/non-linear layers. We recall briefly some of the main results related to our paper in the following.

Linear Layers. Most of the recent work focuses on searching for lightweight maximum distance separable (MDS) diffusion matrices to be used in SPN, that is matrices that

provide maximum diffusion property. In [KPPY14], the authors proposed quantifying the hardware implementation cost of diffusion matrices by counting the number of XOR gates needed to implement the linear layer (simply called XOR count of the matrix). Several works like [SKOP15, LS16, LW16, SS16b] adopted this metric and search for different types of lightweight diffusion matrices. In [BKL16], the authors used a single field element to construct new lightweight left-circulant matrices. Notably in [LW16], the authors considered invertible binary matrices as the entries of the diffusion matrix rather than field elements. The non-commutative property of the invertible binary matrices allows them to construct involution (self-inverse) MDS circulant matrices of order 4 and 8, which was proven to be non-existent over finite fields  $GF(2^n)$  [GR15]. More details about these papers will be discussed in Section 5.2.

Non-linear Layers. The research line studying the implementation of cryptographic non-linear functions with few input variables (e.g., less than eight) falls within the much broader domain of logic synthesis [DGK94]. There have been extensive research in this area, in particular with applications to Very Large Scale Integration (VLSI), see [BHMSV84] for instance. While general circuit minimization problems are known to be  $\Sigma_2^P$ -complete [BU08], there are several heuristic algorithms that provide suboptimal solutions, such as BOOM [HF01] or the more commonly used ESPRESSO algorithm [Rud86], which is probably implemented in many commercial synthesizers.

In the particular case of small cryptographic building blocks (e.g., 4-bit to 4-bit functions), the same heuristics algorithms seem to be used by the general synthesizers but it does not seem infeasible to reach optimal solutions due to the small dimension of the problem. Several academic papers carry out either full or partial exhaustive searches on the 4-bit permutations space from different points of view. Indeed, this search space has a size within practical reach (even without elaborated pruning strategies) as it "only" contains  $2^4! \approx 2^{44.2}$  permutations.

For instance in [UDCI<sup>+</sup>11], the authors look for efficient bit-sliced implementations of 4-bit permutations grouped in affine equivalence classes. The enumeration relies on a depth-first traversal of a tree labeled by permutations, where one goes down one level by applying one operation from AND, OR, XOR, NOT, and MOV. The search uses extra memory unit (in the form on an additional temporary register) and applies the rules from Osvik [Osv00], which essentially provide ways to add cuts in the tree (idea initially applied to optimize the software implementation of SERPENT [BAK98]). The results described by the authors cover about 90% of the search space, and they derive a very small 9-instruction software implementation of a 4-bit permutation with good cryptographic properties (differential probability and absolute linear bias being  $2^{-2}$ ).

In [Saa12], Saarinen enumerates and classifies all 4-bit permutations up to permutation equivalence (about  $2^{27}$  equivalence classes). One of the reasons to introduce this class pertains to the similarity of the implementations of the elements within the same class, which in general is not the case for the elements within a same affine equivalence class. The main contribution of the paper is the classification of the permutation equivalence classes with respect to cryptographic properties and the introduction of so-called Golden Sboxes which maximize all these criteria.

More recently, Boyar, Matthews and Peralta introduced in [BMP13] a new technique for combinational logic optimization which essentially relies on a two-step algorithm successively reducing the number of non-linear then linear gates required. They apply this algorithm to the AES Sbox and improve upon previous results, most notably the Canright decomposition from [Can05]. Later, several papers improved under various metrics the design of the AES Sbox, for instance [ZWYD15, WHS15, AEBAF14].

In [CDL16], the authors construct a small implementation of an 8-bit Sbox from a small implementation of a 4-bit Sbox. The main contribution is to deduce cryptographic

properties of the large Sbox from properties of the small Sbox while at the same time ensuring the implementation overhead is minimized.

In [BBI<sup>+</sup>15], the authors introduced a metric called *depth* to estimate the path delay of an Sbox, and designed two new Sboxes  $Sb_0$  and  $Sb_1$  with small delay as part of a new energy-efficient cipher called MIDORI. Based on this metric, the authors of [GJN<sup>+</sup>17] developed an Sbox depth evaluation tool, which computes the logical operation expression with least depth of a given 4-bit Sbox.

Finally in [Sto16], Stoffelen models the problem of finding an efficient implementation (in terms of number of gates) of a lightweight Sbox as a SAT problem. Additional criteria like number of non-linear gates or depth can be injected in the SAT problem, which is then solved more or less efficiently using off-the-shelf SAT solvers. However, we note that this technique does not allow to optimize the implementation depending on the technology that will be used. Thus, it is likely to give implementations that will be rather good in general, but not really optimized for a particular technology, as we will see in our comparisons.

#### 2.2 Preliminaries for Linear Layer

The linear layer of a Substitution-Permutation Network (SPN) can usually be represented by a so-called diffusion matrix, that mixes k words of c bits into k other c-bit words to create the diffusion. The coefficients of a diffusion matrix usually belong to some finite field  $GF(2^c)$  (while some exceptions like [LW16] exist), and the multiplication of the finite field elements are defined by some irreducible polynomial<sup>2</sup> of degree c. When necessary, we append the irreducible polynomial p(X) in hexadecimal form to the finite field:  $GF(2^c)/p(X)$ . We also denote the general linear group of degree c over a field  $\mathbb{K}$  by  $GL(c, \mathbb{K})$ .

A Maximum Distance Separable (MDS) diffusion matrix is one that has the maximum diffusion power and relies on an MDS code. This property offers perfect diffusion as changing m words of the inputs changes at least k-m+1 of the outputs [Vau95]. It is known that a necessary and sufficient condition for a matrix to be MDS is that all its square submatrices should be invertible (non-singular) [MS86], and as a consequence, it is necessary that all the coefficients of an MDS matrix are nonzero. A typical example of an MDS diffusion matrix appears in the MixColumns operation of the AES.

As proposed in [KPPY14], the hardware implementation cost of a diffusion matrix can be quantified by counting the number of XOR gates needed to implement it. Note that for MDS matrices, the k-1 many c-bit XORs per row (so-called connecting XORs) are a constant and incompressible cost. However, the variable costs are the implementation costs of the field multiplications, which is what we are interested in optimizing.

**Example 1.** The application of the MixColumns operation of the AES can be expressed as a multiplication by a diffusion matrix  $\mathbf{M}$  over  $\mathrm{GF}(2^8)/\mathtt{0x11b}$ ,

$$\underbrace{ \begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{bmatrix} }_{\mathbf{M}} \underbrace{ \begin{bmatrix} a \\ b \\ c \\ d \end{bmatrix} }_{\mathbf{C}} = \underbrace{ \begin{bmatrix} 2a \oplus 3b \oplus c \oplus d \\ a \oplus 2b \oplus 3c \oplus d \\ a \oplus b \oplus 2c \oplus 3d \\ 3a \oplus b \oplus c \oplus 2d \end{bmatrix}}_{\mathbf{M}},$$

where  $(a, b, c, d)^{\top}$  is a column of the state and  $\oplus$  denotes a c-bit XOR. In the case of the AES, each  $\oplus$  costs 8 XOR gates.<sup>3</sup> Therefore, the total cost to implement this diffusion matrix is  $4 \times (C(2) + C(3) + 24)$  XOR gates, where  $C(\alpha)$  is the implementation cost of the field multiplication  $\alpha$ .

<sup>&</sup>lt;sup>2</sup>As seen in [SS16a, BKL16], the choice of basis also plays a part in the representation of the elements. In this work, we only consider the polynomial basis as it is the most popular choice of basis.

$<sup>^3\</sup>mathrm{In}$  the sequel, an XOR gate refers to a 2-input XOR gate.

We address two different problems in the paper: finding new MDS matrices with smaller implementation costs, and optimizing these costs for already known matrices. In both cases, we start by improving the implementation cost of the multiplication of the field elements, and we then either construct new lightweight MDS diffusion matrices, or we derive an optimized implementation of a given MDS matrix based on these new implementation costs.

Therefore, the linear layer discussion in this paper is split into two parts. We first present the method to improve the implementation costs of the field elements, then based on this metric, we search for new lightweight diffusion matrices.

Multiplication Matrix of Finite Field Elements. Given a finite field  $GF(2^c)$ , we can represent its elements using c-tuple vectors over GF(2). The multiplication of a nonzero element  $\alpha \in GF(2^c)$  can be viewed as a left multiplication matrix of order c over GF(2) that is often known as multiplication matrix and denoted  $\mathbf{M}_{\alpha}$  [BKL16, SS16a, SKOP15]. One can quickly infer that multiplication matrices of nonzero element are invertible and pairwise-commutative, since nonzero elements in  $GF(2^c)$  are invertible and field multiplication is commutative.

**d-XOR metric.** In [KPPY14], the authors proposed to quantify the implementation cost of a field element multiplication by *directly* counting the number of '1's in each row of the multiplication matrix. We call this metric d-XOR.

**Definition 1** (d-XOR, [KPPY14]). The d-XOR value of a finite field element  $\alpha \in \operatorname{GF}(2^c)/p(X)$  is a metric to estimate the number of XOR operations needed to implement the field multiplication by  $\alpha \colon x \to \alpha x$ . It is counted as the Hamming weight of the multiplication matrix  $\mathbf{M}_{\alpha}$  minus the number of rows, and denoted by d-XOR( $\mathbf{M}_{\alpha}$ ) =  $\omega(\mathbf{M}_{\alpha}) - c$ , where  $\omega(\mathbf{M}_{\alpha})$  is the number of '1's in  $\mathbf{M}_{\alpha}$  and c is the number of rows. When it is clear from the context that  $\mathbf{M}_{\alpha}$  refers to the multiplication matrix for  $\alpha \colon x \to \alpha x$ , one simply writes d-XOR( $\alpha$ ).

Note that this only provides an overestimation of the minimal implementation cost of the finite field elements: in practice the number of XOR operations required could be smaller. In the sequel, we introduce another metric to quantify the implementation cost.

**s-XOR metric.** In practice, given an arbitrary input vector, we can implement any finite field multiplication *in place*, that is by updating the components of the vector without using extra memory storage. This can be realized by performing a *sequence* of XOR instructions (e.g.,  $R_i \leftarrow R_i \oplus R_j$  for some rows  $R_i$  and  $R_j$ ).

**Definition 2** (s-XOR). The s-XOR of a field element  $\alpha$  is the minimum number of XOR operations needed to implement the left multiplication of a multiplication matrix  $\mathbf{M}_{\alpha}$ , where the minimum is taken over all implementation sequences. We denote it by s-XOR( $\mathbf{M}$ ) for an invertible binary matrix  $\mathbf{M}$ , or simply s-XOR( $\alpha$ ) if the matrix is  $\mathbf{M}_{\alpha}$ .

**Example 2.** Given the finite field  $GF(2^3)/Oxb$ , the multiplication of  $\alpha = 7$  seen as  $(1,1,1) \in (GF(2))^3$  can be computed by:

$$(1,1,1)(b_2,b_1,b_0) = (b_2 \oplus b_0, b_2 \oplus b_1, b_1) \oplus (b_1, b_2 \oplus b_0, b_2) \oplus (b_2, b_1, b_0)$$

=  $(b_1 \oplus b_0, b_0, b_2 \oplus b_1 \oplus b_0),$

where  $(b_2, b_1, b_0)$  is an arbitrary element of  $GF(2^3) \cong (GF(2))^3$ . Expressing the same computation as a matrix multiplication, it rewrites as

$$\begin{bmatrix} 0 & 1 & 1 \\ 0 & 0 & 1 \\ 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} b_2 \\ b_1 \\ b_0 \end{bmatrix} = \begin{bmatrix} b_1 \oplus b_0 \\ b_0 \\ b_2 \oplus b_1 \oplus b_0 \end{bmatrix}.$$

From the multiplication matrix, we can see that d- $XOR(\alpha) = 3$  XOR instructions. To find one s-XOR value for  $\alpha$ , we note that  $b_1 \oplus b_0$  appears in both the first and third components. Hence in practice, we can upward-rotate the input vector components, XOR the second component to the first, followed by XORing the first component to the third to obtain the desired output. We can easily verify that such sequence has the minimum number of XORs to implement the multiplication matrix. Therefore, in that case, we get s- $XOR(\alpha) = 2 < d$ - $XOR(\alpha)$ .

Consequently, our goal is to find an optimal sequence (with the least number of XOR instructions) for any given multiplication matrix, or more generally, for any invertible binary matrix.

# 3 A Graph-Based Search

We now describe two generic algorithms that produce implementations of functions given a set of Boolean instructions  $\mathcal{B}$  relying on some bitwise Boolean operation like AND ( $\wedge$ ), OR ( $\vee$ ), XOR ( $\oplus$ ), NOT ( $\neg$ ), etc. We make the distinction between *operation* and *instruction* to capture the need for an internal state to produce an implementation. For instance,  $\mathcal{B}$  could contain the following instructions

$$x \leftarrow x \land y, \qquad x \leftarrow x \lor y, \qquad x \leftarrow x \oplus y, \qquad x \leftarrow \neg x,$$

if we are interested in software implementations, or instructions based on logical 2-input gates like NAND, NOR, XOR, XNOR if we consider hardware implementations:

$$x \leftarrow \neg (x \land y), \qquad x \leftarrow \neg (x \lor y), \qquad x \leftarrow x \oplus y, \qquad x \leftarrow \neg (x \oplus y).$$

**Definitions and Notations.** In the rest of the paper, we call an implementation only using instructions from a set  $\mathcal{B}$  a  $\mathcal{B}$ -implementation. In the case where  $\mathcal{B}$  only contains the XOR instruction, we call them XOR-implementations. Furthermore, since all the functions we consider are  $\mathrm{GF}(2^c) \to \mathrm{GF}(2^c)$ , we make no distinction between the function f and the ordered sequence  $(f(x))_{x \in \mathrm{GF}(2^c)}$  for a predetermined ordering of  $\mathrm{GF}(2^c)$ , and we use the term function to refer to both objects. Additionally, we define  $one^4$   $\mathcal{B}$ -implementation  $\mathcal{I}_{Id}^f$  of a function f as the sequence  $((f_i, o_i))_{i=1,\ldots,n}$ , transforming the identity function into the function f using the instructions  $o_i \in \mathcal{B}$  and intermediate functions  $f_i$ , for  $i=1,\ldots,n$ . We represent it by:

$$Id \stackrel{o_1}{\to} f_1 \cdots \stackrel{o_n}{\to} f_n = f.$$

More generally, we introduce  $\mathcal{I}_f^g$  to represent the sequence transforming a function f into another function g, and denote  $|\mathcal{I}_f^g|$  its length in terms of number of instructions the sequence contains. For simplicity, we write  $\mathcal{I}_{Id}^f$  as  $\mathcal{I}^f$ . The concatenation of two implementations  $\mathcal{I}_f^g$  and  $\mathcal{I}_g^h$  is denoted by  $\mathcal{I}_f^g + \mathcal{I}_g^h$ . Finally, we denote by  $\|o\|$  the cost assigned to the instruction  $o \in \mathcal{B}$  and abuse notations to define the cost of an implementation  $\mathcal{I}_g^f = ((f_i, o_i))_{i=1,\dots,n}$  by  $\|\mathcal{I}_f^g\| = \sum_i \|o_i\|$ .

The first algorithm described below finds optimally small  $\mathcal{B}$ -implementations of functions for user-defined costs of each element in  $\mathcal{B}$ . The problem solved can be expressed as an optimization problem where all the feasible solutions consist in  $\mathcal{B}$ -implementations of the input function, and are weighted by summing the individual cost affected to each instructions from  $\mathcal{B}$ . The algorithm then finds (one of) the best solution(s) using a graph-based approach (Section 3.1).

<sup>&</sup>lt;sup>4</sup>Note that a function can be implemented in more than one way.

The second algorithm comes into play when the first one fails at producing the optimal solution (Section 3.2). Instead, by starting from a heuristically found  $\mathcal{B}$ -implementation of the input function, the algorithm incrementally reduces it to a smaller one under the same metric by locally applying the first algorithm.

# 3.1 Optimal **B**-Implementations Using MITM Technique

We explicit in this section an algorithm allowing to reach optimally small  $\mathcal{B}$ -implementations of a given function. We recall that by optimal, we mean an implementation that minimizes an integer objective function defined as the cumulative sum of each individual cost ||o|| of the instructions o used.

The algorithm relies on a generic meet-in-the-middle strategy that can accommodate different logical instructions with possibly different costs (e.g., area, delay, energy consumption, etc). As a result, the technique applies to any linear and non-linear cryptographic building blocks and targets any technology for specific user-tuned parameters.

The algorithm takes a function  $f: \mathrm{GF}(2^c) \to \mathrm{GF}(2^c)$  as input, and outputs the circuit implementing f using a set of logical instructions  $\mathcal B$  parameterized by some costs. We restrict the functions to those defined over the binary field  $\mathrm{GF}(2^c)$  of order c to rely on a bit-sliced representation of the functions (see representation details in Section 3.3).

At a high level, the algorithm independently starts from the identity function and from the target function f, and expands each of them to sets of functions constructed by applying all the logical instructions from  $\mathcal{B}$ . Going backwards from f may induce a high branching depending of the set  $\mathcal{B}$ : we address this in Section 4. The process stops when the two constructed sets have a non-empty intersection that defines a sequence transforming the identity function into f.

We describe the algorithm as a solution to a graph problem, where the vertex set V represents the functions and there is an edge  $(v_1 \to v_2) \in E$  between two nodes if  $v_2$  can be deduced from  $v_1$  by applying an instruction from  $\mathcal{B}$ . Then, the algorithm looks for the shortest path between the source node S (representing the identity function) and the target node T (representing the function f), where the distance is defined by summing the cost of each traversed edge (instruction).

At every step of the execution, the algorithm maintains an integer counter  $\lambda$  and the subgraph of all functions reachable from the root node at a distance at most  $\lambda$ . The initialization simply sets the counter to 0 and inserts the root node as starting point. Then, the graph of reachable functions is incrementally constructed by computing the closest nodes (functions) to the root not yet included in the graph, to finally add and connect those new nodes. Internally, all the nodes at the same distance from the root are stored in a same (lexicographically sorted) list, and there are as many lists as different distances. This allows to efficiently generate the newly introduced nodes.

We give a simplified pseudo-code description of this algorithm in the following Algorithm 1. The MITM function takes the two functions  $f_0$  and  $f_1$  as inputs and possibly a limit  $\Lambda$  after which the algorithm will abort. The returned value is one implementation  $\mathcal{I}_{f_0}^{f_1}$ . In the current case where we look for one implementation of the f function, we call this algorithm with MITM $(Id, f, \infty)$ , with Id the identity function. Later in Section 3.3, the first function  $f_0$  will not necessarily be Id, and  $\Lambda$  will be useful. For simplicity, we omit the details of GETIMPLEMENTATION $(v_0, I, v_1)$ , which simply retrieves the full sequence of instructions (i.e., the implementation) from the traversed edge between the root node  $v_0$ , the half-way node I belonging to the two subgraphs, and the target node  $v_1$ . Similarly, we skip the specifics of Conv(f) which converts a function  $f: \text{GF}(2^c) \to \text{GF}(2^c)$  into its bit-sliced representation and that of SUCC(v, o), which returns the functions reachable from v using the instructions o (both are detailed in Section 3.3).

The core of the algorithm lies in the EXPAND function, which generates new nodes in the graph. As mentioned before, we structure the nodes of the set V according to their

#### Algorithm 1 – Meet-in-the-Middle Implementation Search (Simplified).

```

1: function MITM(f_0, f_1[, \Lambda = \infty])

v_0 \leftarrow \operatorname{Conv}(f_0), \quad \lambda_0 \leftarrow 0, \quad V_0^0 \leftarrow \{v_0\}, \quad \mathcal{G}_0 \stackrel{\text{def}}{=} (V_0, E_0) \leftarrow (\{V_0^0\}, \emptyset)

v_1 \leftarrow \operatorname{Conv}(f_1), \quad \lambda_1 \leftarrow 0, \quad V_1^0 \leftarrow \{v_1\}, \quad \mathcal{G}_1 \stackrel{\text{def}}{=} (V_1, E_1) \leftarrow (\{V_1^0\}, \emptyset)

\sigma \leftarrow 0

4:

> Possible limitation to abort the algorithm

while \lambda_0 + \lambda_1 < \Lambda do

5:

(\mathcal{G}_{\sigma}, \lambda_{\sigma}) \leftarrow \text{Expand}(\mathcal{G}_{\sigma}, \lambda_{\sigma})

6:

I \leftarrow V_0 \cap V_1

\triangleright Look for meet-in-the-middle collision

7:

if I \neq \emptyset then return GETIMPLEMENTATION(v_0, I, v_1)

8:

\sigma \leftarrow \sigma \oplus 1

9:

10:

return \emptyset

1: function Expand(\mathcal{G} = (\{V^0, \dots, V^{\lambda-1}\}, E), \lambda)

V^{\lambda} \leftarrow \emptyset, \quad E^{\lambda} \leftarrow \emptyset

\triangleright Initialize (V^{\lambda}, E^{\lambda})

for all o \in \mathcal{B} do

\triangleright For all possible instructions

3:

\triangleright Retrieve the cost of instruction o

c \leftarrow \|o\|

4:

for all v \in V^{\lambda-c} do

\triangleright Check whether a node in V^{\lambda} can be created

5:

S \leftarrow \text{Succ}(v, o)

\triangleright All successors of v using instruction o

6:

V^{\lambda} \leftarrow V^{\lambda} \cup S

7:

E^{\lambda} \leftarrow E^{\lambda} \cup \{v \rightarrow w, w \in S\}

\mathcal{G} \leftarrow (\{V^0, \dots, V^{\lambda - 1}, V^{\lambda}\}, E \cup E^{\lambda}) \qquad \qquad \triangleright \text{Insert and connect new nodes (if any)}

9:

if V^{\lambda} = \emptyset then

\triangleright If there are no possible nodes at distance \lambda, try \lambda + 1

10:

return Expand(\mathcal{G}, \lambda + 1)

11:

12:

return (\mathcal{G}, \lambda)

13:

```

distance to the root. Namely, if node v is at distance d from the root, we store it in  $V^d$ , and then  $V = \{V^d, d\}$ . Now, Expand $(\mathcal{G}, \lambda)$  fills  $V^{\lambda}$  from the nodes already present in  $\mathcal{G}$  using the instructions in  $\mathcal{B}$ .

We emphasize that Algorithm 1 gives a simplified version of the actual algorithm implemented in our tools. Indeed, in this simple form, the algorithm may not return the optimal result as the search stops as soon as one collision has been found between the two subgraphs  $\mathcal{G}_0$  and  $\mathcal{G}_1$  (Line 8). We implement instead what can be seen as a bi-directional Dijsktra's shortest path finding algorithm, which continues executing the main while-loop of Line 5 to keep expanding the subgraphs until the current best implementation cannot be further improved.

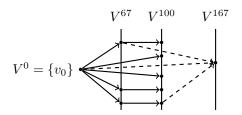

We give a visual example of the graph construction in Figure 1.

**Figure 1:** Example of a graph constructed by EXPAND. The set  $\mathcal{B}$  contains three hypothetical instructions of cost 67, 100 and 167, which implies that nodes at distance 167 from the root  $v_0$  can be reached from nodes in  $V^{100}$ ,  $V^{67}$ , or  $V^0$ .

# 3.2 Efficient $\mathcal{B}$ -Implementations

The meet-in-the-middle algorithm presented in the previous section outputs optimal  $\mathcal{B}$ -implementations of general functions  $f: \mathrm{GF}(2^c) \to \mathrm{GF}(2^c), c > 0$ . However in practice, the computational and memory complexities may restrict its application only to small functions (e.g.,  $c \leq 4$ ), and do not apply to *all* functions for higher c (although in *some* particular cases, the algorithm can terminate, for instance for linear functions). In case the algorithm does not terminate, no solution is returned. The algorithm presented below overcomes this limitation.

The main idea is to start from a heuristically found  $\mathcal{B}$ -implementation of the target function f and iteratively reduce it locally using the previous MITM optimal algorithm for some finite limit value  $\Lambda$ . We assume in this section that a  $\mathcal{B}$ -implementation of a function f is known, and concentrate on minimizing it. We partially address the problem of finding one initial implementation in Section 4.

In the sequel, we assume that the known  $\mathcal{B}$ -implementation  $\mathcal{I}^f$  equals the sequence  $((f_i,o_i))_{i=1,\dots,n}$ . To find another implementation  $\mathcal{I}'^f$  of f such that  $\|\mathcal{I}'^f\| \leq \|\mathcal{I}^f\|$ , we start by fixing a bound  $\Lambda \geq 2$  for the time spent in the underlying meet-in-the-middle algorithm MITM. Then, we recursively consider all the decompositions of  $\mathcal{I}^f$  by splitting it in parts containing between two and  $\Lambda$  instructions. For all the partial implementations  $\mathcal{I}_f^{f_\beta}$  of length at most  $\Lambda$ , we apply the previous algorithm with the  $\Lambda$  parameter: MITM $(f_\alpha, f_\beta, \Lambda)$ . As we know there exists at least one  $\mathcal{B}$ -implementation transforming  $f_\alpha$  into  $f_\beta$  in at most  $\Lambda$  instructions, this call necessarily terminates and may produce an implementation with a smaller cost. Then, for all the decompositions, the algorithm selects the one that minimizes the overall cost. We repeat this process as long as the implementation cost keeps reducing and return it if no further improvement occurred.

We give a simplified pseudo-code description of this algorithm that we call ChainMitm in the following Algorithm 2. The initial call to decrease the implementation cost of  $\mathcal{I}$  is ChainMitm( $\mathcal{I}, \Lambda$ ), which subsequently calls the recursive function Split. In case of success, the returned implementation has a cost strictly smaller than that of  $\mathcal{I}$ , otherwise,  $\mathcal{I}$  is returned.

#### 3.3 Graph Vertex and Edge Representations

We specify in this section details about the representation of the functions serving as nodes in the graph. We differentiate the general case where the vertices are all functions  $GF(2^c) \to GF(2^c)$  from the situation where we restrict the space of functions to linear ones only. While the same algorithms apply for either type, the representation of linear functions can be more compact. In both cases, we also specify how the functions are linked together by the edges representing the logical instructions.

**General Functions.** To encode a function  $f: \mathrm{GF}(2^c) \to \mathrm{GF}(2^c)$ , at least  $c \cdot 2^c$  bits are required as there are  $2^{c \cdot 2^c}$  different functions having this signature. We use the technique called *bit-slicing*, which provides a natural way to optimally encode such functions. The idea is to see the function as a vectorial Boolean function and encodes the truth table of every c Boolean functions independently.

For example, as seen in Table 1 in the case of the PRESENT Sbox S (a permutation over  $GF(2^4)$ ), we can see S as a function  $x \in GF(2^4) \to (y_3, y_2, y_1, y_0) \in (GF(2))^4$  and simply encode the c truth tables  $y_i : GF(2^4) \to GF(2)$  as  $2^c$ -bit words. In this example, we would represent S as the 4-tuple of 16-bit words (0x9b70, 0xe16c, 0x32e5, 0x59a6). Similarly, the identity permutation over  $GF(2^4)$  would be represented by (0x00ff, 0x0f0f, 0x3333, 0x5555).

Having the function encoded in this form allows to perform a single Boolean instruction on all input values from the domain at once. That way, a tuple  $v_f = (v_f^1, v_f^2, \dots, v_f^c)$  representing function  $f: GF(2^c) \to GF(2^c)$  could be transformed to  $(o(v_f^1, v_f^2), v_f^2, \dots, v_f^c)$

#### Algorithm 2 – Improve Heuristic Implementation.

```

1: function ChainMitM(\mathcal{I}, \Lambda)

do

2:

3:

m \leftarrow \|\mathcal{I}\|

\mathcal{I} \leftarrow \text{Split}(\mathcal{I}, \Lambda)

4:

while \|\mathcal{I}\| < m

5:

6:

return \mathcal{I}

▷ Return a possibly optimized implementation

1: function Split(\mathcal{I}_{f_{\alpha}}^{f_{\beta}}, \Lambda)

\mathcal{I} \leftarrow \mathcal{I}_{f_{\alpha}}^{f_{\beta}} \\ \left( \left( f_{i}, o_{i} \right) \right)_{i} \leftarrow \mathcal{I}

\triangleright Try to find a sequence smaller than \mathcal I

3:

l \leftarrow |\mathcal{I}|

\triangleright Length of the sequence

4:

5:

m \leftarrow \|\mathcal{I}\|

\triangleright Current best cost

if l \leq \Lambda then return MITM(f_{\alpha}, f_{\beta}, \Lambda)

\triangleright Base case

6:

for \lambda = 2, \dots, \Lambda do

\triangleright General case

7:

for t = 0, \ldots, l - \lambda \operatorname{do}

8:

\begin{aligned} &\mathcal{I}_0 \leftarrow \text{Split}(\mathcal{I}_{f_{\alpha}}^{f_{\alpha+t}}, \lambda) \\ &\mathcal{I}_0 \leftarrow \text{Split}(\mathcal{I}_{f_{\alpha}}^{f_{\alpha+t}}, \lambda) \\ &\mathcal{I}_1 \leftarrow \text{Split}(\mathcal{I}_{f_{\alpha+t}}^{f_{\alpha+t+\lambda}}, \lambda) \\ &\mathcal{I}_2 \leftarrow \text{Split}(\mathcal{I}_{f_{\alpha+t+\lambda}}^{f_{\beta}}, \lambda) \\ &\text{if } \|\mathcal{I}_0\| + \|\mathcal{I}_1\| + \|\mathcal{I}_2\| < m \text{ then } \end{aligned}

9:

10:

12:

\mathcal{I} \leftarrow \mathcal{I}_0 + \mathcal{I}_1 + \mathcal{I}_2

13:

\triangleright New shorter sequence found

m = ||\mathcal{I}||

14:

return \mathcal{I}

▷ Return a possibly optimized implementation

15:

```

**Table 1:** Bit-sliced representation of the PRESENT Sbox  $S: x \in GF(2^4) \to (y_3, y_2, y_1, y_0) \in (GF(2))^4$  used in our algorithms.

| $\overline{S(x)}$ | 12 | 5 | 6 | 11 | 9 | 0 | 10 | 13 | 3 | 14 | 15 | 8 | 4 | 7 | 1 | 2 | Hex              |

|-------------------|----|---|---|----|---|---|----|----|---|----|----|---|---|---|---|---|------------------|

| $y_3$             | 1  | 0 | 0 | 1  | 1 | 0 | 1  | 1  | 0 | 1  | 1  | 1 | 0 | 0 | 0 | 0 | 0x9b70           |

| $y_2$             | 1  | 1 | 1 | 0  | 0 | 0 | 0  | 1  | 0 | 1  | 1  | 0 | 1 | 1 | 0 | 0 | 0xe16c<br>0x32e5 |

| $y_1$             | 0  | 0 | 1 | 1  | 0 | 0 | 1  | 0  | 1 | 1  | 1  | 0 | 0 | 1 | 0 | 1 | 0x32e5           |

| $y_0$             | 0  | 1 | 0 | 1  | 1 | 0 | 0  | 1  | 1 | 0  | 1  | 0 | 0 | 1 | 1 | 0 | 0x59a6           |

by applying the Boolean instruction  $v_f^1 \leftarrow o(v_f^1, v_f^2)$ . We give in the following Table 2 an example of the application of an XOR instruction.

In the following Section 4 on heuristics, we precise which specific instructions  $\mathcal{B}$  we used in our search of non-linear function implementations.

**Linear Functions.** In the more particular case where the functions  $f: GF(2^c) \to GF(2^c)$  are known to be linear, less than  $c \cdot 2^c$  bits are required to encode f, as one can simply encode f as a binary matrix of order c. Therefore, only  $c^2$  bits are required to encode all linear functions defined over  $GF(2^c)$ .

Then, the graphs used in the algorithms only work with linear functions, and the set of instructions  $\mathcal B$  only contains linear Boolean operations as well. Again, this representation enables to apply a single instruction to all the values of the domain, however in this case, one implementation simply encodes row matrix operations transforming one end of the path to the other. For the multiplication of finite field element, it can simply be represented

| Id(x)            | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | Hex    |

|------------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|--------|

| $y_3$            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 0x00ff |

| $y_2$            | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | 1  | 0x0f0f |

| $y_1$            | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1  | 1  | 0  | 0  | 1  | 1  | 0x3333 |

| $y_0$            | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0  | 1  | 0  | 1  | 0  | 1  | 0x5555 |

| $y_3$            | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 0x00ff |

| $y_2$            | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0  | 0  | 1  | 1  | 1  | 1  | 0x0f0f |

| $y_1$            | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1  | 1  | 0  | 0  | 1  | 1  | 0x3333 |

| $y_0 \oplus y_1$ | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1  | 0  | 0  | 1  | 1  | 0  | 0x6666 |

**Table 2:** Bit-sliced representation of the identify function Id, and example of an application of the instruction  $y_0 \leftarrow y_0 \oplus y_1$ .

by its multiplication matrix as seen in Example 2.

**Successors and Branching.** In the Algorithm 1 previously described, the function SUCC(v, o) is used to generate the set of all functions reachable from v using the Boolean instruction  $o \in \mathcal{B}$ . Although the set of successors highly depends on the elements present in  $\mathcal{B}$ , we can still give an intuition about its cardinality. Indeed, what one usually call branching represents the number of successors per node in the graph (related to the term out-degree in graph theory).

For 2-variable instructions (e.g.,  $x \leftarrow x \oplus y$  or  $y \leftarrow x \oplus y$ ), the set of successors for a function  $f: \mathrm{GF}(2^c) \to \mathrm{GF}(2^c)$  would contain c(c-1) functions. Depending on the instruction considered, the branching can be higher or smaller.

## 4 Heuristics

We explicit in this section several heuristics we use throughout our work. One can split them into two categories: first, the heuristic algorithms we use to generate  $\mathcal{B}$ -implementations of a given function (either linear or non-linear). This first type of heuristic is only used when the MITM algorithm (Algorithm 1) targeting optimal  $\mathcal{B}$ -implementations fails.

Then, we describe the restriction on the possible instructions due to the meet-in-the-middle nature of our graph algorithms. Indeed, since the implementations are evaluated in both direct and indirect directions, we heuristically impose the instructions in  $\mathcal{B}$  to be invertible. While this constraint naturally means that the  $\mathcal{B}$ -implementations found by our algorithms necessarily have a cost higher or equal than the overall optimal implementation under the same metric (for any possible instruction set  $\mathcal{S}$ ,  $\mathcal{B} \subseteq \mathcal{S}$ ), we nevertheless observe that in practice, this heuristic already provides very good results.

#### 4.1 Heuristics for Linear Layers

Heuristic Implementations for Linear Layers. To apply the CHAINMITM algorithm (Algorithm 2), we need an initial implementation as input for the optimization process. If a starting implementation is unknown, we need a deterministic method to find it. When the function f to implement is linear, we can encode it in the form of a binary matrix  $\mathbf{M}_f$  as seen before, and then finding an implementation of f reduces to finding a sequence of instructions transforming  $\mathbf{M}_f$  to the identity matrix. In the sequel, we assume  $\mathbf{M}_f$  to be invertible.

The problem of finding an initial implementation for a binary matrix can easily be solved using the Gauss-Jordan elimination (GJE) method, a long-standing algorithm in

linear algebra used to solve systems of linear equation. Indeed, as the matrix is invertible, it can be regarded as a homogeneous system of linear equations with an unique solution. One refers to [Kno08] for a description of the GJE.

In the GJE algorithm, there is no fixed rule on the choice of the row and pivot to perform the reduction. This freedom implies there are possibly several implementations for the same function and allows to choose one that minimizes the number of instructions. Hence, we exhaust all possible choices of row order and pivot point to search for the least number of XOR instructions needed to reduce a binary matrix to a row permutation of the identity matrix.

**Example 3.** Suppose we consider the linear function  $f: GF(2^4) \to GF(2^4)$  encoded by the following binary matrix:

$$\underbrace{\begin{bmatrix} 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & 0 & 1 & 0 \end{bmatrix}}_{\mathbf{M}_{\mathfrak{E}}} \begin{bmatrix} b_3 \\ b_2 \\ b_1 \\ b_0 \end{bmatrix} = \begin{bmatrix} b_3 \oplus b_2 \oplus b_0 \\ b_3 \oplus b_2 \oplus b_1 \\ b_3 \oplus b_2 \oplus b_1 \oplus b_0 \\ b_3 \oplus b_1 \end{bmatrix}.$$

where  $(b_3, b_2, b_1, b_0)$  is an arbitrary element of  $(GF(2))^4$ .

However, by applying the GJE on the matrix, we find a sequence of 4 XOR operations that simplifies the multiplication matrix to a row permutation of the identity matrix. The instructions are  $R_0 \leftarrow R_0 \oplus R_2$ ,  $R_2 \leftarrow R_2 \oplus R_1$ ,  $R_1 \leftarrow R_1 \oplus R_3$  and  $R_3 \leftarrow R_3 \oplus R_0$ , which gives the permutation  $\pi = (3, 1, 0, 2)$  of the rows of the identity matrix.

Consequently, to implement the given binary matrix  $\mathbf{M}_f$ , we first start by applying  $\pi$ , followed by the reverse sequence of XOR instructions, and finally obtain the output vector, that is:

$$\begin{bmatrix}

b_3 \\

b_2 \\

b_1 \\

b_0

\end{bmatrix} \xrightarrow{\pi} \begin{bmatrix}

b_1 \\

b_2 \\

b_0 \\

b_3

\end{bmatrix} \xrightarrow{R_3 \leftarrow R_3 \oplus R_0} \begin{bmatrix}

b_1 \\

b_2 \\

b_0 \\

b_3 \oplus b_1

\end{bmatrix} \xrightarrow{R_1 \leftarrow R_1 \oplus R_3} \begin{bmatrix}

b_1 \\

b_3 \oplus b_2 \oplus b_1 \\

b_3 \oplus b_1

\end{bmatrix}$$

$$\xrightarrow{R_2 \leftarrow R_2 \oplus R_1} \begin{bmatrix}

b_1 \\

b_3 \oplus b_2 \oplus b_1 \\

b_3 \oplus b_2 \oplus b_1 \oplus b_0 \\

b_3 \oplus b_1

\end{bmatrix} \xrightarrow{R_0 \leftarrow R_0 \oplus R_2} \begin{bmatrix}

b_3 \oplus b_2 \oplus b_0 \\

b_3 \oplus b_2 \oplus b_1 \\

b_3 \oplus b_2 \oplus b_1 \oplus b_0 \\

b_3 \oplus b_1

\end{bmatrix},$$

This implementations yields 4 XORs which is smaller than d-XOR( $\mathbf{M}_f$ ) = 8.

Tweaking Gauss-Jordan Elimination Method. In GJE method, one may notice that when a pivot is chosen from some row, that row is continuously used to update the other rows. After which, that row will never be used again to update other rows. Therefore, there are instances where GJE method would not be optimal (with respect to the number of instructions).

In [Ber], Bernstein presented an algorithm (we call it DJB method) that also achieves optimized implementations of linear functions. However, similarly to the GJE, due to the nature of the algorithm there are instances where the output sequence is not optimal. To find the shortest sequence, we could apply both algorithms and pick the best one. However, we observe a simple way to simulate the behavior of DJB from the GJE strategy. Namely, one needs to apply the GJE method on the transpose of the given matrix. In contrast to the sequence obtained from GJE, a chosen row will be continuously updated by other rows.

Let  $\mathbf{E}_{i,j}$  be the identity matrix of order n with an additional '1' on the i-th row and j-th column, where  $i, j \in \{1, 2, ..., n\}$ . Each XOR instruction can be represented by a

left-multiplication of some  $\mathbf{E}_{i,j}$  to an *n*-tuple column vector  $(x_1, x_2, ..., x_n)^{\top}$ , it is basically updating the vector component  $x_i \leftarrow x_i \oplus x_j$  to the column vector. On the other hand, if a row vector is right-multiplied by the same matrix, the update becomes  $x_j \leftarrow x_j \oplus x_i$ .

Since a given invertible binary matrix M can be decomposed into a sequence of XOR operations and a bit permutation, we can express it as

$$\mathbf{M} = \mathbf{E}_{i_1,j_1} \mathbf{E}_{i_2,j_2} \cdots \mathbf{E}_{i_s,j_s} \mathbf{P},$$

where  $\mathbf{P}$  is a permutation matrix. Let  $\mathbf{u}$  be a column vector, the left multiplication yields:

$$\mathbf{M}\mathbf{u} = \mathbf{E}_{i_1,j_1} \left( \mathbf{E}_{i_2,j_2} \cdots \left( \mathbf{E}_{i_s,j_s} (\mathbf{P}\mathbf{u}) \right) \cdots \right).$$

On the other hand, starting from the transpose matrix  $\mathbf{M}^{\top}$ , we can also rewrite it using the GJE as:

$$\mathbf{M}^{\top} = \mathbf{E}_{i'_1,j'_1} \mathbf{E}_{i'_2,j'_2} \cdots \mathbf{E}_{i'_t,j'_t} \mathbf{P}',$$

for another matrix permutation  $\mathbf{P}'$ . By rewriting the multiplications, this gives

$$\begin{aligned} \mathbf{M}\mathbf{u} &= \left(\mathbf{u}^{\top}\mathbf{M}^{\top}\right)^{\top} = \left(\left(\cdots\left(\left(\mathbf{u}^{\top}\mathbf{E}_{i'_{1},j'_{1}}\right)\mathbf{E}_{i'_{2},j'_{2}}\right)\cdots\mathbf{E}_{i'_{t},j'_{t}}\right)\mathbf{P'}\right)^{\top} \\ &= \mathbf{P'}^{\top}(\mathbf{E}_{j'_{1},i'_{1}}\cdots(\mathbf{E}_{j'_{2},i'_{2}}(\mathbf{E}_{j'_{1},i'_{1}}\mathbf{u}))\cdots\right), \end{aligned}$$

where  $\mathbf{P'}^{\top}$  also describes a permutation matrix. Hence, the decomposition of the transpose matrix  $\mathbf{M}^{\top}$  can also be used to derive an implementation of the matrix  $\mathbf{M}$ .

As a result, to determine an initial implementation of a given invertible binary matrix  $\mathbf{M}_f$  (encoding a linear function f), we simply apply the GJE algorithm to both  $\mathbf{M}_f$  and  $\mathbf{M}_f^{\top}$  and choose whichever sequence of XOR instructions is shorter.

#### 4.2 Heuristics for Non-Linear Layers

**Instruction Restriction in**  $\mathcal{B}$ . Unlike the linear instructions used to implement linear functions, non-linear Boolean operations like NAND are not invertible. Consequently, it is non-trivial to use instructions relying on those operations as an edge in our MITM technique as we want to grow the graph in the backward direction too. Using non-linear instructions induces a very high branching in the graph associated to the backward expansion, and quickly reaches the practical memory complexity limit. Therefore, we require special invertible instructions in  $\mathcal{B}$  for the edges of the graph: these instructions are built from combinations of linear and non-linear operations.

The general rules for creating the invertible instructions are as follows.

- 1. Only linear instructions are used to update the bits.

- 2. Non-linear instructions are only used to create temporary values from the bits.

- Temporary values are used to update bits that are not used to create these temporary values.

The only invertible instructions involving a single variable is  $x \leftarrow \neg x$  (NOT). For 2-variable instructions, the instructions are necessarily linear to be invertible, for instance  $x \leftarrow x \oplus y$  (XOR) and  $x \leftarrow \neg (x \oplus y)$  (XNOR). For instructions of three or more variables, we can compute any non-linear Boolean operation on all but one variable, store the output bit in a temporary variable, and use it to linearly mask the last variable.

To give a concrete example, one set  $\mathcal{B}$  of instructions that could be used in the graph-based algorithms described is:

$$x \leftarrow \neg x$$

,  $x \leftarrow x \oplus y$ ,  $z \leftarrow \neg (x \land y) \oplus z$ ,  $z \leftarrow \neg (x \lor y) \oplus z$ .

The main benefit of using such instructions is the reduced branching of the graph expansion in the backward direction. In addition, the inverse function can be easily implemented by simply reversing the instruction sequence. Examples of such construction appear in the PICCOLO Sbox [SIH<sup>+</sup>11], and in the SKINNY family [BJK<sup>+</sup>16].

Finding an Implementation for the Non-linear Layer. Similar to the linear layer, when the MITM algorithm cannot output an optimal  $\mathcal{B}$ -implementation, it is possible to start with an initial  $\mathcal{B}$ -implementation and apply the second ChainMITM algorithm. We devised a deterministic algorithm to reduce a given Sbox to an identity mapping using instructions conforming to the previous rules, however, for all the 4-bit Sboxes that we have tested, optimal  $\mathcal{B}$ -implementations could be found using MITM technique. This heuristic algorithm is not implemented in our current tool but investigating this direction might serve as basis for future works.

# 5 Results on Linear Layers

We present in this section the results of our search on linear layer consisting of MDS matrices. First, we detail the application of the graph-based search for (possibly optimal) implementations of the individual field multiplications  $x \to \alpha x$ , for all non-trivial element  $\alpha$  in the field (Section 5.1). Next, we discuss about some of the recent work on MDS diffusion matrix search (Section 5.2), and describe our search parameters and some strategies for searching new lightweight MDS diffusion matrices (Section 5.3). Finally, in the rest of the section, we give the concrete implementations we obtained for several new and known MDS matrices (Section 5.4).

# 5.1 Implementations of Individual Field Multiplications

We ran the MITM algorithm to search for the optimal implementation for field elements over  $GF(2^4)$  and  $GF(2^8)$  defined by all possible irreducible polynomials of degree 4 and 8. For  $GF(2^4)$ , the results show that all elements can be implemented with no more than 5 XOR operations. For  $GF(2^8)$ , our MITM technique could reach up to  $\Lambda=12$  XOR instructions in reasonable time and memory complexities. To give concrete numbers, this search took a few hours and about 32-64 GB of RAM on a 16-core machine. For elements that have no solution within 12 XOR instructions, we applied the GJE method on both their multiplication matrix and its transpose to find an initial sequence and used Chainmitm algorithm with parameter  $\Lambda=12$  to further improve the implementation and obtain a (sub)optimal sequence.

Although the implementation of some field elements are not optimal, we can already observe the following proposition.

**Proposition 1.** For any nonzero multiplication matrix  $\mathbf{M}_{\alpha}$  of the field element  $\alpha \in \mathrm{GF}(2^c)$ , where c=4 or c=8, there exists an XOR-implementation of  $\mathbf{M}_{\alpha}$  such that  $s\text{-}XOR(\alpha) \leq d\text{-}XOR(\alpha)$ .

We checked for all the irreducible polynomials for  $GF(2^4)$  and  $GF(2^8)$  that the proposition holds, and the previous Example 2 shows a case where the inequality is strict. Besides, we conjecture that this property also holds for any invertible binary matrix of arbitrary order; that is:

**Conjecture 1.** Let c be a positive integer and  $\mathbf{M} \in \mathrm{GL}(c,\mathrm{GF}(2))$ . Prove that there exists an XOR-implementation of  $\mathbf{M}$  such that:  $s\text{-}XOR(\mathbf{M}) \leq d\text{-}XOR(\mathbf{M})$ .

In summary, the s-XOR count of the field elements is smaller or equal than its d-XOR count. This shows that in practice, most of the field elements can actually be implemented

with less XOR gates than previously known. The implementations of the field elements (except trivial elements 0 and 1) from  $GF(2^4)/0x13$  are presented in Appendix A.1.

After obtaining the lists of s-XOR counts of elements in  $GF(2^4)$  and  $GF(2^8)$  over all possible irreducible polynomials, we search for new lightweight MDS diffusion matrices based on this new metric. In this paper, we use the terms *d-lightest* and *s-lightest* to describe matrices that have the least XOR count under the d-XOR and the s-XOR metrics, respectively.

In recent years, there are several papers presenting different ways to search for new lightweight MDS diffusion matrices. In the following section, we discuss the strengths and limitations of their methodologies. Next, we present our strategy to search for lightweight MDS diffusion matrices.

# 5.2 Previous MDS Diffusion Matrix Searches

To the best of our knowledge, the authors of [KPPY14] were the first to propose the d-XOR metric. In addition, they proposed the sub-field construction to design a lightweight MDS matrix over some finite field  $\mathbb{K}$  using a matrix of the same order but over some smaller sub-field  $\mathbb{L}$  of  $\mathbb{K}$ . The idea of the sub-field technique is rather simple: to construct an MDS matrix over finite field  $GF(2^{mc})$ , we use m copies of an MDS matrix<sup>5</sup> over  $GF(2^c)$ . Hence, the implementation cost of the matrix over  $GF(2^{mc})$  is m times the cost of the matrix over  $GF(2^c)$ .

In [SKOP15, LS16], the authors proposed compact equivalence classes (CEC) of Hadamard and circulant matrices to reduce the exhaustive search space on these two types of matrices and presented the d-lightest MDS Hadamard and circulant matrices over  $GF(2^4)$  and  $GF(2^8)$ . Using these equivalence classes, they could complete the search for MDS Hadamard and circulant matrices of order 8, which was previously intractable.

In [LW16], the authors extended the coefficients of a diffusion matrix from finite field  $GF(2^c)$  to invertible binary matrices GL(c, GF(2)), where  $c \in \{4, 8\}$ , and found new lightweight MDS non-involution and involution  $4 \times 4$  Hadamard and circulant matrices over GL(c, GF(2)). However, it is non-trivial to extend their search on matrices of order 8, essentially because the cardinality of GL(c, GF(2)) is much larger than that of  $GF(2^c)$ :  $2^{c\cdot(c-1)/2}\prod_{i=1}^c(2^i-1)\gg 2^c$ .

Using our s-XOR metric, the authors [BKL16] constructed lightweight MDS  $4 \times 4$  and  $8 \times 8$  left-circulant matrices using a single field element  $\alpha$ . Focusing on a single field element allows them to explore all possible bases for representing finite field elements and search for one with the minimum s-XOR count, while in the conventional way, as we did in this paper, the polynomial basis is used to represent the finite field. The limitation of their methodology consists in the structure of the matrices, that must have elements of the form  $\alpha^{\pm n}$  for a field element a, and for small n, say  $n \leq \frac{k}{2}$ . Consequently, they consider only a subclass of all the circulant matrices.

Recently, another paper [ZWZZ16] adopted our s-XOR metric to improve on the implementation of the AES diffusion matrix. They considered the AES diffusion matrix as a  $32 \times 32$  binary matrix and applied a heuristic algorithm to find a sequence of XOR instructions. However, their approach is different from ours as we focus on optimizing the implementation of individual elements, which also allow us to construct new lightweight diffusion matrices.

In [SS16b], the authors searched for lightweight MDS Toeplitz matrices over  $GF(2^4)$  and  $GF(2^8)$  based on the d-XOR metric. The advantage of Toeplitz structure over Hadamard and circulant is the larger degree of freedom for the choice of the coefficients. In addition, their empirical evidence showed that their MDS  $4 \times 4$  Toeplitz matrices over  $GF(2^4)$  and

<sup>&</sup>lt;sup>5</sup>One may also use different MDS matrices, the implementation cost is simply the sum of the cost of the matrices.

$GF(2^8)$  are the d-lightest possible MDS non-involution matrices over  $GF(2^4)$  and  $GF(2^8)$ . However, there are two limitations to the use of Toeplitz matrices. First, as proven by the authors, MDS involution Toeplitz matrices of order  $2^m$  does not exist, which is a widespread practical choice for the order of diffusion matrices. Second, the search for an MDS Toeplitz matrix of order 8 seems intractable due to the large search space.

# 5.3 Our Search for Lightweight MDS Diffusion Matrices

Our search parameters for the lightweight MDS matrices have three dimensions: non-involution or involution matrices, matrices of order 4 or 8, and matrix coefficients over  $GF(2^4)$  or  $GF(2^8)$ . These criteria have been chosen because they capture classical parameters for the diffusion matrices used in practice.

When we search for lightweight MDS matrices, we start with some threshold value,  $\tau$ , for the cost of the matrix, say the XOR count of some existing lightweight MDS matrix, and search for MDS matrices that have lower cost than this threshold value. A simple search pruning strategy is to arrange the field elements in the increasing order of its s-XOR. When we pick an element for some coefficient, we check if the sum of the s-XOR of elements in the matrix exceeds the threshold value, if it does, we do not need to consider the remaining elements for that coefficient. In addition, recall that all coefficients of an MDS matrix are nonzero, thus we do not consider element zero as a coefficient of the matrix.

$4 \times 4$  MDS (Involution) Diffusion Matrices Over  $GF(2^4)$ . To search for the s-lightest MDS non-involution and involution  $4 \times 4$  matrices over  $GF(2^4)$ , we do not put restriction on the shape of the matrix (e.g., Hadamard, circulant, etc.). Instead, we apply an improved exhaustive search over the entire matrix space. Although the entire space of  $4 \times 4$  matrices over  $GF(2^4)$  counts as many as  $2^{64}$  elements, there are a couple of early-abort strategies that we can use to discard invalid candidates prematurely, including the pruning of field elements based on their s-XOR mentioned before.

The exhaustive search algorithm, EXHAUSTIVESEARCH, uses nested for-loops to enumerate the coefficients of the matrix in the following order:

$$\begin{bmatrix} 1 & 2 & 3 & 4 \\ 5 & 8 & 9 & 10 \\ 6 & 11 & 12 & 13 \\ 7 & 14 & 15 & 16 \end{bmatrix},$$

where coefficients with low indices are enumerated first.

When we select an element for the 8th coefficient, we can compute the determinant of the  $2 \times 2$  submatrix (with 1st, 2nd, 5th and 8th coefficients). If it is zero, we already know that any choice for the remaining coefficients will not form an MDS matrix. Hence, we can directly discard this element and pick another. Otherwise, if this submatrix is non-singular, then we continue to pick an element for the next coefficient. Similarly, we check the determinant of all the square submatrices (of any sizes) involving that coefficient. This greatly reduces the search space as we prematurely discard many combinations of coefficients. When all the square submatrices are non-singular (including the entire  $4 \times 4$  matrix), we have found an MDS matrix with lower cost than a threshold value. We store that matrix, update this threshold value and continue the search. At the end of the algorithm, we obtain the s-lightest MDS  $4 \times 4$  matrix over  $GF(2^4)$ .

For involution matrices, we have an additional condition that the dot product of the i-th row and j-th column of the matrix has to be one if i = j, and zero otherwise. Hence, when we pick an element for the 7-th coefficient, we can check whether it is a possible candidate for involution matrix. If the dot product of the 1st row and 1st column differs

#### Algorithm 3 – Lightest MDS Diffusion Matrix Search.

```

1: function MDSMATRIXSEARCH(\mathcal{C}, \mathbb{K}, k, \tau, inv)

if (\dim(\mathbb{K}) \le 4 and k \le 4) then

M_{lightest} \leftarrow \text{EXHAUSTIVESEARCH}(\mathcal{C}, \mathbb{K}, k, \tau, inv)

3:

4:

M_{lightest} \leftarrow \text{CirHadSearch}(\mathcal{C}, \mathbb{K}, k, \tau, inv)

5:

return M_{lightest}

6:

1: function CIRHADSEARCH(\mathcal{C}, \mathbb{K}, k, \tau, inv)

2:

M_{lightest} \leftarrow \emptyset

for all S = \{x_0, \ldots, x_{k-1}\} \subset \mathbb{K} do

\triangleright For all possible multisubsets of \mathbb{K}

3:

4:

if ||S|| < \tau then

\triangleright Cost of the elements are obtained from C

Clist \leftarrow GenCir(S, inv)

▷ Generate CEC rep. of circulant matrices

5:

for all M \in Clist do

6:

if CHECKMDS(M) then

7:

8:

\tau \leftarrow ||S||

9:

M_{lightest} \leftarrow M

ightharpoonup Generate CEC rep. of Hadamard matrices

Hlist \leftarrow \text{GenHad}(S, inv)

10:

for all M \in Hlist do

11:

12:

if CHECKMDS(M) then

\tau \leftarrow ||S||

13:

M_{lightest} \leftarrow M

14:

15:

return M_{lightest}

```

from one, we can discard this element and pick another. The subsequent checks occur for the 10th, 13th, 14th, 15th and 16th coefficients. If all dot products of rows and columns satisfy the condition, the algorithm outputs the s-lightest MDS  $4 \times 4$  involution matrix over  $GF(2^4)$ .

We have implemented this algorithm, and the search for both non-involution and involution arbitrary matrices took less than a minute on a personal computer.

Other Parameters of Diffusion Matrices. Scaling the algorithm for general  $8 \times 8$  matrices over  $GF(2^4)$  seems intractable as the input space contains  $2^{256}$  elements. However, it has been experimentally verified by the authors from [LS16] that there is no MDS  $8 \times 8$  circulant matrix over  $GF(2^4)$ . Therefore, we detail in the following the result of our search on Hadamard matrices for both MDS non-involution and involution matrices over  $GF(2^4)$ .

For matrices over  $GF(2^8)$ , in addition to searching for lightweight MDS Hadamard and circulant matrices, we use the sub-field technique to construct MDS matrices from the s-lightest matrices over  $GF(2^4)$ .

Using the concept of CEC of Hadamard and circulant matrices, the search space for lightweight MDS Hadamard and circulant matrices reduces significantly. This allows to perform an exhaustive search for these. The details of the CEC of Hadamard and circulant matrices can be found in [SKOP15] and [LS16], respectively.

We give a simplified pseudo-code description of the algorithm (Algorithm 3) used for searching lightweight MDS matrices. The MDSMATRIXSEARCH function takes a list  $\mathcal{C}$  containing the implementation cost of the field elements, a finite field  $\mathbb{K} = \mathrm{GF}(2^c)/p(X)$ , matrix order k, threshold value  $\tau$ , and Boolean value for involution matrix inv. For our work, we focus on field dimensions 4 or 8, and matrix orders 4 or 8. If both the field dimension and matrix order are 4, we can apply the function EXHAUSTIVESEARCH as

described above. Otherwise, we apply function Cirhadsearch. First, a (multi)subset S of k field elements, whose summation of the implementation costs is less than  $\tau$ , is selected. Next, S is used to generate the potential MDS matrix candidates using the functions GenCir and GenHad. When the necessary condition for the candidate S to be MDS is not satisfied, the function returns an empty set. For instance, it is known that involution MDS circulant matrices do not exist [GR15], therefore whenever inv holds true, GenCir returns an empty set. We omitted the details of the functions GenCir, GenHad and CheckMDS as the conditions for MDS and construction of the CEC representatives of circulant and Hadamard matrices are discussed extensively in [SKOP15, LS16]. When a candidate matrix is found to be MDS, we store it, update the threshold value and continue the search. At the end of the algorithm, we obtain the s-lightest possible MDS matrix of the given parameter. A simple early-abort strategy is to select subsets with the least possible implementation cost, and gradually increase the cost when no MDS matrix is found. The algorithm can be terminated prematurely once an MDS matrix is found.

#### 5.4 Results on Linear Layers

In a nutshell, among the  $2^3 = 8$  categories of MDS diffusion matrix (that consist of non-involution/involution matrices, matrices of order 4/8, and matrices over  $GF(2^4)/GF(2^8)$ ), we found new lightweight MDS matrices which outperform existing lightweight diffusion matrices in four categories, and we improved the implementation of some existing lightweight matrices and obtained smaller s-XOR counts in three categories. The case of non-involution  $4 \times 4$  matrices over  $GF(2^8)$  is the only one we do not improve: the best result is from [LW16].

Recall that we are interested in minimizing the implementation costs of the field multiplication matrices. We therefore only state the sum of the implementation costs of the coefficients plus the connecting XORs in one row, and if the rows have different implementation costs, we take the average cost for one row. For instance, if a  $4 \times 4$  MDS matrix over  $GF(2^4)$  costs 2.5 + 12, it means that the average cost of the coefficients in one row is 2.5, there are 12 connecting XORs in each row and the total cost is 58. We also include the cost of its inverse matrix for reference. However, we emphasize that for non-involution matrices, our searches focus on optimizing the direct cost.

In the following, we detail the results of our search in four paragraphs, first for matrices over  $GF(2^4)$  and then over  $GF(2^8)$ .

**Lightweight MDS**  $4 \times 4$  **Matrices Over GF**( $2^4$ ). In our exhaustive search for the slightest MDS  $4 \times 4$  arbitrary matrices over GF( $2^4$ ) (described in Section 5.3), we found that the s-lightest matrix  $\mathbf{M}_{4,n,4}$ ,

$$\mathbf{M}_{4,n,4} = \begin{bmatrix} 0 \texttt{x1} & 0 \texttt{x1} & 0 \texttt{x1} & 0 \texttt{x2} \\ 0 \texttt{x1} & 0 \texttt{x2} & 0 \texttt{xd} & 0 \texttt{x1} \\ 0 \texttt{x2} & 0 \texttt{xd} & 0 \texttt{x1} & 0 \texttt{x1} \\ 0 \texttt{xd} & 0 \texttt{x1} & 0 \texttt{x2} & 0 \texttt{x1} \end{bmatrix},$$

outperforms the circulant matrix presented in [BKL16]. As mentioned before, we found this new matrix by an improved exhaustive search over the full space  $GL(4, GF(2^4))$ , while the search from [BKL16] relies on particular matrices in this space. Similarly for MDS involution  $4 \times 4$  matrices over  $GF(2^4)$ , we found the s-lightest involution arbitrary matrix  $\mathbf{M}_{4,i,4}$ ,

$$\mathbf{M}_{4,i,4} = egin{bmatrix} 0 x2 & 0x1 & 0x1 & 0x9 \ 0x1 & 0x4 & 0xf & 0x1 \ 0xd & 0x9 & 0x4 & 0x1 \ 0x1 & 0xd & 0x1 & 0x2 \end{bmatrix}.$$

It is known that MDS involution circulant matrices do not exist over any finite field  $GF(2^n)$ . Therefore, Hadamard matrices are commonly used to construct MDS involution matrices. An example of such a matrix can be found in the linear layer of Joltik, and under our s-XOR metric, the results of our algorithms optimize the implementation of the coefficients in this matrix.

The results are summarized in Table 3. As mentioned in Section 5, the authors of [BKL16] considered the representation of the field element under all possible bases. In their paper, only the multiplication matrix of the field element is provided but not the irreducible polynomial. Therefore in the table, we only state the size of the finite field but not the irreducible polynomial.

|                | Matrix        |      |                  | Ref.        |                                   |              |     |                      |

|----------------|---------------|------|------------------|-------------|-----------------------------------|--------------|-----|----------------------|

| Field/Ring     | Type          | Inv. | $d	ext{-}XOR(M)$ | s-XOR $(M)$ | $s	ext{-}	ext{XOR}(	ext{M}^{-1})$ | Opt          | Min | nei.                 |

| $GF(2^4)/0x13$ | Arbitrary     | No   | 2.5 + 12         | 2.5 + 12    | 9.25 + 12                         | ✓            | s   | $\mathbf{M}_{4,n,4}$ |

| $GF(2^4)/0x19$ | Toeplitz      | No   | 2.5 + 12         | 2.5 + 12    | 11.5 + 12                         | $\checkmark$ | d   | [SS16b]              |

| GL(4, GF(2))   | Circulant     | No   | 3 + 12           | 3 + 12      | _                                 | $\checkmark$ | _   | [LW16]               |

| $GF(2^4)$      | Circulant     | No   | 4 + 12           | 3 + 12      | _                                 | _            | _   | [BKL16]              |

| $GF(2^4)/0x13$ | Arbitrary     | Yes  | 5 + 12           | 3.7         | 5 + 12                            | ✓            | s   | $\mathbf{M}_{4,i,4}$ |

| $GF(2^4)/0x13$ | Hadamard-like | Yes  | 4 + 12           | 4           | + 12                              | $\checkmark$ | _   | [SS16b]              |

| GL(4, GF(2))   | Circulant     | Yes  | 5 + 12           | 5           | + 12                              | $\checkmark$ | _   | [LW16]               |

| CF(24)/0v13    | Hadamard      | Voc  | $6 \pm 12$       | 5           | ⊥ 19                              | ./           | _   | Iol+ik               |

**Table 3:** Comparison of  $4 \times 4$  MDS matrices over  $GF(2^4)$  and GL(4, GF(2)).

Opt: Implementations of coefficients have been optimized under the s-XOR metric.

Min: Lightest possible matrix under field/order/involution based on d/s-metric.

When the rows have different cost, we take the average cost of a row.

To have an idea of how an entire diffusion matrix can be implemented, we provide an example of one possible implementation of the diffusion matrix  $\mathbf{M}_{4,n,4}$  in Appendix A.2. We emphasize that this implementation only gives an illustration of the implementation of the entire diffusion matrix: further improvements are possible, for instance in ASIC if 3-or 4-input XOR cells are available in the library used, or in software with less intermediate registers.

MDS  $8 \times 8$  Matrices Over  $GF(2^4)$ . We observed that the Hadamard matrices presented in [SKOP15] are among the s-lightest MDS Hadamard matrices that we have found. This means that if we optimize the implementation of the field multiplications of the coefficients used in these matrices, we obtain the s-lightest MDS non-involution/involution Hadamard  $8 \times 8$  matrices over  $GF(2^4)$ . To be consistent, we name the non-involution Hadamard  $8 \times 8$  matrices over  $GF(2^4)$  as  $M_{8,n,4}$ ,

| - N                              |          |      |                                    | Ref.        |                                         |              |     |                                |

|----------------------------------|----------|------|------------------------------------|-------------|-----------------------------------------|--------------|-----|--------------------------------|