# Carbon – Science and Technology

ISSN 0974 - 0546

http://www.applied-science-innovations.com

### **RESEARCH ARTICLE**

Received: 18/02/2018, Accepted: 07/04/2018

# A Comparative analysis of steep retrograde and uniform doping for high-k dielectrics based multi-gate devices

## Rajiv Ranjan Thakur <sup>a)</sup> \*, Pragati Singh <sup>a)</sup>

Department of Electronics & Communication Engineering, National Institute of Technology (NIT) Mizoram, Aizawl 796001, India.

**Abstract:** A brief comparison has been done for the uniform doped and steep retrograde doped Multi-Gate Devices with High-k Dielectric Oxide Layer in comparison with the traditional Silicon Dioxide Oxide Layer. Analytical modeling has been done for the steep retrograde doping and it has been found that the effects of Threshold Voltage ( $V_{th}$ ) Roll-Off have been suppressed up-to certain extent using Steep Retrograde Doping. The study also predicts that Hafnium Dioxide can be very good alternatives to the traditional gate oxide as it greatly suppresses high leakages and other problems. The device was carried out using Sentaurus 3D-TCAD Tools.

Keywords: High-k dielectrics, retrograde doping, uniform doping, threshold voltage, oxide capacitance

-----

1. Introduction: The semiconductor industry has been driven by the continuous scaling of Complementary Metal-Oxide-Silicon (CMOS) technology over the past three decades [1, 2]. MOS transistor success source lies in the fact that a transistor can be scaled to an increasingly smaller dimension, which enables the microelectronics industry to meet many technological requirements: high circuit density, fast switching speed and low standby power [3, 4]. The traditional Si-based CMOS scaling includes gate length, T<sub>ox</sub> S/D extension, and depths of the S/D Junctions [5, 6]. Among them, the key element is the gate dielectric that has been employed for decades to separate the gate from the silicon channel: silicon dioxide (SiO<sub>2</sub>). Tox and Lg should be scaled in proportion in order to have an effective electrostatics control over the active region of the device [7, 8]. Since the gate leakage current exponentially increases with the decreasing of the physical  $T_{ox}$ , the traditional SiO<sub>2</sub> gate dielectric has reached the fundamental leakage limit, due to tunneling [9, 10]. New material must be explored to replace the Si0<sub>2</sub> which can help us to suppress the tunneling through the gate oxide and thus improve the performance of the device [11, 12]. In this work, a comparative study was carried out between the commonly used Dielectric materials to study their properties using Steep Retrograde and Uniform Doping. The study shows that using steep retrograde doping we can control the effects of threshold voltage roll off. Also, the various simulations model of TCAD has been used to study the device.

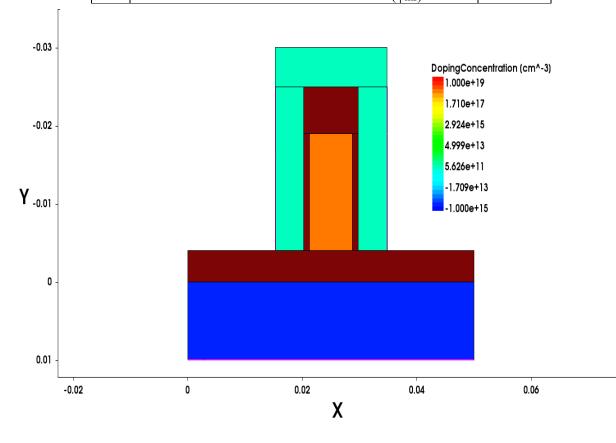

**2. Device Structure:** The simulated device cross-section has been shown in Figure (1). The drift diffusion and degradation model are used to analyze the quality of the Si-SiO<sub>2</sub> interface. The structure depicts a Double Gate FinFET device with different types of doping in the active region of the device to suppress short channel effects associated with the device at a lower technology node. Due to the Carrier Quantization effects that took place at this node, the density gradient quantization model was used along with the various transport models for simulations. Due to the presence of the higher doping concentration in the simulated device we have also included the Auger Recombination and Band Gap

Narrowing model has been used. This device is compatible with the existing fabrication technologies which is an added advantage.

| No | Parameters                                                          | Value |

|----|---------------------------------------------------------------------|-------|

| 1  | Gate Length of the Device (Lg) in nm                                | 22    |

| 2  | Length of the Source Region (L <sub>s</sub> ) in nm                 | 35    |

| 3  | Length of the Drain Region (L <sub>d</sub> ) in nm                  | 35    |

| 4  | Thickness of the Oxide Layer (Tox) in nm                            | 1 – 5 |

| 5  | Gate to Source Voltage (V <sub>gs</sub> ) in Volts                  | 1.2   |

| 6  | Acceptor Doping Concentration (N <sub>a</sub> ) in cm <sup>-3</sup> | 1017  |

| 7  | Donor Doping Concentration (N <sub>d</sub> ) in cm <sup>-3</sup>    | 1019  |

| 8  | Metal-Semiconductor Work Function ( $\phi_{ms}$ ) in eV             | 4.4   |

Table (1): Simulations and calculations parameters used for the study.

Figure (1): Simulated device cross-section.

#### 3. Mathematical Study of the Device

Uniformly Doped Device Threshold Voltage is [13, 14]

$$V_{threshold} = V_{flatband} + \phi_{s+\frac{\sqrt{2.\varepsilon_{s.q.NA.\phi_s}}}{Coxide}}$$

For a constant Threshold Voltage, Acceptor Doping Concentration ( $N_A$ ) should not increase unless the oxide Capacitance ( $C_{OX}$ ) is increased which indicates that the oxide thickness should decrease. The threshold voltage can be rewritten as:

© Applied Science Innovations Pvt. Ltd., India

Carbon - Sci. Tech. 10/4(2018)87-94

$$V_{threshold} = V_{flatband} + \phi_s \left[ 1 + \frac{2\mathcal{E}_{sTox}}{EoxideW_d} \right]$$

The electric field on the surface can be given as:  $E_{surface} = \frac{r^2}{T_{ld}}$

Due to the applied bias oxide field is:

$$E_{oxide} = E_{surface} \cdot \frac{\mathcal{E}_s}{\mathcal{E}_{ox}}$$

The voltage of the oxide is:

$$V_{oxide} = \phi_s \cdot \frac{T_{oxide}}{T_{ld}} \cdot \frac{\varepsilon_s}{\varepsilon_{ox}}$$

For steep retrograde device Threshold Voltage is: Vthreshold = Vflatband +  $\phi_s \left[ 1 + \frac{Toxide}{T_{Ld}} + \frac{\varepsilon_s}{\varepsilon_{OT}} \right]$

ations (1) and (5), we get:

$$V_{oxide} = \frac{\sqrt{2\varepsilon_{s.}q.N_{A.}\phi_s}}{\varepsilon_{ox}}.T_{oxide}$$

Comparing equa

Equating equations (9) and (4), we get:

$$T_{ld} = \sqrt{\frac{\phi_{s.\mathcal{E}s}}{2.q.N_A}}$$

where, T<sub>ld</sub> is lightly doped thin layer thickness.

It can be shown that T<sub>ld</sub> must be scaled in the extent to T<sub>oxide</sub> if we do not want any fluctuations in the device threshold voltage. For a steep retrograde doping profile used in this paper, depletion width was found to be half of the uniform doping profile and at the same time no threshold voltage fluctuations are present in the device. This one of the major advantage we get in this new type of doping [8]. This helped us to calculate the threshold voltage for the steep retrograde device depending upon the concentration in the active region. For maintaining, the tradeoff between off-state leakage and channel length reduction, depletion width, as well as oxide thickness, should be scaled in proportion. For extremely small channel length devices which demands an increase in a doping concentration of the device. The consequence of increased doping concentration is increased threshold voltage for uniformly doped devices. The trade-off between the threshold voltage and supply voltage also needs to be maintained otherwise the device performance will decrease due to a large reduction of gate drive.

#### 4. Results and Discussion:

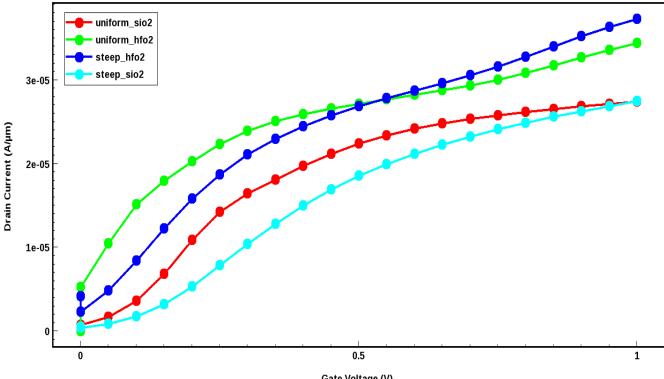

The  $I_d$ , Vs,  $V_{gs}$  characteristics of the device has been plotted in Figure (1.1). As it has been shown in the plotted graph that the leakage current is being suppressed greatly with the inclusion of the hafnium dioxide. Further, it is clear that the steep retrograded doping profile does not allow the current to be saturated. This also shows that the drain current has been greatly increased as compared to its counterpart in the plotted graph and further this indicates that the carrier random thermal velocity is increasing slowly which help us to reduce the scattering near the interface of the device thus reducing the effect of the hot carrier in the device.

Gate Voltage (V)

Figure (1.1): Drain Current (Id) Vs. Gate to Source Voltage (Vgs) characteristics of the device.

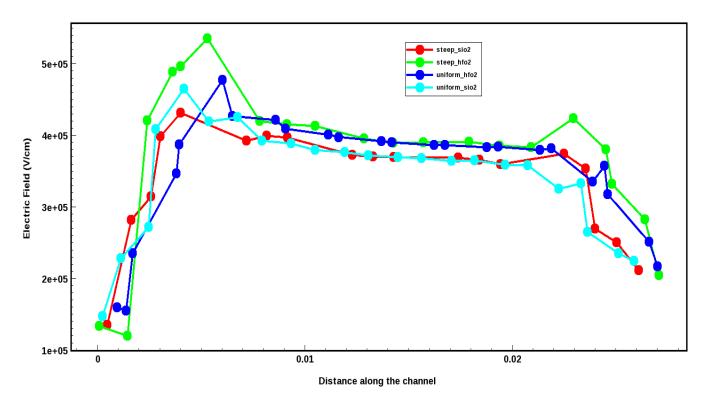

Figure (1.2): Variations of the Electric Field along the channel of the device.

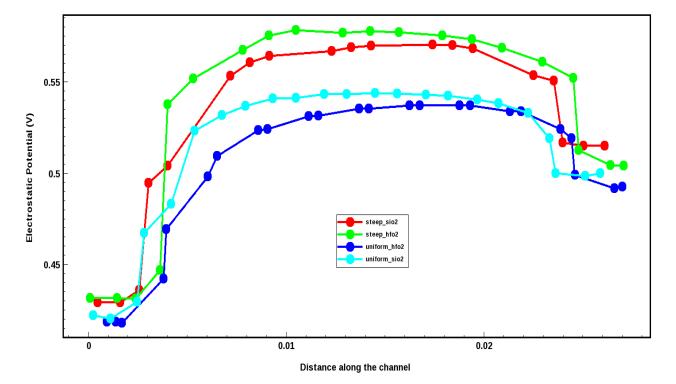

Figure (1.3): Variation of electrostatic potential along the channel of the device.

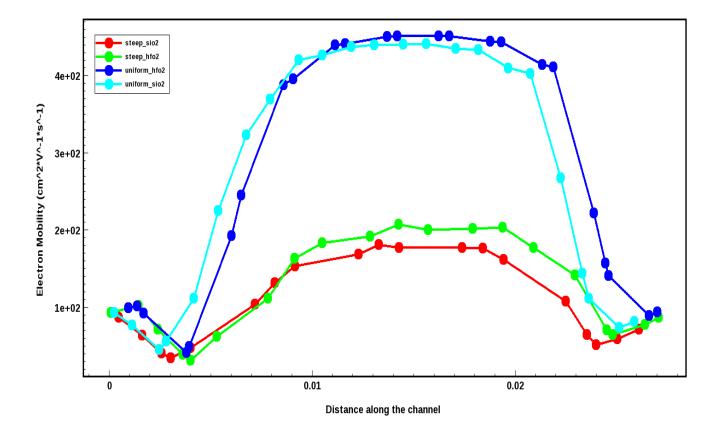

Figure (1.4): Variation of Electron Mobility along the channel of the device.

Distance along the channel

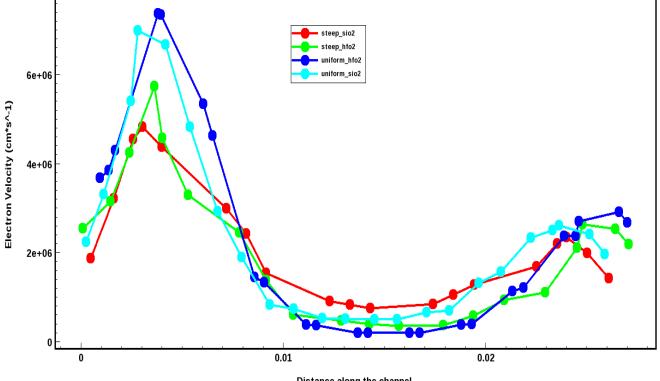

Figure (1.5): Variation of Electron Velocity along the channel of the device.

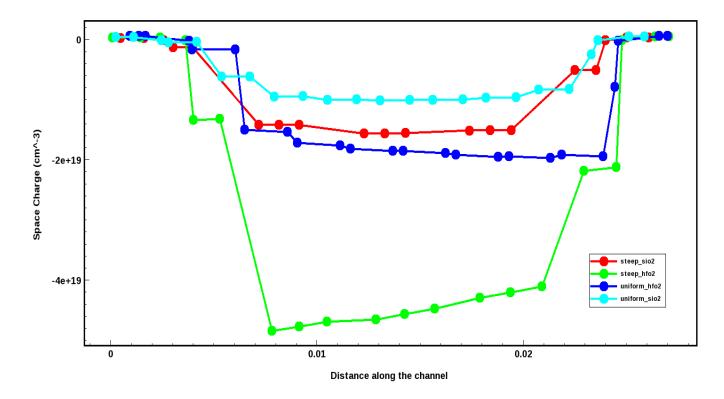

Figure (1.6) Variation of Space Charge along the channel of the device.

The variations of the electric field along the channel of the device has been shown in Figure (1.2). The electric field is found to be increased compared to the traditional dielectric materials for the used hafnium dioxide and thus the increased field also suggests that the carrier can gain enough velocity to travel through the channel without being scattered to the gate oxide interface. The peak of the electric field near the source side of the device indicates that the carrier is getting enough accelerated at the beginning but their velocity gets reduced somehow in the middle of the channel due to the channel interface region being doped with lighter doping concentrations but as the carriers reach the drain region of the device there is a slight increase in the carrier velocity again in the region due to the pinch-off region near the drain but this is not that much affecting the device performance as the values are in the limit and thus it will not have much impact on the overall device operations. The variation of the electrostatic potential has been plotted along the channel for the simulated device in Figure (1.3). The plot reveals the electrostatic control of the gate over the channel and it is clear for the plot that the device with the steep retrograde doping profile and hafnium dioxide as a dielectric material is having the best control reason being that the region near the gate and oxide layer is highly insulated such that the carrier cannot easily penetrate through this region and thus the gate leakage is not affecting the device performance much in the steep retrograde device. The electron mobility has been plotted along the channel for the simulated device in Figure (1.4). The mobility as depicted by the plot for the steep doping profile is lower as compared to the uniform profile due to the presence of much lighter region near the channel which helps us to have higher channel inversion near the interface thus will give more current for the same device. Further, the effects of the higher velocity of the carrier i.e. scattering will not be found in the steep device. The variations of the electron velocity along the channel have been plotted in Figure (1.5). The electron velocity was found to be high enough at the source end of the device for all the doping profile but as we move towards the drain region of the device is was found to be decreased gradually and then again it started increasing near the drain end. The main reason for this is the reduction in the mobility of the carrier in the channel. The variation of the space charge along the channel has been depicted in Figure (1.6). The variations show that the channel is getting highest inverted for the steep devices and hafnium oxide-based devices as compared uniformly doped devices with silicon dioxide as a dielectric.

**5.** Conclusions: The study shows how surface mobility of the device can be enhanced by reducing the ionized impurity scattering using a low-high channel doping profile in the device. Prevent dopant diffusion must be taken care of and thus the said doping profile is mostly used. For a required  $V_{\text{threshold}}$ , this doping profile gives smaller depletion width as compared to its counterpart. Also, the mobility of the carries in the channel can be improved using a low-high doping profile. Thus, a new type of doping profile named as Steep Retrograde Doping is needed in order to reduce gate controlled depletion width while maintaining the threshold voltage scaling trends for optimized device performance. This doping is a low-high channel doping which is vertically non-uniform and is used to improve the short channel effects and also increase the surface mobility simultaneously.

**6.** Acknowledgments: The Authors would like to thank SMDP-C2SD Project for providing the necessary resources and support.

### 7. References:

- [1] Chenming Calvin Hu, Modern semiconductor devices for integrated circuits. Upper Saddle River, N. J: Prentice Hall, 2010.

- [2] Roy Kaushik, Hamid Mahmoodi-Meimand, Saibal Mukhopadhyay, Juan A. Montiel-Nelson, and Dimitris Pavlidis, VLSI Circuits and Systems, 2003.

- [3] I. De, C. M. Osburn, 'Impact of super-steep-retrograde channel doping profiles on the performance of scaled devices', IEEE Transactions on Electron Devices, 1999.

- [4] Nirmal, Vijaya Kumar, K Shruti, Divya Mary Thomas, Patrick Chella Samuel, and Mohan Kumar, 'Analysis of Single Halo Double Gate MOSFETs using high-k dielectrics', 2011 3<sup>rd</sup> International Conference on Electronics Computer Technology, 2011.

- [5] G. V. Reddy, 'A New Dual-Material Double-Gate (DMDG) Nanoscale SOI MOSFET Two Dimensional Analytical Modeling and Simulation', IEEE Transactions on Nanotechnology, 3/2005.

- [6] H. R. Huff and D. C. Gilmer, High Dielectric Constant Materials VLSI MOSFET Applications, Springer Berlin Heidelberg, New York, 2005.

- [7] De and C. M. Osburn, 'Impact of super-steep-retrograde channel doping profiles on the performance of scaled devices', in IEEE Transactions on Electron Devices, vol. 46, no. 8, pp.1711-1717, Aug1999; doi:10.1109/16.777161

- [8] J. S. Suehle, "Ultrathin gate oxide reliability: physical models, statistics, and characterization," in IEEE Transactions on Electron Devices, vol. 49, no. 6, pp. 958-971, Jun. 2002; doi: 10.1109/TED.2002.1003712

- [9] Oldiges, P., R. Muralidhar, P. Kulkarni, C-H. Lin, K. Xiu, D. Guo, M. Bajaj, and N. Sathaye, 'Critical analysis of 14nm device options', 2011 International Conference on Simulation of Semiconductor Processes and Devices, 2011.

- [10] G. G. Shahidi, D. A. Antoniadis, and H. I. Smith, 'Indium channel implant for the improved short- channel behavior of submicrometer NMOSFET's', IEEE Trans. Electron Devices, vol. 14, p. 409, Aug. 1993.

- [11] K. Noda, T. Uchida, T. Tatsumi, T. Aoyama, H. Miyamoto, and I. Sasaki, '0.1 m delta-doped MOSFET using post low-energy implanting selective epitaxy', in Proc. Symp. VLSI Technol., 1996, p. 19.

- [12] R. Kircher, J. Moruta, M. Foruno, K. Aizawa, M. Kato, A. Horinouchi, and S. Ono, 'In-situ doping of epitaxial silicon by low-temperature LPCVD for the fabrication of delta-doped MOSFET's', in Proc. Int. Conf. SSDM, 1991, p. 672.

- [13] M. Aoki et. al., 'Design and performance of 0.1 \_m CMOS devices using low-impurity channel transistors', IEEE Electron Device Lett., vol. 13, p. 50, Jan. 1992.

- [14] K. Yamaguchi, Y. Shiraki, Y. Katayama, and Y. Muriyama, 'A new short-channel MOSFET with an atomic-layer-doping impurity profile', Jpn. J. Appl. Phys., vol. 22, pp. 267–270, 1983.

- [15] Rajiv Ranjan Thakur and Pragati Singh, 'Study of Quantization and Carrier Scattering Effects in SOI Tri-Gate FinFET for SoC Applications', 2018 2nd International Conference on Trends in Electronics and Informatics (ICOEI). IEEE, 2018.

- [16] Rajiv Ranjan Thakur and Pragati Singh, 'Analysis of interface trap charges and densities using capacitance-voltage (CV) and conductance voltage (GV) methods in steep retrograded Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub> based gate all around FinFETs', AIP Conference Proceedings. Vol. 2009. No. 1. AIP Publishing, 2018.

\*\*\*\*