## A 4.8-μV<sub>rms</sub>-Noise CMOS-Microelectrode Array With Density-Scalable Active Readout Pixels via Disaggregated Differential Amplifier Implementation

Jun Ogi<sup>1\*</sup>, Yuri Kato<sup>1</sup>, Yusaku Nakashima<sup>2</sup>, Kenji Ikeda<sup>2</sup>, Motoko Jingu<sup>1</sup>, Yoshihisa Matoba<sup>1</sup>, Naohiko Kimizuka<sup>1</sup>, Chigusa Yamane<sup>3</sup>, Masataka Maehara<sup>3</sup>, Takuya Kishimoto<sup>2</sup>, Shigeki Hashimoto<sup>2</sup>, Eriko Matsui<sup>2</sup> and Yusuke Oike<sup>1</sup>

<sup>1</sup> Research Division 1, Sony Semiconductor Solutions Corporation, Kanagawa, Japan, <sup>2</sup> Department of Biomedical Research, R&D Center, Sony Corporation, Tokyo, Japan, <sup>3</sup> Research Division 2, Sony Semiconductor Solutions Corporation, Kanagawa, Japan

We demonstrate a  $4.8 - \mu V_{rms}$  noise microelectrode array (MEA) based on the complementary-metal-oxide-semiconductor active-pixel-sensors readout technique with disaggregated differential amplifier implementation. The circuit elements of the differential amplifier are divided into a readout pixel, a reference pixel, and a column circuit. This disaggregation contributes to the small area of the readout pixel, which is less than 81  $\mu$ m<sup>2</sup>. We observed neuron signals around 100  $\mu$ V with 432 electrodes in a fabricated prototype chip. The implementation has technological feasibility of up to 12- $\mu$ m-pitch electrode density and 6,912 readout channels for high-spatial resolution mapping of neuron network activity.

Keywords: microelectrode array (MEA), CMOS integration circuits, readout noise, differential amplifier circuit, neuron action potentials

## INTRODUCTION

In previous decades, a complementary-metal-oxide-semiconductor (CMOS)-based MicroElectrode Array (MEA) was introduced to achieve two-dimensional high spatial resolution mapping of action potentials (APs) (Eversmann et al., 2003; Ballini et al., 2014). The high resolution mapping of APs in neuron cells can provide information regarding the complexities of neuron network activities, such as the nature of dendritic integration, the electrical functions of dendritic spines, and variations in spontaneous native activity patterns or network oscillations (Gross et al., 1997; Peterka et al., 2011).

#### OPEN ACCESS

#### Edited by:

Günther Zeck, Natural and Medical Sciences Institute, Germany

#### Reviewed by:

Domenico Caputo, Sapienza University of Rome, Italy Bruce C. Wheeler, University of Florida, United States

> \***Correspondence:** Jun Ogi Jun.Ogi@sony.com

#### Specialty section:

This article was submitted to Neural Technology, a section of the journal Frontiers in Neuroscience

Received: 31 October 2018 Accepted: 27 February 2019 Published: 21 March 2019

#### Citation:

Ogi J, Kato Y, Nakashima Y, Ikeda K, Jingu M, Matoba Y, Kimizuka N, Yamane C, Maehara M, Kishimoto T, Hashimoto S, Matsui E and Oike Y (2019) A 4.8- μV<sub>rms</sub>-Noise CMOS-Microelectrode Array With Density-Scalable Active Readout Pixels via Disaggregated Differential Amplifier Implementation. Front. Neurosci. 13:234. doi: 10.3389/fnins.2019.00234

1

To better comprehend the network activity, both readout channel numbers and electrode density must be further increased while maintaining sufficiently low noise levels (less than 10  $\mu$ V<sub>rms</sub>). Various implementation methods have been proposed in previous works on the CMOS-MEA (Obien et al., 2015). While readout techniques with Active Pixel Sensors (APS) have been proposed to increase the channel number to over ten thousand, electrode density is limited above electrode pitch of 30  $\mu$ m, because of the large area of the readout circuits integrated under the each electrode (Huys et al., 2012; Johnson et al., 2013). We present scalability for a higher-density and larger channel number with a 24-um-pitch and 6,912-readout-channels CMOS-MEA (Ogi et al., 2017). However, the noise level was 23  $\mu$ V<sub>rms</sub> in this CMOS-MEA, and this was not sufficiently low to observe the neuron APs.

In this paper, we demonstrate a  $4.8 \cdot \mu V_{rms}$  noise CMOS-MEA based on the APS readout technique with disaggregated differential amplifier implementation method. This has the technological feasibility for high-density electrode integration with 12- $\mu$ m pitch electrode density and 6,912 readout channels.

#### IMPLEMENTATION

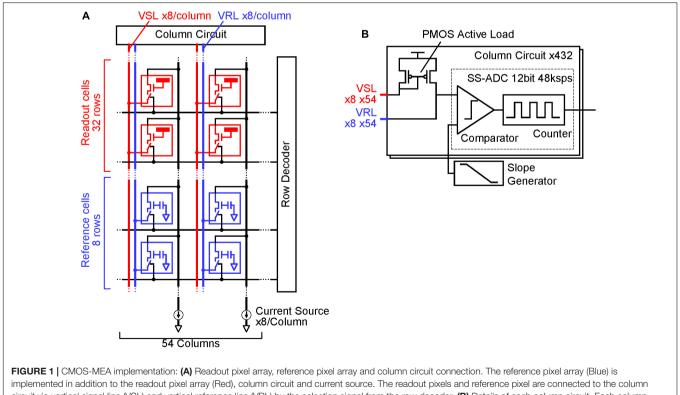

To reduce noise in the readout channel of CMOS-MEAs, the channel is usually equipped with a large input capacitance, a low-noise and high-gain differential amplifier, and a band pass filter (Frey et al., 2010). In previous works for sub-10  $\mu V_{rms}$  readout noise using the APS, these circuit elements were integrated under each electrode, increasing the readout pixel area (Johnson et al., 2013). Figure 1 shows the readout implementation of this work. The circuit elements in the differential amplifier are divided into the readout pixel, the reference pixel and the column circuit in this implementation; we call this disaggregated differential amplifier.

In addition to the readout pixel array and the column circuits, the reference pixel array is implemented. Electrodes that can sense cell AP are directly connected to the input amplifier in the readout pixel. In the reference pixel, the input amplifier connects to the ground via an input capacitance. When each one row in the readout and reference pixel array is selected by a signal from the row decoder, the two input amplifiers are connected to the PMOS active load in the column circuit via vertical signal line (VSL) and vertical reference line (VRL), and the differential amplifier is constituted by the connection. This differential amplifier amplifies the AP signals from the sensing electrode, and it contributes in relatively reducing the input-referrednoise induced by analog to digital converters (ADCs) after the amplifier. Despite the simplicity and small area of the readout pixel circuit, the high-gain differential amplifier can be implemented by the disaggregation of the circuit components in each block.

implemented in addition to the readout pixel array (Red), column circuit and current source. The readout pixels and reference pixel are connected to the column circuit via vertical signal line (VSL) and vertical reference line (VRL) by the selection signal from the row decoder. **(B)** Details of each column circuit. Each column circuit includes a pair of PMOS active loads and a single slope ADC. The combination of one readout pixel, one reference pixel and a pair of PMOS active load acts as a differential amplifier, which amplifies the input signal at the readout pixel before input to ADC.

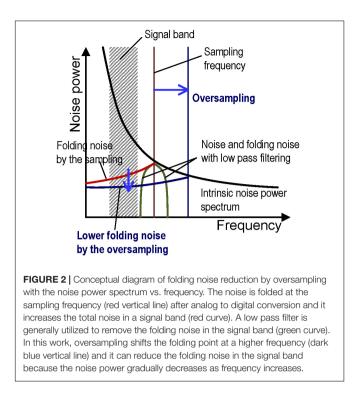

Single slope ADCs (SS-ADCs) have the advantage of highspeed data conversion through the use of a high-speed input clock (Wakabayashi et al., 2010) and it performs 48-ksps (sample per second) high-speed ADC with 12-bit resolution in this work. The number of VSLs and column circuits are eight times larger than the pixel column numbers, as shown in Figure 1, so that the 8-rows and 54-columns pixel array (total 432 pixels) can be read simultaneously with the 432 parallel VSLs and column circuits at 48-ksps. In contrast, the required signal frequency band to measure neuron AP (AP band) ranges from 300 Hz to 3.3 kHz (Yuan et al., 2016), and the required minimum sampling rate is about 6 kHz. The 48-ksps sampling rate, which is eight times larger than the 6 kHz, contributes in reducing the folding noise in the ADC, as shown in Figure 2. Higher frequency noise is folded at the half of the sampling rate, and the folding noise increases the noise power in the signal frequency band. A low pass filter is usually utilized to cut the folding noise. On the other hand, the noise power is gradually decreased as frequency is increased and over sampling can shift the folding point of the noise to lower noise power. As a result, oversampling can reduce the folding noise instead of the low pass filter. This also contributes in decreasing the pixel area, due to the absence of the low pass filter in each pixel.

## PROTOTYPING

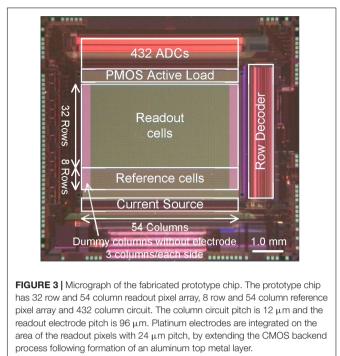

**Figure 3** shows a micrograph of a fabricated prototype chip with a 0.14- $\mu$ m 1-poly 3-Cu 1-Al CMOS process. The column circuit pitch is 12  $\mu$ m and the readout electrode pitch is 96  $\mu$ m. Although the electrode pitch is limited by the number

of the column circuits, the readout circuit area in each pixel is less than 81  $\mu m^2$ . This is considerably smaller than the 450  $\mu m^2$  in the previous two-stage amplifier implementation (Huys et al., 2012). The 432 column circuits were integrated in the small area over the readout pixel array because of the area efficiency and the high-density integration of single slope ADCs. The small readout circuit area and small column pitch contribute to the high-scalability of the CMOS-MEA in this work.

Platinum electrodes are integrated on the area of the readout pixels with 24  $\mu$ m pitch, by extending the CMOS backend process following formation of an aluminum top metal layer. Selected electrodes with 96  $\mu$ m pitch are connected to the active readout pixels one by one and work as the sensing electrodes.

## MEASUREMENT RESULTS

#### **Random Noise on Readout Circuit**

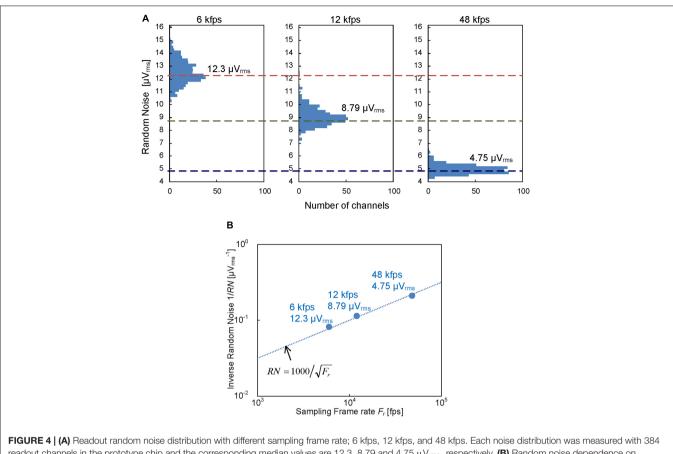

**Figure 4** shows that the input-referred noise on the readout channels in the prototype CMOS-MEA was reduced to 4.75  $\mu$ V<sub>rms</sub> after post-processing of the frequency band limitation to the AP band by digital finite response (FIR) filters. The intrinsic noise without FIR filtering was reduced to 12.8  $\mu$ V<sub>rms</sub> by the disaggregated differential amplifier implementation. In addition, the noise after filtering was further reduced by the over sampling in the ADCs, as shown in **Figure 4A**. The reduction is proportional to the inverse of the readout sampling rate, as shown in **Figure 4B**. These results show that the disaggregated differential amplifier and the oversampling can reduce the random noise as we intend.

readout channels in the prototype chip and the corresponding median values are 12.3, 8.79 and 4.75  $\mu$ V<sub>ms</sub>, respectively. **(B)** Random noise dependence on sampling frame rate. The frame rate dependence is proportional to the inverse of the frame rate.

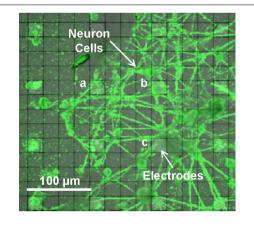

**FIGURE 5** Optical micrograph image of neuron cells cultured on the prototype CMOS-MEA. A fluorescence image of the neuron cells is composited on the visible image of the microelectrode array. The green shapes are cultured neuron cells and the gray bright regions under the neurons are the sensing electrodes.

## **Neuron Action Potential**

Figure 5 is a visible optical micrograph of the prototype CMOS-MEA with composited fluorescence imaging of neonatal

pyramidal neurons primary cultured on the prototype chip. The gray bright regions under the green neurons are the sensing electrodes. The neurons were cultured on the electrode coated with PDL and Laminin for 4 weeks in 37°C 5% CO<sub>2</sub>. PKH67 Green Fluorescent Cell Linker Midi Kit for General Cell Membrane Labeling was used to capture the fluorescence imaging of the neuron cells.

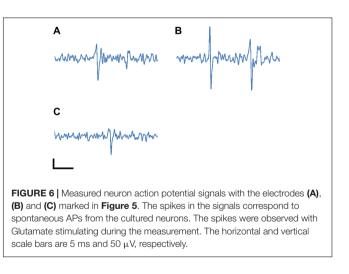

Figure 6 shows action potential signals observed with electrodes (a), (b) and (c) covered by the cultured neurons in Figure 5. The spikes in the signals correspond to spontaneous APs from the cultured neurons with Glutamate stimulating. 100  $\mu$ V peak signal levels were clearly recognized because of the sufficiently low noise in the readout circuit. These results show the feasibility of our CMOS-MEA technology for neuron AP measurements.

# SCALABILITY AND COMPARISON WITH PREVIOUS WORK

The electrode density and channel number can both be increased by increasing the ADC number and pixel multiplication factor for each ADC, due to the small readout pixel area and small column pitch in the CMOS-MEA technology proposed in this work.

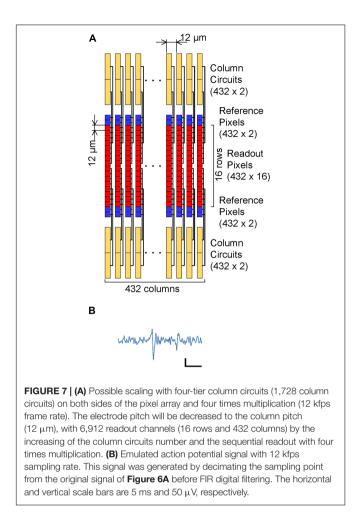

**Figure 7A** shows the case of four-tier column circuits (a total of 1,728 column circuits) on both sides of the pixel array with four times multiplication. The larger number of column circuits, compared with the prototype in the present work, contributes to an increase in the readout electrode number and a reduction in the electrode pitches, even with the same in-pixel and column circuit implementations as those in the present work. In the

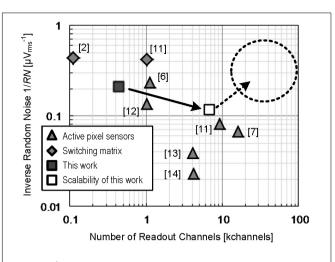

FIGURE 8 | Comparison of this work with previous works for high-density CMOS-MEA in terms of the relations between readout channels number and readout noise. The shaded triangles present the previous works on APS readout scheme and the shaded diamonds denote the previous works on switching matrix readout scheme. The closed square presents the result of this work. The opened square indicates possible scaling applying the CMOS-MEA technology proposed in this work. The area in the dashed circle is also feasible to achieve by applying more advanced CMOS processes with our CMOS-MEA readout scheme.

present work, the column pitch limits the readout electrode pitch, because the in-line eight column circuits (96  $\mu$ m pitch) are needed to simultaneously read eight rows. On the other hand, for the four-tier case, four rows of the pixel array with a 12  $\mu$ m pitch can be read simultaneously by the four-tier column circuits and four parallel VSLs. In addition, the other four rows in the pixel array are connected to the same VSL and column circuit, and the connected rows are sequentially read with the selecting signals from the row decoder (four times multiplication). This quadruples the readout row number to 16, while it quarters the sampling frame rate to 12 kfps. As a result of the four-tier column circuits and four times multiplication, the readout electrode pitch is decreased to the column pitch (12  $\mu$ m) and 6,912 electrodes (16 rows and 432 columns) can be read at 12 kfps.

Although a small pitch of the electrode reduces the available area for the in-pixel readout circuits and affects the readout noise level, the noise level is still maintained because the area of each in-pixel circuit in this work was smaller than the area for 12  $\mu$ m square (= 144  $\mu$ m<sup>2</sup>), as mentioned in "Prototyping." On the other hand, the low sampling frame rate (12 kfps) should have increased the AP band noise to 8.8  $\mu$ V<sub>rms</sub>, as shown in **Figure 4B**, but the 100  $\mu$ V signal peak is still observed, as shown in **Figure 7B**, because the noise level was still less than 10  $\mu$ V<sub>rms</sub>. In addition, increasing the column circuit numbers should result in an increased chip size, however, the chip size is limited due to the small area of the ADCs, as can be seen in **Figure 3**.

Furthermore, the introduction of advanced processes for logic circuit in the column circuit can increase the channel number and decrease readout random noise. In single slope ADCs, the area and the sampling speed are limited by the transistor size for digital counter. However, the area can be decreased and the sampling speed can be increased by reducing the transistor size in the advanced CMOS processes. The small area contributes in increasing ADC numbers and readout channel numbers, and the higher sampling speed contributes in decreasing the readout random noise.

**Figure 8** shows the comparison of this work with previous works for high-density CMOS-MEA by relationships between readout channels number and readout noise. The noise in this work is one of the lowest levels in the previous works of the APS readout scheme (Imfeld et al., 2008; Huys et al., 2012; Johnson et al., 2013; Bertotti et al., 2014; Yuan et al., 2016; Lopez et al., 2018) and it is comparable with the previous works of switching matrix readout scheme (Ballini et al., 2014; Yuan et al., 2016), which has an advantage usable in readout noise reduction. The largest number of the channels in previous works is also feasible with the four-tier ADC implementation by applying the technology proposed in this work. Further scaling is also feasible up to 100 thousands readout channels with utilizing more advanced CMOS processes.

#### CONCLUSION

We introduce the disaggregated differential amplifier implementation that can reduce the circuit area of the readout

#### REFERENCES

- Ballini, M., Mualler, J., Livi, P., Chen, Y., Frey, U., Stettler, A., et al. (2014). A 1024channel CMOS microelectrode array with 26,400 electrodes for recording and stimulation of electrogenic cells in vitro. *IEEE J. Solid State Circuits* 49, 2705–2719. doi: 10.1109/JSSC.2014.2359219

- Bertotti, G., Velychkoy, D., Dodel, N., Keil, S., Wolanskyz, D., Tillakz, B., et al. (2014). "A CMOS-based sensor array for in-vitro neural tissue interfacing with 4225 recording sites and 1024 stimulation sites," in *Proceedings of the IEEE Biomedical and Life Science Circuit and Systems*, Lausanne, 304. doi: 10.1109/ BioCAS.2014.6981723

- Eversmann, B., Jenkner, M., Hofmann, F., Paulus, C., Brederlow, R., Holzapfl, B., et al. (2003). A 128 × 128 CMOS biosensor array for extracellular recording of neural activity. *IEEE J. Solid State Circuits* 38:2306. doi: 10.1109/JSSC.2003. 819174

- Frey, U., Sedivy, J., Heer, F., Pedron, R., Ballini, M., Mueller, J., et al. (2010). Switchmatrix-based high-density microelectrode array in CMOS technology. *IEEE J. Solid State Circuits* 45, 467–482. doi: 10.1109/JSSC.2009.2035196

- Gross, G. W., Harsch, A., Rhoades, B. K., and Gopel, W. (1997). Odor, drug and toxin analysis with neuronal networks in vitro :extracellular array recording of network responses. *Biosens. Bioelectron.* 12, 373–393. doi: 10.1016/S0956-5663(97)00012-2

- Huys, R., Braeken, D., Jans, D., Stassen, A., Collaert, N., Wouters, J., et al. (2012). Single-cell recording and stimulation with a 16k micro-nail electrode array integrated on a 0.18 mm CMOS chip. *Lab Chip* 12, 1274–1280. doi: 10.1039/ c2lc21037a

- Imfeld, K., Neukom, S., Maccione, A., Bornat, Y., Martinoia, S., Farine, P. A., et al. (2008). Large-scale, high-resolution data acquisition system for extracellular recording of electrophysiological activity. *IEEE Trans. Biomed. Eng.* 55, 2064–2063. doi: 10.1109/TBME.2008.919139

- Johnson, B., Peacey, S. T., Clelandz, T. A., and Molnar, A. (2013). "A 50µm pitch, 1120-channel, 20kHz frame rate microelectrode array for slice recording," in *Proceedings of the Conference on IEEE Biomedical Circuits and Systems (BioCAS)* (Rotterdam: IEEE). doi: 10.1109/BioCAS.2013.6679651

- Lopez, C. M., Chun, H. S., Berti, L., Wang, S., Putzeys, J., Bulcke, C. V. D., et al. (2018). "A 16384-electrode 1024-channel multimodal CMOS MEA for

pixel in CMOS-MEA with APS readout technique. The prototype chip with the implementation demonstrated a  $4.8 - \mu V_{rms}$  readout noise and observation of neuron AP at about a 100  $\mu V$  signal level. The CMOS-MEA technology proposed in this work is scalable for high spatial resolution mapping of neuron network activity up to 100 thousands readout channels.

#### DATA AVAILABILITY

The datasets generated for this study are available on request to the corresponding author.

#### **AUTHOR CONTRIBUTIONS**

JO, YK, MJ, YM, NK, CY, MM, and YO contributed to the CMOS circuit design and prototyping, and circuit characteristics evaluation. YN, KI, TK, SH, and EM contribute to observation of the neuron action potential with the prototype chip.

#### ACKNOWLEDGMENTS

We would like to thank Editage (www.editage.jp) for English language editing.

high-throughput intracellular action potential measurements and impedance spectroscopy in drug-screening applications," in *Proceedings of the IEEE International Solid State Circuit Conference*, San Francisco, CA, 464. doi: 10. 1109/ISSCC.2018.8310385

- Obien, M. E. J., Deligkaris, K., Bullmann, T., Bakkum, D. J., and Frey, U. (2015). Revealing neuronal functiont hrough microelectrode array recordings. *Front. Neurosci.* 9:423. doi: 10.3389/fnins.2014.00423

- Ogi, J., Kato, Y., Matoba, Y., Yamane, C., Nagahata, K., Nakashima, Y., et al. (2017). Twenty-four-micrometer-pitch microelectrode array with 6912channel readout at 12 kHz via highly scalable implementation for high-spatialresolution mapping of action potentials. *Biointerphases* 12:05F402.

- Peterka, D. S., Takahashi, H., and Yuste, R. (2011). Imaging voltage in neurons. *Neuron* 69, 9–21. doi: 10.1016/j.neuron.2010.12.010

- Wakabayashi, H., Yamaguchi, K., Okano, M., Kuramochi, S., Kumagai, O., Sakane, S., et al. (2010). "A 1/2.3-inch 10.3Mpixel 50frame/s back-illuminated CMOS image sensor," in *Proceedings of the IEEE International Solid State Circuit Conference*, San Francisco, CA, 410. doi: 10.1109/ISSCC.2010. 5433963

- Yuan, X., Kim, S., Juyon, J., D'Urbino, M., Bullmann, T., Chen, Y., et al. (2016).

"A microelectrode array with 8,640 electrodes enabling simultaneous full-frame readout at 6.5 kfps and 112-channel switch-matrix readout at 20 kS/s," in *Proceedings of the IEEE VLSI Circuit* (Delft: TU Delft), 258. doi: 10.1109/VLSIC. 2016.7573558

**Conflict of Interest Statement:** All authors were employed by Sony Corporation. JO, YK, MJ, YM, NK, CY, MM, and YO were also loaned employee in Sony Semiconductor Solutions Corporation.

Copyright © 2019 Ogi, Kato, Nakashima, Ikeda, Jingu, Matoba, Kimizuka, Yamane, Maehara, Kishimoto, Hashimoto, Matsui and Oike. This is an open-access article distributed under the terms of the Creative Commons Attribution License (CC BY). The use, distribution or reproduction in other forums is permitted, provided the original author(s) and the copyright owner(s) are credited and that the original publication in this journal is cited, in accordance with accepted academic practice. No use, distribution or reproduction is permitted which does not comply with these terms.