A Microprogrammed Operating System Kernel

Andrew James Herbert

St. John's College

A dissertation submitted for the degree of Doctor Of Philosophy in the University Of Cambridge, November 1978.

Except where otherwise stated in the text, this dissertation is the result of my own work and is not the outcome of any work done in collaboration.

Copyright @ A. J. Herbert. 1978

Thesis Summary

"A Microprogrammed Operating System Kernel"

Andrew James Herbert

St. John's College

The subject of the thesis is the design and implementation of an operating system kernel for the Cambridge Capability Computer (CAP). The kernel of an operating system is its most primitive level of facilities and forms the foundation stone around which the rest of the system is structured.

The particular emphasis of the CAP kernel is concerned with protection the control of access to information. The kernel uses the notion of capabilities to provide a flexible and controlled mechanism for the sharing of information within a computer system. The protection mechanisms include provision for the efficient control of access to memory as well as facilities for handling abstract resources like files and virtual peripherals. The kernel allows the introduction of new types of resources in addition to the basic set of hardware resources to permit user extension of the system. Attention is given to the problem of recall of privilege or revocation in capability systems and the kernel includes operations for both permanent and temporary revocation of particular access rights to information in a selective manner.

In the past many of these functions have only been found in kernels implemented in user-level software which are frequently cumbersome and inefficient. An examination is made of why this should be and how efficiency and simplicity can be gained by a microprogrammed implementation. The thesis draws on the experience of a number of software kernels to discover the various design decisions that have to be made and the techniques that may be used to implement a successful kernel.

The feasibility of the design arrived at by considering these issues is demonstrated by describing its implementation on the Cambridge Capability Computer in terms of the primitives provided and the internal organisation of the proposed kernel. In an evaluation, the kernel is examined in the light of the analysis of other kernels to point out its strengths and weaknesses and to gain insights into the utility of the design as a practical operating system kernel.

#### PREFACE

I am indebted to my supervisor, Dr Roger Needham, for his encouragement of my research and also to other members of the CAP Project, especially Dr Andrew Birrell, Dr Robin Walker and Martyn Johnson, for their helpful advice and constructive criticisms during all of the stages of my work.

The Computer Laboratory Of The University Of Cambridge, headed by Professor M.V. Wilkes, furnished many facilities, including use of the CAP computer and, in conjunction with St. John's College Cambridge, provided funds enabling me to visit the United States Of America in my final year which proved to be a valuable and stimulating experience.

The CAP Project as a whole and my own work in particular were supported by the Science Research Council during the period that the research was carried out.

Finally I wish to acknowledge my debt to my wife Jane, both for her support and forbearance while I was engaged in research and more recently for her help in typing this thesis.

# CONTENTS.

|     | CHAPTER PAGE                               |

|-----|--------------------------------------------|

| 1.  | Introduction1                              |

| 2.  | Kernel Design Principles14                 |

| 3.  | Capabilities And Naming21                  |

| 4.  | Capabilities And Addressing                |

| 5.  | Type-Extension Mechanisms44                |

| 6.  | Revocation Mechanisms53                    |

| 7.  | Processes And Protection Domains62         |

| 8.  | The CAP Computer73                         |

| 9.  | A Kernel For The CAP Computer              |

| 10. | Type-Extension And Revocation Operations97 |

| 11. | Domain And Process Structure               |

| 12. | Organisation Of The Kernel Microprogram121 |

| 13. | Review And Evaluation134                   |

|     | References140                              |

#### CHAPTER ONE.

#### INTRODUCTION.

#### 1.1. Overview.

The subject of this thesis is the design and implementation of a microprogrammed operating system kernel. The kernel of an operating system is the most primitive level of the system and forms the foundation of the rest of its structure and so it is important that the kernel is well-designed and efficient if the entire system is to be successful.

An operating system can be considered as a mapping between rudimentary hardware resources and the advanced facilities of an abstract machine. The duties of a kernel include the provision of mechanisms for performing this mapping and also making abstract resources such as files and virtual memory available to users through some addressing and access control schemes. The cost-effectiveness of an operating system can be judged by weighing the benefits of an elegant abstract machine, such as ease of use, against its cost, both in terms of development and the machine cycles consumed in its operation. The effectiveness of an entire system will be greatly impaired by any weaknesses or inefficiencies in the kernel and this is the motivation for investigating the structure and organisation of operating system kernels.

The major concerns of a kernel are protection (the control of access to information by programs running within a computer system), multiprogramming, I/O control and fault handling. This thesis is primarily concerned with the protection aspects of kernel design and the influence of protection on the other kernel functions. A protection architecture which permits flexible and controlled sharing of information by all programs, including those that make up the operating system will be described in the latter part of this thesis.

Many operating system kernels have been implemented in software rather than microprogram. Normally they execute in a

- 1-

highly privileged special state or supervisor mode in which powers are available that allow the contents of processor descriptor registers, and so on, to be modified. The close relationship between the kernel and the underlying hardware means that it is usual to find that the kernel has been written as a large monolithic assembly code program because of the difficulties of writing compilers to generate compact fast code that interfaces in a straightforward fashion with the hardware primitives used. In consequence, such kernels are difficult to verify and debug, even if great care is taken to ensure that code is written and tested in a well-structured and organised way.

In general, a software kernel preserves a lot of information about the state of the hardware so that it may decide what action to take in response to a kernel call by a program. It is therefore necessary for the kernel to carry out all operations that involve modifying hardware protection registers and the like; even quite trivial functions have to be directed through the kernel so that changes to the state of the hardware can be recorded. This will involve the considerable overhead of establishing kernel calls, which might include preserving and restoring the state of executing processes, and checking the arguments presented against tables of privileges before any function can be carried out. There is also a temptation, if an operating system service does little else beyond a series of kernel calls, to build it into the kernel and this further compounds the problem. Much of the clumsiness of a software kernel comes from a lack of intimacy with the hardware of the underlying machine that carries out the operations programmed in leads us to consider the the kernel and this use of а microprogrammed kernel because of the closer association between microprogram and the basic hardware.

Microprogramming is а long established technique for organising computer hardware [Wilkes 51]. Microprogramming has many properties that aid the development of machines which include complex operations in their instruction repertoire. A microprogrammable machine consists of a simple, fast microprogram processor with rudimentary logical, control and arithmetic

-2-

facilities that executes microinstructions held in a microprogram memory. The microprogram emulates user instructions by activating other parts of the machine in the correct sequence and arranging for the passage of data through the machine's registers. If the user machine is to be reasonably fast, the microprogram must be fetched from microstore and executed at high speed. In the past. when the cost of very fast memory was high, microprogram memories were very small, but now with falling hardware costs owing to integration (LSI) technology, large scale quite substantial memories of sufficient speed can be obtained for a reasonable This enables critical components of the software of a price. system to be put into microprogram to reap benefits in the areas of high level facilities and efficiency; for example, the GEC 4000 range of computers [GEC 72] have a microprogrammed nucleus that is responsible for the control of multiprogramming, synchronisation and inter-process communication.

There are other advantages apart from efficiency to be gained from microprogramming. A microprogrammed operating system kernel has a much greater degree of intimacy with hardware addressing and protection functions, interrupt handling and so on than a special state supervisor for a conventional machine. This makes it easier for the kernel to provide a powerful machine to users without the expense of kernel calls in software, because the microprogram is better placed to carry out access checking and argument verification cheaply as part of the normal hardware instruction decoding and addressing operations. Kernel functions can be encoded as a single instruction at the user level which means that interfaces tend to be simple in terms of a few arguments in registers and kernel calls are uniform with the hardware instruction and addressing formats. On the other hand, in a software kernel it is easy to make interfaces very complex and confusing for users.

It is an unfortunate fact of life that microprograms are on the whole harder to write and less easy to understand than assembly code programs. This is because microinstructions specify the operation of basic hardware components rather than the higher level logical functions expressed by machine instructions.

-3-

Furthermore, debugging is not straightforward as it requires use of the raw hardware for hands-on access which is wasteful of computer resources, whereas software systems can be tested concurrently on a time-shared system with other programs and can be written in high level languages. There is often insufficient room in microstore to include both a development microprogram and a debugging system, so that a lot of testing has to be carried out with just the aid of register display lights and control switches. To some extent these difficulties can be avoided by the use of a microprogram processor simulator, although it must be ensured that simulation faithfully duplicates the hardware because the microprogrammers are fond of taking advantage of hardware peculiarities and side-effects to save on instructions or time. If oddities are not carefully duplicated in the simulation, there is a strong likelihood that a microprogram will behave wrongly on the real machine.

Even in these days of large semiconductor memories, microprogram memories are usually of modest size, often only a few thousand bytes, which greatly restricts the amount that can be included in a microprogrammed kernel, whereas a software kernel may be many hundreds of thousands of bytes long. On the other hand, if there is microprogram memory space available, it is tempting to put more and more into the kernel on the grounds of efficiency, with the result that the kernel becomes cumbersome, unwieldy and much harder to debug fully and test. The key to microprogramming operating system kernels is thecorrect identification of those primitives that rightly belong in the kernel and those that should be left to software.

Microprogrammed machines may not be as fast as those built in hard-wired logic because of the overheads of fetching and decoding microinstructions. This is the penalty paid for the ability to implement highly complex functions and to change the nature of the machine by modifying its microprogram. speed Some can be recovered by providing functions such user instruction as decoding, address translation and protection checks in raw hardware and leaving the microprogram to handle more difficult loss of some flexibility in the things, at a range of

-4-

architectures that can be presented at the user level.

#### 1.2. A Wider View of Protection.

The bulk of this thesis is concerned with mechanisms for protection [Lampson 71, Jones 73, Graham 68, Saltzer and Schroeder 75], which can be defined as the control of access to information by executing programs. Protection is just one facet of the overall issue of computer security [Ware 67, Anderson 73, Branstad 73, Hoffman 73]. In recent times, computers have been used more and more as repositories for large volumes of information of a confidential or proprietory nature, shared by a large community of users who are unwilling to trust one another not to steal or access private data. The social and legal implications of retaining information within a computer have generated а requirement for the formulation of policies governing the security of computer systems [U.S. Department of Health, Education and Welfare 73] and to implement such policies there is is a need for a technological framework within which it is possible to discuss and judge the security of a computer system.

Aspects of security include hardware reliability, secure communication between terminals and computers, authentication of access to machines and the physical security of the computing system hardware and ancilliary equipment such as magnetic tapes and discs. These external issues of security can be characterised by the property that it is not possible to achieve total security in any of them; instead the measures taken to enhance security can be judged only in terms of the cost-effectiveness of reaching some level of quantified optimism about the degree of security The notion of the work factor involved in breaching the attained. security measures is often used as an indication of the amount of effort that must be expended to defeat security, and in many cases to discourage deliberate attack it is sufficient to ensure that the cost of the work done exceeds the value of the information that is illegally obtained. A system is only as strong as its weakest component and if the security of the system is undermined at any point all other aspects of it including protection, are put at risk.

-5-

If an artificial view of the real world in which external security can be guaranteed completely is adopted, it is possible to describe protection mechanisms which enable positive and absolute statements to be made about the security of information within a computer system in terms of which programs may access information and change it. This approach is useful despite its divergence from reality because, if protection can be established within a computer system, it is only necessary to concentrate upon the external aspects of security, safe in the knowledge that the system cannot be subverted from within. The protection state of a computer system can be represented by an access matrix [Lampson 71] whose columns correspond to items of information and whose rows refer to programs as shown below:

| program       | item |       |      |    |

|---------------|------|-------|------|----|

| а<br>С. С. А. | A    | В     | С    | D  |

| a             | R    | R     |      | RW |

| b             | R    | - 650 | 6000 | R  |

| с             | RW   | -     |      | -  |

| d             | RW   | -     | RW   | R  |

|               |      |       |      |    |

Program a has R (read) access to items A,B,D and also W (write) access for D, but is unable to access item C at all. Indeed, item C can only be accessed by program d. Obviously, in a real life system, an access matrix is vast, with entries for many items of information and programs. In the design of a protection system it is necessary to look for some suitable representation of the information in the matrix. There are two main approaches: (i) access control list systems such as MULTICS [Organick 72] in which each item has associated with it an access control list that encodes the information in a column of the matrix, stating which programs are allowed access to the item, and (ii) capability systems [Dennis and Van Horn 66, Lampson 69 and Needham 72] where each program is given a set of tickets stating which privileges are possessed by the program in respect of each item; that is to say, a program's set of capabilities is an encoding of a row in the access matrix.

It is fairly straightforward to arrange that information belonging to one program cannot be accessed by another, but in

-6-

general it should be possible to allow information to be shared by programs with possibly differing degrees of privilege; for example, in the access matrix above, the item A is shared by programs a, b, c, d with read access, but only d has the ability to write to it. In a closed community, programs and data might be shared with no restrictions, in a spirit of free cooperation, but if the computer is shared by a general public with competing interests, users will not trust one another and the sharing of information will take on the nature of commercial bargaining in which each party to a transaction is suspicious of the others. calls this mutual suspicion [Schroeder 72]. Schroeder A protection mechanism must be able to support controlled sharing in this sort of environment. For example, it should be possible for one user to allow another to have use of a program performing some service, while at the same time not allowing him read access to the binary code of the program, so that it may not be stolen or misused.

The level of trust between users will change with time and the owner of a privilege may subsequently wish to restrict use of it, perhaps because a user has defaulted on the payment of a rental. The action of recalling a privilege is known as <u>revocation</u>. Revocation may be temporary, and privileges might subsequently be restored when circumstances change. Sometimes it is only desired to recall a particular privilege while leaving other privileges for the object undisturbed, and this is known as partial revocation.

To summarise, protection is just one aspect of computer system security and protection mechanisms must be able to support a variety of protection policies that reflect the relationships between users of a system and the information it retains.

#### 1.3. A Framework for Discussion.

For this discussion, it is convenient to regard an operating system as an abstract machine that defines <u>operations</u> which can be carried out on a set of abstract <u>objects</u> such as files, I/O streams and virtual memory. The operating system is responsible for the mapping between basic hardware resources and the the set

-7-

of objects. Each object has an attribute known as its <u>type</u> which specifies the set of operations that can be meaningfully applied to it.

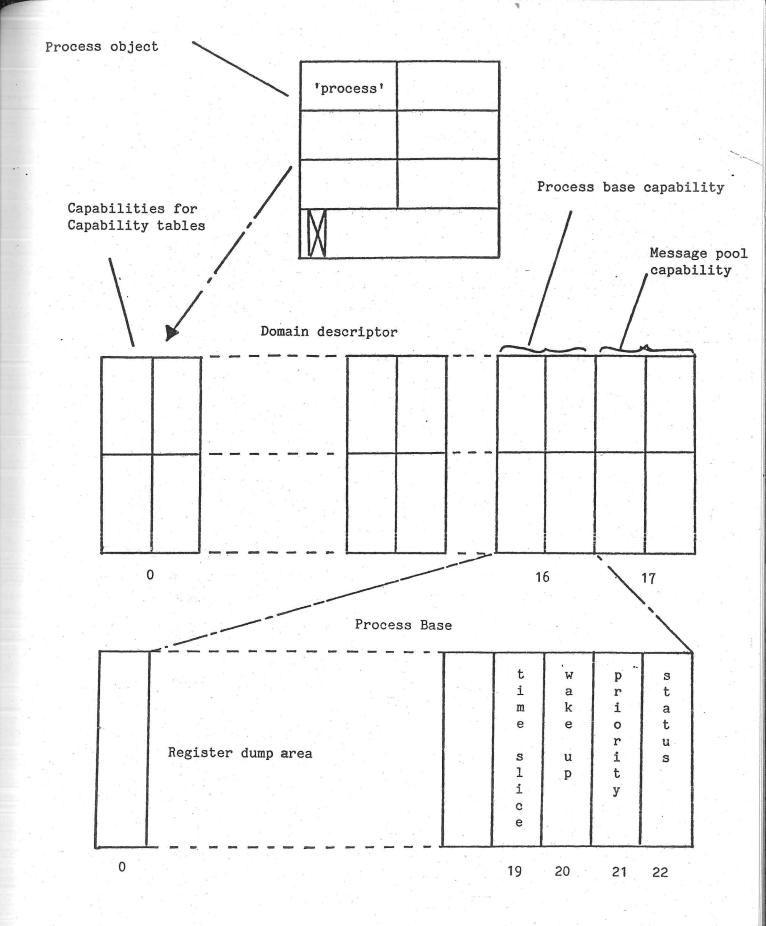

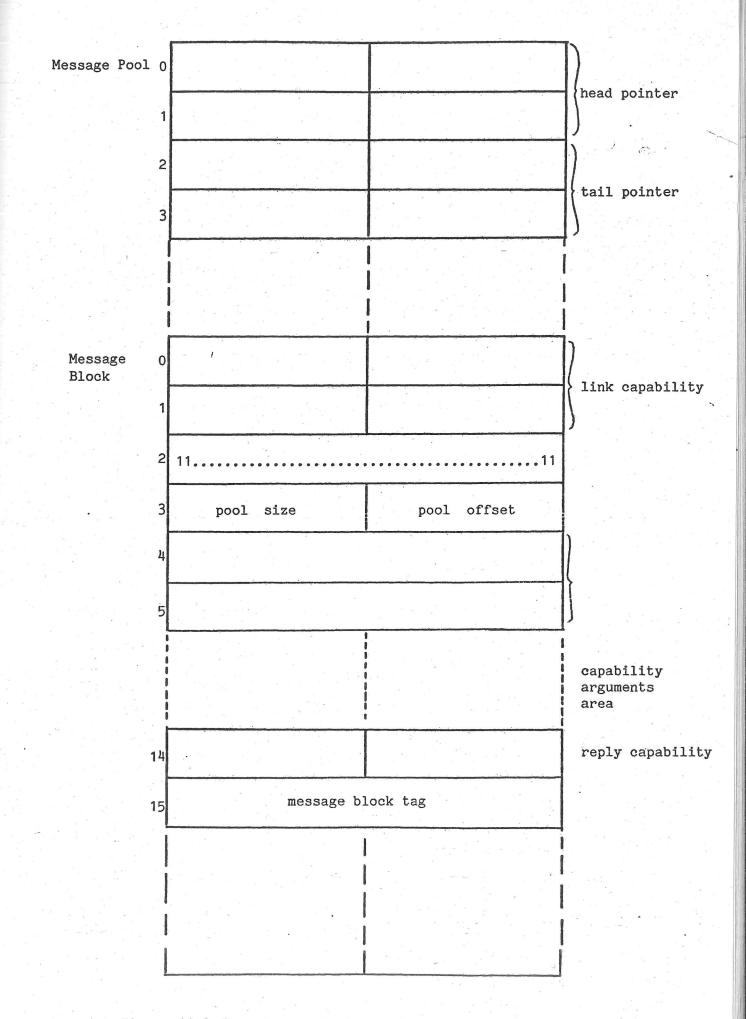

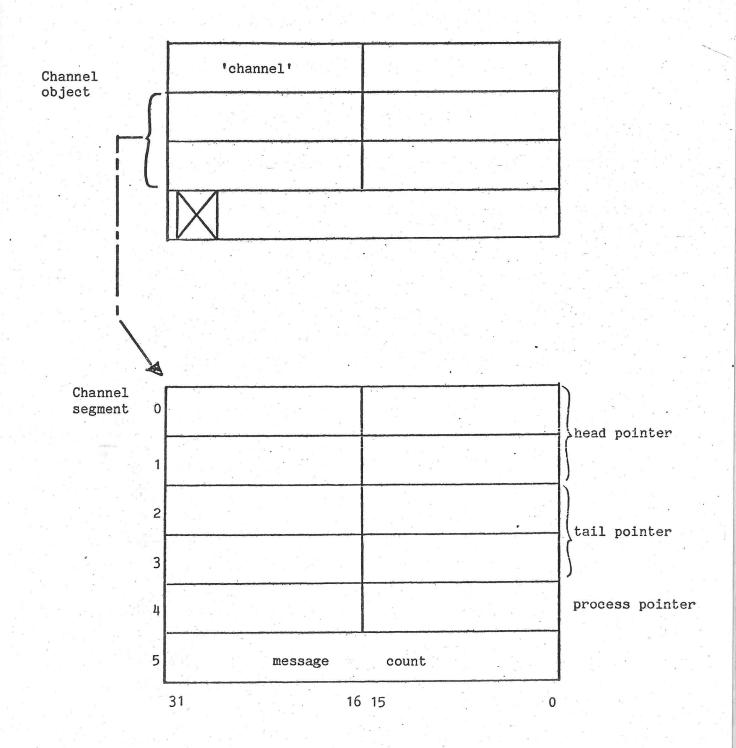

There are many types of object. <u>Processes</u> are the most important from the point of view of protection because a process is the unit of execution and represents the locus of execution of a virtual processor through a <u>procedure</u> or sequence of code. The state of a process is held in a <u>process base</u> or state vector. Processes can synchronise and exchange information with one another by use of an inter-process communication system. At any time a process will have a set of privileges describing the information to which the process is allowed access.

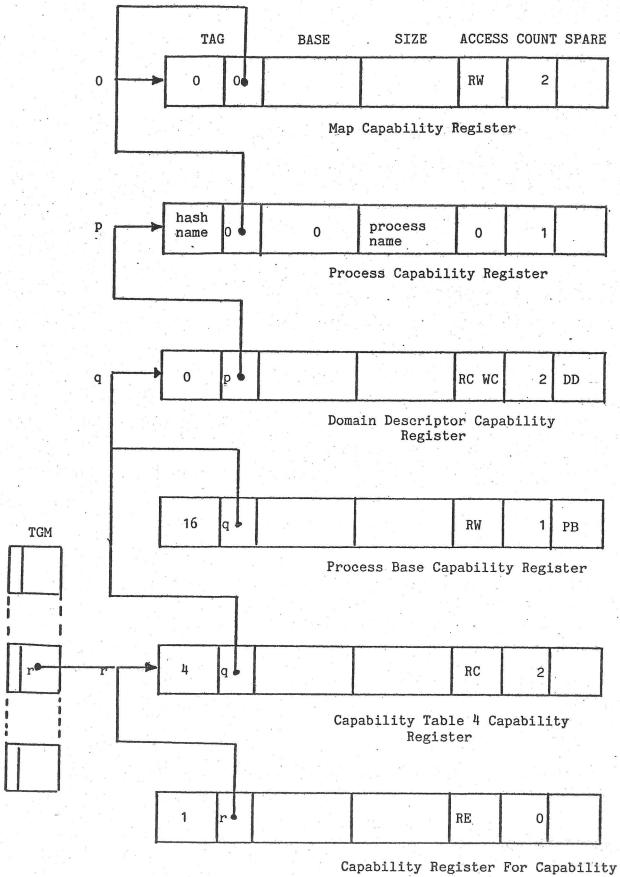

Only capability-based systems are considered in this thesis. A privilege is represented by a <u>capability</u> that specifies both an object and an <u>access code</u> describing the privileges the capability confers. A capability is not an object; it is a ticket of permission that cannot be forged or corrupted. Capabilities are stored in memory marked in some way to distinguish them from ordinary data and it is not possible for arbitrary programs to mark items in memory; otherwise, it would be possible for users to manufacture bogus capabilities. Processes can share access to a common object by having copies of a capability for the object, each containing identical information about the substance of the object, although the access codes might differ if the various processes have unequal rights of access. A process can share its privileges with others by distributing copies of capabilities and if one of these capabilities is subsequently revoked, all copies derived from it must also be revoked.

The set of privileges owned by a process at a given time form a <u>protection domain</u>. The privileges of the process can be altered either by transferring capabilities in or out of the current domain, or by switching to another domain. In capability systems, domains consist of a set of capabilities that form an environment, one component of which is the code associated with the domain. Execution is switched between domains by use of a domain call primitive which has a <u>domain capability</u>, specifying the environment of the called domain, as its argument. After a domain

-8-

call, execution continues with the privileges of the called domain made available and those of the calling domain made inaccessible. Control is always transferred to a predetermined starting address in the procedure of the new domain so that the domain's privileges cannot be misused by jumping into its code at some random point. The process may call other domains for which there are capabilities in the current domain's environment. When execution in the domain has finished, a domain return operation is performed which resumes control in the original calling domain immediately after the point at which it was left, with the privileges of the called domain disabled and those of the caller restored. The domain call mechanism is very similar to the notion of a subroutine in a high level language and the similarity extends to inter-domain communication by a parameter mechanism which permits capabilities to be transmitted between protection domains.

An important property of a domain architecture based on capabilities is that it is non-hierarchical and can be used to model situations of mutual suspicion because the capabilities of different protection domains can be disjoint. This means that the only privileges that can be acquired by a called domain from its caller are those passed as arguments in the domain call. Similarly, a calling domain has no influence on the privileges of the called domain and can only gain capabilities that are returned as results.

So far, domains have been characterised passively as repositories for capabilities and code in which a process can execute. However, it is often useful to consider a domain in a more active sense as the exercisor of the privileges bound into it whenever a process executes within the domain and the term 'domain' will be used for either interpretation provided that any ambiguity can be resolved by the context of its use.

The memory of a domain will be assumed to consist of a number of <u>segments</u> [Dennis 65] each of which consists of contiguous addressable items. To be able to protect small data structures effectively, a protection mechanism must be capable of protecting many small segments only a few words in length as well as larger ones. It is also necessary to be able to generate capabilities

-9-

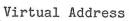

for only some portion of a segment and this can be achieved by holding <u>refinement</u> information in a capability for a segment to select some sub-segment of the total segment referenced by the capability.

#### 1.4. Extensibility

In the design and construction of large software systems there is need for a suitable design methodology to describe the relationships between all of the components of the system so that its complexity can be reduced to manageable proportions. Perhaps the most promising scheme is that of <u>layering</u> in which the system is constructed as a base level or <u>kernel</u> surrounded in an onion skin like manner by a series of extension layers. Each layer enriches its environment by adding to the features provided by the inner layers to produce an enhanced environment for higher layers. The CAL-TSS operating system was designed as a sequence of protected layers and the technique proved successful in aiding the construction of the system [Lampson 76].

The primary rule of the methodology is that knowledge about higher layers must not be built into lower layers. This is so that, in conjunction with the obvious precaution of protecting lower layers against interference from higher layers, there will be a structure in which modifications to, and malfunctions of, higher layers cannot affect the correct functioning of lower layers in the system.

From a top-down point of view the construction of a layered design can be seen as the successive decomposition of a complex system into simpler functions until eventually, in the kernel, they can be directly mapped onto hardware operations. On the other hand, a bottom-up view shows each level of extension as transforming some pre-existing system into a more complete environment by adding useful new features and facilities. This latter view is the most appropriate in the case of extensions written by users to tailor the system to suit their requirements, although to a considerable degree the exact distinction between systems programs and user programs becomes blurred in a layered system.

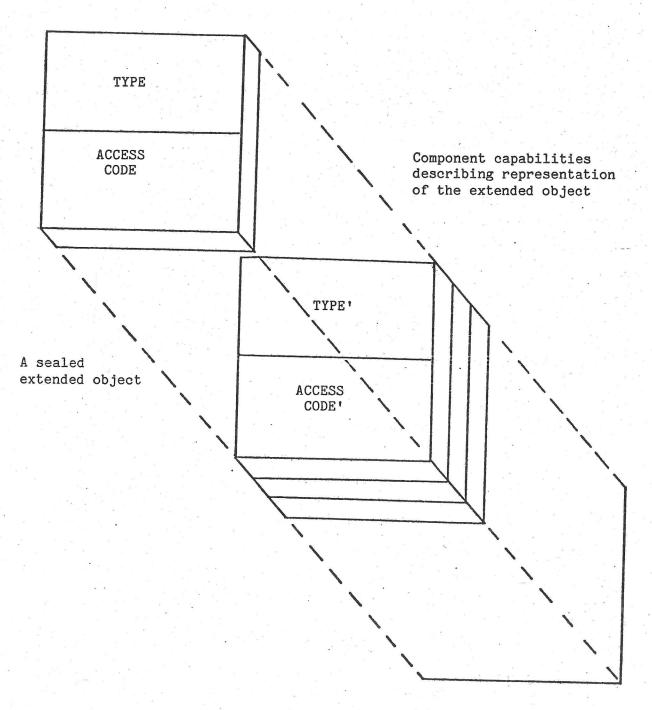

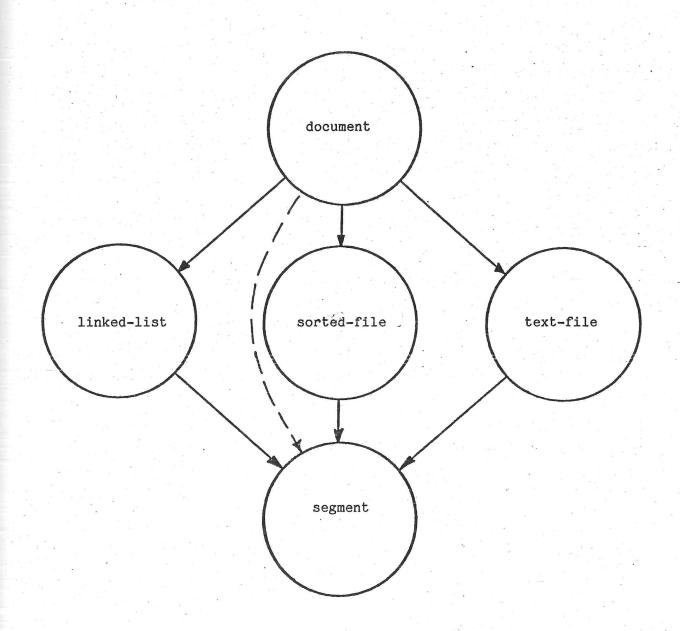

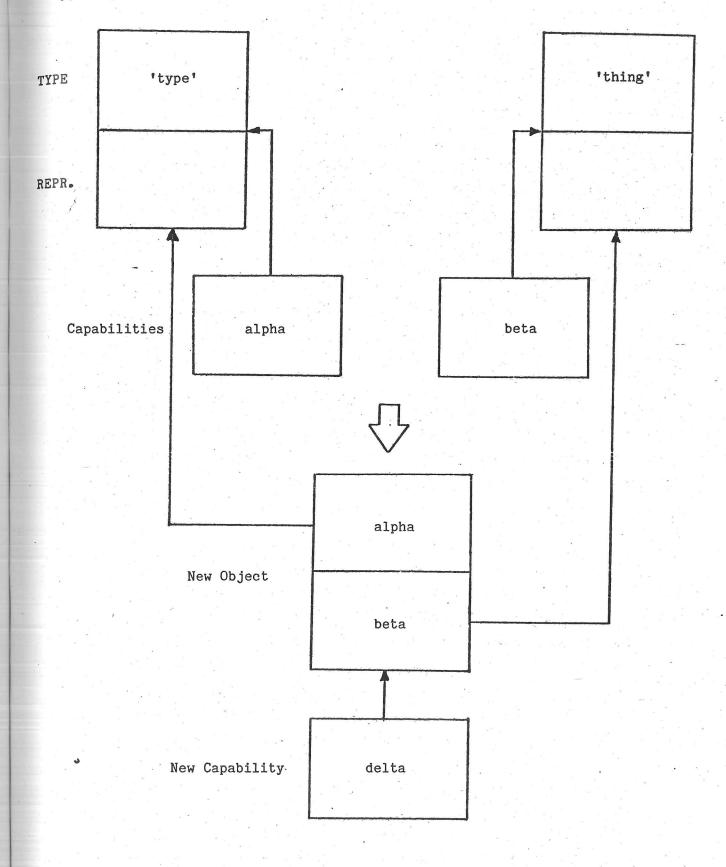

In the object oriented approach, extensions are viewed as defining new types of object and providing the operations that manipulate them. Each layer in the system can be thought of as providing a new abstract machine whose operations are constructed out of the operations of the abstract machines running in inferior layers. The objects provided by extension layers are described as extended objects and they are represented in terms of objects administered by lower layers. In general, representations are concealed from the users of extended objects who see these objects as atomic items. The manipulation of extended objects in terms of modifications to their representations is the duty of software running in the level providing the extension. An obvious constraint is that the layer providing the abstraction of a new extended object must not be able to subvert the layers providing the types of object it uses to implement its own types.

In an operating system kernel, the sort of abstract objects expected are files, directories, I/O streams and so on. The base level protection mechanisms of the kernel must be capable of extension to provide access control and naming functions for these objects in a manner uniform with that used for with hardware resources. The features of a kernel for coping with extended objects are known as <u>type-extension</u> features.

#### 1.5. Scope of the Thesis.

The work described in this thesis follows up work on the CAP project which led to the building of a microprogrammable processor for investigating a powerful and efficient memory protection architecture based on capabilities [Needham 77, Needham and Walker 77]. The CAP project successfully demonstrated the usefulness of capability-based protection in the construction and debugging of an operating system. The protection mechanisms of the CAP machine were all microprogrammed, which greatly contributed to their simplicity and efficiency.

By concentrating purely upon memory protection, the CAP microprogram lacked some of the more advanced features of software kernels such as HYDRA for C.mmp [Wulf et al. 74] and CAL-TSS [Sturgis 73, Lampson and Sturgis 76] in the area of type-extension and revocation of access. The aim of the research leading to this thesis was to investigate the possibility of providing a kernel in microprogram which was comparable with the software kernels, but retained the effectiveness the CAP of memory protection architecture, especially with respect to efficiency. It was also decided to investigate some other addressing and naming strategies in the new kernel both because they aided the introduction of new facilities and also to compare the various mechanisms used in protection systems. The work involved designing a kernel and implementing it in microprogram for the CAP machine as a substitute for the memory protection microcode.

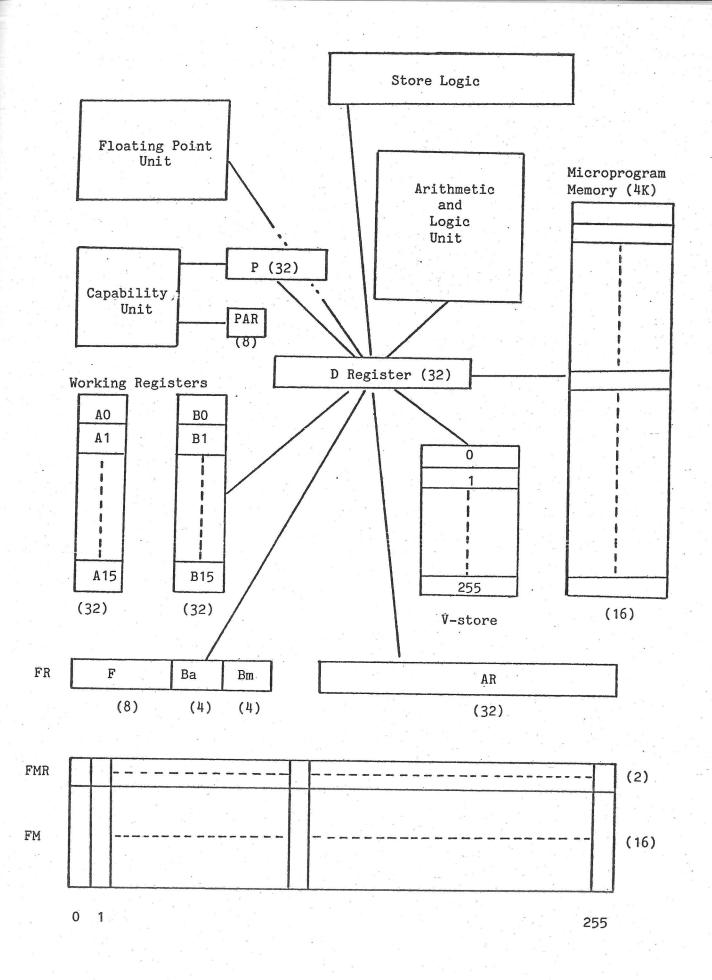

The CAP has a modest amount of microprogram memory (4K of sixteen bit words) which has to hold code for emulating basic instructions and organising I/O in addition to protection mechanisms, so the range of facilities that can be considered is fairly limited, although not too severely. The CAP processor includes hardware for instruction decoding, virtual address translation and carrying out access checks, which helps both to reduce microprogram length and to increase efficiency.

This thesis falls into two parts: the first seven chapters deal with the design of protection kernels and the remaining six chapters describe the implementation of a kernel for the CAP machine, whose design evolved from a consideration of the issues discussed in the first part. This latter part is entirely original work, whereas the first part compares and analyses work by others which is acknowledged appropriately in the text.

Chapter Two is devoted to a description of the design aims and guiding principles involved in kernel design. Chapter Three deals with the ways in which capabilities can be associated with objects, and Chapter Four explores the relationships between capabilities and addressing mechanisms. Chapters Five and Six deal with type-extension and revocation and in Chapter Seven there is a discussion about protection domains and processes.

Part Two starts at Chapter Eight in which there is a detailed description of the CAP hardware which provides the basis for Chapters Nine to Eleven that describe the following aspects of a

-12-

kernel for CAP: basic mechanisms, type-extension and revocation scheme and a process and protection domain architecture. Chapter Twelve gives a detailed description of the internal organisation of the kernel microcode. The final thirteenth chapter reviews and evaluates the kernel and looks towards future research.

#### CHAPTER TWO.

## KERNEL DESIGN PRINCIPLES.

#### 2.1. Protection Mechanism Design.

From their experience with the construction of protection systems, many people have proposed guidelines for the design and construction of successful systems and these are enumerated by Saltzer and Schroeder [75] in their paper on protection. In the following paragraphs these principles will be examined to see how they influence the design of a protection kernel and, in the next section, particular attention will be paid to their implications for a microprogrammed kernel. Many of the design principles may may be described as common sense and they are applicable to all aspects of system design, not just to protection.

It is universally acknowledged that a simple small design is better than one which is large and complex because it is much easier to check the correctness of its implementation (by simple line-by-line inspection of its code, for example) and also because it is likely to be more efficient. If the number of functions carried out by a mechanism is small, it is a simple task to exhaustively test all of its operations to verify their accuracy. An economy of mechanism has benefits for the users of the system too, as the amount of information they have to learn will be small, and this increases the likelihood that they will understand the mechanisms and use them effectively. To the system designer this principle suggests that he ought to consider carefully the primitives he is going to supply and ruthlessly remove any facilities which are redundant or unlikely to be used. An analogy may be drawn from the language Algol68 [Van Wijngaarden et al. 76] whose basic constructs are designed to be 'orthogonal' in the sense that to achieve a particular effect it is obvious which construct is appropriate. It is clear that the benefits of a compact design must be traded against any loss in the number of functions provided by of the system or inefficiency caused by the lack of an important operation.

In a protection system it is important to arrange that the default relationship between programs and information is that of 'no access permitted' until an appropriate privilege has been duly checked. This is true of capability systems because every access to an object must be accompanied by a capability that is inspected before the access can proceed. The explicitness of privilege in this sort of arrangement makes it easy to find out which objects a program can access by looking at its stock of capabilities. Furthermore, if the default state is to refuse access, any error in a program has less chance of causing harm by spoiling information to which it has no right of access.

In Chapter One it was noted that the degree of privilege possessed by a program will change with time and it is therefore not sufficient to perform access checks statically or just once only on the first access to an object, because subsequently the execution of a program running in parallel may cause an access code to be modified by revocation of a capability. This implies that there must be complete mediation, which is to say that every access to an object must be verified independently of whether or not the access has succeeded in the past. This imposes a system-wide view of protection independent of considerations of the structure and constitution of objects and provides the motivation for designing protection mechanisms as a low level component of a system. However, the implementor of a kernel does not have the full benefit of protection machinery and has to rely on weak hardware support for protection. For this reason, a kernel should contain as little as possible in the way of facilities beyond basic protection primitives so that as much of the system as possible is built upon the protection mechanism as its foundation to obtain a greater level of ruggedness. By contrast, in software kernels like HYDRA and CAL-TSS it is common to find that the kernel is a substantial operating system in its own right and makes little use of its own protection services. The designer of a kernel should aim to implement the basics of his protection machinery as a simple, small core which is then used by every other component of the kernel to access objects so that the kernel does not have private (and therefore suspect) protection.

- 15 -

naming and addressing schemes. Access control must persist at all stages in the life of a system from initialisation through normal running to shutdown. For example, it should not be possible for a user to tamper with the information that is to be loaded at the next system start up while the system is running, otherwise he could modify the system to pass him privileges illegally the next time it is reloaded.

A protection system that relies on the concealment of a secret or password to ensure the non-subvertibility of its mechanisms should be treated with suspicion because the security of the system will not be assessable in absolute terms. Passwords belong to the external realms of authorisation of access and it is only possible for a protection mechanism to prevent unacceptable access to secrets; it is not safe to assume that secrets can neither be guessed nor deduced from the observation of external events. Reliance should not be placed on the concealment of system code as a protection mechanism either, because if the protection system is free of secret algorithms, it can be reviewed independently by sceptical users without fear of abuse. This builds up the trust held in the system by its users and if the protection mechanism is audited independently by several people, the probability of outstanding errors remaining within it is decreased.

The ruggedness of a protection mechanism is greatly increased if it requires the presence of two 'keys' to open a 'lock' because no single mishap can lead to a breach of security. The major example of the separation of privilege in protection schemes is that of type managers which are programs responsible for looking after all objects or resources of a particular type. A type manager usually has privileges relating to the class of objects as a whole, such as being able to create objects in the class or to alter their representation, whereas the privileges to use particular members of the class are distributed amongst the users of the system. The only time at which a particular object can be modified is when two keys in the form of a privilege for a particular object and a privilege for the class of objects to which it belongs are brought together when the user responsible for the object passes a privilege for it to the type manager.

Possibly the most important design principle is that of minimum privilege, or as it is known in security conscious evironments, "the need to know", which is to say that a program should only have access to the information strictly necessary to carry out its function. In a capability system, this means that a protection domain should contain just those capabilities essential to completing its task and that a complex series of operations should be divided out amongst a set of domains, each element of which performs a simple, well-defined job and has exactly the privileges required to carry it out. Putting firewalls into a system in this way limits the propagation of damage after an error because only the few objects accessible to the erring domain can be harmed. It is also easier to locate errors because any failure can be directly accounted to the domains that have access to the information damaged by the error. A common practice is to associate a protection domain with each distinct data structure or abstraction so that a domain is rather like a module of the sort proposed by Parnas [72]. This organisation has the advantage that all of the operations for an abstraction are located in one place and it is easy to get interlocks right and to ensure the consistency of internal tables. However, for each particular service provided by the module, its domain is over-privileged because it carries around privileges for all of the services of the module. To some extent, this over-privilege can be overcome by use of the separation of privilege described earlier or by the use of templates, as found in HYDRA [Jones 73], that modify the privileges of a domain according to the access codes of capability arguments presented to it. A major consequence of minimum privilege for the designer of a protection mechanism is that it must be capable of efficiently supporting the interaction of many small, independent domains and this demands that the cost of a domain call operation be small.

Small protection domains tend to contain very simple data structures and in consequence it must be possible to protect very simple objects and segments just a few words in length. The notion of the 'grain' of a system is used to indicate to what degree it is reasonable to distinguish between items of data and

- 17-

protect them individually. In general terms compared to most software kernels, the CAP memory protection system has a very fine grain of protection and this greatly contributes towards the ruggedness of the operating system built upon it [Needham 77].

Jones [73] proposes a yardstick known as a <u>suitability factor</u>, which indicates how closely a protection mechanism will allow the principle of minimum privilege to be attained. For every domain in the system, Jones defines an <u>accuracy measure</u> which is the ratio of the number of privileges exercised by a domain to the total number of privileges it owns. Clearly in the state of minimum privilege, this ratio will be one and will fall away to zero as the degree of over-privilege rises. The suitability factor of the entire system is defined as the average accuracy measure across the system and Jones shows that for a capability system with a non-hierarchical domain structure, it is possible to approach very close to the ideal value. This has also been demonstrated in an analysis of the CAP system [Cook 78].

Most conventional computer systems have very weak protection mechanisms and in consequence, users have little experience of taking full advantage of a well-protected system. So, for this reason, it is essential that protection mechanisms should be that it is easier for users to remember straightforward so protection techniques and how to employ them. To a great extent, this principle can be met by keeping to a simple, compact design in which all of the basic primitives are distinct and easy to The psychological acceptability of a protection understand. system depends upon users being readily able to employ the functions of protection machinery to suit their particular requirements.

A cornerstone of the HYDRA project has been the separation of policy from mechanism [Levin et al 75]. For example, a process scheduler in an operating system may be driven by interrupts alone or may allocate fixed duration time-slices, and there are many different ways of organising priority queues in response to different modes of operation. Ideally, these policy matters should be parameterised so that common kernel primitives can serve all possibilities. This is an important design principle because,

-18-

in the lifetime of a system, it is likely to be put to a variety of uses that may not have been apparent at the time that the kernel was designed and it is clearly undesirable to have to modify the kernel for every new application of the system. Separating policy from mechanism also holds advantages if it is required that the system should be able to provide two different services simultaneously, such as a transaction-based information retrieval system and a general purpose time-sharing system, because the same mechanism can be used for both services which may have different sets of policy parameters.

#### 2.2. Microprogrammed Kernel Design.

It has been a long standing principle throughout the life of the CAP project that the set of facilities provided by the microprogram should be a self-contained whole that does not rely on the integrity of the software built upon it, rather than a microprogrammed extension of systems software. This is so that the verification of the basic protection machinery can be accomplished simply by inspecting the microcode free of any considerations relating to other software. It is likely that there will be awkward and complex interfaces between microprogram and software if the kernel is split between them because of the difficulty of keeping state information in step between the two levels. On those occasions when the microprogram is unable to cope, for example on a virtual memory fault, the only acceptable means of communication to the software is by raising an interrupt and the microprogram must not make any assumptions about whether or not the software will handle the condition correctly. Whenever the software wishes to negotiate with the microprogram, it must present its arguments in a form which the microprogram can check against appropriate capabilities before going ahead. Thus for example it would be inadmissible for the microprogram to accept an absolute address or to manipulate an object in the absence of a suitable capability.

The need for simplicity in a microprogrammed kernel is much greater than in a software kernel because of the lack of space for long sequences of code and the untidy nature of microinstructions and their side-effects. A lot can be gained by sharing as much common code as possible in the kernel between its primitives, for example, to evaluate capabilities, modify representations of objects and carry out access checks. The advantage of this is that it is only necessary to verify the correctness of a particular function once and also there is a saving of program code. Naturally, this must be balanced against the overheads of microprogram subroutine calls and any inefficiencies introduced by calling routines that handle general cases rather than using possibly shorter code to handle particular simple cases. This can often be circumvented by careful design of kernel subroutine entry points and parameters.

To avoid confusion in software or accidentally permitting breaches of security, the microprogram must check all of the arguments of a kernel operation before it goes on to modify any data structures so that a protection violation cannot occur during the execution of the primitive and leave things in an inconsistent state. This means that kernel functions must be restartable and on a restart all arguments must be checked from scratch, because an excursion into software caused by an interrupt is liable to result in the modification of the state of the machine.

Complete mediation is possible by ensuring that the microprogram always uses virtual addresses to access data structures through the addressing and protection mechanism and not by remembering evaluated absolute addresses, so that an error in the microprogram or a bad argument causing the kernel to make an illegal access will be duly trapped and reported as an access violation. This increases the ruggedness of the kernel and greatly aids debugging at the cost of an increased overhead in accessing information owing to the protection checks. If the some device for optimising efficiency microprogram has by retaining evaluated capabilities and representations of objects, it must detect when such an optimisation is no longer valid, perhaps because a capability has been overwritten in store. It is in the area of these optimisations that there are most likely to be mistakes that will allow unauthorised access to privileges.

#### CHAPTER THREE.

## CAPABILITIES AND NAMING.

## 3.1. Names and Objects.

In Section 1.3 the essential contents of a capability were said to consist of an access code describing the privileges conferred by the capability and information to identify uniquely the object which the capability protects. In an early capability scheme due to Fabry [68], the information simply consisted of the representation of the object; for example, a segment capability contained the absolute base of the segment and its size. This is rather unsatisfactory because information about the structure of objects is not centralised and leads to difficulties if the representation of an object needs to be modified. A typical example occurs in virtual memory management: a segment can be relocated in store by altering its absolute base address and it is essential that all capabilities for the segment refer to its new position. To do so in Fabry's design involves searching through all of the capabilities in the system to locate those to modify. This tedious task is easily avoided by holding the representation data in some central tables and retaining a pointer into the tables within a capability. This pointer is known as the <u>name</u> of the object.

If the naming mechanism only accepts names that are embedded in capabilities, names can be kept free from forgery or corruption. The name of an object serves to identify it uniquely from all other objects known to the system. As names are found in capabilities, the issues of naming and protection are very closely related; in particular, naming mechanisms have a considerable influence upon the nature of the protection system that can be built around them.

Naming schemes may be divided into two categories: <u>nested</u> and <u>global</u> [Lauer 74]. In a nested naming scheme the name of an object is only meaningful within one node of a hierarchical tree of name spaces. In each name space there is a table giving

-21-

information about all the objects which exist within it and an object is defined in terms of selecting objects in an immediately superior name space in the tree, apart from at the top level where representational information is found. Thus, the entries in a particular table will contain names belonging to its higher name space. The bit pattern of a name has a different significance in every name space and it is necessary to translate names if they are passed between name spaces.

A global naming system is characterised by having a central table of object representations and names which are pointers into the table and have the same significance everywhere. It is usually the case that each object has a name different for all time from every other name, known as its <u>unique identifier</u>. Uniqueness implies that there is a single entry in the table for every object and that modifying this entry will affect all capabilities for the object throughout the system.

#### 3.2. Nested Naming Schemes.

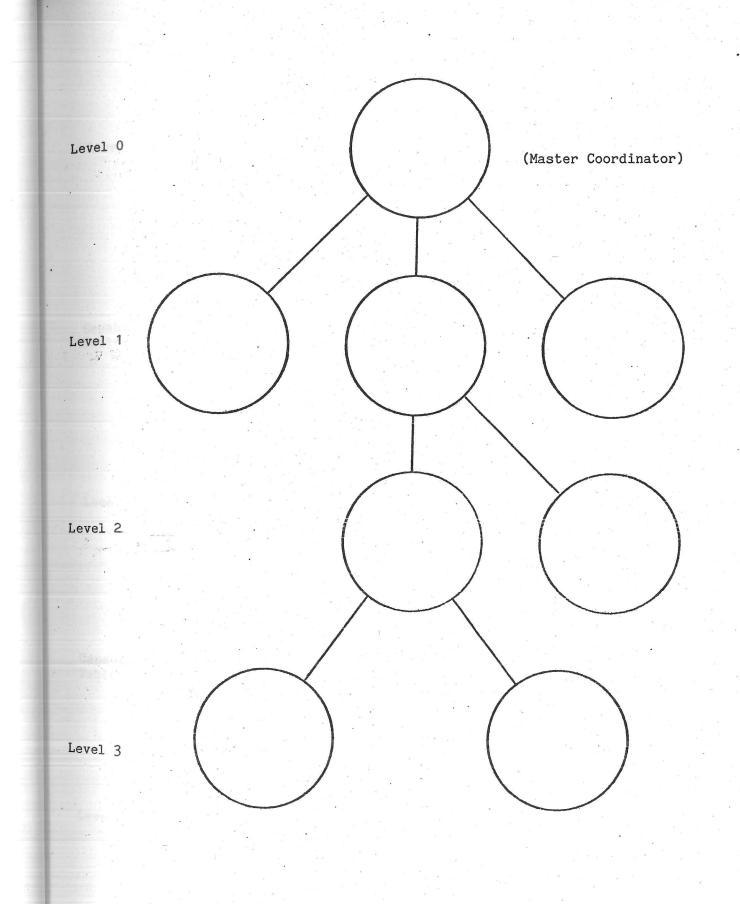

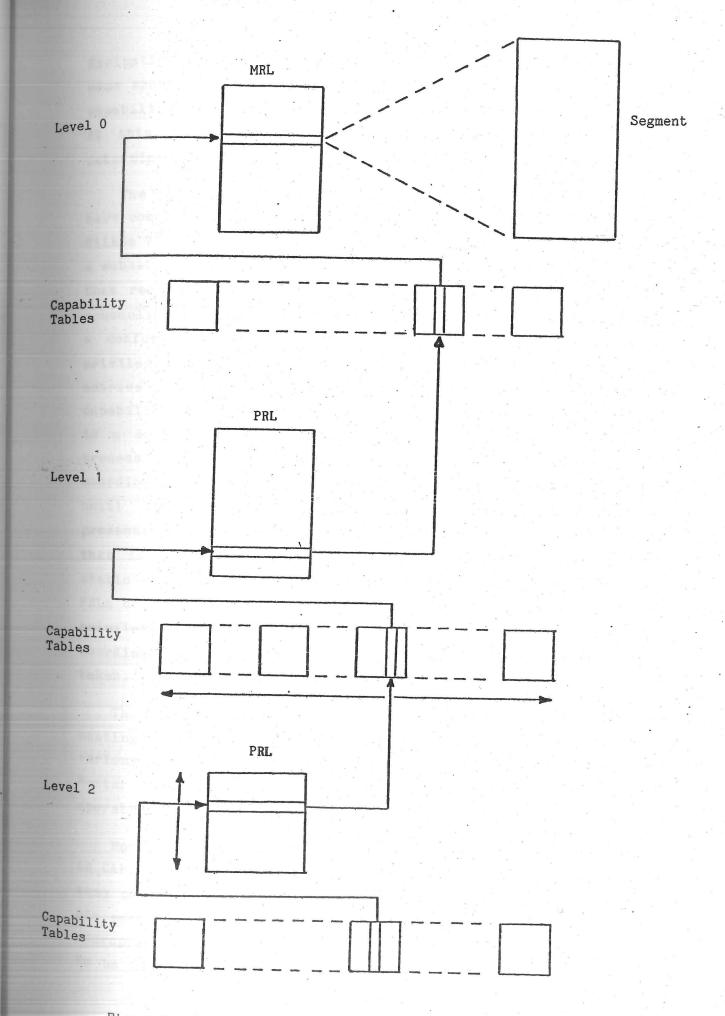

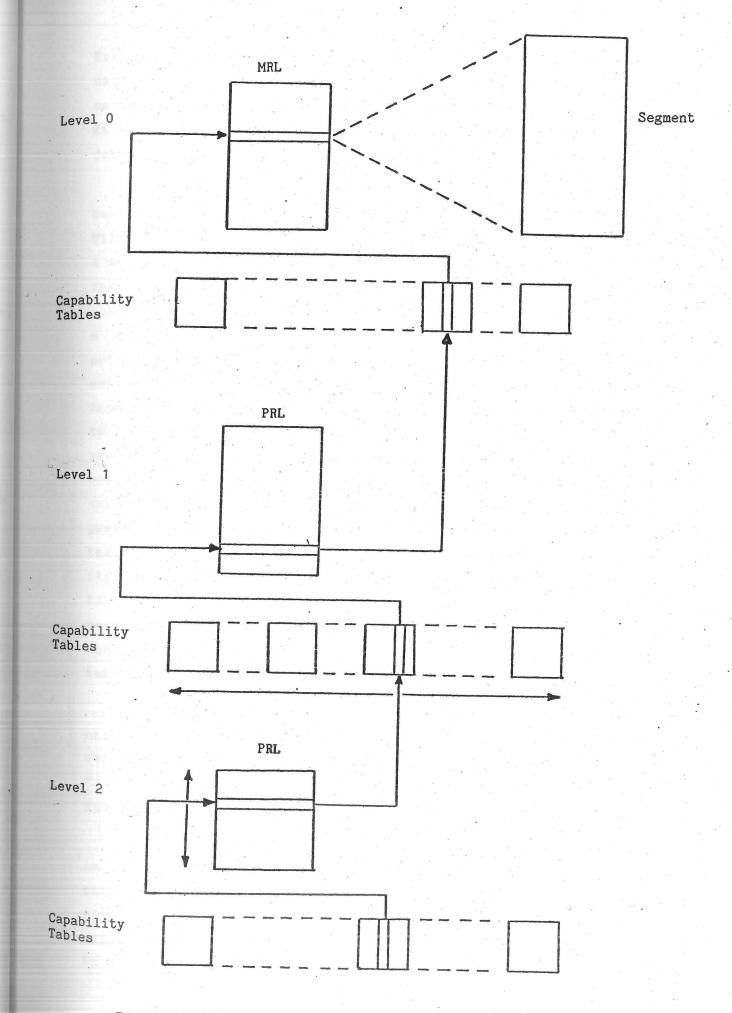

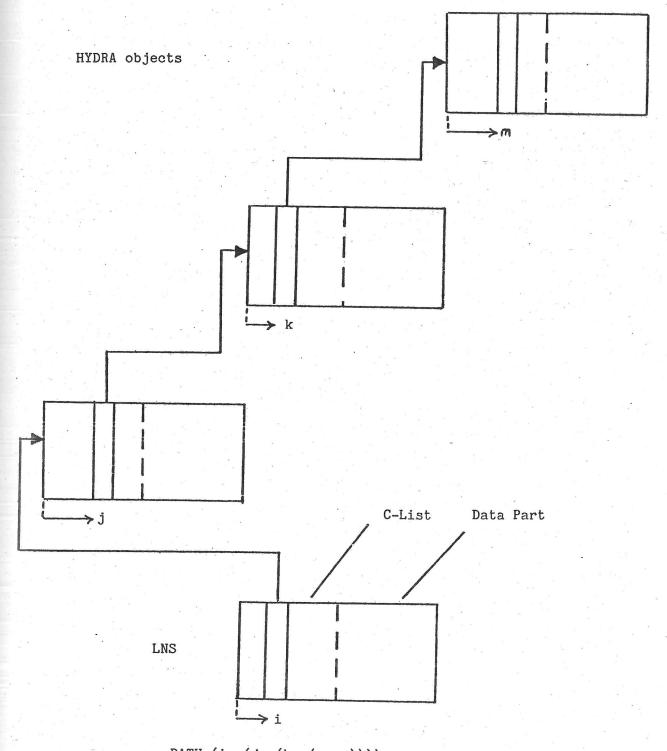

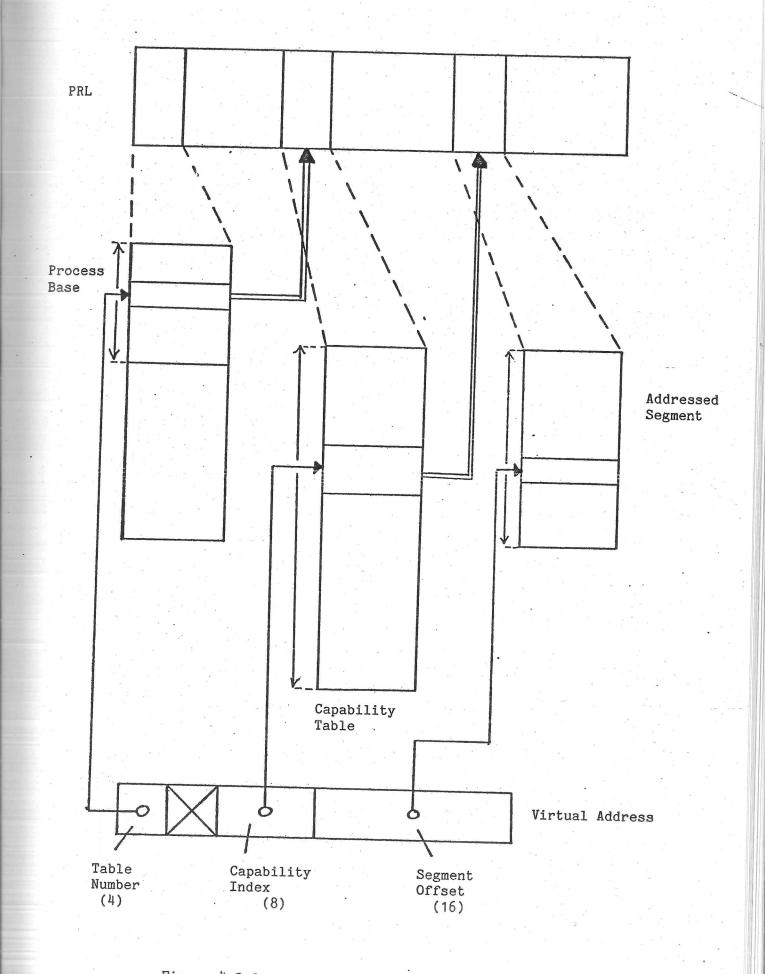

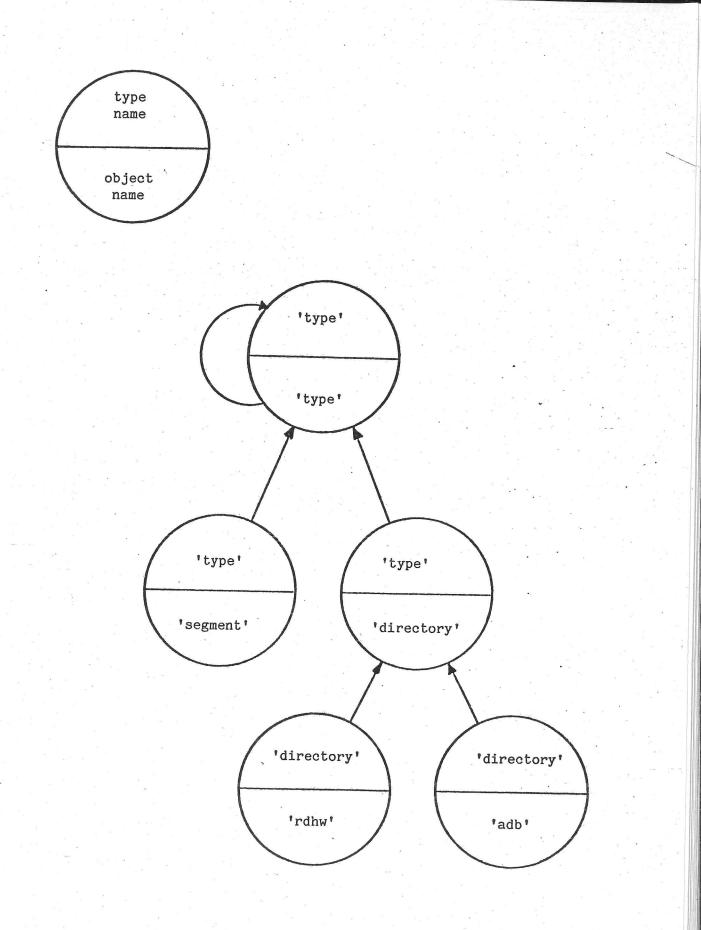

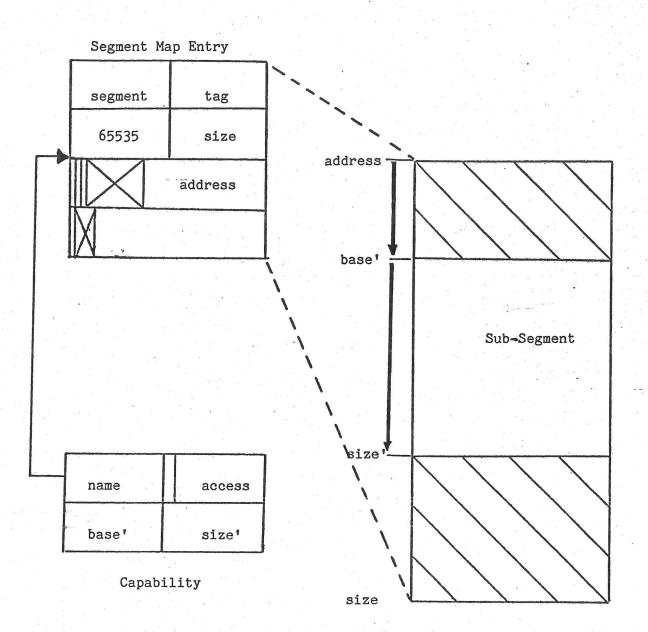

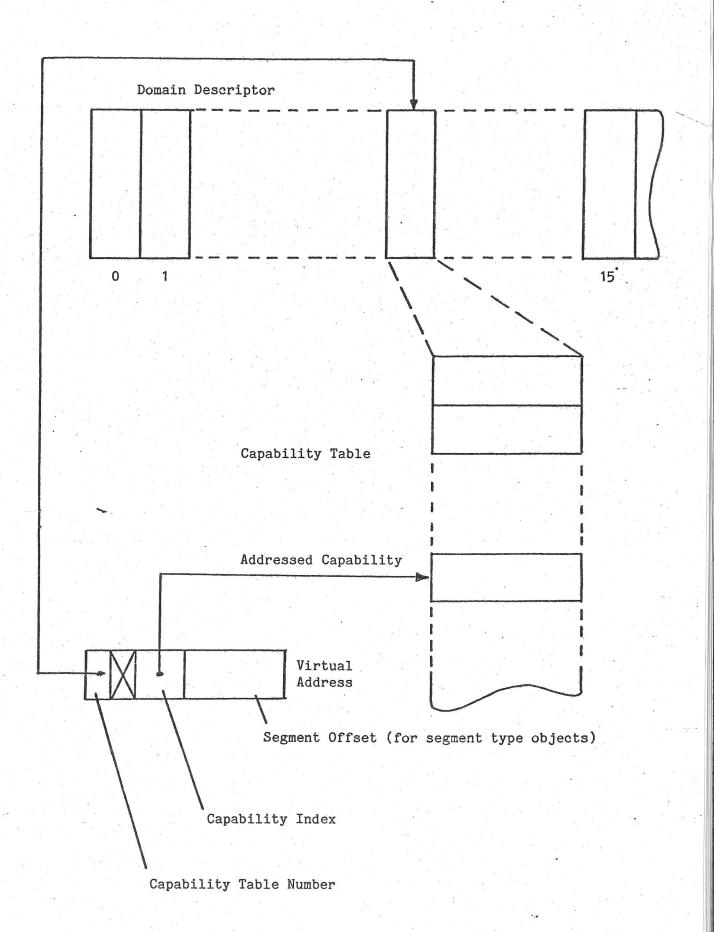

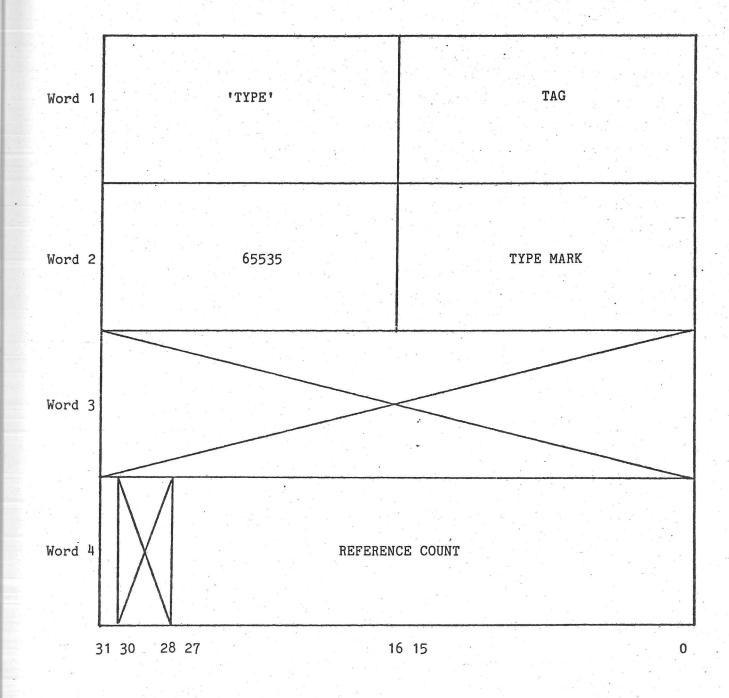

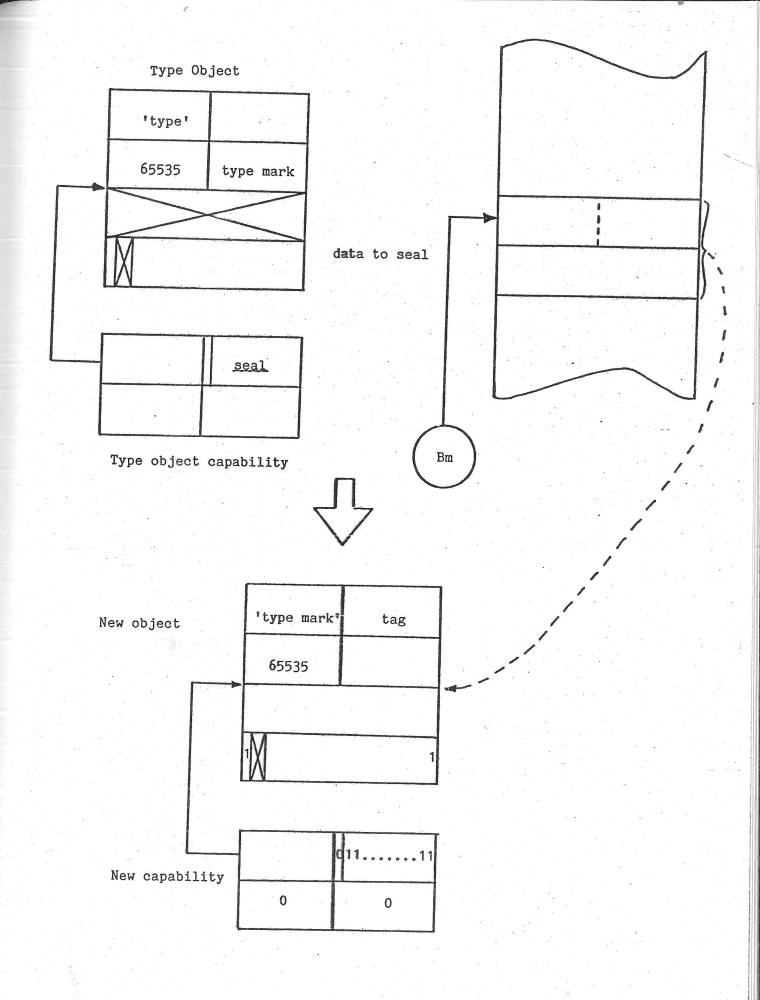

The major example of a protection architecture based on a nested naming scheme is the CAP system [Needham and Walker 77]. The system supports a hierarchical tree of processes and each node of the process tree acts as a coordinator to the processes immediately descending from it. These processes in turn are responsible for coordinating their sub-processes and so on. A typical process hierarchy is illustrated in Figure 3.2-1. There is a name space associated with each process and capabilities within a process contain short (sixteen bit) names that point into a table of objects available to the process, known as the Process Resource List (PRL) which contains information about the representation of the process's objects. For segments, the PRL at the top level, known as the Master Resource List (MRL), holds absolute base addresses and sizes. A segment entry in a PRL lower down the process hierarchy contains the address of a capability for the segment in the immediately superior address space. These data structures are illustrated in Figure 3.2-2. There is a mechanism by which segment capabilities can contain refinement data so that a junior process can have access to sub-segments of segments at higher levels with the same or reduced access.

-22-

# Figure 3.2-1 CAP Hierarchical Process Structure

# Figure 3.2-2 CAP Capability Evaluation

Figure 3.2-2 CAP Capability Evaluation

2 . S. 18

Evaluating a capability involves ascending through a hierarchy of name spaces, following indirections from capabilities to PRLs, to capabilities in higher name spaces until an MSL entry is reached. At this point, the position of the segment in memory can be determined and data within it may be accessed.

The rationale of the CAP scheme is that a coordinator should have complete control over the processes it schedules [Needham and Wilkes 74] and for this reason the privileges of a sub-process are a subset of those of its coordinator. In fact the only privileges that really belong to a coordinator are those that relate to the scheduling of processes. As it stands the CAP system suffers from a confusion between the control of time and the control of privilege which may be directly attributed to the fact that PRL entries define the representation of objects by addressing capabilities at the next level, rather than by pointing directly to a superior PRL. The reason for the capabilities of a CAP process leading to capabilities in the address space of its coordinator process is because CAP processes have no existence until they are actually running. A process is started by presenting to the microprogram a data segment of the coordinator that is to become the PRL of the new process and there is no static way of deciding which segments in the machine are potential PRLs or not. This means that the only possible place at which the privileges of a process can be gathered together is within the coordinator process from which the apparatus of the new process is taken.

The CAP architecture will support an indefinite depth of nesting, subject to hardware constraints, although in practice, various considerations lead to the adoption of just a single Master Coordinator and one level of sub-processes in the CAP operating system.

Moving capabilities around within a process is straightforward in CAP: all of the protection domains in a process belong to the same process-wide name space so it is sufficient just to copy the bit pattern of a capability whenever it is moved and CAP provides microprogrammed instructions for this purpose. If a capability is to be transmitted between processes having a common coordinator,

-23-

the transfer involves establishing a PRL entry in the receiving process identical to the PRL entry in the sending process and then copying the source capability to its destination slot with the name field translated to point at the new PRL entry in the receiver. Moving capabilities between processes that do not share a common coordinator is more involved: firstly a node in the process tree that embraces the name spaces of the communicating processes must be located; then the capability to send must be evaluated as far as this common node and finally, the capability must be allocated space in all of the intervening name spaces in the tree down to the receiver. There is no microprogram support provided for these operations so they must performed by be software. The complication of inter-process communication between different levels of the hierarchy has lead the CAP operating system to only permit messages containing capabilities to be despatched between sub-processes of the Master Coordinator. As message passing is implemented by software and involves the translation of names between name spaces it is considerably slower than the microprogrammed orders that may be used to communicate between domains within a process [Cook 78].

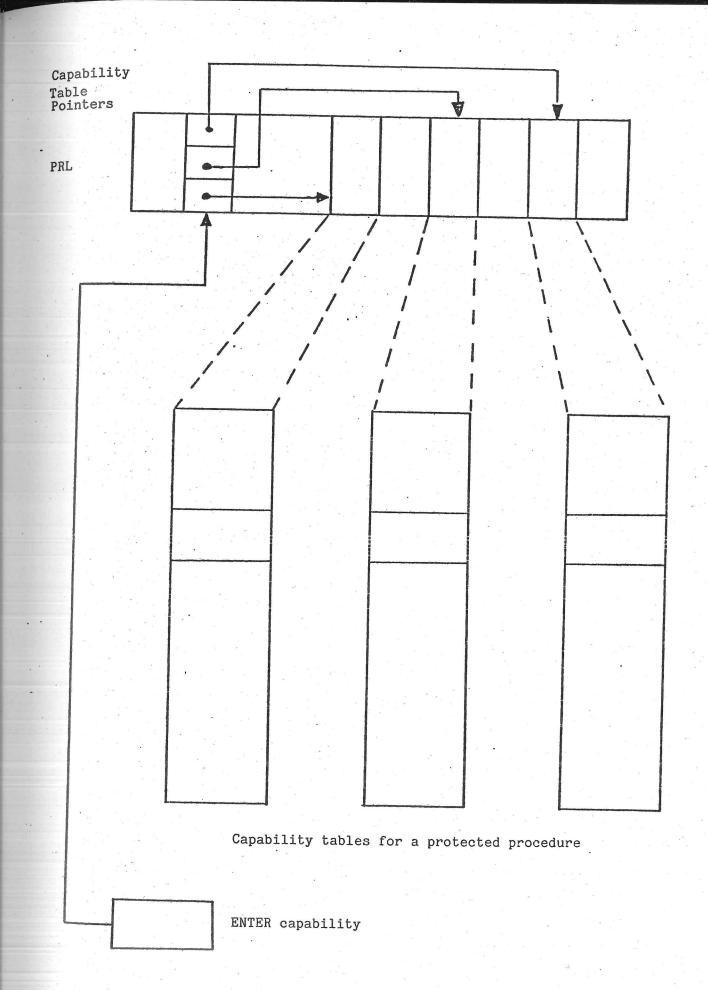

The CAP inter-process message system will only perform the transfer of segment capabilities with the result that it is not possible to send capabilities for objects containing names, such as protection domains. A CAP protection domain is known as a protected procedure and it is defined by an ENTER capability (named after the ENTER instruction which is used to change protection domains) that points to a PRL entry that in turn points at up to three other PRL entries for capability tables holding the capabilities that form the protected procedure. Figure 3.2-3. shows the structure of a ENTER capability. To transfer an ENTER capability between processes it would be necessary to make new copies of these tables so that all of the capabilities within them can be edited to index the correct offsets in the destination PRL when the procedure is transferred and space has to be allocated in this PRL for all of the segments accessible from the procedure. If the protected procedure included capabilities for other protected procedures, these too would have to be unravelled. Even if it were possible to pass protected procedures between

-24-

Figure 3.2-3 A CAP ENTER Capability

processes, there are other problems concerned with parallel execution in a single protection domain which will be discussed further in Chapter Seven.

In conclusion, the advantages of a nested naming scheme mainly arise from the efficiency of name look-up by simple indirection and compactness of short names, together with the simplicity of the object tables found in each name space. In return, there are problems concerned with passing names between name spaces and managing objects whose representations are distributed around the system in the several name space tables.

## 3.3. Global Naming Schemes With Forever-Unique Names.

All of the naming problems mentioned above may be avoided by the use of global names which are independent of domain and process architectures, so there is no difficulty in passing a capability around by copying its bit pattern. The HYDRA system [Wulf et al. 74] uses global naming and ensures that names are unique in space and time by deriving them from a fast clock that will never stop during the entire lifetime of the system. Every object ever known by HYDRA is given a unique name which remains associated with the object, even after it has been deleted. To cope with the number of objects that will exist during the system's life, unique identifiers are long (sixty-four bits), as opposed to the smaller sixteen bit name field of CAP capabilities. As well as being vast, the HYDRA name space is also sparse because of gaps owing to objects that have been deleted, and the intervals in which the clock runs but no new names are generated. For this reason, associating names with entries in the central table must be done by hashing. The entire hash table is too massive to retain in primary memory and it is paged from a fixed head disc. A small hash table in memory, the Active Global Symbol Table holds map entries describing objects that have been used recently and a low priority process slowly scans the table and arranges that it only contains information corresponding to objects that are in current use. If an entry for an object is not found in the active table, an entry must be found for it from the Passive Global Symbol Table on disc. The process of hashing in the active table is quite slow even compared to the time taken to traverse the

-25-

naming hierarchy in the CAP system and if an object is not in the active table, the time taken to find it is considerably longer because of real-time delays while the disc is accessed. Thus, although the mechanisms of HYDRA are conceptually simpler than those of CAP they are much more expensive in terms of time and computation.

A major advantage of a unique identifier scheme is that it is possible to preserve capabilities directly in a filing system. In a nested scheme this is not possible as a capability may be subsequently retrieved in a name space different from that in which the name it contains is valid. In the CAP system, filed objects are given a unique System Internal Name and when a capability is filed, its name field is translated from a local name to a System Internal Name [Needham and Birrell 77]. For this reason capability segments are not filed, as to do so would require the translation of all of the names in the capabilities within the segment. CAP capabilities are preserved in filing system directories and it is the responsibility of the directory manager program to perform translations between local and System Internal Names. With HYDRA this is not necessary, as the unique identifier in a capability is always valid and has the same meaning throughout the system at all times. However, the integrity of the unique naming scheme depends upon the object table being kept scrupulously up-to-date and consistent; it must be retained without corruption over a system break and the table management software must guarantee that the table is never left in an ill-defined state. The same remarks apply to the internal name table in CAP, but that table only has to be updated whenever a capability is preserved in the filing system and the overhead of keeping this table up-to-date on disc is less severe than in HYDRA, where the table is modified more frequently in response to operations on all objects and not just those in the filing system.

The advantages that a global naming system has over a nested naming scheme for transferring capabilities between domains and processes is a strong influence on the level of type-extension features found in a protection system. In most type-extension schemes, abstract objects are represented by a data structure that

-26-

contains information about the lower level components of the object which is frequently in the form of capabilities. In a nested naming system the problems faced in moving these structures around are similar to those provoked by trying to pass ENTER capabilities in CAP. If a type-extension mechanism is to be useful, it must be possible to protect a large number of objects of varying levels of complexity which can be transmitted easily between protection domains and processes. For these reasons, those protection architectures that wish to support abstract objects are normally based on global naming schemes, so that capabilities and names may be passed around in a free and flexible manner. Furthermore, if a filing system is to allow protected objects to be preserved, the expense of translating run-time names to filing system names within the representation of objects may prove too great and unique identifiers are most commonly used as global names to avoid this overhead.

## 3.4. Other Global Naming Mechanisms.

It is possible to have global naming schemes that do not rely on forever-unique identifiers. A system considered by Watson [78] uses global names that are only unique for a run of the system, that is, whenever the operating system or machine is stopped and subsequently restarted, identifiers are issued afresh from their This approach relies on the observation that origin. most computer systems are halted at frequent intervals for routine maintenance, lack of work or because of hardware malfunction. Usually these events are separated by days or weeks rather than years, so the identifiers in Watson's scheme need not be as long as those in a forever-unique scheme, with the advantage that capabilities are smaller and less work is required to hash names. Hashing is still the only method applicable for organising the global object table because, even in a few days, its size would become immense if measures were not taken to keep it compact.

In this scheme it is not possible to place capabilities in a filing system without translating names into some internal unique form because preserved names will become invalid whenever the system restarts. On the other hand, it is no longer necessary to go to great lengths to keep the table intact over a system break

since the names it contains are volatile. As the table will no longer require backing up on disc, it can be looked after by microprogram because most table operations like identifier look-up will not need the advanced facilities (such as paging from disc) used by the HYDRA global symbol table machinery. Some software might still be required to locate and remove garbage from the table and perform other high level operations, but otherwise it would not be unreasonable to expect the microprogram to provide primitives for evaluating capabilities, distributing them, simple type-extension (including object creation and deletion) and so on. Unique identifier look up by hashing, however, can lead to a waste of machine cycles when collisions occur in the hash table and a search must be continued. In particular, looking for an entry for an object that has been deleted may occupy the kernel for a long time, causing a degradation of efficiency.

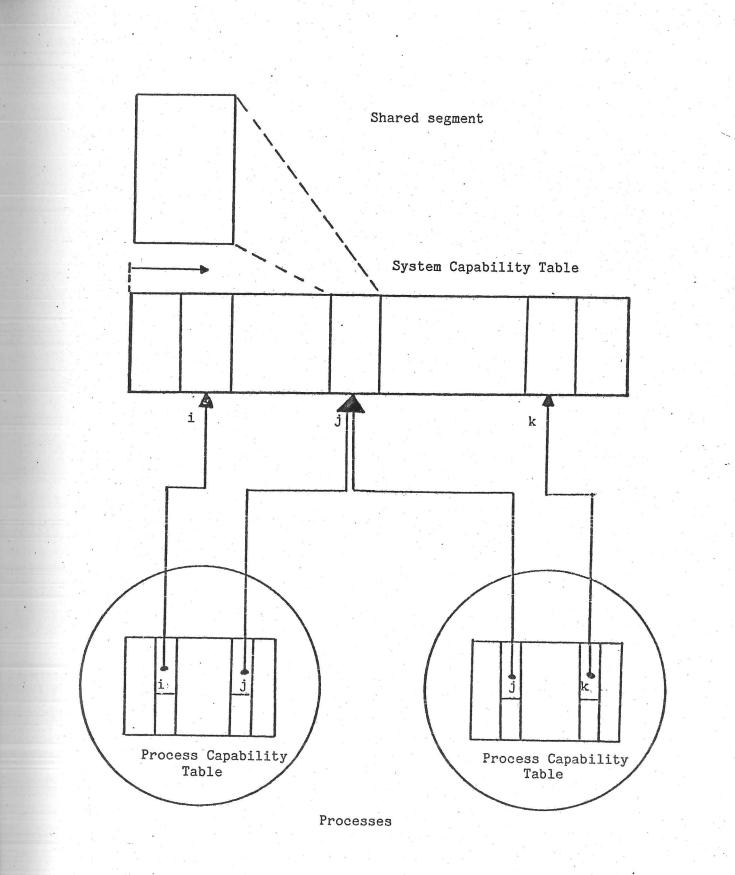

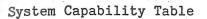

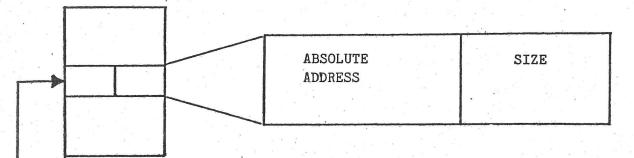

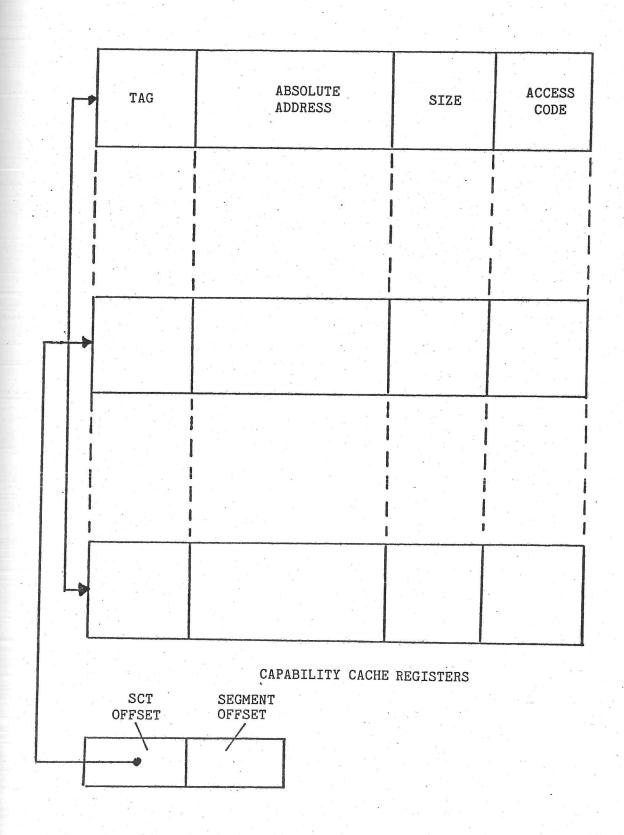

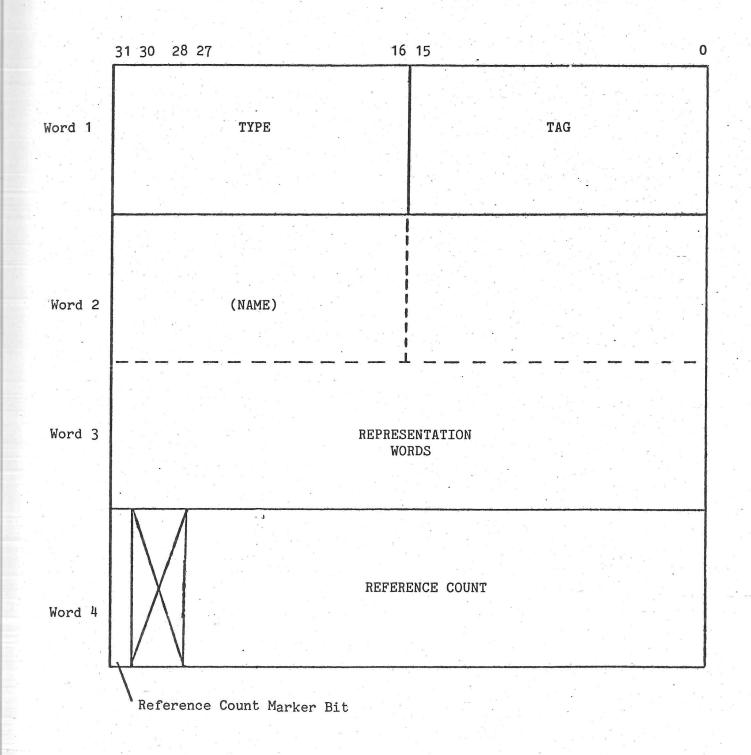

The Plessey System 250 [England 74] circumvents the cost of hashing short term names by arranging that names in capabilities directly index a global name table which is called the System Capability Table (SCT) as shown in Figure 3.4-1. The Plessey system only provides memory protection and does not support any form of extended objects, so all objects in the SCT are segments. The operating system for the Plessey machine detects and recovers any slots in the SCT that are occupied by segments that are no longer accessible from active capabilities so that they may be given to segments that are created subsequently. Names in the Plessey system are still global, but they are only unique in the sense that at any time a name is only associated with a single segment, although at another time the name might refer to a different segment if the original has been destroyed. Finding free slots in the SCT requires the use of a garbage collector that periodically scans all of the capabilities that are active in the system to determine which SCT slots are not referenced. The frequency at which the garbage collector runs and the size of the SCT must both be carefully tuned to avoid wasting space in the table and also to prevent the system locking up if the SCT is full. Names in the Plessey system are just sixteen bits long, which greatly contributes towards having short capabilities and the pricipal advantage of this scheme over Watson's proposal is

-28-

Figure 3.4-1 Plessey System/250 Naming Scheme

that proceeding from names to table entries only involves following a simple indirection and avoids the expense and complication of hashing.

The essential point to notice about the architectures proposed by Watson and Plessey is that, unlike the active global symbol table of HYDRA, the tables in memory are not caches for a larger data structure owned by the kernel. It might be the case that a higher level unique name table (such as the CAP System Internal Name table) exists, but the primitive naming and protection mechanisms know nothing about it and themanagement of forever-unique names is not a kernel function. The main advantage of adopting this view is that the global name table need only be of moderate size and resident in memory so that kernel naming and protection mechanisms can be implemented in simple and efficient code. The price paid for this facility is the need for translation between filing system names and run time names. In HYDRA the active global symbol table is purely a cache for the passive symbol table kept on disc and it is the duty of the HYDRA kernel to maintain both data structures, which is one reason why the HYDRA kernel is slow and unwieldy and has to be implemented in software rather than microprogram.

A compromise suggested by Lampson and Sturgis [76] to gain the benefits of short names whilst retaining a forever-unique name system is to make capabilities hold both a short run-time name and a long forever-unique name. Operations on the global name table in memory are carried out using short names to address slots within it and a quick check is made to ensure that a unique name held in the slot matches the unique name held in the capability being exercised. If the unique names do match, the operation is allowed to proceed, otherwise a trap is generated and the operating system can use the unique name to find or construct an entry in the table for the object, and the short name field of the faulty capability is then made to be the offset of the new slot. In essence, a short name is a 'hint' to the position of an entry for an object in the map. With this sort of organisation the map can function as a cache for a unique name table that is kept on backing store without involving the kernel in disc operations.

The kernel uses short names as pointers and this avoids the expense of hashing and leaves the management of forever-unique names to higher level components of the system. While this technique may seem to offer an ideal compromise between short names and unique names, there are many pitfalls to avoid. Capabilities are very long because of the need to hold both short and long names, and space must be found in the central object table entries for long names as for well as details of representations. It is necessary to provide code to manage both the small resident map and the larger permanent structure which have different naming conventions, and the interactions between the tables and the algorithms for managing them must be carefully considered to avoid problems of inconsistency, over-complication and loss of efficiency.

In general terms, all of the different management strategies for global name tables represent a compromise between the usage of space and time, so it is unreasonable to expect any single mechanism to be ideal. Instead it is necessary to consider the desired behaviour of a system and to adopt the techniques most suited to it.

### CHAPTER FOUR.

#### CAPABILITIES AND ADDRESSING.

### 4.1. Capability Structure and Organisation.

The natural place at which to start considering capabilities and addressing is with the nature and substance of capabilities themselves: a capability is evaluated from the contents of a data structure in memory which serves to define both the object protected by the capability, the privileges the capability confers, and in some systems (CAL-TSS for example), information about the type of the protected object. It is useful to be able to refer to the data structures themselves as capabilities although, in the strictest sense, it is the result of evaluating the data structures that yields capabilities. In this thesis, the term 'capability' is used with both meanings provided that it is possible to resolve any ambiguity from the context.

Because they contain names, capabilities must not be either forged or corrupted if protection is to be guaranteed. It is therefore necessary to have some method for distinguishing capabilities from ordinary data so that they can be recognised and only authorised capability operations carried out upon them. There are two common techniques for performing this discrimination: firstly, each item of information in memory may be tagged with a bit saying whether or not the item is a capability, and secondly, memory may be partitioned into disjoint capability and data regions.

Tagging has been successfully employed by the Burroughs B5000 computer system and its descendants [Burroughs 61] and has been extensively investigated by Feustel [73]. The protected items in these systems are 'descriptors' rather than capabilities, but the differences between them are of no immediate concern except for one point: descriptors typically tend to be smaller than capabilities as they contain less information. The impact of this becomes apparent in the light of current trends to reduce the size of addressable items in memory. In the past, machines with items

of thirty-two, forty-eight and even sixty bit items were common, but nowadays the eight bit character, or byte, is becoming universal and proposals have been made for bit-addressable memories. In such addressing organisations a large object such as a capability is implemented as a contiguous sequence of locations of memory usually addressed by the offset of the first element in the frame. If tagging is to be used, it would seem that at first sight two tag bits are required, with the significance 'first item of a capability' and 'subsequent of item a capability' respectively, so that it may be ensured that capabilities are correctly manipulated, but clearly the overhead of associating two extra bits with a small item of, say, eight bits is wasteful and expensive.

A simple way of avoiding the expense is to insist that capabilities can only be stored starting at addresses that are a multiple of the length of a capability and that capability addresses must locate one of the predetermined capability frames; this only requires a single tag bit but complicates software because of the need to align capabilities which sacrifices many of the advantages of being able to access small items. A full discussion of tagging hardware for a capability machine can be found in Redell [74] together with some proposals for a scheme which is economic in terms of the number of tag bits, yet permits items to be arbitrarily laid out in store.

The generality of being able to mix capabilities and data freely in a tagged memory regime poses some system problems: some part of the protection system must be responsible for creating new capabilities and destroying unwanted ones and to do so it must be possible to write arbitrary bit patterns in capabilities, although the use of this privilege must be protected to ensure the integrity of the rest of the protection machinery. This operation conflicts with the setting of a capability's tag bit and some escape mechanism must be provided to overide tags which, in most tagged machines, is available only in a special or privileged state that allows <u>any</u> capability to be modified. This latter privilege is more sweeping than that which is actually required and it is not possible to limit selectively the capabilities which

-32-

#### may be affected.

A further problem arises from the observation that an operating system is obliged to know the location of capabilities and other protection data structures; for example, it may be necessary to scan all the capabilities belonging to a protection domain to find lost objects, or to detect garbage in internal tables. If capabilities are freely distributed throughout a domain's memory (as tagging would allow), the scan would have to include every item in memory that could possibly contain a capability. In any system, and even more so in one that has a large backing store, this task would be exceptionally expensive in both processor time and virtual memory traffic.

The difficulties encountered in a tagged architecture may be avoided by partitioning capabilities and data. In a partitioned system the access code of a capability for a segment will belong to one of two categories: capability type access or data type access. To perform data operations such as addition or shifting on items in a segment, it is necessary to present a capability bearing the appropriate data type access code such as read, write or execute and for a capability operation, a capability presenting a capability type code such as read-capability or write-capability must be used. Thus the interpretation of the contents of a segment depends upon the capability used to gain access to it and it is usual to refer to a segment for which capability access is held as a capability segment; otherwise, if the access is of data type, it is referred to as a data segment. In this scheme, the part of the operating system concerned with altering the contents of capabilities would have a capability giving data access to segments that are elsewhere accessed with capability access and because the ability to modify a particular capability is itself by a capability, it is possible to controlled control the privilege.

The software for managing capabilities in a partitioned architecture does not have to scan the entire memory of the system to find all capabilities, instead it is only necessary to consider capability segments, that is, those for which there is a capability with a capability type access code in existence. It may be expected that there will be far fewer of these segments than data segments.

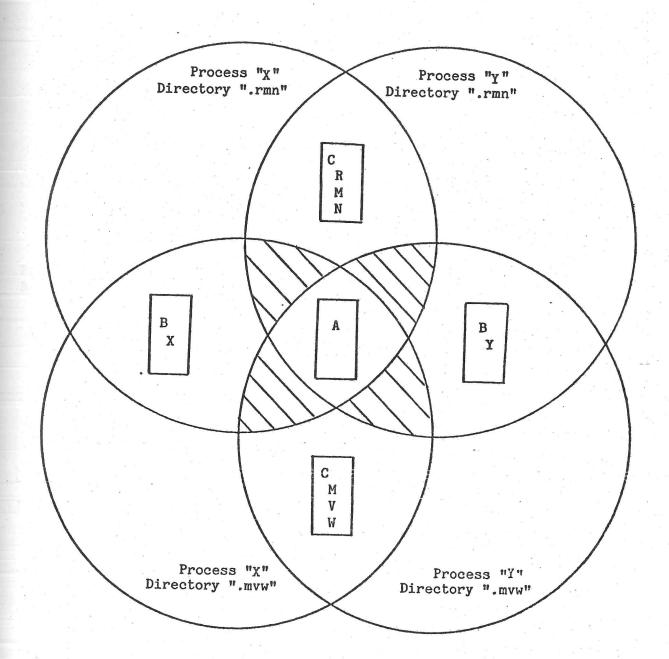

The disadvantage of partitioning is that a certain amount of generality is lost: it is not possible to have data structures represented by segments that contain a mixture of capabilities and data and there are occasions when the lack of this feature is a nuisance. Consider, for example, a directory or catalogue for a filing system: the directory cannot be implemented as a segment containing both capabilities for the objects filed within it together with data representing file names and access control information, whereas in a tagged machine the directory could be made easily from a single segment. In a partitioned architecture it would have to be implemented as two segments, one for data and one for capabilities, which is inefficient as it requires two transfers to bring all of the directory into store. The HYDRA system [Cohen and Jefferson 74] employs partitioning but tries to recapture generality by providing 'universal' objects, holding both data and capabilities, that are formed from two segments, one of which holds the data part of the object and one for its capabilities. The implementation of the object as two segments is concealed from the user, but it is not possible to interleave capabilities and data arbitrarily inside the object as the two sorts of information are addressed in different ways. By careful allocation of disc space it can be arranged that the two segments of a universal object are adjacent on disc and can be brought into store in a single transfer. The CAP and Plessey 250 systems also partition capabilities and data but neither has any facility for mixed type segments.

An important consequence of adopting а partitioned architecture is that, unless ordinary orders recognise capability data type access codes, they and cannot be used to move capabilities around between capability segments which means that a special suite of capability orders must be provided.

# 4.2. Capabilities and Virtual Address Translation.

In a segmented addressing architecture, an address contains two fields, one of which selects a descriptor for one of the segments in a virtual address space and the other indexes a particular item within the segment. Capabilities can be usefully employed as descriptors because they are protected from forgery or corruption and can be passed between address spaces to permit sharing, without the need to resort to complex linkage tables such as those found in MULTICS [Organick 72]. Capability segments can take the place of descriptor tables and each capability within the tables will define a segment associated with some virtual addresses. Two address spaces sharing access to some object will have similar capabilities for it in their (descriptor) capability segments. A capability used as a descriptor provides a bridge between virtual address spaces and the naming machinery because an address nominates a capability which in turn, provided there are no access violations, yields the name of an object which is the key for obtaining its representation.

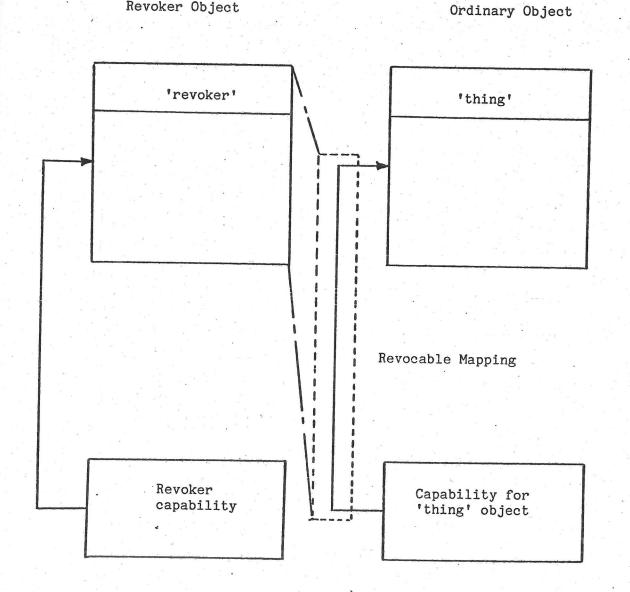

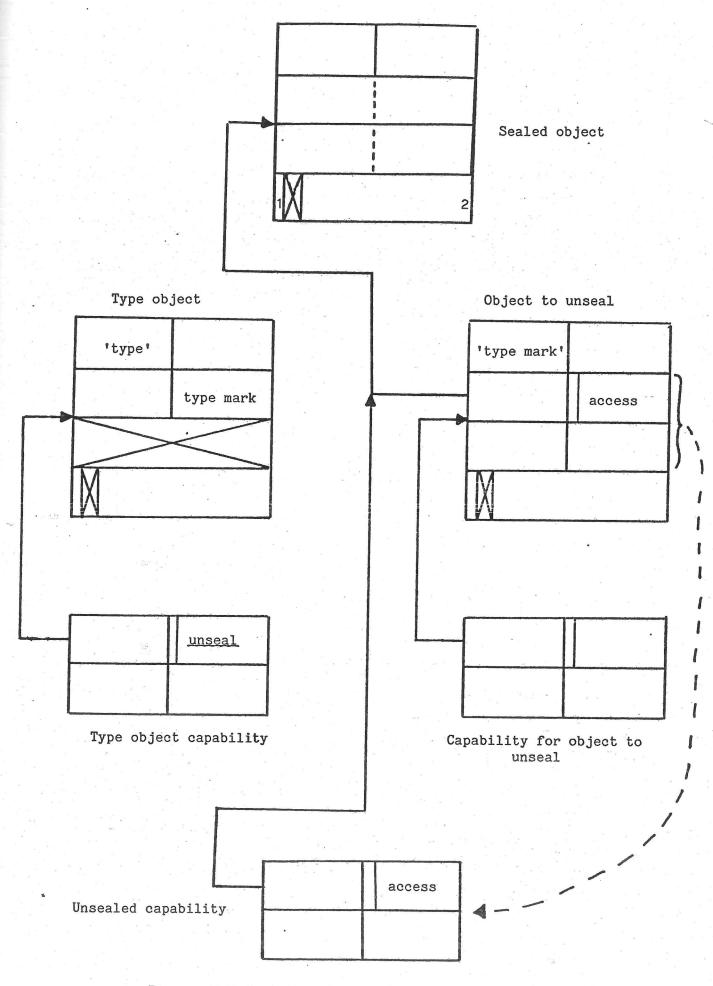

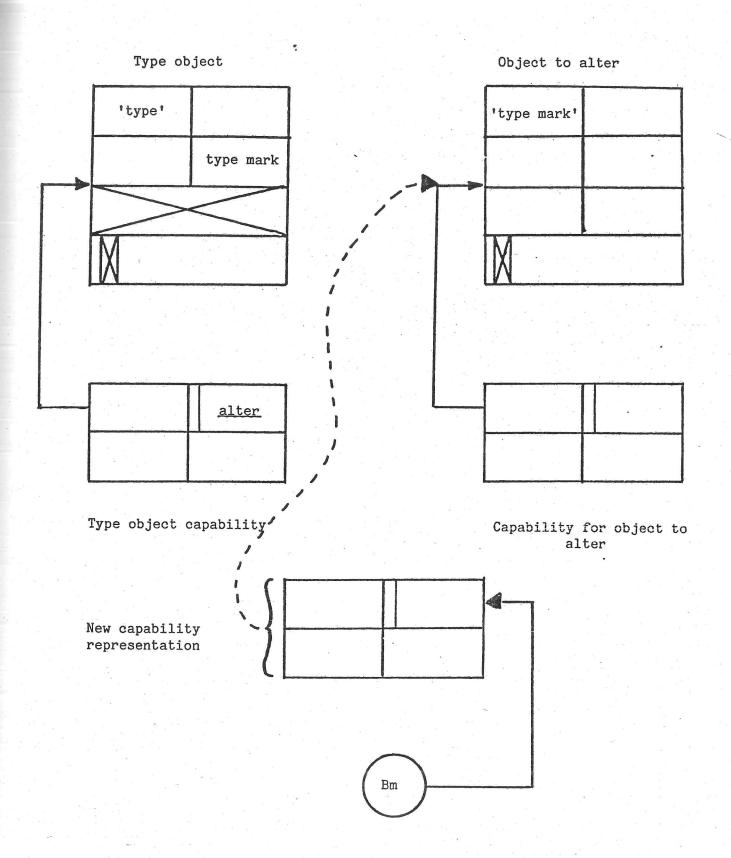

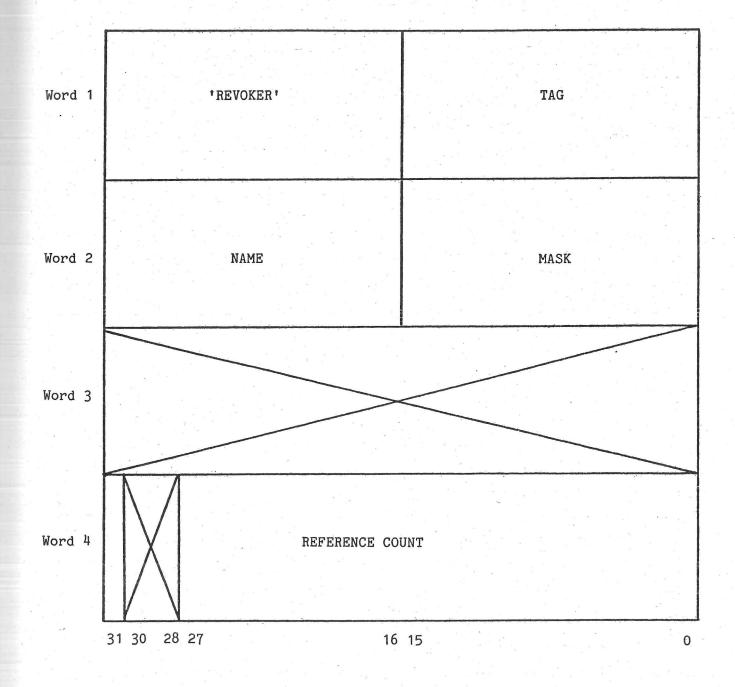

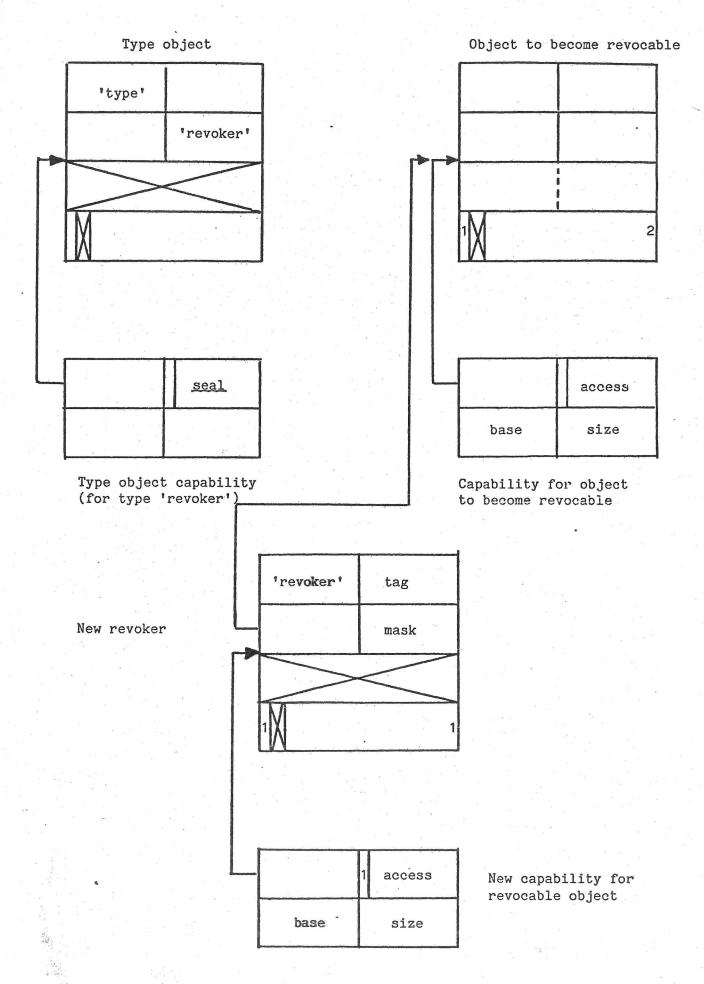

There are two ways of using capability descriptors: explicitly by loading them into capability registers or implicitly by making the virtual address translation mechanism evaluate descriptor capabilities automatically.