# Optimization of the Memory Subsystem of a Coarse Grained Reconfigurable Hardware Accelerator

vom Fachbereich Elektrotechnik und Informationstechnik der Technischen Universität Darmstadt

zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.)

Dissertation

von

Lukas Johannes Jung

Erstgutachter: Prof. Dr.-Ing Christian Hochberger Zweitgutachterin: Prof. Dr.-Ing. Diana Göhringer

Lukas Johannes Jung:

# Optimization of the Memory Subsystem of a Coarse Grained Reconfigurable Hardware Accelerator

Darmstadt, Technische Universität Darmstadt Jahr der Veröffentlichung der Dissertation auf TUprints: 2019 Tag der mündlichen Prüfung: 27.03.2019

Verfügbar unter lediglich die vom Gesetz vorgesehenen Nutzungsrechte gemäß UrhG.

# Erklärung laut Promotionsordung

#### § 8 Abs. 1 lit. c PromO

Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.

#### § 8 Abs. 1 lit. d PromO

Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen.

#### § 9 Abs. 1 PromO

Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der angegebenen Quellen verfasst wurde.

#### § 9 Abs. 2 PromO

Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.

#### L. J. Jung

# Kurzfassung

Schnelle und energieeffiziente Datenverarbeitung ist seit jeher eine wichtige Anforderung an Prozessorentwicklung. Aktuelle Entwicklungen in Bereichen wie zum Beispiel Bildverarbeitung verstärken diese Anforderungen. Die Nutzung von vielen mobilen Endgeräten steigert den Bedarf an energieeffizienten Lösungen. Viele Anwendungen wie zum Beispiel Fahrerassistenzsysteme setzen immer mehr auf Algorithmen aus dem Bereich Maschinelles Lernen. Hierbei müssen unter harten Echtzeitbedingungen viele Daten in kürzester Zeit verarbeiten werden. Bis zu den 1990er Jahren wurden Leistungssteigerungen in Prozessoren meist dadurch erreicht, dass neue und bessere Fertigungstechnologien verwendet wurden. Dadurch wurde es möglich, Prozessoren mit einer höheren Taktfrequenz zu betreiben, während die eigentliche Prozessorarchitektur weitestgehend unverändert blieb. Seit Beginn des einundzwanzigsten Jahrhunderts jedoch stagniert diese Entwicklung. Neuere Fertigungstechnologien ermöglichen es zwar mehr Prozessorkerne auf der gleichen Chipfläche zu fertigen, jedoch wurden kaum noch Steigerungen in der Taktfrequenz erreicht. Dies erforderte ein Umdenken in sowohl dem Entwurf von Prozessorarchitekturen als auch im Software-Entwurf. Anstatt die Leistung eines einzelnen Prozessors zu verbessern, muss nun ein zu berechnendes Problem so formuliert werden, dass es in kleinere Teile aufgeteilt wird welche auf mehreren Recheneinheiten parallel und dadurch schneller berechnet werden können.

Ein oft genutzter Ansatz ist der Einsatz von Mehrkernprozessoren oder GPUs (Graphic Processing Units), in dem jeder Prozessorkern einen Teil des Problems unabhängig von den restlichen Kernen berechnet. Dies erfordert jedoch neuartige Programmiertechniken und bestehende Software muss umformuliert werden. Ein anderer Ansatz sind Hardware-Beschleuniger, die mit einem Prozessor verbunden werden. Hier wird für ein bestimmtes Problem eine spezielle Schaltung entworfen, die dieses Problem effizient und schnell lösen kann. Die Berechnung dieses Problems findet dann nicht mehr auf dem Prozessor statt, sondern auf dem Hardware-Beschleuniger. Der Nachteil dieser Lösung ist jedoch, dass für jedes Problem eine eigene Schaltung in Hardware entwickelt werden muss. Dies bedeutet einen hohen Entwicklungsaufwand und die Schaltung kann im allgemeinen nicht im Nachhinein geändert werden.

Diese Arbeit beschäftigt sich mit der Nutzung von rekonfigurierbaren Hardware-Beschleunigern. Diese werden während der Laufzeit umkonfiguriert, um mehrere Probleme mithilfe der gleichen Hardware beschleunigen zu können. Wenn während der Laufzeit rechenintensive Software-Abschnitte erkannt werden, so startet der Prozessor selbstständig einen Prozess, der eine Konfiguration für den Hardware-Beschleuniger berechnet. Anschließend kann diese Konfiguration geladen werden und das Problem wird effizienter und schneller auf dem Beschleuniger ausgeführt. Es wurde eine grobkörnig rekonfigurierbare Architektur gewählt, da die Komplexität eine Konfiguration zu berechnen sehr viel geringer ist als in feinkörnig rekonfigurierbaren Architekturen wie zum Beispiel FPGAs (Field Programmable Gate Array). Außerdem sind durch den vergleichsweise

geringeren Mehraufwand für die Rekonfigurierbarkeit höhere Taktfrequenzen möglich als bei FPGAs. Ein Vorteil dieses Verfahrens ist, dass ein Programmierer oder eine Programmiererin keinerlei Kenntnis über die Hardware besitzen muss, da die Beschleunigung automatisch während der Laufzeit geschieht. Außerdem können bereits vorhandene Programme (bei denen möglicherweise kein Programmcode mehr vorliegt) ohne weiteren Aufwand beschleunigt werden.

Ein Problem, das für alle Rechnerarchitekturen relevant ist, ist die effiziente und schnelle Datenübertragung zwischen Recheneinheit und Hauptspeicher. Diese Arbeit konzentriert sich daher auf die Optimierung der Speicheranbindung eines grobkörnig rekonfigurierbaren Hardware-Beschleunigers. Zu diesem Zweck wurde während dieser Arbeit ein Simulator für einen Java-Prozessor entworfen, in dem ein grobkörnig rekonfigurierbarer Hardware-Beschleuniger eingebunden ist. Es wurden mehrere Verfahren entwickelt, die die Speicheranbindung des Hardware-Beschleunigers verbessern. Dies umfasst sowohl Lösungen auf Hardware-Ebene als auch Lösungen auf Software-Ebene, die bei der Generierung der Konfiguration für den Beschleuniger versuchen die Nutzung der Speicherschnittelle zu optimieren. Der entwickelte Simulator wurde genutzt, um den Entwurfsraum nach der besten Implementierung abzusuchen. Durch diese Optimierung des Speichersystems wurde eine Leistungssteigerung von 22,6 % erreicht.

Außerdem wurde während dieser Arbeit ein erster Prototyp eines solchen Beschleunigers in Hardware entworfen und auf einem FPGA implementiert, um die korrekte Funktionalität des Verfahrens und des Simulators zu zeigen.

#### Abstract

Fast and energy efficient processing of data has always been a key requirement in processor design. The latest developments in technology emphasize these requirements even further. The widespread usage of mobile devices increases the demand of energy efficient solutions. Many new applications like advanced driver assistance systems focus more and more on machine learning algorithms and have to process large data sets in hard real time. Up to the 1990s the increase in processor performance was mainly achieved by new and better manufacturing technologies for processors. That way, processors could operate at higher clock frequencies, while the processor microarchitecture was mainly the same. At the beginning of the 21st century this development stopped. New manufacturing technologies made it possible to integrate more processor cores onto one chip, but almost no improvements were achieved anymore in terms of clock frequencies. This required new approaches in both processor microarchitecture and software design. Instead of improving the performance of a single processor, the current problem has to be divided into several subtasks that can be executed in parallel on different processing elements which speeds up the application.

One common approach is to use multi-core processors or GPUs (Graphic Processing Units) in which each processing element calculates one subtask of the problem. This approach requires new programming techniques and legacy software has to be reformulated. Another approach is the usage of hardware accelerators which are coupled to a general purpose processor. For each problem a dedicated circuit is designed which can solve the problem fast and efficiently. The actual computation is then executed on the accelerator and not on the general purpose processor. The disadvantage of this approach is that a new circuit has to be designed for each problem. This results in an increased design effort and typically the circuit can not be adapted once it is deployed.

This work covers reconfigurable hardware accelerators. They can be reconfigured during runtime so that the same hardware is used to accelerate different problems. During runtime, time consuming code fragments can be identified and the processor itself starts a process that creates a configuration for the hardware accelerator. This configuration can now be loaded and the code will then be executed on the accelerator faster and more efficient. A coarse grained reconfigurable architecture was chosen because creating a configuration for it is much less complex than creating a configuration for a fine grained reconfigurable architecture like an FPGA (Field Programmable Gate Array). Additionally, the smaller overhead for the reconfigurability results in higher clock frequencies. One advantage of this approach is that programmers don't need any knowledge about the underlying hardware, because the acceleration is done automatically during runtime. It is also possible to accelerate legacy code without user interaction (even when no source code is available anymore).

One challenge that is relevant for all approaches, is the efficient and fast data exchange between processing elements and main memory. Therefore, this work concentrates on the optimization of the memory interface between the coarse grained reconfigurable hardware accelerator and the main memory. To achieve this, a simulator for a Java processor coupled with a coarse grained reconfigurable hardware accelerator was developed during this work. Several strategies were developed to improve the performance of the memory interface. The solutions range from different hardware designs to software solutions that try to optimize the usage of the memory interface during the creation of the configuration of the accelerator. The simulator was used to search the design space for the best implementation. With this optimization of the memory interface a performance improvement of 22.6 % was achieved.

Apart from that, a first prototype of this kind of accelerator was designed and implemented on an FPGA to show the correct functionality of the whole approach and the simulator.

# Contents

| I. | Introduction                                                | 13           |

|----|-------------------------------------------------------------|--------------|

| 1. | Introduction  1.1. Motivation                               |              |

| 2. | Technical Background2.1. Reconfigurable Hardware2.2. Caches |              |

| 3. | Related Work  3.1. Reconfigurable Accelerators              | . 34<br>. 35 |

| 4. | Description of Our Approach 4.1. Problem Formulation        |              |

| II | . System Description                                        | 41           |

| 5. | Java as Instruction Set Architecture                        | 43           |

| -  | 5.1. Java Memory System                                     | _            |

|    | 5.2. Java Bytecode                                          | . 46         |

|    | 5.3. Java Method calls                                      | . 48         |

| 6. | AMIDAR Processor                                            | 49           |

|    | 6.1. Basic Principle                                        |              |

|    | 6.2. Functional Units                                       | . 50         |

|    | 6.3. AMIDAR Executable Format                               | _            |

|    | 6.4. Online Profiler                                        | . 53         |

| 7. | CGRA Architecture                                           | 55           |

|    | 7.1. Processing Element Array                               |              |

|    | 7.2. Context Memories                                       |              |

|    | 7.3. Context Control Unit                                   |              |

|    | 7.4. Condition Box                                          |              |

|    | TO TROUDELAND RESIDERS OF THE CASE A                        | nı           |

10 Contents

| 8.        | AMIDAR CGRA Interface                            | 63        |

|-----------|--------------------------------------------------|-----------|

|           | 8.1. Interface Configuration Memories            | 63        |

|           | 8.2. CGRA Bytecodes                              | 65        |

|           | 8.3. Live-In/Out Strategies                      | 67        |

|           |                                                  |           |

| 9.        | Kernel Mapping Algorithm                         | <b>73</b> |

|           | 9.1. Speculative Method Inlining                 | 74        |

|           | 9.2. Instruction Graph Generation                | 76        |

|           | 9.3. Control and Dataflow Graph Generation       | 76        |

|           | 9.4. Resource and Routing Constrained Scheduling | 79        |

|           | 9.5. Context Management                          | 80        |

|           | 9.6. Bytecode Patching                           | 81        |

| II        | .Memory Subsystem Optimization                   | 83        |

| 10        | High-Level Compiler Optimizations                | 85        |

|           | 10.1. Software Pipelining                        | 85        |

|           | 10.2. Aliasing Speculation                       | 91        |

|           |                                                  |           |

| 11        | Memory Subsystem                                 | 97        |

|           | 11.1. Cache Architecture                         | 97        |

|           | 11.2. Coherence Protocol                         | 100       |

|           | 11.3. Access Classification and Distribution     | 102       |

| 10        |                                                  | 100       |

| 12        | Memory Prefetching                               | 103       |

|           | 12.1. Lookahead Prefetching                      |           |

|           | 12.2. Prefetch management                        | 106       |

| 12        | Implementation and Timing Analysis               | 109       |

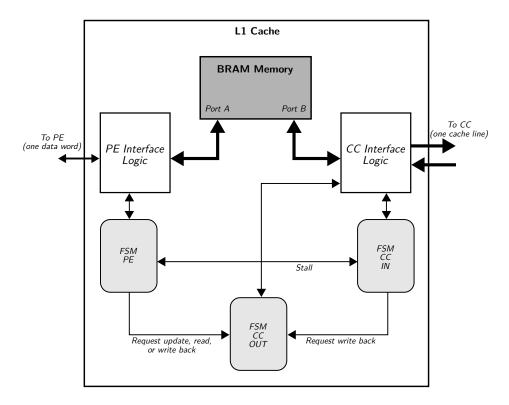

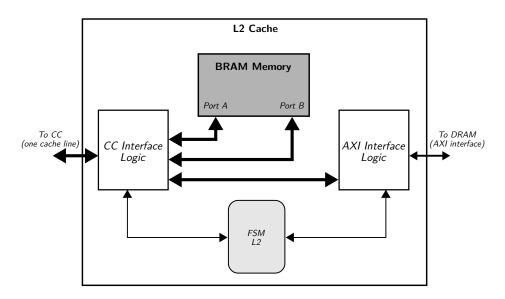

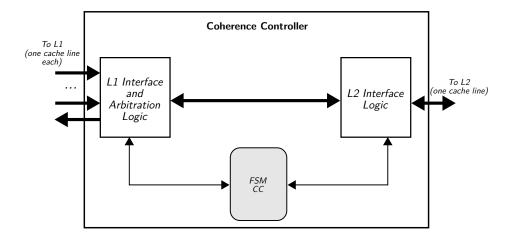

| 10        | 13.1. L1 Cache                                   |           |

|           | 13.2. L2 Cache                                   | 110       |

|           | 13.3. Coherence Controller                       |           |

|           |                                                  |           |

|           | 13.4. Timing Analysis                            | 111       |

| IV        | .Evaluation                                      | 115       |

| 14        | AMIDAR Simulator                                 | 117       |

| 11        | 14.1. Simulator Implementation                   | 117       |

|           | 14.2. Parallel Sweeps                            | 117       |

|           | <del>-</del>                                     |           |

|           | 14.3. Performance                                |           |

|           | 14.4. Measurement Procedure                      | 125       |

| <b>15</b> | Prerequisites                                    | 127       |

|           | 15.1. Benchmark Applications                     | 127       |

|           | 15.2. CGRA Comparison                            | 128       |

Contents 11

| 16.Design Space Exploration              | 131          |

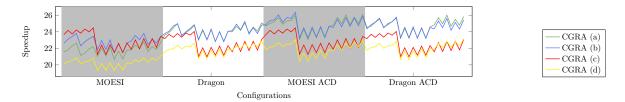

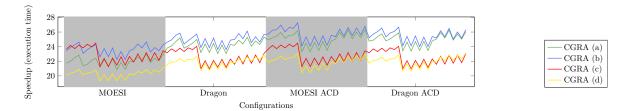

|------------------------------------------|--------------|

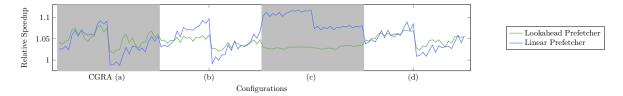

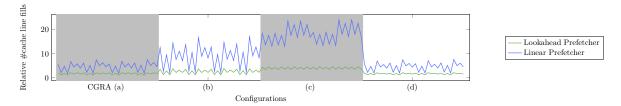

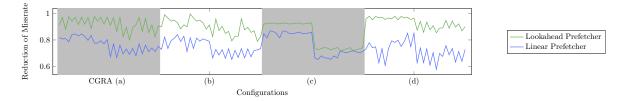

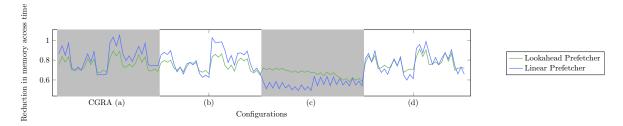

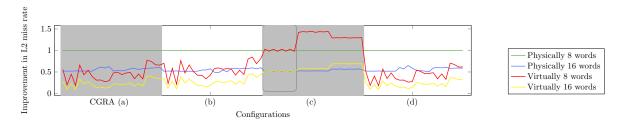

| 16.1. Discussion of Prefetching          | 133          |

| 16.2. Discussion of Coherence Mechanisms | 135          |

| 16.3. Discussion of Aliasing Speculation | 137          |

| 16.4. Discussion of L2 Cache Design      | 139          |

| 16.5. Discussion of CGRA Design          |              |

| 16.6. Summary                            |              |

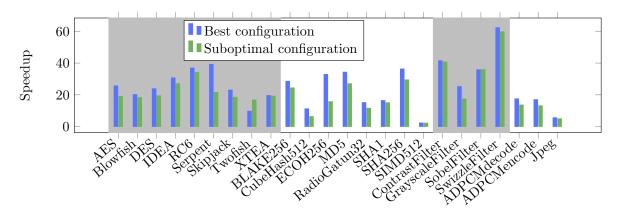

| 17.Results                               | 145          |

| 17.1. Comparison With Other Approaches   | 146          |

| 17.2. Prototype Implementation           | 148          |

| 18.Conclusion                            | 151          |

| 18.1. Open Points and Future Work        | 152          |

| 18.2. Summary                            |              |

| Bibliography                             | 155          |

| A. AMIDAR Simulator Accuracy             | III          |

| B. CGRA Description                      | $\mathbf{V}$ |

| C. Nested Loops in The Schedule          | IX           |

| D. Design Space Exploration D.1. Results | XI<br>XII    |

| E. Contributions of this Work in Part II | XXIII        |

# Part I. Introduction

# 1. Introduction

Writing working program code is easy. Writing good program code takes some effort. Writing program code that perfectly exploits all features of the machine on which it is running is hard. Especially, if the programmer doesn't have any information about the underlying hardware. Normally, this leads to two mutually exclusive design goals: The software can either be highly performant or it is cheap. In the last millennium this problem could simply be solved by waiting. The processor speeds kept increasing due to better manufacturing technologies so that after some time the written software would execute significantly faster on a new processor. Due to higher power consumption this trend stopped at around 2003. The improvements in single thread performance stagnated. To improve the performance further new concepts like multi-core processors were introduced and are being researched to exploit parallelism. Yet, in most cases this means that existing software has to be adapted so that it can benefit from these new concepts.

#### 1.1. Motivation

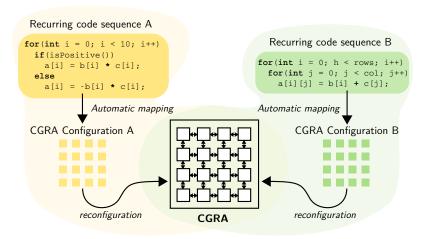

In this work a new concept is used, that tries to exploit parallelism without user interaction. The idea is that the processor "knows" its own architecture so the processor itself will parallelize the code. A Coarse Grained Reconfigurable Array (CGRA) will

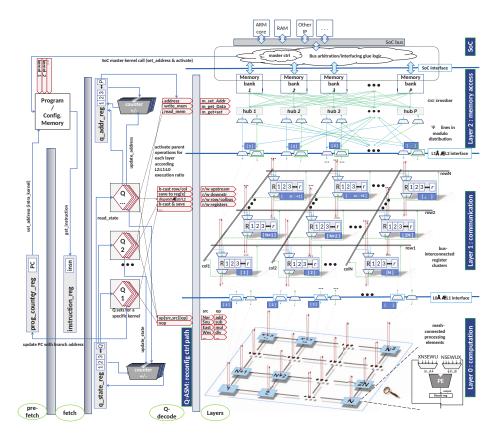

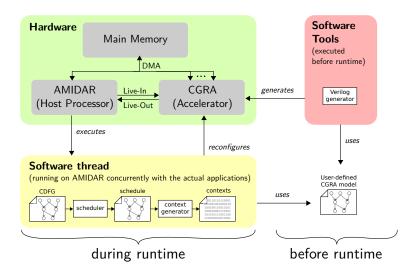

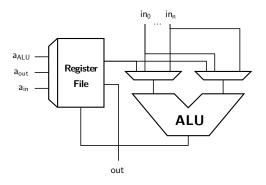

Figure 1.1.: Accelerator concept used in this work

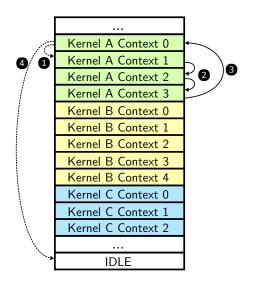

be coupled to a host processor and will be used as an accelerator for recurring code sequences (called *kernel* in the remainder of this work) as shown in Figure 1.1. The code sequences will be mapped to the CGRA automatically and totally transparent for the user during runtime. The CGRA can be reconfigured quickly so that the same

1. Introduction

hardware can be used to accelerate different code sequences. Mapping the sequences to the CGRA during runtime gives the possibility to react to changes in both software execution or the hardware when for example a PE produces erroneous results.

This approach leads to the following benefits:

- 1. The programmer can write simple working code and the processor will automatically accelerate it on the CGRA so that it will be executed efficiently. This will result in performant software execution at low development cost.

- 2. Legacy code will be parallelized and thus accelerated automatically without user interaction or recompilation.

- 3. Hardware costs are low due to reconfiguration and reuse.

- 4. Applications can be accelerated with CGRAs of different sizes without the need to adapt the code.

The memory subsystem is a bottleneck of modern computers due to the memory wall[77][33]. The performance of the compute engine doesn't matter if the memory subsystem is not able to provide the data that has to be processed. Thus, this work concentrates on the design and optimization of the memory subsystem of the reconfigurable accelerator. The memory system is tightly coupled with the accelerator, so both parts cannot be designed independently. For that reason this work also covers significant parts of the whole CGRA based accelerator framework and not only the memory subsystem.

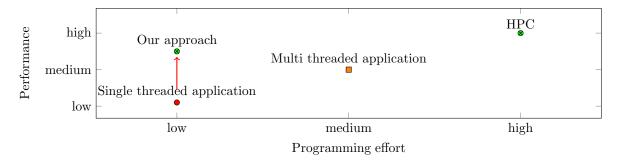

It is obvious that the performance of this approach can not compete with hand optimized code running on commercial high performance computers (HPC) which require a high programming effort as shown in Figure 1.2. In contrast to that, single threaded software

Figure 1.2.: Qualitative illustration of programming effort vs performance

can be written easily but results in a low performance. Multi-threaded applications exploit task level parallelism and range between HPC and single threaded applications both in performance and programming effort. The aim of this work is to increase the performance of arbitrary single threaded applications by exploiting both instruction level parallelism and loop level parallelism. At the same time the programming effort should be kept low as shown in Figure 1.2.

Parallel patterns are often well studied and efficient implementations for different architectures are provided for common tasks like matrix multiplication or FFT. Thus,

|                 | Requirements on       |                     |                    |

|-----------------|-----------------------|---------------------|--------------------|

| Goal            | CGRA                  | Memory subsystem    | Mapping Algorithm  |

| Support arbi-   | Flexible interface to | Flexible memory in- |                    |

| trary applica-  | host processor        | terface             |                    |

| tions           |                       |                     |                    |

| Reconfiguration | Quick reconfigura-    |                     | Low complexity to  |

| during runtime  | tion times            |                     | minimize overhead  |

| High perfor-    | Support control       | Parallel memory ac- |                    |

| mance           | flow on CGRA so       | cesses with low la- |                    |

|                 | that larger code      | tency               |                    |

|                 | regions can be        |                     |                    |

|                 | mapped to the         |                     |                    |

|                 | CGRA                  |                     |                    |

| Low program-    |                       |                     | Support high level |

| ming effort     |                       |                     | language           |

Table 1.1.: Goals and resulting requirements

in this work the focus lies on applications with irregular and possibly data dependent program flow and memory access patterns. This leads to several requirements for the CGRA based accelerator, the memory subsystem and the mapping algorithm which are listed in Table 1.1.

#### 1.2. Contribution of this Work

The result of this work will not be to find *the* memory subsystem design which outperforms all other designs in all cases. The performance of the memory subsystem depends too much on the accelerator it is coupled to, the supported programming language and the technology that is used to implement the hardware or the application itself. Some general statements can be made but the optimal memory subsystem does not exist.

Instead this work aims to describe a way to find the best configuration for a certain setup exemplarily. A simulator of the accelerator framework will be implemented in work, which makes it possible to do huge design space explorations. This simulator should be able to run tests with more than thousand different configurations in a matter of hours with high accuracy. In order to be able to produce profound results, a prototype should be implemented in hardware, which is used to tune the simulator.

The high accuracy can only be guaranteed when the whole system and not just the memory subsystem is implemented. Otherwise assumptions are made which lead to inaccuracies. Previous publications ([20][19][15][12][13][16][18]) already described the whole system to some extend but only on a higher level of abstraction and no hardware implementation was available. Thus, the system will be (re-)implemented and significant parts of this work concern the design of the whole accelerator system as mentioned before.

1. Introduction

This leads to the following goals that this work aims to achieve:

1. Implement a prototype of the CGRA based accelerator coupled with a processor based on the previous work mentioned above. The prototype should hold the requirements given in Table 1.1.

- 2. Extend the existing simulator of the CGRA based accelerator system or implement a new one. The insights of the prototype implementation should be used to achieve high accuracy while maintaining high simulation speed so that the simulator can be used to do design space explorations with profound results.

- 3. Use the simulator to find the optimal memory subsystem in the given setup. Which parameters are optimal and which factors influence the choice of parameters? Are there general findings?

As mentioned above, this work extends an existing framework so the Parts I and II describe both existing and new work while Parts III and IV contain only new work.

In Appendix E a detailed description is given which parts of the existing system were just reused without change, which were adapted and which are completely new.

# 2. Technical Background

This chapter provides technical background which is helpful to understand the remainder of this work.

## 2.1. Reconfigurable Hardware

This section gives a short overview of the most common reconfigurable hardware architectures and discusses why CGRAs are used in this work. Typically, reconfigurable hardware consists of logic blocks that are connected by reconfigurable interconnect.

#### 2.1.1. Field Programmable Gate Arrays

Field Programmable Gate Arrays (FPGA) are the most common reconfigurable hardware. As the name states, they are reconfigurable in the field which means that the hardware design can be changed even after the product has been deployed. The logic blocks in an FPGA are typically called CLB (Configurable Logic Block) and consist of look up tables (LUT), flip flops and multiplexers which can be configured and connected via switches at bit level. Thus, any application can be mapped to an FPGA. The downside is that the high hardware overhead that realizes the reconfigurability leads to relatively low clock frequencies at around 100-200MHz in the final design. Additionally, mapping the hardware design to the FPGA is a very complex task. Typically, a design is given in a Hardware Description Language (HDL) like Verilog or VHDL. Vendor tools map this design to the FPGA and create a bitfile that contains the configuration of all logic blocks and their interconnect. Creating this can take up to hours. Mapping the design that is described in this work on to a middle-class Artix 7 FPGA takes 29 minutes on an Intel i7 6700 with 3.4 MHz. The bitfile has a size of 9.7 MB and it takes milliseconds to load it onto the FPGA.

Commercial FPGAs usually also contain hard macros that are frequently used in typical FPGA designs. These hard macros range from RAM blocks (BRAM) over clock managers to DSP blocks with integrated integer adders and multipliers.

FPGAs can be reconfigured partially which can be used implement different hardware accelerators like in [28].

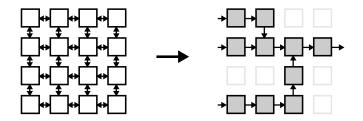

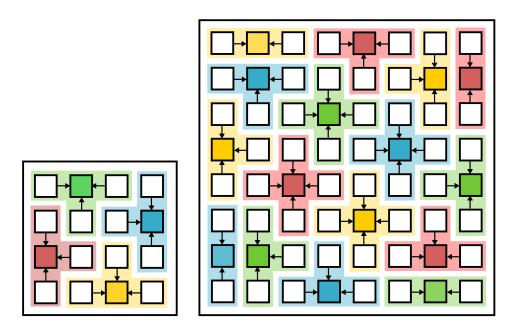

Figure 2.1.: Static kernel mapped onto a CGRA

#### 2.1.2. Coarse Grained Reconfigurable Arrays

In contrast to FPGAs Coarse Grained Reconfigurable Arrays (CGRA) are not reconfigured at bit level but on word level. The logic blocks which are also called Processing Element (PE¹) in this context, contain complete ALUs with one ore more registers or even a register file. PEs are connected with parallel busses that transfer one word in one cycle. The more coarse granularity limits the ability to map arbitrary code to the reconfigurable hardware (especially for operations on the bit level) but at the same time the complexity of the mapping process is reduced. Mapping a design to the CGRA can be done in less than one second and the configuration contains only around 1 kBit depending on the number of PEs and their interconnect. One configuration of a CGRA is also called *context*. FPGAs can only store one configuration in the fabric. Due to the small context size, it is possible to include a context memory on the CGRA that stores up to thousands of contexts. Once the contexts are loaded into that memory they can be switched in one clock cycle. Also, the coarse granularity results in higher frequencies. Preliminary tests have shown that frequencies of up to 1GHz are possible on 45nm TSMC technology.

CGRAs can be used in different fashions. In the **static** case a hardware description is mapped to the CGRA (e.g.[37] or [22]). Only a single context is used to create a specialized data path. Data is typically fed in to the CGRA on one side of the array and the results will be returned on the other side as shown in Figure 2.1. This way, efficient hardware pipelines can be created for regular and compute intense applications like image processing. Yet, only basic control flow can be included with the help of multiplexers. Also, the size of the datapaths that can be realized is limited to the number of PEs. This approach is often used in CGRAs that are included in the datapath of a CPU so that a set of instructions can be executed efficiently on that specialized datapath (e.g. [22] or [76]).

In the **dynamic** case an *application* is mapped to the CGRA. A dynamic datapath is created from several contexts. The next context that will be executed can be dependent on previous results. It is possible to realize complex control flow and larger datapaths. Hardware pipelines like in the static case can not be created. Thus, techniques like

<sup>&</sup>lt;sup>1</sup>In some literature the term Functional Unit (FU) is used. In the CGRA that is used in this work, the term PE will be used, as parts of our AMIDAR processor are also called FUs as described in Chapter 6

2.2. Caches 21

software pipelining have to be applied when an application is mapped to the CGRA to increase parallelism.

In this work a CGRA will be used with dynamic kernels for the following reasons:

- 1. CGRAs can operate at higher frequencies than FPGAs

- 2. CGRA configurations can be computed much faster which is important for runtime reconfiguration

- 3. CGRAs can store multiple contexts

- 4. Dynamic Kernels allow the acceleration of kernels with complex control flow

Often CGRAs are created as an overlay design for FPGAs so that an existing design can be adapted quickly. In this work the proposed CGRA design will also be mapped on to an FPGA but only to test the prototype. Creating an ASIC is the goal so that higher frequencies can be used.

A detailed description of the used CGRA is given in Chapter 7.

#### 2.2. Caches

The performance of modern memories does not match the performance of modern processors. Either the memories are fast enough to provide the required data in time or they are large enough to hold all data of an application at one time. Both at the same time is not possible with current memory technologies.

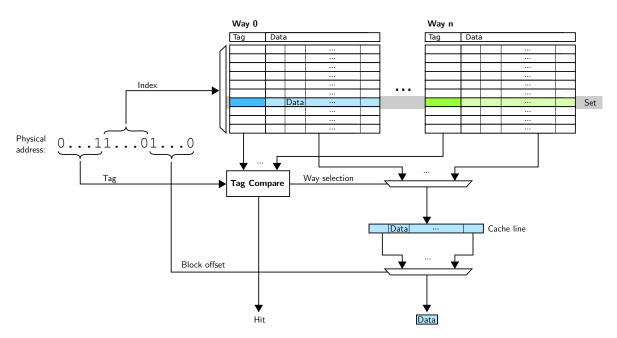

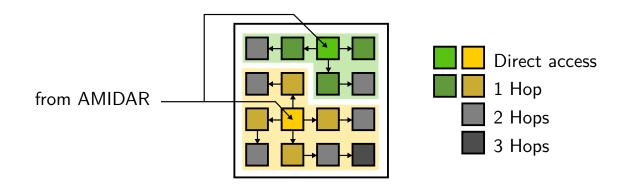

Fortunately, memory accesses typically follow two principles: First, data that is used in the processor is likely to be used again in the near future (temporal locality). Second, data that lies in the same memory region is likely to be used as well (spatial locality). Thus, it is possible to connect the processor to a small but fast memory (called cache) that holds only the subset of the data that is currently needed. Caches are organized in lines that contain data words from a contiguous memory region. When the required data is in the cache (hit) it can be sent to the processor directly. Only when the required data is not in the cache, the larger and slower main memory has to be accessed. In this case not only the desired data is loaded, but a whole set of data from the same region (exploiting spatial locality) is loaded into one cache line (shown for example in light blue in Figure 2.2). The main memory is traditionally realized in DRAM which has a high overhead when a memory cell is accessed but data from the same memory row can then be read with low cost. When the cache memory is full, data that has been used least recently will to be replaced (exploiting temporal locality).

In order to know which data resides in one cache line, not only the data but also meta information has to be stored. This information is called tag and contains (parts of) the original address of the data (shown in dark blue in Figure 2.2).

In fully associative caches any cache line can contain any data. This means that the tag of every cache line has to be checked in order to find out whether the desired data is currently in the cache. This is very costly and not used in practice. Instead *n*-way

Figure 2.2.: Illustration of working principle of caches

associative caches are used. A certain data word can only be cached in one of definite n cache lines (called set - shown in Figure 2.2) which are identified by an index i which is calculated from the physical address of the data word. Thus, only the tag of n cache lines has to be checked. The correct data word can then be read from the cache line with the block offset b which is also calculated from the physical address as shown in Figure 2.2.

The average access time of a cache can then be calculated with  $t = t_{cache} + p_{miss} \cdot t_{DRAM}$  where  $p_{miss}$  is the probability that the desired data is not in the cache. In a good cache this probability converges against zero. Thus, from the processor point of view the memory is approximately as fast as the cache and has the size of the DRAM.

When data is written to the cache from the processor, the data can either be written to the main memory directly (*write-through*) or only when the cache line is replaced by another cache line (*write-back*). The latter will be used in this work as it reduces the number of accesses to the main memory.

The parameters of such a cache are replacement strategy, write back strategy, number of ways, data words per cache line, number of ways and the cache size. The number of sets can then be calculated from the parameters.

Typically, more than one cache level is used. The cache size increases with each cache level while the speed decreases. Each cache accesses the next cache level only in case of a cache miss. The cache that is connected directly to the processor is called L1 cache and other levels are named with increasing number. Thus, the cache that is directly connected to the main memory has the highest number.

2.2. Caches 23

#### 2.2.1. Cache Coherency

Note: Parts of this section have already been published in [61]. The marking of self-citation is omitted in order to improve the reading flow.

When the *write-back* strategy is used, modified cache lines are only written to the next cache level when that line is replaced. For example a L2 cache can contain outdated cache lines when the data has not yet been written back by a L1 cache. Those cache lines are called *dirty*. In single core systems this is not a problem, but in multi-core processors each core has a separate L1 cache which all access the main memory via a L2 cache. If two processors access the same cache line, it has to be ensured, that both caches use the same (coherent) data. Thus, the caches need to communicate which data they access.

In a **snoop based** cache system all caches on the same level listen to all transfers on the bus that connects them to the lower cache level in order to ensure coherency. In a **directory based** cache system a directory is maintained that contains which caches share which cache lines. With this information it is possible to send coherence messages only to relevant caches. This directory introduces overhead in timing and hardware costs but can reduce the communication between caches if cache lines are shared among a small amount of caches [29]. The system only benefits from this approach, if there are multiple communication channels between the caches on one level<sup>2</sup>. If there is only one bus, all other caches can not communicate while the coherence messages are exchanged and there is no benefit compared to a snoop based system [67].

Coherence Protocols To ensure coherence, the MSI (Modified Shared Invalid) protocol was developed. Here a cache is allowed to hold dirty lines only as long as no other cache needs this cache line. When another cache accesses the cache line, the new value has to be written back to the next lower cache level. The drawback of this protocol is, that a cache does not know whether the cache line resides in another cache as well. Thus, for every write access to a cache line every other cache has to be notified that it has to invalidate the cache line in case it also holds that cache line.

In order to overcome this issue, the *Exclusive* state was added in the MESI protocol. If a cache line is in the Exclusive state, no notification has to be sent to the other caches when the cache line is modified. Still if another cache wants to read a modified cache line it has to be written back to the next cache level. That way, shared cache lines are never dirty. The MOESI protocol introduces the *Owned* state which allows to share dirty cache lines. The dirty value is only written back when the cache line is replaced. This leads to even less write backs. All the protocols described above have in common that upon a write access a notification is sent and all other caches holding that cache line will invalidate this line. If the data is needed later on, it has to be reloaded.

<sup>&</sup>lt;sup>2</sup>Intels Xeon Phi X100 for example uses a distributed directory. All caches are connected via a bidirectional ring so that two transmissions between two caches in each case are possible.

The Dragon protocol [3] tries to avoid these reloads by not invalidating the cache line in all other caches upon a write access. Instead, the new value is directly provided. A more detailed description of MOESI and Dragon can be found in Chapter 11.

#### 3. Related Work

Recently many coarse and fine grained reconfigurable architectures have been researched. In most of them the memory interface is not covered in depth. Many approaches focus on accelerating applications with known regular memory access patterns. The data can easily be streamed into the accelerator so that the required data is available in the accelerator just in time (for example [8],[38],[60], [4], [65], [39]). Thus, many approaches can not handle irregular memory accesses efficiently. In other cases, the research is in early stage so that the problem of efficient memory accesses is simply not yet covered.

In the following, selected reconfigurable accelerators are described that either address general applications or represent milestones in their field of research. Afterwards, the memory subsystem of a Nvidia GPU is briefly described. In the third part of this chapter software approaches are described to increase the performance of the memory interface.

## 3.1. Reconfigurable Accelerators

Reconfigurable Accelerators can be divided into three categories. The first category are tightly coupled accelerators which are included into the execution stage of a processor. The second category are tightly coupled co-processors that share some hardware like caches with the processor but can execute at least simple loops autonomously. The third category are loosely coupled co-processors that only communicate with the processor via shared memory. In the following, relevant examples are given for all categories roughly sorted according to the date of publication.

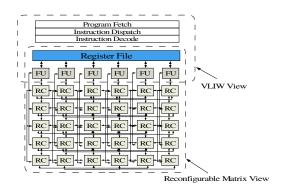

#### 3.1.1. ADRES

In ADRES (Architecture for Dynamically Reconfigurable Embedded Systems) a VLIW processor is coupled with a CGRA consisting of Reconfigurable Cells (RC) and FUs [48]. The Reconfigurable Matrix shares the FUs and the global register file with the VLIW processor as shown in Figure 3.1. ADRES supports simple control flow using predication and it realizes dynamic kernels as described above. The contexts are stored in a configuration RAM and can be switched within one cycle. Its configurations are generated by DRESC (Dynamically Reconfigurable Embedded System Compiler) [47] before runtime. DRESC supports modulo scheduling to exploit loop level parallelism [46] but the runtimes are high. The authors state that "it takes minutes to schedule a loop of medium size" (about 50 to 70 operands). The CGRA relies on the VLIW processor to access the memory. Several FUs are provided with access to a multiport L1 cache which is very costly [72]. In [45] a AVC decoder was implemented with ADRES.

3. Related Work

Figure 3.1.: ADRES architecture [48]

In this work the authors replaced the data cache with a software controlled data memory consisting of 4 SRAM banks that can be accessed in parallel. Using such a memory structure needs some improvements in the compiler and the ADRES architecture [44].

ADRES accelerates the VLIW processor by a factor 4.6[48]

| Requirement                | Realization                                    |

|----------------------------|------------------------------------------------|

| Flexible memory interface  | Access through a multiport L1 cache            |

| Parallel accesses possible | Yes                                            |

| Programmer transparency    | CGRA mapping is done automatically by the com- |

|                            | piler framework                                |

| Ease of use                | Programmed in C                                |

| Accelerates control flow   | Limited to simple constructs                   |

| Time of mapping process    | Before Runtime with slow compiler              |

Table 3.1.: ADRES summary

#### 3.1.2. Warp Processor

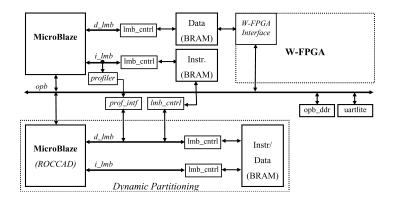

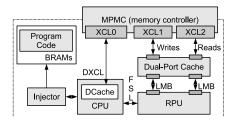

Warp processors use a profiler to identify time consuming kernels during runtime. Those kernels are then mapped to an FPGA [42]. Mapping kernels to an FPGA is a complex task due to the fine granularity. Thus, Lysecky et al. implemented a custom FPGA for Warp (W-FPGA) which can efficiently be routed with Riverside On Chip CAD tools (ROCCAD) [43]. Still, a dedicated MicroBlaze processor is used to do the mapping on chip during runtime as shown in Figure 3.2. The W-FPGA can access the data cache (Data BRAM in Figure 3.2) with the help of an address generator in the W-FPGA interface. This generator only supports regular address patterns, like linear array accesses. Kernels with irregular accesses cannot be mapped. A loop controller is able to support loops with a specific number of iterations and also break conditions[41].

Figure 3.2.: Warp architecture [42]

| Requirement                | Realization                          |

|----------------------------|--------------------------------------|

| Flexible memory interface  | Only regular patterns are supported  |

| Parallel accesses possible | Only single port access to the cache |

| Programmer transparency    | Yes                                  |

| Ease of use                | Programmed in c                      |

| Accelerates control flow   | Limited                              |

| Time of mapping process    | During runtime                       |

Table 3.2.: Warp processor summary

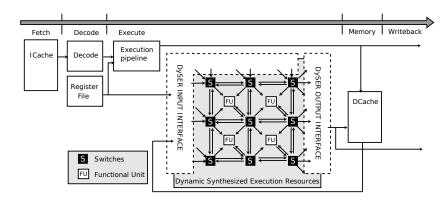

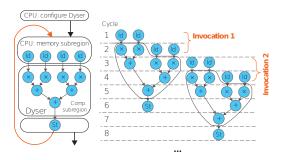

## 3.1.3. DySER

In DySER (*Dynamically Specialized Datapaths*) a CGRA is used to create static datapaths that speed up recurring code sequences. Figure 3.3 shows the overview of the processor with the integrated DySER CGRA in the execution stage. The DySER compiler creates specialized datapaths and maps them to the DySer CGRA before runtime. Special DySER instructions to invoke computations on DySER are included in the program code. Before the execution can start, the FUs and the switches of

Figure 3.3.: DySer architecture [23]

DySER have to be configured by a dyser\_init instruction[25]. The configuration bits are distributed between the FUs using the data flow network of the CGRA. The

28 3. Related Work

instructions dyser\_send and dyser\_load are used to load values from the register file or the memory respectively and send it to the DySER Input Interface. When all required data is available, the execution on DySER begins. When the execution is finished, the instructions dyser\_recv and dyser\_store are used to write values from the DySER Output Interface back to the register file (in the writeback phase) or the memory respectively. The execution on DySER can be pipelined as shown in Figure 3.4

Figure 3.4.: Pipelining on DySER [22]

Simple control flow like an if/else construct can be realized on DySER with the help of predication signals that are distributed among the FUs.

The DySER compiler can identify critical code regions automatically which leads to a speedup of about 3 compared to the OpenSPARC processor. The programmer has the possibility to support the compiler with pragmas which increases the performance by a factor of 2[27].

The authors of [27] implemented a prototype of DySER on an FPGA coupled with an OpenSPARC processor. They found that speculative loads / stores and address aliasing from the "early-stage design [...] proved overly complex" so that they were omitted in the prototype. This leads to very limited speedup in the SPECINT benchmarks (and even slowdown in one case). The following reasons can be identified:

- Only limited control flow is supported. DySER does not support data dependent control flow [22] and the prototype doesn't even support conditional memory accesses [27]. Loop carried dependencies can not be mapped efficiently.

- DySER relies on the processor to provide data from the memory as shown in Figure 3.4. No parallel accesses are possible an thus the DySER array has to wait on the data from the memory and the ability to pipeline iterations can not be exploited [27].

- Irregular memory accesses can not be mapped to the DySER array [22] efficiently.

RequirementRealizationFlexible memory interfaceIrregular memory accesses cannot be mapped efficientlyParallel accesses possibleCGRA relies on the host processor to load/store dataProgrammer transparencyPragmas can be usedEase of useProgrammed in cAccelerates control flowLimited to simple constructsTime of mapping processBefore runtime

Table 3.3.: DySER summary

#### 3.1.4. Layers CGRA

In the Layers CGRA[58] a memory layer is responsible to access the main memory as shown in Figure 3.5. P memory banks can be accessed in parallel. They execute load and store patterns which are activated by a state machine (see  $q\_state\_reg$  in Figure 3.5). Deriving efficient patterns for a kernel is a complex task as shown in [59]. The  $N^2$  PEs can access the memory banks via register clusters in the communication network. Each register is connected to one of the P hubs in the memory layer[57]. Each hub can access each memory bank via  $P \times P$  crossbar. The state automaton also controls the communication and the computation layers but apparently no feedback from the computation layer to the state automaton exists. Thus, it is not possible to realize data dependent control flow on the CGRA.

| Requirement                | Realization                                         |

|----------------------------|-----------------------------------------------------|

| Flexible memory interface  | Only patterns are supported                         |

| Parallel accesses possible | Memory banks allow parallel accesses (via an ex-    |

|                            | pensive $P \times P$ crossbar)                      |

| Programmer transparency    | Application has to be designed specifically for the |

|                            | Layers CGRA                                         |

| Ease of use                | Efficient memory access patterns have to be derived |

| Accelerates control flow   | Limited to simple constructs                        |

| Time of mapping process    | Before runtime                                      |

Table 3.4.: Layers CGRA summary

#### 3.1.5. Accelerating Megablocks

Paulino et al accelerate so called megablocks with a CGRA[53] called RPU (Reconfigurable Processing Unit) which is loosely coupled to a MircoBlaze processor. Megablocks are code sequences that are executed regularly. Typically, they contain several basic blocks from different branches. That means that it is possible to accelerate code with control flow if the control flow is regular and predictable, because the most common

3. Related Work

Figure 3.5.: Architecture of Layers CGRA [57]

branches are mapped to the RPU. If actually another branch is taken, the execution on the RPU has to be stopped. Before runtime an Instruction Set Simulator is used to extract megablocks from the execution traces. With this knowledge an application specific RPU and the corresponding configurations for all megablocks are generated [54]. The RPU accesses the main memory via a dual ported cache as shown in Figure 3.6. The cache is direct mapped and supports two parallel accesses. The accesses have

Figure 3.6.: Architecture of Paulino et al's approach [53]

a delay of four clock cycles but can be pipelined [53].

The RPU is loosely coupled with the CPU. This means that no coherence protocol can be implemented. Before the execution on the RPU starts, both the cache in the CPU and and the RPU cache are invalidated. In the RPU cache this can be done in one clock cycle whereas the CPU cache needs 192 clock cycles. When the execution

on the RPU is long enough, this time introduces no delay, as it can be done in the background. For kernels with small execution times, this means a significant overhead. A write through strategy is used in the RPU cache to ensure that the correct data will be loaded into the CPU cache afterwards.

| Requirement                | Realization                                        |

|----------------------------|----------------------------------------------------|

| Flexible memory interface  | Yes, but with high delay and no coherency support. |

|                            | Thus, invalidation is needed                       |

| Parallel accesses possible | Two parallel accesses are possible                 |

| Programmer transparency    | No programmer interaction needed                   |

| Ease of use                | RPU and configurations have to generated before    |

|                            | runtime with the help of traces                    |

| Accelerates control flow   | Limited to the most common control flow path       |

| Time of mapping process    | Before runtime                                     |

Table 3.5.: Accelerating megablocks summary

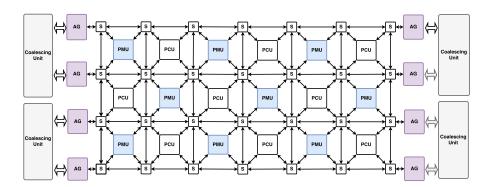

#### 3.1.6. Plasticine

Plasticine [56] is a relatively new approach which targets parallel patterns. A mesh constructed from Pattern Compute Units (PCU) and Pattern Memory Units (PMU) is connected via switches as shown in Figure 3.7. Each PCU consists of a small CGRA that computes inner loops and supports parallel data transfers in order to perform SIMD instructions. Within this CGRA different rows are used in parallel to exploit loop level parallelism and the columns represent pipeline stages.

Figure 3.7.: Architecture of Plasticine [56]

PMUs contain scratchpad memories that have to be managed by the programmer to buffer data on chip. Ideally, those scratchpads are not used and the produced data is directly forwarded to the next PCU. The off chip DRAM memory can be accessed via four channels. Address generators are used to generate the read and write addresses according to the input and output memory access pattern of the accelerated parallel pattern. In case of sparse memory access patterns, a coalescing unit combines several

3. Related Work

requests in order to minimize the DRAM accesses. Otherwise, burst requests are issued.

As this approach focuses on parallel patterns, no sophistic control flow mechanisms are needed. Tokens are used to ensure correct execution when loop carried dependencies exist and a simple enable signal is used in streaming applications.

Plasticine is programmed using the parallel pattern based language DHDL (Delite Hardware Description Language). Supported patterns are for example map or fold. The pattern map takes a vector  $a_i$  of length n as inputs and calculates an output vector  $b_i = f(a_i)$  where the function f is independent in each case. The pattern fold first calculates a map and then reduces the output vector  $b_i$  to a scalar value using the function z = g(x, y) multiple times.

The authors compared the performance and energy consumption of Plasticine to a Stratix V FGPA. They report a 95x improvement in performance and a 77x improvement in performance per Watt[56]. The mapping process is only a matter of minutes on Plasticine while it can take up to hours to map a design on an FPGA.

While this approach is very promising to accelerate parallel patterns, it cannot unfold its potential to accelerate applications with irregular memory access patterns or data dependent control flow as it uses counters to control the loop iterations.

| Requirement                | Realization                                     |

|----------------------------|-------------------------------------------------|

| Flexible memory interface  | Coalescing Units combine sparse memory accesses |

| Parallel accesses possible | DRAM can be accessed via four channels          |

| Programmer transparency    | Programmer has to use parallel patterns         |

| Ease of use                | Programmed in DHDL                              |

| Accelerates control flow   | Regular nested loops are supported              |

| Time of mapping process    | Before runtime                                  |

Table 3.6.: Plasticine summary

#### 3.1.7. Accelerating x86 Instruction Streams

Brandalero and Beck proposed a CGRA that is tightly coupled to a superscalar processor with out of order execution as shown in Figure 3.8 (a). When the code is executed for the first time on the processor, it will be executed regularly on the superscalar processor. A Code Transformation (CT) module observes the execution and generates CGRA configurations that describe static data graphs for recurring kernels. The configurations are stored in a configuration cache. When the kernel is executed the next time, it is checked in the fetch stage whether there is a CGRA configuration in the configuration cache. If yes, the configuration and input values from the register file are loaded and the kernel is executed on the CGRA. When the execution is finished, the results are committed in the register file.

The structure of the CGRA is shown in Figure 3.8 (b). The CGRA is organized in rows and columns. The rows contain different PEs like adders or load units. The PEs of two

Figure 3.8.: Architecture of Brandalero and Becks approach[7]

columns are connected by crossbar networks (marked with x). Data always flows from left to right. The delay of an adder is 1/3 of a clock cycle. So one level that consists of three columns corresponds of one clock cycle. If an operation like multiplication has a latency longer than the addition, it spans over several columns or even levels.

The CGRA only consists of combinatorial logic and has no registers. That means, that if a kernel is mapped onto n levels of the CGRA, the results can be read from the results buffer only after n cycles. The more levels the CGRA has, the bigger are the kernels that can be mapped. At the same time, the energy consumption increases. The authors found that a CGRA with 30 levels give the best trade-off. Two load units (4 cycles latency) and one store unit (1 cycle latency) access the 3-level cache hierarchy of the base processor which has a latency of 4 clock cycles. The load store units maintain a request queue to avoid pipeline stalls.

Control flow is realized with speculation. Several control flow paths are mapped onto the CGRA but only the results of valid paths are committed. Similar approaches are described in [68] and [5]

|                            | v.                                   |

|----------------------------|--------------------------------------|

| Requirement                | Realization                          |

| Flexible memory interface  | Yes                                  |

| Parallel accesses possible | Yes via two loads and one store unit |

| Programmer transparency    | Transparent for the programmer       |

| Ease of use                | Programmed in C                      |

| Accelerates control flow   | Simple control flow is supported     |

| Time of mapping process    | During runtime                       |

Table 3.7.: Acceleration of x86 instruction streams summary

3. Related Work

## 3.2. Graphic Processing Units

As the name suggests, graphic processing units (GPU) are originally used to speed up image processing for example for computer games. Yet, GPUs are more and more used to accelerate code from other applications domains like machine learning. Those application domains have in common that huge amounts of data have to be processed quickly. Normally, the algorithms include a huge amount of parallelism on thread and loop level. GPUs are designed to exploit this parallelism. GPUs target other goals than this work but a huge challenge of the GPU design is to load the data into the processing elements quickly. Thus, it is helpful to have a quick look at the memory subsystem of a GPU.

Figure 3.9.: Architecture of a Nvidia Fermi Streaming Multiprocessor [52]

Figure 3.9 shows the architectural overview of the Nvidia Fermi Streaming Multiprocessor (SM). Each SM consists of 32 Cuda cores (including integer and float ALUs), 16 Load/Store units and 4 Special Functional Units (SFU) to calculate for example trigonometric functions or roots. The Nvidia GPU consists of 16 SMs which share a L2 cache, which results in 512 Cuda Cores in one Fermi GPU. Newer Versions like the Volta GPU eva have up to 5120 Cuda Cores.

The SM contains a L1 cache which can also be used as a software managed shared memory [52]. Using shared memory is highly efficient but requires programming effort. Using the L1 cache instead trades performance against less programming effort and allows efficient accesses to addresses that are not known beforehand. The programmer

can chose an approach depending on the software design goal. Nvidia states that "While shared memory remains the best choice for maximum performance, the new Volta L1 design enables programmers to get excellent performance quickly, with less programming effort"[51]. This suggests that using L1 caches in this work is a good choice to accelerate irregular applications with low programming effort.

It has to be noted that GPUs have a dedicated DRAM. Thus, every data that has to be processed has to be copied from the processor main memory to the GPU memory and results have to be copied from the GPU memory back to the main memory.

# 3.3. Compiler-based Approaches

Some research focuses on the smart mapping of memory instructions to PEs in order to improve the memory access times. Little research projects focus on this topic, as most CGRAs are used to accelerate streaming applications and assume the data is available just in time. In the following two examples are explained in more detail.

#### 3.3.1. Alleviating the Memory Bandwidth Bottleneck

The authors of [10] assume a two dimensional CGRA in which all PEs are connected to a L1 cache via one data bus. Each PE has a local RAM to store intermediate values and operands. In this work the local RAMs will be used as L0 cache. If desired data lies in one of these RAMs, the mapping algorithm can either load it from the L1 cache or from a local RAM. If it is loaded from the RAM, routing delay might be introduced when the PE holding this data is not directly connected to the PE that requires that data. If it is loaded from the L1 cache, the data bus is blocked for other accesses. The mapping tool comes to a decision based on a cost function that evaluates routing and cache access delays.

This procedure decreases the load on the data bus but it only works if data is reused in the control and data flow graph that is mapped to the CGRA. The authors show that this procedure works well when loops are unrolled, because this results in more data reuse in the control and data flow graph. This mechanism to decrease the load on the L1 cache is also called load forwarding. This will also be used in this work as shown in Chapter 10.

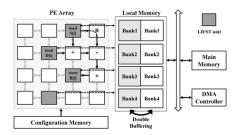

#### 3.3.2. Memory-Aware Application Mapping

The authors of [35] use the same technique to minimize the number of memory accesses. In contrast to the previous approach they assume a different CGRA structure. Here selected PEs are connected to different memory banks which are filled with double buffering as shown in Figure 3.10.

The compiler tries to classify the kernel that is mapped to the CGRA. If a kernel is compute intense, it is mapped in a way that routing paths on the CGRA are short even

3. Related Work

Figure 3.10.: Architecture of the CGRA used to do memory-aware application mapping [35]

if this results in a suboptimal memory bank usage. If the kernel has many memory operations, longer routing paths are allowed in order to optimize the memory bank usage as described above. This is done by a compiler that tries to minimize duplicates of arrays in the banks so save memory by applying smart mapping of memory instructions to the corresponding PEs.

### 3.4. Summary

It can be seen that none of the described approaches satisfies all requirements mentioned above. Some approaches focus solely on regular memory accesses while others rely on the single cache of the host processor. Only Brandalero and Becks approach fulfills all requirements but only limited control flow is supported.

Four key findings can be drawn from the study of related work:

- 1. Using caches is mandatory if irregular memory accesses are to be supported.

- 2. Using a single cache is not sufficient as only one word can be read in one clock cycle. Multi-port caches are too expensive (see ADRES )[72]. Instead multiple caches have to be used.

- 3. Coherence not only between the caches of the accelerator but also in the host processor has to be ensured (see the acceleration of Megablocks [53]).

- 4. The mapping algorithm can support the performance of the memory subsystem as shown in [35] and [10].

# 4. Description of Our Approach

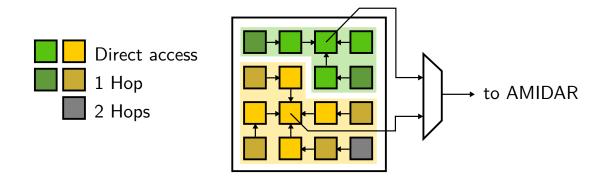

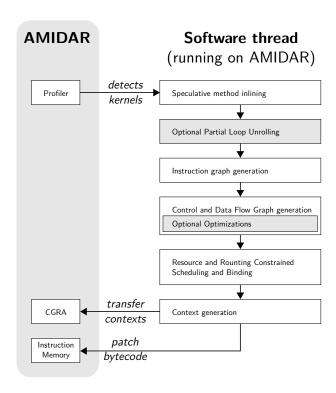

In this work a CGRA based accelerator will be tightly coupled to a Java processor. During runtime a profiler will identify hotspots in the code that consume substantial runtime. These kernels will then be mapped automatically to the CGRA during runtime in order to accelerate the execution. The mapping algorithm will run as a separate

Figure 4.1.: Overview over the whole system

task on the Java processor totally transparent for the programmer as shown in Figure 4.1. Changing program flow is detected by the profiler and new kernels can always be mapped to the CGRA.

Coupling the CGRA based accelerator to a Java processor has two benefits: First, the programmer does not have to learn any specialized language like Cuda to make use of the accelerator. Second, analyzing Java byte code during runtime in the mapping process is less complex than analyzing for example native ARM machine code. Properties such as the independence of two memory operations can be proved much easier as shown in Section 10.2.

The used CGRA was specifically designed to be able to execute kernels with complex data dependent control flow autonomously.

As mentioned before, it is a goal to accelerate arbitrary code independent of the application or even application domain. Thus, at design time of the accelerator the code structure and the memory access patterns of the application are not known. This leads to several challenges that will be discussed in the following sections.

#### 4.1. Problem Formulation

Designing the memory subsystem independently of the rest of the system is not possible as we will see in the following. This section describes the problems and challenges that have to be solved in order to be able to evaluate the whole system.

#### 4.1.1. Full Stack Main Memory Interface Optimization

Accessing the main memory is the bottleneck in both performance and energy consumption for many applications [70].

Many accelerator techniques such as Plasticine [56] heavily rely on a priori knowledge of the access patterns. This knowledge is used to implement streaming engines that load the desired data and transfer it to the accelerator in time. Other approaches like Layers CGRA [59] even rely on the programmer to load the data and distribute it in different memory banks in the accelerator to enable efficient parallel memory accesses.

As mentioned above, in this work the memory access patterns are not known a priori and can be irregular. Thus, the CGRA will be equipped with direct access to the memory so that the CGRA can load the desired data on demand. Multiple caches will be used to allow parallel accesses to the memory with small average memory access times. Prefetching will be used to fill the caches efficiently.

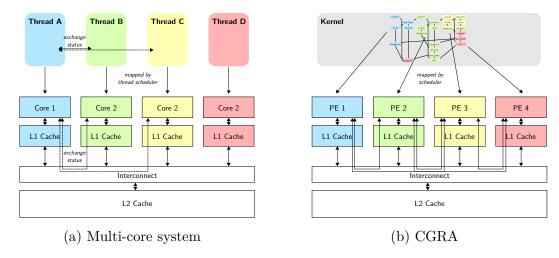

Memory subsystems of multi-core systems have been studied thoroughly but they have different characteristics. Several software threads are designed so that they use as little common variables as possible to exchange for example status messages. They will mostly run independently and can be optimized independently. Those threads will be mapped by a thread scheduler to the different cores as shown in Figure 4.2 (a). As those threads are normally communicating only sparsely, the communication between the cores and the number of shared cache lines is low. Hence, the load on the interconnect between the L1 caches is low. The design of the memory subsystem, the thread scheduler and the threads itself are almost decoupled and each part can be optimized independently.

When a kernel is mapped to the CGRA, the nodes of a complex graph are mapped to the different PEs as shown in Figure 4.2 (b). Those nodes have strong dependencies and they may access similar memory regions which results in many shared caches lines. This increases the load on the interconnect between the L1 caches tremendously. The decisions that are made during the mapping process strongly influence the performance of the memory subsystem. For example, when the mapping algorithm is not able to prove that two memory accesses are independent, the capability of the memory subsystem to allow parallel memory accesses cannot be exploited. Also, it is possible to map two memory accesses to adverse PEs so that many cache misses occur as described later in Section 11.2. Thus, unlike in multi-core systems, the several parts can not be optimized independently. Instead the whole system consisting of kernel detection, graph generation, mapping process and memory subsystem has to be optimized jointly. This increases the design space tremendously. Implementing and debugging all options in

Figure 4.2.: Comparision of memory subsystem usage

hardware is a tedious task and mapping such a design to an FPGA takes tremendous amount of time. Thus, a fast and accurate simulation framework is needed for an efficient design space exploration.

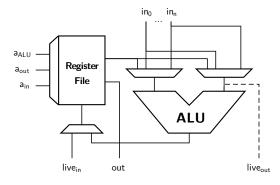

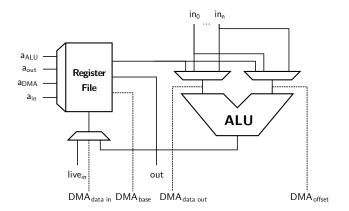

#### 4.1.2. Local Variables Interface

Code Example 1 shows the code to find the number of the first 42 array elements that are greater than 314. It can be seen that before the execution of the loop the potential accelerator has to know the values of the variables array and cnt. Those variables are called *Live-In* variables. Additionally, the values of the constants 1, 42 and 314 have to be made known to the accelerator.

Code Example 1: Code Example showing *Live-In* Variables (green), *Live-Out* variables (blue) and Constants (yellow)

```

for (i =0; i < 42; i = i + 1;) do

2 | if (array [i] < 314) then

3 | cnt = cnt + 1;

```

When the execution is finished, the value of the variable cnt has to be transferred from the accelerator back to the host computer. Such variables are called Live-Out variables. Transferring Live-In and Live-Out variables and constants between accelerator and host computer results in an overhead that is negligible for loops with long runtimes but has a large impact on the performance of the accelerator for smaller loops. The Live-In and Live-Out variables are different for each kernel. Thus, it is important to implement an efficient and flexible interface between the Local Variable Memory of the host computer and the accelerator. A thorough discussion can be found in Chapter 8.

#### 4.1.3. Context Memory Interface

The CGRA configuration for a kernel is stored in several contexts. Once, those contexts are loaded in the context memory of the CGRA, they can be switched in a single cycle. Still, loading the contexts in the memory generates some overhead. Thus, preloading the contexts parallel to the normal code execution is desirable to mask this overhead. This problem is independent of the design of the memory subsystem and it is not the focus of this thesis. Therefore, it is only covered briefly in this work.

#### 4.2. Thesis Outline

This chapter concludes Part I of this thesis which contains the introduction.

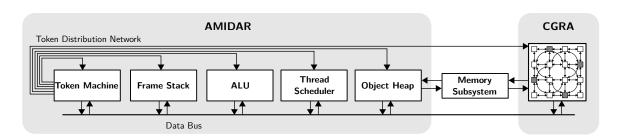

In the next Part, the existing system is described with several enhancements that were implemented during this work. Chapter 5 explains the basic concepts behind the programming language Java. Chapters 6 and 7 describe the host processor AMIDAR and the CGRA which is used as accelerator. Afterwards, Chapter 8 describes the interface between both. This part is concluded with the description of the kernel mapping algorithm in Chapter 9.

Part III covers the optimization of the memory subsystem. Chapter 10 describes the high level compiler optimizations that are included in the kernel mapping algorithm in order to exploit the capabilities of the memory subsystem fully. Afterwards, Chapter 11 describes the actual memory subsystem including the cache architecture and coherence protocols. Chapter 12 describes *Lookahead Prefetching* which improves the performance of the memory subsystem further. This part is concluded in Chapter 13 with a description of the implemented memory subsystem.

Finally, the whole system is evaluated in Part IV with the AMIDAR simulator which is described in Chapter 14. Chapter 15 describes the benchmarks and the evaluated CGRA instances while Chapter 16 contains the actual design space exploration. The results are shown in Chapter 17. This work is then concluded in Chapter 18 with a summary and an outlook on future works.

# Part II. System Description

#### 5. Java as Instruction Set Architecture

This chapter aims to explain the basic processes behind the programming language Java rather than explaining the programming language itself, as it is already well known. Further details can be found in [21].

First, the Java memory system will be explained because this has some impact on the design oft the memory subsystem of the whole system including the AMIDAR processor and the CGRA based accelerator. Afterwards, information about the Java bytecode and method calls is given. This is necessary to understand the process that maps Java bytecode to the accelerator.

#### 5.1. Java Memory System

The Java memory system is divided in the parts Local Variable Memory, Stack Memory and the Heap Memory. As the name suggests, the Local Variable Memory stores local variables. In contrast to that, the Heap Memory contains all objects and arrays<sup>1</sup>. Operands of an operation can be loaded both from Local Variable Memory or Heap Memory. Values will be pushed to the Stack Memory prior to the execution of the operation. When the operation is executed, the operands are popped from the stack and the result is pushed. Afterwards, the value result is again popped from the Stack Memory and stored in the Local Variable Memory or Heap Memory, respectively. Both Local Variable Memory and Stack Memory are located inside of the processor and can be accessed directly. The heap is typically too big to be part of the processor. Thus, it is for example realized as DRAM.

The code example shown in Listing 5.1 is used to explain the memory accesses.

#### 5.1.1. Heap Memory

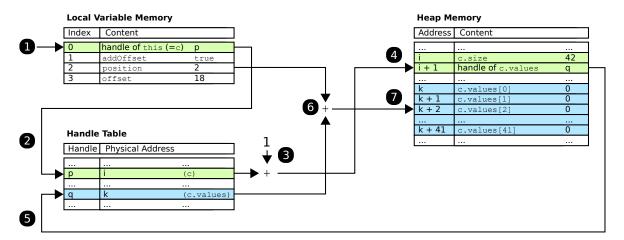

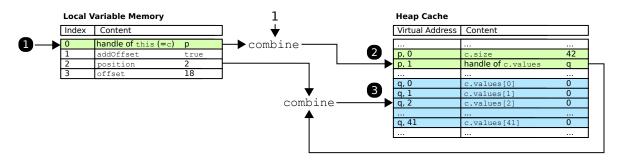

In this work memory objects are identified by a unique handle. The *Heap Memory* is then addressed indirectly with the handle of the memory object and the offset. A dedicated memory called *Handle Table* stores the physical addresses of each memory object<sup>2</sup> as shown in the lower left corner of Figure 5.1. With  $addr = physical \ address + offset$  the desired object field or array element can be loaded. This addressing scheme will be called *virtual addressing* in the remainder of this work. The advantage of this virtual addressing scheme is that the Garbage Collection is eased as described in Section 5.1.4. Figure 5.1 shows on the right side how the object c (green) and the array value (blue) are stored in the heap after the constructor call in line 11 of Listing 5.1.

<sup>&</sup>lt;sup>1</sup>In the remainder of this work the term *memory objects* is used to refer to both arrays and objects.

<sup>&</sup>lt;sup>2</sup>Note that the *Handle Table* also contains additional information like object/array size or class type.

Listing 5.1: Memory access example

```

class Container{

int [] values;

2

int size;

3

4

public Container(int size){

this.size = size;

this.values = new int[size];

8

9

public static void main(String [] args){

10

Container c = new Container(42);

11

12

System.out.println(c.getValue(true, 2));

13

}

14

15

public int getValue(boolean addOffset, int position){

16

int offset = 18;

if(addOffset){

return values[position] + offset;

19

} else {

20

return values[position];

21

}

23

24

```

#### 5.1.2. Local Variable Memory

Local variables are variables that are only defined within one method. The main method in Listing 5.1 for example has the local variables args and c. The *Local Variable Memory* is simply addressed by an index. In object methods the handle of the this object is stored at index zero followed by the method parameters and all local variables that are declared in the method. Figure 5.1 shows all local variables of the method getValue in the upper left corner.

When a new method is called, the *Local Variable Memory* has to be saved so that the new *Local Variable Memory* can be initialized. When this method returns the old *Local Variable Memory* has to be restored. The same holds for the *Stack Memory*.

#### 5.1.3. Heap Access Example

In order to obtain the value of the expression values[position] in line 19 in Listing 5.1 the following steps (also shown in Figure 5.1) have to be executed when getValue is called on object c in line 13:

1. Load handle of c from Local Variable Memory index = 0

Figure 5.1.: Heap Memory access example without cache

- 2. Load physical address of c from Handle Table (= i)

- 3. Calculate i + 1 to get the address where the handle of c.values is stored

- 4. Load the handle of c.values from the Heap Memory

- 5. Load physical address of c.values from Handle Table (= k)

- 6. Calculate k + position to get the address of the values [position]

- 7. Load values [position] from the Heap Memory

From this example it is clear that heap accesses are expensive and it is beneficial the to use a cache for the *Heap Memory* that is virtually addressed with a combination of handle and offset.

#### 5.1.4. Garbage Collection

In Java the programmer is relieved of the task to free memory manually. The Garbage Collector task is executed repeatedly and finds dead objects that can not be accessed by the running program because there are no references from the running program to the object any more. Those dead objects are deleted and the memory space can be reused. Over time this leads to a fragmented memory. Thus, the Garbage Collector moves living objects in the memory to defragment it. When objects are moved in the memory, all references to the original memory address have to be updated. Here the advantage of the virtual addressing scheme becomes obvious. In that case the only reference to the physical memory address is in the corresponding entry of the Handle Table. If the objects were addressed directly with physical addresses, every reference to that object has to be updated.

#### 5.2. Java Bytecode

Unlike other programming languages, Java is not compiled to machine code but to Java bytecode which is typically run on a virtual stack machine. For each Java class a \*.class file containing the Java bytecode is created. For many bytecodes the naming follows a simple scheme: {data type, operation Name}. Data type can for example be I (for Integer) or F (for Float). Operation names are are for example ADD or LOAD. This results for example in the bytecodes IADD, ILOAD, FADD or FLOAD. Bytecodes are 8-bit wide and can have a variable number of 8-bit parameters, which are determined during compile time and stored in the instruction code directly behind the bytecode. The bytecodes can coarsely be categorized into four groups:

# • Method calls and jumps

Examples:

- INVOKEVIRTUAL Pops the method parameters from the Stack Memory, saves

Local Variable Memory and Stack Memory and enters a new object method.

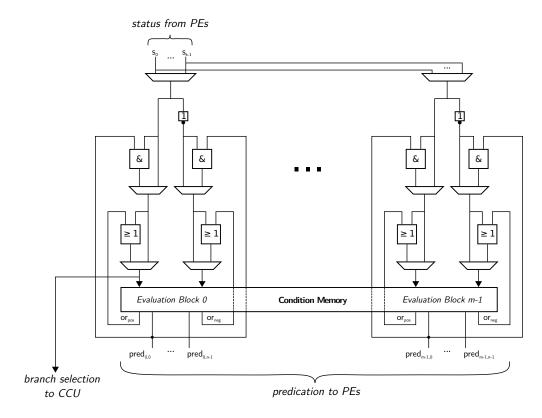

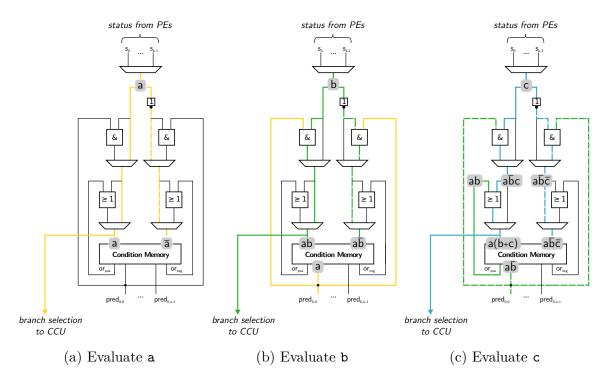

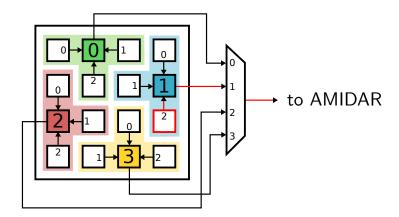

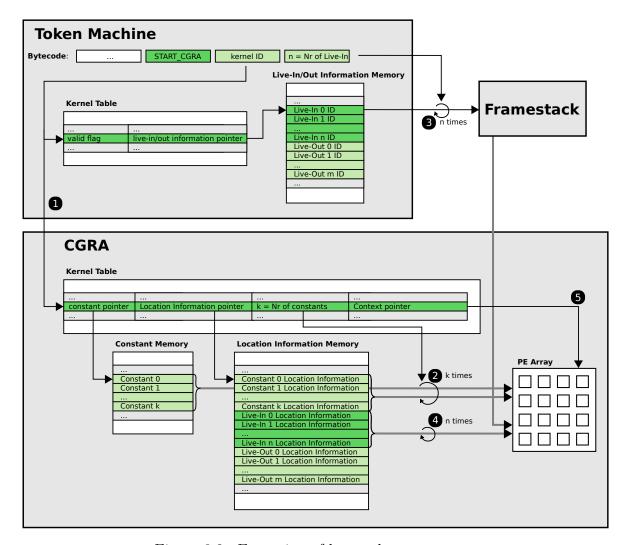

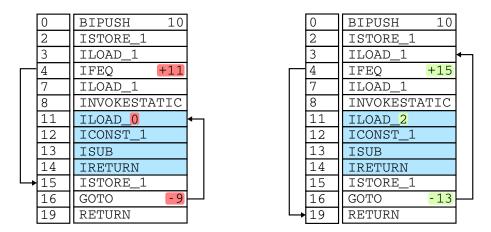

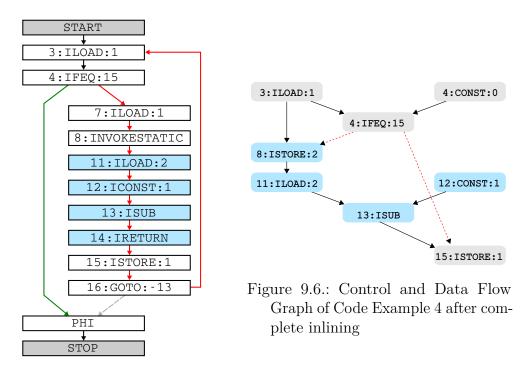

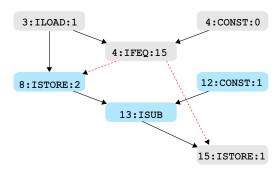

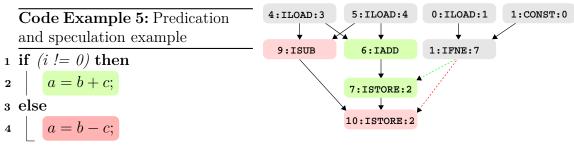

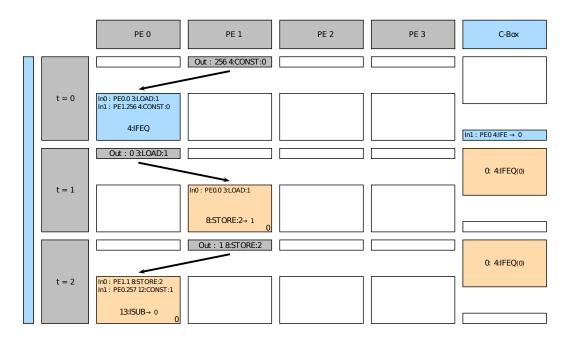

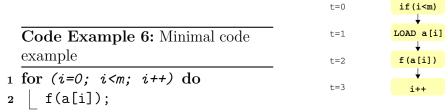

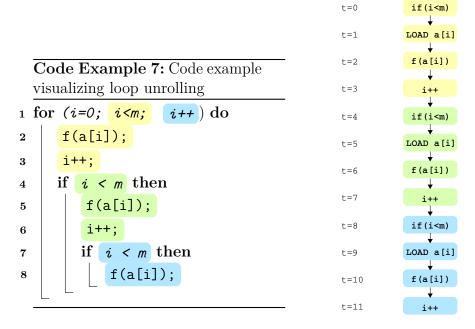

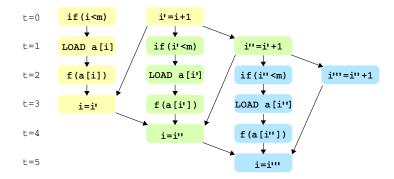

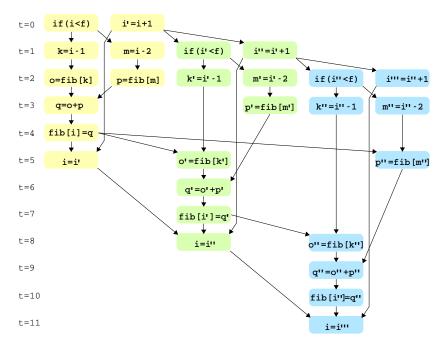

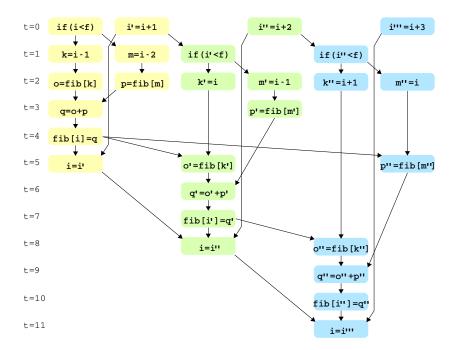

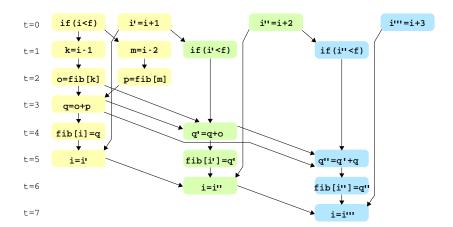

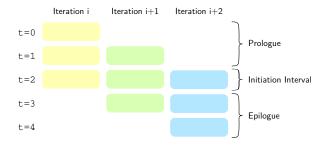

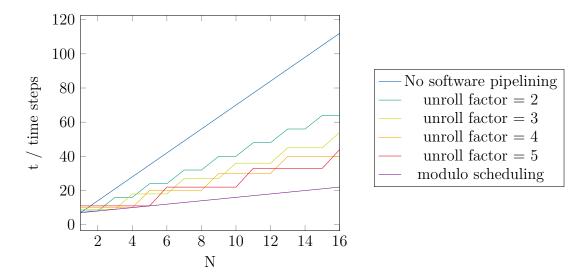

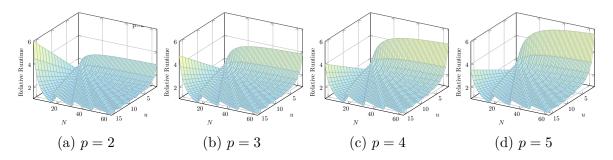

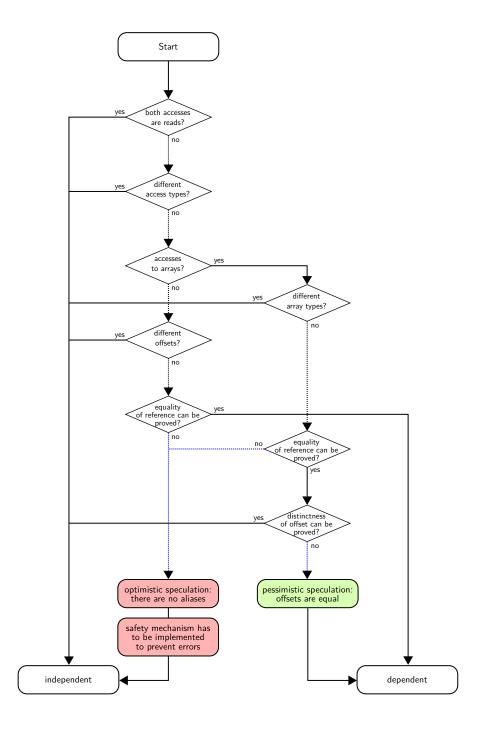

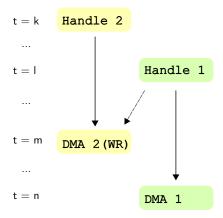

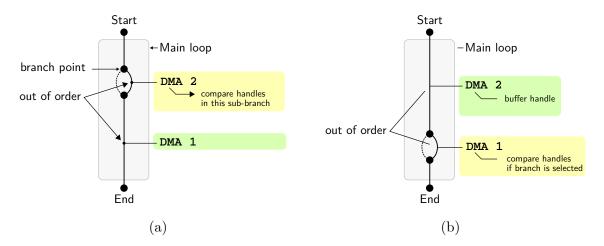

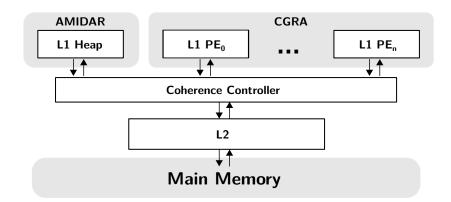

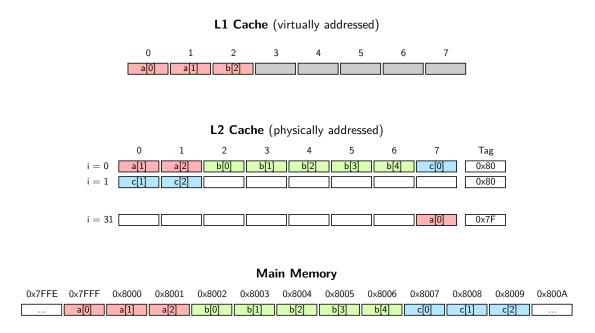

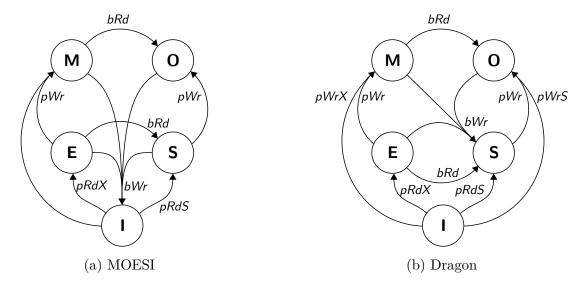

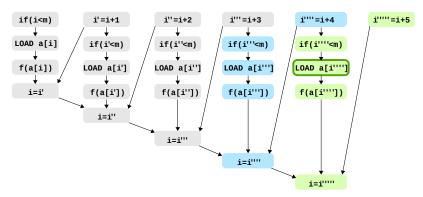

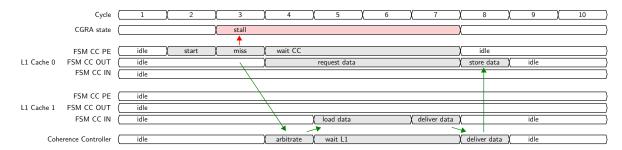

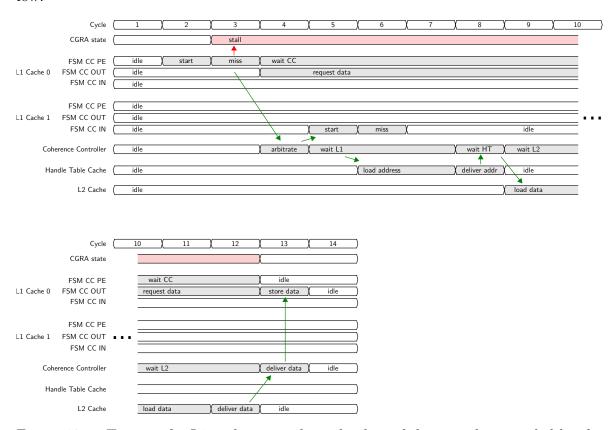

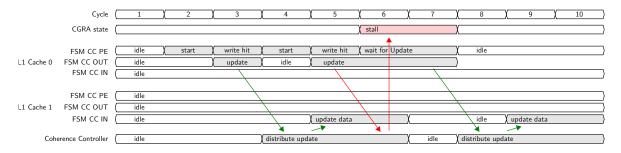

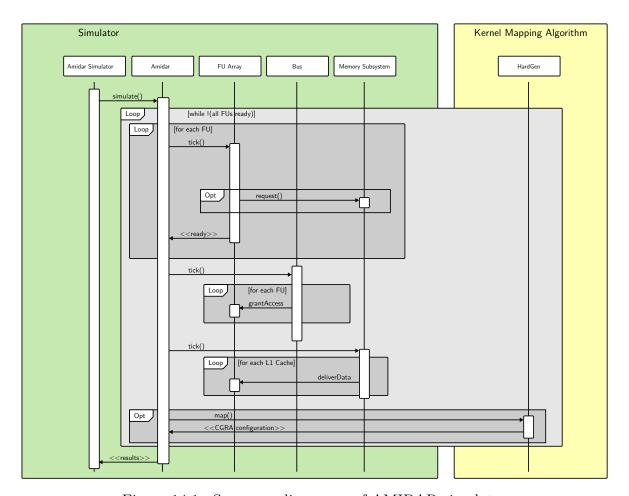

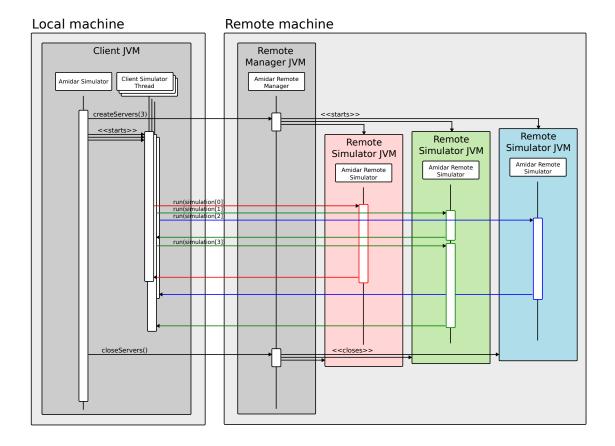

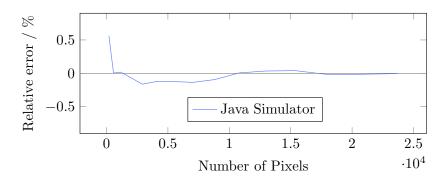

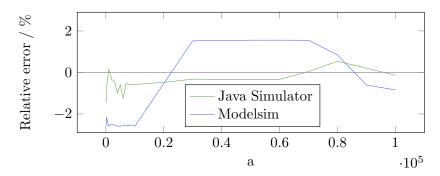

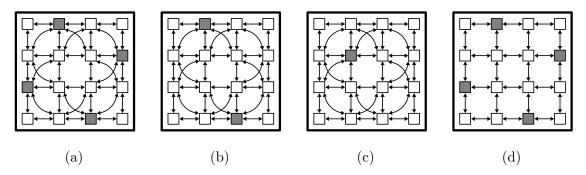

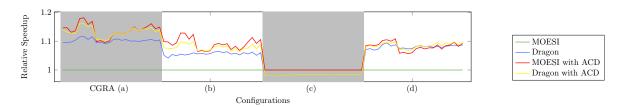

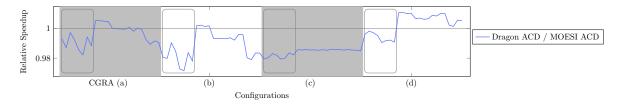

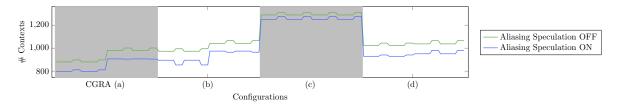

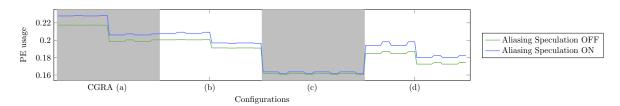

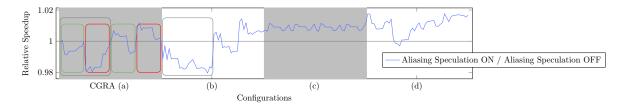

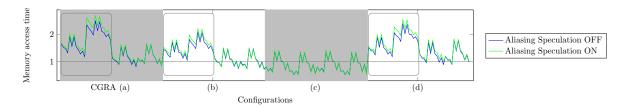

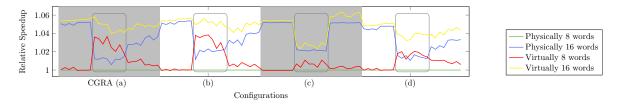

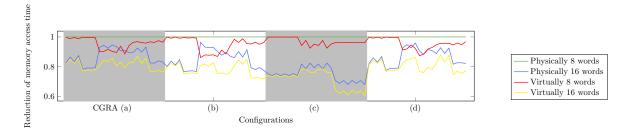

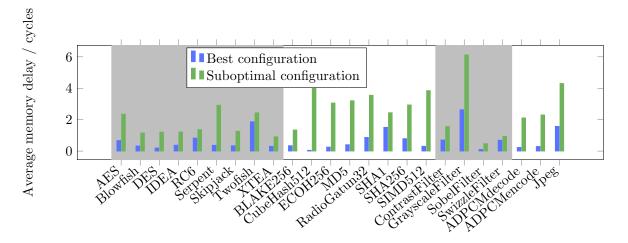

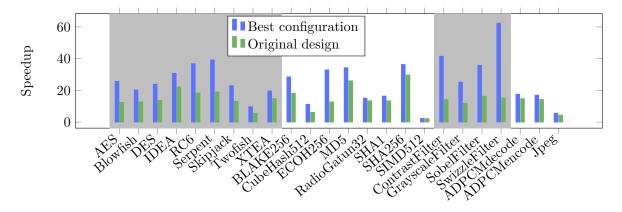

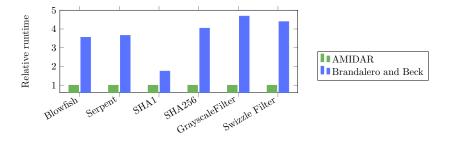

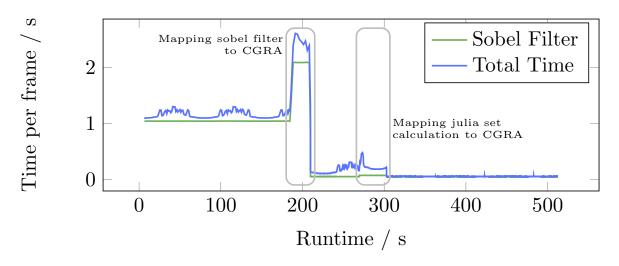

- IRETURN Ends the current method, restores Local Variable Memory and Stack Memory and returns an integer value by pushing it onto the restored Stack Memory.