# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Walder, Sam

Title:

Mitigation of The Influence of Parasitic Elements in Wide-Bandgap Power Converters

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

#### Take down policy

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

· Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Mitigation of The Influence of Parasitic Elements in Wide-Bandgap Power Converters

By

SAMUEL WALDER

Department of Electrical and Electronic Engineering UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Engineering.

September 2018

Word count: 61,507

ABSTRACT

This work undertakes a detailed investigation of the Mitigation of The Influence of Parasitic Elements in Wide-Bandgap Power Converters. It primarily considers techniques applied to Silicon Carbide (SiC) Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) in low voltage (<600 V) power converters.

It is shown that parasitic circuit elements have a broad range of negative impacts on the performance of Wide Band Gap (wide band gap) power converters. Analysis of an experimental set-up is performed to create an accurate simulation model which is then validated against experimental results. A parametric analysis of the parasitic Printed Circuit Board (PCB) elements is performed highlighting the sensitivity of the converter's performance to these.

State-of-the-art techniques for mitigating the influence of the parasitic elements are reviewed and a method for incorporating a small inductor into the converter output for mitigation of the load parasitics is proposed.

Considerable analysis is dedicated to the identification of the temporal source of frequency domain characteristics of power converter waveforms. The technique of successive differentials is demonstrated as a tool for analysing time domain waveforms and identifying key noise generating features.

The largest portion of this work proposes smoothed waveform transitions as an important technique in the mitigation of the influence of the parasitic elements of the converter. They are first defined, and a range of analytical tools considered. Following this they are shown to be able to provide significant performance improvements in terms of the interactions with parasitic elements of the converter.

Finally, methods for the practical realisation of waveform smoothing are explored, showing that the predicted performance improvements can be realised. Additional work is performed on the creation of gate drive systems with low complexity that realise the suggested performance improvements.

Dedicated to my parents and Meg

#### ACKNOWLEDGEMENTS

I would like to thank my primary supervisor Prof. Xibo Yuan for his continuing support throughout not only my PhD, but also my masters project. The technical discussion and focus on new areas of research has helped to shape my work into what it is now. I would also like to thank my secondary supervisors for their academic support.

A also owe a massive thank you to all the members of the Electrical Energy Management Group at the University of Bristol for the quality of technical discussion, help with experimental work, advice on related issues, and their general support. In particular, I owe thanks to Dr. Niall Oswald for supporting the technical content of my early work, to Dr. Philip Anthony for our technical discussions, to Dr. Apollo Charalambous for his support with frequency domain analysis, to Dr. Jason Yon for his practical knowledge and support, to Mr. Jeremy Dalton for our technical discussions, and to Dr. Harry Dymond for his expert advice on equipment and experimental implementation.

My thanks also goes to all of the technical support staff throughout the faculty of engineering who have offered expert advice and help through my experimental work. In particular I would like to thank Mr. Richard Walker for his sound advice in device procurement, and Mr. Mike Penney for his knowledge of flexible drive couplings.

I would like to thank the schools outreach and student liaison manager Ms Caroline Higgins for her support in a broad range of non-technical matters relating to this work.

I am extremely grateful to the EPSRC for providing the funding that supported this work.

Finally, I would like to thank my family and friends for their unwavering support, encouragement, and understanding through the 8 years that have lead to this work.

### **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

### TABLE OF CONTENTS

| Abstra       | ct                                          | i                                                                      |

|--------------|---------------------------------------------|------------------------------------------------------------------------|

| Dedica       | tion                                        | iii                                                                    |

| Ackno        | wledgements                                 | v                                                                      |

| Declar       | ation                                       | vii                                                                    |

| List of      | Tables                                      | xiii                                                                   |

| List of      | Figures                                     | xv                                                                     |

| List<br>List | ries<br>ssary                               | xxiii                                                                  |

| Memorandum x |                                             | XXV                                                                    |

|              |                                             |                                                                        |

| Public       | ations                                      | xxvii                                                                  |

|              | ations         coduction         Background | xxvii<br>1<br>1<br>1<br>3<br>5<br>7<br>8<br>10<br>10<br>11<br>12<br>14 |

|   |                                                                                                                     | 2.1.3 Simulation and Modelling                                                                                                                                                                                                                                                                                                                                                             | 21                                                                                                        |

|---|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

|   | 2.2                                                                                                                 | Parasitic Elements of a Circuit                                                                                                                                                                                                                                                                                                                                                            | 22                                                                                                        |

|   |                                                                                                                     | 2.2.1 Device Parasitics                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                                        |

|   |                                                                                                                     | 2.2.2 Interaction with Other Converter Parasitics                                                                                                                                                                                                                                                                                                                                          | 24                                                                                                        |

|   |                                                                                                                     | 2.2.3 Interaction with Load Components                                                                                                                                                                                                                                                                                                                                                     | 26                                                                                                        |

|   |                                                                                                                     | 2.2.4 Measurement Techniques                                                                                                                                                                                                                                                                                                                                                               | 27                                                                                                        |

|   |                                                                                                                     | 2.2.5 Methods of Parasitic Extraction                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                                        |

|   |                                                                                                                     | 2.2.6 Mitigation                                                                                                                                                                                                                                                                                                                                                                           | 31                                                                                                        |

|   | 2.3                                                                                                                 | Electromagnetic Interference                                                                                                                                                                                                                                                                                                                                                               | 33                                                                                                        |

|   |                                                                                                                     | 2.3.1 Modelling and Analysis                                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 38                                                                                                        |

|   | 2.4                                                                                                                 | Active Gate Driving                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                        |

|   |                                                                                                                     | 2.4.1 Advantages of Active Gate Driving                                                                                                                                                                                                                                                                                                                                                    | 39                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 41                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 43                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                                        |

|   | 2.5                                                                                                                 | Limitations of The Literature and Research Opportunities                                                                                                                                                                                                                                                                                                                                   | 47                                                                                                        |

|   |                                                                                                                     | 2.5.1 Wide Band Gap Semiconductors                                                                                                                                                                                                                                                                                                                                                         | 47                                                                                                        |

|   |                                                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                          | 48                                                                                                        |

|   |                                                                                                                     | 2.5.3 Electromagnetic Interference                                                                                                                                                                                                                                                                                                                                                         | 48                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            | 49                                                                                                        |

|   |                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                           |

| 3 | Ana                                                                                                                 | ysis of the Performance of Power Converters Under the Influence of Par-                                                                                                                                                                                                                                                                                                                    |                                                                                                           |

|   | • ,                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                           |

|   | asit                                                                                                                | e Elements                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                                        |

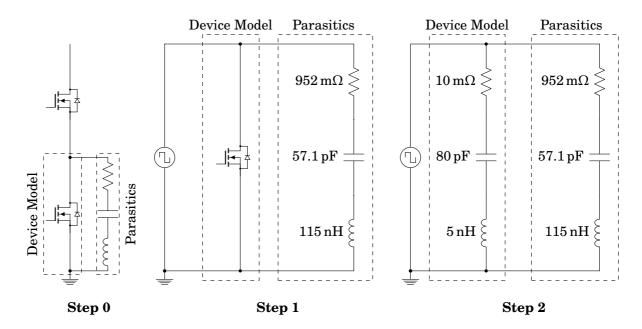

|   | <b>asıt</b><br>3.1                                                                                                  | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | <b>51</b><br>51                                                                                           |

|   |                                                                                                                     | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | 51<br>52                                                                                                  |

|   |                                                                                                                     | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | 51<br>52<br>55                                                                                            |

|   |                                                                                                                     | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | 51<br>52                                                                                                  |

|   |                                                                                                                     | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | 51<br>52<br>55<br>57<br>61                                                                                |

|   |                                                                                                                     | Extraction of System Parasitics                                                                                                                                                                                                                                                                                                                                                            | 51<br>52<br>55<br>57                                                                                      |

|   | 3.1                                                                                                                 | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model                                                                                                                                                                                                                  | 51<br>52<br>55<br>57<br>61<br>65<br>65                                                                    |

|   | 3.1                                                                                                                 | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model                                                                                                                                                                                                                  | 51<br>52<br>55<br>57<br>61<br>65                                                                          |

|   | 3.1                                                                                                                 | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model                                                                                                                                                                                                                  | 51<br>52<br>55<br>57<br>61<br>65<br>65                                                                    |

|   | 3.1<br>3.2                                                                                                          | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model3.2.2Sensitivity AnalysisMitigation                                                                                                                                                                               | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67                                                              |

|   | 3.1<br>3.2                                                                                                          | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model3.2.2Sensitivity AnalysisMitigation                                                                                                                                                                               | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70                                                        |

|   | 3.1<br>3.2                                                                                                          | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model3.2.2Sensitivity AnalysisMitigation3.3.1Inductor Sizing                                                                                                                                                           | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70<br>71                                                  |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                                           | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model3.2.2Sensitivity AnalysisMitigation3.3.1Inductor Sizing3.3.2Experimental Verification                                                                                                                             | 51<br>52<br>55<br>57<br>61<br>65<br>67<br>70<br>71<br>72<br>74                                            |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden</li> </ul>                                        | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation                                                                                                                                                                                                                                                                | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70<br>71<br>72<br>74<br><b>77</b>                         |

| 4 | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                                                           | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation                                                                                                                                                                                                                                                                | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70<br>71<br>72<br>74<br>72<br>74<br>77                    |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden</li> </ul>                                        | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation                                                                                                                                                                                                                                                                | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70<br>71<br>72<br>74<br><b>77</b><br>78<br>79             |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden</li> </ul>                                        | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation3.2.1Design and Validation of Simulation Model3.2.2Sensitivity AnalysisMitigation3.3.1Inductor Sizing3.3.2Experimental VerificationSummarytification of the Temporal Source of Frequency Domain CharacteristicsAnalysis Techniques4.1.1The DFT4.1.2Spectrograms | 51<br>52<br>55<br>57<br>61<br>65<br>67<br>70<br>71<br>72<br>74<br>72<br>74<br>79<br>79                    |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden<br/>4.1</li> </ul>                                | Extraction of System Parasitics3.1.1Device Parasitics3.1.2PCB Parasitics3.1.3Load Parasitics3.1.4Probe ParasiticsSimulation                                                                                                                                                                                                                                                                | 51<br>52<br>55<br>57<br>61<br>65<br>65<br>67<br>70<br>71<br>72<br>74<br><b>77</b><br>78<br>79<br>79<br>81 |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden 4.1</li> <li>4.2</li> </ul>                       | Extraction of System Parasitics         3.1.1       Device Parasitics         3.1.2       PCB Parasitics         3.1.3       Load Parasitics         3.1.4       Probe Parasitics         Simulation                                                                                                                                                                                       | 51<br>52<br>55<br>57<br>61<br>65<br>67<br>70<br>71<br>72<br>74<br><b>77</b><br>78<br>79<br>79<br>81<br>85 |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> </ul> | Extraction of System Parasitics         3.1.1       Device Parasitics         3.1.2       PCB Parasitics         3.1.3       Load Parasitics         3.1.4       Probe Parasitics         Simulation                                                                                                                                                                                       | 51<br>52<br>55<br>57<br>61<br>65<br>67<br>70<br>71<br>72<br>74<br>72<br>74<br>78<br>79<br>81<br>85<br>89  |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Iden 4.1</li> <li>4.2</li> </ul>                       | Extraction of System Parasitics         3.1.1       Device Parasitics         3.1.2       PCB Parasitics         3.1.3       Load Parasitics         3.1.4       Probe Parasitics         Simulation                                                                                                                                                                                       | 51<br>52<br>55<br>57<br>61<br>65<br>67<br>70<br>71<br>72<br>74<br><b>77</b><br>78<br>79<br>79<br>81<br>85 |

5 Design and Analysis of Smoothed Waveforms

93

|   | 5.1 | Definition and Measurement                                                    | 93  |

|---|-----|-------------------------------------------------------------------------------|-----|

|   | 5.2 | Interaction with Parasitics                                                   | 97  |

|   | 5.3 | Simulation Predictions                                                        | 104 |

|   | 5.4 | Summary                                                                       | 108 |

|   |     |                                                                               |     |

| 6 | Pra | ctical Realisation and Application of Smoothed Waveforms                      | 109 |

|   | 6.1 | Target Waveform                                                               |     |

|   | 6.2 | Experimental Implementation                                                   |     |

|   | 6.3 | Experimental Results                                                          | 113 |

|   | 6.4 | Summary                                                                       | 119 |

| 7 | Pas | sive Profiling Gate Drives                                                    | 121 |

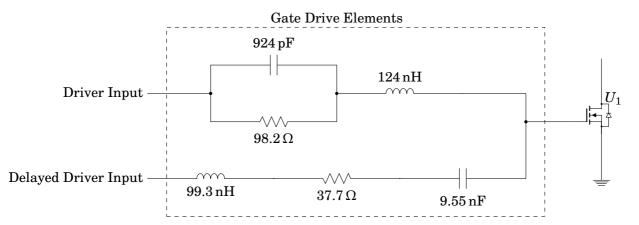

| • | 7.1 | Design of a Passive Driver                                                    |     |

|   | 7.2 | Experimental Validation                                                       |     |

|   |     | 7.2.1 Simulation                                                              |     |

|   |     | 7.2.2 Initial Validation                                                      |     |

|   |     | 7.2.3 Automated Testing                                                       |     |

|   | 7.3 | Performance Evaluation                                                        |     |

|   | 7.4 | Refined Design                                                                |     |

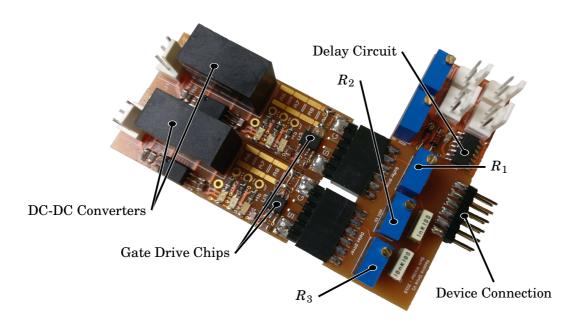

|   | 1.1 | 7.4.1 New Driver                                                              |     |

|   |     | 7.4.2 Initial Testing                                                         |     |

|   |     | 7.4.3 Measured Parasitics                                                     |     |

|   |     | 7.4.4 Results                                                                 |     |

|   |     | 7.4.5 Varying Current                                                         |     |

|   | 7.5 | Summary                                                                       |     |

|   | ••• | Summary                                                                       | 110 |

| 8 | Con | clusions and Critical Review                                                  | 147 |

|   | 8.1 | Understanding the Influence of Parasitic Elements in WBG Based Power Convert- |     |

|   |     | ers                                                                           | 147 |

|   |     | 8.1.1 Impact of Parasitics                                                    | 147 |

|   |     | 8.1.2 Simulation                                                              | 148 |

|   |     | 8.1.3 Mitigation                                                              | 149 |

|   | 8.2 | Understanding and Modelling the EM Impact of Device Switching Transients      | 150 |

|   |     | 8.2.1 Analysis                                                                | 150 |

|   |     | 8.2.2 EMI Metrics                                                             | 150 |

|   | 8.3 | Defining Smoothed Switching Transitions and Practical Realisation             | 151 |

|   |     | 8.3.1 Smoothness Metrics                                                      | 151 |

|   |     | 8.3.2 Analysis                                                                | 152 |

|   |     | 8.3.3 Simulation                                                              | 152 |

|   |     | 8.3.4 Practical Implementation                                                | 153 |

|   |     | 8.3.5 Changing Conditions                                                     | 154 |

|   | 8.4 | Development of Passive Gate Drivers for Waveform Shaping                      | 156 |

|   |     | 8.4.1 Design                                                                  | 156 |

|   |     | 8.4.2 Simulation                                                              | 156 |

|   |     | 8.4.3 Experimental Validation                                                 | 157 |

|   |     |                                                                               |     |

| A | Appendix | А- | Double | Pulse | Testing |

|---|----------|----|--------|-------|---------|

|---|----------|----|--------|-------|---------|

### TABLE OF CONTENTS

|    | A.1 Zero Current Switching                           | . 160               |

|----|------------------------------------------------------|---------------------|

| B  | Appendix B - Code ListingsB.1Matlab DFT codeDFT code | <b>163</b><br>. 163 |

| Bi | ibliography                                          | 171                 |

# LIST OF TABLES

| Тав | LE Page                                                                              | , |

|-----|--------------------------------------------------------------------------------------|---|

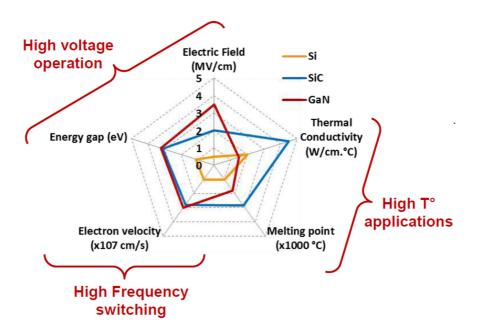

| 1.1 | Comparison of semiconductor material properties                                      | 7 |

| 1.2 | Influence of gate resistance on switching speed 11                                   | L |

| 2.1 | Comparison of AGC improvements                                                       | ) |

| 3.1 | Estimation of switching loop inductance 58                                           | 3 |

| 3.2 | Details of swept parameters and their sweep ranges                                   | 3 |

| 4.1 | Parameters used to characterise the overshoot and ringing during the switching tran- |   |

|     | sient                                                                                | 7 |

| 6.1 | Performance of waveform shaping 11'                                                  | 7 |

| 7.1 | Comparison of previous passive gate drive works                                      | 3 |

### **LIST OF FIGURES**

| Figi | PIGURE Pa                                                              |    |

|------|------------------------------------------------------------------------|----|

| 1.1  | Basic model of a power converter                                       | 2  |

| 1.2  | Simple three phase converter                                           | 3  |

| 1.3  | Illustration of the position of gate drivers in a typical half bridge  | 4  |

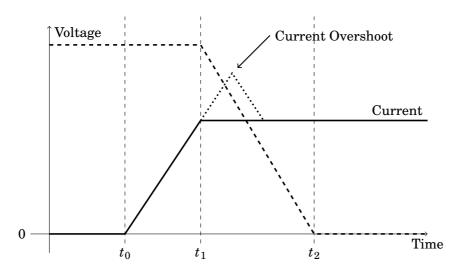

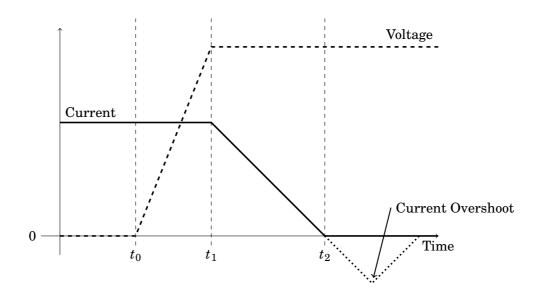

| 1.4  | Typical shape of a MOSFET turn-on transient                            | 5  |

| 1.5  | Typical shape of a MOSFET turn-off transition                          | 6  |

| 1.6  | Example of power converter voltage and current waveforms               | 6  |

| 1.7  | Inductor with typical parasitic elements                               | 7  |

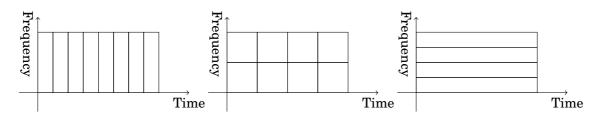

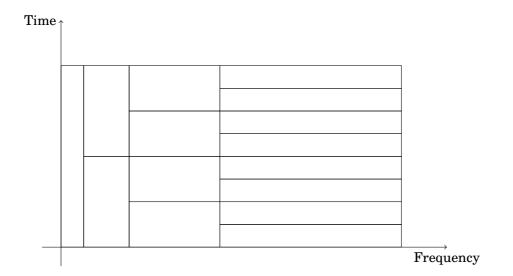

| 1.8  | Time vs frequency domain localisation trade-off                        | 9  |

| 1.9  | Time vs frequency domain localisation trade-off with Wavelet Transform | 9  |

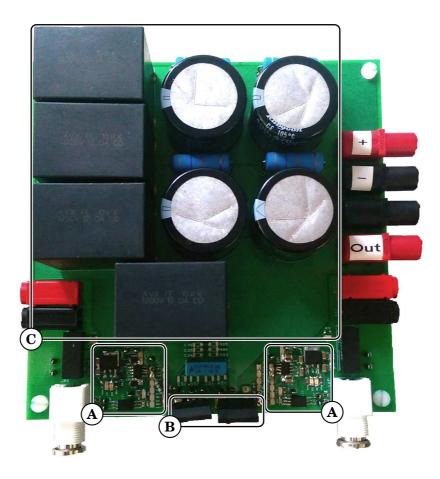

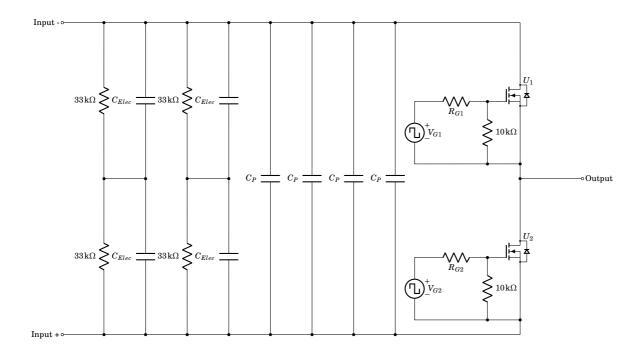

| 1.10 | Photo of the test PCB used in this work                                | 12 |

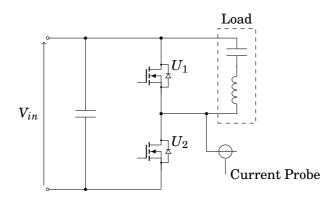

| 1.11 | Circuit diagram of the test PCB                                        | 13 |

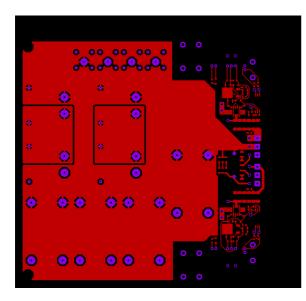

| 1.12 | PCB top copper layout                                                  | 13 |

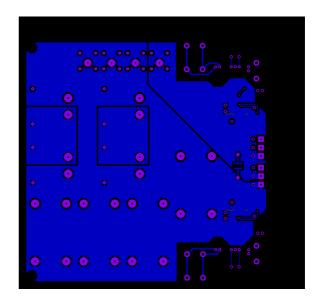

| 1.13 | PCB bottom copper layout                                               | 13 |

| 1.14 | Initial DPT results from the experimental set-up                       | 14 |

| 2.1  | Comparison of wide band gap material properties                        | 18 |

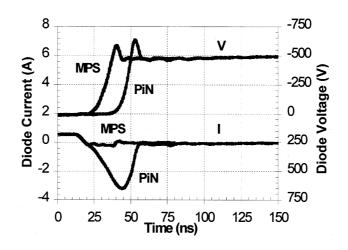

| 2.2  | Reverse recovery characteristics of diodes                             | 20 |

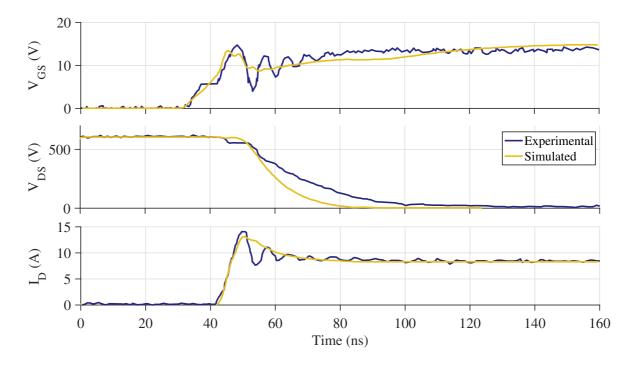

| 2.3  | Example of accurate simulation results                                 | 22 |

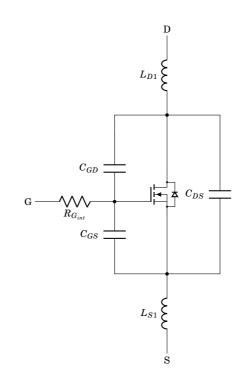

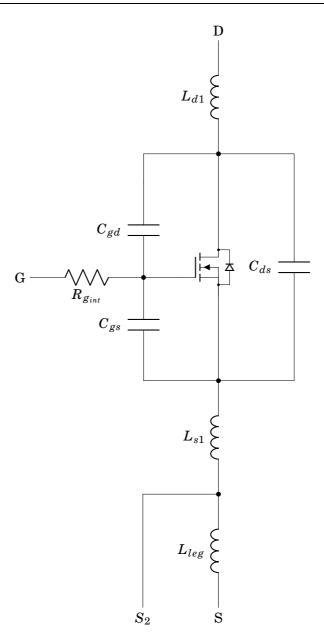

| 2.4  | Equivalent model of a MOSFET                                           | 24 |

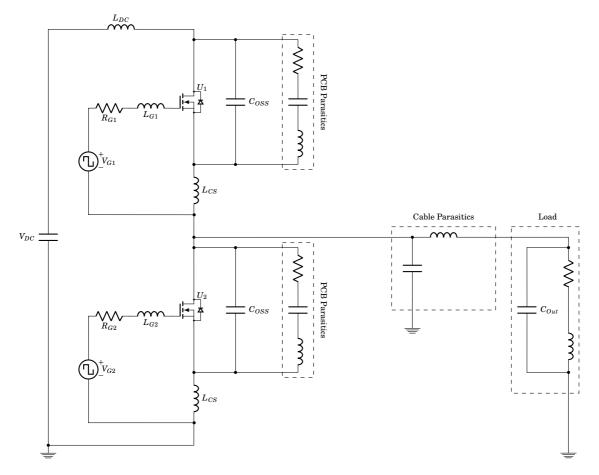

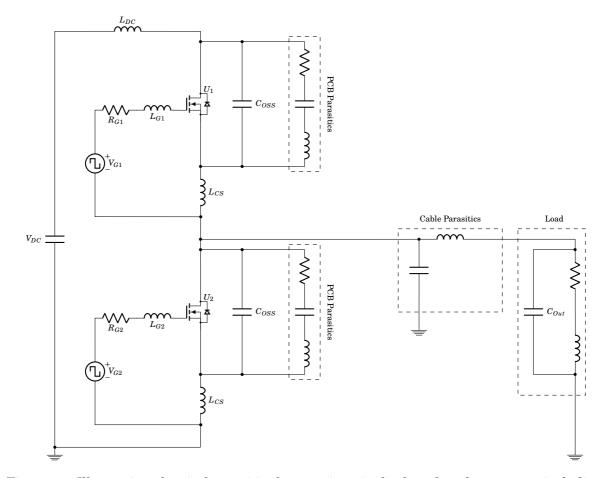

| 2.5  | Illustration of typical power converter parasitic elements             | 25 |

| 2.6  | Illustration of typical power converter parasitic elements             | 28 |

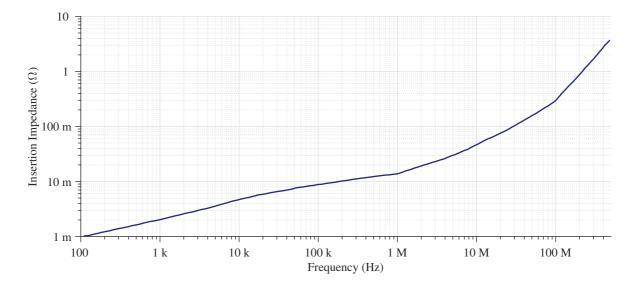

| 2.7  | Insertion impedance of typical hybrid current clamp probe              | 30 |

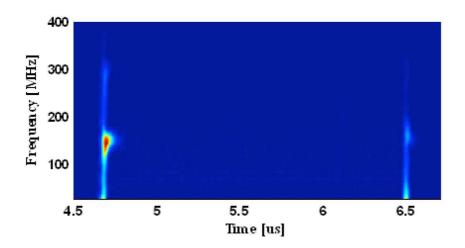

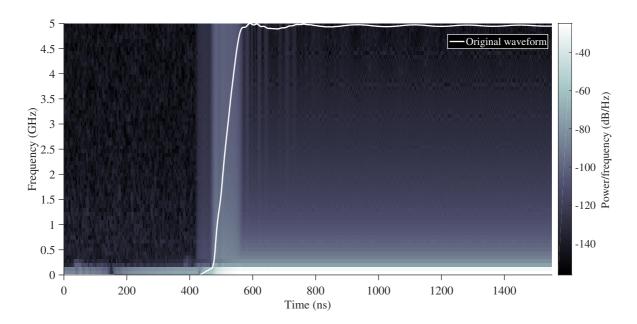

| 2.8  | Example of a spectrogram                                                                    | 35 |

|------|---------------------------------------------------------------------------------------------|----|

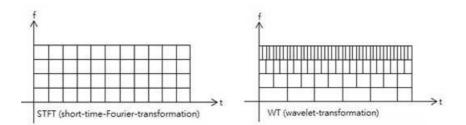

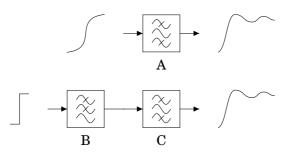

| 2.9  | Comparison of STFT and WT                                                                   | 36 |

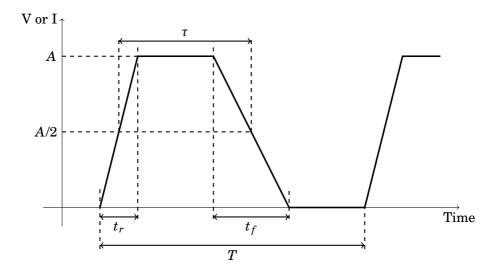

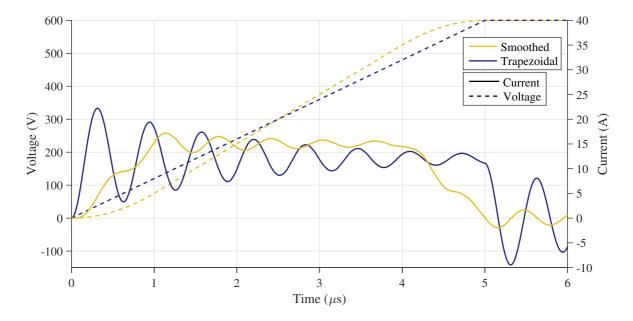

| 2.10 | Example of power converter voltage and current waveforms                                    | 36 |

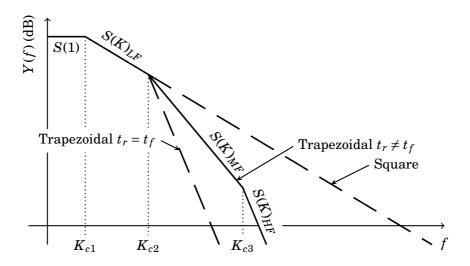

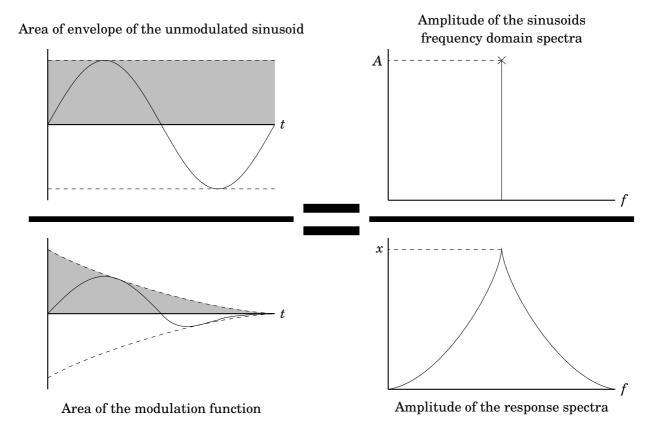

| 2.11 | Typical spectral envelope of power converter waveforms                                      | 37 |

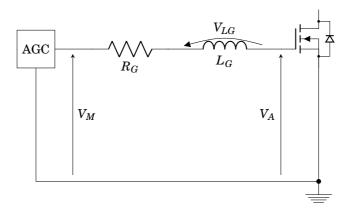

| 2.12 | Active gate driver connection model                                                         | 44 |

| 2.13 | Photo of a closed-loop controlled gate driver implementation                                | 46 |

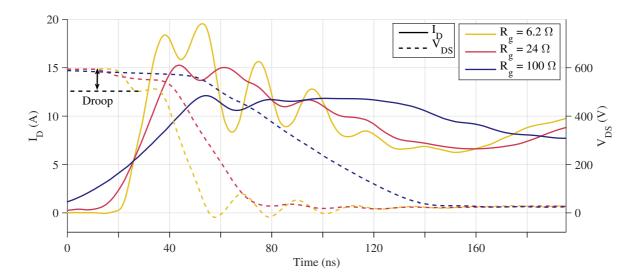

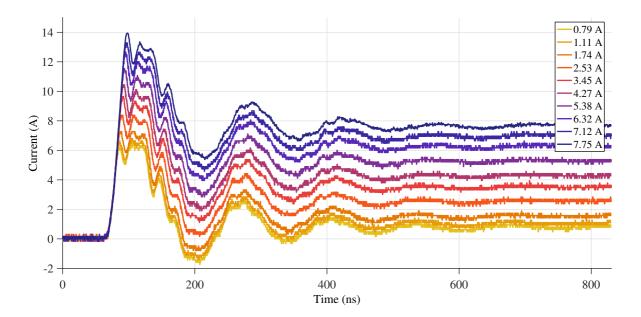

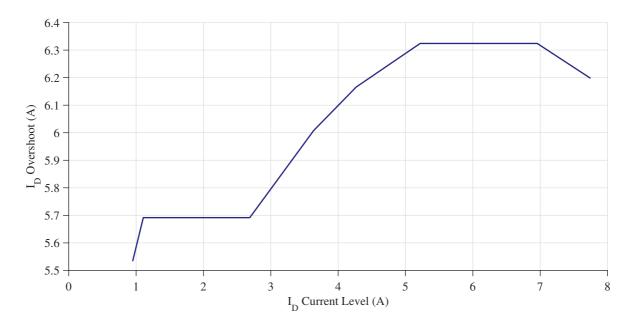

| 3.1  | Turn-on current waveforms for the top switching device with varying load current $\$ .      | 53 |

| 3.2  | Overshoot current vs. load current in the top switching device                              | 54 |

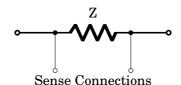

| 3.3  | Illustration of Kelvin (or 4-port) connection                                               | 55 |

| 3.4  | MOSFET with Kelvin source connection                                                        | 56 |

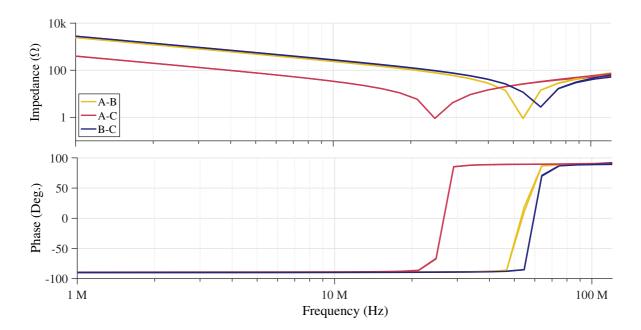

| 3.5  | Measured impedance between the main PCB power terminals                                     | 57 |

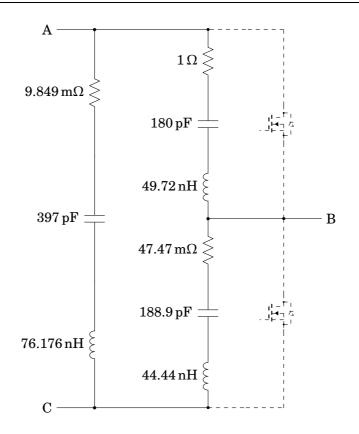

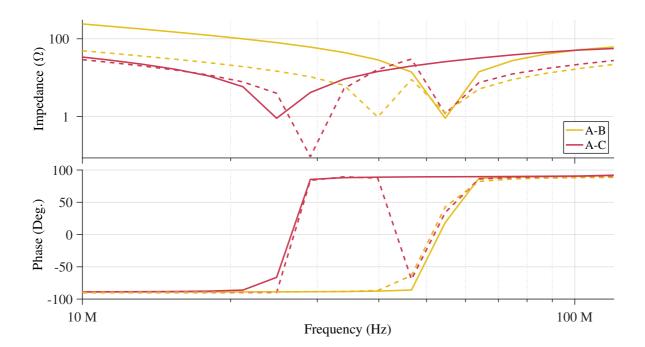

| 3.6  | Equivalent parasitic circuit of the PCB                                                     | 58 |

| 3.7  | Measured and estimated parameter comparison                                                 | 59 |

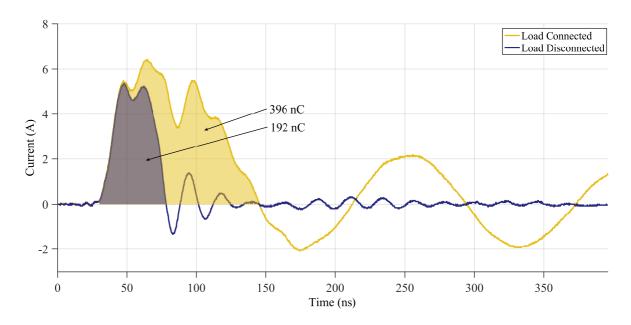

| 3.8  | Load current due to $C_{Out}$                                                               | 60 |

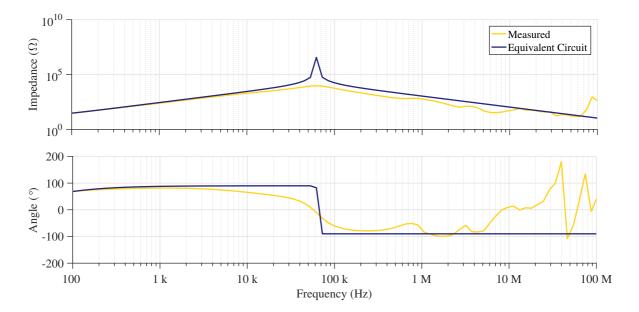

| 3.9  | Load impedance as measured with an impedance analyser                                       | 60 |

| 3.10 | Influence of output cable on turn-on current overshoot                                      | 61 |

| 3.11 | Illustration of the connection of the current clamp probe to a stub of wire $\ldots \ldots$ | 62 |

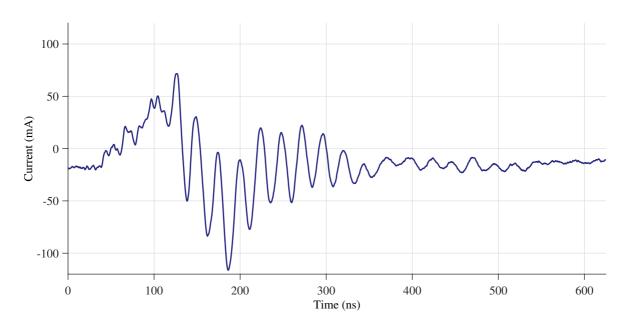

| 3.12 | Measured current due to $dV/dt$ induced noise. The ringing frequency is $41.2{\rm MHz}$     | 63 |

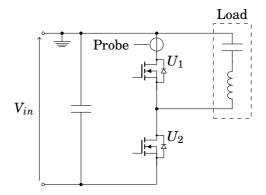

| 3.13 | Connection of the current probe to a grounded node                                          | 63 |

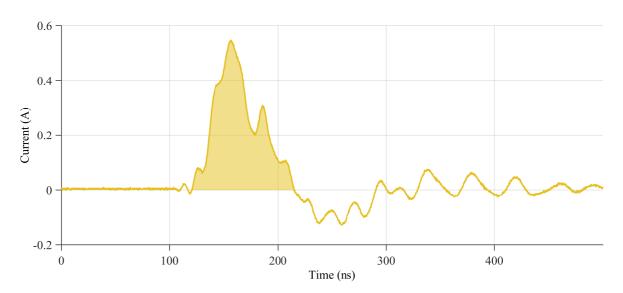

| 3.14 | Measured current into one of the connections of the differential voltage probe $\ldots$ .   | 64 |

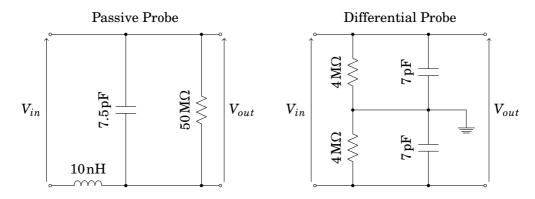

| 3.15 | The equivalent circuits of the voltage probes                                               | 64 |

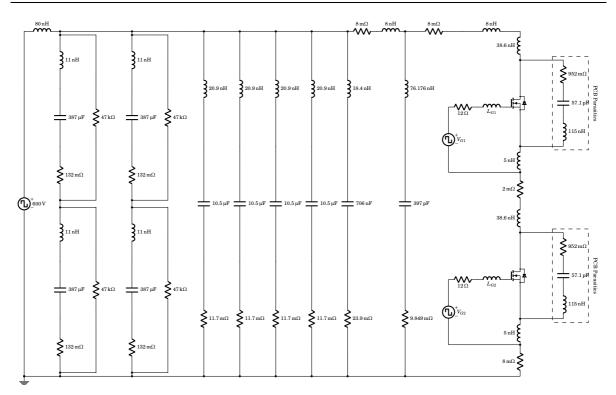

| 3.16 | Detailed simulation model of parasitic elements                                             | 66 |

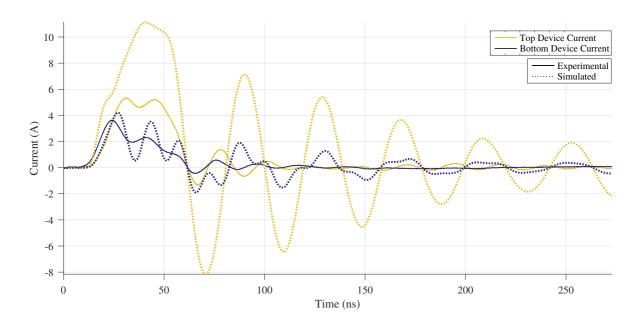

| 3.17 | Comparison of the simulated and experimental results                                        | 67 |

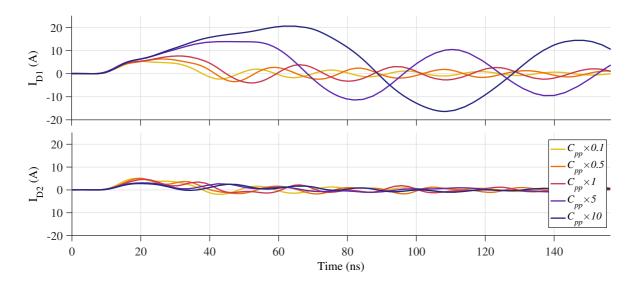

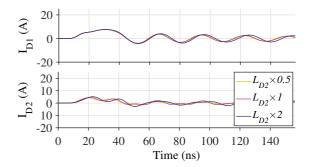

| 3.18 | Variation in the switching device current waveforms for varying values of $C_{pp}$          | 68 |

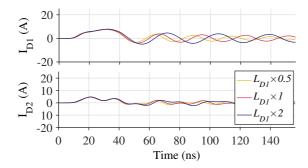

| 3.19 | Variation in the switching device current waveforms for varying values of the top           |    |

|      | device drain inductance                                                                     | 68 |

| 3.20 | Variation in the switching device current waveforms for varying values of the bottom        |    |

|      | device drain inductance                                                                     | 68 |

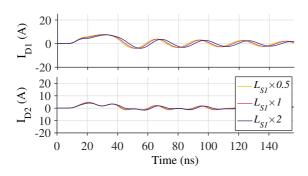

| 3.21 | Variation in the switching device current waveforms for varying values of the top        |    |

|------|------------------------------------------------------------------------------------------|----|

|      | device source inductance                                                                 | 69 |

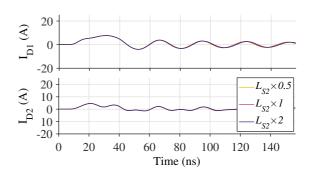

| 3.22 | Variation in the switching device current waveforms for varying values of the bottom     |    |

|      | device source inductance. Note that changing this parameter in the range explored        |    |

|      | changes the waveforms very little, hence the difference is only very slight. $\ldots$ .  | 69 |

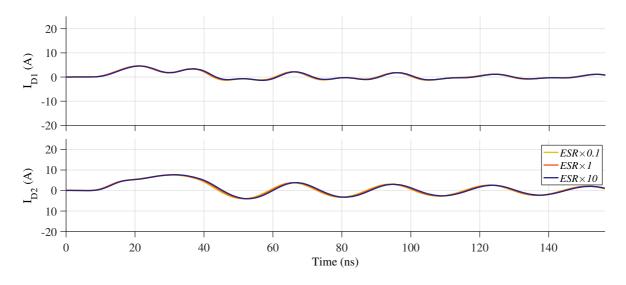

| 3.23 | Variation in the switching device current waveforms for varying values of DC-link        |    |

|      | capacitance ESR                                                                          | 69 |

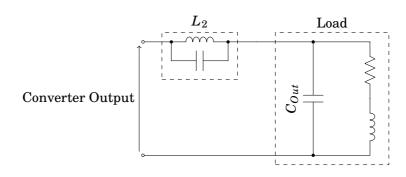

| 3.24 | Series connection of a small inductor for controlling overshoot due to the load EPC $$ . | 70 |

| 3.25 | A small, low EPC, inductor                                                               | 71 |

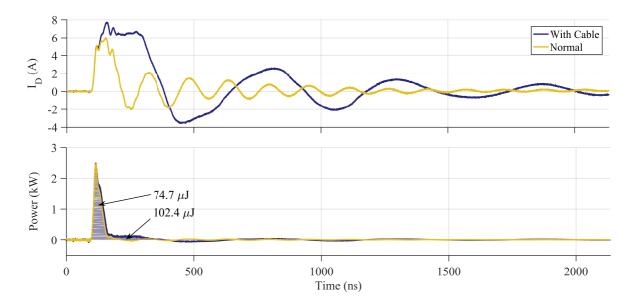

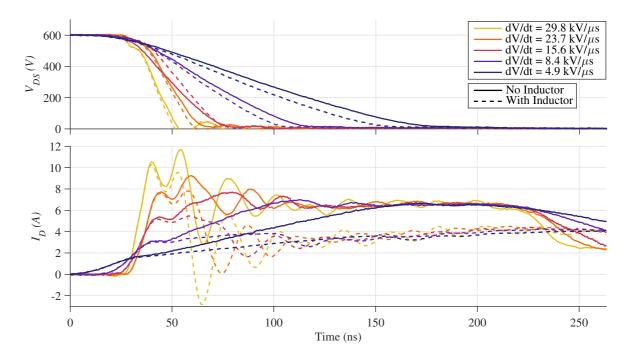

| 3.26 | Influence of small inductor on top switching device current waveform                     | 73 |

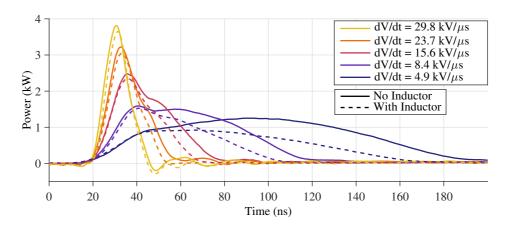

| 3.27 | Top switching device turn-on power waveforms with and without the inclusion of the       |    |

|      | additional inductor                                                                      | 74 |

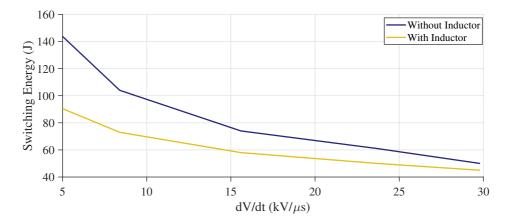

| 3.28 | Reduction of switching loss with inclusion of a small inductor                           | 74 |

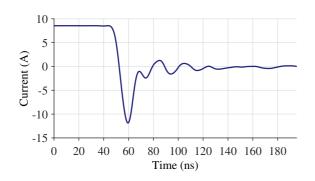

| 4.1  | Top switching device current waveform during turn-off                                    | 78 |

| 4.2  | Spectra of the top switching device current waveform at turn-off                         | 78 |

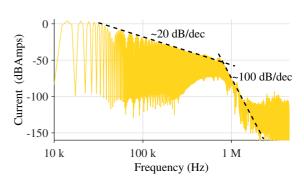

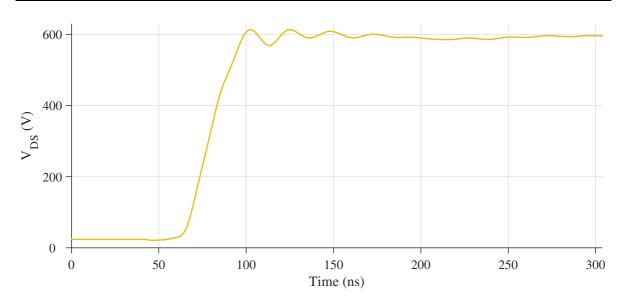

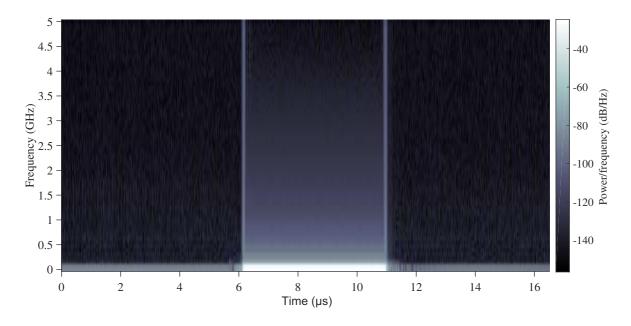

| 4.3  | Voltage waveform considered for spectral analysis                                        | 80 |

| 4.4  | Spectrogram of the voltage waveform showing the device switching                         | 80 |

| 4.5  | Spectrogram of the turn-off of the top switching device                                  | 81 |

| 4.6  | Various possible transient shapes                                                        | 82 |

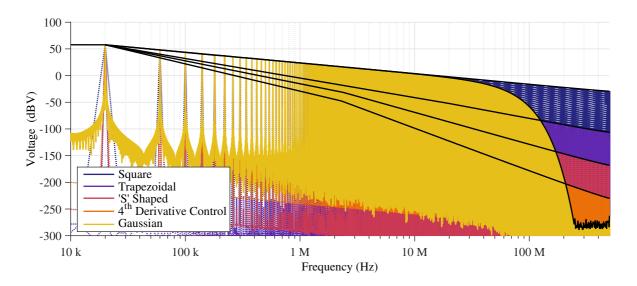

| 4.7  | Spectral envelope of various transient shapes                                            | 83 |

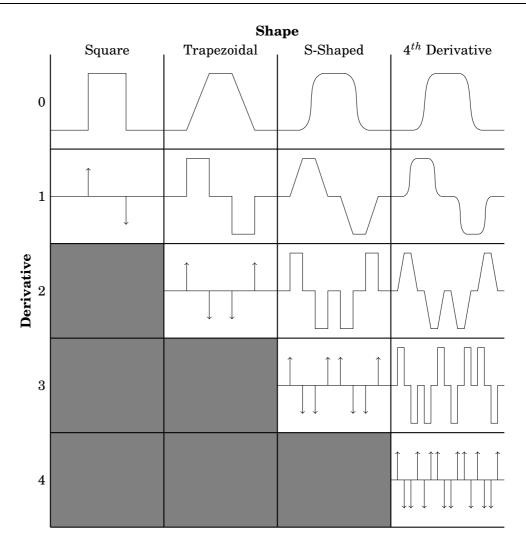

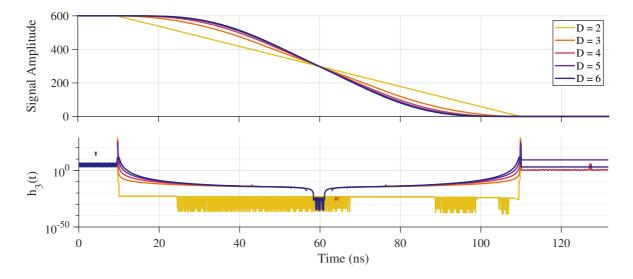

| 4.8  | Illustration of successive differentiation                                               | 84 |

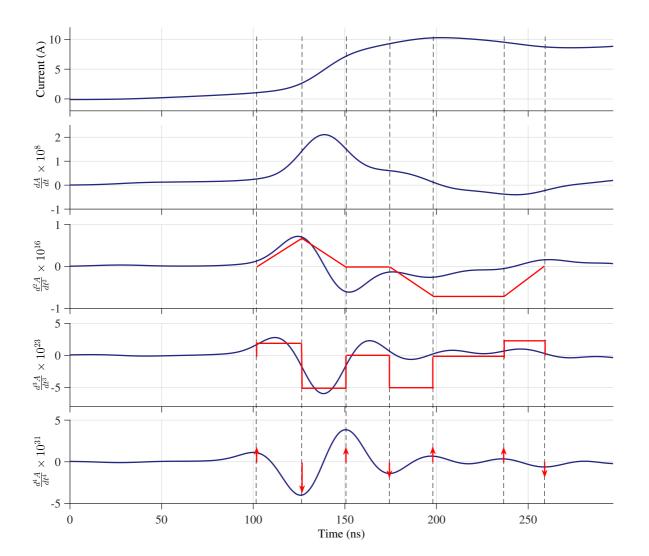

| 4.9  | Successive differentiation of an experimental waveform                                   | 85 |

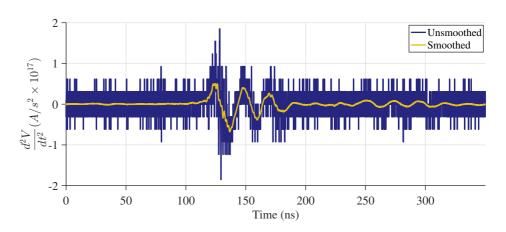

| 4.10 | Illustration of the use of smoothing in successive differentiation                       | 86 |

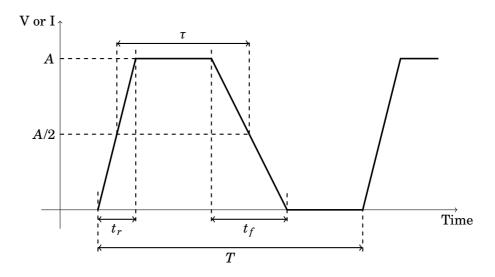

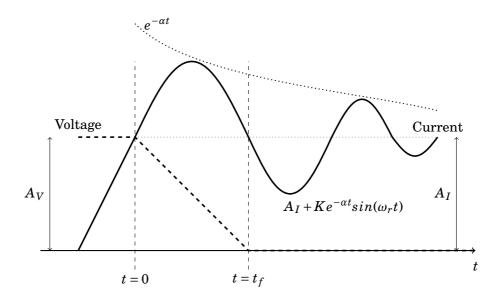

| 4.11 | Parametrisation of the characteristics of a typical device transient waveform            | 86 |

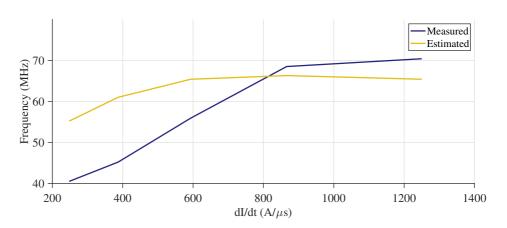

| 4.12 | Comparison of calculated and measured current ringing frequency                          | 88 |

| 4.13 | Experimental current waveforms from the top switching device with various gate           |    |

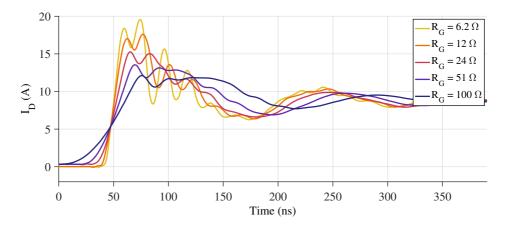

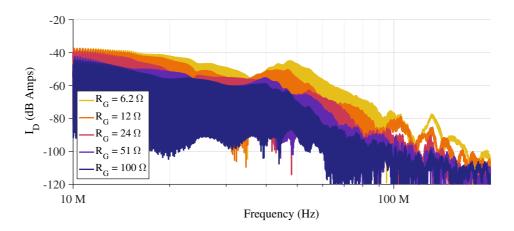

|      | resistances                                                                              | 88 |

| 4.14 | Spectra of the time domain waveforms shown in fig. 4.13                                  | 88 |

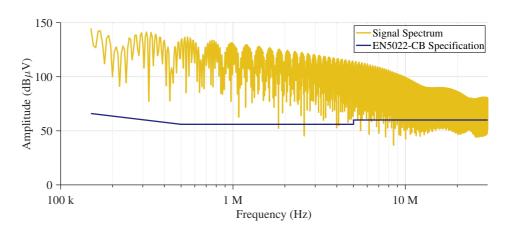

| 4.15 | $Comparison \ of \ the \ spectra \ of \ the \ voltage \ waveform \ with \ the \ EN5022-CB \ specification$       | 90  |

|------|------------------------------------------------------------------------------------------------------------------|-----|

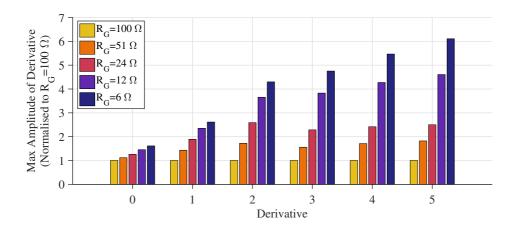

| 4.16 | Amplitude of the differentials of the current waveform with varying $R_G$ $\ldots$ $\ldots$ $\ldots$             | 91  |

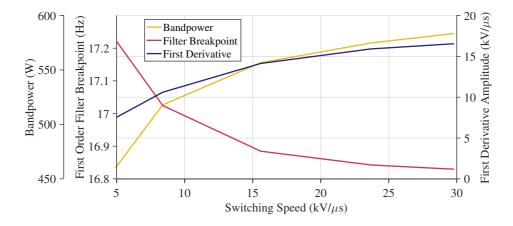

| 4.17 | $Comparison \ of \ the \ variation \ of \ each \ of \ the \ discussed \ metrics \ with \ transition \ speed \ .$ | 91  |

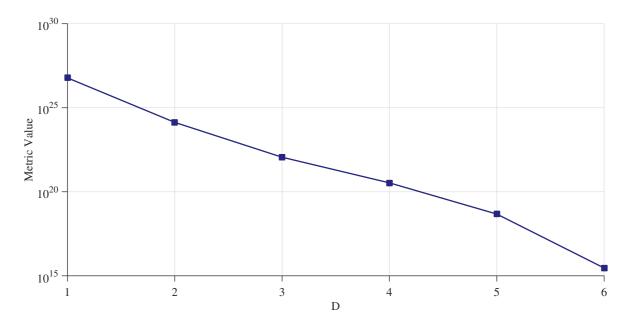

| 5.1  | Illustration of a smoothness metric varying with transition shape                                                | 96  |

| 5.2  | Variation of a smoothness metric with $D$                                                                        | 96  |

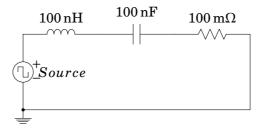

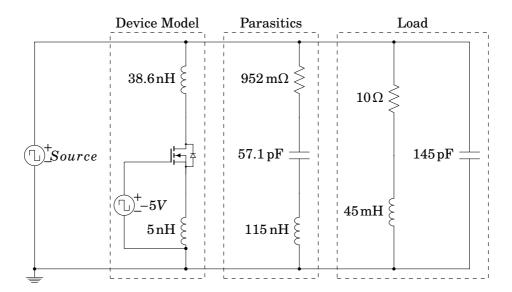

| 5.3  | Simple simulation circuit for comparing smoothed and trapezoidal waveforms $\ldots$ .                            | 98  |

| 5.4  | Reduction of current overshoot through the use of smoothing                                                      | 98  |

| 5.5  | Proposed analytical relationship for overshoot prediction                                                        | 99  |

| 5.6  | Method for separating the complex plant and excitation for analysis                                              | 100 |

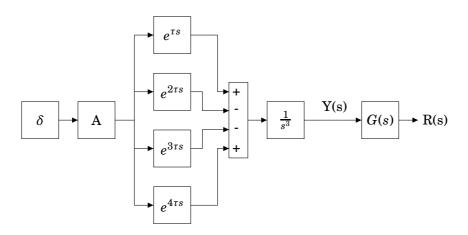

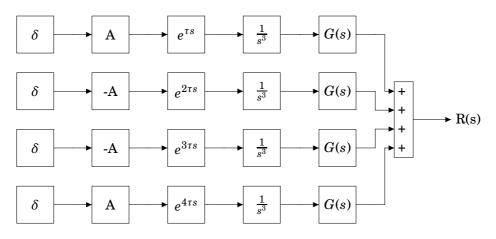

| 5.7  | Block diagram representation of the equations describing the smoothing system $\ldots$                           | 101 |

| 5.8  | Illustration of a method for decimating the system of fig. 5.7 into the sum of simpler                           |     |

|      | systems                                                                                                          | 101 |

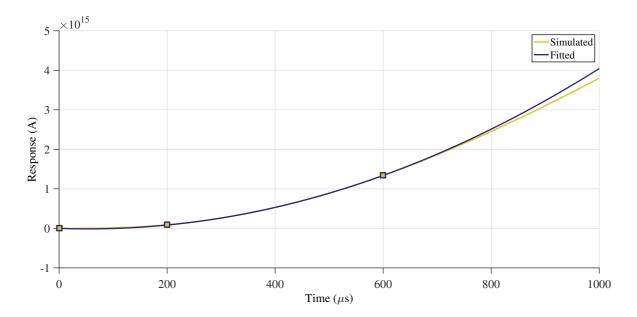

| 5.9  | Comparison of simulated response with a fitted polynomial                                                        | 103 |

| 5.10 | Development of the simple LTspice simulation circuit from the half bridge                                        | 104 |

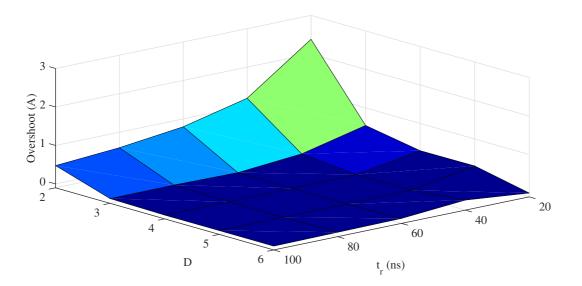

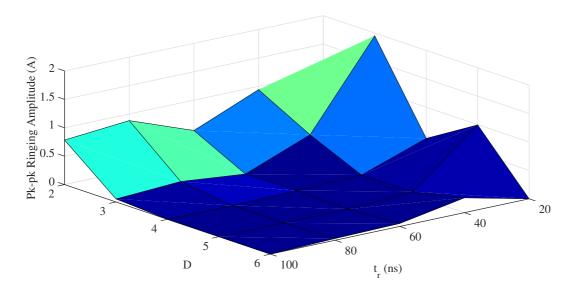

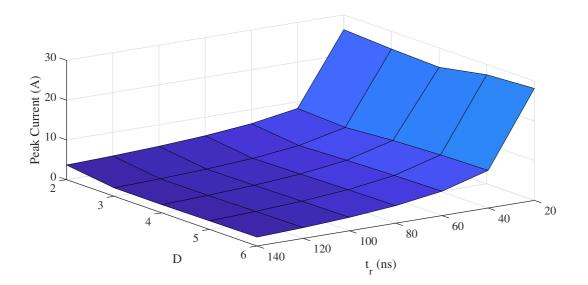

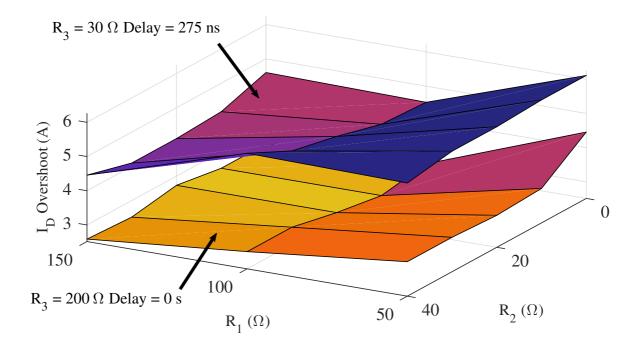

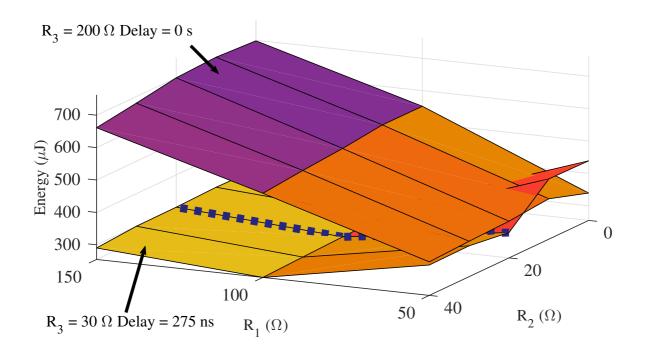

| 5.11 | Current overshoot vs. smoothness and rise-time                                                                   | 105 |

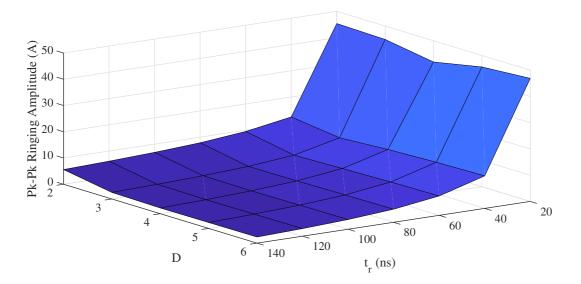

| 5.12 | Ringing amplitude vs. smoothness and rise-time                                                                   | 105 |

| 5.13 | Full LTspice simulation circuit                                                                                  | 106 |

| 5.14 | Overshoot characteristics of the current waveform in a more detailed simulation                                  |     |

|      | model                                                                                                            | 107 |

| 5.15 | Ringing amplitude vs. smoothness and rise-time                                                                   | 107 |

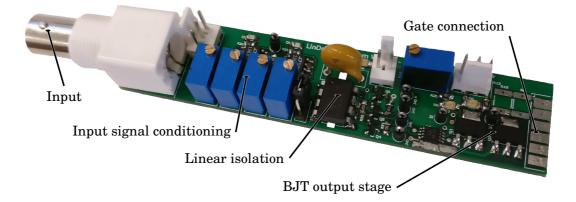

| 6.1  | Photo of a closed-loop controlled gate driver implementation                                                     | 111 |

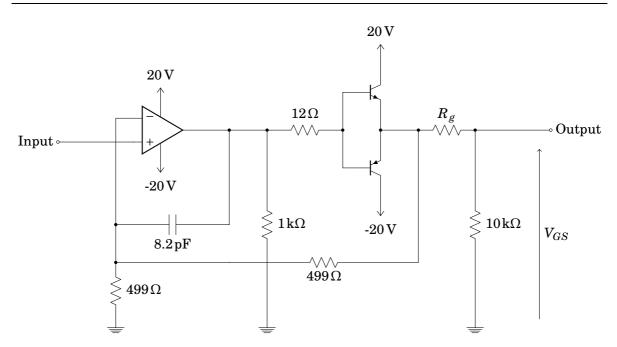

| 6.2  | Linear gate drive output stage design                                                                            | 112 |

| 6.3  | Third generation linear gate drive circuit for the application of profiled gate wave-                            |     |

|      | forms                                                                                                            | 112 |

| 6.4  | Double Pulse Test Graphical User Interface                                                                       | 113 |

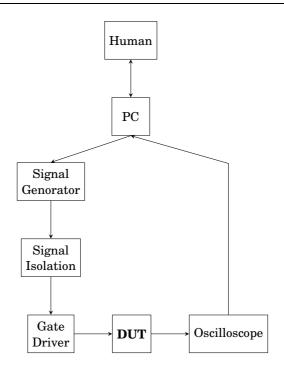

| 6.5  | Automated experimental system design                                                                             | 114 |

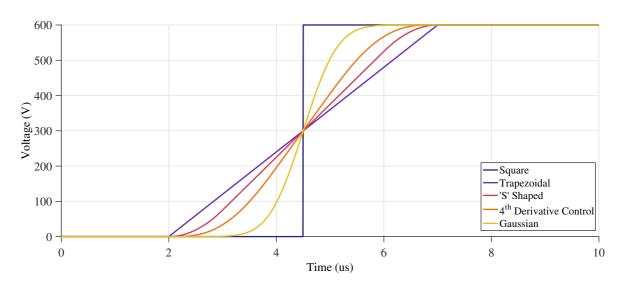

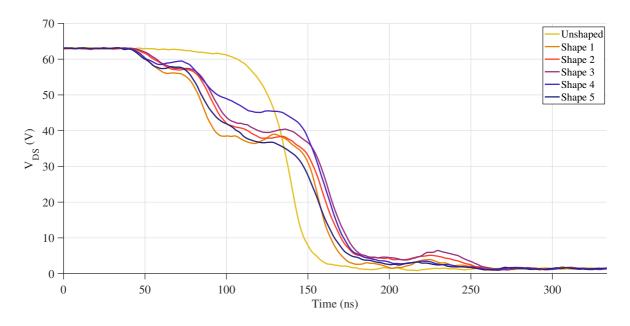

| 6.6  | $V_{DS}$ turn-on waveform profiles achieved in the 60 V DPTs $\ldots \ldots \ldots \ldots \ldots$                | 114 |

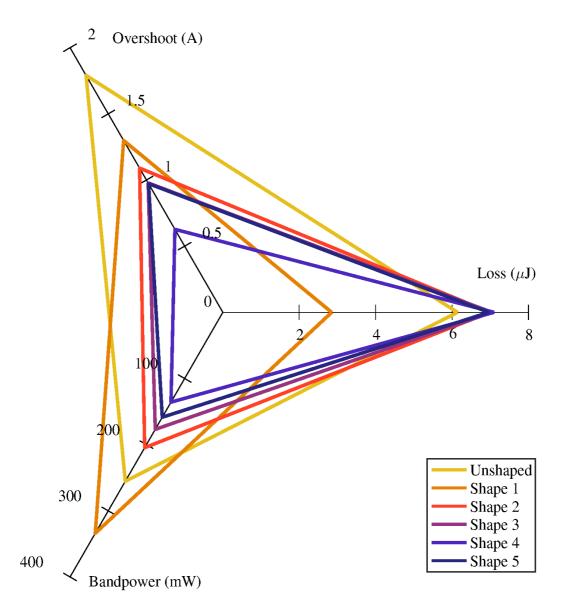

| 6.7  | Comparison of the performance metrics of the five waveforms from fig. 6.6. For all                                                                                                          |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | three of the metrics presented here closer to the centre of the spider (ie. smaller                                                                                                         |    |

|      | areas) indicate better performance                                                                                                                                                          | 15 |

| 6.8  | Improved $V_{DS}$ waveform shape $\ldots \ldots \ldots$                     | 16 |

| 6.9  | Optimal gate waveform profile at different current levels                                                                                                                                   | 18 |

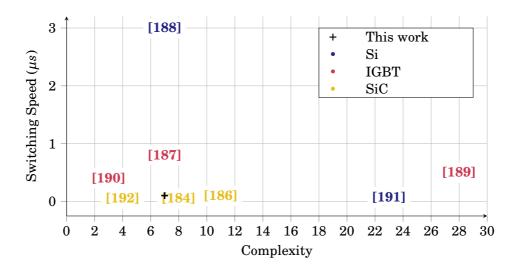

| 7.1  | Comparison of previous passive gate drive works                                                                                                                                             | 22 |

| 7.2  | Turn-on excitations used in fully active tests                                                                                                                                              | 24 |

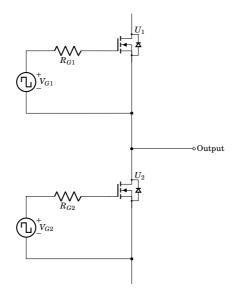

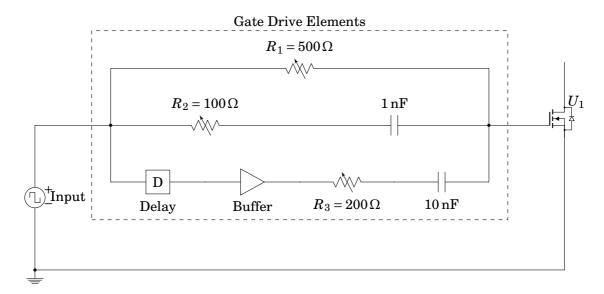

| 7.3  | Passive gate driver design                                                                                                                                                                  | 24 |

| 7.4  | Passive gate driver test waveforms                                                                                                                                                          | 26 |

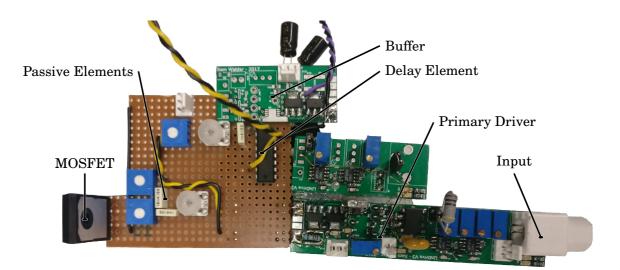

| 7.5  | Prototype passive gate drive system                                                                                                                                                         | 26 |

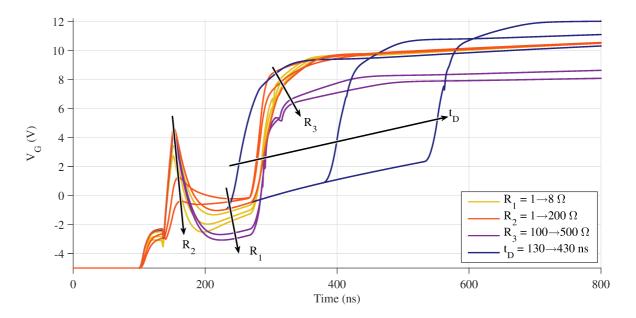

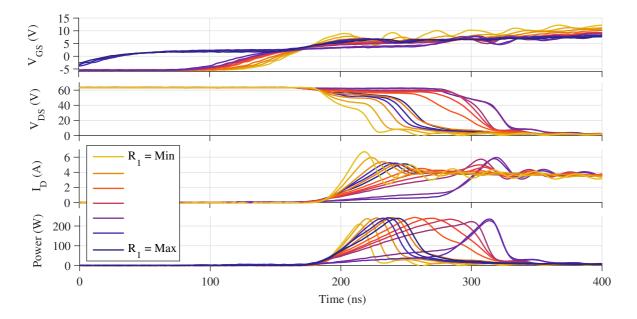

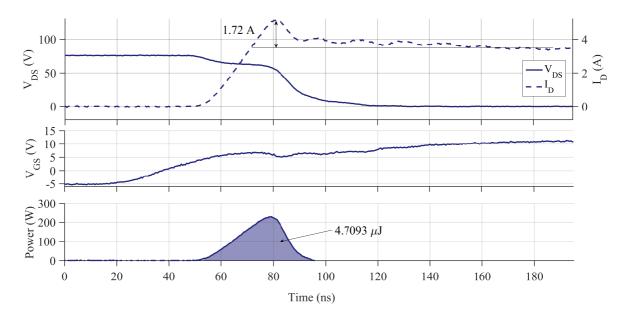

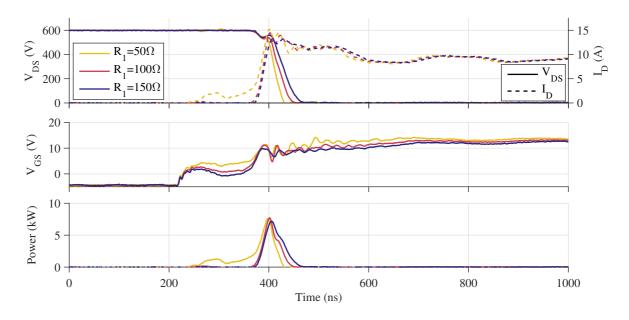

| 7.6  | Passive gate drive waveforms with swept $R_1$                                                                                                                                               | 27 |

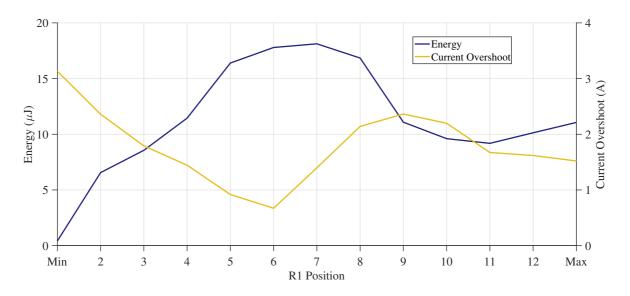

| 7.7  | Switching energy and overshoot with $R_1$ variations $\ldots \ldots \ldots$ | 28 |

| 7.8  | Waveforms from minimum switching loss search 1                                                                                                                                              | 28 |

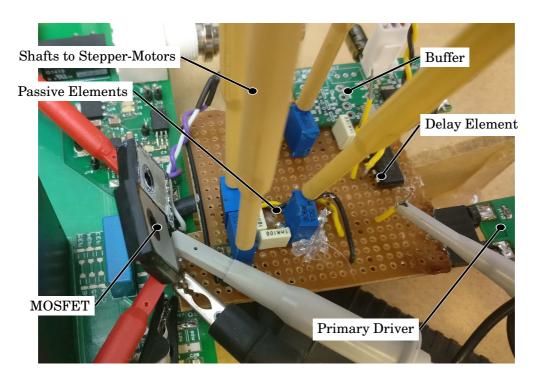

| 7.9  | Prototype passive gate drive system in automated setup                                                                                                                                      | 29 |

| 7.10 | Current overshoot with passive gate driver 1                                                                                                                                                | 30 |

| 7.11 | Switching energy with passive gate driver 1                                                                                                                                                 | 31 |

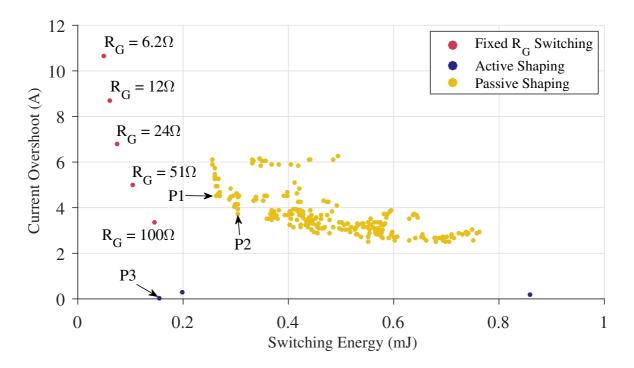

| 7.12 | Elucidation of convoluted passive gate drive results                                                                                                                                        | 32 |

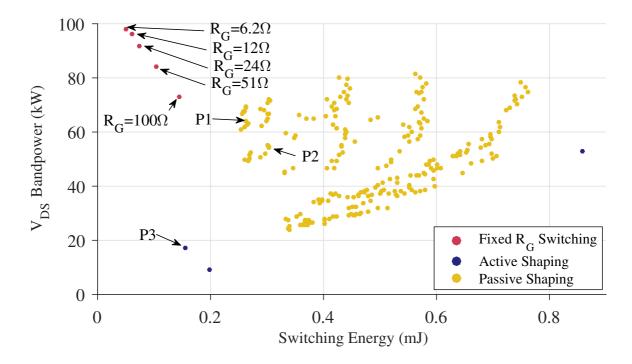

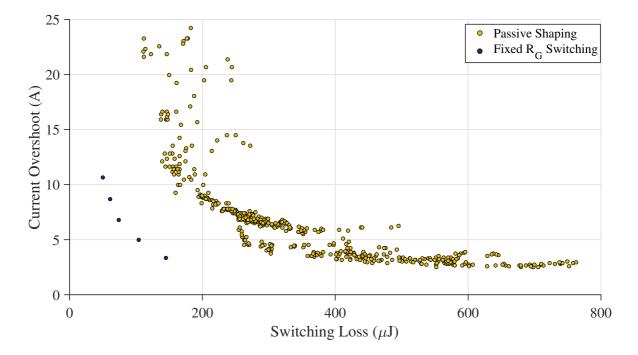

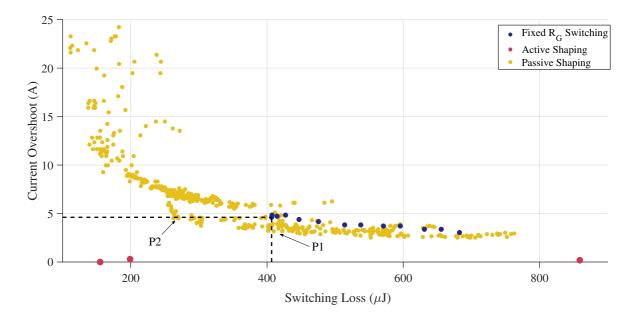

| 7.13 | Current overshoot performance of various drive techniques                                                                                                                                   | 33 |

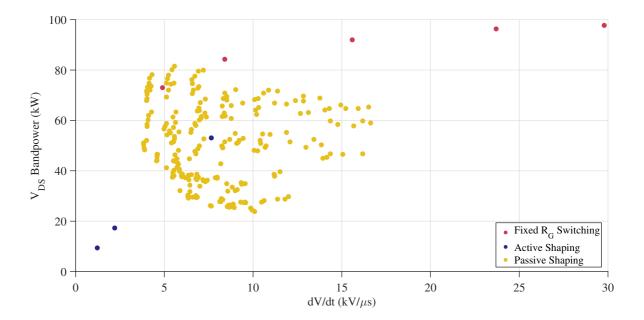

| 7.14 | Bandpower performance of various drive techniques 1                                                                                                                                         | 34 |

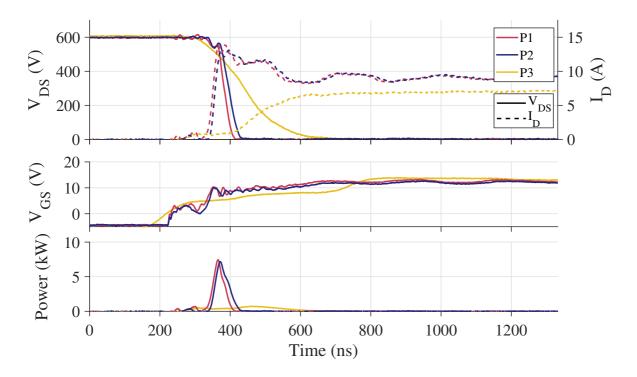

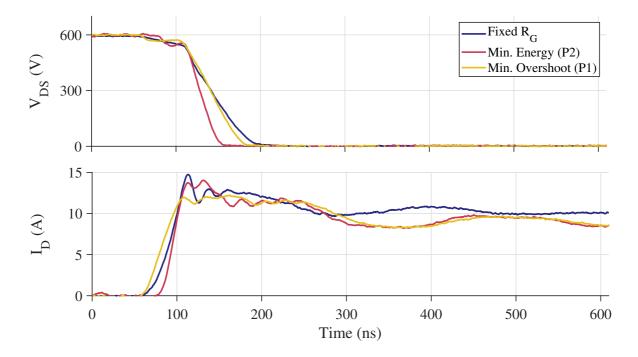

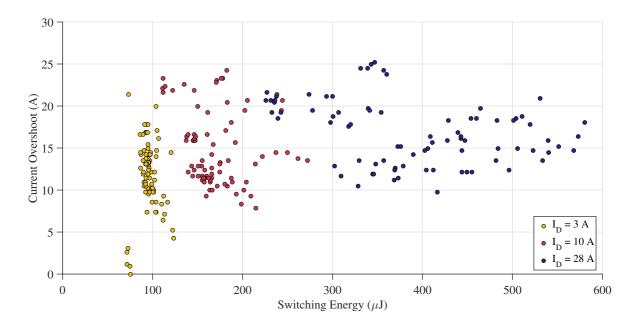

| 7.15 | Exemplary time domain waveforms from various gate drivers                                                                                                                                   | 35 |

| 7.16 | Bandpower vs. switching speed for various gate drivers 1                                                                                                                                    | 36 |

| 7.17 | PCB based passive gate driver 1                                                                                                                                                             | 37 |

| 7.18 | Initial results from the PCB based passive driver 1                                                                                                                                         | 38 |

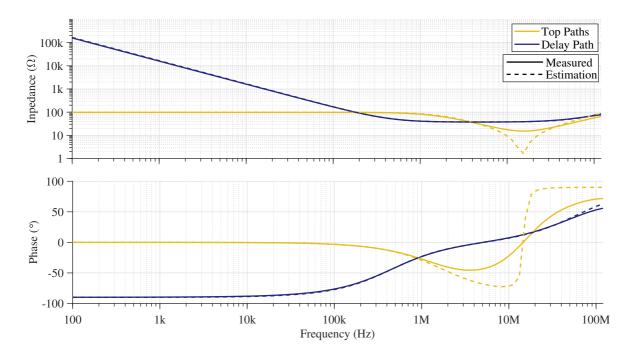

| 7.19 | New passive gate driver measured impedances 1                                                                                                                                               | 39 |

| 7.20 | Passive gate driver parasitics                                                                                                                                                              | 39 |

| 7.21 | New passive gate drive performance comparison 1                                                                                                                                             | 41 |

| 7.22 | New passive driver temporal waveforms                                                                                                                                                       | 41 |

| 7.23 | Gate voltage waveforms from the new passive driver                                                                                                                                          | 42 |

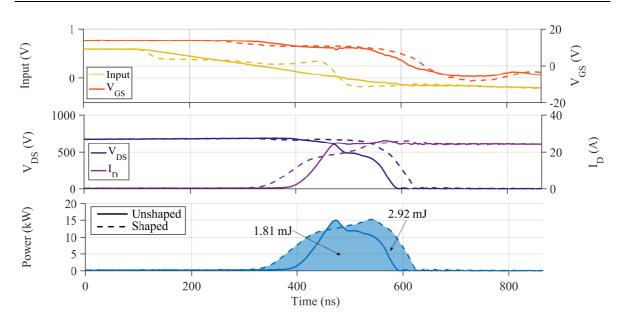

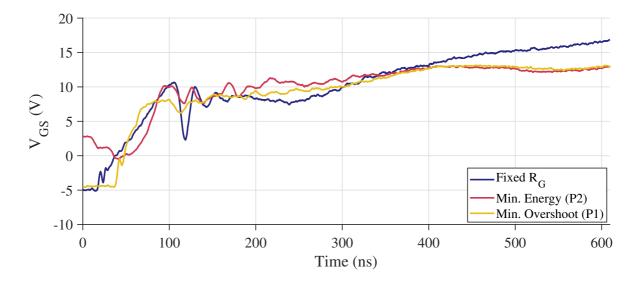

| 7.24 | Power waveforms from the new passive driver                  | 143 |

|------|--------------------------------------------------------------|-----|

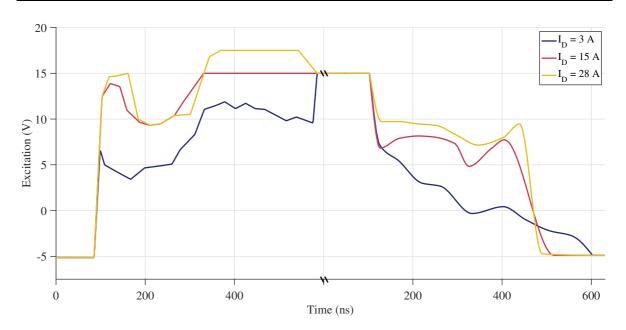

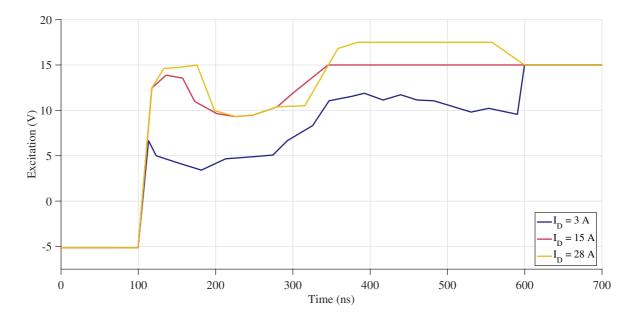

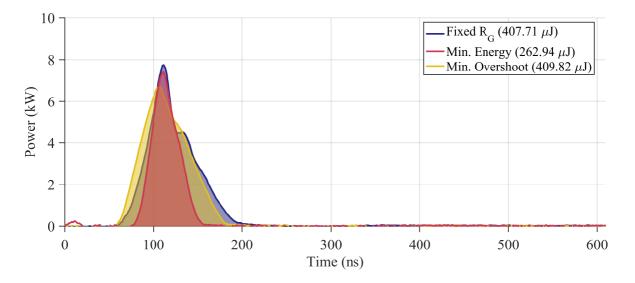

| 7.25 | Passive driver performance with changing current             | 144 |

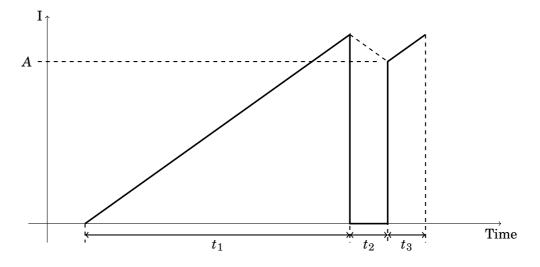

| A.1  | Switching device current waveform during a double pulse test | 160 |

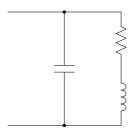

| A.2  | Typical load connected to the switching device               | 161 |

### **GLOSSARIES**

# Glossary

| Bandpower                                   | A measure of the power contained within a specific fre-                                                                                                                                                             |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | quency band of a signal                                                                                                                                                                                             |

| Co-device                                   | In a phase leg of a converter made up of two devices the                                                                                                                                                            |

|                                             | co-device refers the the other device in the leg                                                                                                                                                                    |

| DC-link                                     | The converters connection to a DC voltage supply                                                                                                                                                                    |

| Galvanic isolation                          | A design technique that allows the transfer of signals but                                                                                                                                                          |

|                                             | not current between two points by removing any direct                                                                                                                                                               |

|                                             | conduction path                                                                                                                                                                                                     |

| LCR meter                                   | A device for measuring inductance, capacitance and resis-                                                                                                                                                           |

|                                             |                                                                                                                                                                                                                     |

|                                             | tance                                                                                                                                                                                                               |

| Op-amp                                      | tance<br>Operational Amplifier                                                                                                                                                                                      |

| Op-amp<br>Scattering parameter              |                                                                                                                                                                                                                     |

|                                             | Operational Amplifier                                                                                                                                                                                               |

|                                             | Operational Amplifier<br>Parameters describing the behaviour of an electrical net-                                                                                                                                  |

| Scattering parameter                        | Operational Amplifier<br>Parameters describing the behaviour of an electrical net-<br>work under a steady state excitation (S-parameter)                                                                            |

| Scattering parameter                        | Operational Amplifier<br>Parameters describing the behaviour of an electrical net-<br>work under a steady state excitation (S-parameter)<br>A measure of the frequency at which the switching tran-                 |

| Scattering parameter<br>Switching frequency | Operational Amplifier<br>Parameters describing the behaviour of an electrical net-<br>work under a steady state excitation (S-parameter)<br>A measure of the frequency at which the switching tran-<br>sients occur |

| Switching speed | The switching speed (switching rate/switching time/tran-     |

|-----------------|--------------------------------------------------------------|

|                 | sition time) refers to how fast the switching device transi- |

|                 | tions between the on and off states                          |

## List of Acronyms

| AC   | Alternating Current                     |

|------|-----------------------------------------|

| AGC  | Active Gate Control                     |

| ASIC | Application Specific Integrated Circuit |

| AWG  | Arbitrary Waveform Generator            |

| BJT  | Bipolar Junction Transistor             |

| CDCM | Continuous Derivative Control Method    |

| СМ   | Common Mode                             |

| CMRR | Common Mode Rejection Ratio             |

| CWT  | Continuous Wavelet Transform            |

| DC   | Direct Current                          |

| DFT  | Discrete Fourier Transform              |

| DPT  | Double Pulse Test                       |

| DUT  | Device Under Test                       |

| EM   | Electromagnetic                         |

| EMC  | Electromagnetic Compliance              |

| EMI  | Electromagnetic Interference            |

| EPC  | Equivalent Parallel Capacitance         |

| ESR  | Equivalent Series Resistance            |

| FEA  | Finite Element Analysis                 |

| FFT  | Fast Fourier Transform                  |

| FT   | Fourier Transform                       |

| GaN  | Gallium Nitride                         |

| GUI  | Graphical User Interface                |

| IGBT          | Insulated-Gate Bipolar Transistor                 |

|---------------|---------------------------------------------------|

| JFET          | Junction gate Field-Effect Transistor             |

| MOSFET        | Metal-Oxide-Semiconductor Field-Effect Transistor |

| MPS           | Merged-PIN-Schottky diode                         |

| РСВ           | Printed Circuit Board                             |

| RRC           | Reverse Recovery Current                          |

| SBD           | Schottky Barrier Diode                            |

| Si            | Silicon                                           |

| SiC           | Silicon Carbide                                   |

| STFT          | Short-Time Fourier Transform                      |

| VNA           | Vector Network Analyser                           |

| wide band gap | Wide Band Gap                                     |

| WT            | Wavelet Transform                                 |

## **List of Functions**

| Dirac  | The Dirac delta function     |

|--------|------------------------------|

| sinc() | $sinc(x) = \frac{sin(x)}{x}$ |

# List of Symbols

| $C_{DS}$          | MOSFET output capacitance (equivalent to $C_{OSS}$ ) |

|-------------------|------------------------------------------------------|

| $C_{OSS}$         | MOSFET output capacitance                            |

| $C_{pp}$          | PCB pad-to-pad capacitance                           |

| D                 | Smoothness of a waveform                             |

| dI/dt             | Rate of change of current                            |

| dV/dt             | Rate of change of voltage                            |

| $\epsilon_{crit}$ | Material critical field strength                     |

| $E_g$             | Band gap                                             |

- $\mu$  Electron mobility

- *I*<sub>D</sub> MOSFET drain current

- j The square root of -1

- $\varepsilon_r$  Relative permittivity

- *s* Complex frequency as used with the Laplace transform

- $V_{DS}$  MOSFET drain source voltage

- $V_{GS}$  MOSFET gate source voltage

#### **Memorandum**

The accompanying thesis "Mitigation of The Influence of Parasitic Elements in Wide-Bandgap Power Converters" is based on work carried out by the author in the Department of Electrical and Electronic Engineering of the University of Bristol.

The main contributions claimed by the author are as follows:

- Development of a highly accurate simulation model for SiC MOSFETs based in the freeto-use LTspice simulation package

- A technique for designing an inductor for the purpose of mitigating the influence of the load capacitance on the converter performance

- A technique for analysing experimentally obtained power converter waveforms using exemplary waveform shapes for comparison to identify the temporal source of frequency domain characteristics

- A demonstration of a metric that can be effectively used to quantify both the smoothness and Electromagnetic Interference (EMI) generation capability of experimentally obtained waveforms

- A demonstration that the use of smoothed waveforms can mitigate the influence of many parasitic elements of a power converter

- A design of a predominantly passive waveform profiling gate drive circuit capable of achieving some of the advantages of a fully active linear gate driver with far lower complexity and cost

**PUBLICATIONS**

This research has resulted in, or contributed to, the following publications:

### **Conference Papers**

- S. Walder and X. Yuan, "Effect of load parasitics on the losses and ringing in high switching speed SiC MOSFET based power converters," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 6161-6168.

- A. Charalambous, X. Yuan, N. McNeill, S. Walder, Q. Yan and C. Frederickson, "Controlling the output voltage frequency response of the auxiliary commutated pole inverter," *IECON* 2016 - 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, 2016, pp. 3305-3310.

- S. Walder, X. Yuan, I. Laird and J. J. O. Dalton, "Identification of the temporal source of frequency domain characteristics of SiC MOSFET based power converter waveforms," 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, 2016, pp. 1-8.

- S. Walder, X. Yuan, "Waveform Profiling as a Tool for Suppressing the Influence of Parasitic Elements," 9th International Conference on Power Electronics, Machines and Drives (PEMD 2018), Manchester, 2018

- S. Walder, X. Yuan, Q. Yan, "SiC MOSFET Switching Waveform Profiling Through Passive Networks," 44th Annual Conference of IEEE Industrial Electronics Society, 2018. IECON 2018, [in press, accepted: 18th July 2018].

#### **INTRODUCTION**

his thesis describes the motivation for, approach to, and results of, the body of research undertaken by the author between 2014 and 2018. The work, under the title "Mitigation of The Influence of Parasitic Elements in Wide-Bandgap Power Converters" considers the influence of parasitic circuit elements on the performance of a power converter, and explores techniques for mitigating these effects.

### 1.1 Background

#### 1.1.1 Power Conversion

In electronics, "power converter" refers to any circuit or system which transforms electrical energy from one form to another. Typical examples of power converter functions are conversion from Alternating Current (AC) to Direct Current (DC), changing voltage, or changing current. Historically, many power conversion applications have been achieved using passive systems transformers for change in AC voltage and resistive voltage divides for DC voltage reduction. More recently, active circuits have been employed for these conversion applications.

Power converters are used in a huge range of applications; they are found in distribution grids, industrial drives, traction applications, and consumer applications to name a few. They

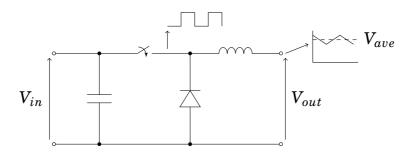

Figure 1.1: Model of a basic (Buck) power converter

handle the transfer of electrical power from milliwatts to megawatts and are critical to many technologies. With power converters handling so much electrical energy, their efficiency is extremely important - in many applications they reduce the power consumption significantly. Power converters are essential for integrating low carbon generation technologies into the grid and for ensuring that electrical energy is used efficiently.

Previously, power conversion has relied on transistors operating in their linear region - these would dissipate energy as they reduced the voltage to the required level. More modern power converters are of the switched-mode type. In these converters the fundamental operating principle is to reduce a voltage by turning on and off a supply at high frequency - this produces a rectangular voltage waveform which is then averaged. Figure 1.1 illustrates a basic switching mode converter - the switch creates a rectangular waveform, which is then averaged by the inductor and diode arrangement. The output voltage can then be regulated by varying the ratio of time the switch is on, or off.

Switched-mode converters achieve very high efficiencies and power densities. This is because the transistor implementing the switching device is operated in either the blocking state (off) or the conducting state (on) and only transiently in the linear region. With modern transistors having very high off-state resistance and low on-state resistance, most of the remaining loss is from the time spent transitioning between states. These very low losses have other system level benefits such as reduced heatsink volume, and reduced converter size. Operating the switch at high frequency also benefits the power density, as the size of the passive elements in the system can be greatly reduced.

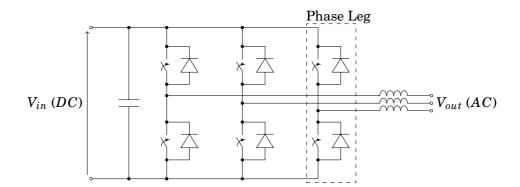

A common switched-mode converter design is that of the three-phase inverter. In this design

Figure 1.2: Model of a three phase converter

DC is switched so as to produce three phases of AC. This is a common converter as the DC supply can be created from rectified mains, and the output voltage and frequency can be varied, making it an ideal topology for driving an AC motor. Each phase is created using two switching devices, as this allows for current to be returned into the phase through the lower of the two devices. An example of such a converter is illustrated in fig. 1.2. As this is such a common converter topology, a single 'phase leg' (as labelled) of it will be used as the test circuit in this work.

#### 1.1.2 Switching Devices

The circuits in figs. 1.1 and 1.2 have been illustrated using an ideal switch. In reality this is not a practical component to use and a semiconductor device will be used to implement this. With a view for maximising the efficiency, this semiconductor device should be like the perfect switch in that it should have an infinite off-state resistance, and zero on-state resistance. It should also be able to transition between these states instantaneously - though later this will be found not to be ideal from the perspective of EMI generation.

Presently there is a large range of semiconductor devices that could be used to implement the switching cell. These include:

- The MOSFET

- The Bipolar Junction Transistor (BJT)

- The Insulated-Gate Bipolar Transistor (IGBT)

- Thyristors

Figure 1.3: Illustration of the position of gate drivers in a typical half bridge

Each of these devices can be sourced in a variety of ratings, and more recently, many of these devices have also been produced in Wide Band Gap materials - a technology which is discussed in detail in section 2.1.

To operate these devices requires the application of a control signal. In the case of MOSFETs and IGBTs the gate terminal of the device is insulated from the conducting terminals - allowing control through application of a voltage signal. In the case of the other devices, control must be realised through application of a small current to the base terminal of the device.