Copyright

by

Abhishek Tondon

2013

The Report Committee for Abhishek Tondon Certifies that this is the approved version of the following report:

Performance Impact of Programmer-Inserted Data Prefetches for Irregular Access Patterns with a Case Study of FMM VList Algorithm

# APPROVED BY SUPERVISING COMMITTEE:

Supervisor:

Lizy K John

George Biros

# Performance Impact of Programmer-Inserted Data Prefetches for Irregular Access Patterns with a Case Study of FMM VList Algorithm

by

## Abhishek Tondon, B. Tech.

## Report

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## Master of Science in Engineering

The University of Texas at Austin December 2013

## Acknowledgements

I would like to acknowledge the cooperation extended by Dhairya Malhotra, M. Tech, Graduate Student at the Institute for Computational Science, Engineering and Mathematics, The University of Texas at Austin, by letting me use the code authored by him as a Case Study for this report. The experiments conducted for this report use the FMM V-list kernel written by Dhairya as the baseline code, in which I insert software prefetches at strategic points to showcase the performance improvements brought by programmer inserted prefetches. An excerpt of the code is included in Appendix B. Additionally, in section 4.1, I rely on the paper lead-authored by Dhairya to present an overview of the FMM algorithm on a part of which the case study is performed.

#### Abstract

# Performance Impact of Programmer-Inserted Data Prefetches for Irregular Access Patterns with a Case Study of FMM VList Algorithm

Abhishek Tondon, M.S.E.

The University of Texas at Austin, 2013

Supervisor: Lizy K John

Abstract: Data Prefetching is a well-known technique to speed up applications wherein hardware prefetchers or compilers speculatively prefetch data into caches closer to the processor to ensure it's readily available when the processor demands it. Since incorrect speculation leads to prefetching useless data which, in turn, results in wasting memory bandwidth and polluting caches, prefetch mechanisms are usually conservative and prefetch on spotting fairly regular access patterns only. This gives the programmer with a knowledge of application, an opportunity to insert fine-grain software prefetches in the code to clinically prefetch the data that is certain to be demanded but whose access pattern is not too obvious for hardware prefetchers or compiler to detect.

In this study, the author demonstrates the performance improvement obtained by such programmer-inserted prefetches with the case study of an FMM (Fast Multipole Method) VList application kernel run with several different configurations. The VList computation requires computing the Hadamard product of matrices. However, the way each node of the octree is stored in the memory, leads to indirect accessing of elements where memory accesses themselves are not sequential but the pointers pointing to those memory locations are still stored sequentially. Since compilers do not insert prefetches for indirect accesses, and to hardware, the access pattern appears random, programmer-inserted prefetching is the only solution for such a case. The author demonstrates the performance gain obtained by employing different prefetching choices in terms of what all structures in the code to prefetch and which level of cache to prefetch those to and also presents an analysis of the impact of different configuration parameters on performance gain. The author shows that there are several prefetching combinations which always bring performance gain without ever hurting the performance, and also identifies prefetching to L1 cache and prefetching all data structures in question, as the best prefetching recommendation for this application kernel. It is shown that this one combination gets the highest performance gain for most run configurations and an average performance gain of 10.14% across all run configurations.

## **Table of Contents**

| 1 | Introduc | ction                                      | 1    |

|---|----------|--------------------------------------------|------|

| 2 | Backgro  | ound Details                               | 5    |

|   | 2.1      | Hardware versus Software prefetching       | 5    |

|   | 2.2      | Previous Work                              | 6    |

|   | 2.3      | Current State of the art                   | 7    |

|   | 2.4      | Programmer Inserted Prefetches             | 8    |

| 3 | Measure  | ement Infrastructure                       | 9    |

|   | 3.1      | Intel VTune                                | 9    |

|   | 3.2      | PAPI                                       | 10   |

|   | 3.3      | SPEC Validation of PAPI                    | 11   |

| 4 | Case Stu | udy Details                                | 13   |

|   | 4.1      | Overview of FMM                            | 13   |

|   | 4.2      | Prefetchability scenario                   | 16   |

|   | 4.3      | System specification                       | . 18 |

|   | 4.4      | Experiment configurations                  | 18   |

| 5 | Results  | and Analysis                               | 21   |

|   | 5.1      | Broader results                            | . 21 |

|   | 5.2      | Impact of prefetch choices                 | 23   |

|   | 5.3      | Impact of prefetch destination             | . 24 |

|   | 5.4      | Impact of uniform/non-uniform distribution | . 25 |

|   | 5.5      | Impact of MPI/OpenMP configuration         | 26   |

|   | 5.6      | Impact of Co-processor offloading          | 27   |

|   | 5.7      | Impact of Compiler Prefetching             | 28   |

|   | 5.8      | Result tables and graphs                   | 29   |

| 6 | Conclus  | sion                                       | . 45 |

| Appendix A    | PAPI Code Insertions                     | 46 |

|---------------|------------------------------------------|----|

| Appendix B    | Programmer Inserted Prefetches in code   | 47 |

| Appendix C.1  | -C.16 Raw Dataset for all configurations | 48 |

| Bibliography. |                                          | 64 |

## **1 INTRODUCTION**

Processors run faster than memories. And the processors cannot work unless they have the data to work with. The data resides in memory, and therefore programs have loads and stores. Clearly, if an instruction is waiting on a load from memory, even with out-of-order processors, all instructions truly dependent on that, will have to wait as well. The more loads we have in our applications, the more the number of dependent instructions on those loads. Therefore, to have an idea of how severe is the impact of this 'memory wall' problem, we can look at the fraction of loads/stores versus computation operations in the applications of concern.

Table 1, taken from the work by Phansalkar et. al. [1] lists the instruction mix of SPECCPU2006 benchmarks. There also we see that the percentage of loads and stores as a fraction of total instruction approaches 50% in few cases and is above 40% in many of them.

| Integer Benchmarks | % Branches | % Loads | % Stores |

|--------------------|------------|---------|----------|

| 400.perlbench      | 23.3%      | 23.9%   | 11.5%    |

| 401.bzip2          | 15.3%      | 26.4%   | 8.9%     |

| 403.gcc            | 21.9%      | 25.6%   | 13.1%    |

| 429.mcf            | 19.2%      | 30.6%   | 8.6%     |

| 445.gobmk          | 20.7%      | 27.9%   | 14.2%    |

| 456.hmmer          | 8.4%       | 40.8%   | 16.2%    |

| 458.sjeng          | 21.4%      | 21.1%   | 8.0%     |

| 462.libquantum     | 27.3%      | 14.4%   | 5.0%     |

| 464.h264ref        | 7.5%       | 35.0%   | 12.1%    |

| 471.omnetpp        | 20.7%      | 34.2%   | 17.7%    |

| 473.astar          | 17.1%      | 26.9%   | 4.6%     |

| 483.xalancbmk      | 25.7%      | 32.1%   | 9.0%     |

| FP Benchmarks | % Branches | % Loads | % Stores |

|---------------|------------|---------|----------|

| 410.bwaves    | 0.7%       | 46.5%   | 8.5%     |

| 416.gamess    | 7.9%       | 34.6%   | 9.2%     |

| 433.milc      | 1.5%       | 37.3%   | 10.7%    |

| 434.zeusmp    | 4.0%       | 28.7%   | 8.1%     |

| 435.gromacs   | 3.4%       | 29.4%   | 14.5%    |

| 436.cactusADM | 0.2%       | 46.5%   | 13.2%    |

| 437.leslie3d  | 3.2%       | 45.4%   | 10.6%    |

| 444.namd      | 4.9%       | 23.3%   | 6.0%     |

| 447.dealll    | 17.2%      | 34.6%   | 7.3%     |

| 450.soplex    | 16.4%      | 38.9%   | 7.5%     |

| 453.povray    | 14.3%      | 30.0%   | 8.8%     |

| 454.calculix  | 4.6%       | 31.9%   | 3.1%     |

| 459.GemsFDTD  | 1.5%       | 45.1%   | 10.0%    |

| 465.tonto     | 5.9%       | 34.8%   | 10.8%    |

| 470.lbm       | 0.9%       | 26.3%   | 8.5%     |

| 481.wrf       | 5.7%       | 30.7%   | 7.5%     |

| 482.sphinx3   | 10.2%      | 30.4%   | 3.0%     |

Table 1 - SPECCPU2006 benchmarks instruction mix for combined inputs

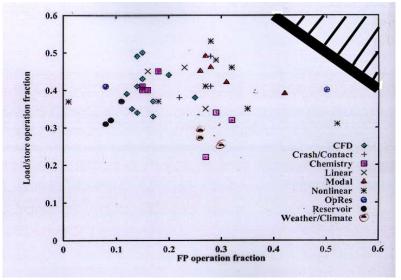

Figure 1 below from a talk given by John McCalpin [2] on an Industry Perspective on Performance Characterization, presents a scatter plot of the same for most common scientific applications. We see that this fraction is a good  $\sim$ 30%-50% for a good population of applications.

Figure 1 - Fraction of memory instructions in Scientific applications (Source: [2])

The takeaway from the figure and the table above is that there are simply too many memory instructions to take the problem lightly. But then, we have had a solution in the form of caches. Owing to the growing gap between processor and memory speeds, these days, we have up to 3 levels of those. So, should that not solve this problem?

The answer in this regard is a yes and a no. Caches are good when data is being reused. We need some data, we bring it from memory, place a copy in the cache closer to the processor, and work with this copy until an eviction is required, at which time, it is written back to memory, assuming a simplistic single core view. But, for the first time we need this data, it's not in the cache, we have a cold miss and we wait for it to arrive from the memory (or next level cache, as the case might be). We benefit only when the same data is accessed next time because of temporal locality, or we benefit when there is spatial locality so that the cache line we brought into the cache at the previous miss, also contains some data that we might need next.

While bringing more data than requested finds justification due to the property of spatial locality, another way to look at it is, "bringing data before it is demanded", which is nothing but a form of data prefetching.

Thus, even without any hardware prefetchers or any compiler or software prefetching, the very act of bringing a cache line which contains some data that is not yet demanded, but, due to spatial locality, is likely to be demanded in near future, can be termed as data prefetching. This underlines how fundamental Data Prefetching is to caching itself.

However, there is a difference too. There has to be some finite granularity at which the data will be brought from lower level memory to a higher level cache. That granularity is the cache line size. Since the cache line does contain the data that was requested, irrespective of whether the extra contiguous data that's being brought in the cache line, is used or not, that data would have to accompany the data that was actually demanded. This is where data prefetching defers.

In data prefetching, we bring into cache a line that contains none of the data that was demanded. Rather, we bring data closer to the processor on the basis of speculation rooted in access patterns that that data would be demanded in near future. This speculation can be performed either in hardware by hardware prefetchers or in software, either by compiler at higher optimization levels or by programmers by inserting prefetches in the application code.

Both hardware and software approaches have their pros and cons. We'll look at them in Chapter 2 while discussing briefly the previous work done in both fields. However, both the hardware prefetchers as well as the compilers can detect fairly regular access patterns only. They tend to be conservative due to the reason that there is a cost involved with prefetching. The cache space is limited and any data that's being prefetched into the cache, would evict some other data. If the speculation was incorrect and prefetched data was not something that would be used in near future, it means polluting the cache and also wasting the precious memory bandwidth. That could potentially hurt the performance instead of helping. That's why these prefetch mechanisms get activated only when the access patterns are fairly regular and result in high confidence level in terms of next accesses.

This is where this study comes into picture. Using the tools described in Chapter 3, this author works on an application kernel, FMM (Fast Multipole Method) VList (described in Section 4.1), which has complex access patterns where hardware prefetchers and compiler inserted prefetches are unlikely to help, and manually insert fine-grain conditional prefetches. The goal is to corroborate the hypothesis that programmer inserted prefetches are indeed likely to bring performance improvement in an application having complex or irregular access patterns. In the course of this study, this author inserts prefetches at strategic points in the FMM VList kernel, and profiles the performance in terms of absolute number of processor cycles taken to execute that.

Hardware prefetchers remain on (default configuration) for all the experiments. Compiler prefeching is turned off and on and does not seem to make any difference in most cases. Several other knobs too are tweaked and the performance gains thus obtained, are profiled. The details of those knobs are covered in Section 4.4 and their impact is discussed through section 5.2 to 5.7. Section 5.8 presents the data and comparison results and a conclusion is drawn on that basis which is presented in Chapter 6. The raw data of these experiments is also included as Appendix C.1 to C.16.

## **2** BACKGROUND DETAILS

In this chapter, in the first section, a general comparison of hardware and software prefetching is presented, followed by a brief overview of previous work in the field of hardware and software prefetching, the current state of the art and relevant details on programmer inserted prefetches.

## 2.1 Hardware versus Software prefetching

Broad differences between the two flavors of prefetching are summarized in Table 2 below. Both have their own advantages and disadvantages based on which the preferred one is employed as the use case might require. It's evident from the table that for applications involving irregular access patterns, software prefetching is the solution, that too, programmer inserted ones, as will be clear from section 2.3.

| Hardware Prefetchers             | Software Prefetchers                                          |

|----------------------------------|---------------------------------------------------------------|

| Regular access patterns          | Irregular access patterns                                     |

| Start-up penalty, more wastage   | Doable for smaller ranges with no wastage                     |

| Won't cross page boundaries      | Page boundaries crossable                                     |

| Works with existing applications | Need source modification                                      |

| Sequential and strided prefetch  | Compiler inserted, Programmer inserted                        |

| Prefetch into fixed cache levels | Prefetch to L1, L2, L3, Non-Temporal<br>Aligned (NTA) buffers |

Table 2 - Differences between Hardware and Software prefetching

### 2.2 **Previous Work**

Anacker and Wang [4] were the earliest to show the improvements of fetching sequential cache lines beyond just the required word. Their work became the basis of variants like One Block Lookahead [11] and Sequential Prefetching [10] where a block would be prefetched at every access versus at a miss. Another variant, called tagged prefetching [7], involved prefetching a block only if the previously prefetched block was used. A method for measuring the dynamic spatial locality of a program was also proposed by Dahlgran [6] as a means to dynamically control the number of blocks to prefetch ahead. Later called, Adaptive Sequential Prefetching, this scheme was conservatively added to Intel's NetBurst Microarchitecture [8] for prefetching to Unified L2 cache.

Chen and Baer [5] went a step ahead and proposed Stride prefetching combined with the adaptive property of Dahlgran's design. A 2004 survey by Perez. et. Al [9] showed that Stride Prefetching was superior to other mechanisms in terms of performance and power both. Subsequently, this was added to Intel's core microarchitecture.

With regard to software prefetching, Callahan et. al. [13] were the first to propose using a non-blocking prefetch instruction in 1991, and they were able to show >99% hit ratio for demand requests with prefetching on, for their set of benchmarks. Subsequently, an Integrated scheme for Hardware/Software Data prefetching was proposed [14] by Edward Gornish of University of Illinois in 1994 for Shared Memory Multiprocessors. They showed that an Integrated scheme performed better than plain hardware prefetching because of its ability to handle more complex patterns and better than software only approach as it required fewer instructions. Other prominent related work in this domain includes a study of the interaction of Software prefetching with ILP processors in shared memory systems by Parthasarthy et.al. [15] in 1997 and one studying its efficacy for future memory systems by Badawy et. al. [16] in 2004, among others.

### 2.3 Current State of the art

Present day Intel processors have more than one type of hardware prefetchers. Intel's website says that the Core i7 and Xeon 5500 series processors have prefetchers that can prefetch into either L2 only or both L1 and L2. They employ more than one algorithms too, which include simpler ones such as fetching 2 cache lines instead of one, when a demand is made, and more sophisticated ones that involve monitoring the access patterns of a cache.

With regard to software prefetching, modern compilers come equipped with the capability to insert prefetches on their own. Compiler prefetching is turned on by default for Optimization level O2 and above for Intel C Compiler for the Knights' Corner platform being used in this experiment. The architecture supports several instructions. Vprefetch1 instruction brings a 64 byte cache line into L2 cache and vprefetch0 pulls it into L1 cache. Their corresponding variations vprefetche1 and vprefetchet0 do the same while additionally marking the prefetched line as exclusive [12].

The compiler can issue prefetches for all regular memory accesses inside loop [12]. In the process of determining prefetch distances, the compiler takes into account the latency of accessing the target level in memory hierarchy and the expected total latency of the loop to complete its one iteration. Compiler can also generate initial value prefetches before entering a loop to help even the first few iterations. However, compiler does not issue any prefetching for indirect accesses of the form a[b[i]]. Such cases need

to be handled by programmer inserted manual prefetches, which is what is exploited in this work.

To avoid interfering with programmer inserted prefetches, the compiler prefetching can be disabled by using the compile-time switch **-no-opt-prefetch**.

## 2.4 Programmer Inserted Prefetches

Programmer can insert prefetches using the \_mm\_prefetch() compiler intrinsic. This takes 2 arguments, first of which is a character pointer pointing to the address to start the prefetch from. The second argument can take one of the 4 following values.

| MM_HINT_T0   | Prefetch into L0 cache                     |

|--------------|--------------------------------------------|

| _MM_HINT_T1  | Prefetch into L1 cache                     |

| _MM_HINT_T2  | Prefetch into L2 cache                     |

| _MM_HINT_NTA | Prefetch into Non-temporal aligned buffers |

#### Table 3 - Prefetch destination for Programmer Inserted Prefetching

Since the caches are inclusive, prefetching to a higher level of cache essentially means prefetching to all levels below it. Prefetching into Non-temporal aligned buffers is useful when the prefetched data is not likely to exhibit temporal locality and therefore, it's not desired to occupy cache space for that data. The header file mmintrin.h needs to be included to use this intrinsic.

### **3 MEASUREMENT INFRASTRUCTURE**

Since this research is about measuring performance gain, it becomes critical to select the right tool(s) which provide(s) trustworthy results. Hardware Performance Counter tools come to mind as natural choice. The tools considered for this research included Intel VTune Amplifier XE 2013 and PAPI (Performance Application Programming Interface) which are discussed in the sections 3.1 and 3.2. The last section of the chapter covers information about validating the chosen tool.

#### 3.1 Intel VTune

The foremost reason behind picking Intel VTune was the availability of a vast set of processor events that are directly measurable with this tool. Coming from the processor manufacturer Intel itself, there was little to doubt the accuracy of the numbers provided by the tool. Moreover, the tool did not require changes in the source and just launching the tool and running the application with command line arguments or with GUI, let's one obtain the events one wants.

However, in the case of this study, this author found severe inconsistencies in the data obtained using VTune. The numbers were wildly fluctuating, often to the order of 30% or more. Clearly, such a high level of variability could not be tolerated.

There were a couple of reasons that this author suspected, were causing this behavior. The first one is inherent to VTune which is that it's based on sampling. It does not keep an accurate count but samples the counters at regular intervals. The sampling interval is chosen by the tool itself using its inbuilt algorithms and the number of events that are being counted, although that can be overridden.

As a first measure, reducing the number of events to make way for finer sampling interval, did not seem to make any difference. The variations remained as wide.

As second measure, this author turned off power cycling, which were suspected to be another reason behind wild variations as it could be causing error in multiplication factors if processor changes its operating frequency in the middle of the run. Unfortunately, even this change did not seem to help VTune numbers stabilize.

Consequently, this author had to abandon the tool and discard the datasets obtained with VTune.

## **3.2 PAPI**

After having an unsatisfactory experience with VTune, this author decided to switch to PAPI [3]. PAPI, Performance Programming Application Interface, specifies a standard API for accessing hardware counters available on the processor.

Evidently, PAPI requires changes in the source of the application. However, it also easily facilitates measuring counters for a specific part of the application. This was a requirement for this research the the FMM VList kernel that this research considers as a Case Study for Programmer Inserted prefetches, is only a part of the complete FMM algorithm.

In this research, the low level interface of PAPI was used. The low level interface allows dealing with hardware events by creating EventSets. Low level functions such as PAPI\_add\_event, PAPI\_start and PAPI\_stop are called in addition to PAPI\_create\_eventset. The code added for PAPI profiling is only a few lines and is included in Appendix A.

We measure the following preset events among others, PAPI\_L1\_DCM, PAPI\_L2\_DCM, PAPI\_L3\_TCM, PAPI\_TOT\_CYC, PAPI\_LD\_INS, PAPI\_TOT\_INS for one thread which, for our configurations, will cover 1/16<sup>th</sup> of the complete task.

Table 4 lists these events and its meanings.

| PAPI Preset Event | Meaning of the event (all events per thread) |

|-------------------|----------------------------------------------|

| PAPI_L1_DCM       | L1 D-cache misses                            |

| PAPI_L2_DCM       | L2 D-cache misses                            |

| PAPI_L3_TCM       | L3 Total cache misses                        |

| PAPI_LD_INS       | Load instructions count                      |

| PAPI_TOT_INS      | Total instructions count                     |

| PAPI_TOT_CYC      | Total cycles taken                           |

| PAPI_DP_OPS       | Floating point operations                    |

#### **Table 4 - PAPI Event descriptions**

Since there are only 5 hardware counters available on the processor, two runs are required to get one set of all these events. Unlike VTune, PAPI numbers show very small variations, of about 2%. To be accurate, 10 runs are made for each run configuration to obtain 5 sets of all event values. Trimmed averages of each such groups are computed and those raw datasets for all run configurations are reported in Appendices C.1 to C.16.

#### **3.3 SPEC Validation of PAPI**

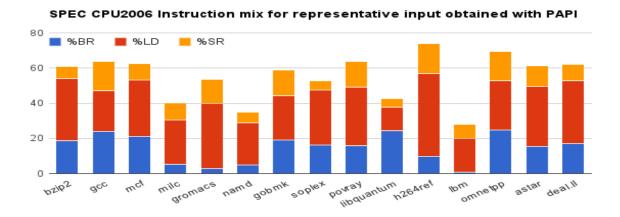

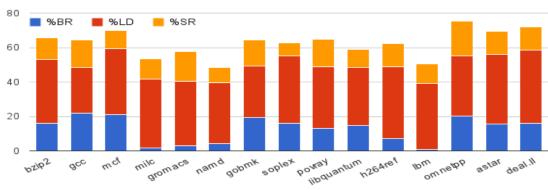

As an additional check on the veracity of the numbers reported by PAPI, an analysis of select SPEC CPU2006 benchmarks was undertaken. 15 Integer and Floating point SPEC benchmarks were picked (the ones with code in C or C++) and PAPI calls were inserted in them. The event set for this test comprised PAPI\_BR\_INS (branch instruction count) and PAPI\_SR\_INS (store instruction count) in addition to PAPI\_LOAD\_INS, and PAPI\_TOT\_INS so as to calculate Instruction mix. The representative reference input sets for those benchmarks which had multiple input sets,

were chosen based on [1]. The instruction mix of these benchmarks are plotted in Figure 2. Figure 3 plots the instruction mix for the same benchmarks as reported in [1] which we use as reference. It is evident that our instruction mix of Figure 2 is visibly close to the reference mix of Figure 3. The slight differences can be attributed to compiler optimizations which have taken place over the duration since [1] was written and also to the fact that for benchmarks with multiple inputs, our instruction mix relies on the representative input sets, which, therefore, results in close but not identical instruction mix.

Figure 2 - SPEC CPU2006 Instruction mix with PAPI

Reported SPEC CPU2006 Instruction mix combined input set

Figure 3 - SPEC CPU2006 Instruction mix reference as reported in [1]

## **4 CASE STUDY DETAILS**

In this chapter, an introduction of the FMM algorithm is presented in section 4.1 with an emphasis of VList computation, which is that step of the algorithm, which forms the focus of this study. In section 4.2, the prefetching scenario is explained highlighting how there is a case for programmer inserted prefetches in this application kernel. The specification of the system on which all experiments are run, is covered in section 4.3 and different experiment configurations are discussed in section 4.4.

### 4.1 Overview of FMM

FMM, or Fast Multipole Method, is an algorithm for computing volume potentials used to construct spatially adaptive solvers for Poisson and Stokes' equations. Computation domain is partitioned hierarchically by using an Octree structure. Given a set of M point sources with individual charge strengths and N target points, FMM calculates the total potential at each target point. This is essentially an N-body problem which involves pairwise interactions among system of N particles. The inherent complexity for such a problem would be  $O(N^2)$  but FMM reduces that by using approximations for far interactions. A Far interaction is approximated by computing multipole expansion, multipole-to-local translation, and evaluating local expansion. The following paragraphs in this section, which draw an explanation from Malhotra et. al's paper [17], explain the concept.

Both the multipole expansion as well as the local expansion for a node are represented by sets of source points on an equivalent surface around the node such that it produces the same potential at the points on a check surface as the original source points. To distinguish between the two, upward-equivalent and upward check surfaces are used for multipole expansion and downward equivalent and downward check are used for local expansion. For a leaf node, potential at the check surface is computed due to source points, while for non-leaf nodes, the check surface potential from points on the equivalent surface of children is computed followed by computing the equivalent source intensities for leaf nodes.

The FMM algorithm involves an upward pass followed by a downward pass. In the upward pass, the octree is traversed postorder and multipole expansion of each node is computed. For the leaf nodes, it's computed directly from underlying source distribution, and for the non-leaf nodes, it's computed from the multipole expansion of its children. In the downward pass, a preorder traversal is performed, and local expansion are computed for each node. The local expansion of the parent node and the multipole expansions of those nodes which are at the same level as the node in question, and well-separated from it, but not well-separated from its parent node, are added to that. For leaf nodes, the final potential at target points is computed by first computing direct interactions from sources in adjacent leaf nodes and then adding contribution from local expansion.

For non-uniform distribution of points, which translates to adaptive octrees, the interactions are complex. Based on the type of interactions which in turn depend on the relative positions of nodes, all interactions can be classified into 4 lists - U, V, W and X lists. The U-list contains near interactions of the leaf nodes with itself or with an adjacent leaf node. U-list interactions are not approximated and are always computed accurately. The V-list includes contributions to the local expansion of a node from source nodes which are at the same depth in octree, lie completely outside the downward equivalent surface of the node and are within the equivalent surface of its parent node. The W-list includes source nodes that are at a finer level than the target node and for which the target node lies outside the upward check surface of their source octant, but which do not lie

outside the downward equivalent surface of the target node. For such interactions, multipole expansion of source node is used to evaluate the potential directly at target points. The last list, X-list includes source nodes which are leaf nodes, and are at a coarser level than the target node, and for which the target node is not outside its upward check surface but the source nodes are outside the downward-equivalent surface of the target node, allowing the local expansion to be constructed. For such interactions, the downward check potential at the target node is evaluated directly from the points in the source node.

| l |   | U                                                         | V V |   |

|---|---|-----------------------------------------------------------|-----|---|

|   | J | 0                                                         | V   | V |

| V | U | ·····                                                     | V   | V |

| V | U | U     U     U     U     W       W     W     W     W     W | V   | V |

| V | V | ~                                                         |     | / |

| V | V | Х                                                         |     |   |

Figure 4 - Interactions in a Quad-tree

It is difficult to graphically explain this for Octrees as the problem requires 3-dimensions, however, the same can be explained for quad-trees in 2-dimensions. Figure 4, drawn from [17], marks the nodes that'll go in different list w.r.t to the central node which is marked with stars, based on their positioning and level of granularity.

In this research, entire focus is on V-list computation step of the algorithm. Complex Hadamard product computation between vectors in Fourier space is needed for V-list computation. There are Interleaved source and target vectors for sibling octants. 8 elements are loaded from source and target vectors, one for each sibling, and then, all interactions are computed among those as matrix-matrix multiplications. The same is repeated for next octet. That is the kernel whose performance is targeted for optimization by custom inserting prefetches. The arrays and pointers of interest in this kernel and their access patterns are discussed in the next section.

#### 4.2 Prefetchability scenario

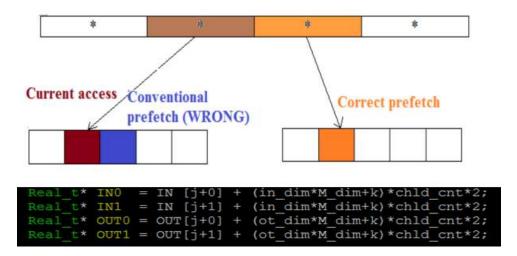

The V-list computation step involves the calculation of Hadamard product, which is element by element product for two matrices. However, because of the nature of the algorithm, the addressing is indirect. A simplified view of the same is shown in Figure 5.

Figure 5 - Simplified view of access patterns

As it's clear from the figure, an array of pointers stores a set of pointers which point to the some elements in an array. In the context of the attached code snapshot, IN and OUT are pointers. The relevant excerpt of the code is available in Appendix B. From the code in Figure 5, it's clear how IN0, IN1 and OUT0, OUT1 point to some element within IN and OUT which further point to some addresses. Since this assignment takes place inside a loop, whose counter is j, each time j changes, IN0, IN1, OUT0, OUT1 end up pointing to a new location. Since the subsequent code performs memory and multiplication operations on IN0, IN1, OUT0 and OUT1, those are the ones which require prefetching. However, those are neither sequential, nor strided, so hardware prefetchers cannot work on those. Since those are indirect accesses, compiler prefetching won't work on those either. In fact, an attempt to sequentially prefetch would only hurt the performance as in the next iteration of the inner loop, the consecutive next location of the IN0, IN1 or OUT0, OUT1 will not be accessed at all. As the Figure 5 depicts, the locations which are pointed by the next location in IN and OUT, will be accessed.

Therefore, programmer inserted prefetches are the only way to perform prefetching at all. Also, because this all is inside nested loops and j values keep getting reset at each iteration of the outer loop, it becomes important to take care of bound violations. Therefore, the prefetches need to be inserted conditionally and the prefetches need to be performed on IN and OUT instead of IN0, IN1, OUT0, OUT1, as those are the ones which move sequentially, at least within the inner loop iteration.

Other than IN and OUT, there is another pointer, M, which exhibits similar access pattern, albeit at an outer loop, thereby becoming a candidate for prefetch. This gives us several choices in terms of which all arrays to prefetch, and which all levels of cache to prefetch it to. Additionally, there is choice about in how much advance the prefetches should be made. For that, a cursory inspection of the code makes it clear that prefetching for the next iteration is the best. Reason being, there are lots of operations that take place within the inner most loop, which are sufficient to hide the latency of a prefetch. It is also worth mentioning that the code uses Intel AVX extensions and operates on a chunk of 128 byte data at a time. Since the size of a cache line is only 64 bytes, it becomes imperative to prefetch 2 cache lines each for IN0, IN1 and OUT0, OUT1, and M, if at all prefetching is being done for those. These configuration choices and several others are discussed and tabulated in section 4.4. A brief specification of the Stampede machine on which the experiments are conducted, is presented next.

#### 4.3 System specification

All the experiments are carried out on the Stampede Supercomputer of the Texas Advanced Computing Center (TACC). Each node of Stampede consists of 2 Xeon E5-2680 processors and a Xeon Phi SE 10P Coprocessor (referred as MIC). Each Xeon processor has 8 cores running at the frequency of 2.7 GHz. There is 32 KB of L1I Cache and L1D cache per core, and 256 KB of unified L2 Cache per core. There is 20 MB of shared L3 cache per processor (8 cores). Thus, each node has 16 cores and 32 GB memory per node.

#### 4.4 **Experiment configurations**

In addition to the choice of which all locations to prefetch and which cache levels to prefetch those to, there are several other configuration knobs that need attention.

Since this is a multi-threaded code, there is parallelism available in terms of MPI tasks and OpenMP threads. Since this kernel is a part of a complete algorithm, and cannot be made to run standalone, and the fact that there is only OpenMP parallelism within the VList kernel but number of MPI tasks determine how many of those kernels will run in parallel, also make the number of MPI tasks and OpenMP threads a variable to sweep. Since the algorithm has differences in terms of uniform versus non-uniform distribution, that's yet another variable. Also, while compiler prefetching apparently should not kick in within the kernel of concern, it can certainly affect other portions of the overall algorithm and the cache utilization therefore can affect the kernel too. So, keeping Compiler prefetching on versus keeping it off, is another configuration setting. Finally, the platform where this code is run, also has a coprocessor and parts of the complete algorithm (though not the VList kernel itself) can be offloaded to the coprocessor. That is another knob which can affect the impact of inserted prefetches. Therefore, all these

knobs are varied and the impact of inserted prefetches in profiled across the design space. Table 5(a) below summarizes all these configuration choices that're exercised in this experiment.

| What to prefetch         | No<br>prefetch            | Prefet<br>IN | ch   | Prefetch<br>IN, M<br>arrays |   | Prefetch<br>IN, OUT<br>arrays |        | Prefetch IN,<br>OUT, M<br>arrays |

|--------------------------|---------------------------|--------------|------|-----------------------------|---|-------------------------------|--------|----------------------------------|

| Where to prefetch        | To L1                     | -            | Го L | L2 To                       |   | To L3                         |        | To NTA                           |

| Distribution             | Ur                        | niform       |      | Non                         |   | Jon-ur                        | niform |                                  |

| Parallel threads setting | 1 MPI task<br>OMP threads | -            |      |                             | , |                               |        | MPI tasks, 1<br>IP thread/task   |

| Coprocessor offloading   |                           | OFF          |      | ON                          |   |                               | N      |                                  |

| Compiler prefetching     | OFF ON                    |              |      | N                           |   |                               |        |                                  |

#### Table 5(a) - Experiment Configurations

Some of these combinations are not allowed. For example, "What to prefetch" and "Where to prefetch" together result in 17 different prefetching combinations, 4 "What to prefetch" times 4 "Where to prefetch" and 1 "No prefetch". Note that the IN array is always prefetched if unless it's a no prefetch case. That's because the code cannot proceed until IN0 and IN1 are loaded. Also, with Coprocessor offloading ON, only one parallel thread setting, involving 1 MPI tasks and 16 OMP threads, is used. That's because of the way the overall code is structured, and each task needs parts of it offloaded to coprocessor. Thus, it results in 16 different run configurations. Those run configurations are listed in Table 5(b) below. That, multiplied with 17 prefetching combinations, i.e. 272 sets of values, multiplied with 10 runs made for each set.

Several scripts were written to make required code changes to build the binaries and launch the batch run scripts with required settings, generate the performance logs. The results are presented and analyzed in the next chapter.

| Sr.<br>No. | Configuration details                                                                                              | Section 5.8<br>Table/Fig. |

|------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1.         | No coprocessor offloading; 1 MPI task,16 OMP threads/task;<br>Uniform distribution; Compiler prefetching off       | 6                         |

| 2.         | No coprocessor offloading; 1 MPI task,16 OMP threads/task;<br>Uniform distribution; Compiler prefetching on        | 7                         |

| 3.         | No coprocessor offloading; 1 MPI task,16 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching off   | 8                         |

| 4.         | No coprocessor offloading; 1 MPI task, 16 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching on   | 9                         |

| 5.         | No coprocessor offloading; 4 MPI tasks, 4 OMP threads/task;<br>Uniform distribution; Compiler prefetching off      | 10                        |

| 6.         | No coprocessor offloading; 4 MPI tasks, 4 OMP threads/task;<br>Uniform distribution; Compiler prefetching on       | 11                        |

| 7.         | No coprocessor offloading; 4 MPI tasks, 4 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching off  | 12                        |

| 8.         | No coprocessor offloading; 4 MPI tasks, 4 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching on   | 13                        |

| 9.         | No coprocessor offloading; 16 MPI tasks,1 OMP threads/task;<br>Uniform distribution; Compiler prefetching off      | 14                        |

| 10.        | No coprocessor offloading; 16 MPI tasks, 1 OMP threads/task;<br>Uniform distribution; Compiler prefetching on      | 15                        |

| 11.        | No coprocessor offloading; 16 MPI tasks, 1 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching off | 16                        |

| 12.        | No coprocessor offloading; 16 MPI tasks, 1 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching on  | 17                        |

| 13.        | Coprocessor offloading on; 1 MPI task,16 OMP threads/task;<br>Uniform distribution; Compiler prefetching off       | 18                        |

| 14.        | Coprocessor offloading on; 1 MPI task,16 OMP threads/task;<br>Uniform distribution; Compiler prefetching on        | 19                        |

| 15.        | Coprocessor offloading on; 1 MPI task,16 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching off   | 20                        |

| 16.        | Coprocessor offloading on; 1 MPI task,16 OMP threads/task;<br>Non-uniform distribution; Compiler prefetching on    | 21                        |

## Table 5(b) - Run configurations and corresponding tables/figures in section 5.8

## 5 **RESULTS AND ANALYSIS**

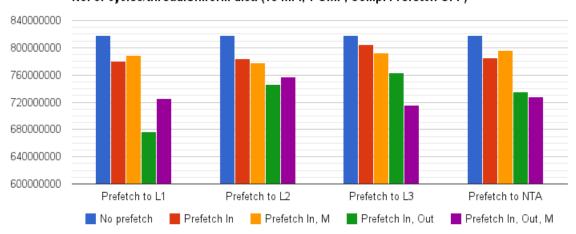

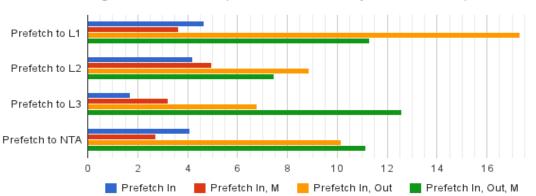

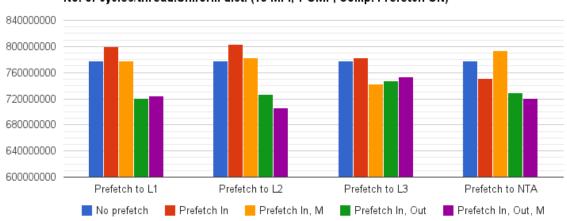

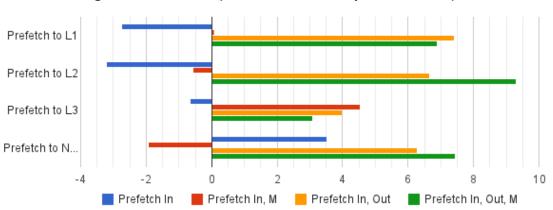

The 272 sets of values obtained as trimmed averages from 2720 runs are organized as sets of 17 prefetching options under 16 run configurations. All experiments were run for 150000 points in the N-body FMM problem. The raw datasets of trimmed averages are included in Appendix C.1 to C.16. Section 5.8 in this chapter includes the cycle count as the measure of performance and Tables 6 to 21 present those numbers. Absolute number of cycles are plotted for all 17 prefetching options for each of the 16 run configurations in Figure 6(a) to 21(a). The percentage gain/loss for each of the 16 prefetch combination against the 'no prefetch' baseline is plotted for each run configuration as well, in Figure 6(b) to 21(b). The broader results are summarized and analyzed in section 5.1. Sections 5.2 to 5.7 analyze the impact of each configuration or prefetching choice.

### 5.1 Broader results

Looking at the graphs 6(b) to 21(b), it is evident that in programmer inserted prefetches in general bring significant gains to the performance as manifested in the reduction in absolute number of processor cycles recorded in corresponding tables. There are few run configurations for which some prefetch combinations end up hurting performance, but those are those combinations which are never among the best performers for any run configurations. That is to say, the best prefetching choices never hurt the performance across any run configurations, and consistently bring significant gains across all.

In terms of prefetch destination, prefetching the data to either L1 cache or to NTA buffers brings the most gains. In fact, prefetching to L1 or prefetching to NTA buffers brings nearly the same performance gains for most run configurations which leads the author to believe that NTA buffers have the same access latency as the L1 cache. Strictly counting, prefetching to L1 cache is found to be the best for 10 out of 16 run configurations, while prefetching to NTA buffers is found to be the best for 5. There's an outlier in that regard for which prefetching to L2 yields the most benefit followed by prefetching to NTA buffers or L1 cache.

In terms of prefetch choices, prefetching all 3 arrays, IN, OUT and M turns out to be the best decision for 12 out of 16 run configurations. There are only 4 configurations for which not prefetching M array proves slightly better than prefetching M. Since M array is prefetched in an outer loop, there are fewer prefetches for it, and the impact is, either way, not substantial.

In general, it can be recommended that the programmer, for this application kernel, should insert prefetches on all 3 structures, IN, OUT and M, and should prefetch those into L1 cache. This, as per the results of this study, would ensure highest percentage performance gain for 8 out of 16 run configurations and second highest percentage performance gain for 4 out of the remaining. This combination of what-to-prefetch and where-to-prefetch performs better than any other combination across different run configurations. On an average, it provides 10.14% of performance gain across all run configurations which is only marginally lower than the average of the individual best prefetching combinations for each run configuration, that comes out to be 10.86%.

The Appendices C.1 to C.16 contain other useful data such as the absolute number of loads, total instructions, and cache misses at different levels. An important thing to note in this regard is that the absolute number of load instructions and consequently total instructions increases as more data is prefetched. The Xeon processor events to which PAPI cache miss preset events map to, are the ones which include both demand misses and prefetch misses. The same is reflected in increased number of absolute cache misses. Unfortunately, while Intel VTune offered events to separately count demand and prefetch misses, the same is not included in PAPI preset events which count both separately. Since unlike demand misses, prefetch misses do not cause the processor to keep waiting for the data, those prefetch misses do not harm the performance. On the contrary, prefetching ensures data is available for the next iteration at the right time, and the same is reflected in the reduction observed in the number of cycles required with prefetching versus no prefetching.

## 5.2 Impact of prefetch choices

Other than no prefetching, there are 4 prefetching choices that're studied and profiled in these experiments as listed in Table 5(a). A cursory look at the graphs 6 (b) to 21 (b) reveals that for 13 out of 16 run configurations, the best performance comes when all these 3 are being prefetched. In many cases, prefetching M or not prefetching it makes less difference than not prefetching OUT, and the reason lies in the fact that M is at a much outer loop in the nesting order, as compared to IN and OUT and therefore, undergoes far fewer prefetches. There are also 3 configurations where not prefetching M while still prefetching IN and OUT arrays proves slightly better than prefetches. There is no economical way to check if two prefetches are interfering in mutually destructive manner on an access by access basis, as even for a fixed configuration, there could be sets of accesses that could interfere constructively, and some other sets destructively. Repeated empirical runs are the only way to ascertain that, because all the address layout changes with so many factors including parallelization settings, type of distribution etc.

Since the idea behind tweaking all the prefetching choices and destination essentially was to come up with the best and consistent combination across all run configurations, it can be safely concluded, that prefetching all 3 locations, IN, OUT and M is the preferred choice.

#### 5.3 Impact of prefetch destination

In terms of prefetch destination, again looking at Figure 6(b) to 21(b) shows that the choice is between prefetching to either L1 cache or to the non-temporal aligned buffers. Prefetching to L2 or L3 yields less performance gains across all runs. Between prefetching to L1 and prefetching to NTA, in 10 out of 16 run configurations, prefetching to L1 gives the best performance along with corresponding prefetch data choice. Among the remaining, 5 have prefetching to NTA performing better but except one of them, the difference is marginal. It is only intuitive that prefetching the data closest to the processor would result in minimal latency and hence maximal performance gain as long as the prefetching choices are correct. Therefore, these results too make sense. Prefetching to NTA buffers for some configurations proves slightly better than prefetching to L1 cache as it would utilize L1 cache's limited space better. However, an important thing to keep in mind here is the fact that while the data brought into IN and OUT arrays is used only for one iteration, the data prefetched into M array is used for several iterations, and therefore, prefetching M array to NTA buffers contributes to lower gains. Again, since the objective is to find the general best prefetching combination across all runs which never hurts performance and provides consistent performance gain, it can be safely said that prefetching to L1 cache is the best bet.

#### 5.4 Impact of Uniform/Non-uniform distribution

Since there is significant difference in the way interactions behave in uniform versus non-uniform distribution of points, the vast difference between baseline performance is understandable. The distribution simply affects the net amount of work to be done and that reflects in the absolute number of cycles. That is inherent in the algorithm and has nothing to do with prefetches.

However, the difference in the relative performance gain due to prefetches should not be significant, as prefetches still work the same way. In that regard, the general trend is that the performance gain observed for uniform distribution is slightly but consistently higher than that observed for non-uniform distribution. An intuitive explanation for that could lie in the count of inner loops. Since the prefetches inserted are conditional, to avoid bound violations, no prefetching is done in the last iteration of the inner loop. Consequently, during the next iteration of the outer loop, the data needed for the first iteration of the inner loop is not prefetched. Since a non-uniform distribution results in inner loops having fewer iterations, that would decrease the impact of prefetching as there will be more prefetch skips per total number of prefetches. That appears to be the reason behind the prefetch performance gain for non-uniform case for best performing combinations a notch lower than the uniform distribution.

For 1 MPI, 16 OMP run configurations without coprocessor offloading, the non-uniform case also exhibits negative gains for those prefetching choices which were low performing for uniform distribution, i.e. Cases when OUT is not prefetched. While a general lower value is explained in the previous paragraph, not prefetching OUT array would further wash away any gains because of more frequently skipping prefetches and a constant branch check overhead. This effect is more pronounced when 16 openMP threads because of the way an outer loop work is divided among openMP threads. Higher number of threads would mean lesser work per thread and that would make the overhead more pronounced resulting in performance hurt for the unpreferred prefetching choices.

In a nutshell, since the objective is to deal with best and consistent prefetching choices, it can be said that this prefetching methodology performs slightly better for uniform distribution as compared to non-uniform one.

## 5.5 Impact of MPI/OpenMP configuration

The number of MPI tasks and OpenMP threads per task is a vital choice. This complete affects what addresses a thread will get to work upon and consequently affects both, the baseline performance as well as the prefetching gains.

One clear trend is that MPI parallelism results in better performance as compared to equivalent openMP parallelism for uniform distribution. For non-uniform distribution, it's a totally different case. Clearly, for non-uniform distribution, distributed memory parallelism of using moe MPI threads proves to be a bad way as it results in 4-5 times as many cycles. This is something that deals with the surrounding code, as the kernel of concern for these experiments gets launched as a single task, and has only OpenMP parallelism within it. Hence, it's out of scope of this study to explain this peculiarity with regard to non-uniform distribution having such baseline performance when run with more than 1 MPI tasks.

What is in the scope of this study is to analyze the impact of these run choices on the performance gain caused by the inserted prefetches. And that comparison reveals that more or less the relative performance improvement brought by inserted prefetches remains the same irrespective of the parallelization choice. This is expected too as in each case, there are 16 threads sharing the total work and prefetching works the same way, so should lead to similar performance gains.

#### 5.6 Impact of Co-processor offloading

This is an interesting run configuration choice because of the reason that it deals with the indirect impact of the surrounding code on the kernel performance. No part of the VList kernel in question gets to offload on the coprocessor but parts of rest of the algorithm's steps do. Also, due to the way the overall code is structured, it is only possible to run it with 1 MPI task while coprocessor offloading in on, so for apples to apples comparison, it should be compared against the corresponding no processor offloading, 1 MPI task, 16 OMP thread run cases.

In terms of baseline performance, for uniform distribution, having coprocessor offloading improves the performance of kernel by about 2%. This can totally be attributed to indirect effects of having parts of surrounding code getting accelerated on MIC, resulting in possibly more cache and resources for the kernel. This difference is less pronounced with non-uniform distribution. This baseline shift causes a similar effect in terms of prefetch gains too, which are slightly more pronounced for uniform distribution without offloading than with offloading, and almost the same for non-uniform distribution.

In terms of the absolute number of cycles taken for the best prefetching combination for both uniform and non-uniform distribution, the numbers are almost the same for both co-processor offloading and no offloading. Therefore, it can be said that programmer inserted prefetches remain largely unaffected due to the indirect effects of coprocessor offloading on non-uniform distribution, and while they're affected nominally on uniform distribution, an improved baseline compensates for the change.

#### 5.7 Impact of Compiler prefetching

With regard to the compiler prefetching, the most important thing to check is the baseline cycles, i.e. the no prefetch cycles. Out of 8 pairs of runs, there is only one pair which exhibits a significant difference in that baseline. That happens with Uniform distribution run with 16 MPI tasks without coprocessor offloading where with compiler prefetching on, the baseline performs 5% better. There is no apparent reason for this behavior as to why compiler prefetching becomes helpful for this particular configuration. It could possibly be an indirect effect of prefetching improving the performance of the surrounding code. That is also apparent from the fact that this run configuration pair is also the only one where the programmer inserted prefetches make a different impact in compiler prefetching off versus on case. Looking at Figure 14(b) and 15(b), while all the prefetching combinations improve the performance over baseline in varying degree complying with the general trend across runs, when compiler prefetching is off, when it's on, for some combinations, the performance is hurt. The reduction in performance can be attributed to higher than usual baseline. This shifted baseline also results in the preferred prefetching combinations registering less performance gains as compared to the compiler prefetching off case. There is no certain explanation for the shifted baseline but since all numbers are trimmed averages over 10 runs, there is no reason to doubt the veracity of the data either. It's an outlier.

However, except this one case, in general, compiler prefetching does not seem to make any difference to either the baseline numbers, or to the performance gain caused by programmer inserted prefetches against the baseline.

In the next section, the results for all these 16 run configurations are tabulated and plotted.

#### 5.8 **Result tables and graphs**

| Uı       | Uniform Distribution, Compiler prefetching off, 1 MPI task,<br>16 OMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                          | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                               | 890187105        | 904994736    | 813382025         | 805577876            |  |  |  |  |

| To L2    | 010600228                                                                                                     | 872184914        | 894746093    | 827706953         | 838120182            |  |  |  |  |

| To L3    | 910690228                                                                                                     | 871359035        | 863538677    | 843003230         | 863370050            |  |  |  |  |

| To NTA   |                                                                                                               | 885392530        | 869261588    | 814912617         | 837429676            |  |  |  |  |

Table 6 - No. of cycles/thread for run configuration 1

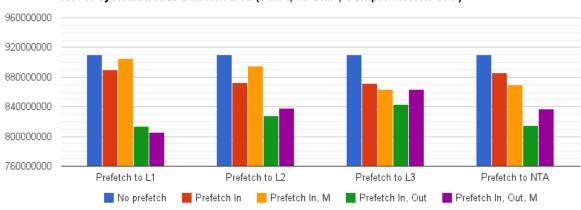

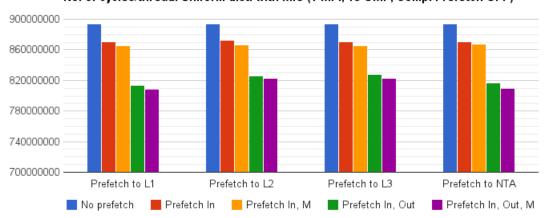

No. of cycles/thread: Uniform dist. (1 MPI, 16 OMP, Comp. Prefetch OFF)

Figure 6(a) - No. of cycles/thread for run configuration 1

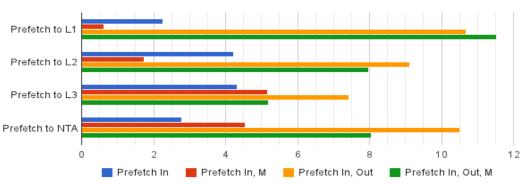

% gain: Uniform dist. (1 MPI, 16 OMP, Comp. Prefetch OFF)

Figure 6(b) - Percentage gain (reduction in no. of cycles) for run configuration 1

| 1 M      | Uniform Distribution, Compiler prefetching on<br>1 MPI task, 16 OpenMP threads/task, No coprocessor offloading |               |              |                   |                      |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------|---------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                           | IN array only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                | 886954686     | 865685085    | 828099237         | 806611975            |  |  |  |  |

| To L2    | 022121450                                                                                                      | 870189954     | 869126026    | 825903477         | 823958212            |  |  |  |  |

| To L3    | 923121459                                                                                                      | 899146662     | 864530659    | 829791047         | 836722495            |  |  |  |  |

| To NTA   |                                                                                                                | 870962281     | 877236662    | 832166812         | 808844077            |  |  |  |  |

Table 7 - No. of cycles/thread for run configuration 2

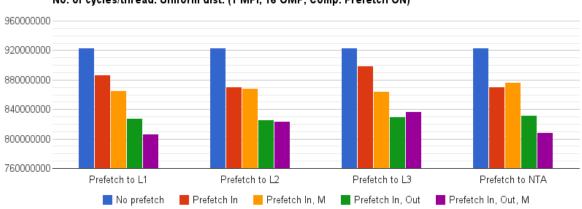

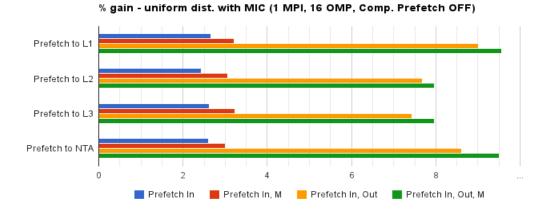

No. of cycles/thread: Uniform dist. (1 MPI, 16 OMP, Comp. Prefetch ON)

Figure 7(a) - No. of cycles/thread for run configuration 2

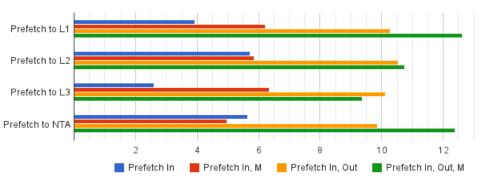

% gain: Uniform dist. (1 MPI, 16 OMP, Comp. Prefetch ON)

Figure 7(b) - Percentage gain (reduction in no. of cycles) for run configuration 2

| 1 N      | Non-uniform Distribution, Compiler prefetching off<br>1 MPI task, 16 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                                | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                     | 585410370        | 589778331    | 536397631         | 536415413            |  |  |  |  |

| To L2    | 595575549                                                                                                           | 567900933        | 591813417    | 548788574         | 541069085            |  |  |  |  |

| To L3    | 585525548                                                                                                           | 591012437        | 593237952    | 554709976         | 560555564            |  |  |  |  |

| To NTA   |                                                                                                                     | 581841270        | 589551645    | 529840825         | 533794800            |  |  |  |  |

Table 8 - No. of cycles/thread for run configuration 3

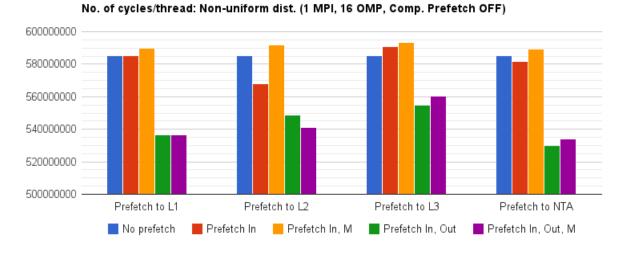

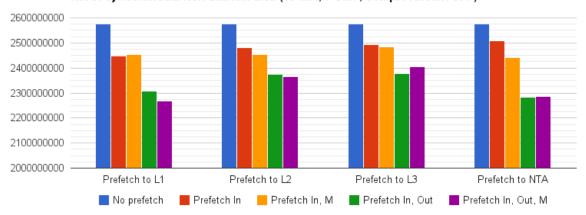

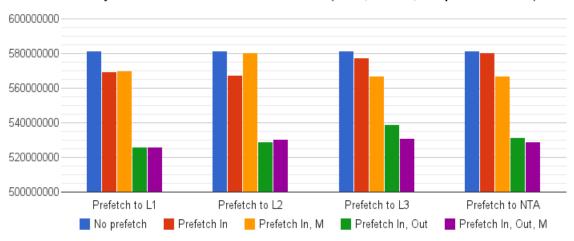

Figure 8(a) - No. of cycles/thread for run configuration 3

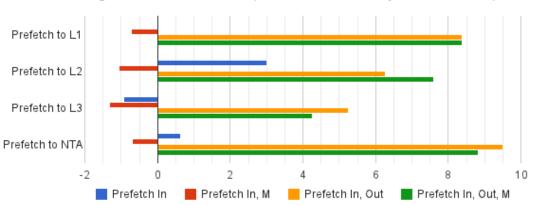

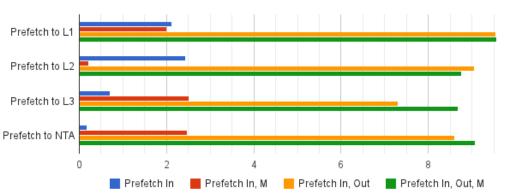

% gain: Non-uniform dist. (1 MPI, 16 OMP, Comp. Prefetch OFF)

Figure 8(b) - Percentage gain (reduction in no. of cycles) for run configuration 3

| 1 M      | Non-uniform Distribution, Compiler prefetching on<br>1 MPI task, 16 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                               | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                    | 581782884        | 581419167    | 537565610         | 524479564            |  |  |  |  |

| To L2    | 590159527                                                                                                          | 569617045        | 567717723    | 544640816         | 541850677            |  |  |  |  |

| To L3    | 580158527                                                                                                          | 580541427        | 590075549    | 544634967         | 527423338            |  |  |  |  |

| To NTA   |                                                                                                                    | 581159757        | 577361946    | 544242122         | 522934693            |  |  |  |  |

Table 9 - No. of cycles/thread for run configuration 4

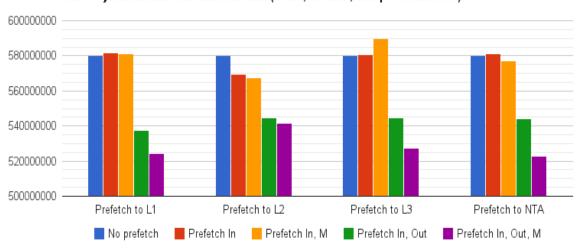

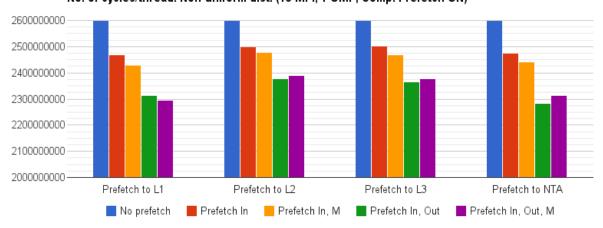

No. of cycles/thread: Non-uniform dist. (1 MPI, 16 OMP, Comp. Prefetch ON)

Figure 9(a) - No. of cycles/thread for run configuration 4

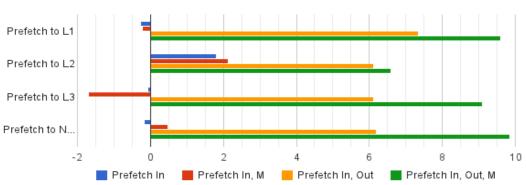

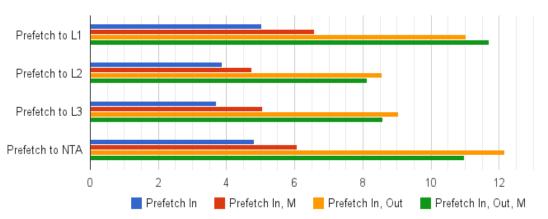

% gain: Non-uniform dist. (1 MPI, 16 OMP, Comp. Prefetch ON)

Figure 9(b) - Percentage gain (reduction in no. of cycles) for run configuration 4

| 4 N      | Uniform Distribution, Compiler prefetching off<br>4 MPI tasks, 4 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                            | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                 | 828071103        | 822131540    | 770931280         | 770829800            |  |  |  |  |

| To L2    | 9(1552042                                                                                                       | 834141983        | 821182869    | 794805420         | 791047907            |  |  |  |  |

| To L3    | 861552943                                                                                                       | 831186364        | 822954890    | 789903764         | 776795429            |  |  |  |  |

| To NTA   |                                                                                                                 | 824474602        | 822783422    | 779644684         | 762068794            |  |  |  |  |

Table 10 - No. of cycles/thread for run configuration 5

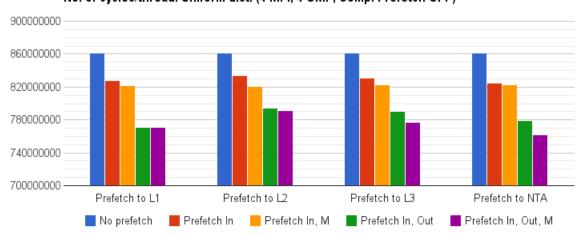

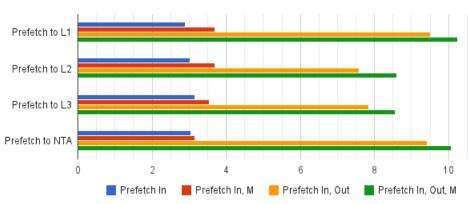

No. of cycles/thread: Uniform dist. (4 MPI, 4 OMP, Comp. Prefetch OFF)

Figure 10(a) - No. of cycles/thread for run configuration 5

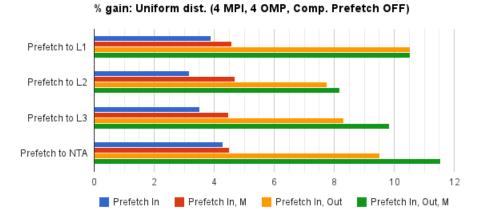

Figure 10(b) - Percentage gain (reduction in no. of cycles) for run configuration 5

| 4 N          | Uniform Distribution, Compiler prefetching on<br>4 MPI tasks, 4 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch     | None                                                                                                           | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1        |                                                                                                                | 825329581        | 807386664    | 763337044         | 765418328            |  |  |  |  |

| <b>To L2</b> | 856204162                                                                                                      | 823979100        | 816563058    | 788341661         | 785329449            |  |  |  |  |

| To L3        | 856304163                                                                                                      | 828714417        | 821044614    | 788136555         | 792211088            |  |  |  |  |

| To NTA       |                                                                                                                | 828540243        | 812495344    | 779148500         | 764570545            |  |  |  |  |

Table 11 - No. of cycles/thread for run configuration 6

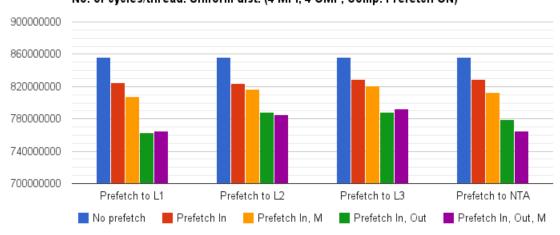

No. of cycles/thread: Uniform dist. (4 MPI, 4 OMP, Comp. Prefetch ON)

Figure 11(a) - No. of cycles/thread for run configuration 6

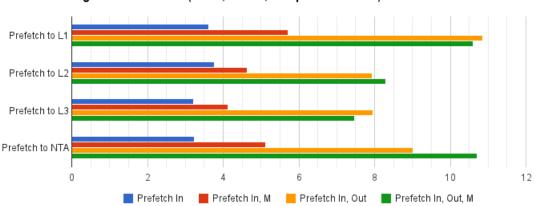

% gain: Uniform dist. (4 MPI, 4 OMP, Comp. Prefetch ON)

Figure 11(b) - Percentage gain (reduction in no. of cycles) for run configuration 6

| 4 N      | Non-uniform Distribution, Compiler prefetching off<br>4 MPI tasks, 4 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                                | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                     | 2607237244       | 2586955006   | 2476054782        | 2452162642           |  |  |  |  |

| To L2    | 2602200726                                                                                                          | 2604391502       | 2598818781   | 2522211248        | 2509300542           |  |  |  |  |

| To L3    | 2692200736                                                                                                          | 2619871098       | 2589067698   | 2519774272        | 2500372906           |  |  |  |  |

| To NTA   |                                                                                                                     | 2605647314       | 2600025509   | 2459153446        | 2450824145           |  |  |  |  |

Table 12 - No. of cycles/thread for run configuration 7

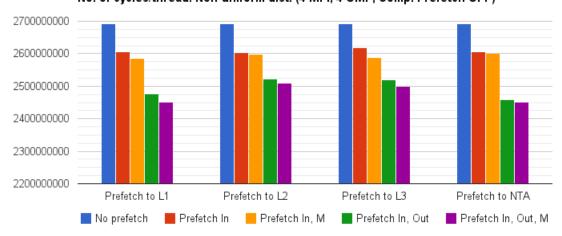

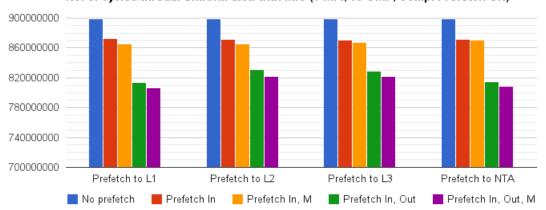

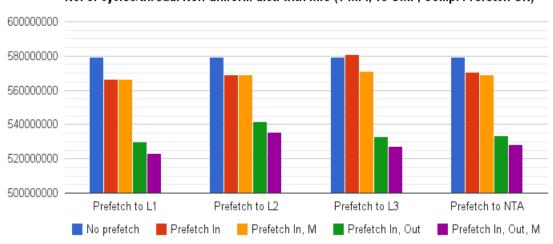

No. of cycles/thread: Non-uniform dist. (4 MPI, 4 OMP, Comp. Prefetch OFF)

Figure 12(a) - No. of cycles/thread for run configuration 7

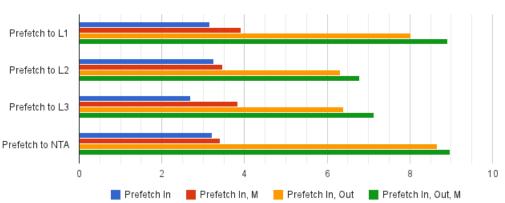

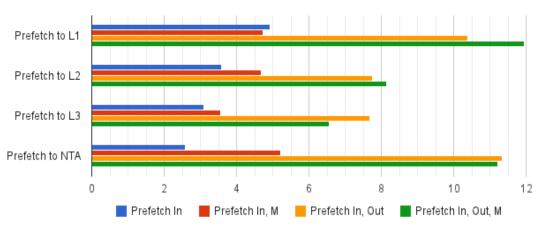

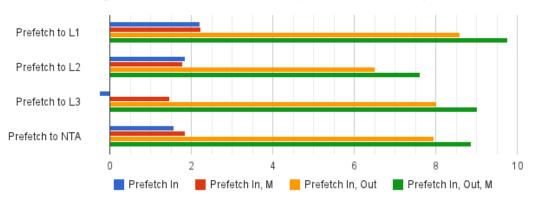

% gain: Non-uniform dist. (4 MPI, 4 OMP, Comp. Prefetch OFF)

Figure 12(b) - Percentage gain (reduction in no. of cycles) for run configuration 7

| 4 N      | Non-uniform Distribution, Compiler prefetching on<br>4 MPI tasks, 4 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                               | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                    | 2600029065       | 2585300081   | 2458011688        | 2443226047           |  |  |  |  |

| To L2    | 2686200580                                                                                                         | 2604692366       | 2588299467   | 2519532033        | 2503456685           |  |  |  |  |

| To L3    | 2686209580                                                                                                         | 2604080247       | 2613487092   | 2529253910        | 2517189108           |  |  |  |  |

| To NTA   |                                                                                                                    | 2612387307       | 2577576503   | 2457885961        | 2460558988           |  |  |  |  |

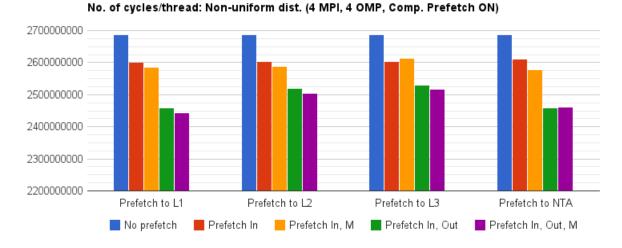

Table 13 - No. of cycles/thread for run configuration 8

Figure 13(a) - No. of cycles/thread for run configuration 8

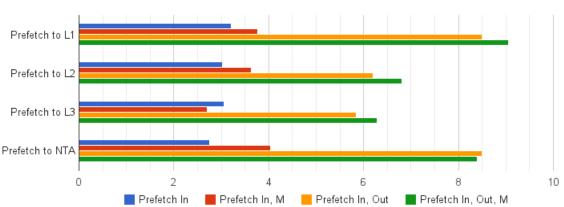

% gain: Non-uniform dist. (4 MPI, 4 OMP, Comp. Prefetch ON)

Figure 13(b) - Percentage gain (reduction in no. of cycles) for run configuration 8

| 16 N         | Uniform Distribution, Compiler prefetching off<br>16 MPI tasks, 1 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch     | None                                                                                                             | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1        |                                                                                                                  | 780420295        | 788755148    | 676736573         | 726061328            |  |  |  |  |

| <b>To L2</b> | 818500707                                                                                                        | 784199460        | 778057876    | 746167243         | 757623671            |  |  |  |  |

| <b>To L3</b> | 818590707                                                                                                        | 804639318        | 792194888    | 762975476         | 715500402            |  |  |  |  |

| To NTA       |                                                                                                                  | 785157955        | 796414733    | 735356392         | 727481281            |  |  |  |  |

Table 14 - No. of cycles/thread for run configuration 9

No. of cycles/thread:Uniform dist. (16 MPI, 1 OMP, Comp. Prefetch OFF)

Figure 14(a) - No. of cycles/thread for run configuration 9

% gain: Uniform dist. (16 MPI, 1 OMP, Comp. Prefetch OFF)

Figure 14(b) - Percentage gain (reduction in no. of cycles) for run configuration 9

| 16 N     | Uniform Distribution, Compiler prefetching on<br>16 MPI tasks, 1 OpenMP threads/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                            | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                 | 799506258        | 777568677    | 720362061         | 724550227            |  |  |  |  |

| To L2    | 778070040                                                                                                       | 803117329        | 782626923    | 726324415         | 705618299            |  |  |  |  |

| To L3    | 778079949                                                                                                       | 783115452        | 742796331    | 746999163         | 753926871            |  |  |  |  |

| To NTA   |                                                                                                                 | 750622889        | 793244770    | 729227175         | 720189404            |  |  |  |  |

Table 15 - No. of cycles/thread for run configuration 10

No. of cycles/thread:Uniform dist. (16 MPI, 1 OMP, Comp. Prefetch ON)

Figure 15(a) - No. of cycles/thread for run configuration 10

% gain: Uniform dist. (16 MPI, 1 OMP, Comp. Prefetch ON)

Figure 15(b) - Percentage gain (reduction in no. of cycles) for run configuration 10

| 16 1     | Non-uniform Distribution, Compiler prefetching off<br>16 MPI tasks, 1 OpenMP thread/task, No coprocessor offloading |                  |              |                   |                      |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|----------------------|--|--|--|--|

| Prefetch | None                                                                                                                | IN array<br>only | IN, M arrays | IN, OUT<br>arrays | IN, OUT, M<br>arrays |  |  |  |  |

| To L1    |                                                                                                                     | 2447734995       | 2453215485   | 2306941143        | 2267227094           |  |  |  |  |

| To L2    | 2574704529                                                                                                          | 2482538144       | 2454004520   | 2375136413        | 2365039945           |  |  |  |  |