# Singapore Management University Institutional Knowledge at Singapore Management University

Dissertations and Theses Collection (Open Access)

Dissertations and Theses

8-2018

# Secure enforcement of isolation policy on multicore platforms with virtualization techniques

Siqi ZHAO

Singapore Management University, siqi.zhao.2013@phdis.smu.edu.sg

Follow this and additional works at: https://ink.library.smu.edu.sg/etd coll

Part of the Databases and Information Systems Commons

#### Citation

ZHAO, Siqi. Secure enforcement of isolation policy on multicore platforms with virtualization techniques. (2018). Dissertations and Theses Collection (Open Access).

Available at: https://ink.library.smu.edu.sg/etd\_coll/184

This PhD Dissertation is brought to you for free and open access by the Dissertations and Theses at Institutional Knowledge at Singapore Management University. It has been accepted for inclusion in Dissertations and Theses Collection (Open Access) by an authorized administrator of Institutional Knowledge at Singapore Management University. For more information, please email libIR@smu.edu.sg.

# Secure Enforcement of Isolation Policy on Multicore Platforms with Virtualization Techniques

SIQI ZHAO

SINGAPORE MANAGEMENT UNIVERSITY 2018

# Secure Enforcement of Isolation Policy on Multicore Platforms with Virtualization Techniques

### by **Siqi Zhao**

Submitted to School of Information Systems in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Information Systems

#### **Dissertation Committee:**

Xuhua DING (Supervisor / Chair) Associate Professor of Information Systems Singapore Management University

Debin GAO (Co-supervisor) Associate Professor of Information Systems Singapore Management University

Robert DENG Huijie Professor of Information Systems Singapore Management University

Jianying ZHOU

Professor of Cyber Security

Singapore University of Technology and Design

Singapore Management University 2018

Copyright (2018) Siqi Zhao

# Secure Enforcement of Isolation Policy on Multicore Platforms with Virtualization Techniques

#### Siqi Zhao

#### **Abstract**

A number of virtualization based systems have been proposed in the literature as an effective measure against the adversaries with the kernel privilege. However, under a systematic analysis, such systems exhibit vulnerabilities that can still be exploited by such an attacker with the kernel privilege. The fundamental reason is that there is an inherent incompatibility between the tamper-proof requirement and the complete mediation requirement of the reference monitor model. The incompatibility manifests in the virtualization based systems in the form of a discrepancy between the enforcement capability demanded by the high-level policy and the one achievable through the system design approach mandated by the low-level hardware enforcement mechanism.

The scenario is further complicated by an implicit assumption in existing works, which is that the underlying platform is single-threaded. This assumption is becoming increasingly distant from the real-world computing landscape where multi-core machines have become ubiquitous. With the broken assumption, the adversarial threads running on other cores gain capabilities that are not possible on uni-core platforms and are possible to launch new attacks.

In this work, the existing systems are firstly examined in a systematic manner. The consequences and implications of the aforementioned discrepancy are shown by dissecting and examining existing systems' high-level security goals and design details of leveraging the hardware enforcement mechanism. Meanwhile, the issues caused by concurrent execution on multicore platforms are presented. Two concrete attacks are shown as the examples of the complications of the multicore scenario.

In light of the issues, Fully Isolated Micro-Computing Environment (FIMCE)

is proposed. FIMCE addresses the issues revealed in the analysis by managing involvement of semantics from the kernel. It encloses a complete set of resources needed by a program. FIMCE also features great flexibility and can be tailored to various applications. Built on top of this environment, Immersive Execution Environment (ImEE) is presented. ImEE is designed for efficient introspection through consistent address space mappings. In the ImEE's design, an isolated environment is equipped with tweaked address mappings. It directly reuses the page tables of a target VM and synchronizes the root of the page tables with the target VM. As a result, the target VM cannot present fake address mappings to the introspection tool to mislead the results.

# **Table of Contents**

| 1 | Intr | oduction                                          | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Overview                                          | 1  |

|   |      | 1.1.1 Adversaries with Kernel Privilege           | 2  |

|   |      | 1.1.2 Virtualization-based Systems                | 4  |

|   |      | 1.1.3 Issues and Research Objectives              | 5  |

|   | 1.2  | Threat Model                                      | 8  |

|   | 1.3  | Security Policy Enforcement                       | 8  |

|   | 1.4  | Enforcing Isolation Policy on Multicore Platforms | 10 |

|   | 1.5  | Consistent Virtual Machine Introspection          | 11 |

|   | 1.6  | Background                                        | 12 |

|   |      | 1.6.1 Address Translation in Virtualization       | 12 |

|   |      | 1.6.2 Memory Access in SMP Systems                | 14 |

|   | 1.7  | Organization                                      | 15 |

| 2 | Rela | ated Work                                         | 16 |

|   | 2.1  | Trusted Execution Environment                     | 16 |

|   | 2.2  | Kernel Integrity                                  | 18 |

|   | 2.3  | Mapping Redirection                               | 19 |

|   | 2.4  | Event Trap                                        | 19 |

|   | 2.5  | Auxiliary Uses                                    | 20 |

|   | 2.6  | Virtual Machine Introspection                     | 20 |

|   |      | 2.6.1 In-VM Introspection                         | 21 |

|   |      |                                                   |    |

|   |      | 2.6.2                              | Out-of-VM Introspection                                      | 21    |

|---|------|------------------------------------|--------------------------------------------------------------|-------|

|   | 2.7  | Isolatio                           | on With Other Techniques                                     | 22    |

| 3 | An A | Analysis                           | of Effectiveness of the Existing Virtualization-based Scheme | es 24 |

|   | 3.1  | A Model of the Enforcement Systems |                                                              |       |

|   |      | 3.1.1                              | Conflict Between Tamper-Proof and Complete Mediation         | 27    |

|   |      | 3.1.2                              | The Inference Gap                                            | 28    |

|   |      | 3.1.3                              | The Approximation Function                                   | 30    |

|   |      | 3.1.4                              | Example Use of Semantics Beyond the Trust Boundary           | 32    |

|   | 3.2  | Policy                             | Formulation                                                  | 33    |

|   |      | 3.2.1                              | Process Subjects                                             | 34    |

|   |      | 3.2.2                              | Memory Ranges                                                | 35    |

|   |      | 3.2.3                              | Issues in $SP^3$                                             | 36    |

|   |      | 3.2.4                              | Privilege Level Based Subjects                               | 38    |

|   | 3.3  | Utiliza                            | tion by Low-Level Mechanism                                  | 39    |

|   |      | 3.3.1                              | A General Approach                                           | 39    |

|   |      | 3.3.2                              | Division into Binary Policy Sets                             | 41    |

|   |      | 3.3.3                              | Detecting Subject Switches                                   | 43    |

|   |      | 3.3.4                              | Event Synthesis                                              | 45    |

|   | 3.4  | The Im                             | npact of Concurrency                                         | 47    |

|   |      | 3.4.1                              | Race Conditions                                              | 47    |

|   |      | 3.4.2                              | Permission Revocation                                        | 48    |

|   |      | 3.4.3                              | TLB-Related Attacks                                          | 49    |

|   |      | 3.4.4                              | Implications                                                 | 53    |

|   | 3.5  | Discus                             | sions                                                        | 54    |

|   |      | 3.5.1                              | Memory Monitors                                              | 54    |

|   |      | 3.5.2                              | Runtime Updates and Policy Coherence                         | 56    |

|   |      | 3.5.3                              | Functionality                                                | 56    |

|   |      | 3.5.4                              | Forced Serialization of Concurrent Accesses                  | 57    |

|   | 3.6  | 3.6 Possible Solutions |                                                          |    |  |

|---|------|------------------------|----------------------------------------------------------|----|--|

|   |      | 3.6.1                  | Expanding the Trust Boundary                             | 58 |  |

|   |      | 3.6.2                  | Self-Supplied Semantics                                  | 58 |  |

|   |      | 3.6.3                  | Hardware Assistance                                      | 59 |  |

|   |      | 3.6.4                  | Restricting Untrusted Software                           | 60 |  |

| 4 | Enfo | orcing I               | solation with Fully Isolated Micro-Computing Environment |    |  |

|   | (FIN | ACE)                   |                                                          | 61 |  |

|   | 4.1  | FIMC                   | E Architecture                                           | 62 |  |

|   | 4.2  | The Li                 | ifecycle of FIMCE                                        | 64 |  |

|   |      | 4.2.1                  | FIMCE Bootup                                             | 65 |  |

|   |      | 4.2.2                  | Runtime                                                  | 67 |  |

|   |      | 4.2.3                  | Termination                                              | 67 |  |

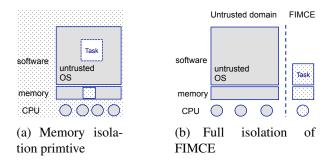

|   |      | 4.2.4                  | Comparisons to Memory Isolation Primitive                | 67 |  |

|   | 4.3  | FIMC                   | E and SGX                                                | 68 |  |

|   |      | 4.3.1                  | Comparisons                                              | 69 |  |

|   |      | 4.3.2                  | Integration with SGX                                     | 71 |  |

|   | 4.4  | Modul                  | larized Software Infrastructure                          | 73 |  |

|   |      | 4.4.1                  | Pillars                                                  | 74 |  |

|   |      | 4.4.2                  | Pillar Verification and Linking                          | 75 |  |

|   | 4.5  | Applic                 | cations of FIMCE                                         | 77 |  |

|   |      | 4.5.1                  | Malleability                                             | 77 |  |

|   |      | 4.5.2                  | Runtime Trust Anchor                                     | 79 |  |

|   | 4.6  | Evalua                 | ations                                                   | 80 |  |

|   |      | 4.6.1                  | Security Analysis                                        | 80 |  |

|   |      | 4.6.2                  | Implementation                                           | 83 |  |

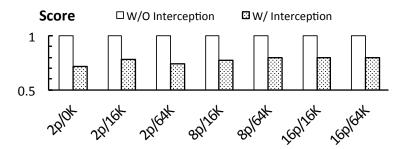

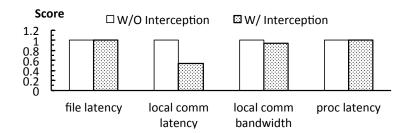

|   |      | 4.6.3                  | Benchmarks                                               | 85 |  |

|   |      | 4.6.4                  | Component Costs                                          | 86 |  |

|   |      | 4.6.5                  | Application Evaluation                                   | 87 |  |

| Con | sistent | Virtual Machine Introspection              |

|-----|---------|--------------------------------------------|

| 5.1 | The In  | ference Gap in Software-based Guest Access |

| 5.2 | Overvi  | iew                                        |

|     | 5.2.1   | Basic Idea                                 |

|     | 5.2.2   | Challenges                                 |

|     | 5.2.3   | System Overview                            |

| 5.3 | The D   | esign Details                              |

|     | 5.3.1   | ImEE Internals                             |

|     | 5.3.2   | ImEE Agent                                 |

|     | 5.3.3   | Defeating Attacks via the Blind Spot       |

|     | 5.3.4   | Operations of ImEE                         |

| 5.4 | Impler  | mentation                                  |

|     | 5.4.1   | ImEE on KVM                                |

|     | 5.4.2   | Specialized Agent                          |

|     | 5.4.3   | Usability                                  |

| 5.5 | Evalua  | ution                                      |

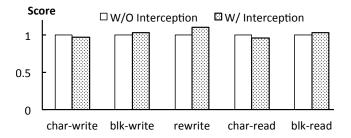

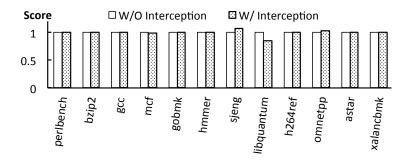

|     | 5.5.1   | ImEE Overhead                              |

|     | 5.5.2   | Guest Access Speed                         |

|     | 5.5.3   | Introspection Performance Comparison       |

|     | 5.5.4   | Handling Multiple VMs                      |

| 5.6 | Discus  | sions                                      |

|     | 5.6.1   | CPU State                                  |

|     | 5.6.2   | Integration with Existing VMI Tools        |

|     | 5.6.3   | ImEE vs. In-VM Introspection               |

|     | 5.6.4   | Paging Modes Compatibility                 |

|     | 5.6.5   | Architecture Compatibility                 |

# **List of Figures**

| 1.1 | The paradigm of memory access in an SMP setting. The first core                       |    |  |  |

|-----|---------------------------------------------------------------------------------------|----|--|--|

|     | has TLB misses and accesses the memory via the guest page tables                      |    |  |  |

|     | and the EPTs, while the last core has TLB hits and accesses the                       |    |  |  |

|     | memory without consulting any page table                                              | 14 |  |  |

| 3.1 | The Enforcement System Model                                                          | 26 |  |  |

| 3.2 | An Example of the Enforcement System                                                  | 32 |  |  |

| 3.3 | The Effective Policy of Memory Ranges                                                 | 35 |  |  |

| 3.4 | The Access Control Design of SP <sup>3</sup>                                          | 37 |  |  |

| 3.5 | The Effective Policy of Privilege Levels                                              | 38 |  |  |

| 3.6 | The EPT Arrangement in SeCage                                                         | 43 |  |  |

| 3.7 | Illustration of the stifling attack bypassing the EPT's access control                |    |  |  |

|     | over the victim's data. The attacker controls core <sub>1</sub> and core <sub>2</sub> | 51 |  |  |

| 3.8 | The enforcement system in the monitor scenario                                        | 55 |  |  |

| 4.1 | Memory isolation for FIMCE without EPT                                                | 64 |  |  |

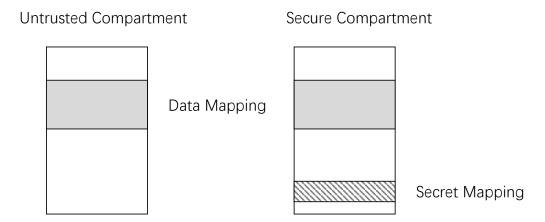

| 4.2 | The comparison between the memory isolation primitive and FIMCE.                      |    |  |  |

|     | The gray regions denote resources controlled by the adversary and                     |    |  |  |

|     | the dotted regions denote isolated resources                                          | 68 |  |  |

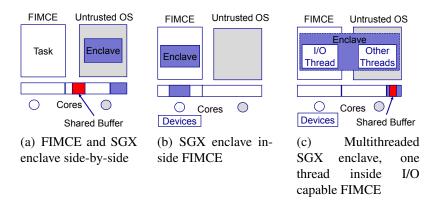

| 4.3 | FIMCE based isolated I/O for SGX enclaves                                             | 71 |  |  |

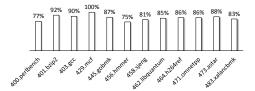

| 4.4 | SPECint_rate 2006 results. The numbers are the percentage of the                      |    |  |  |

|     | score with FIMCE to the score without FIMCE                                           | 86 |  |  |

| 4.5  | Lmbench results. The numbers are the percentage of the score with          |

|------|----------------------------------------------------------------------------|

|      | FIMCE to the score without FIMCE                                           |

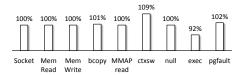

| 5.1  | Illustration of the idea of direct usage of the target VM's VA-to-         |

|      | GPA mappings and splitting in GPA-to-HPA mappings. Note that               |

|      | the shadow box is fully controlled by the target (i.e., the adversary). 96 |

| 5.2  | Illustration of the blind spot comprising three virtual pages (in the      |

|      | dark color). Target kernel objects in those pages cannot be intro-         |

|      | spected since they are mapped to the local memory                          |

| 5.3  | Overview of ImEE-based introspection. The box with dashed lines            |

|      | illustrates the mixture of physical memory. The shadowed regions           |

|      | belong to the target and are not trusted                                   |

| 5.4  | The solid arrows describe the translation for a VA within the ImEE,        |

|      | while the dotted arrows describe the translation inside the target.        |

|      | All target frames accessible to the ImEE agent are set as read-only        |

|      | and non-executable in EPT <sub>T</sub>                                     |

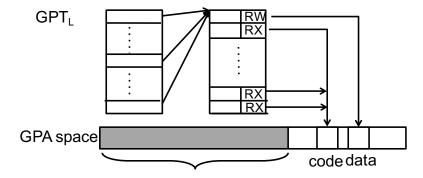

| 5.5  | The Illustration of $GPT_L$ . All entries in the page table directory      |

|      | point to the same page table page which has one PTE points to the          |

|      | data frame and all other to the code frame                                 |

| 5.6  | The sketch of the ImEE agent's pseudo code                                 |

| 5.7  | LMBench: normalized result on context switch time. The higher              |

|      | score means better performance                                             |

| 5.8  | LMBench: normalized result on other system aspects. The higher             |

|      | score means better performance                                             |

| 5.9  | Bonnie++: normalized results on disk performance. The higher               |

|      | score means better performance                                             |

| 5.10 | SPEC INT: normalized results on CPU performance. The higher                |

|      | score means better performance                                             |

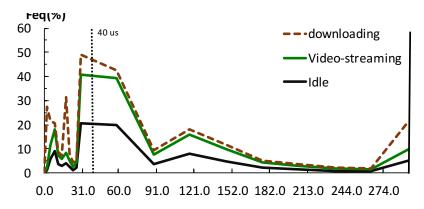

| 5.11 | The frequency distribution of interval lengths between context switches |

|------|-------------------------------------------------------------------------|

|      | in three workloads: idle, video streaming and file downloading. The     |

|      | x-axis is not displayed to the scale                                    |

# **List of Tables**

| 4.1 | User Space Library Interfaces and Macros                            | 84  |

|-----|---------------------------------------------------------------------|-----|

| 4.2 | Kernel Build Time (in seconds)                                      | 86  |

| 4.3 | Netperf Bandwidth With And Without FIMCE Running (in Mbps) .        | 86  |

| 4.4 | Single-threaded Postmark Performance with and without FIMCE         |     |

|     | Running (in seconds)                                                | 87  |

| 4.5 | Loading Time for Pillars with Various Sizes                         | 87  |

| 4.6 | Modified Apache Performance, # of SSL Handshakes per Second         | 89  |

| 4.7 | Overhead Of Other Protection Schemes (numbers are excerpted from    |     |

|     | respective paper)                                                   | 89  |

| 4.8 | TPM Performance (in seconds)                                        | 90  |

| 5.1 | Address notations. For instance, GP_c is the guest physical address |     |

|     | of the ImEE code page in the local address space                    | 103 |

| 5.2 | Three ImEE agents. The Type-3 agent uses 2 pointer deferences       |     |

|     | while the Type-2 agent uses one                                     | 109 |

| 5.3 | Overhead comparison between ImEE and LibVMI                         | 112 |

| 5.4 | Memory read performance comparison                                  | 115 |

| 5.5 | Kernel object introspection performance in kernel and ImEE (time    |     |

|     | in $\mu$ s)                                                         | 115 |

| 5.6 | Kernel object introspection performance by LibVMI (time in $\mu$ s) | 116 |

# Acknowledgments

I would like to thank my advisor and committee chair Xuhua Ding for his guidance over the course of the program, for the intellectual challenges posed during the discussion sessions and for the rigorous scrutinization over the entire course of the work. These glimpses of the power of reasoning, and what it might achieve, are the greatest lessons I have learned so far. I am also grateful to the other dissertation committee members, Debin Gao, Robert Deng and Jianying Zhou, for their effort and time on evaluation and guidance during the dissertation defense process.

# **List of Publications**

### **Conference Papers**

- **S. Zhao** and X. Ding. On the Effectiveness of Virtualization Based Memory Isolation on Multicore Platforms. In *Security and Privacy (EuroS&P)*, 2017 IEEE European Symposium on, 546-560.

- S. Zhao, X. Ding, W. Xu and D. Gu. Seeing Through The Same Lens: Introspecting Guest Address Space At Native Speed. In 26th USENIX Security Symposium (USENIX Security 17), 799-813

### **Journal Paper**

S. Zhao and X Ding. FIMCE: A Fully Isolated Micro-Computing Environment for Multicore Systems. ACM Transactions on Privacy and Security (TOPS) 21 (3), Article 15 (May 2018)

# Chapter 1

# Introduction

#### 1.1 Overview

The Operating System typically acts as the reference monitor [15] that enforces the system-wide security policy on a computer system. For such a purpose, it is granted with the highest privilege. However, complexity in modern OS weakens its own integrity guarantees and leads to frequent security breaches. Once breached, the attackers obtain the same privilege as the kernel, therefore, it is possible for them to launch arbitrary software attacks and compromise the entire system. Such attackers pose serious threats.

The virtualization based approach was proposed to defend against this kind of attackers because it leverages a higher level of privilege than the kernel. A number of such systems have been proposed in the literature. However, these systems exhibit certain issues, drawbacks and even vulnerabilities upon close inspection. In this section, the severity of the adversaries with the kernel privilege is firstly described as the motivation for the rest of the work. A brief summary of the virtualization systems is given next, so as to lay down the context for the research questions pursued in this work.

#### 1.1.1 Adversaries with Kernel Privilege

The Operating System is the entity that manages the resources in a traditional computer system. Conveniently, it also serves as the reference monitor that monitors the accesses to the resources by individual subjects, and enforces any security policies. The reference monitor concept mandates three requirements to be satisfied, namely, tamper-proof, complete mediation and verifiability. In the traditional computer systems, the OS had long been regarded as trusted in the sense that it maintains its own integrity, i.e. it satisfies the requirement of tamper-proof.

However, just as any software, the OS also contains vulnerabilities that can be exploited. Such exploitation is serious since it can lead to violation of any security policies. Once inside the OS, the attackers gain the privilege of the kernel and can manipulate the system-wide policy enforcement. Therefore, arbitrary attacks can be launched. An example class of attack is the so-called *rootkits*. The rootkits are malicious code produced by the attackers and injected into the kernel space, such as the adore-ng rootkit [1] which modifies the kernel function pointers. In this case, because the system-wide policy enforcement has been manipulated by the attackers, even detection of these attacks is challenging.

The problem of the adversaries with the kernel privilege is relevant because of two factors. The first factor is that the interface to modern OSes is becoming increasingly complex. Such a complex interface exposes an enormous attack surface. The enormity is exhibited from two aspects. First, the system call interface is known to be large and complex. For example, Linux contains over three hundred system calls and there are more on Windows. Many system calls also contain complex semantics such as ioctl whose behavior completely depends on the device that it is interacting with. Second, besides the system calls, the applications can also interact with the kernel via implicit interfaces such as the file systems, e.g. /proc and /sys. These interfaces also do not have clearly defined semantics. Therefore, it is hard to reason about the behaviors of the applications and enforce effective poli-

cies. In existing works, the complex interface frequently introduces challenges to security designs that interpose on the system call interface such as Janus [45].

The second factor is that a modern OS consists of an enormous amount of code. For example, the Linux kernel reached one million lines of code at version 2.1.63 [5]. Since then, the size of the kernel has undergone a steady increase. Version 4.15.9 has accumulated 20 million lines of code. The large amount of code results in complex semantics that is reachable from the large attack surface. Therefore, the likelihood of vulnerability is high and the modern OSes are routinely broken by attackers.

In practice, the threat from a kernel level adversary is present in many scenarios. One such scenario is when the kernel is owned by a party not necessarily trusted, e.g. the manufacturers. In this case, there is no guarantee that the kernel will enforce any security policy, including the basic isolation policy. In other scenarios, the kernel may be compromised in various ways besides code injection. For example, dataonly attacks can leave the kernel data in an invalid state, leading to security policy violations. As shown by the attacks that modify the identity in the cred structures, it is possible to obtain root privilege.

Without modifications on the system architecture, certain integrity measurement schemes alleviate this problem by measuring integrity at certain points during the execution. For example, TPM-based integrity measurement [90] can be leveraged to construct a chain of authenticated component loaded. However, this approach has a great limitation because it only guarantees integrity during the load time. The malicious behavior could be injected to the kernel after the measurement had finished. An example is the Trusted Boot [11] which is a boot loader that utilizes the TPM to perform measurement of the loaded OS image. However, integrity of the kernel at runtime is not protected. Furthermore, integrity measurement is usually made over code and static data, however, attacks can also be launched via modification on the dynamic data. An example is the aforementioned adore-ng rootkit which modifies dynamic function pointers in the file system layer. Integrity measurement does

not cover the dynamic data, therefore, it cannot prevent this kind of attacks. Other integrity measurement schemes, such as PRIMA [54] and Linux Integrity Measurement Architecture [79], measure applications. Since they assume a trusted kernel, they cannot be applied, neither.

#### 1.1.2 Virtualization-based Systems

The virtualization based approach is an effective means to defend against the adversaries with kernel privilege. This approach is architectural in that it de-privileges the kernel so that it is no longer the entity with the highest privilege. In such systems, the OS is de-privileged to run in a *domain* or virtual machine (VM), which is managed and regulated by a higher-level entity usually called the virtual machine monitor (VMM) or the hypervisor. By the nature of the attacker with the kernel privilege, only the OS is vulnerable; the hypervisor is not affected. Therefore, policy enforcement by the hypervisor is not affected by such powerful attackers.

From a system perspective, the virtualization based systems are reference monitors implemented by hardware virtualization mechanism. Hardware virtualization mechanism allows the reference monitor to interpose on the hardware-software interface through which traditionally the kernel directly interacts with the hardware. The interposition allows the hypervisor to distinguish individual accesses to hardware resources, thereby provides an opportunity to enforce security policies.

In its basic form, such systems enforce a type of policy called domain isolation. In domain isolation, the hypervisor distinguishes accesses to hardware resources by domains. The untrusted OS runs in one of the domains while the trusted OS and applications run in others. Domain isolation guarantees integrity and confidentiality of the trusted domain, which enables the establishment of further security properties of the system. Examples include Terra [46], Lares [73] and HookSafe [96]. The main drawback of this design, however, is that the TCB includes the trusted OS, which is still large.

Further systems push the enforcement granularity level towards the fine-grained direction. They distinguish the accesses by more fine-grained entities such as processes or even code segments. This approach eliminates the guest OS from the TCB, because the logic in the kernel that manages the entities other than the ones concerned is not needed. However, since hardware virtualization mechanism is not aware of the concerned entities which are usually defined by the kernel, policy enforcement by the virtualization based systems needs to rely on the facilities of the untrusted OS that define such concerned entities, such as dynamic memory allocation, file systems and the kernel's page table. The consequence of the reliance is that certain semantics from the untrusted kernel is involved in the policy enforcement process, which creates issues. The issues of the involvement are elaborated in Section 1.3. In the rest of the work, this approach is called the memory isolation because the fine-grained entities are usually memory segments.

A number of existing works have utilized the hardware virtualization mechanism for various security purposes. For the rootkit problem, for example, SecVisor [80] ensures that only whitelisted code can execute with kernel privilege. Lares [73] protects the integrity of hooks placed in the kernel. HookSafe [96] proposes a lightweight approach to protect kernel function pointers by aggregating them.

The virtualization mechanism is also versatile so that it can be used for many other security objectives when facing a malicious kernel, such as isolated execution [46, 68, 51, 26, 29, 93, 86], memory compartmentalization [67], integrity measurement [17], stealthy debugging [41, 37], enforcing execute-only permission [32, 97] and virtual machine introspection [49, 24, 39, 42, 56]. Chapter 2 provides a list of description of these systems.

#### 1.1.3 Issues and Research Objectives

**Effectiveness of Policy Enforcement** The virtualization based systems are reference monitors implemented by hardware virtualization mechanism. Since hardware

virtualization mechanism mandates a special form of policy, the systems all need to translate the elements of the high-level security policy into the special form, which is expressed with the abstractions both within the virtualization context and observable at the hardware-software interface, e.g. memory pages and domains. For example, TrustVisor enforces that only a sensitive module can access its own code and data. It needs to translate "the sensitive module" into "a registered set of pages".

The main issue is that the translation process involves semantics from the untrusted kernel, because the high-level entities are defined and managed by the untrusted kernel. However, most systems do not explicitly describe this translation process. The extend to which such semantics is involved is not clear, neither the consequences.

Because of involvement of the semantics from the kernel, effectiveness of policy enforcement can be affected by the subtlety in the translation process. The subject and object identity are vulnerable to manipulation and can be inconsistent. For example, when processes are identified by CR3 values, the processes can be impersonated since the values are managed by the untrusted kernel. Also, the mediation of the operations by the hypervisor can be incomplete. Therefore, it remains an important research question: *how effective can a system based on virtualization techniques enforce the high-level policies?*

Enforcing Isolation In order to enforce the high-level policies, the fundamental guarantee the hypervisor needs to provide is isolation. Isolation concerns about the identity of the entities in the high-level policies. It refers to the requirement that there is no overlap between the low-level representations for any two high-level policy entities. For example, no "sensitive modules" share a memory page. Here, the issues of existing systems are two fold. First, as mentioned above, isolation is enforced with semantics from the untrusted kernel. Second, when the first issue is compounded with concurrent execution, the enforcement become ineffective.

In virtualization based systems, the specific translation that the hypervisor needs to perform is from the high-level entities to the low-level domains defined by the extra paging structures. Since the kernel firstly defines the high-level entities, the kernel semantics which is the identities information recorded in the kernel page tables is needed to craft the low-level domains. During policy enforcement, because the observed accesses through the hardware-software interface are influenced by the address translation configurations, the kernel can still influence the policy enforcement by manipulating the kernel semantics. Many systems noticed this issue and performed checks on the kernel's page table on various occasions. However, such checks are ad-hoc and not systematic.

Furthermore, the fact that modern hardware platforms are multi-core complicates the situation. Parallel execution on multi-core platforms allows the untrusted domain and the trusted domain to run at the same time, which cannot occur on single-threaded platforms assumed by previous works. The untrusted domain thus can take advantage of any resources available to attack the trusted domain.

Therefore, whether existing approaches still guarantee isolation on a multi-core platform requires a closer investigation. Due to the importance of isolation, we pose the second research question. *How to ensure secure isolation by virtualization techniques on modern multi-core hardware systems?*

Consistent Introspection An isolated trusted domain can serve as a suitable standpoint for extending the trust beyond. One possibility is that it can be used to scan the memory content inside other domains; a technique called Virtual Machine Introspection (VMI). VMI is a prerequisite of many analyses that aim to detect malicious activities, because it provides the raw data for the detection tools to analyze.

The VMI systems face a special form of the policy translation issue mentioned above. Although they do not necessarily enforce any policy over the other domains, they do need to translate the high-level objects typically in memory to raw bytes observed by the hypervisor. More precisely, the VMI systems need to translate the virtual addresses of the objects into the physical addresses so that it can read the content out. Inevitably, the kernel's page tables in the untrusted domain are involved.

The previous VMI tools rely on software logic to walk the kernel's page tables during the translation process. However, the kernel can modify its own page tables in arbitrary ways, which affects the memory layout of the untrusted domain. As a consequence, the VMI tools do not have a consistent view of the virtual address space. Any further analysis, therefore, leads to invalid results. This method is also slow because the page table walks require a series of loads from the memory. Therefore, the agility of introspection cannot match with the untrusted domain's operations on the address mappings. In the face of these issues, the last question is thus: how to ensure consistency in memory introspection?

#### 1.2 Threat Model

The adversary in consideration is one with the kernel privilege. For example, the adversary may be the kernel infected by the rootkits. However, the means by which the adversary obtains this privilege is irrelevant. With the kernel privilege, the adversary can launch arbitrary software-based attacks, such as arbitrary memory accesses and execution context manipulations. He is also capable of manipulating external devices that he can access for his purposes. Meanwhile, it is assumed that the BIOS, the firmware and the hardware components in the platform are not compromised by the adversary and behave in compliance with the respective specifications. The hypervisor's code, data and control flow are trusted throughout the lifetime of the platform. Side channel attacks are not considered, nor are denial-of-service attacks.

#### 1.3 Security Policy Enforcement

As stated in Section 1.1.2, the virtualization based systems interpose on the hardware-software interface in order to enforce a set of high-level security policies. Following the reference monitor concept [15], they need to satisfy three basic requirements, namely, tamper-proof, complete mediation and verifiability. Among

these, the tamper-proof requirement is satisfied due to the higher privilege. Meanwhile, the requirement of verifiability typically requires formal verification of the logic which is a separate field of study, therefore, it is out of the scope of this work.

The focus here is the interaction between the tamper-proof requirement and the complete mediation requirement. Ideally, both requirements should be met to guarantee effectiveness of policy enforcement. The tamper-proof requirement is met by adopting the virtualization mechanism; the higher privilege ensures integrity of the hypervisor. However, this design approach introduces inevitable involvement of semantics from the untrusted kernel. The involvement, if not treated with care, can cause failure in meeting the complete mediation requirement.

Involvement of semantics from the untrusted kernel is inevitable due to the point of interposition in the virtualization based systems. At the hardware-software interface, only hardware related states are available, such as the physical addresses of the memory accesses, the current value of the program counter or the root of the current page tables. As a result, there exists a wide gap between this information and the one needed to make useful inference at the level of the high-level policy, leading to a discrepancy between the capability needed to enforce the high-level policy and the one achievable by the naive use of virtualization mechanism. The gap is thereafter referred to as the *inference gap*. Bridging the inference gap requires semantics from the untrusted kernel because the high-level entities are defined by the untrusted kernel. Therefore, the specific strategy adopted by individual systems to leverage such semantics to close the inference gap provides key insights into effectiveness of policy enforcement. Chapter 3 examines involvement of such semantics in the gap-bridging attempts.

Also addressed in Chapter 3 are the issues with respect to concurrency. Possible issues of existing schemes are discussed. In addition, two concrete attacks are presented. The stifling attack allows the guest kernel to preserve stale access permissions for certain memory pages and prevent the hypervisor from revoking the permissions. The VPID attack exploits a performance optimization feature also to

# 1.4 Enforcing Isolation Policy on Multicore Platforms

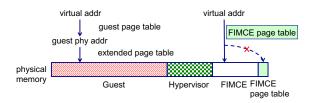

The aforementioned inference gap results in an incomplete isolation boundary when enforcing the isolation policies on multi-core platforms. The reason is that kernel semantics in the guest page tables is involved to translate the subjects and objects, while the guest page tables are subject to manipulation by the guest kernel on a multi-core platform. Therefore, an approach called *full isolation* which specifically takes multi-core platforms into consideration is proposed.

The full isolation approach controls involvement of kernel semantics in the enforcement process of the isolation policy. It applies this principle in its isolation of the memory of the sensitive program, of a physical processor core and of any needed I/O devices. The isolated core, memory and devices form an isolated execution environment which is termed *Fully Isolated Micro-Computing Environment* (FIMCE). Similar to existing works, the FIMCE leverages on the hardware virtualization extension and uses the hypervisor's control on the system resources to achieve isolation.

Due to the full isolation approach, the isolation boundary is clearly defined. The hardware resources are cleanly divided between the trusted and the untrusted, including the core, the memory and any external devices. Because of the complete control over involvement of semantics from the kernel, the inference gap is eliminated. Plus, the concurrency issues are also eliminated by full isolation. The overall benefit is that the malicious guest kernel cannot interfere with management of the identities, neither can it disrupt the execution of the isolated environment.

Another advantage of FIMCE is that the configuration is rather nimble. The hypervisor is free to tweak the hardware configuration of the FIMCE for innovative

use cases. Meanwhile, FIMCE provides a suite of useful libraries for the isolated application, so that the application does not need to be self-contained. The libraries are loaded on demand to minimize the amount of code inside the environment, reducing the risk. To relieve the hypervisor from managing any file system, the library loading process is delegated to the kernel. Thus, the hypervisor's logic is simplified, minimizing its code size. Although the kernel handles library loading, the integrity of the libraries is verified after they are loaded. The linking between the libraries and the application is also verified.

The recently emerged Software Guard Extension (SGX) to the x86 architecture provides hardware based isolation to the applications. Although SGX offers strong memory isolation guarantees, compared to the FIMCE it lacks full isolation and I/O capabilities. A comparison between SGX and the FIMCE and a discussion about possible ways to integrate both for stronger security guarantees are presented.

#### 1.5 Consistent Virtual Machine Introspection

The fully isolated environment can be applied for consistent and efficient Virtual Machine Introspection (VMI). As introduced in Section 1.1.3, in a traditional out-of-VM VMI system, the introspection program faces a special form of the inference gap. The gap is between the memory view at the level of the concerned data objects in the target VM and the low-level memory view provided by virtualization primitives. In a traditional VMI system, the gap is bridged by the replication of the MMU logic of the target VM and the guest page tables. The replication is necessary because the VMI tools need to translate the virtual addresses used in the target VM to the physical addresses. However, the replication causes issues. It is not only slow due to emulation of the hardware logic, but also not consistent due to replicated page table data. It is thus possible for a malicious target VM to present a fake memory view to the introspection tool, while use another for its own execution.

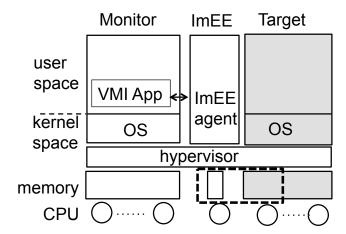

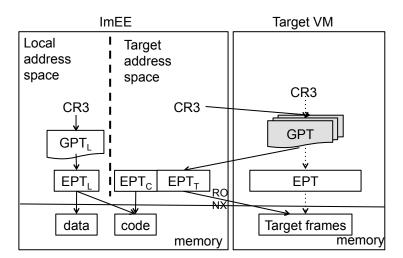

The Immersive Execution Environment (ImEE) addresses these issues. The

ImEE is a special execution environment based on the FIMCE with tweaked address space mappings. The ImEE directly reuses the address space mappings of the target VM by setting the CR3 register to be the same value as the one in the target VM. During execution of the ImEE, the hypervisor also ensures that the CR3 value is always synchronized with the value in the target VM. Therefore, this design ensures that the target VM cannot manipulate any address translations to hide memory content, neither can it stealthily switch to another set of mappings.

Besides a consistent memory view, utilization of hardware virtualization mechanism provides the ImEE a performance advantage, too. In the evaluations, the ImEE shows a remarkable speedup compared to existing software-based tools. Serving as a memory access engine, the ImEE can be integrated with existing VMI tools, providing immediate benefits.

### 1.6 Background

The following two pieces of background knowledge are necessary for the understanding of the rest of the content. First, the address translation process in a virtualized platform is necessary, which is self-evident. The first subsection provides a brief description of the process. For the full details, the readers are referred to the Intel's Software Developer Manual. The second subsection describes memory access in a symmetric multiprocessing (SMP) system. This is necessary for the understanding of the multi-core complications.

#### 1.6.1 Address Translation in Virtualization

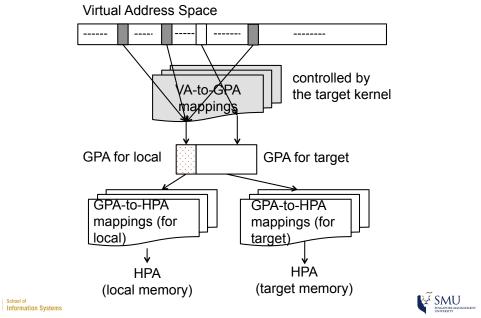

With hardware-assisted memory virtualization, address translation is divided into two stages for any memory access inside the guest. In the first stage, the MMU translates a virtual address (VA) into a Guest Physical Address (GPA) by walking the guest page tables managed by the kernel. In the second stage, the MMU translates a GPA to a Host Physical Address (HPA) by traversing the EPTs managed by

the hypervisor. The roots of the guest page tables and the EPTs are stored in the CR3 register and a control structure field called EPT Pointer, respectively. During address translation, the MMU raises an exception if the type of a memory access conflicts with the permitted types specified in these page tables. There are multiple sets of the page tables in either stages at runtime. Only one set in each stage is active at any time. However, the MMU does not switch the sets automatically, instead, the system software is designated with such a responsibility. The kernel is responsible for switching the CR3 for any reason that it deems appropriate, and the hypervisor is responsible for the EPT Pointer switching.

To reduce latency of address translation, Translation Lookaside Buffers (TLBs) in each CPU core cache recently used translations and access permissions. The MMU traverses the page tables only when the TLBs do not store a matching entry. However, unlike data and instruction caches, it is the software, instead of the hardware, that maintains consistency between the TLBs and the page tables. The operating system and the hypervisor are expected to invalidate the relevant TLB entries after updating the page tables except a few special occasions such as reloading the CR3 register.

The TLB entries can be tagged to improve efficiency. In case of a context switch, all TLB entries need to be flushed because the cached entries may not match the address mapping in the new address space. When context switch happens frequently, such as when there are frequent hypercalls, the MMU needs to walk all the page tables again after each switch, which can incur performance penalties. With hardware virtualization, the number of the page tables to walk can be sixteen<sup>1</sup>, which means sixteen consecutive loads from memory. To avoid such performance penalties, the TLB entries are tagged with certain address space identifiers such as the *Virtual Processor ID* on later x86 architecture. With a tagged TLB, a TLB entry is considered a hit during translation only if its tag matches with the current address

<sup>&</sup>lt;sup>1</sup>This assumes a 64-bit guest with 4KB pages, therefore, there are four levels of page table. To reach the guest page table in every next level, EPT needs to be walked because guest page tables store GPAs. Each EPT walk also traverses four levels of page tables, assuming 4KB pages.

space identifier.

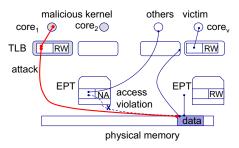

#### **1.6.2** Memory Access in SMP Systems

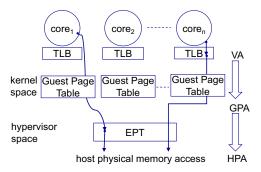

In an SMP setting, multiple cores access the shared physical memory independently as shown in Figure 1.1. They may use different address mappings since address translation is performed independently by each core's MMU. The VA-to-GPA mappings on all cores are controlled by the guest kernel. Depending on the running threads, the cores may or may not use the same set of page tables. The GPA-to-HPA mappings are controlled by the hypervisor. In the most common design, *all* cores of the same VM use the same set of EPTs since the GPA-to-HPA mappings are for the entire virtual machine. In other words, the guest kernel's scheduling, i.e. the guest page table usage, is transparent to the hypervisor.

Figure 1.1: The paradigm of memory access in an SMP setting. The first core has TLB misses and accesses the memory via the guest page tables and the EPTs, while the last core has TLB hits and accesses the memory without consulting any page table.

In the SMP setting, it is more complicated to maintain TLB consistency since the threads on any core may modify the shared page tables while the TLBs are local to each core. Typically, the thread that modifies the paging structures initiates a sequence of operation called *TLB shootdown* whereby the thread on the initiating core fires an Interprocessor Interrupt (IPI) to other cores. Upon the arrival of an IPI, a handler is invoked to invalidate those stale TLB entries on the receiving core. On x86 platforms, the Advanced Programmable Interrupt Controller (APIC) is responsible for receiving and sending IPIs. Its proper behavior affects the success of TLB

shootdown, consequently TLB consistency.

### 1.7 Organization

The rest of this document is organized as follows: Chapter 2 reviews closely related literature. Chapter 3 investigates the issues encountered by existing virtualization based systems, including two attacks on the multi-core platforms. Chapter 4 presents the design of FIMCE. Chapter 5 shows an application in the context of VMI, i.e. the ImEE system and its details. Finally, Chapter 6 concludes this document.

# Chapter 2

### **Related Work**

Virtualization techniques were shown to have application in security systems by early works such as Terra [46] and Proxos [88]. These works utilize the virtualization architecture in its crude form that one VM is assumed to be trusted while the others are not. The security-critical software is subsequently run in the trusted VM. Due to the isolation between VMs, the other untrusted part cannot tamper with the code inside the trusted VM. Further works all are based on the isolation between domains defined by the hypervisor, while they are geared towards different security purposes.

#### 2.1 Trusted Execution Environment

The goal of establishing a TEE is to protect confidentiality and integrity of a sensitive task's data and execution against attacks from the untrusted kernel. With the blessing of the EPT, the hypervisor isolates a sensitive task's code and data regions so that the external software (including the kernel) does not have *any* access to them. The rest of the section groups the literature of isolation-based TEE based on the protected task's scope.

**Code Segment Isolation** TrustVisor [68] proposes to protect a few memory pages called a piece of application logic (PAL) and allows attestation. TrustPath

[104] and MiniBox [62] both build on top of TrustVisor. TrustPath builds a trusted I/O path between a device and an application end point. MiniBox realizes a two-way sandbox by running a Native Client [102] instance as a PAL. XMHF [93] aims for providing a framework for building hypervisor based solutions and is formally verified. Later version of TrustVisor is re-implemented on top of XMHF. XMHF serves as the foundation for two systems that performs I/O isolation [103, 105]. Driverguard [28] is another work on I/O isolation. CAFE [57] also built on XMHF to provide runtime isolation of secret binaries. As a separate line of research, SeCage [67] combines software analysis and hypervisor protection to automatically extract compartments that are protected by the hypervisor at runtime. Fides [86] also protects modules that consist of a few pages. However, the modules are not completely isolated, the code portion is readable while the secret portion is inaccessible. On ARM platform, OSP [30] combines the virtualization extension and TrustZone to offer flexible on-demand protection of a piece of code.

Isolation of a code segment using a separate address space has been demonstrated in previous works such as Gateway [85]. Although the secure driver code is isolated from the guest kernel using shadow page table, it can also be achieved by using EPT.

Application Isolation InkTag [51] isolates the pages of an application and only allows the guest OS to access the ciphertext. A feature of InkTag is that it allows application to express intention to modify the address space so that the hypervisor later can verify the changes performed by the guest OS, a mechanism called *paraverification*. Based on InkTag, Sego [59] improves on verification of the system services. On top of the isolated execution, AppSec [75] provides a trusted human interface for the isolated application. AppShield [29] does not allow guest OS to access the isolated pages, requiring extensive wrapping of system call interfaces. The idea of isolating an entire application has been demonstrated earlier by Overshadow [26] and SP<sup>3</sup> [101], although they are not implemented using the EPT because it was not available.

The difference in the scale of the protected memory results in different design approaches. The systems that protect the entire address space typically need to consider dynamic behavior of the region, i.e. newly mapped or unmapped regions. Therefore, they need to track the changes on the address space. Both Inktag [51] and AppShield [29] lock the page tables of the guest in order to perform such tracking.

The systems that protect only a few pages usually do not consider page swapping by guest kernel. The protected pages are typically allocated by the kernel and are assumed to be always present in memory.

#### 2.2 Kernel Integrity

SecVisor [80] and HUKO [99] remove certain access according to the current code occupying the CPU, in order to protect kernel integrity. While they both try to protect the entire kernel space memory, SecVisor focuses on protecting the kernel space as a whole from user space applications and untrusted extensions. HUKO enforces a fine-grained access control model among kernel space subjects such as kernel module and kernel code.

SecVisor [80] protects the integrity of the kernel code and uses a whitelist to allow any listed kernel extension to be also integrity-protected. On the other hand, HUKO [99] does consider dynamic kernel modules. For this purpose, it needs kernel level semantics so it inserts a module into the protected kernel space in order to track newly added or removed kernel space memory.

As a prerequisite to kernel integrity, SecVisor identifies the kernel by intercepting all traps to kernel. To further harden the kernel, it ensures that the kernel always starts to execute at predefined entry points.

Previous systems that ensure part or the whole of the kernel's integrity before the EPT include HIMA [17], NICKLE [76], HookSafe [96] and Lares [73]. HIMA marks only measured memory pages to be executable during runtime. NICKLE separates the execute and other types of access to different copies of the kernel code

using page table mappings. HookSafe ensures that the gathered kernel hooks are protected. Lares also protects the hooks placed inside the guest using page table permission bits. All these goals can also be achieved using the EPT.

#### 2.3 Mapping Redirection

Heisenbyte [89] separates read access and instruction fetch to a code page to separate copies prepared for each type of access. The separation is applied to any code uniformly. The EPT is used to distinguish the memory accesses. This type of systems does not consider the kernel as malicious. However, when these systems are deployed to practical use, the consequences of a compromised kernel should be considered. Other measure, such as kernel integrity should be coupled with these systems to ensure the security of the system as a whole.

#### 2.4 Event Trap

The EPT can be utilized as merely a means to intercept certain access to memory. After interception, the access is allowed to continue as per normal. Graffiti [33] tracks the rate of allocation in the address space of an application by tracking modifications on the page table. It uses the EPT to intercept writes to the page table. SPIDER [37] and HyperDBG [41] use the EPT to detect execution of code and data access to memory to implement stealth debugging facilities.

Before the EPT became available, trapping events in the guest had been achieve via using shadow page tables. As demonstrated in Patagonix [65], the execution of any binary code is detected by marking memory pages non-executable. The EPT can also be used for this purpose.

#### 2.5 Auxiliary Uses

The EPT can also be used to enforce access permissions that are not supported by guest page table. For example, execute-only permission is *not* possible with guest page table. Because once the P-bit is set, both read and execute permission are granted, however, there is only the NX-bit that removes the execute permission. No such bit that removes the read permission exists. Readactor [32] and NEAR [97] leverage the EPT to enforce execute-only memory on the code pages of a protected application to mitigate memory disclosure.

# 2.6 Virtual Machine Introspection

The fundamental problem of VMI is to acquire the kernel's semantic by reconstructing the kernel objects. Significant efforts have been spent on directly recovering the kernel's data structures from the raw bytes. It can be based on expert knowledge (e.g., Memparser [22], GREPEXEC [23], Draugr [38], and others [4, 7, 8, 9, 12, 13, 47, 74]) and automatic tools (e.g., SigGraph [63], KOP [25], and MAS [35]). These studies usually involve a large amount of engineering work and are useful for memory forensic analysis. Since they do not emphasize on live memory introspection, the security and effectiveness of accessing the guest's live state are not their main concerns. In general, they are orthogonal to our study.

A more sophisticated approach is to reuse the existing kernel to interpret and construct the desired kernel objects from the memory of a live guest. Based on whether the introspection uses the guest VM's kernel or not, schemes using this approach can be further divided into in-VM introspection and out-of-VM introspection.

#### 2.6.1 In-VM Introspection

In general, in-VM introspection schemes aim to save the engineering efforts by relying on the guest kernel's capabilities. Process Implanting [49] loads a VMI program such as *strace* and *ltrace* into the guest VM and executes it under the camouflage of an existing process. SYRINGE [24] runs the VMI application in the monitor VM and allows the introspection code to call the guest kernel functions under a guest thread's context. When the guest kernel is not trusted, the security and effectiveness are totally broken, because it is straightforward for a rootkit to evade or tamper with the introspection. Hence, these in-VM introspection schemes are only useful to monitor the user space behavior in the guest VM. SIM [81] is an in-VM monitoring scheme against rootkits. To run the monitoring code inside the untrusted guest, it creates a SIM virtual address space isolated from the guest kernel. Hooks are placed in the guest to intercept events. The address switches between the kernel and the SIM code is guarded by dedicated gates.

#### 2.6.2 Out-of-VM Introspection

The out-of-VM introspection code stays outside of the target guest. Therefore, it is capable of introspecting the guest VM to detect kernel-level malicious activities without directly facing the attack. Virtuoso [39] generates the introspection code by training the monitor application in a trusted VM and reliably extracting the introspection related instructions from the application. The execution trace is replayed in a trusted VM when performing introspection, during which data accesses are redirected to the guest VM's memory. VMST [42] is another out-of-VM introspection technique. It manages to reuse the kernel code by running the introspection application in a monitor VM emulated by QEMU [21]. A taint analysis runs in the monitor VM and relevant data accesses are redirected to the guest's live memory. Hybrid-bridge [78] is a hybrid approach which combines the strengths of both VMST and Virtuoso. Similarly, the VMI application is running in the trusted monitor VM and

the OS code is reused. The kernel data accesses which are related to the monitoring functionality are identified and redirected to the guest kernel memory when needed. EXTERIOR [44] is another space traveling approach inspired by VMST, which supports not only guest VM introspection but also reconfiguration and recovery of the guest VM.

Process Out-Grafting [84] relocates the monitored process from the guest VM to the monitor VM. The monitor VM always forwards system calls to the guest. The guest kernel handles it and returns the results to the monitored process. This approach requires the implicit assumption that the guest kernel is trusted. VMwatcher [56] is a system that performs rootkit detection from outside of a VM by manually reconstructing the semantic view.

TxIntro [66] is an out-of-VM and non-blocking approach designed for timely introspection. It mainly focuses on retrofitting the hardware transactional memory to avoid reading inconsistent kernel states. In its design, the VMI code runs on an implanted core and can also access the guest memory at a native speed. Nevertheless, it lacks sufficient security concerns and does not provide the introspection code a consistent memory view to that of the guest's.

# 2.7 Isolation With Other Techniques

Flicker [69] makes use of trusted computing techniques to set up a secure execution environment at runtime. It explores AMD's late launch technology which incorporates the TPM-based DRTM. The late launch technique sets up a secure and measured environment to protect a piece of code and data. The drawback is its high latency due to the slow speed of the TPM chip. Moreover, the protected code cannot interact with the rest of the platform.

The recently announced Intel Software Guard Extensions (SGX) [53] offers a set of instructions for an application to set up an *enclave* to protect its sensitive code and data. The hardware isolates the memory region and ensures that data in

the region can only be accessed by the code within. All other accesses are rejected by the hardware. Nonetheless, it is not able to support secure I/O operations, e.g., taking a password input from the keyboard.

As shown in TZ-RKP [18], a security monitor that resides in the secure world established by ARM TrustZone can protect the OS kernel in the normal world at runtime. Virtual Ghost [34] uses a language-level virtual machine to prevent an untrusted OS from accessing an application's sensitive memory regions. It requires compiler support and source code instrumentation on the kernel code in order to ensure control-flow integrity at runtime. PixelVault [92] creates an isolated execution environment on Graphics Processing Units (GPUs). Being an isolated device from the CPU with its own memory, GPU provides a natural ground for building an isolated execution environment. In the past, programming on GPU was difficult because of its highly specialized hardware. However, modern GPUs are becoming increasingly programmable so that executing code on GPU is easier. Nonetheless, this approach still requires significant development effort because there is little support from current systems. SICE [19] isolates a program that ranges from an instrumented application to a complete VM from the guest OS using System Management Mode (SMM). Compared to the micro-hypervisor approach, it features a smaller TCB since the TCB only consists of the hardware, BIOS and the SMM code. However, compared to virtualization, SMM is less standardized, which makes it hard to apply SICE's approach on certain platforms. For example, SICE's multiple processor support relies on hardware features only available on AMD processors.

# **Chapter 3**

# An Analysis of Effectiveness of the

# **Existing Virtualization-based**

# **Schemes**

As introduced in Chapter 1, to meet the tamper-proof requirement and the complete mediation requirement, virtualization based systems resort to the higher privilege level given by the hardware virtualization mechanism. Although this approach guarantees integrity thus satisfies tamper-proof, the systems are confronted with the inference gap which is caused by the system design approach dictated by the hardware virtualization mechanism. Interposing over the hardware-software interface, such systems are limited by the semantics available inside its trust boundary, i.e. the hypervisor space. The limitation makes involvement of semantics from the untrusted kernel inevitable. In order to enforce the high-level policy, these systems need to construct the view at the level of the high-level policy, however, they typically include kernel-defined entities. The construction occurs in a process called policy translation, during which the high-level policy is converted to a form understood by the hardware virtualization mechanism.

In this chapter, the policy translation process in various previous systems is reviewed. And the involvement of semantics from untrusted kernel in the gapbridging process is analyzed. The purpose is to show how the effectiveness of the enforcement is influenced. In doing so, firstly, a conceptual model that serves as the foundation of the rest of the discussion in this chapter is described. Next, the details of the policy enforcement process are examined. The virtualization based systems are referred to as enforcement systems hereafter, because their purpose is to enforce a set of high-level policy.

# 3.1 A Model of the Enforcement Systems

In this section, a model of the enforcement systems is described. The model provides a conceptual foundation for subsequent discussion of this chapter. It shows the policy formulation process in the enforcement system. It emphasizes the trust boundary and the involvement of semantics outside of the boundary during the policy formulation process.

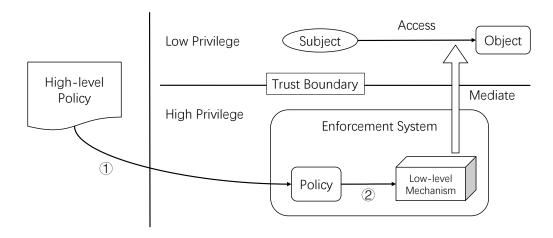

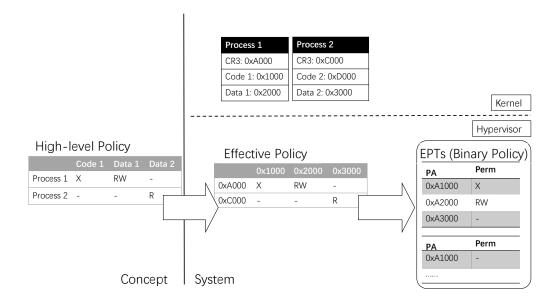

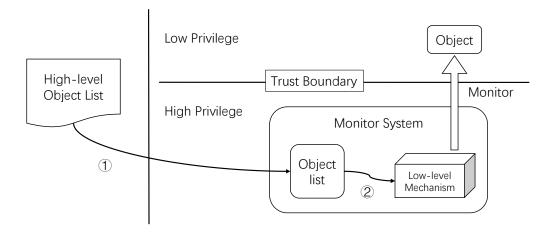

The enforcement systems under consideration are designed to fulfill certain high-level security goal by exercising the reference monitor model. The high-level security goal is expressed in the form of a set of security policy, of which the enforcement realizes the security goal. For the actual enforcement, the enforcement systems rely on certain low-level mechanism, such as the MMU, assumed to be trusted. An illustration is shown in Figure 3.1. An example is a virtualization based system for the purpose of isolation, which enforces a set of isolation policies. The enforcement is achieved by configuring the MMU which is the low-level mechanism.

The enforcement system resides in an environment in which there are two privilege levels, low privilege level denoted  $P_L$ , and high privilege level denoted  $P_H$ . It is assumed that all entities in  $P_H$  are trusted, while all entities in  $P_L$  are not. In practice, there usually exists more than one privilege level in a contemporary computer system. All the privilege levels from low to high constitute an ordered set  $L = L_1, L_2, ..., L_n$ . Our discussion considers the partition of the set L at various

Figure 3.1: The Enforcement System Model

positions. All the privilege levels in the left set is denoted  $P_L$  and only the lowest privilege levels in the right set is denoted  $P_H$ . The boundary between  $P_L$  and  $P_H$  is call the *trust boundary*.

The model also shows the policy formulation process commonly observed in the enforcement systems. Note the fact that the high-level policy is usually described in natural language and involves terms that describe the user-facing entities of a computer system. For example, a policy may be concerned about files, programs or network connections. Furthermore, the fact that the enforcement systems are programs themselves implies that the system designer needs to carefully convert the policy to a form that can be understood by the systems, since programs do not understand the language in which the high-level policies are specified. This form understandable to programs is called *effective policy* thereafter. Lastly, the reliance on the lower-level mechanism usually dictates a second conversion from the effective policy to a form required by the low-level mechanism. This form is called *binary policy*. The two stages of conversion are also illustrated as step 1 and step 2 in Figure 3.1.

The point of mediation by the low-level mechanism on the accesses to objects depend on the nature of the mechanism itself. Typically, the mediation occurs on certain execution path that each access must undergo, so as to satisfy the complete mediation requirement for the low-level mechanism itself. From an architectural

point of view, the mediation usually concentrates at the interfaces between layers, because all accesses can be easily intercepted when they cross an interface. In the case of virtualization, the hypervisor interposes over the hardware-software interface which is traditionally used by the kernel to interact with the hardware. In past systems, the mediation typically happens at the system call interface such as the Janus [45] system. A common drawback of this type of mediation is that the information available at the interface is limited compared to that which is needed for certain high-level policy. For example, the hypervisors are only able to obtain information about physical pages, domains and program counters etc., all of which cannot be directly related to the high-level entities.

## 3.1.1 Conflict Between Tamper-Proof and Complete Mediation

There are two observations that can be made from the model. First, in order to satisfy the tamper-proof requirement, the enforcement system is isolated from the untrusted for its own integrity via the privilege separation mechanism. Second, the isolated states do not provide necessary semantics for decision-making at the level of the high-level policy.

Due to the limited scope, the enforcement system is obliged to associate the isolated states to the high-level entities. Note that the association usually involves semantic information, not necessarily data, beyond the trusted boundary. Such semantic information is defined by the software outside of the trust boundary. However, the enforcement system cannot directly execute untrusted code. Rather, it needs to replicate the semantics-defining logic inside its trust boundary and then acquire the needed semantics using the replicated logic. The consequence of the extra acquisition step is that, the semantics acquired by they enforcement systems is not always accurate. Such inaccurate semantic information relied upon by the enforcement systems presents an approximated view of the rest of the system, which affects the completeness of mediation.

In essence, the enforcement systems face a dilemma. For its own tamper-proof, only isolated states are used which provide limited semantics. However, for complete mediation, all semantics that are relevant should be used. It is, therefore, possible that the scope required by tamper-proof mismatch with the scope required by complete mediation. This situation leads to compromises in design that result in sacrifice in either requirement. For example, the Chrome browser adopts a process-based isolation design, and each browser tab is isolated using one process. The security monitor of Chrome checks the origins of the accesses made by the scripts on a web page to enforce the Same Origin Policy. To perform the checks, rich semantics of the web page and scripts is required. The security monitor resides in the same process as the scripts so that acquisition of the semantics is straightforward. However, this design gives up on the tamper-proof, leading to vulnerabilities that bypasses the checks [55].

On the other hand, many systems choose to ensure tamper-proof first. Consequently, they are limited in the scope of semantics and must approximate by acquiring the semantics outside of the trust boundary. In other words, they need to cross the inference gap. It is shown in the subsequent sections that when this approximation is inaccurate, the complete mediation requirement is compromised.

CAVEAT The discussion here is different from the semantic gap problem discussed in previous works such as VMST [42] and Virtuoso [39], although they appear to both be related to semantics. The semantic gap refers to the challenges in interpreting the meaning of a chunk of bytes. The problem here is about the consequence of the involvement of the semantics outside of the trust boundary in the policy enforcement process.

# 3.1.2 The Inference Gap

The inference gap refers to the gap between the semantics provided within the trust boundary and necessary semantics needed to enforce the high-level policy. The gap exists when the trust boundary does not encompass all the semantics needed to construct the semantic universe defined by the high-level policy. Because of the fact that the enforcement systems all interpose on the hardware-software interface, the semantics in the trust boundary is limited. Therefore, the gap exists and semantics outside of the trust boundary is involved in policy enforcement. Consequently, the enforcement is not accurate because of the untrusted party's manipulation of the semantics. This is a challenging problem and exposes unexpected attack vectors to the untrusted party.

In the enforcement systems, both stages of the policy formulation process cross the inference gap. First, in order to formulate the effective policy, the enforcement systems choose a set of trusted states inside the trust boundary to represent instances of the entities in the high-level policy. The inference gap is crossed in the sense that the trusted states are associated with the high-level entities by using the identity-defining semantics beyond the trust boundary. Secondly, to formulate the binary policy, low-level states and events observable by the low-level enforcement mechanism are associated with the entities and operations defined in the high-level policy.

For example, a hypervisor can securely utilize the architectural states and the physical states of the guest VMs, i.e. register states and physical memory. These states are considered to be inside its trust boundary. Now consider a case where a policy concerns about user input data is desired. To enforce this policy using a hypervisor, the hypervisor needs to deduce the physical address of the input data from the guest's address mappings. However, the guest's address mappings are the semantics outside of the trust boundary of the hypervisor. The hypervisor crosses the inference gap in the sense that it uses this mapping to associate physical addresses to the high-level entity which is the input buffer.

## 3.1.3 The Approximation Function

Crossing the inference gap needs to define relations to bind the states inside the trust boundary to the intended entity at the high-level. A set of such relation is called an *approximation function*. The approximation function is where the fundamental conflict between tamper-proof and complete mediation manifests. Therefore, it is given an abstract treatment first and discuss the concrete conflicts afterwards.

Informally, an approximation function  $F_{approx}: S \to E$  maps from the states in the trust boundary S to the intended entities E. For example, an enforcement system based on the kernel contains the states that correspond to the OS abstractions, such as files and processes etc., inside the trust boundary.