Universidade do Minho Escola de Engenharia

Pedro Miguel Silvestre Machado

Self-Secured Devices: Securing shared device access on TrustZone-based systems

Outubro de 2018

Universidade do Minho Escola de Engenharia

Pedro Miguel Silvestre Machado

Self-Secured Devices: Securing shared device access on TrustZone-based systems

Dissertação de Mestrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efectuado sob a orientação do **Professor Doutor Sandro Pinto**

Outubro de 2018

## Declaração do Autor

Nome: Pedro Miguel Silvestre Machado Correio Eletrónico: a68526@alunos.uminho.pt Cartão de Cidadão: 14390510 4ZY0

Titulo da dissertação: Self-Secured Devices: Securing shared device access on TrustZone-based systems

Ano de conclusão: 2018

Orientador: Professor Doutor Sandro Pinto

Designação do Mestrado: Ciclo de Estudos Integrados Conducentes ao Grau de Mestre em Engenharia Eletrónica Industrial e Computadores

Área de Especialização: Sistemas Embebidos e Computadores

Escola de Engenharia

Departamento de Eletrónica Industrial

De acordo com a legislação em vigor, não é permitida a reprodução de qualquer parte desta dissertação.

Universidade do Minho, 29/10/2018

Assinatura: Pedro Miguel Silvestre Machado

### Acknowledgements

It has been a challenging journey, but there is no easy path to success. And in the end, I'm really grateful for this journey becoming into a personally rewarding one. Nothing would be possible without the people that surrounded me throughout it, and I will hereby try to express my gratitude towards them.

Firstly, I would like to thank my advisor Dr. Sandro Pinto, who challenged me with his pioneer ideas, always made himself available when I most needed, provided me opportunities to improve myself, for all the inexhaustible support that gave me, and for treating me not only as a student but also as a friend. Thanks to Dr. Adriano Tavares for also giving me advice and insight at our meetings and for sharing his extensive knowledge during my master's.

I would also like to thank all my lab colleagues, my companions throughout this journey: Ailton Lopes, Ângelo Ribeiro, David Cerdeira, Franciso Petrucci, Hugo Araújo, José Martins, José Ribeiro, José Silva, Nuno Silva, Ricardo Roriz, and Sérgio Pereira. That proved that the ESRG is more than just a group of extremely competent people, it's a family. Where we all support each other and overcome obstacles as one, with each of these individuals' skill set combined great things can be accomplished.

Thanks to my long-term friends: Álvaro Silvestre, Diogo Pinto, João Peixoto, João Santos, João Coutinho, Jorge Carvalho, Jorge Pereira, Miguel Rego, Paulo Pontes, Ricardo Marques, and Tiago do Val with whom, lately, I was not able to spend as much time as I would like, but were always there for me.

Special thanks to my family for being my biggest supporters and to my girlfriend, Carolina Guimarães, who unconditionally supported me all along and gave me strength to carry on, especially in those moments I was feeling down, sorry for my absense during this period.

### Abstract

With the advent of the Internet of Things (IoT), security emerged as a significant requirement in the embedded systems development. Attacks against embedded systems infrastructures have been increasing, because security is being misconstrued as the addition of features to the system in a later stage of the system development. A new change in the way that systems are being developed is needed, to start guaranteeing security from the outset.

ARM Trustzone is a hardware technology that adds significant value to the security picture. TrustZone promotes hardware as the initial root of trust and has been gaining particular attention in the embedded space due to the massive presence of ARM processors into the market. TrustZone technology splits the hardware and software resources into two worlds - the secure world, dedicated to the secure processing, and the *non-secure world* for everything else. A lot of research has been done around TrustZone technology, ranging from efficient and secure virtualization solutions to trusted execution environments (TEE). Both cases, despite targeting different applications with different requirements, consolidate multiple virtual environments into the same platform and necessarily need to share resources among them. Currently, hardware devices on TrustZone-enabled system-on-chips (SoC) can only be configured as secure or non-secure, which means the dual-world concept of TrustZone is not spread to the devices itself. With this direct assignment method both worlds are unable to use the same device unless it is entirely duplicated, significantly increasing overall hardware costs. Existing shared device access on TrustZone-based architectures have been shown to negatively impact the overall system in terms of security and performance, besides often come with associated engineering effort or substantial hardware costs.

This thesis proposes the concept of self-secured devices, a novel approach for shared device access in TrustZone-based architectures. Self-secured devices extend the TrustZone dual-world concept to the inner logic of the device by splitting the device's hardware logic into a secure and non-secure interface. The implemented solution was deployed on LTZVisor, an open-source and in-house lightweight TrustZone-assisted hypervisor, and the achieved results are encouraging, demonstrating that we increase the security properties of the system for an acceptable cost in terms of hardware.

### Resumo

Com o advento da Internet das Coisas (IoT), começaram a surgir mais preocupações relativas à segurança no desenvolvimento de sistemas embebidos. Os ataques contra infraestruturas deste tipo de sistemas têm vindo a aumentar exponencialmente, dado que a segurança tem vindo a ser reforçada através da adição de várias funcionalidades ao invés de ser considerada desde a fase inicial de desenvolvimento do sistema.

ARM TrustZone, é um exemplo de uma tecnologia de hardware que veio contribuir significativamente para o panorama de segurança. A tecnologia TrustZone promove o hardware como base inicial de segurança, tendo vindo a ganhar particular relevância em soluções de sistemas embebidos devido à presença massiva dos processadores ARM no mercado. A tecnologia TrustZone separa todos os recursos de software e hardware em dois ambientes de execução diferentes, os quais são denominados de mundo seguro, onde é realizado todo o processamento seguro, e o mundo não seguro para tudo o resto. Esta tecnologia já foi alvo de bastante investigação e tem sido explorada na implementação de soluções seguras de virtualização ou até mesmo ambientes seguros de execução (TEE). Apesar de ambos os casos visarem diferentes aplicações com diferentes requisitos, ambos consistem em consolidar vários ambientes virtuais numa só plataforma e inerentemente necessitam de partilhar recursos entre os mesmos. Contudo, atualmente, os dispositivos em system-on-chips (SoC) habilitados com TrustZone podem somente ser configurados como seguros ou não seguros, o que significa que o conceito de duplo ambiente de execução da TrustZone não está estendido aos próprios dispositivos. Com este método de atribuição direta, ambos os mundos não podem utilizar simultaneamente o mesmo dispositivo a não ser que o mesmo seja duplicado, aumentando significativamente os custos de hardware. Atualmente, os métodos existentes de acesso a dispositivos partilhados em sistemas com TrustZone demonstram ter um impacto negativo no sistema em termos de segurança, desempenho e por vezes requerem um grande esforço de engenharia ou custos de *hardware* excessivos.

Esta tese propõe desenvolver o conceito de dispositivos *self-secured*, um novo método de acesso a dispositivos partilhados em sistemas com TrustZone. Estes dispositivos estendem o conceito da TrustZone à logica interna dos dispositivos, dividindo a sua lógica numa interface segura e não segura. A solução implementada foi integrada no LTZVisor, um hipervisor em código aberto e de baixo *overhead* assistido por TrustZone, demonstrando que a segurança do dispositivo partilhado é assegurada com reduzidos custos de *hardware*.

## Contents

| Li       | st of | Figures                                 | xix   |

|----------|-------|-----------------------------------------|-------|

| Li       | st of | Tables                                  | xxi   |

| Li       | st of | Listings                                | xxiii |

| G        | lossa | ry                                      | xxv   |

| 1        | Intr  | oduction                                | 1     |

|          | 1.1   | Motivation                              | . 2   |

|          | 1.2   | Objectives                              | . 3   |

|          | 1.3   | Document Structure                      | . 4   |

| <b>2</b> | Bac   | kground, Context, and State of the Art  | 7     |

|          | 2.1   | Background                              | . 7   |

|          |       | 2.1.1 Virtualization $\ldots$           | . 7   |

|          |       | 2.1.2 ARM TrustZone                     | . 15  |

|          |       | 2.1.3 TrustZone-assisted Virtualization | . 17  |

|          | 2.2   | Related Work                            | . 18  |

|          |       | 2.2.1 Devices Access in TrustZone       | . 19  |

|          |       | 2.2.2 Proxy Task                        | . 20  |

|          |       | 2.2.3 Device Emulation                  | . 21  |

|          |       | 2.2.4 Device Para-Virtualization        | . 23  |

|          |       | 2.2.5 Device Para-TrustZone             | . 24  |

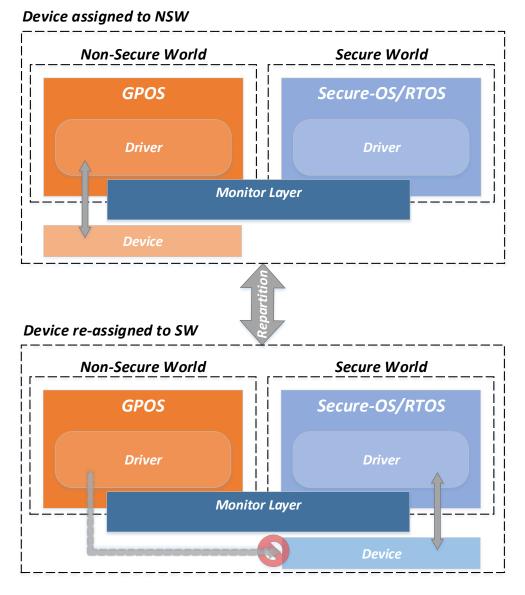

|          |       | 2.2.6 Device re-Partitiong              | . 25  |

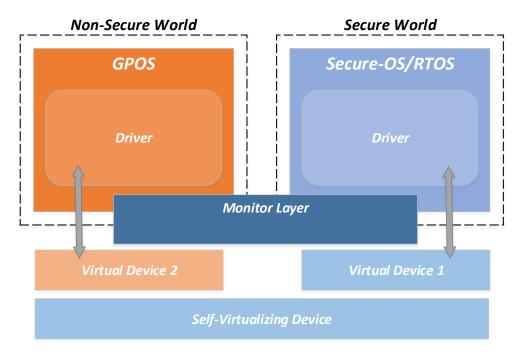

|          |       | 2.2.7 Self-virtualizing                 | . 27  |

|          | 2.3   | Gap Analysis                            | . 29  |

| 3        | Plat  | form and Tools                          | 31    |

|          | 3.1   | Platform Requirements                   | . 31  |

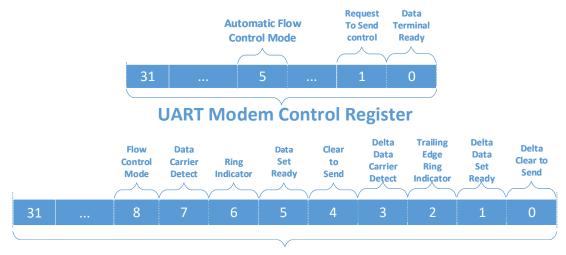

|          | 3.2   | AMBA Advanced eXtensible Interface      | . 32  |

|   |                                               | 3.2.1                                                                                                                            | AXI-Lite                                                                                                                                                                                                                                                                                                                                        |

|---|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

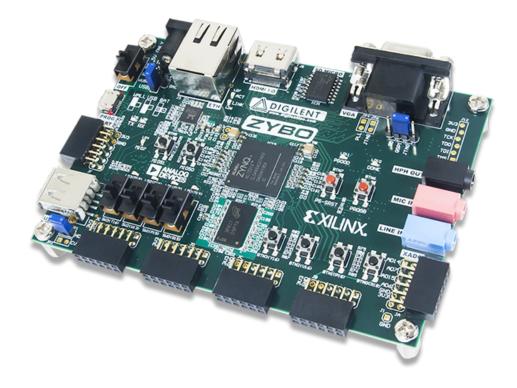

|   | 3.3                                           | ZYBO                                                                                                                             | Zynq-7000 SoC                                                                                                                                                                                                                                                                                                                                   |

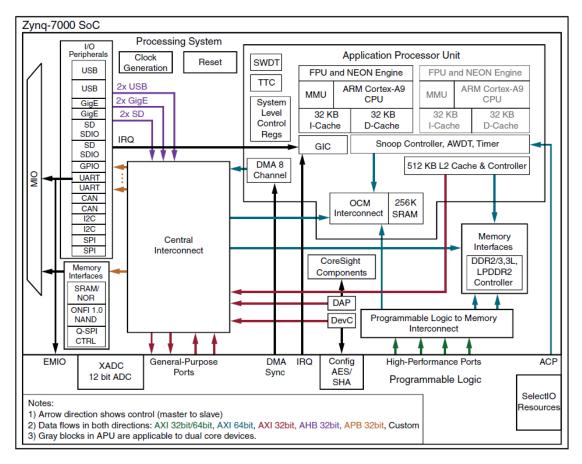

|   |                                               | 3.3.1                                                                                                                            | Zynq-7000 family                                                                                                                                                                                                                                                                                                                                |

|   |                                               | 3.3.2                                                                                                                            | TrustZone technology Support in Zynq-7000 AP SoC $\ldots$ 37                                                                                                                                                                                                                                                                                    |

|   | 3.4                                           | Develo                                                                                                                           | ppment Toolchain                                                                                                                                                                                                                                                                                                                                |

|   |                                               | 3.4.1                                                                                                                            | Vivado Design Suite                                                                                                                                                                                                                                                                                                                             |

|   |                                               | 3.4.2                                                                                                                            | Xilinx SDK                                                                                                                                                                                                                                                                                                                                      |

|   | 3.5                                           | LTZV                                                                                                                             | sor $\ldots \ldots 40$                                                                                                                                                                                                                        |

|   |                                               | 3.5.1                                                                                                                            | CPU virtualization                                                                                                                                                                                                                                                                                                                              |

|   |                                               | 3.5.2                                                                                                                            | Scheduler                                                                                                                                                                                                                                                                                                                                       |

|   |                                               | 3.5.3                                                                                                                            | Memory isolation                                                                                                                                                                                                                                                                                                                                |

|   |                                               | 3.5.4                                                                                                                            | MMU and Cache                                                                                                                                                                                                                                                                                                                                   |

|   |                                               | 3.5.5                                                                                                                            | Device partitioning                                                                                                                                                                                                                                                                                                                             |

|   |                                               | 3.5.6                                                                                                                            | Interrupt managment                                                                                                                                                                                                                                                                                                                             |

|   |                                               | 3.5.7                                                                                                                            | Time management                                                                                                                                                                                                                                                                                                                                 |

|   |                                               | 3.5.8                                                                                                                            | Execution Flow                                                                                                                                                                                                                                                                                                                                  |

|   | 3.6                                           | Opera                                                                                                                            | ting System stacks                                                                                                                                                                                                                                                                                                                              |

|   |                                               | 3.6.1                                                                                                                            | FreeRTOS                                                                                                                                                                                                                                                                                                                                        |

|   |                                               | 3.6.2                                                                                                                            | Linux                                                                                                                                                                                                                                                                                                                                           |

|   |                                               |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                 |

| 4 | Self                                          | -Secur                                                                                                                           | ed Devices 51                                                                                                                                                                                                                                                                                                                                   |

| 4 | <b>Self</b><br>4.1                            |                                                                                                                                  | ed Devices         51           iew                                                                                                                                                                                                                                                                                                             |

| 4 |                                               | Overv                                                                                                                            | iew                                                                                                                                                                                                                                                                                                                                             |

| 4 | 4.1                                           | Overv                                                                                                                            | $iew \dots \dots$                                                                                                                                                                                                                         |

| 4 | 4.1                                           | Overv<br>Self-Se                                                                                                                 | iew                                                                                                                                                                                                                                                                                                                                             |

| 4 | 4.1                                           | Overv:<br>Self-Se<br>4.2.1<br>4.2.2                                                                                              | iew                                                                                                                                                                                                                                                                                                                                             |

| 4 | 4.1                                           | Overv:<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3                                                                                     | iew                                                                                                                                                                                                                                                                                                                                             |

| 4 | 4.1<br>4.2                                    | Overv:<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3                                                                                     | iew                                                                                                                                                                                                                                                                                                                                             |

| 4 | 4.1<br>4.2                                    | Overv:<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se                                                                          | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63                                                                                                                                                                                   |

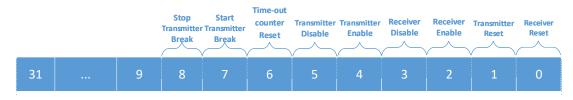

| 4 | 4.1<br>4.2                                    | Overv:<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1                                                                 | iew51ecured Private Timer53Device driver55Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64                                                                                                                                                        |

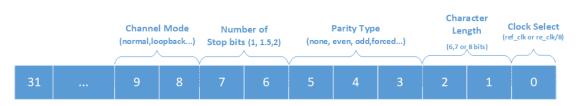

| 4 | 4.1<br>4.2                                    | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2                                                       | iew51ecured Private Timer53Device driver55Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68                                                                                                                            |

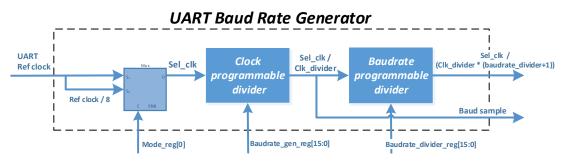

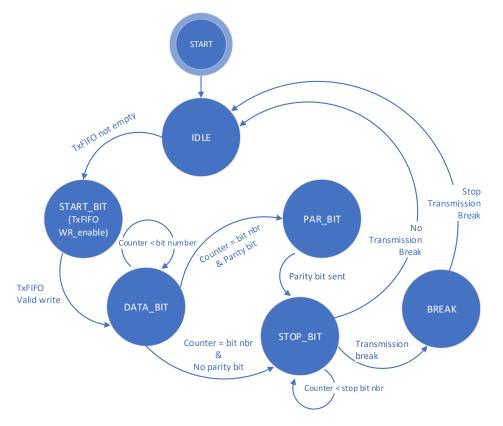

| 4 | 4.1<br>4.2                                    | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3                                              | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules68                                                                                  |

| 4 | 4.1<br>4.2                                    | Overv:<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                      | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules68Receiver and receiver FIFO modules70                                              |

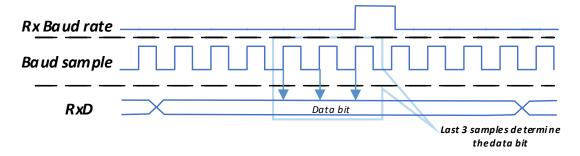

| 4 | 4.1<br>4.2                                    | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                            | iew51cured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60cured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules68Receiver and receiver FIFO modules70Mode switch module72                            |

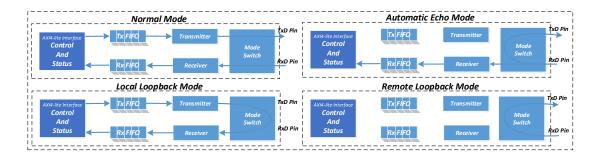

| 4 | 4.1<br>4.2                                    | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6                   | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules68Receiver and receiver FIFO modules70Mode switch module72Modem control module73    |

| 4 | 4.1<br>4.2                                    | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8 | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules70Mode switch module72Modem control module73Device driver74                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Overver<br>Self-Se<br>4.2.1<br>4.2.2<br>4.2.3<br>Self-Se<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.3.7<br>4.3.8 | iew51ecured Private Timer53Device driver56Self-Securing the Private Timer: Minimal Approach57Self-Securing the Private Timer: Default Approach60ecured UART63Control and Status Module64Baud rate generator Module68Transmitter and transmitter FIFO modules70Mode switch module72Modem control module73Device driver74Self-Securing the UART75 |

| <b>5</b> | Eva   | luatior | 1                                                                                              | 95  |

|----------|-------|---------|------------------------------------------------------------------------------------------------|-----|

|          | 5.1   | Engine  | eering effort                                                                                  | 95  |

|          |       | 5.1.1   | Hardware Modifications                                                                         | 95  |

|          |       | 5.1.2   | LTZVisor Modifications                                                                         | 96  |

|          |       | 5.1.3   | FreeRTOS Modifications                                                                         | 97  |

|          |       | 5.1.4   | GPOS Modifications                                                                             | 98  |

|          | 5.2   | Memor   | ry Footprint                                                                                   | 98  |

|          | 5.3   | Perform | mance                                                                                          | 100 |

|          | 5.4   | Hardw   | vare Costs                                                                                     | 101 |

|          |       | 5.4.1   | Self-Secured: Private Timer                                                                    | 102 |

|          |       | 5.4.2   | Self-Secured: UART                                                                             | 102 |

|          | 5.5   | Securit | ty                                                                                             | 103 |

|          |       | 5.5.1   | Security Guarantees                                                                            | 103 |

|          |       | 5.5.2   | Security Experiments                                                                           | 104 |

|          | 5.6   | Discus  | sion $\ldots$ | 107 |

| 6        | Con   | clusio  | n                                                                                              | 109 |

|          | 6.1   | Future  | e Work                                                                                         | 110 |

| Re       | efere | nces    |                                                                                                | 111 |

# List of Figures

| 1.1  | Motivational example for shared device access                   | 2 |

|------|-----------------------------------------------------------------|---|

| 2.1  | System Virtualization Stack.                                    | 8 |

| 2.2  | CPU protection ring levels                                      | 0 |

| 2.3  | Trap and emulate technique                                      | 1 |

| 2.4  | System calls in native and para-virtualized systems             | 2 |

| 2.5  | Virtualization Topologies.                                      | 4 |

| 2.6  | Arm TrustZone hardware Architecture                             | 5 |

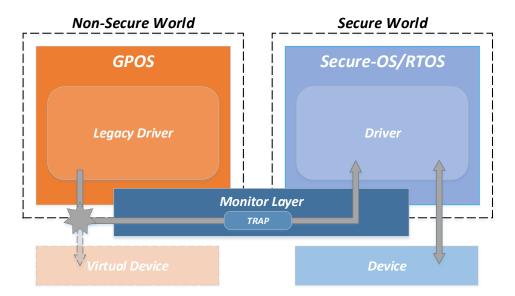

| 2.7  | Direct assignment access method                                 | 9 |

| 2.8  | Proxy Task method                                               | 1 |

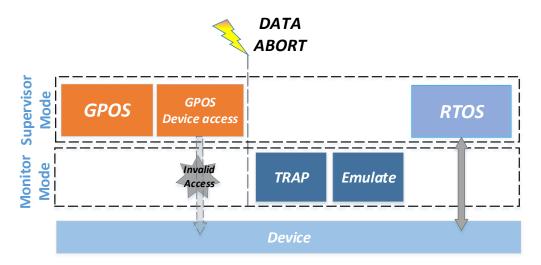

| 2.9  | Device emulation method                                         | 2 |

| 2.10 | Ideal device emulation flow control                             | 2 |

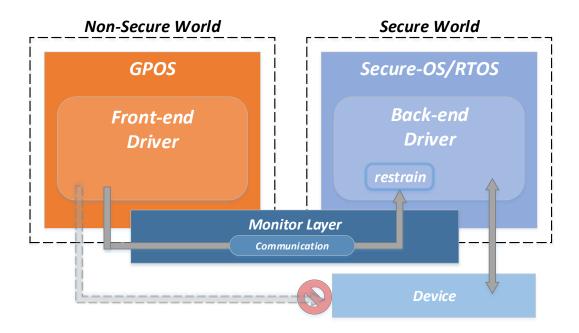

| 2.11 | Device Para-Virtualization method                               | 3 |

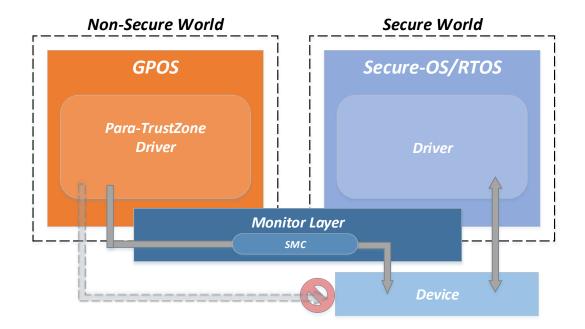

| 2.12 | Device Para-TrustZone method                                    | 5 |

| 2.13 | Device Re-partitioning method                                   | 6 |

| 2.14 | Self-virtualized devices method                                 | 8 |

| 3.1  | The ZYBO Zynq-7000 development board                            | 5 |

| 3.2  | Zynq-7000 SoC overview                                          | 6 |

| 3.3  | Advanced eXtensble Interface (AXI) non-secure control signals 3 | 8 |

| 3.4  | LTZVisor architecture overview                                  | 0 |

| 3.5  | LTZVisor memory configuration                                   | 3 |

| 3.6  | LTZVisor interrupt management when RTOS is running 44           | 5 |

| 3.7  | LTZVisor interrupt management when GPOS is running 44           | 5 |

| 3.8  | LTZVisor execution flow                                         | 7 |

| 3.9  | FreeRTOS software layers                                        | 8 |

| 4.1  | Self-Secured Device Generic Architecture                        | 1 |

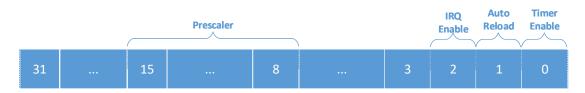

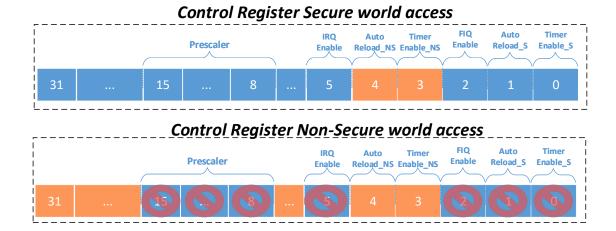

| 4.2  | Private Timer: Control Register                                 | 3 |

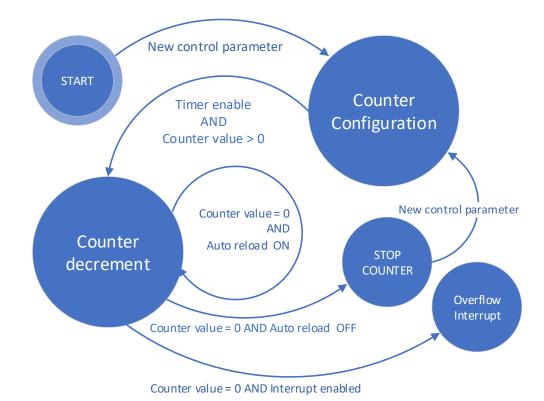

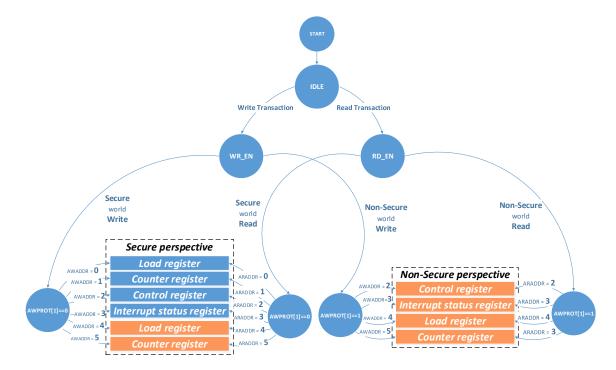

| 4.3  | Private Timer Counter finite state machine                      | 4 |

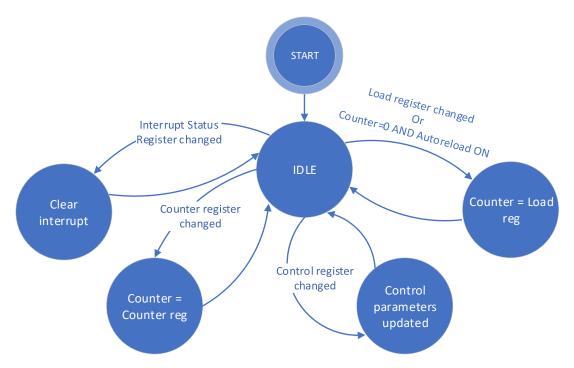

| 4.4  | Private Timer control signals finite state machine                 | 55  |

|------|--------------------------------------------------------------------|-----|

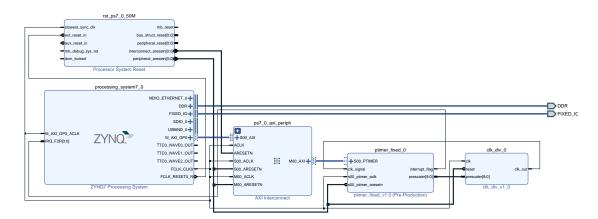

| 4.5  | Private Timer Block design.                                        | 55  |

| 4.6  | Private Timer Block diagram.                                       | 56  |

| 4.7  | Self-Secured Private Timer: Minimal Approach architecture          | 58  |

| 4.8  | Minimal Approach control and interrupt status register             | 59  |

| 4.9  | Self-Secured Private Timer: Minimal Approach register access flow. | 60  |

| 4.10 | Self-Secured Private Timer: Default Approach architecture          | 61  |

| 4.11 | Default Approach control register                                  | 62  |

| 4.12 | Self-Secured Private Timer: Default Approach register access flow  | 62  |

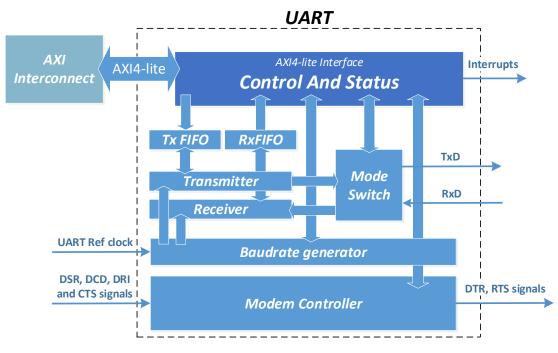

| 4.13 | UART block diagram.                                                | 64  |

| 4.14 | UART Control register layout                                       | 65  |

| 4.15 | UART Mode register layout.                                         | 66  |

| 4.16 | UART Interrupt enable/disable/mask registers layout.               | 66  |

| 4.17 | UART Channel status register layout                                | 66  |

| 4.18 | UART Baudrate generator.                                           | 68  |

| 4.19 | Transmitter finite state machine.                                  | 69  |

| 4.20 | Transmitter data stream                                            | 70  |

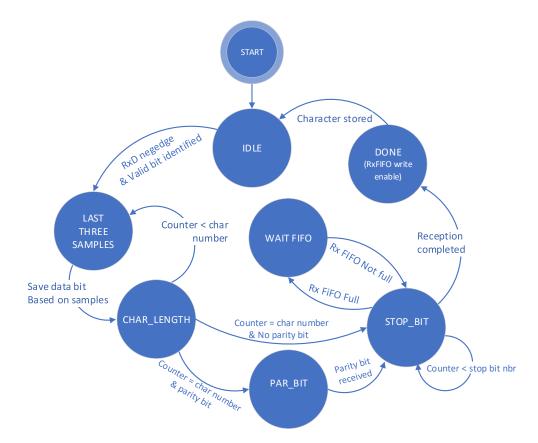

| 4.21 | Receiver finite state machine.                                     | 71  |

| 4.22 | Resynchronized baud rate at data bit mid-point                     | 71  |

| 4.23 | UART operation modes.                                              | 73  |

| 4.24 | UART modem registers layout.                                       | 73  |

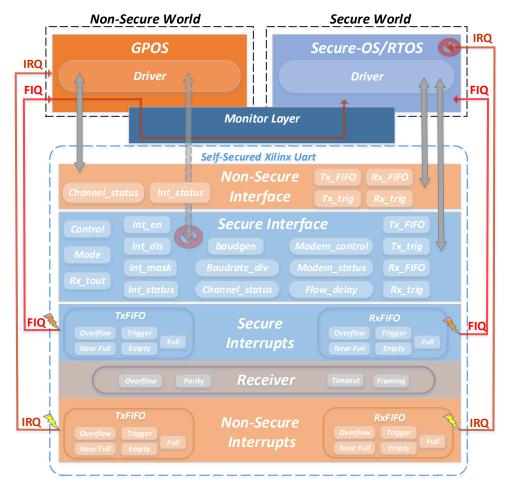

| 4.25 | Self-Secured UART architecture                                     | 76  |

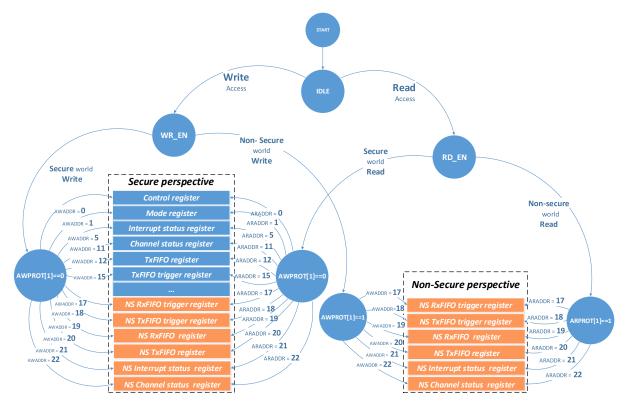

| 4.26 | Self-secured UART register access flow.                            | 80  |

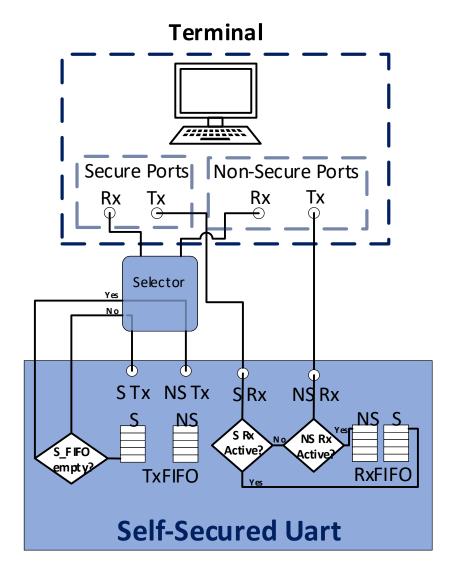

| 4.27 | Self-Secured UART application example                              | 81  |

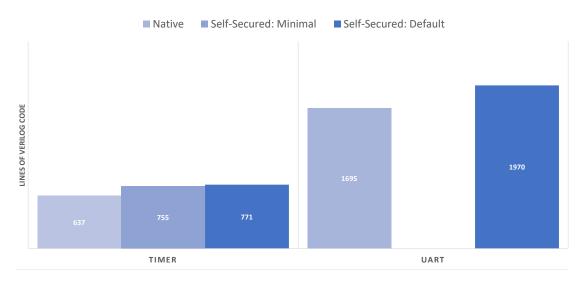

| 5.1  | LoC of the Verilog files, with and without the self-secured imple- |     |

|      | mentation.                                                         | 96  |

| 5.2  | Number of LTZV isor lines of source code for each approach         | 96  |

| 5.3  | Number of FreeRTOS and SW device driver LoC for each approach.     | 97  |

| 5.4  | GPOS Device drivers number of lines of code on each approach       | 98  |

| 5.5  | Number of clock cycles for write/read device operations and in-    |     |

|      | curred device latency.                                             | 101 |

| 5.6  | Self-Secured private timer post-implementation hardware costs      | 102 |

| 5.7  | Self-Secured UART post implementation hardware costs               | 103 |

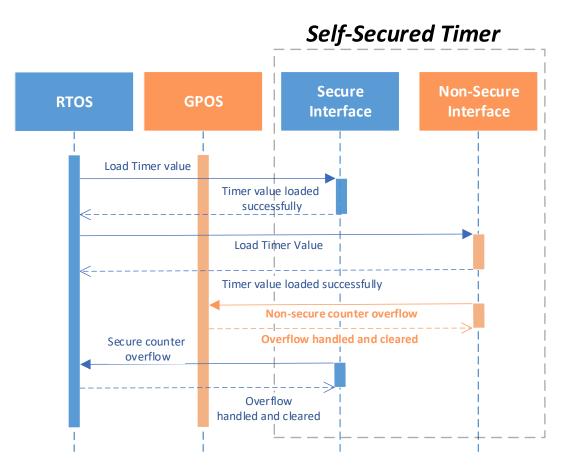

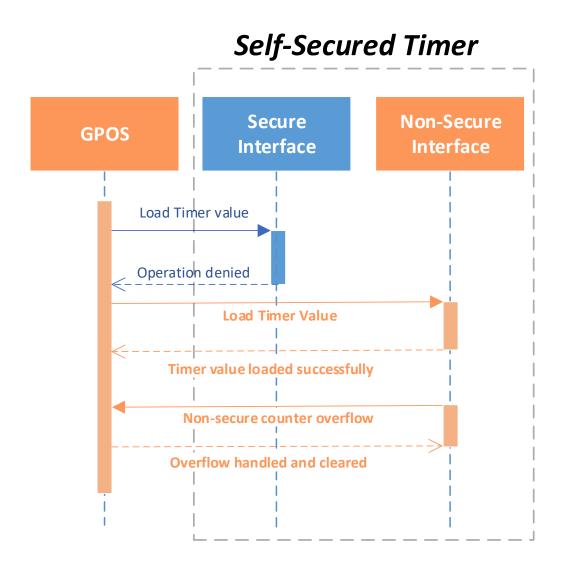

| 5.8  | Protection mechanisms of the Self-Secured Timer upon FreeRTOS      |     |

|      | accesses.                                                          | 105 |

| 5.9  | Protection mechanisms of the Self-Secured Timer upon GPOS ac-      |     |

|      | cesses.                                                            | 106 |

## List of Tables

| 2.1 | Existing shared device access methods comparison          | 29  |

|-----|-----------------------------------------------------------|-----|

| 3.1 | AXI-lite signals                                          | 33  |

| 3.2 | AXI access protection levels                              | 37  |

| 4.1 | Private Timer register map.                               | 53  |

| 4.2 | Self Secured Private Timer: Default Approach register map | 61  |

| 4.3 | UART register map.                                        | 65  |

| 4.4 | Self-Secured UART register map                            | 79  |

| 5.1 | LTZVisor and FreeRTOS memory footprint (bytes)            | 99  |

| 5.2 | Device drivers memory footprint (bytes)                   | 100 |

| 5.3 | Evaluation results comparison                             | 108 |

# List of Listings

| 4.1  | TxFIFO write enable upon AXI TxFIFO register write               | 67 |

|------|------------------------------------------------------------------|----|

| 4.2  | RxFIFO read enable upon AXI RxFIFO register read                 | 67 |

| 4.3  | Example of overflow interrupt management on the Control and sta- |    |

|      | tus module                                                       | 67 |

| 4.4  | Tx signal set according to current state.                        | 70 |

| 4.5  | Secure data transmission prioritization                          | 82 |

| 4.6  | Secure data reception prioritization                             | 83 |

| 4.7  | Resources security configuration at board inialitzion            | 85 |

| 4.8  | LTZVisor GIC hardware initial security configuration             | 86 |

| 4.9  | FreeRTOS interrupt setup                                         | 87 |

| 4.10 | Private Timer entry on Linux device tree                         | 88 |

| 4.11 | Example of an user application to access a device driver         | 88 |

| 4.12 | Platform driver code extract.                                    | 91 |

| 4.13 | Example of Para-TrustZone driver assembly functions              | 92 |

| 4.14 | Board handler function in <i>board.c.</i>                        | 92 |

## Glossary

| ABI           | Application binary interface              |

|---------------|-------------------------------------------|

| ACP           | Accelerator Coherency Port                |

| ACTLR         | Auxiliary Control Register                |

| AMBA          | Advanced Microcontroller Bus Architecture |

| APB           | Advanced Peripheral Bus                   |

| API           | Application Programming Interface         |

| APU           | Accelerated Processing Unit               |

| ASIC          | Application-Specific Integrated Circuit   |

| AXI           | Advanced eXtensible Interface             |

| blob          | Binary Large OBject                       |

| BRAM          | Block RAM                                 |

| BUFG          | Global buffer                             |

| CLB           | Bonfigurable Logic Blocks                 |

| CPU           | Central Processing Unit                   |

| DECERR        | Decode error                              |

| DMA           | Direct memory access                      |

| DRAM          | Dynamic random-access memory              |

| DSP           | Digital signal processing                 |

| DTS           | Device tree source                        |

| $\mathbf{FF}$ | Flip-flop                                 |

| FIFO          | First In, First Out                       |

| FIQ           | Fast Interrupt Requests                   |

| FPGA          | Field Programmable Gate Array             |

| GIC           | Generic Interrupt Controller              |

| GPOS          | General-purpose operating system          |

| HDL           | Hardware description language             |

| I/O           | Input/Output                              |

| IDE           | Integrated Development Environment        |

| IoT           | Internet of Things                        |

|               |                                           |

| IP                     | Intelectual Propertie                     |

|------------------------|-------------------------------------------|

| IPC                    | Inter process communication               |

| IPI                    | Inter-processor interrupt                 |

| IRQ                    | Interrupt Request Line                    |

| ISA                    | Instruction set architecture              |

| ISR                    | Interrupt Status Register                 |

| KB                     | Kilobyte                                  |

| LoC                    | Lines-of-Code                             |

| LTZVisor               | Lightweight TrustZone-assisted Hypervisor |

| $\mathbf{LUT}$         | Look up Table                             |

| MB                     | Megabyte                                  |

| MMU                    | Memory Managment Unit                     |

| $\mathbf{NS}$          | Non-Secure                                |

| NSW                    | Non-Secure World                          |

| OCM                    | On-chip memory                            |

| OS                     | Operating System                          |

| PC                     | Program counter                           |

| $\mathbf{PL}$          | Programmable logic                        |

| PLL                    | Phase-locked loop                         |

| $\mathbf{PMU}$         | Performance Monitor Unit                  |

| $\mathbf{PS}$          | Processing system                         |

| QSPI                   | Quad serial peripheral interface          |

| RAM                    | Random-access memory                      |

| RO                     | Read only                                 |

| ROM                    | Read only memory                          |

| RTOS                   | Real Time Operating System                |

| $\mathbf{R}\mathbf{W}$ | Read/Write                                |

| SCR                    | Secure Configuration Register             |

| SCTLR                  | System Control Register                   |

| SCU                    | Snoop control unit                        |

| SDIO                   | Secure Digital Input Output               |

| SLCR                   | System level control register             |

| SLVERR                 | slave error                               |

| SMC                    | Secure Monitor Call                       |

| SoC                    | System on a chip                          |

| SRAM                   | Static Random Access Memory               |

| $\mathbf{SW}$          | Secure World                              |

|                        |                                           |

| TCB                    | Trusted Computing Base                                                 |

|------------------------|------------------------------------------------------------------------|

| TEE                    | Trusted Execution Environment                                          |

| TLB                    | Translation lookaside buffer                                           |

| TTC                    | Triple Timer Counter                                                   |

| TXT                    | Intel Trusted Execution Technology                                     |

| TZ                     | TrustZone                                                              |

| TZASC                  | TrustZone Address Space Controller                                     |

| TZMA                   | TrustZone Memory Adapter                                               |

| TZPC                   | TrustZone Protection Controller                                        |

| UART                   | Universal asynchronous receiver-transmitter                            |

| UCB                    | Untrusted Computing Base                                               |

| $\mathbf{UI}$          | User interface                                                         |

|                        | User interface                                                         |

| VIF                    | Virtual Interface                                                      |

| VIF<br>VM              |                                                                        |

|                        | Virtual Interface                                                      |

| $\mathbf{V}\mathbf{M}$ | Virtual Interface<br>Virtual Machine                                   |

| VM<br>VMCB             | Virtual Interface<br>Virtual Machine<br>Virtual Machine Control Block. |

### 1. Introduction

With the rise of embedded system's complexity, the demand for solutions to fulfill security and real-time requirements has been escalating [SYKS14]. For decades virtualization technology has been used by the scientific community to efficiently exploit hardware resources between multiple virtual environments [PBB13]. While the advantages of virtualization are quite clear in embedded systems where size, weight, power, and cost (SWaP-C) are important considerations, it also enforces the overall system's security [MJNH16].

Upon the advent of the Internet of Things (IoT), security emerged even further as a significant requirement in the embedded systems development. Ensuring security in such systems is extremely crucial, as they play an important role in many mission and safety-critical systems (aviation, medical, transportation, military), and prior attacks on cyber systems have proven that can even cause physical harm [Lan11]. However, attacks against embedded systems infrastructures have been increasing because security is being misconstrued as the addition of features (e.g., cryptographic algorithms and security protocols) to the system [USK11, PMB15]. A new change in the way that systems are being developed is needed, to start guaranteeing security from the outset [OGP18].

ARM Trustzone [ARM09] and Intel TXT (Intel Trusted Execution Technology) are examples of security-oriented technologies which promote hardware as the initial root of trust. The former is gaining particular attention in the embedded space due to the massive presence of ARM processors in the market. TrustZone technology splits the hardware and software resources into two worlds - the *secure world* (SW), dedicated to the secure processing, and the *non-secure world* (NSW) for everything else. A lot of research has been done around TrustZone technology, ranging from efficient and secure virtualization solutions [FLWH10, PPG<sup>+</sup>17b, MAC<sup>+</sup>17, POP<sup>+</sup>17, PPG<sup>+</sup>17a, PTM16] to trusted execution environments (TEE) [SRSW14, PGP<sup>+</sup>17, POP<sup>+</sup>15]. Both cases, despite targeting different applications with different requirements, consolidate multiple virtual environments in the same platform and necessarily need to share resources among them. Ideally, hardware devices should also be capable of being shared between this virtual environments. However, in TrustZone-enabled SoCs, hardware devices can only be configured as secure or non-secure, which means the dual-world concept of TrustZone is not spread to the devices itself. Consequently, with this direct assignment method, if both worlds require a certain device it needs to be completely duplicated, significantly increasing the overall hardware cost.

#### 1.1 Motivation

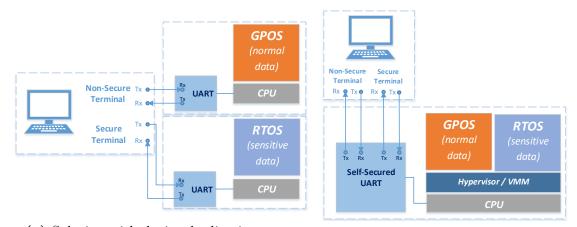

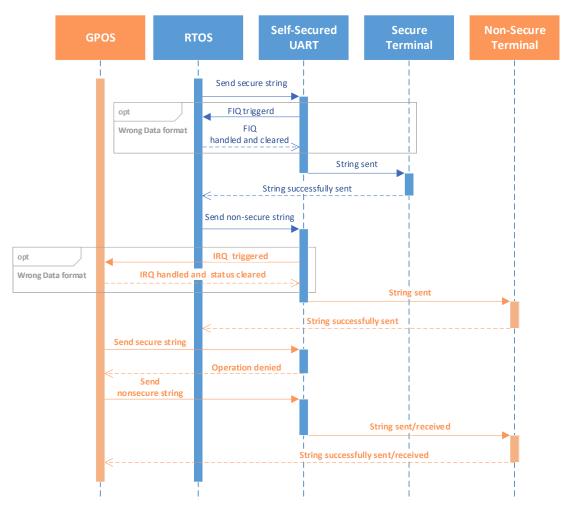

Figure 1.1 illustrates a motivation example with a shared universal asynchronous receiver-transmitter (UART). In this scenario, a computer terminal requires simultaneously to communicate and exchange data with two separate operating systems: a Real-Time Operating System (GPOS), and a General purpose operating system (RTOS). Given the security-critical nature of an RTOS [YBW10], sensitive data exchanged between the computer terminal cannot be accessed or compromised in any way. With the former presented solution shown in Figure 1.1a, the computer terminal exchanges data between two separate terminal interfaces and two individual UART devices. Although this approach can satisfy the design requirements, it requires duplication of the hardware device, considerably increasing the hardware costs. In contrast, the latter solution presented in Figure 1.1b, is based on a virtualized system with device sharing capabilities. This solutions allows consolidating both operations systems in the same platform and avoids duplicating the device.

(a) Solution with device duplication. (b) Solution with shared device access.

Figure 1.1: Motivational example for shared device access.

Herewith, the RTOS can exchange its sensitive data through the secure terminal interface, while simultaneously allowing the GPOS also exchanging its data through the non-secure interface, using the exact same device. With this approach, the GPOS cannot compromise the device, neither can access or compromise the sensitive data being exchanged by the RTOS.

Currently, shared device access on TrustZone-based architectures can follow different approaches:(i) Proxy task [LMH<sup>+</sup>14]; (ii) Device emulation [SVL01]; (iii) Device Para-virtualization [FLWH10, KLJ<sup>+</sup>13]; (iv) Device Para-TrustZone [Pin17]; (v) Device repartitioning [SHT12b]; and (vi) Self-virtualizing devices [RS07, WSC<sup>+</sup>07]. Among all these methods, some bring platform independence and flexibility, with an expense in the TCB size and execution overhead. Others, although presenting less execution overhead, require a considerable engineeringeffort or/and hardware costs and may present limitations in the number of functionalities. Most importantly, several aforementioned approaches allow the device to be intentionally manipulated and cause failure or do not even take security into consideration, compromising the secure state of a device. Therefore, there is a need for a new shared device method that can fully and simultaneously address security while not compromising performance.

#### 1.2 Objectives

This thesis proposes the concept of self-secured devices, a novel approach for shared device access in TrustZone-based architectures. Self-secured devices extend the TrustZone concept to the device itself by separating the device's hardware logic into a secure and non-secure interface.

Under the light of the above arguments, this thesis proposes to achieve the following goals:

- Study and in-depth analysis of Virtualization and ARM TrustZone technology;

- In-depth review and comparison of existing state-of-the-art methods;

- Familiarization with the platform and tools employed throughout this thesis development, including the Zynq7000 SoC, LTZVisor, as well as a deep understanding of the used hardware mechanisms;

- Implementation of the Self-Secured approach on devices of different complexity levels;

- Integration of the implemented solution on LTZVisor, an open-source and in-house lightweight TrustZone-assisted hypervisor, which will be deployed on the Xilinx Zybo board featuring the ARM TrustZone technology;

- Conducting quantitative studies about the hardware costs introduced by the Self-Secured approach, relatively to the device complexity level;

- Extensive evaluation of the Self-Secured devices comparatively to relevant existing state-of-the-art methods in terms of engineering effort, memory foot-print, achieved speedup, and security enhancements.

#### **1.3 Document Structure**

This thesis is structured as follows:

- Chapter 1: The first chapter presents the motivation, goals and the structure of the thesis.

- Chapter 2: The second chapter is divided into two sub-chapters, the first part covers up theoretical concepts of virtualization and ARM TrustZone technology, highlighting the relevant features for this thesis implementation. The second sub-chapter, the state-of-art, describes and compares existing shared device access methods on TrustZone-based systems.

- Chapter 3: The third chapter describes the platform and tools. Firstly, the platform requirements are identified and the development platform chosen according to those requirements. Thereafter, the Advanced eXtensible Interface (AXI) bus protocol is discussed, given its relevance for the development process. Then, the Zybo platform and main features are laid out, highlighting the platform features that were used throughout the development process. Lastly, the LTZVisor, the hypervisor where the developed work is integrated and tested is carefully analyzed and OSes used as guest OSes are justified.

- Chapter 4: The fourth chapter proposes the development of the self-secured approach and the approach application to devices with different complexity level. This chapter also encapsulates the developed device drivers for managing the devices. Finally, it describes the performed modifications to the LTZVisor and hosted guests OSs, in order to integrate and test the developed devices in this hypervisor.

- Chapter 5: The fifth chapter addresses the evaluation. It describes the performed experiments comparing different state-of-the-art solutions.

- Chapter 6: The sixth chapter concludes this thesis, presenting the obtained conclusions derived from this research and tangible results, identifying the limitations, and suggesting future work towards further development on identified limitations.

# 2. Background, Context, and State of the Art

### 2.1 Background

This chapter is divided into two sub-chapters. Firstly, some background regarding virtualization, ARM TrustZone and shared device access is described. Then, the state of art, presents up-to-date methods for sharing devices on TrustZonebased systems, while comparing them among each other, considering their pros and cons.

#### 2.1.1 Virtualization

A computer system is usually represented as consisting of several abstraction levels arranged in a hierarchy that allows the separation of concerns and ease platform independence. The lower layers are implemented in hardware and relate to the operating system and hardware platforms providing the application binary interface (ABI) and instruction set architecture (ISA), interfaces that applications depend on to run. Virtualization technology allows conceiving multiple emulated environments from a single, physical hardware system. This layers can be virtualized and their available resources and interfaces are simulated and mapped onto the interface and resources of the real system [SN05]. This concept of virtualization can be applied not only to subsystems but to an entire machine. By adding a software layer to the real system to support the desired architecture it appears as an emulated different machine, or even a set of multiple machines, duplicates of the original one. These machines, so-called virtual machines can be classified as: Process VMs, providing a virtual ABI or API environment for user applications delivering replication, emulation, and optimization; or System VMs [Hei08], the relevant type for this thesis context, providing a complete environment in which a single-host hardware platform is partitioned into several virtual

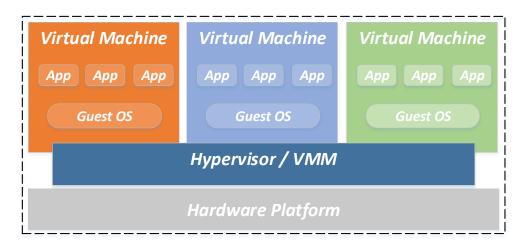

machines supporting the concurrent execution of multiple, isolated guest operating system simultaneously. In Figure 2.1, it is demonstrated the basic software stack for system virtualization. The Virtual Machine Monitor (VMM) or hypervisor component is the software layer that provides the VM environment. The hypervisor normally runs with full privileges, having access to, and managing all the hardware resources. While the guest operating system and its application processes run with lower privilege and are managed under control of the VMM, which in some cases can verify and perform privileged operations in behalf of the unprivileged guest, upon a request for shared hardware resources.

Figure 2.1: System Virtualization Stack.

The classical Popek and Goldberg virtualization requirements [PG74], derived under simplifying assumptions, identify the three essential properties of virtual machines:

- Equivalence: The virtualized environment running under the VMM should have identical behavior to that demonstrated when running on the original machine. This also minimizes the engineering effort of porting guest software to the VM.

- **Resource Control**: It must be impossible to an arbitrary guest to affect other guests resources. The VMM must be in complete control of all the virtualized resources.

- Efficiency: All harmless instructions must be executed by the hardware directly without VMM intervention, minimizing the overhead mechanisms of the VMM. Guest software must show none or only a slight deterioration from their native performance.

In the Popek and Goldberg's terminology, a VMM must present all of the above mentioned properties. This guarantees an acceptable performance without considerable deterioration, mutual isolation among guests while minimizing porting efforts.

#### 2.1.1.1 Classical Software Virtualization Techniques

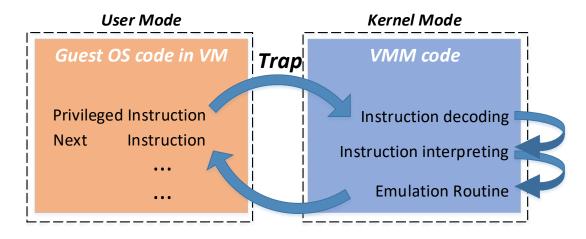

To achieve the necessary technical requirements for virtualization, the target processor must have several modes with different privilege levels that implicate different access rights to the system resources, also known as protective rings in a ring model, illustrated in Figure 2.2. For instance, the well known x86 architecture has four execution modes (or four rings). Typically, the OS running in a physical machine is executed in kernel-mode and the user applications in user-mode. The OS kernel runs with the highest privilege and has access to the full set of instructions (privileged and unprivileged) of the physical processor. Differently, applications running in the unprivileged user mode have no direct access to the privileged instructions, [RHFN<sup>+</sup>12]. The hypervisor must run on an additional privileged mode, in order to be protected from the guest OSs, and guest OSs from their applications, guaranteeing the second property of virtual machines. When a guest OS executes a privileged instruction and does not have the required privilege it creates traps, also known as processor exceptions, which are events that turn control over to the privileged software (hypervisor) by changing the processor mode and setting the program counter (PC) to a known entry point. This extra layer that has an extra privileged mode is provided by CPU extensions for virtualization support. When this extra layer is not provided, implementations often recur to a technique named ring decompression or ring deprivileging [UNR<sup>+</sup>05]. In such approach, the hypervisor is placed in kernel mode and both the OS kernel and user code are pushed back to the unprivileged mode. However, in many processors, only two privilege levels are provided. In that scenario, through a simple technique called trap-and-emulate, an extra virtual privileged level is created, subdividing the OS and user code into two separate privileged layers. Upon the occurrence of a trap, the hypervisor checks the current state of the VM: if it is running on kernel mode it performs the required action, otherwise, it emulates a trap in the VM by changing its state and forwarding the exception to the guest OS. Therefore, both ring compression and trap-and-emulate techniques incur considerable performance costs due to every crossing of modes or execution of a sensitive instruction having to go through the hypervisor, breaking one of the essential properties of virtual machines [PG74].

Figure 2.2: CPU protection ring levels. Adapted from [RHFN<sup>+</sup>12].

Popek and Goldberg [PG74], introduced a classification of instructions of an ISA into different groups, according to their behavior when executed in different processor modes:

- **Privileged**: Instructions that trap if the machine is in user mode, and do not trap if it is in kernel mode.

- **Control sensitive**: Instructions that attempt to change the configuration of resources in the system.

- Behavior sensitive: Instructions whose behavior or result depends on the configuration of the system's resources.

- **Innocuous**: Instructions which are not sensitive, do not require a privileged processor mode to run, and cannot change hardware resources context.

That said, to apply classic virtualization to an architecture all sensitive instructions in its ISA must be privileged. The rest of the sensitive instructions which are not privileged are considered critical instructions. These requirements, guarantee the resource control property, above mentioned, by running the hypervisor with a higher privilege level than the guests. Consequently, in a trap-and-emulate approach, depicted in Figure 2.3, whenever a guest executes a sensitive instruction (in user mode), the following actions are performed in the stated order: the hypervisor takes full control of that action; the instruction is decoded; the trap originating instruction is interpreted; the instruction is emulated; the VM state is updated. To comply with the efficiency property, most of the hosted virtual machines ISA instruction should be identical to the physical underlying hardware in order to be considered innocuous, consequently enabling their execution directly by the hardware.

Figure 2.3: Trap and emulate technique.

#### 2.1.1.2 Para-Virtualization

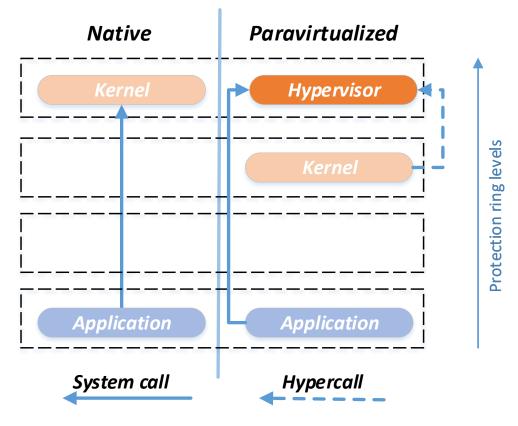

Until this point, the term virtualization has been used to refer to the classic virtualization, known as full-virtualization [RHFN<sup>+</sup>12]. With full-virtualization guest run unmodified and not aware of their virtualization, which may cause performance deterioration for not being able to easily take advantage of virtualization features. Nonetheless, full-virtualization has to possess the strict requirements of classic virtualization (previously described) or hardware virtualization support. Para-virtualization [Chi07, Kai09, VMw06, WSG02] offers potential performance benefits, a consequence of modifying the guest by exploiting its virtualization awareness. Modifications to the guest OS code consist in adding a special set of instructions (named hypercalls) for the execution of critical instructions, replacing instructions of the real machine's ISA. These hypercalls are conceptually equal to a system call. Figure 2.4 shows the difference between system calls and hypercalls and the ring transitions when a system call from an application is issued. An extra transition between layers allows applications to run without modification with the cost of a small speed penalty.

Figure 2.4: System calls in native and para-virtualized systems. Adapted from [Chi07].

A single hypercall can replace a set of many sensitive instructions [Chi07], reducing the frequency of switches between modes and consequently the overhead incurred by the decoding of those instructions and hardware emulation. Overall, para-virtualization can provide a solution for non-virtualizable architectures that do not provide any hardware virtualization support and performance enhancements. Also, due to guest awareness, efficient communication and synchronization mechanisms (IPC) among guests can be implemented. One of the biggest bottlenecks in many full-virtualized systems is device emulation. Device paravirtualization, later scrutinized, replaces the device driver for the emulated device with a front-end device driver removing the emulation associated overhead. Despite all advantages, para-virtualization implicates high engineering effort and can break the resource control property of virtual machines, violating guest isolation.

#### 2.1.1.3 Hardware-Assisted Virtualization

All of the virtualization methods formerly referred are still too inefficient due to the high overhead associated with processor exception mechanisms and context save and restore operations necessary whenever the hypervisor takes control. At some point, different manufacturers have extended the architecture in different ways to overcome the overhead introduced by these mechanisms and decrease VMM complexity, providing virtualization hardware support extensions to aid virtualization adding a set of instructions that makes virtualization considerably easier. These extensions target a wide range of architectures, such as server, desktop architectures (Intel's VT-x [UNR+05]) and embedded architectures as AMR's VE [VH11] or Imagination Technologies' MIPS VZ [ZMH15]. Conceptually, virtualization extensions can be thought as adding a new privilege processor mode, in which, the hypervisor is expected to run and can trap-and-emulate operations that previously, would have failed silently. This added mode, also allows the OS to stay at the same level it expects to be without virtualization and catching attempts to access the hardware directly. However, these extensions also provide other different features, such as replicating and multiplexing important hardware configuration registers, two-level address translation, and virtual interrupt support. In the context of this thesis, is also worth mentioning ARM TrustZone hardware extensions. Even though ARM TrustZone is a security extension and not a virtualization extension, some of the provided features are very similar, for instance, much of the critical hardware is replicated and also adds an extra privileged mode. ARM TrustZone is widely spread and available in low-end and mid-end range microprocessors, contrariwise to virtualization hardware extensions. Hence, it has been exploited to also enable embedded virtualization [FLWH10, HGX<sup>+</sup>17]. Compared to para-virtualization, hardware assisted virtualization allows running unmodified OSs. However, given that the guest is not aware that is running in a virtual environment it cannot take easy advantage of virtualization features which makes it more likely to be slower. Nevertheless, a hybrid approach might be advantageous, for instance, taking advantage of hardware assisted faster system calls and support for nested page tables, and para-virtualization better I/O performance due to its lightweight interfaces to devices.

#### 2.1.1.4 Hypervisor Architectures

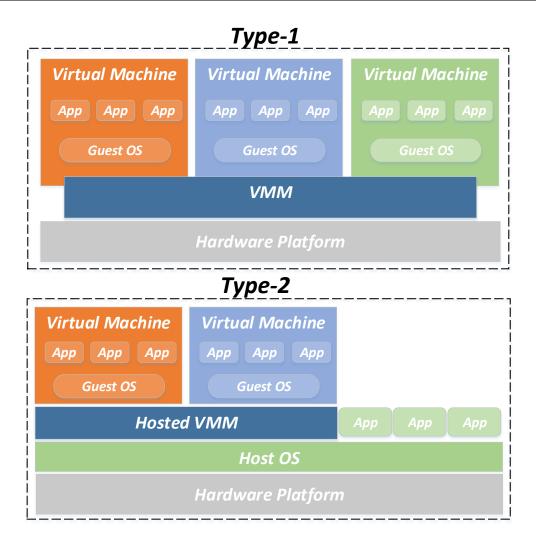

Based on the location of the virtualization layer in the system stack and on the permission of the VMM accesses to the hardware resources, hypervisor topologies [RHFN<sup>+</sup>12, SGB<sup>+</sup>16], despited in Figure 2.5, can be categorized as:

Figure 2.5: Virtualization Topologies.

- **Type-1**, or bare-metal Hypervisors, run in a higher privileged mode than the guest OSs, directly over the hardware where it can manage and access every hardware resource of the system.

- **Type-2**, or hosted Hypervisors, run in an unprivileged mode over the privileged host OS that is already executing, with no direct permissions to the hardware.

Bare-metal hypervisors also referred to as native virtualization, are more suitable for time-critical systems due to the performance degradation of guest OSs only depending on the hypervisor performance. In addition, hosted hypervisors lack of privilege and security is not adequate for embedded devices where critical applications will run, and usually exhibit a poorer performance compared to type-1 hypervisors.

#### 2.1.2 ARM TrustZone

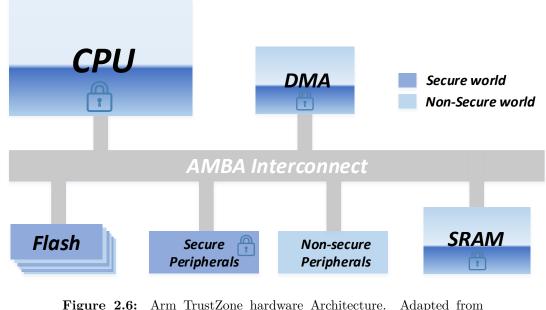

TrustZone technology [ARM09, ARM16] refers to security extensions available in all ARM Application-processors (Cortex-A) for several years, since the ARMv6 architecture. This hardware security extension splits all hardware resources and virtualizes a physical core into two virtual cores, providing two completely separated execution environments: the secure and the non-secure worlds, as illustrated in Figure 2.6. Hardware mechanisms are provided, to ensure secure world resources are not accessible by the non-secure world, while the secure world can access any resource. This strong isolation is important in scenarios where a trusted OS with a small TCB, executing time-critical and security-critical applications, runs in the secure side, alongside a rich untrusted GPOS running in the non-secure world. With the addition of a new architectural feature at the processor level, the 33rd bit, also referred as the NS (Non-Secure) bit, provides separation between these two worlds, indicating in which world the processor is currently executing. This bit is accessible through the added Secure Configuration Register (SCR) present in the System Control Co-processor (CP15) and exclusively accessible by the secure world. Some of the System Control Co-processor (CP15) registers and other critical processor bits are banked in both worlds. The remaining registers which are not duplicated, are either non-accessible by the non-secure world or kept under close supervision of the secure world.

[ARM15].

TrustZone adds a special new secure processor mode called *monitor mode*. This

new mode is used for bridging transactions between both worlds, while preserving the processor state. Unlike other processor modes, monitor mode is only present in the secure world, hence always considered secure. A new privileged instruction was also specified, SMC (*Secure Monitor Call*) analogous to system calls, through this instruction the non-secure world is able to enter monitor mode. The monitor mode can also be enabled by configuring it to handle interrupts (IRQs, FIQs) and exceptions in the secure side.

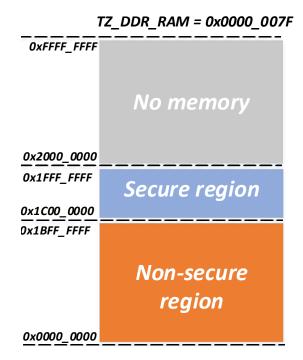

Secure and non-secure world partitioning is not only restricted to the processor, but also propagated to other system resources such as memory, peripherals and buses. Memory infrastructure can also be partitioned into distinct memory regions, which can be configured to be used by both worlds or exclusively by the secure world. If the non-secure world tries to access the secure address space, an abort routed to the monitor mode is triggered. The processor also provides two virtual Memory Management Units (MMUs), delivering separate virtual-to-physical memory address translation tables to each world. Even though the NS bit is still available in the non-secure side, from the non-secure world perspective is transparent, since accesses are always performed with with NS set. This memory isolation is extended and still available at cache level, with the NS bit tagging each entry with the processor state upon the access. At the cache-level, entries from both worlds can coexist removing the need for duplication and cache flushing, consequently accelerating world switching.

To provide the aforementioned memory infrastructure isolation, TrustZone features hardware peripherals such as the TrustZone Address Space Controller (TZASC) and the TrustZone Memory Adapter (TZMA). The TZASC hardware controller provides a programming interface, only accessible by the secure world, that can configure specific memory regions of the DRAM, after being partitioned into different memory segments, whose granularity depends on the SoC implementation. If the TZASC configures one of these memory regions as secure, nonsecure attempts to access it will be denied. TZMA provides the same functionalities, but targeted at the on-chip memory, such as ROM or SRAM. However, TZMA cannot be used for partitioning dynamic memories or memories that require multiple secure regions, unlike TZASC. Additionally, through TrustZone Protection Controller (TZPC), which is a configurable signal control block placed on Advanced Peripheral Bus (APB), system devices can be dynamically configured as secure or non-secure. Moreover, to avoid overloading the processor, direct memory access (DMA) controller can be used for moving data around physical memory. TrustZone is also extended to this engine, featuring both a secure and

non-secure concurrent channels with independent interrupts and controlled by a dedicated APB interface. TZASC, TZMA and TZPC components are all optional and implementation-specific.

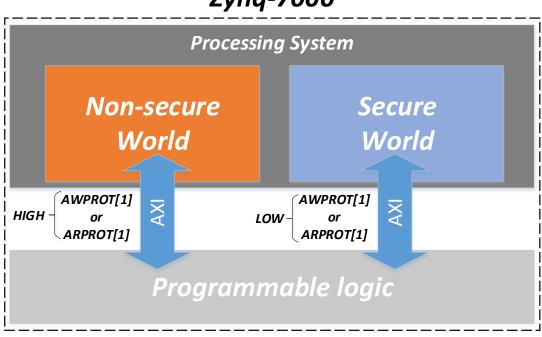

The TrustZone-enabled AMBA Advanced eXtensible Interface (AXI) system bus, carries extra control signals to restrict access on the main system bus, including an additional control bit, the non-secure bit, for each of the read and write channels on the main system interconnect. This enables TrustZone architecture to also secure peripherals (e.g. interrupt controllers, timers, and user I/O devices) through this additional non-secure bit.

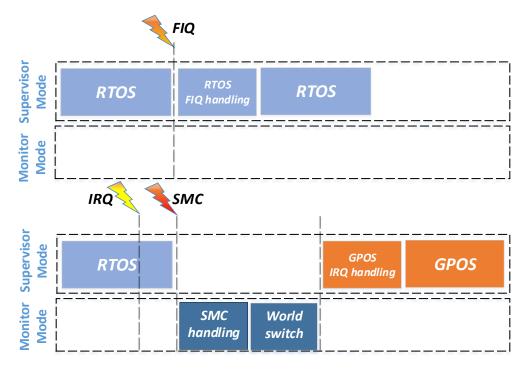

To support the robust management of secure and non-secure interrupts, the Generic Interrupt Controller (GIC) provides both secure and non-secure prioritized interrupt sources. Through the Interrupt Security Register of the GIC an interrupt can be configured as either secure or non-secure. Interrupt prioritization is available, allowing to configure secure interrupts as higher priory than the non-secure interrupts. An important feature that allows secure interrupts to be handled with higher priority than non-secure interrupts, preventing potential denial-of-service attacks. Among other possible interrupt models the GIC allows to configure FIQs as secure and IRQs as non-secure interrupt sources, as suggested by ARM and adopted by LTZVisor.

### 2.1.3 TrustZone-assisted Virtualization

Even though ARM TrustZone hardware extension is security-oriented, some of its features are very familiar to other hardware-assisted virtualization extensions. In particular, the existence of an extra higher privileged mode (monitor mode) where the hypervisor can run; the ability to have full control over the exception system; and being able to execute OSs in the other remaining processor modes. However, classical hardware virtualization depends on two-level address translation which, in fact, is not provided by TrustZone. Instead, the TZASC enables memory segmentation for isolation. Nevertheless, unmodified guest OSes need to cooperate in order to be executed in the respective preassigned segments achieving memory isolation. TrustZone can be efficiently exploited to assist virtualization with the enormous advantage of being widely spread to most low-end and mid-range microprocessors used in embedded devices. The segmented memory model should not impose any problem, given the reduced and fixed number of VMs normally deployed in embedded use-cases.

TrustZone-assisted virtualization can support systems with different OS configurations [PS18], such as single-guest, dual-guest, and multi-guest systems. The simplest architectures use a single-guest setup [FLWH10], in which the single guest OS and its applications run in the non-secure side and the hypervisor in monitor mode. The hypervisor has full access to the whole system, composing the entire system's TCB, and has the responsibility of keeping the secure resources under its close supervision. In contrast, the non-secure guest may only manage and access resources (i.e. devices, memory, and interrupts) configured as non-secure. However, if the non-secure guest requires accessing secure resources, it is able to perform those accesses through para-virtualized drivers, under the hypervisor's supervision.

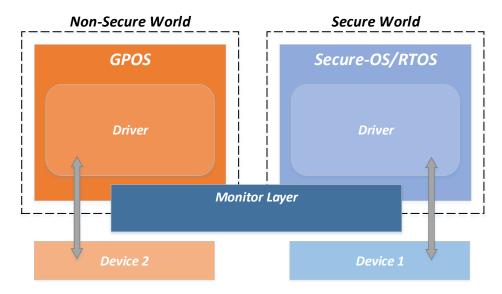

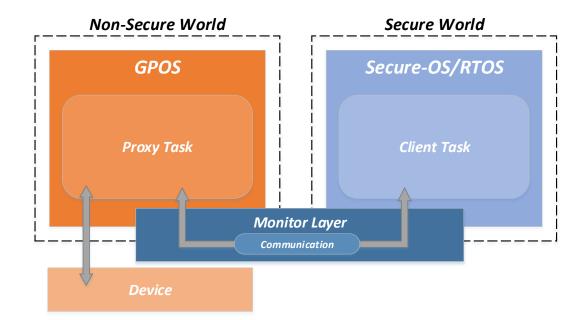

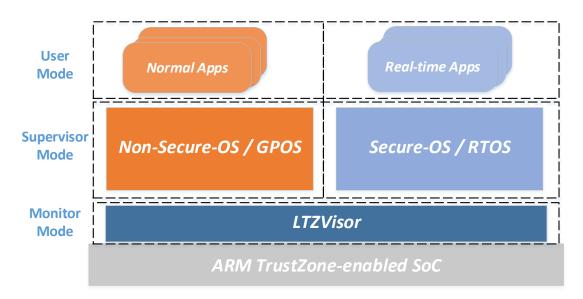

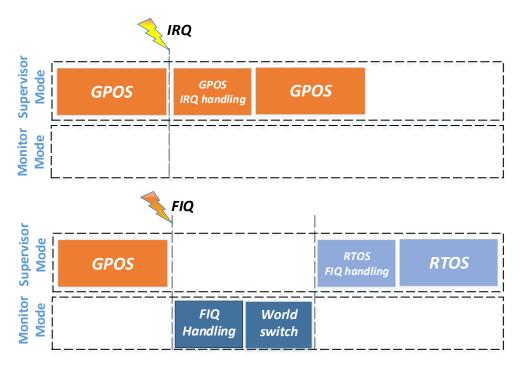

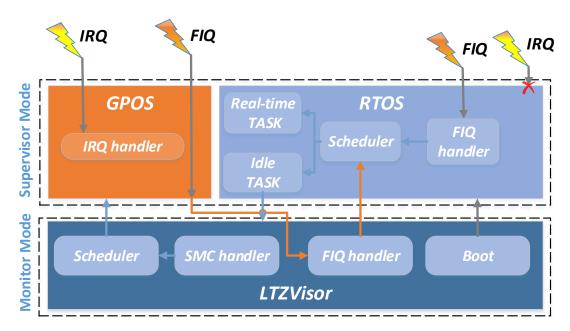

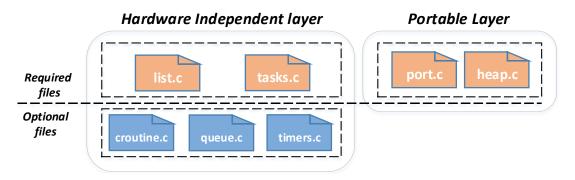

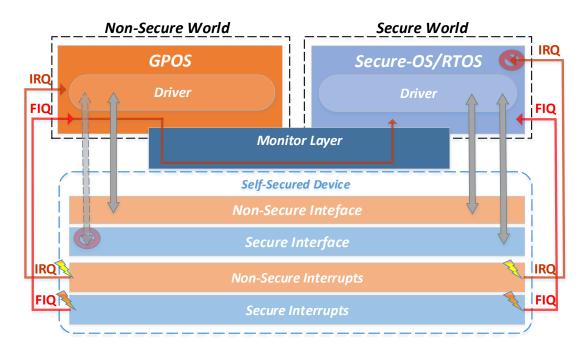

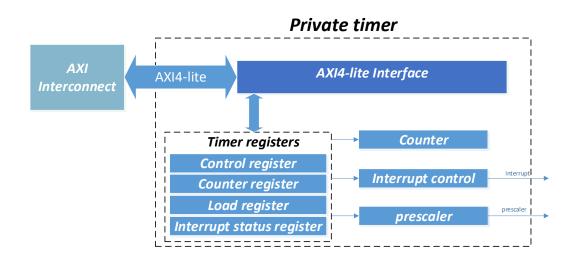

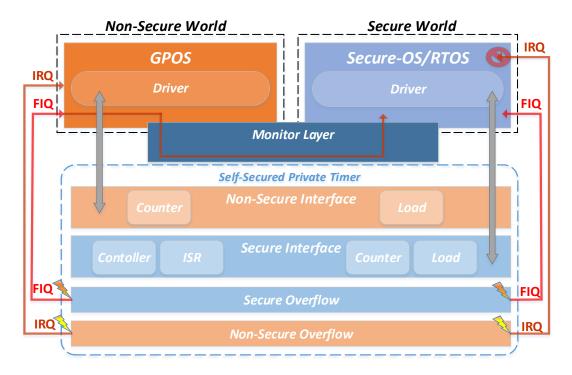

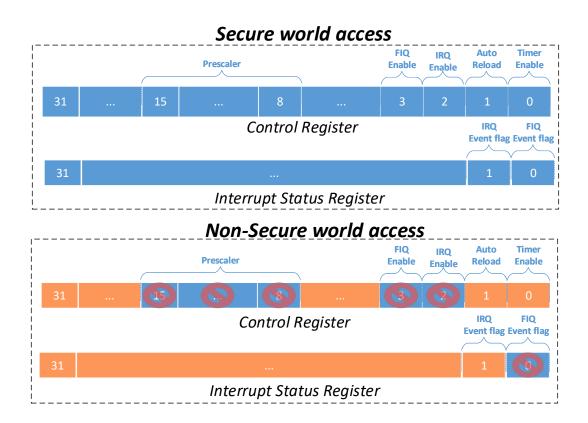

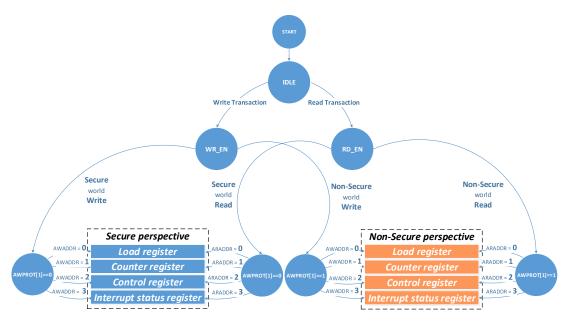

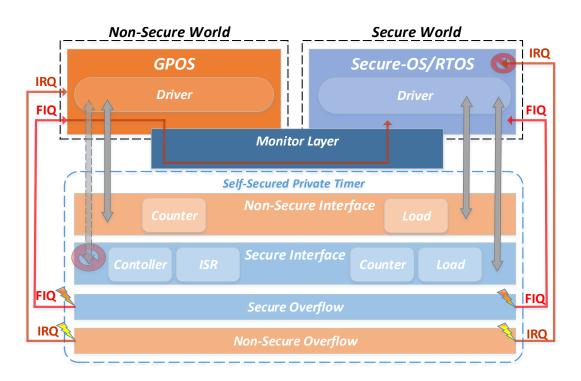

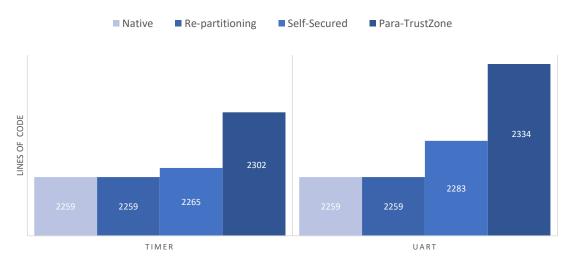

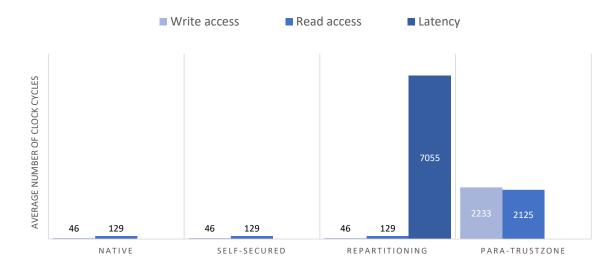

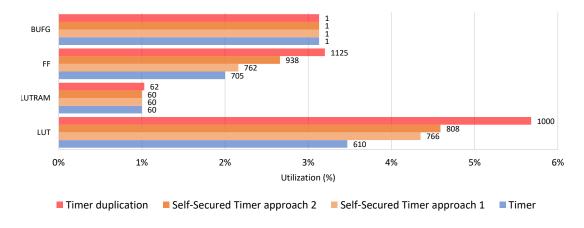

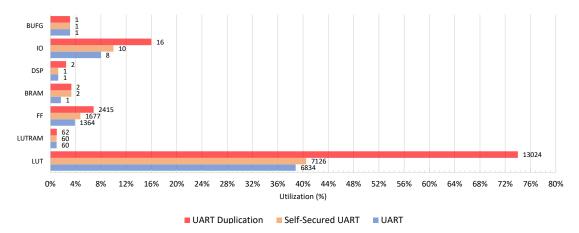

Most of the existing solutions commonly implement a dual-OS configuration in order to have one processor virtual state (non-secure and secure state) dedicated to each guest OS. In this manner, the hypervisor also runs in the monitor mode, while each guest OS runs individually in each world. This type of configuration is ideal in scenarios where an RTOS with real-time functionalities and requirements runs in the secure world, isolated from the GPOS, which runs in the non-secure world, usually during the RTOS idle periods to ensure timing requirements are meet. The LTZVisor [PPG<sup>+</sup>17b], is an example of an open-source lightweight TrustZoneassisted hypervisor mainly targeting the consolidation of mixed-criticality systems, and supports the coexistence of two OSs, one secure RTOS side by side with an untrusted, rich GPOS.