## Università degli Studi di Cagliari

#### **DOTTORATO DI RICERCA**

# INGEGNERIA ELETTRONICA ED INFORMATICA Ciclo XXV

Integrated support for Adaptivity and Fault-tolerance in MPSoCs

# Settore scientifico disciplinare di afferenza ING-INF/01 ELETTRONICA

Presentata da: GIUSEPPE TUVERI

Coordinatore Dottorato PROF. ALESSANDRO GIUA

Tutor/Relatore PROF. LUIGI RAFFO

Esame finale anno accademico 2011 – 2012

#### Ph.D. in Electronic and Computer Engineering Dept. of Electrical and Electronic Engineering University of Cagliari

# Integrated support for Adaptivity and Fault-tolerance in MPSoCs

Giuseppe TUVERI

Advisor: Prof. Luigi RAFFO Curriculum: ING-INF/01 Elettronica

XXV Cycle April 2013

#### Ph.D. in Electronic and Computer Engineering Dept. of Electrical and Electronic Engineering University of Cagliari

# Integrated support for Adaptivity and Fault-tolerance in MPSoCs

Giuseppe TUVERI

Advisor: Prof. Luigi RAFFO Curriculum: ING-INF/01 Elettronica

XXV Cycle April 2013

EBBÉ ECCO

## **Abstract**

The technology improvement and the adoption of more and more complex applications in consumer electronics are forcing a rapid increase in the complexity of multiprocessor systems on chip (MPSoCs). Following this trend, MPSoCs are becoming increasingly dynamic and adaptive, for several reasons. One of these is that applications are getting intrinsically dynamic. Another reason is that the workload on emerging MPSoCs cannot be predicted because modern systems are open to new incoming applications at run-time. A third reason which calls for adaptivity is the decreasing component reliability associated with technology scaling. Components below the 32-nm node are more inclined to temporal or even permanent faults. In case of a malfunctioning system component, the rest of the system is supposed to take over its tasks. Thus, the system adaptivity goal shall influence several design decisions, that have been listed below: 1) The applications should be specified such that system adaptivity can be easily supported. To this end, we consider Polyhedral Process Networks (PPNs) as model of computation to specify applications. PPNs are composed by concurrent and autonomous processes that communicate between each other using bounded FIFO channels. Moreover, in PPNs the control is completely distributed, as well as the memories. This represents a good match with the emerging MPSoC architectures, in which processing elements and memories are usually distributed. Most importantly, the simple operational semantics of PPNs allows for an easy adoption of system adaptivity mechanisms. 2) The hardware platform should guarantee the flexibility that adaptivity mechanisms require. Networks-on-Chip (NoCs) are emerging communication infrastructures for MPSoCs that, among many other advantages, allow for system adaptivity. This is because NoCs are generic, since the same platform can be used to run different applications, or to run the same application with different mapping of processes. However, there is a mismatch between the generic structure of the NoCs and the semantics of the PPN model. Therefore, in this thesis we investigate and propose several communication approaches to overcome this mismatch. 3) The system must be able to change the process mapping at run-time, using process migration. To this end, a process migration mechanism has been proposed and evaluated. This mechanism takes into account specific requirements of the embedded domain such as predictability and efficiency. To face the problem of graceful degradation of the system, we enriched the MADNESS NoC platform by adding fault tolerance support at both software and hardware level. The proposed process migration mechanism can be exploited to cope with permanent faults by migrating the processes running on the faulty processing element. A fast heuristic is used to determine the new mapping of the processes to tiles. The experimental results prove that the overhead in terms of execution time, due to the execution time of the remapping heuristic, together with the actual process migration, is almost negligible compared to the execution time of the whole application. This means that the proposed approach allows the system to change its performance metrics and to react to faults without a substantial impact on the user experience.

## **Contents**

| 1 | Intro              | duction                                                        | 1  |  |  |  |

|---|--------------------|----------------------------------------------------------------|----|--|--|--|

|   | 1.1                | Main goals and thesis organization                             | 1  |  |  |  |

| 2 | 2 State of the art |                                                                |    |  |  |  |

|   | 2.1                | System adaptivity for MPSoCs                                   | 3  |  |  |  |

|   |                    | 2.1.1 Open issues and related works                            | 4  |  |  |  |

|   | 2.2                | Fault-tolerance in NoC-based MPSoCs                            | 6  |  |  |  |

|   |                    | 2.2.1 Open issues and related works                            | 6  |  |  |  |

| 3 | The                | MADNESS Project                                                | 9  |  |  |  |

|   | 3.1                | Framework outline                                              | 9  |  |  |  |

|   | 3.2                | High-level DSE                                                 | 1  |  |  |  |

|   | 3.3                | FPGA-based evaluation environment                              | .3 |  |  |  |

|   | 3.4                | Compilation toolchain and hardware abstraction layer           | 4  |  |  |  |

|   |                    | 3.4.1 Compilation toolchain                                    | 4  |  |  |  |

|   |                    | 3.4.2 Hardware abstraction layer                               | 4  |  |  |  |

|   | 3.5                | Support for Adaptivity                                         | 5  |  |  |  |

|   | 3.6                | Support for Fault-tolerance                                    | .5 |  |  |  |

| 4 | The                | MADNESS evaluation platform 1                                  | 7  |  |  |  |

|   | 4.1                | Platform overview                                              | 7  |  |  |  |

|   | 4.2                | System-level platform description input file                   | 8  |  |  |  |

|   | 4.3                | The soft IP cores RTL repository                               | 21 |  |  |  |

|   |                    | 4.3.1 Elements of the Open Core communication Protocol (OCP) 2 | 21 |  |  |  |

|   |                    | 4.3.2 Processing elements, memories and I/O                    | 22 |  |  |  |

|   |                    | 4.3.3 Interconnection elements                                 | 23 |  |  |  |

|   |                    | 4.3.4 Message Passing programming model                        | 25 |  |  |  |

|   |                    | 4.3.5 Message Passing hardware support                         | 25 |  |  |  |

|   |                    | 4.3.6 Interrupt generation support                             | 26 |  |  |  |

|   |                    | 4.3.7 Software libraries                                       | 26 |  |  |  |

|   |                    | 4.3.8 Shared memory support: synchronization modules 2         | 82 |  |  |  |

|   | 4.4                | The SHMPI platform builder                                     | 29 |  |  |  |

|   | 4.5                | Performance extraction                                         | 80 |  |  |  |

| 5 | Metl               | odologies for adaptive MPSoCs 3                                | 3  |  |  |  |

iv CONTENTS

| Bi | bliogi | raphy    |                                                                     | 71 |

|----|--------|----------|---------------------------------------------------------------------|----|

| 7  | Con    | clusion  | s and future developments                                           | 69 |

|    |        | 6.2.5    | Architectural support hardware overhead                             | 64 |

|    |        | 6.2.4    | Evaluation of the remapping strategy                                | 62 |

|    |        | 6.2.3    | Remapping heuristic and process migration execution time overhead . | 61 |

|    |        | 6.2.2    | Flow control functionality assessment                               | 60 |

|    |        | 6.2.1    | Case studies                                                        |    |

|    | 6.2    | Experi   | ments and results                                                   |    |

|    |        | 6.1.3    | Online task remapping strategies                                    |    |

|    |        | 6.1.2    | Task migration hardware module                                      |    |

|    | 0,1    | 6.1.1    | Fault detection                                                     |    |

|    | 6.1    |          | sed approach                                                        |    |

| 6  | Faul   | t-tolera | ance support within the MADNESS framework                           | 55 |

|    |        | 5.3.3    | Process migration benefits and overhead                             | 50 |

|    |        | 5.3.2    | Inter-tile communication efficiency                                 |    |

|    |        | 5.3.1    | Case studies and MPSoC platform setup                               |    |

|    | 5.3    | -        | ments and results                                                   |    |

|    |        | 5.2.2    | Process migration mechanism                                         |    |

|    |        | 5.2.1    | Migratable PPN process structure                                    |    |

|    | 5.2    | Proces   | ss migration                                                        |    |

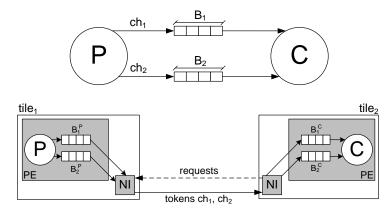

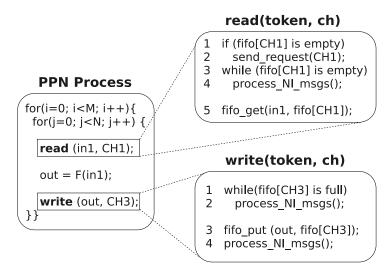

|    |        | 5.1.5    | Request-driven approach (R)                                         | 39 |

|    |        | 5.1.4    | Virtual connector with variable rate approach (VRVC)                | 38 |

|    |        | 5.1.3    | Virtual connector approach (VC)                                     | 37 |

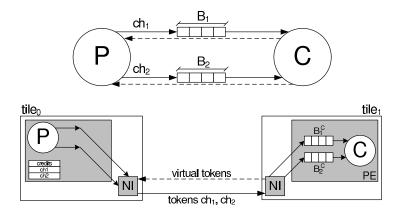

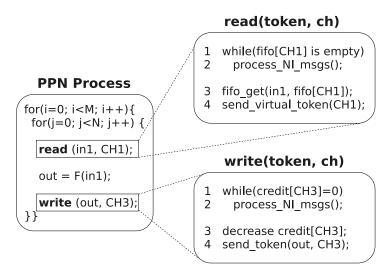

|    |        | 5.1.2    | Inter-tile synchronization problem                                  | 35 |

|    |        | 5.1.1    | Some definitions                                                    | 34 |

|    | 5.1    | PPN-o    | ver-NoC communication                                               | 34 |

## **List of Figures**

| 3.1<br>3.2 | The MADNESS framework                                                             |    |

|------------|-----------------------------------------------------------------------------------|----|

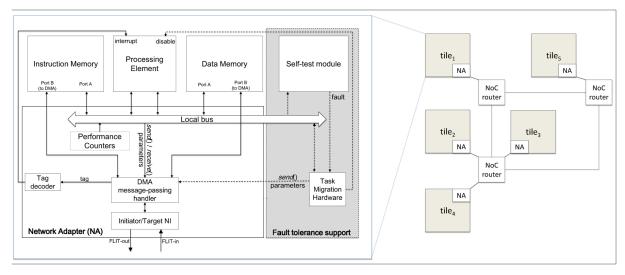

| 4.1        | Overview of the evaluation platform                                               | 18 |

| 4.2        | ×pipes switch architecture                                                        |    |

| 4.3        | A general overview of an example template instance                                | 25 |

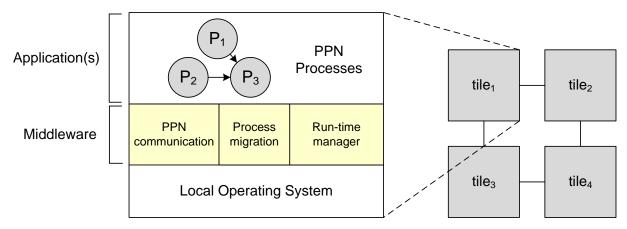

| 5.1        | Software infrastructure for each tile of the NoC                                  | 34 |

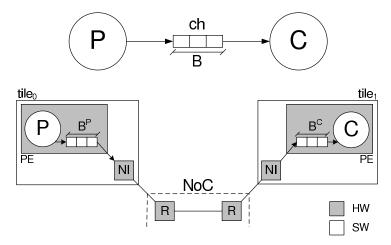

| 5.2        | Producer-consumer pair with FIFO buffer split over two tiles                      | 35 |

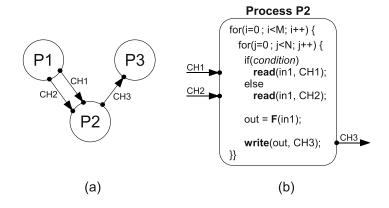

| 5.3        | Example of a PPN and structure of process <i>P</i> 2                              | 35 |

| 5.4        | Producer-consumer pair using the virtual connector approach                       | 36 |

| 5.5        | Pseudocode of the VC approach                                                     | 37 |

| 5.6        | Producer-consumer implementation                                                  | 38 |

| 5.7        | Pseudocode of the R approach                                                      | 39 |

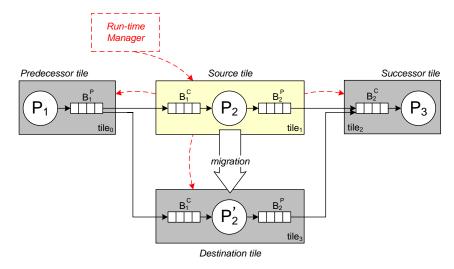

| 5.8        | Migration diagram                                                                 | 41 |

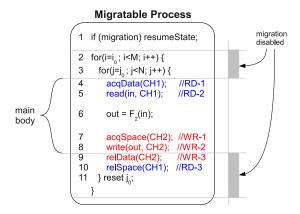

| 5.9        | Migratable PPN process                                                            | 42 |

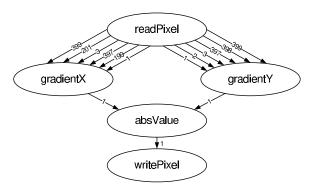

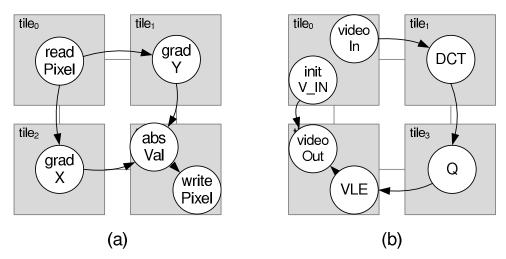

| 5.10       | PPN specification of the Sobel filter                                             | 45 |

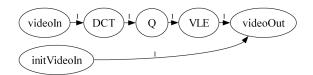

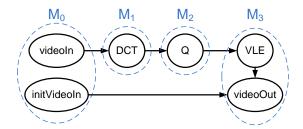

| 5.11       | PPN specification of the M-JPEG encoder                                           | 46 |

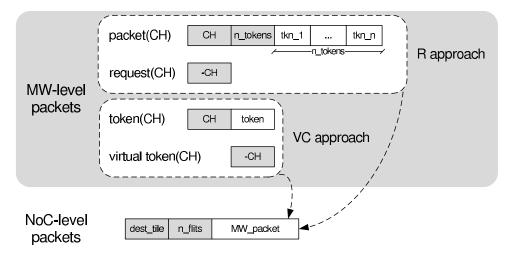

| 5.12       | Structure of middleware- and network- level packets                               | 47 |

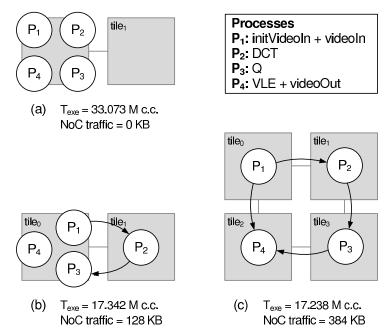

| 5.13       | Fixed mappings for Sobel and M-JPEG                                               | 48 |

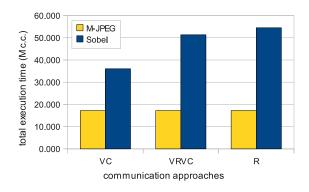

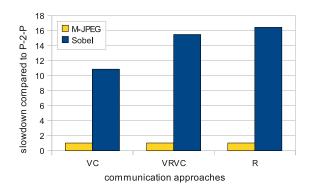

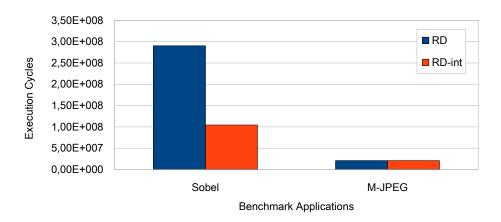

| 5.14       | Total execution time for different communication approaches                       | 49 |

|            | Slowdown for different communication approaches                                   | 49 |

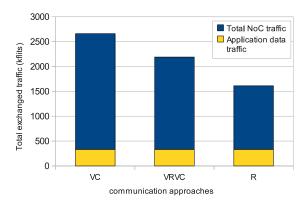

| 5.16       | Traffic injected into the NoC by executing Sobel                                  | 49 |

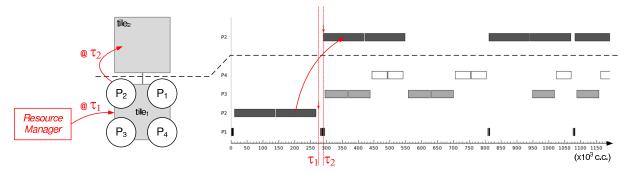

| 5.17       | M-JPEG process scheduling when running on a single tile                           | 51 |

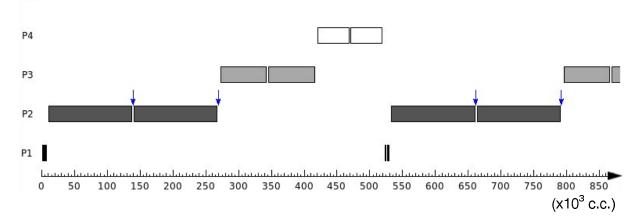

| 5.18       | M-JPEG process scheduling while migrating $P_2$                                   | 51 |

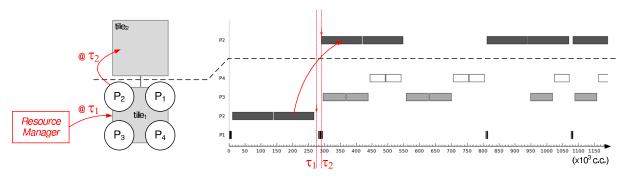

| 5.19       | Execution time and generated traffic as a function of the process mapping $\dots$ | 53 |

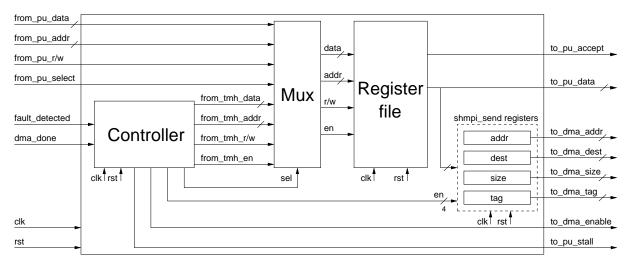

| 6.1        | Interface and internal block diagram of the task migration hardware module        | 57 |

| 6.2        | PPN specification of the M-JPEG encoder                                           | 59 |

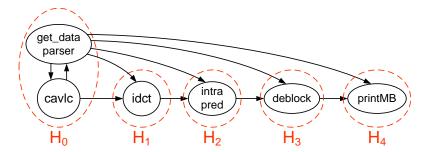

| 6.3        | Simplified PPN specification of the H.264 decoder                                 | 60 |

| 6.4        | Impact of the interrupt-based request messages on the RD flow control             | 60 |

| 6.5        | M-JPEG process scheduling when migrating $M_1$                                    | 61 |

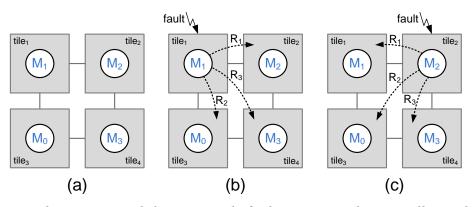

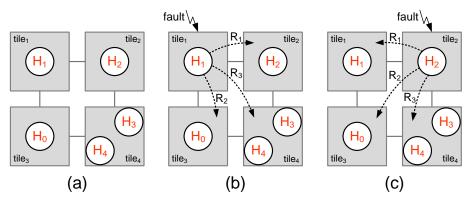

| 6.6        | Initial mapping and the two single-fault scenarios                                | 63 |

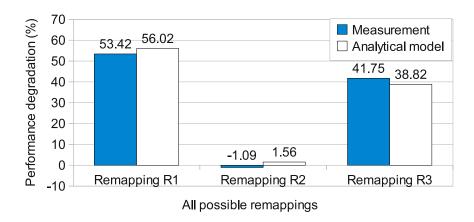

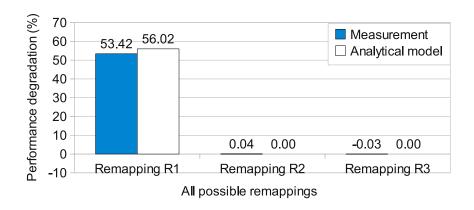

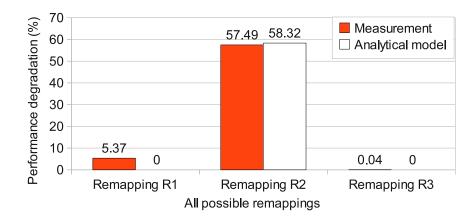

| 6.7        | Comparison of performance degradation when $n_1$ is faulty                        | 63 |

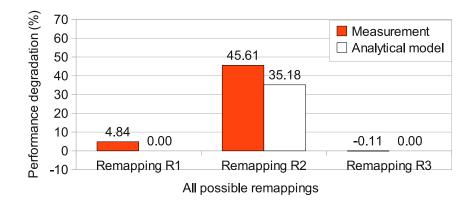

| 6.8        | Comparison of performance degradation when $n_2$ is faulty                        | 63 |

| 6.9        | Initial mapping and the two single-fault scenarios                                | 64 |

vi LIST OF FIGURES

| 6.10 | Comparison of performance degradation when $n_1$ is faulty             | 64 |

|------|------------------------------------------------------------------------|----|

| 6.11 | Comparison of performance degradation when $n_2$ is faulty             | 65 |

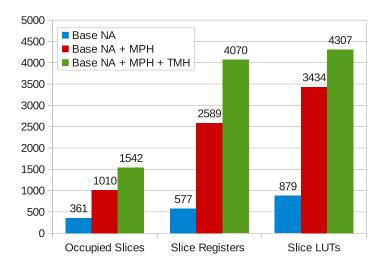

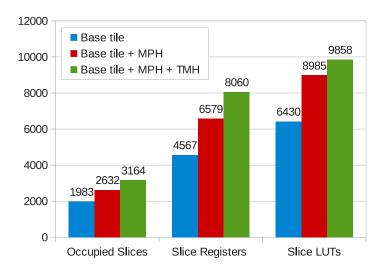

| 6.12 | Area occupation overhead in comparison to the baseline network adapter | 65 |

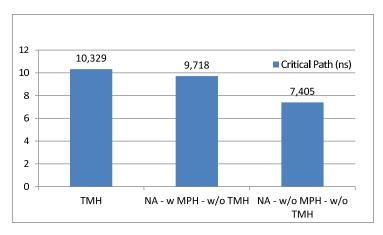

| 6.13 | Critical path length overhead                                          | 66 |

| 6.14 | Area occupation overhead                                               | 67 |

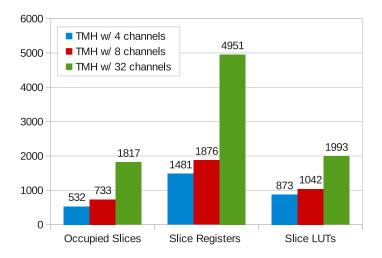

| 6.15 | Area overhead dependence on the supported number of channels           | 67 |

## **List of Tables**

| 4.1 | Implemented OCP signals                   | 22 |

|-----|-------------------------------------------|----|

| 5.1 | Middleware table example                  | 40 |

| 5.2 | Execution times of Sobel functions        | 45 |

| 5.3 | Execution times of M-JPEG functions       | 46 |

| 6.1 | Execution times of M-JPEG processes       | 59 |

| 6.2 | Execution times of H.264 processes        | 60 |

| 6.3 | Calculation times of remapping heuristics | 62 |

## **Chapter 1**

## Introduction

### 1.1 Main goals and thesis organization

Modern embedded systems become increasingly dynamic and adaptive. This is true for both application and architecture. Regarding application, we can distinguish between two classes of dynamic behaviour: intra-application and inter-application. An example of intraapplication dynamic behaviour is when an application aims at keeping an estabilished level of Quality of Service (QoS) under varying circumstances. For example, a video application could dynamically lower its resolution to decrease its computational demands in order to reduce the battery drain. Inter-application adaptive behaviour is caused by the fact that modern embedded systems often require to support an increasing amount of applications and standards. Also, where such systems used to be "closed systems" in the past, today's embedded systems become more and more "open systems" for which third-party software applications can be downloaded and installed, or updated. As a consequence, the application workload in such systems (i.e., the applications that are concurrently executing and contending for system resources), and therefore the intensity and nature of the application demands, can be very fluctuating. For this reason, the notion of workload scenarios has gained considerable popularity in the past years [36], [16]. The underlying computer architectures of embedded systems also become more and more adaptive and dynamic. For example, reconfigurable hardware components such as Field Programmable Gate Arrays (FPGAs) have become popular architectural elements that allow for accelerating specific computational kernels in applications (e.g., [44]). Moreover, there has been a growing interest on reconfigurable on-chip networks (e.g., [20]). Such reconfigurable networks allow for adapting the network (in terms of e.g. QoS requirements, topology, etc.) to the demands of the application(s) that are being executed. Improving system reliability is another area in which the notion of adaptivity is gaining research attention. In the case of, e.g., a malfunctioning architecture component, other components in the system could take over the task(s) of the faulty component. This either requires component duplication and some voting mechanism (which may be undesirable for many embedded systems in which system costs play a key role) or adaptive system behaviour that allows for a redistribution of application tasks to architecture resources.

The above trend towards adaptivity and dynamic systems causes an important anomaly in design methods for modern embedded systems. Traditionally, the mapping of applications

onto the underlying architectural components of an embedded system has always been done in a static fashion. Here, we refer to the term "mapping" as the process of allocating architectural resources that will be used by the application(s), and the spatial binding as well as scheduling of application tasks to these resources. This mapping process is of primary importance to embedded systems as it should carefully trade-off non-functional requirements (performance, power, costs, reliability, etc.). However, with the increasing adaptive and dynamic behaviour of systems, such mapping decisions cannot be made at design time anymore. A run-time system will be needed to dynamically map and re-map applications onto the (available) underlying architectural resources. Moreover, with deep-sub-micron technology, the possibility of experiencing faults in the circuitry is significant, requiring the system to feature support for graceful degradation of the performance in case of malfunctioning.

To cope with these issues, we have devised techniques that allow to change the mapping of the application processes onto the processing cores at run-time. The development of these techniques required the introduction of dedicated support at several levels. At the architectural level, we considered a distributed-memory tile-based template, where tiles are interconnected through a NoC, to support the high flexibility and scalability demands. The architectural template is customizable in terms of the number of processors and network topology. It has been extended with newly developed hardware IPs that facilitate the runtime management and that expose to the applications the needed communication and synchronization primitives, referring to a message-passing model of computation. Extensions will be described in Chapter 4. At the software level, a specific layered infrastructure has been devised, that is actually in charge of managing the mapping of the tasks, the communication between them and the migration process. The software/middleware infrastructure will be described in Chapter 5. Eventually, fault-tolerance support has been introduced at both software and hardware levels. The idea is to exploit the migration method in case of runtime faults in the processing cores. The tasks mapped on faulty cores have to be migrated to fault-free ones at run-time, so that the application can continue its execution without disruption. To this aim, several extensions to the process migration mechanism are required. The details of the proposed techniques for fault-tolerance will be described in Chapter 6.

## **Chapter 2**

## State of the art

## 2.1 System adaptivity for MPSoCs

The technology improvement and the adoption of more and more complex applications in consumer electronics are forcing a rapid increase in the complexity of multiprocessor systems on chip (MPSoCs). Following this trend, MPSoCs are becoming increasingly dynamic and adaptive, for several reasons. One of these is that applications are getting intrinsically dynamic. Another reason is that the workload on emerging MPSoCs cannot be predicted because modern systems are open to new incoming applications at run-time. A third reason which calls for adaptivity is the decreasing component reliability associated with technology scaling. Components below the 32-nm node are more inclined to temporal or even permanent faults. In case of a malfunctioning system component, the rest of the system is supposed to take over its tasks.

Thus, the system adaptivity goal shall influence several design decisions, that have been listed below:

1) The applications should be specified such that system adaptivity can be easily supported. To this end, we consider Polyhedral Process Networks (PPNs) [45], a special class of Kahn Process Networks (KPNs) [22], as model of computation to specify applications. PPNs are composed by concurrent and autonomous processes that communicate between each other using bounded FIFO channels. Moreover, in PPNs the control is completely distributed, as well as the memories. This represents a good match with the emerging MPSoC architectures, in which processing elements and memories are usually distributed. Most importantly, the simple operational semantics of PPNs allows for an easy adoption of system adaptivity mechanisms. For instance, the process state which has to be transferred upon process migration does not have to be specified by hand by the designer and can be smaller compared to other solutions.

2) As a second design decision, the hardware platform should guarantee the flexibility that adaptivity mechanisms require. Networks-on-Chip (NoCs) [12], which is the platform model considered within this thesis, are emerging communication infrastructures for MP-SoCs that, among many other advantages, allow for system adaptivity. This is because NoCs are generic, since the same platform can be used to run different applications, or to run the same application with different mapping of processes. However, there is a mismatch between the generic structure of the NoCs and the semantics of the PPN model of compu-

tation (MoC). Therefore, in this thesis we investigate and propose several communication approaches to overcome this mismatch.

*3)* Finally, the system must be able to change the process mapping at run-time, using process migration. To this end, a process migration mechanism has been proposed and evaluated. This mechanism takes into account specific requirements of the embedded domain such as predictability and efficiency. The efficiency of the proposed process migration mechanism depends on the design decisions discussed above, such as the MoC used to specify the applications. In this respect, the adoption of the PPN MoC ease the realization of process migration, when using the proposed approach. During our research activities, we found that the problem of a predictable and efficient process migration mechanism in distributed-memory MPSoCs has not received sufficient attention. The aim of the work done over these years is to contribute to a more mature solution of this problem.

#### 2.1.1 Open issues and related works

Run-time resource management is a known topic in general purpose distributed systems scheduling [9]. In particular, process migration mechanisms [40, 29], have been developed and evaluated in this context to enable dynamic load distribution, fault resilience, and improved system administration and data access locality. In recent years, run-time management is gaining popularity and applications also in multiprocessor embedded systems. This domain imposes tight constraints, such as cost, power, and predictability, that run-time management and process migration mechanisms must consider carefully. [34] provides a survey of run-time management examples in state-of-the-art academic and industrial solutions, together with a generic description of run-time manager features and design space.

A relevant part of the work spent working on adaptivity topics has been focused on a specific component of run-time management strategies, namely the process migration mechanism. Papers addressing process (or task) migration implementation in MPSoCs can also be found in the literature. The closest to the presented work is [4], in which the goals of scalability and system adaptivity are achieved through a distributed task migration decision policy over a purely distributed-memory multiprocessor. Similar to our approach, their platform is programmed using a process network MoC. However, in their approach the actual task migration can take place only at fixed points, which correspond to the communication primitive calls. The described approach, instead, enables migration at any point in the execution of the main body of processes. This leads to a faster response time to migration decisions, which is preferable for instance in case of faults.

Other task migration approaches are explained and quantitatively evaluated in [7] and [3]. Dynamic task re-mapping is achieved at user-level or middleware/OS level respectively. In both these approaches, the user needs to define checkpoints in the code where the migration can take place. This can require some manual effort from the designer which is not needed in the proposed approach. Moreover, a relevant difference from the presented approach is the inter-task communication realization, which exploits a shared memory system. We argue that our approach, which uses purely distributed memory, can perform better in emerging MPSoC platforms since it provides better scalability.

The model of computation that we have adopted (Polyhedral Process Networks [45]) not only eases significantly the implementation of system adaptivity mechanism, but it also has several other advantages and applications which can be found in the literature. In particular, the proposed approach exploits the pn compiler [46] to automatically convert static affine

nested loop programs (SANLPs) to parallel PPN specifications and to determine the buffer sizes that guarantee deadlock-free execution. Thus, usage of the PPN model of computation allows us to program an MPSoC in a systematic and automated way. Although the pn compiler imposes some restrictions on the specification of the input application, we note that a large set of streaming applications can be effectively specified as SANLPs. In addition to the case studies considered in this thesis, more application examples regard image/video processing (JPEG2000, H.264), sound processing (FM radio, MP3), and scientific computation (QR decomposition, stencil, finite-difference time-domain). Moreover, a recent work [41] has shown that most of the streaming applications can be specified using the Synchronous Data Flow (SDF) model [25]. The PPN model is more expressive than SDF, thus it can as well be used effectively to model most streaming applications.

In general Kahn Process Networks (KPNs), of which PPNs represent a special class, are a widely studied distributed model of computation. They are used for describing systems where streams of data are transformed by processes executing in sequence or parallel. Previous research on the use of KPNs in multiprocessor embedded devices has been mainly focusing on the design of frameworks which employ them as a model for application specification [33, 32, 23], and which aim at supporting and optimizing the mapping of KPN processes on the nodes of a reference platform [6, 18]. In [33, 32], different methods and tools are proposed for automatically generating KPN application models from programs written in C/C++. Design space exploration tools and performance analysis are then usually employed for optimizing the mapping of the generated KPN processes on a reference platform. A design phase usually follows in which software synthesis for multi-processor systems [23, 18], or architecture synthesis for FPGA platforms [33] is implemented. A survey of design flows based on the KPN MoC can be found in [17].

The approaches described above, which map applications described as KPNs to customized platforms, have a strong coupling between the application and the platform. Running a different application on the generated platform would not be possible or, even if possible, would give bad performace results. We adopt a different approach where we start by the assumption that we have a platform equipped with (possibly heterogeneous) cores well interconnected with a NoC. We provide a PPN API for this platform that the PPN application processes will comply to. Most importantly, the application code remains the same in all possible mappings of the processes. This is achieved by a proposed intermediate layer, called *middleware*, that includes the mapping related information and implements the PPN communication API.

This approach, where software synthesis relies on the high level APIs provided by the reference platform for facilitating the programming of a multiprocessor system, can be seen elsewhere. The trend from single core design to many core design has forced to consider inter-processor communication issues for passing the data between the cores. One of the emerged message passing communication API is Multicore Association's Communication API (MCAPI) [2] that targets the inter-core communication in a multicore chip. MCAPI is the light-weight (low communication latencies and memory footprint) implementation of message passing interface APIs such as Open MPI [1]. However these MPI standards are not quite fit for the KPN semantics [13] and building the semantics on top of their primitives brings an overhead compared to platforms with dedicated FIFO support.

The communication and synchronization problem when implementing KPNs over multiprocessor platforms without hardware support for FIFO buffers has been considered in [30] and [18]. In [30] the *receiver-initiated* method has been proposed and evaluated for the Cell BE platform. On the same hardware platform, [18] proposes a different protocol, which makes use of mailboxes and *windowed FIFOs*. The difference with the approach presented in this thesis is that we actually compare a number of approaches to implement the process network semantics, and that we deal with a different kind of platform, with no remote memory access support. Moreover, in both [30] and [18] system adaptivity is not taken into account.

In [31] the problem of implementing the KPN semantics on a NoC is addressed. However, in their approach the NoC topology is customized to the needs of the application at design time and network end-to-end flow control is used to implement the blocking write feature. In this work system adaptivity is considered since the middleware enables run-time management and the platform is generic, i.e. it allows the execution of any application specified as a PPN.

An approach to guarantee blocking write behavior is also used in [4]. That work proposes the use of dedicated operating system communication primitives, which guarantee that the remote FIFO buffer is not full before sending messages through a simple request/acknowledge protocol. The communication approaches described in this thesis assume a more proactive behavior of the consumer processes to guarantee the blocking on write compared to the request/acknowledge protocol. We argue that the presented approach can lead to better performance since it requires less synchronization points.

#### 2.2 Fault-tolerance in NoC-based MPSoCs

As the possibility of experiencing run-time faults becomes increasingly relevant with deep-sub-micron technology nodes, our research activity has been focused on the problem of graceful degradation by dynamic remapping in presence of run-time faults. Within the proposed NoC platform (that will be described in 4, fault-tolerance support has been introduced at both software and hardware levels. The idea is to improve dependability of the system by exploiting the migration method in case of run-time faults in the processing cores. The tasks mapped on faulty cores have to be migrated to fault-free ones at run-time, so that the application can continue its execution without disruption. To this aim, several extensions to the migration mechanism are needed. Firstly, fault detection must be enabled so that the migration can be triggered. Secondly, given that a faulty processor cannot participate in the remapping process, dedicated hardware is needed to ensure the migration functionality to survive in case of malfunctioning. Finally, a remapping decision must be taken in such a way to incur the smallest performance degradation. The details of the proposed solutions are described in Chapter 6.

#### 2.2.1 Open issues and related works

As already said in Section 2.1.1, in [4], a framework that achieves the goals of scalability and system adaptivity is described. Similar to our approach, their platform is programmed using a process network model of computation. However, our approach is fundamentally different because it enables the migration to happen at any time within the main body of the processes. This is a basic requirement in order to allow fault-tolerance, because faults can happen at any time. By contrast, in [4] the process migration is enabled only at fixed points during the execution of processes.

Dynamic task remapping is also performed in [7], [3] by means of a task migration mechanism implemented at user-level or middleware/OS level respectively. Both these approaches require the user to specify checkpoints in the code at which migration can take place. In the presented approach this is not needed because the state that has to be migrated is automatically determined, thanks to the properties of the adopted model of computation (Polyhedral Process Networks [46]).

Task remapping for reliability purposes has been investigated in [24] with the goal of throughput minimization on multi-core embedded systems. The fundamental difference from the presented approach is the use of design-time analysis for all possible scenarios and the storage of all remapping information in the memory. We argue that this technique incurs a large memory requirement to store all fault scenarios.

In [10], a system-level fault-tolerance technique for application mapping, which aims at optimizing the entire system performance and communication energy consumption, is proposed. In particular, the authors address the problem of spare core placement and its impact on system fault-tolerance properties, and propose a run-time fault-aware technique for allocating the application tasks to the available, reachable, and fault-free cores of embedded NoC platforms. In [10], application components running on a faulty core are migrated altogether to available non-employed spare cores, whereas, in our approach, tasks on the faulty core can possibly be remapped to different fault-free cores.

## **Chapter 3**

## The MADNESS Project

This chapter features a detailed description of the MADNESS project (Methods for predictAble Design of heterogeneous Embedded Systems with adaptivity and reliability Support), funded by the European Commission. The whole research activity performed over the topics of this thesis, has been driven according to the needs posed by the MADNESS project goals.

The project aims at the definition of innovative system-level design methodologies for embedded MPSoCs, extending the classic concept of design space exploration in multi-application domains to cope with high heterogeneity, technology scaling and system reliability.

The main goal of the project is to provide a framework able to guide designers and researchers to the optimal composition of embedded MPSoC architectures, according to the requirements and the features of a given target application field. The proposed strategies will tackle the new challenges, related to both architecture and design methodologies, arising with the technology scaling, the system reliability and the ever-growing computational needs of modern applications.

The methodologies developed within MADNESS project act at different levels of the design flow, enhancing the state-of-the art with novel features in system-level synthesis, architectural evaluation and prototyping.

#### 3.1 Framework outline

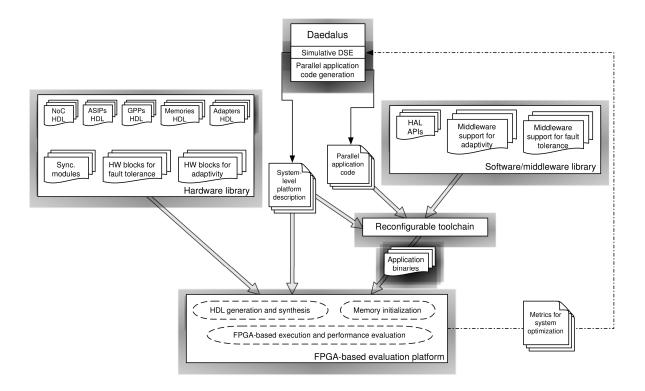

In figure 3.1, a block diagram of the MADNESS system-level design framework is presented. The framework aims at efficiently and effectively performing design space exploration (DSE) to search for the optimal composition of a multimedia NoC-based MPSoC architecture, operating on a library of heterogeneous industrial-strength IP cores and exposing a large number of degrees of freedom.

The MADNESS target platform consists of a library of IP blocks, mentioned in figure 3.1 as *Hardware Library*, which are explored in continuously varying configurations. The project employs a variety of IP building blocks, among which are application-specific instruction-set processors (ASIPs), memories, interconnects, and adapters. This hardware IP library includes industrial-strength blocks from Silicon Hive and Lantiq. Some further blocks, such as a video motion processor, are specifically developed for the MADNESS project. Each ar-

Figure 3.1: The MADNESS system-level design framework for adaptive and fault-tolerant MPSoCs.

chitecture configuration is an abstract collection of target IPs and interconnect structures. The decisions during the optimization process are actually taken by a DSE engine, represented by the box at the top of figure 3.1 and described in detail in section 3.2. The DSE engine iteratively selects one among multiple sets of architecture instances and application mappings, exploiting a specific layer for rapid and accurate architectural evaluation. The DSE engine is based on enhanced versions of several key elements from the Daedalus system-level synthesis design flow [42]. More specifically, it deploys the Sesame simulation environment [37] for simulative DSE and uses the PNgen/ESPAM tools for parallel application code generation [33]. As a consequence, the MADNESS framework, like Daedalus, uses Kahn Process Networks (KPNs) [22] to model parallel multimedia applications. As described later in deeper detail, the Sesame simulation environment has been extended in the scope of the MADNESS project to support DSE for MPSoCs sustaining multi-application dynamic workloads as well as to include with novel techniques for design space pruning including fault-tolerance aspects. As a further point of novelty, the project continuously develops an evaluation layer which integrates a system-level synthesis flow to rapidly evaluate selected design points using an FPGA-based emulation and evaluation platform, described in further detail in Chapter 4. The framework allows to perform system optimization by means of adequately interleaving a high-level simulative design space exploration process with the evaluation of selected design points synthesized on real FPGA-based prototypes. Thus, the DSE engine can access an FPGA-based environment for on-hardware prototyping, when needed during the optimization process, in order to obtain a detailed evaluation of a candidate ar3.2. HIGH-LEVEL DSE

chitecture by actually executing the target application on the implemented prototype. In order to improve design predictability, the flow is improved by annotating the emulation results on adequate analytic "technology-aware" models (energy consumption, execution time per frequency, area obstruction). This allows to translate emulation results to a reliable evaluation of a prospective ASIC implementation of the system on a given technology, before actually performing all the back-end fabrication steps. In order to allow the execution of the target application on the FPGA implementation of completely different design points, featuring different kinds of processing elements and interconnects, the framework includes a re-configurable compilation toolchain, depicted in figure 3.1, which is capable of re-targeting itself according to the design point specification. Furthermore, a hardware abstraction layer (HAL) exposes to the programmer a convenient set of APIs that can be used to program the system without referring to specific low-level details of the platform. The compilation toolchain automatically links the appropriate implementation of the API included in the HAL, according to the description of the design point under evaluation. The compilation toolchain and the HAL are described in further detail in section 3.4. Support for system adaptivity and fault-tolerance, and their implementation aspects, which are main topics of this thesis, will be described in Chapters 5 and 6. The implementation of the platform is biased toward low redundancy and power consumption in order to meed the demands of the embedded systems domain. Characteristics of the dynamic behavior and of the resilience to faults can be taken into account by the system-level synthesis during the architectural optimization process, exploiting the mentioned extensions to Sesame.

To allow the mentioned tools and methods to inter-operate without or with minimal manual intervention, the IP-XACT standard [21] was selected for exchanging abstract platform instance descriptions between different tools. However, with regard to this purpose, IP-XACT has shown a number of shortcomings. As a result, several adaptations were made to the IP-XACT standard, allowing us to capture the variability of the target architectures and to capture the power and area consequences of DSE design choices. Finally, in order to actually construct the heterogeneous platform instances needed for FPGA-based evaluation, the MADNESS project has resulted in novel approaches to automatically convert MADNESS IP-XACT descriptions into RTL implementations of multi-ASIP platform instances.

## 3.2 High-level DSE

The MADNESS framework deploys the Sesame MPSoC simulation framework [37] for simulative DSE. Sesame recognizes separate application and architecture models within a system simulation. An application model, specified as a KPN, describes the functional behavior of a (set of) concurrent application(s). An architecture model defines architecture resources and captures their performance constraints and power consumption characteristics. Subsequently, using a mapping model, an application model is explicitly mapped onto an architecture model (i.e., the mapping specifies which application tasks and communications are performed by which architectural resources in an MPSoC), after which the application and architecture models are co-simulated to study the performance and power consumption consequences of the chosen mapping.

To actually search the design space for optimum design points, Sesame utilizes heuristic search techniques, such as multi-objective Genetic Algorithms (GAs). Such GAs prune the design space by only performing a finite number of design-point evaluations during the

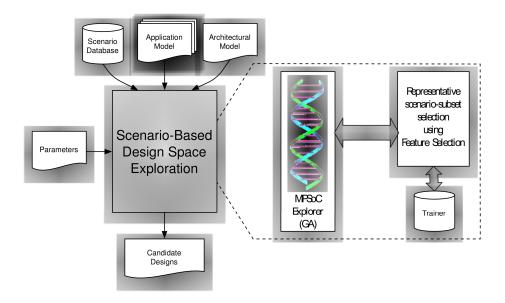

Figure 3.2: Scenario-based DSE.

search, evaluating a population of design points (solutions) over several iterations, called generations. With the help of genetic operators, a GA progresses iteratively towards the best possible solutions.

The Sesame's DSE was focused on the analysis of MPSoC architectures under a single, static application workload. The current trend, however, is that application workloads executing on embedded systems become more and more dynamic. Not only is the behavior of a single application changing over time, but the effect of the interactions between different applications are also hard to predict. This dynamic behavior can be classified and captured using so-called workload scenarios [15]. Workload scenarios make a distinction between two aspects. First, intra-application scenarios describe the dynamic behavior within applications. For example, a QoS mechanism within a decoder application may dynamically lower the bit-rate to save power while still meeting its deadlines. Second, inter-application scenarios describe the interaction between different applications that are concurrently executing on an embedded system and contending for its system resources.

In the context of MADNESS, a novel scenario-based DSE method that allows for capturing the dynamic behavior of multi-application workloads in the process of system-level DSE [43] has been developed. An important problem that needs to be solved by such scenario-based DSE is the rapid evaluation of MPSoC design instances during the search through the MPSoC design space. Because the number of different workload scenarios can be immense, it is infeasible to rapidly evaluate an MPSoC design instance during DSE by exhaustively analyzing (e.g., via simulation) all possible workload scenarios for that particular design point. As a solution, a representative subset of workload scenarios can be used to make the evaluation of MPSoC design instances as fast as possible. The difficulty is that the representative-

ness of a subset of workload scenarios is dependent on the target MPSoC architecture. But since the evaluated MPSoC architectures are not fixed during the process of DSE, we need to simultaneously co-explore the MPSoC design space and the workload scenario space to find representative subsets of workload scenarios for those MPSoC design instances that need to be evaluated. To this end, within MADNESS project a scenario-based DSE method combining a multi-objective GA and a feature selection algorithm have been developed. The GA is used to search the MPSoC design space, while the feature selection algorithm dynamically selects a representative subset of scenarios. This representative subset of scenarios is then used to predict the quality of MPSoC design instances in the GA as accurately as possible.

This scenario-based DSE is depicted in Figure 3.2. As input, the scenario-based DSE uses the application models that need to be mapped onto the MPSoC, an MPSoC platform model, a scenario database in which all possible application scenarios are stored, and search parameters. As output, the DSE produces candidate MPSoC design instances that perform well when considering all the potential situations that can occur in the specified dynamic multi-application workload. The system-level description of the candidate design points is then translated by a utility, and can be elaborated by the FPGA-based prototyping platform, as described in [27].

#### 3.3 FPGA-based evaluation environment

The design flow envisioned in MADNESS raises the need for a fast and accurate evaluation environment. Such a tool has to provide the upper layers of the design flow (i.e., the simulative DSE) with feedback about the performance of any requested candidate architectural configuration. To this aim, within the project, a flexible and fast FPGA-based emulation framework extending the work presented in [28] has been developed. It leverages a library of components, instantiates the desired system configuration, specified through a systemlevel specification file, and generates the hardware description files for the FPGA synthesis and implementation, automating design steps that are usually very error-prone and efforthungry. The mentioned feedback, namely consisting of detailed and precise event/cyclebased metrics, is obtained from the execution of the target software application (compiled and linked with the proper toolchains and communication libraries) on the candidate system configuration, implemented on FPGA and adequately instrumented with counters and hardware probes. Moreover, the prototyping environment provides support for "technology awareness" within the DSE process, by coupling the use of analytic models and FPGA-based fast emulation. This allows to obtain early power and execution time figures related to a prospective ASIC implementation, without the need to perform long post-synthesis software simulations. The FPGA emulation results are back-annotated using analytic models for the estimation of the physical figures of interest. Timing results (cycle counts) are evaluated according to the modeled target ASIC operating frequencies and the evaluated switching activity is translated into detailed power numbers. Thus, the assumptions made at the systemlevel design phase can be verified before the actual back-end implementation of the system, increasing the overall convergence of the design flow. The models included in the evaluation platform are built by interpolation of layout-level experimental results obtained after the ASIC implementation of the reference library IPs, along the lines already defined for NoC building blocks in [26]. In the latter, the accuracy of the models is assessed to be higher than 90% when complete topologies are considered, with respect to post-layout analysis of real ASIC implementations. A detailed description of the evaluation platform will be provided in Chapter 4.

# 3.4 Compilation toolchain and hardware abstraction layer

This section describes the interaction between the DSE, the compilation toolchain and the evaluation platform. Further, a brief overview of the extensions to the available compilers is given. Finally the key features of the hardware abstraction layer and their integration in the compilation toolchain are described.

#### 3.4.1 Compilation toolchain

The DSE tool passes the sources for each process and additional information like mapping and system description to the compilation toolchain (see Figure 3.1). The compilation toolchain takes care of the correct mapping between processes and their corresponding compilers for each processor in an automatic way. In order to determine the right compiler, the user needs to pass an environment description to the compilation toolchain. This description defines which compilers are available and which options to use for each processor in the system.

To meet the requirements of the framework, a hardware abstraction layer (HAL) is integrated in the compilation toolchain in a retargetable manner.

#### 3.4.2 Hardware abstraction layer

The MADNESS framework aims at generating an optimal MPSoC for given hardware components and for a given application. Therefore, the application developer does not know the platform during the development process. Special processor-dependent instructions cannot be exploited during system generation. Even the realization of simple low-level functions like communication or synchronization without knowledge of the underlying processors and hardware components is impossible. For this reason, the MADNESS framework provides a Hardware Abstraction Layer (HAL) which enables the developer to create portable and processor-dependent optimized applications. The developed HAL consists of two parts, a fixed part which covers the standard abilities of processors and a generic processor-dependent part.

#### Standard abilities

Standard abilities include memory access, communication or synchronization mechanisms. One assumes that present and future processors support these mechanisms. As a consequence MADNESS defines a fixed set of standard functions which have to be implemented for each available processor used in the proposed framework.

#### Special abilities

The actual advantage of heterogeneous multi-processor-systems is the composition of different specialized processors. To achieve the best performance one has to take into account that the HAL has also to cover the processor-dependent features. These features are called special ability functions. This part of the HAL is generic and extensible by the user without modifications of the used compilers. For each specialized implementation, a standard ANSI-C implementation must be provided. Thus, the availability of a semantically equivalent application, if the corresponding processor feature is not available, is ensured.

## 3.5 Support for Adaptivity

The term system adaptivity refers to the ability of a system to dynamically assign tasks of the application(s) running on it to the resources available over time. This is an emerging topic in MPSoC design due to recent evolutions in embedded systems [34]. The KPN model of computation (MoC), adopted in the MADNESS framework to model multimedia applications for mapping them onto the MPSoC, presents remarkably simple operational semantics and distributed control, which allow for a natural realization of system adaptivity mechanisms.

From an architectural point of view, the framework is focused on tile-based NoC [12] systems. Among other advantages, this choice is driven by the goal of system adaptivity. NoC-based interconnects' flexibility allows to overcome the drawbacks exposed by point-to-point connections classically used in multimedia. Point-to-point connections are typically more efficient in terms of communication latency, but they are intrinsically less efficient in supporting communication patterns varying at runtime, unless full connectivity among all the processors in the system is provided at design time, at the price of making wiring and buffering of the whole communication structure rather complex. Moreover, NoC communication infrastructures are physically and functionally more scalable than bus-based shared memory systems [5].

The starting assumption is that the target platform is equipped with a heterogeneous set of cores interconnected with a NoC. The application code must remain the same in every possible mapping of the tasks to allow for system adaptivity. This fact implies that the used communication primitives must be neither platform dependent nor mapping dependent. An intermediate layer, or *middleware*, has been implemented to refine such communication primitives, including mapping related information, and to respect the KPN semantics on the NoC-based MPSoC platform.

The middleware layer and the proposed adaptivity strategies will be thoroughly discussed in Chapter 5.

### 3.6 Support for Fault-tolerance

Applications of embedded systems increasingly require high availability of the systems themselves, possibly accepting a measure of graceful degradation. Moreover, increasing complexity of the systems is reaching such levels that the probability that some manufacturing defect will escape end-of-production testing or that faults will become evident during normal operation has to be taken into account. Standard approaches based on massive redundancy are not directly applicable to embedded platforms, constrained by the need for solutions having low cost and low power consumption. New approaches are therefore needed.

The MADNESS project focuses on the development of fault tolerant solutions which are not dependent on a technology-related low-level fault model, but rather on technologyabstracting functional-level error models. This approach allows the development of a functionally identical system for two different implementation technologies - FPGA and ASIC - such that the system's evaluation on one technology can be immediately adoptable and credible for the other technology.

The fault tolerant approaches focus on the detection of run-time faults and on the use of reconfiguration strategies implemented at different levels. In the MADNESS framework, three main types of components are taken into account, i.e., *processing cores, storage elements*, and the *network-on-chip* (NoC). While for storage components standard fault tolerant strategies based on error detecting and correcting codes are adopted, for the NoC and the processing elements ad-hoc strategies for fault detection and reconfiguration have been developed, and will be presented in Chapter 6.

## **Chapter 4**

## The MADNESS evaluation platform

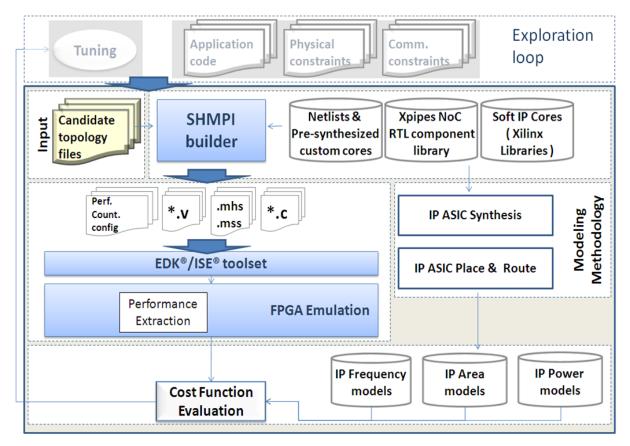

#### 4.1 Platform overview

As described in Chapter 3, within the MADNESS project, an integrated framework for the application-driven design of MPSoCs was studied and implemented, aimed at supporting the designer during such a complex process. Figure 4.1 gives a block decomposition the MADNESS tool support for prototyping activity, which is based on the SHMPI system-level FPGA-based prototyping environment, presented in [39]. A system-level platform description is input to the framework. The description includes processing, interconnection and memory modules instantiation and configuration, and address space partitioning.

A high-level topology compiler is in charge of parsing the topology description file and generating the RTL files that describe the hardware top view of the complete platform. This stage is also intended to generate the hw/sw platform description files to be passed to the Xilinx platform instantiation toolset. This phase of the flow will be specifically addressed and further explained in Section 4.4. The composition and configuration of the selected platform builds upon a repository of soft IP cores. The content of this library will be described in detail in Section 4.3. The use of these repositories does not prevent the inclusion of further modules into the system, since custom cores can always be added as RTL or pre-synthesized netlists with little effort. This is a crucial feature of the RTL libraries, since extensibility is key to the applicability range of the framework. That is also the reason why all the modules included in the library are fully compliant to a common interfacing standard, which is a subset of the well-known OCP-IP communication standard [35], as we will discuss in the following sections.

Regarding the software part of the system, the Xilinx development environment includes the standard compilation and debugging tool-chains for the soft processors that can be instantiated, while the drivers of the peripherals are automatically generated already at the platform compilation stage, according to the parameters provided by the user. The RTL files of the components can potentially be passed, with minor modifications, to an ASIC synthesis flow, in order to obtain power and area figures of the designed platform and to refine the area and power models of the building blocks instantiated within the system. So far, this capability is provided only for the interconnection modules. The framework operating flow proceeds with the FPGA synthesis and implementation through the adoption of the Xilinx proprietary tools (within the Xilinx ISE©environment). The execution of the targeted appli-

Figure 4.1: Overview of the evaluation platform

cation on the configured FPGA can be easily profiled with deep accuracy. Moreover, the emulation of the complete platform enables the rapid collection of cycle-accurate information on the switching activity, that can be used, in cooperation with the available power models, to obtain detailed figures related to a prospective ASIC implementation of the system.

## 4.2 System-level platform description input file

The designer is able to input a platform description by passing as input to the framework a text file that describes the main system-level building blocks of the design under emulation. The granularity of the input file is at the single processing, interconnection, I/O and memorization module level. Regarding the interconnection subsystem architecture, the designer can describe, in case a source routing NoC-based is selected (which is the case of the ×pipes interconnection library), the number of switches, the n-arity of each switch, the number of buffering input/output stages, the routing tables and normally has to tag the different links connecting the switches. Regarding the memorization layer, the type of memory has to be selected. Currently the system is able to instantiate on-FPGA Xilinx proprietary hard BRAM modules, configuring them to emulate single- and double-port memory cores. The address space and the related processor into which the memory module is connected have to be specified. If the memory is shared among the different processing element, the module has to be declared to be such. Regarding the different I/O and synchronization controller and modules, the address spaces have to be declared as well.

The following code contains snippets taken from an actual input system description file:

```

// -----

// define the topology here

// name, mesh/torus specifier (mesh/torus/other)

// -----

topology(topology_2x2, other);

// -----

// define the cores here

// core name and number, switch number, NI clock divider, NI buffers,

// initiator/target type, type of core (if a specific one is requested),

// memory mapping (only if target), fixed specifier

// (only if target and of shared type)

// -----

core(core_0, switch_0, 1, 6, userdefined, initiator);

core(core_1, switch_1, 1, 6, userdefined, initiator);

core(core_2, switch_2, 1, 6, userdefined, initiator);

core(core_3, switch_3, 1, 6, userdefined, initiator);

switch_0, 1, 6, double, target:0x10,high:0x1000ffff);

core(pm_4,

core(pm_5,

switch_1, 1, 6, double, target:0x12,high:0x1200ffff);

core(pm_6, switch_2, 1, 6, ocpmemory, target:0x14,high:0x1400ffff);

switch_3, 1, 6, ocpmemory, target:0x16,high:0x1600ffff);

core(pm_7,

core(ts_8,

switch_3, 1, 6, Testandset,target:0xff,high:0xffffffff);

core(ul_9, switch_0, 1, 6, Uartlite, target: 0x46, high: 0x4600ffff);

core(shm_10, switch_1, 1, 6, shared, target:0x06, high:0x0600ffff);

// -----

// define the switches here

// switch number, switch inputs, switch outputs, number of buffers,

// core ID to which the switch performance counter is attached,

// port ID to which the switch performance counter is attached.

// -----

switch(switch_0, 5, 5, 6, 0, 0);

switch(switch_1, 5, 5, 6, 1, 0);

switch(switch_2, 5, 5, 6, 2, 0);

switch(switch_3, 5, 5, 6, 3, 0);

// -----

// define the links here

// link number, source, destination

// -----

link(link0, switch_0, switch_1);

link(link1, switch_1, switch_0);

```

```

link(link6, switch_1, switch_3);

link(link7, switch_3, switch_1);

// -----

// define the routes here

// source core, destination core, the order in which switches need to be

// traversed from the source core to the destination core

// -----

route(core_0, pm_4, switches:0);

route(core_0, ts_8, switches:0,1,3);

route(core_0, ul_9, switches:0);

route(core_0, shm_10, switches:0,1);

route(core_3, pm_7, switches:3);

route(core_3, ts_8, switches:3);

route(core_3, ul_9, switches:3,2,0);

route(core_3, shm_10, switches:3,1);

route(pm_4, core_0, switches:0);

route(pm_4, pm_5, switches:0,1);

route(pm_4, pm_6, switches:0,2);

route(pm_4, pm_7, switches:0,1,3);

route(pm_7, core_3, switches:3);

route(pm_7, pm_4, switches:3,2,0);

route(pm_7, pm_5, switches:3,1);

route(pm_7, pm_6, switches:3,2);

route(ts_8, core_0, switches:3,2,0);

route(ts_8, core_1, switches:3,1);

```

```

route(ts_8, core_2, switches:3,2);

route(ts_8, core_3, switches:3);

```

The code snippet contains the description of a sample topology named topology\_2x2, which contains 4 processing elements, 2 double-port local memories, 2 single-port local memories, a test&set synchronization module, an UART controller for interfacing with a serial port and a shared memory, all declared with the same core() primitive and different parameters. The parameters allow for specifying different clock domains (unused in this case), the number of buffering stages in the network interface (6 in this case), the core identifier and the basic memory mapping of each device. Local memories with multiple ports have different mappings for each port with respect to the local processor and the other processors, if direct messaging is enabled.

The NoC switches are defined using the switch() primitive, whose parameters allow the designer to specify a name for the switch, the number of inputs and outputs of that switch, which define the arity of the switch itself, the number of buffering stages (output buffering is used in this interconnection library module) and two other IDs. These two other IDs respectively identify the core and the port which the switch performance counters are actually attached to. The actual performance counter logic will be described in detail in Section 4.5. The link() primitive enable link identification. Its parameters simply point to the interconnected switch modules. Links have to be declared as if they were half-duplex, meaning that between two switches connected through a full-duplex link there must be two separate links. In addition to that, if source routing is used, the route() primitive enables specifying the routing path between every core pair inside the network, and its parameters specify the list of switch traversed by the packets from source to destination. Direct communication between two computing cores is not allowed. If direct messaging is intended to happen at higher level, the underlying mechanism implies a communication from the source processing element to the remote memory that is attached to the destination processing element.

## 4.3 The soft IP cores RTL repository

This section will describe the components currently available in the soft IP cores repository. All the modules included in the libraries are highly parametric. This is a key feature with respect to the prospective adoption of the framework for design exploration purposes. Different computing and memorization elements have been added to the libraries and they will not be described within this thesis. The building blocks have been made compliant, where not already done, to a subset of the well known OCP open communication standard [35]. We will first provide a brief introduction to the main features of the standard.

## 4.3.1 Elements of the Open Core communication Protocol (OCP)

The Open Core Protocol (OCP) defines a bus-independent protocol between IP cores that reduces design time, design risk, and manufacturing costs for SOC designs. An IP core can be a simple peripheral core, a high-performance microprocessor, or an on-chip communication subsystem such as a wrapped on-chip bus. The OCP defines a single-clock synchronous interface point-to-point interface between two communicating entities such as IP cores and

bus interface modules (bus wrappers). One entity acts as the master of the OCP instance, and the other as the slave. Only the master can present commands and is the controlling entity. The slave responds to commands presented to it, either by accepting data from the master, or presenting data to the master. For two entities to communicate in a peer-to-peer fashion, there need to be two instances of the OCP connecting them - one where the first entity is a master, and one where the first entity is a slave. The characteristics of the IP core determine whether the core needs master, slave, or both sides of the OCP.

A transfer across this protocol occurs as follows. A system initiator (as the OCP master) presents command, control, and possibly data to its connected slave (a wrapper interface module that abstracts the underlying hardware details). The interface module plays the request across the on-chip physical interconnection system, which can be a bus, a crossbar, a NoC or whatever. The OCP does not specify the underlying hardware functionality. Instead, the interface designer converts the OCP request into a transfer for the underlying hardware. The receiving wrapper interface module (as the OCP master) converts the underlying hardware transfer operation into a legal OCP command. The system target (OCP slave) receives the command and takes the requested action.

The OCP standard defines a huge number of signals, which are grouped in different categories, according to the functionality that the different interconnected modules provide. We chose to implement only compliance with a small subset of the OCP signals, whose list is reported in Table 4.1 together with a brief signal functionality description.

| Name        | Width        | Driver | Function                 |  |

|-------------|--------------|--------|--------------------------|--|

| Clk         | 1            | varies | OCP clock                |  |

| MAddr       | configurable | master | Transfer address         |  |

| MCmd        | 3            | master | Transfer command         |  |

| MData       | configurable | master | Write data               |  |

| MDataValid  | 1            | master | Write data valid         |  |

| MRespAccept | 1            | master | Master accepts response  |  |

| MByteEnable | 4            | master | One-hot byte enable      |  |

| SCmdAccept  | 1            | slave  | Slave accepts transfer   |  |

| SData       | configurable | slave  | Read data                |  |

| SDataAccept | 1            | slave  | Slave accepts write data |  |

| SResp       | 2            | slave  | Transfer response        |  |

Table 4.1: Implemented OCP signals

Where needed, OCP-compliant wrappers modules have been developed to adapt the original module interface to the one specified by the protocol.

## 4.3.2 Processing elements, memories and I/O

The computing element library has been mainly focused around the FPGA-oriented Xilinx proprietary soft cores, that is to say the Microblaze©[47] and PowerPC©[48] cores. Within MADNESS project, a set of other processing elements have been added to the repository, namely a set of multi-media oriented Application Specific Integrated Processors (ASIP) provided by Intel Corporation, and a processor specifically designed for the packet processing domain provided by Lantiq Deutschland GmbH.

As for what regards the memorization and I/O elements, standard Xilinx soft cores are currently being used. The memory modules can be automatically configured as single- or double-port BRAM-based modules. The separation between such cases is operated according to the system-level description provided by the designer. In case direct processor-to-processor message-passing is enabled, double-port memories will be selected, together with the necessary logic to handle DMAs at the network interface level.

Regarding the I/O, standard controller modules are available, such as UART, Ethernet and DVI/TFT controllers.

#### 4.3.3 Interconnection elements

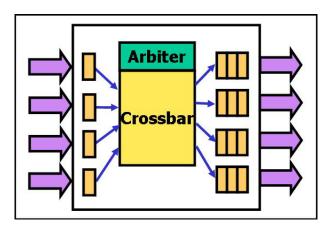

The ×pipes NoC component library ([11]) is a highly flexible library of component blocks that has been chosen as baseline reference for the development activity. The library is suitable for the creation of arbitrary topologies, thanks to the capability of its modules of being almost completely configured at design time. ×pipes, natively, includes three main components: switches, network interfaces (NIs) and links. Figure 4.2 plots the basic architecture of the ×pipes switch. It is a very simple switch configuration, where output buffer is employed through multi-stage variable-latency FIFOs. A round-robin priority arbiter with selectable inputs is employed to allocate the all-to-all crossbar output ports. The minimum traversal latency per switch is 2 clock ticks per flit.

Figure 4.2: ×pipes switch architecture

The backbone of the NoC is composed of switches, whose main function is to route packets from sources to destinations. Arbitrary switch connectivity is possible, allowing for implementation of any topology. Switches provide buffering resources to lower congestion and improve performance. In ×pipes, both output and input buffering can be chosen, i.e. FIFOs may be present at each input and output port. Switches also handle flow control issues, and resolve conflicts among packets when they overlap in requesting access to the same physical links. A NI is needed to connect each IP core to the NoC. NIs convert transaction requests/responses into packets and vice versa. Packets are then split into a sequence of flits before transmission, to decrease the physical wire parallelism requirements. In ×pipes, two separate NIs are defined, an initiator and a target one, respectively associated to OCP system masters and OCP system slaves. A master/slave device will require an NI of each type to be attached to it. The interface among IP cores and NIs is point-to-point as defined by the OCP

subset described in Table 4.1, guaranteeing maximum reusability and compliance with the interface standards.

NI Look-Up Tables (LUTs) are used to specify the path that packets will follow in the network to reach their destination (source routing). Two different clock signals can potentially be attached to the NIs: one to drive the NI front-end (OCP interface), the other to drive the NI back-end (×pipes interface). The ×pipes clock frequency must be an integer multiple of the OCP one. This arrangement allows the NoC to run at a fast clock even though some or all of the attached IP cores are slower, which is crucial to keep transaction latency low. Since each IP core can run at a different frequency of the ×pipes frequency, mixed-clock platforms are possible. Inter-block links are a critical component of NoCs, given the technology trends for global wires. The problem of signal propagation delay is, or will soon become, critical. For this reason, ×pipes supports link pipelining, i.e. the interleaving of logical buffers along links. Proper flow control protocols are implemented in link transmitters and receivers (NIs and switches) to make the link latency transparent to the surrounding logic. Therefore, the overall platform can run at a fast clock frequency, without the longest wires being a global speed limiter. Only the links which are too long for single-cycle propagation will need to pay a repeater latency penalty.

Within the development of the evaluation framework, the original ×pipes library has been extended explicitly for adaptation and integration in MADNESS project, and to provide advanced communication capabilities required for fast prototyping. Here follows a list of the main features that have been added to the library:

- Capability of initializing and handling DMAs (meaning direct memory to memory transfers). The need for this feature has appeared in order to support, at low level, all those models of computations that rely on direct processor-to-processor message passing. In order to implement this added capability, additional logic has been inserted in the processor and memory network interfaces. The way this logic works is basically that the sending processor programs, through memory-mapped registers, a DMA transfer from its memory to a destination memory, by specifying the destination network address and the burst length. The transaction is then translated into an OCP burst transfer, that takes place from the source memory directly to the destination one. Upon receive, the destination network interface is able to store the incoming data on a temporary memory buffer or, if the receiving processor has already reached the receiving primitive call within the application, directly into the destination memory area. Further detail on the software implementation of the message-passing strategy will be provided in Section 4.3.7.

- Insertion of performance counters inside NoC modules has been enabled through addition of dedicated hardware monitors directly attached to the output buffers of the switch. The value of the counters are then written into dedicated memory-mapped registers through which they are accessible to the processing element.

All the mentioned additional features required some modifications of the processor-to-NI interface circuitry. Several dedicated adapters have been developed in this aim, allowing at the same time the seamless integration of the ×pipes library (natively compliant with OCP) with the rest of the environment. Some address decoding logic has been added inside the core in order to detect those load/store operations that are not intended to generate

Figure 4.3: A general overview of an example template instance

traffic over the network, such as accesses to memory mapped registers or to performance counters.

#### 4.3.4 Message Passing programming model

Reference primitives implementing message-passing communication are built, according to the general definition of such model, upon two base functions: <code>send()</code> and <code>receive()</code>. These two primitives are implemented in C, and interact with the hardware structures described in Section 4.3.5. According to the usual message-passing signatures, to send a message with a <code>send()</code>, the programmer has to specify the address (<code>SendAddress</code> hereafter) inside the private memory that contains the information to be sent (message data), a tag assigned to the message (<code>SendTag()</code>), the size of the transfer (<code>SendDim()</code>), and the ID of the destination processor (or process, in case of multi-context execution in the processing elements - <code>SendID()</code>). The <code>receive()</code> parameters are the tag of the expected message (<code>ReceiveTag()</code>), the sender ID (<code>ReceiveID()</code>) and the address where the received message data has to be stored (<code>ReceiveAddress()</code>). Two implementations of the <code>receive()</code> are provided, with blocking and non-blocking behaviour.

## 4.3.5 Message Passing hardware support