THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

## Advanced III-Nitride Technology for mm-Wave Applications

Anna Malmros

Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience - MC2 CHALMERS UNIVERSITY OF TECHNOLOGY

Gothenburg, Sweden, 2019

#### Advanced III-Nitride Technology for mm-Wave Applications

Anna Malmros

© Anna Malmros, 2019 ISBN 978-91-7905-127-3

Doktorsavhandlingar vid Chalmers Tekniska Högskola Ny serie nr 4594 ISSN 0346-718X

Technical Report MC2-414 ISSN 1652-0769 Microwave Electronics Laboratory

Department of Microtechnology and Nanoscience – MC2 Chalmers University of Technology SE-412 96 Göteborg Sweden Tel. +46 (0)31 772 1000

Printed by Chalmers Reproservice Gothenburg, Sweden, May 2019

## Abstract

Within wireless communication, there is a continuously growing need for more bandwidth due to an increasing number of users and data intense services. The development within sensor systems such as radars, is largely driven by the need for increased detection range and robustness. In such systems, power amplification and generation at high frequency are of importance. High-electron mobility transistors based on gallium nitride (GaN HEMTs) offer efficient generation of high output power at high frequency. This is enabled by the unique characteristics of GaN and its heterostructures, with a large breakdown field, related to the wide bandgap, and excellent electron transport properties. Due to this, it is today used in high-performing radar, telecommunications, as well as power electronic systems. Despite substantial progress over the last decade, the GaN HEMT is still the subject of intense research to reach its full potential.

Recent development within epitaxy has significantly improved the quality of III-nitride semiconductors, and enabled indium aluminum nitride (InAlN) and InAlGaN as alternatives to AlGaN in the conventional AlGaN/GaN heterostructure. The higher polarization charge in these materials allows for considerable downscaling of the barrier layer thickness with a sustained high sheet carrier density. This has opened new possibilities for optimization of the high frequency performance.

In this work, HEMTs with downscaled InAl(Ga)N barrier layers have been developed with the goal to optimize the devices for power amplification in the mm-wave range. Electron trapping and short-channel effects have been addressed in the design of the epi and in the optimization of the process modules. Different surface passivation layers and deposition methods have been evaluated to mitigate electron trapping at the surface. The output power density of a HEMT increased from 1.7 to 4.1 W/mm after passivation with a SiN<sub>x</sub> layer. The deposition method for Al<sub>2</sub>O<sub>3</sub> passivation layers showed to have a profound impact on the electron trapping. A layer deposited by plasma-assisted atomic layer deposition (ALD) exhibited superior passivation of the surface traps as compared to the layer deposited by thermal ALD, resulting in an output power at 3 GHz of 3.3, and 1.9 W/mm, respectively. The effect of the channel layer thickness (50 – 150 nm) in InAlGaN/AlN/GaN HEMTs with and AlGaN back barrier demonstrated a trade-off between short-channel effects and deep-level electron trapping in the back barrier. The maximum output power was 5.3 W/mm at 30 GHz, obtained for a GaN layer thickness of 100 nm.

To further enhance the high frequency performance, the ohmic contacts were optimized by the development of a Ta-based, Au free, metal scheme. Competitive contact resistance of  $< 0.2 \ \Omega$ mm was achieved on both AlGaN/GaN and InAlN heterostructures with a Ta/Al/Ta metal stack. The contacts are annealed at a low temperature (550 – 575 °C) compared to more conventional contact schemes, resulting in a smooth morphology and good edge acuity.

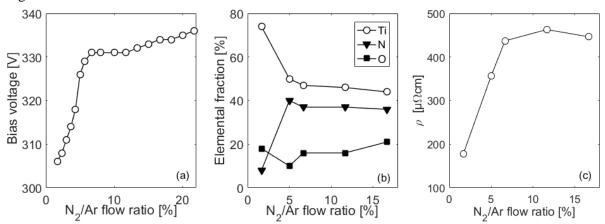

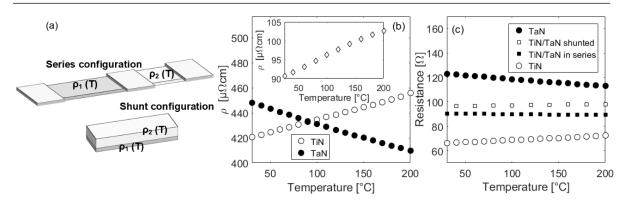

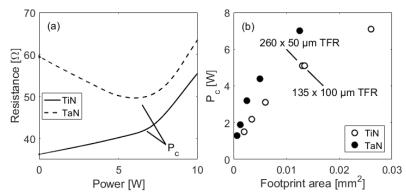

The implementation of microwave monolithic integrated circuits (MMICs) based on III-nitride HEMTs facilitate the use of III-nitride HEMTs in a system where frequency and compactness are key requirements. Thin film resistors (TFRs) are one of the passive components required in MMICs. In this work, a low-resistance titanium nitride (TiN) TFR was developed as a complement to the higher resistance tantalum nitride (TaN) TFR and mesa resistor in the in-house MMIC process. The developed TiN TFR exhibits a sheet resistance of 10  $\Omega/\Box$ , compared to 50 and 200-300  $\Omega/\Box$  of the TaN TFR and semiconductor resistor, respectively. The critical dissipated power in the TFR showed a correlation to the footprint area, indicating that Joule-heating was the main cause of failure. TiN- and TaN films exhibit different signs of the thermal coefficient of resistance. This feature was used to demonstrate a temperature compensated TFR (TCR = -60 ppm °C) with application in MMICs operating in a wide temperature range.

**KEYWORDS:** HEMT, GaN, InAlN, InAlGaN, ohmic contact, passivation, electron trapping, high frequency performance.

### List of appended publications

This thesis is based on the following papers:

- [A] A. Malmros, H. Blanck, and N. Rorsman, "Electrical properties, microstructure, and thermal stability of Ta-based ohmic contacts annealed at low temperature for GaN HEMTs," Semicond. Sci. Technol., vol. 26, no. 7, 2011, doi: 10.1088/0268-1242/26/7/075006.

- [B] J. Bergsten, A. Malmros, M. Tordjman, P. Gamarra, C. Lacam, M.-A. Di Forte-Poisson, and N. Rorsman, "Low resistive Au-free, Ta-based, recessed ohmic contacts to InAlN/AIN/GaN heterostructures," *Semicond. Sci. Technol.*, vol. 30, no. 10, p. 105034, 2015, doi: 10.1088/0268-1242/30/10/105034.

- [C] A. Malmros, P. Gamarra, M. Thorsell, M.-A. di Forte-Poisson, C. Lacam, M. Tordjman, R. Aubry, H. Zirath, and N. Rorsman, "Evaluation of an InAlN/AlN/GaN HEMT with Tabased ohmic contacts and PECVD SiN passivation," *Phys. Status Solidi Curr. Top. Solid State Phys.*, vol. 11, no. 3–4, 2014, doi: 10.1002/pssc.201300320.

- [D] A. Malmros, P. Gamarra, M.-A. Di Forte-Poisson, H. Hjelmgren, C. Lacam, M. Thorsell, M. Tordjman, R. Aubry, and N. Rorsman, "Evaluation of thermal versus plasma-assisted ALD Al2O3as passivation for InAlN/AlN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 36, no. 3, pp. 235–237, 2015, doi: 10.1109/LED.2015.2394455.

- [E] A. Malmros, P. Gamarra, M. Thorsell, H. Hjelmgren, C. Lacam, S. L. Delage, H. Zirath, and N. Rorsman, "Impact of Channel Thickness on the Large-Signal Performance in InAlGaN/AlN/GaN HEMTs With an AlGaN Back Barrier," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 364–371, 2018, doi: 10.1109/TED.2018.2881319.

- [F] A. Malmros, J.-T. Chen, O. Kordina, H. Hjelmgren, E. Ö. Sveinbjörnsson, H. Zirath, and N. Rorsman, "Enhanced Mobility in InAlN/AlN/GaN HEMTs using a GaN interlayer", Accepted for publication in IEEE Trans. Electron Devices, April 2019.

- [G] A. Malmros, M. Südow, K. Andersson, and N. Rorsman, "TiN thin film resistors for monolithic microwave integrated circuits," J. Vac. Sci. Technol. B., vol. 28, no. 5, 2010, doi: 10.1116/1.3475532.

- [H] A. Malmros, K. Andersson, and N. Rorsman, "Combined TiN- and TaN temperature compensated thin film resistors," Thin Solid Films, vol. 520, no. 6, 2012, doi: 10.1016/j.tsf.2011.09.050.

### Other publications

- [a] T. N. T. Do, A. Malmros, P. Gamarra, C. Lacam, M. A. Di Forte-Poisson, M. Tordjman, M. Hörberg, R. Aubry, N. Rorsman, and D. Kuylenstierna, "Effects of Surface Passivation and Deposition Methods on the 1/f Noise Performance of AlInN/AlN/GaN High Electron Mobility Transistors," *IEEE Electron Device Lett.*, vol. 36, no. 4, pp. 315–317, 2015, doi: 10.1109/LED.2015.2400472.

- [b] J. Bergsten, J. T. Chen, S. Gustafsson, A. Malmros, U. Forsberg, M. Thorsell, E. Janzén, and N. Rorsman, "Performance enhancement of microwave gan hemts without an aln-exclusion layer using an optimized AlGaN/GaN interface growth process," *IEEE Trans. Electron Devices*, vol. 63, no. 1, pp. 333–338, 2016, doi: 10.1109/TED.2015.2501838.

- [c] T. Huang, A. Malmros, J. Bergsten, S. Gustafsson, O. Axelsson, M. Thorsell, and N. Rorsman, "Suppression of dispersive effects in AlGaN/GaN high-electron-mobility transistors using bilayer SiN," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 537–539, 2015, doi: 10.1109/LED.2015.2427294.

- [d] Y. K. Lin, J. Bergsten, H. Leong, A. Malmros, J. T. Chen, D. Y. Chen, O. Kordina, H. Zirath, E. Y. Chang, and N. Rorsman, "A versatile low-resistance ohmic contact process with ohmic recess and low-temperature annealing for GaN HEMTs," *Semicond. Sci. Technol.*, vol. 33, no. 9, 2018, doi: 10.1088/1361-6641/aad7a8.

- [e] J. Schleeh, G. Alestig, J. Halonen, A. Malmros, B. Nilsson, P. A. Nilsson, J. P. Starski, N. Wadefalk, H. Zirath, and J. Grahn, "Ultralow-power cryogenic InP HEMT with minimum noise temperature of 1 K at 6 GHz," *IEEE Electron Device Lett.*, vol. 33, no. 5, 2012, doi: 10.1109/LED.2012.2187422.

## **Table of Contents**

| Chapter 1                  | Introduction                                        | 1  |

|----------------------------|-----------------------------------------------------|----|

| Chapter 2                  | III-nitride HEMTs                                   | 3  |

| 2.1 0                      | GaN-based heterostructures                          | 3  |

| 2.1.1                      | The AlGaN/GaN heterojunction                        | 3  |

| 2.1.2                      | Polarization in III-nitrides and origin of the 2DEG | 5  |

| 2.1.3                      | Carrier transport                                   | 7  |

| 2.2 HEMT operation         |                                                     | 8  |

| 2.2.1                      | Small-signal operation                              | 9  |

| 2.2.2                      | Large-signal operation                              | 10 |

| 2.2.3                      | Short-channel effects                               | 11 |

| 2.2.4                      | Downscaling of InAl(Ga)N-based HEMTs                | 12 |

| 2.2.5                      | Electron trapping                                   | 13 |

| 2.3 H                      | Fabrication process                                 | 15 |

| Chapter 3                  | Ohmic contacts                                      | 19 |

| 3.1.1                      | Ti-based contacts                                   | 22 |

| 3.1.2                      | Ta-based contacts                                   | 23 |

| 3.1.3                      | Recess etching                                      | 25 |

| Chapter 4                  | Critical aspects of InAl(Ga)N HEMTs                 | 27 |

| 4.1 N                      | Mobility                                            | 27 |

| 4.1.1                      | GaN interlayer                                      | 29 |

| 4.2 H                      | Electron confinement                                | 30 |

| 4.3 I                      | Passivation                                         | 31 |

| Chapter 5                  | Thin Film Resistors                                 | 35 |

| 5.1.1                      | Thermal dependence                                  | 37 |

| 5.1.2                      | TiN TFRs                                            | 37 |

| 5.1.3                      | Temperature compensated TFRs                        | 38 |

| 5.1.4                      | TFR reliability                                     | 39 |

| Chapter 6                  | Conclusion and future outlook                       | 41 |

| Summary of appended papers |                                                     | 43 |

| Acknowle                   | 47                                                  |    |

| Reference                  | 49                                                  |    |

## **Chapter 1 Introduction**

Mm-waves encompass the frequency range between 30 - 300 GHz, an interval suitable for a large variety of applications, including satellite communications [1]–[3], imaging [4], and motion sensor radars [5]. In mobile communication systems, the ever-increasing demands for higher data rates are pushing the development towards higher operating frequencies, with potentially wider channel bandwidth. Mobile telecommunication networks are currently going through a transition to the 5<sup>th</sup> generation (5G), which target a wide range of frequency bands. Several are located near 30 GHz, but even operation at frequencies in the D-band (110 – 170 GHz) is considered [6], [7]. For wireless communication, a large output power density is advantageous due to smaller components, increased efficiency, and increased bandwidth. The gallium nitride (GaN) high-electron mobility transistor (HEMT) is a technology that shows great potential to meet these demands.

The first GaN HEMTs were based on an AlGaN/GaN heterojunction, and this material system is still extensively used today. Initially, the operating frequency of the GaN HEMT was limited to a few GHz. Radar systems with low requirements on high frequency performance constituted the major application area, and the development was mainly driven by defense industries. Radar remains a very important application. The large output power density is a great advantage in radar transmitters. Further, the GaN HEMT is also considered for receiver applications, implemented in a low-noise amplifier (LNA) [8]. The noise figure is comparable to the GaAs pHEMT and in addition the GaN HEMT offers robustness, which leads to high survivability [9]. A monolithically integrated radar transceiver in GaN technology is therefore feasible [10]. The highest level of integration is achieved for implementation in a microwave monolithic integrated circuits (MMIC). MMICs are circuits in which all elements are processed on a single piece of epitaxially grown material. They are typically a few mm<sup>2</sup> in size, which is considerably smaller than the alternative of mounting the components on a circuit board.

Since the advent of the GaN HEMT in the early 1990's [11], the technology has undergone a remarkable development in terms of high frequency performance. This has been possible through the improvement of the material quality and of the processing methods, and by the optimization of the heterostructure and the device design, for instance by downscaling. However, the downscaling of the AlGaN layer thickness is limited by the simultaneous loss of carrier electrons. On the other hand, the sheet carrier density is dependent on the strength of the built-in polarization field. Progress within epitaxy has enabled the growth of InAlN, InAlGaN, and AlN, with higher polarization fields, allowing for downscaling while maintaining a high sheet carrier concentration.

In this thesis, HEMTs based on InAlN/GaN and InAlGaN/GaN are explored as an alternative to the AlGaN/GaN technology, with the objective to provide large-signal amplification at higher operating frequencies. The adoption of these III-nitrides has already generated many promising results. A cutoff frequency of 374 GHz was demonstrated in [12]. An output power of 5.6 W/mm at 10 GHz was shown in [13], and 5.8 W/mm at 40 GHz was reported in [14]. Nevertheless, several challenges remain.

#### 1. Electron trapping

Electrons are captured and emitted in trap states in the buffer and at the surface. This leads to dynamically varying charge close to the 2DEG, which leads to lower output power, decreased efficiency, and memory effects due to its modulation of carriers in the channel [15].

2. Scaling effects

The device dimensions, in particular the gate length in relation to other device geometries, may prevent the HEMT from being fully switched off at high lateral electric fields. The phenomenon is called short-channel effects (SCEs) and leads to reduced gain, output power, and efficiency [16].

3. Self-heating

GaN HEMTs dissipate a lot of power that cause self-heating. Some mitigation can be provided by the use of a SiC and diamond substrate which have a high thermal conductivity [17]–[19]. However, the issue still remains since the conductivity of intermediate layers is often poor [20]. Self-heating reduces the mobility and is also plays a role for the device reliability.

4. Reliability

The growth of HEMT structures on non-native substrates introduces relatively high dislocation densities. This, in combination with high electric fields and current densities, a high level of dissipated power, and the sensitivity to surface states makes the reliability of III-nitride HEMTs demanding [21]–[25]. Under large-signal operation, both the high electric field and the dissipated power can be problematic. A critical point is next to the gate, where the electric field is the highest.

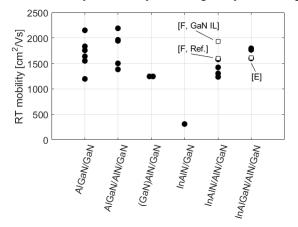

5. *Electron mobility*

The electron mobility is generally lower in InAl(GaN) based heterostructures compared to AlGaN/GaN, which has been attributed to a larger degree of alloy disorder in the barrier layer [26]–[28].

6. Ohmic contacts

Despite numerous reports on ohmic contacts with a low contact resistance, repeatability is still an issue in GaN HEMT technologies [29], [30]. Furthermore, a smooth surface morphology and edge acuity are important aspects.

Electron trapping and short-channel effects have been given special focus in this work. These issues have been addressed through the optimization of the heterostructure and of the processing modules. The use of a back barrier reduced short-channel effects but introduced more electron trapping. The thickness of the intermediate GaN channel layer was optimized with respect to these two phenomena. To reduce surface trapping, different passivation layers and their impact on the HEMT performance have also been investigated. The issue of lower mobility was addressed through the growth of a thin intermediate GaN layer, which resulted in a higher mobility, but also a loss of carrier electrons. This heterostructure was investigated by temperature dependent characterization of the HEMTs. Further, ohmic contacts based on Ta have been developed. The ambition was to minimize the contact resistance and thereby reduce losses, and to achieve a repeatable process.

To fully take advantage of the HEMTs, the ultimate goal is the implementation in MMIC circuitry, and enable highly integrated circuits operating in the mm-wave range. To reach this goal, a number of building blocks are required. Apart from the transistor technology, passive elements are needed. These include capacitors, inductors, and resistors. New thin film resistor based on TiN and TaN have been developed. Aspects such as reliability and temperature dependence have been taken into account.

## Chapter 2 III-nitride HEMTs

### 2.1 GaN-based heterostructures

The first HEMT was demonstrated by Mimura et al at Fujitsu Laboratories in 1980 [31]. The heterojunction was an AlGaAs/GaAs system, where the top AlGaAs layer was Si-doped. A significantly improved mobility was measured compared to a reference MESFET. A little more than a decade later, a HEMT based on an AlGaN/GaN heterojunction was reported by Khan et al [11]. The mobility was in the 500 cm<sup>2</sup>/Vs range, and the transconductance of the HEMT 28 mS/mm. Since then, the GaN HEMT technology has experienced a remarkable progress and is now offered by numerous companies, e.g. MACOM Technology Solutions [32], CREE, Inc. [33], Infineon Technologies [34], and NXP Semiconductors [35].

#### 2.1.1 The AlGaN/GaN heterojunction

GaN is a group III-nitride semiconductor. These compounds consist of one or more elements from group III in the periodic table of elements (In, Al, and Ga), and nitrogen. GaN exhibits a unique set of properties, shown in Table 1. It has a bandgap,  $E_g$ , around three times larger than that of Si, and more than twice that of GaAs. The large bandgap results in a large breakdown field  $E_{br}$ . SiC has a similar bandgap but lacks one of the properties of the III-nitrides: the possibility of growing heterostructures. Lastly, GaN has a high peak velocity. The great interest in GaN HEMT technology arises from the unique combination of material properties, which enables a large output power density as well as a fast device.

|                                                 | Si   | GaAs | 4H SiC | GaN  |

|-------------------------------------------------|------|------|--------|------|

| Bandgap Eg (eV)                                 | 1.1  | 1.4  | 3.2    | 3.4  |

| Breakdown electri field E <sub>br</sub> (MV/cm) | 0.57 | 0.64 | 3.3    | 3.0  |

| Peak electron velocity v (10 <sup>7</sup> cm/s) | 1    | 1.8  | 2      | 2.46 |

| Electron mobility μ (cm <sup>2</sup> /Vs)       | 1400 | 8500 | 610    | 2000 |

Table 1. Material parameters of common semiconductors

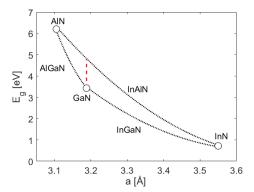

The GaN HEMT is based on a heterojunction formed by the growth of GaN layer and a III-nitride barrier layer. The bandgap ( $E_g$ ) of the III-nitrides are determined by their composition and span a wide range from 0.7 (InN) to 6.2 eV (AlN). The bandgap versus lattice constant *a* for the ternary compounds AlGaN, InAlN, and InGaN is depicted in Fig. 2-1. The barrier layer has a wider bandgap than the GaN layer. This leaves AlGaN and InAlN as potential alternatives. The conventional GaN HEMT uses an AlGaN/GaN heterojunction. Due to the lattice mismatch between AlGaN and GaN, the AlGaN will be subjected to strain, which increases with the Al mole fraction. Strain in the epilayer increases the probability of dislocations and partial relaxation, with negative consequences for the reliability. This limits the maximum Al content in AlGaN to roughly 30 % if the layer is not highly downscaled. InAlN on the other hand can be grown lattice-matched to GaN, as indicated by the red dashed line. Lattice match is obtained at an In content of 17 - 18 %. In recent years, the quality of InAlN and the quaternary InAlGaN has improved. Thus, today these two constitute alternatives to the more established AlGaN.

Fig. 2-1. Bandgap of the III-nitrides versus the lattice constant a. The dashed red line indicates the point where InAlN is lattice-matched to GaN.

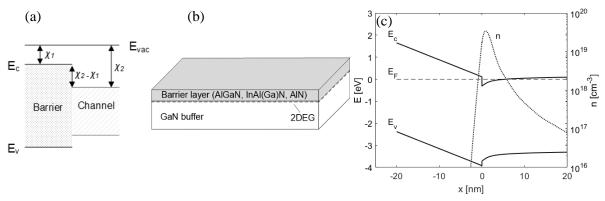

The principle behind the HEMT as opposed to other field effect transistor (FET) technologies is the spatial separation of carrier electrons from the donor atoms. Thereby, the electron scattering caused by collisions between electrons and ionized donor atoms can be avoided, which increases the mobility. Separation is achieved from the different electron affinities,  $\chi_1$  and  $\chi_2$ , of the barrier- and the GaN layers. shown in Fig. 2-2a. The electron affinity is defined as the difference between vacuum level ( $E_{vac}$ ) and the bottom of the conduction band ( $E_c$ ). This results in a conduction band discontinuity  $\chi_2 - \chi_1$ . The carrier electrons originate from the barrier layer but will attain the lower energy level on the GaN side. There they congregate at the interface and form a quantum well. Besides constituting the channel, the GaN layer also serves as a buffer layer, ensuring a good crystal quality near the interface.

The electrons in the quantum well are described to form a "two-dimensional electron gas" (2DEG), as indicated by the dashed line in Fig. 2-2b. In reality, the electron distribution is three-dimensional, which can be seen in Fig. 2-2c, showing the simulated band structure and electron density (n) of an  $Al_{0.30}Ga_{0.70}N/GaN$  heterostructure. Most electrons are found within a thickness of a few nm, while n decays exponentially towards the buffer. A small fraction is located in the barrier layer. It is highly desired to confine the carrier electrons to the quantum well. If the electrons are located in the barrier layer indicates that the device may suffer short-channel effects at high electric fields. The confinement of the 2DEG at the channel - barrier interface plays a crucial role for the HEMT performance.

Fig. 2-2. a) Energy band structure of a heterojunction, b) a GaN HEMT heterojunction, and c) the simulated energy band diagram and electron distribution of an AlGaN/GaN heterojunction with an Al mole fraction of 0.30.

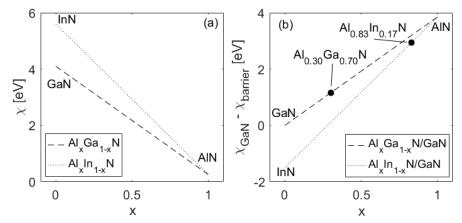

Values of the electron affinity found in the literature vary to some extent due to the difficulties of accurate determination of this property. One method for the estimation of the electron affinity is to measure the ionization energy of the valence band ( $E_v$ ) electrons,  $E_{vac} - E_v$ , by ultraviolet photoemission spectroscopy (UPS), and calculate the affinity by subtraction of the known bandgap of the material [36]. Fig. 2-3a shows the electron affinities for GaN [37], AlN [38], and InN [38], and for AlGaN and InAlN

versus Al content, assuming a linear dependence. The resulting offset in the conduction band for these barrier layers grown on GaN is shown in Fig. 2-3b. Lattice-matched InAlN/GaN exhibits a larger conduction band offset compared to Al<sub>0.30</sub>Ga<sub>0.70N</sub>/GaN, which promotes better confinement from towards the barrier.

Fig. 2-3. a) Electron affinity of AlGaN and InAlN with respect to the Al mole fraction, and b) the resulting band offset for an AlGaN/GaN and an InAlN/GaN heterojunction. Two commonly used compositions for AlGaN- and InAlN-based heterostructures are indicated.

#### 2.1.2 Polarization in III-nitrides and origin of the 2DEG

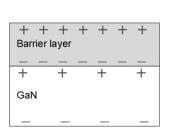

In Fig. 2-2c above, it can be seen that the energy bands of an AlGaN/GaN heterojunction are not flat. This is due to a built-in polarization field, an inherent property of the III-nitrides. The field arises because of a difference in electronegativity between the elements in the compound, which results in a displacement of the electron cloud. The crystal can therefore be envisioned as being made up of small dipoles. Due to the lack of symmetry, the dipoles at the boundaries are left dangling, resulting in a boundary charge, Fig. 2-4. This type of polarization is called spontaneous polarization, denoted  $P_{sp}$ . A second type of polarization is the piezoelectric polarization,  $\vec{P}_{pz}$ , which arises in a layer under strain. The total polarization  $\vec{P}_{tot}$  is

$$\vec{P}_{tot} = \vec{P}_{sp} + \vec{P}_{pz} \tag{1}$$

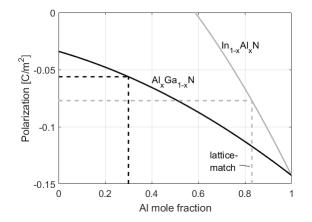

The strength of the built-in field varies with the composition of the compound. For AlGaN and InAlN,  $\vec{P}_{sp}$  increases with the Al mole fraction. AlGaN grown on relaxed GaN is subjected to tensile strain that results in a  $\vec{P}_{pz}$  with the same polarity as  $\vec{P}_{sp}$ , thus adding to a stronger  $\vec{P}_{tot}$ . Generally, the Al content in AlGaN is restricted to around 30% to avoid strain relaxation. Very thin layers can however be grown at a larger Al content.

For InAlN,  $\vec{P}_{pz}$  can be either positive or negative. For lattice-matched InAlN,  $\vec{P}_{pz}$  is zero, which means that the strain is nonexistent. This is an advantage, since strain may cause dislocations that reduce the mobility and have a negative impact on the device reliability. Fig. 2-5 shows  $\vec{P}_{tot}$  versus the Al mole fraction for InAlN and AlGaN. For lattice matched InAlN,  $\vec{P}_{tot}$  is nearly 40 % larger than for AlGaN with an Al content of 30 %. The strongest polarization field among the III-nitrides is exhibited by AlN. On the other hand, AlN grown on GaN suffers so much strain that the thickness is limited to around 2-4 nm.

Fig. 2-4. Illustration of the polarization charges at the layer boundaries in the III-nitrides.

Fig. 2-5. The total polarization of AlGaN and InAlN grown on GaN versus Al mole fraction. The dashed lines indicate resulting polarization of commonly used mole fractions for each of the alloys [39].

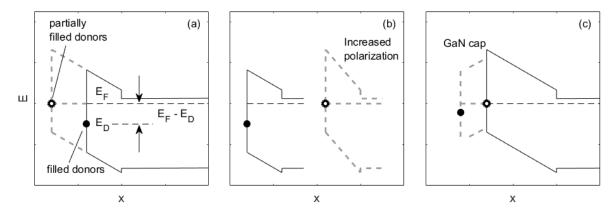

In other HEMT material systems such as AlGaAs/GaAs, carrier-donor spatial separation is achieved through intentional n-doping of the barrier layer. The donated electrons will attain the lower energy level at GaAs side and thereby form a 2DEG. GaN HEMTs are different in this respect, since the 2DEG is formed without intentional doping. There is today a high level of consensus holding that the electrons originate from donor-like surface states. An intuitive model for the formation of the 2DEG has been provided by Ibbetson et al [40]. It assumes a single donor state and makes no assumption about Fermi level pinning at the surface. Fig. 2-6a depicts the band structure of a HEMT with a thin barrier layer (solid lines). A surface donor state is located at a level  $E_D$  from the conduction band. When the donor state is below the Fermi level, it is highly probable that the state is filled. If the barrier is grown thicker (dashed lines),  $E_F - E_D$  will decrease, and  $E_D$  will eventually reach the Fermi level. An empty state implies that the electron has been excited to the conduction band, and if so, it will attain the lower energy level on the GaN side and contribute to the formation of a 2DEG. For a 2DEG to form, a certain critical thickness of the barrier layer is required, and n<sub>s</sub> continues to increase for a thicker barrier layer.

Ensuing from Ibbetsons model, a barrier layer with a higher polarization also leads to a higher  $n_s$ , as illustrated in Fig. 2-6b. A third example is presented in Fig. 2-6c, showing the band structure when an additional GaN layer caps the surface. GaN caps are often used for improving the reliability [41],[42], but are accompanied by a drop in  $n_s$ . The model is useful for the prediction of the impact that a variation in the layer structure has on  $n_s$ .

Fig. 2-6. Principle of 2DEG formation according to Ibbetson's model. The impact of growing a) a thicker barrier layer, b) a barrier with increased polarization, and c) a GaN cap layer.

#### 2.1.3 Carrier transport

The sheet conductivity  $\sigma$  in a HEMT structure can be calculated from

$$\sigma = q\mu n_s \tag{2}$$

where q is the elementary charge, and  $\mu$  is the electron mobility. In the description of a HEMT heterostructure, the sheet resistance  $R_{sh} = 1/\sigma$ , is most often used instead. At low electric fields the electron velocity shows a linear dependence on the electric field *E*, where  $\mu$  is the proportionality factor:

$$\nu = \mu E \tag{3}$$

$\mu$  is limited by different scattering mechanisms, which all have an associated limiting mobility  $\mu_x$ , set by the scattering rate. The total effective mobility of a semiconductor can be approximated by Matthiessen's rule:

$$\frac{1}{\mu_{tot}} = \frac{1}{\mu_1} + \frac{1}{\mu_2} + \dots \frac{1}{\mu_n}$$

(4)

A scattering event is essentially a change in the electron energy and momentum. In GaN-based heterostructures, there are numerous scattering mechanisms. Phonon scattering (i.e. lattice vibrations) has a strong temperature dependence and dominates at room temperature but is insignificant at cryogenic temperature [43], [44]. Therefore, the mobility in GaN-based heterostructures generally improves quite dramatically as the temperature is reduced. Further scattering mechanisms in GaN include e.g. interface scattering and carrier-carrier scattering. In ternary compounds such as InAlN and AlGaN, alloy disorder causes scattering due to the varying potential within the non-perfect crystal. The scattering rate associated with this mechanism is assumed to be high in InAlN layers due to large compositional variations [45]. Charged impurities in the GaN channel is well-known scattering mechanism, sometimes referred to as Coulomb scattering [46]. This mechanism has shown a certain temperature dependence [47], opposite to that of phonon scattering and not as strong. Other scattering mechanisms such as alloy scattering and interface scattering are assumed to be temperature independent [44].

Several non-destructive measurement techniques are available for the determination of  $n_s$ ,  $\mu$ , and  $R_{sh}$  of the as-grown wafer, e.g. eddy current technique, microwave reflectance, and mercury probe C(V) characterization. These are commonly performed on the as-grown wafer, prior to processing. The data presented in this work have been measured by Hall characterization on van der Pauw [48] structures processed simultaneously with the HEMTs. Characterization of the material properties before- and after processing allows the study of any impact on the epitaxial material from the processing.

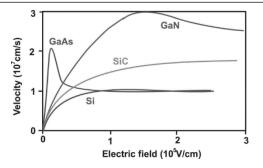

By the optimization of  $n_s$  and the low-field mobility,  $R_{sh}$  can be minimized and thereby the parasitic resistances can be reduced. For the intrinsic HEMT, the high-field properties of the material are of vital importance: The cutoff frequency  $f_T$  is directly dependent on the saturation velocity  $v_{sat}$  by

$$f_T = \frac{v_{sat}}{2\pi L_g} \tag{5}$$

At high electric fields, the electron velocity is no longer linearly dependent on *E*, and  $\mu$  is no longer constant. Fig. 2-7 shows v as a function of the electric field for GaAs, Si, SiC, and GaN as obtained from Monte Carlo simulations. GaN has a very high v<sub>sat</sub>. Similar to GaAs, the peak in v is followed by a region with a negative differential mobility, but for GaN, the peak occurs at a very high electric field, and the drop in v is less pronounced. The behavior of v at high electric fields can be described by (from [37])

$$\nu(E) = \frac{\mu_0 E}{\left(1 + \left(\mu_0 E / \nu_{sat}\right)^{\beta}\right)^{1/\beta}}$$

(6)

where  $\mu_0$  is the low-field mobility, and  $\beta$  is a fitting parameter. However, Eq. (6) does not take the negative differential mobility into account. This behavior has been verified empirically up to the peak velocity by pulsed characterization of un-gated structures [49].

Fig. 2-7. Monte Carlo simulations of the electron velocity with respect to the applied electric field in different semiconductors [50].

### 2.2 **HEMT** operation

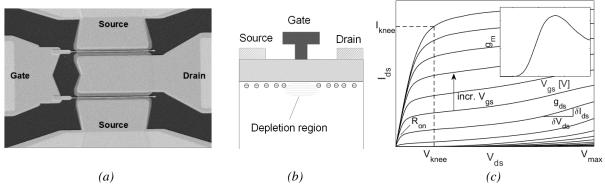

The HEMT is a FET device with three terminals: gate, source, and drain. HEMTs are most often implemented with several gate fingers, like the two-finger HEMT shown in Fig. 2-8a. The gate is a Schottky contact with ideally no current flowing through it when reversed biased, while the source and drain terminals are low-loss ohmic contacts. The drain-source current  $I_{ds}$  is set by the laterally applied  $V_{ds}$  and the vertically applied  $V_{gs}$ . The magnitude of  $I_{ds}$  in the saturation region depends on the number of carriers in the 2DEG, which is set by  $V_{gs}$ , as illustrated in Fig. 2-8b. For the investigated HEMTs in this work, a 2DEG is present at zero gate voltage. These HEMTs are therefore said to be normally on, or depletion-mode devices. The opposite, a normally-off device (enhancement mode device), can be fabricated by e.g. recessing the barrier layer in the gate region [51], [52], or by modifying the barrier by F-implantation [53]–[55].

Examples of DC characteristics  $(I_{ds}-V_{ds})$  of a HEMT are shown in Fig. 2-8c. Some important parameters that can be directly observed are the on-resistance  $(R_{on})$ , the transconductance  $(g_m)$ , see inset of Fig. 2-8c, and the output conductance  $(g_{ds})$ .  $R_{on}$  is the slope of  $I_{ds}$  in the linear region and has a direct impact on the knee voltage and current  $(V_{knee}$  and  $I_{knee})$ .  $g_m$  and  $g_{ds}$  are defined by the equations

$$g_{ds} = \frac{\delta I_{ds}}{\delta V_{ds}} \tag{8}$$

Fig. 2-8. a) SEM image of a 2x50  $\mu$ m HEMT. b) Gate modulation of the 2DEG. c) IV characteristics and transconductance (inset).

$g_m$  serves as a quality measure of the gate modulation, describing the incremental change in  $I_{ds}$  for a change in  $V_{gs}$ . Similarly,  $g_{ds}$  describes the incremental change in  $I_{ds}$  for a change in  $V_{ds}$ . In the saturation region,  $g_{ds}$  is ideally zero. As the gate length is reduced, the output conductance increases, making  $g_{ds}$  a direct measure of short-channel effects, discussed further in 2.2.3.

#### 2.2.1 Small-signal operation

In small-signal operation, the input- and output signals are so small that non-linear characteristics can be regarded as linear. By measuring the scattering parameters (s-parameters), the small-signal currentand unilateral power gains,  $h_{21}$  and U can be calculated:

$$h_{21} = \frac{-2S_{21}}{(1 - S_{11})(1 + S_{22}) + S_{12}S_{21}}$$

(9)

$$U = \frac{|S_{21}|^2}{(1 - |S_{11}|)^2 (1 + |S_{22}|)^2}$$

(10)

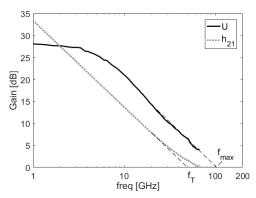

From these gains, two important figures of merit,  $f_T$  and  $f_{max}$ , can be extracted.  $f_T$  is the transit frequency (or cutoff frequency), which is the frequency where  $h_{21}$  equals zero dB.  $f_{max}$  is the maximum frequency of oscillation where U equals zero dB. These figures are used to enable direct comparison of different technologies and gives an indication of the maximum frequency of operation for circuits implemented in these technologies. An example of the measured  $h_{21}$  and U for an InAlN/AlN/GaN HEMT is shown in Fig. 2-9. The figure also shows the extraction of  $f_T$  and  $f_{max}$  from these measurements.

Fig. 2-9. The small-signal gains h21 and U and the determination of  $f_T$  and  $f_{max}$  by extrapolation.

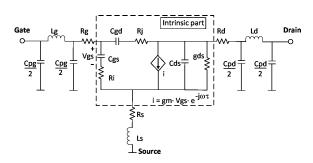

Small-signal characterization permits the extraction of an equivalent circuit model [56]–[58]. The model is conventionally divided into a bias independent extrinsic part and a bias dependent intrinsic part (Fig. 2-10). For accurate determination of the intrinsic elements, it is important that the extraction of the extrinsic elements is precise. These are obtained in two additional cold-FET (off-state) measurements, as described in [58].

Fig. 2-10. Equivalent small-signal electrical model.

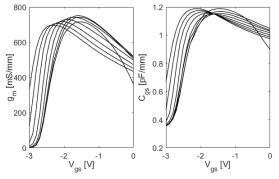

Fig. 2-11. The small-signal  $g_m$  and  $C_{gs}$  extracted at RT for a HEMT on the GaN IL sample in [F] for  $V_{ds}$  from 2 to 9 V.

A small-signal model is valid for one bias point only. The bias dependence of the different elements is obtained by multi-bias s-parameter measurements and model extraction. The bias-dependent parameters are often used as a first approximation for the extraction of large-signal, non-linear models.

Fig. 2-11 shows the extracted values of  $g_m$  and  $C_{gs}$  (gate capacitance) versus  $V_{gs}$  for different values of  $V_{ds}$ . Small-signal models provide valuable insight into the limiting parameters of the HEMT, which to some extent can be related to physical parameters of the device.

The intrinsic  $f_T$  can be described by  $g_m$  and  $C_{gs}$  and  $C_{gd}$  (gate-drain capacitance):

$$f_{T,int} = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \tag{11}$$

Eq. (11) is sometimes approximated by omitting  $C_{gd}$ , since  $C_{gs}$  is often considerably larger than  $C_{gd}$ .  $f_{max}$  can be approximated with the following expression [59]:

$$f_{max} \approx \frac{f_T}{2\sqrt{(R_i + R_s + R_g)g_{ds} + 2\pi f_T R_g C_{gd}}}$$

(12)

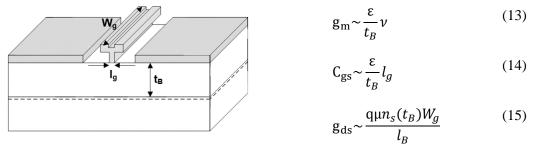

To reach higher operating frequencies, the optimization of  $g_m$ ,  $C_{gs}$ , and  $g_{ds}$ , is paramount. It is desired to maximize  $g_m$  while minimizing  $C_{gs}$  and  $g_{ds}$ . These parameters are related to the physical dimensions  $t_B$  (barrier thickness) and  $l_g$  (gate length), and gate width ( $W_g$ ), shown in

Fig. 2-12. HEMT dimensions with a major impact on the small-signal elements.

$t_B$  and  $l_g$  are clearly important factors in the high frequency optimization. The general approach to increase  $f_T$  and  $f_{max}$  is to simultaneously scale down  $l_g$  and  $t_B$ . In this way  $g_m$  is increased, while both  $C_{gs}$  and  $g_{ds}$  are reduced. However, as discussed in 2.1.2, the downscaling of  $t_B$  implies a loss of carrier electrons, which limits the maximum drain current and ultimately the output power. This results in a trade-off between the high frequency performance and the output power.

#### 2.2.2 Large-signal operation

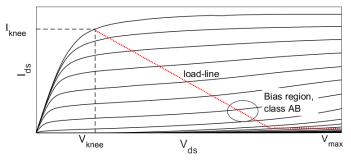

Power amplifiers (PAs) and frequency converters operate under large-signal conditions. For PAs, it is desired to maximize the output power  $P_{out}$ , gain, efficiency, and linearity. The current and voltage waves at the output port depend on the connected load impedance in combination with device properties. PAs are categorized into different classes depending on the bias conditions. In this work, large-signal characterization was generally performed with the HEMTs biased in class AB operation, which means that the transistor is conducting more than half of the cycle. Class AB is a good compromise in terms of gain, output power and efficiency.

Fig. 2-13. IV curves and superimposed load line of a HEMT in large-signal operation.

Maximum output power  $P_{out,max}$  is achieved when the RF swing spans the entire load line. Hence,  $P_{out,max}$  is limited by the knee in the IV characteristics, and also by the breakdown voltage.

$$P_{out,max} = \frac{(V_{max} - V_{knee})(I_{knee})}{8}$$

(16)

The efficiency is often given as the power-added efficiency, PAE:

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} \tag{17}$$

In this work, large-signal characterization has been performed using load- and source pull to find the output matching for maximum output power and efficiency. After the load/source pull sequence, a power sweep is performed, where the input signal is increased until a specific gain compression is reached. Both passive- and active load pull has been performed. The active load-pull system is based on a large-signal network analyzer (LSNA), which enables the direct measurements of the current- and voltage waveforms [60]. Active load-pull has been used up to a fundamental frequency of 10 GHz, allowing for enough harmonics to reconstruct the waveforms. For higher frequencies (up to 40 GHz), passive load-pull was used. Passive load-pull relies on impedance tuners that can present different load impedances to the device under test.

#### 2.2.3 Short-channel effects

The downscaling of the HEMT dimensions and high-voltage operation can lead to the phenomenon known as short-channel effects (SCEs). It occurs when the electrons gain enough energy from the applied lateral electric field to pass underneath the depleted area of the reverse biased HEMT. The consequence is that the HEMT channel cannot be completely pinched. HEMTs with short gates are particularly sensitive to SCEs, since they cannot deplete the channel as efficiently, and require a larger magnitude of the applied voltage to fully pinch the device.

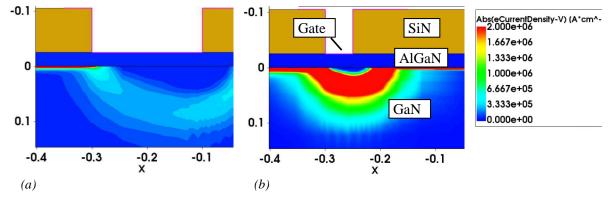

In Fig. 2-14, the phenomenon of SCEs is visualized with TCAD simulations. The current in two AlGaN/GaN HEMTs with gate lengths of 200 and 50 nm, respectively, is compared at a bias  $(V_{gs}, V_{ds}) = (-6, 20)$  V. For the longer gate this bias condition results in a pinched channel. For the short gate the depletion region is much smaller, which facilitates conduction through the buffer. The thickness of the barrier layer also plays a role. A thin barrier layer alleviates SCEs, but also results in fewer carriers in the 2DEG.

Fig. 2-14. Simulated current density of two HEMTs on AlGaN/GaN with gate lengths of a) 200 nm and b) 50 nm. The HEMTs are biased at  $(V_{gs}, V_{ds}) = (-6, 20) V$ .

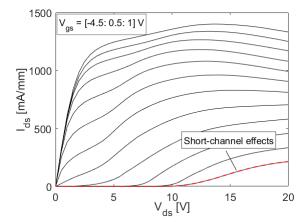

The impact of SCEs is visible in the IV characteristics, as shown in Fig. 2-15. The maximum negative gate voltage of -4.5 V is sufficient to pinch the HEMT at a drain voltage up to 10 V, whereas at higher drain voltage, the HEMT cannot be fully pinched-off.

The gravity of the SCEs is clearer in the transfer characteristics ( $I_{ds}$ - $V_{gs}$ ), Fig. 2-16. As  $V_{ds}$  is increased, the voltage required to pinch the HEMT ( $V_{po}$ ) is shifted towards more negative values. A

useful measure to quantify the SCEs is therefore the drain-induced barrier lowering, DIBL [61], defined as

$$DIBL = \frac{V_{po,high} - V_{po,low}}{V_{ds,high} - V_{ds,low}}$$

(18)

The determination of DIBL requires the definition of a pinch-off condition, in this work defined as a drain current  $I_{po}$  of 1 mA/mm. DIBL is given in mV/V. Another measure of SCEs is the subthreshold swing (SS) [62], [63], which considers the behavior of  $V_{gs}$  with respect to log10( $I_{ds}$ ) below the threshold voltage, as shown in the inset of Fig. 2-16. SS is given in mV/decade and should be minimized.

$$SS = \frac{\delta V_{gs}}{\delta \log_{10}(I_{ds})} \tag{19}$$

In the extraction of DIBL it is important to choose the  $V_{ds}$  interval within a region which is relevant for the intended application, and similar reasoning should be applied to SS. Since there is no consensus for the extraction of these figures, it can be difficult to compare results in the literature.

Increasing V  $10^{2}$ Extraction of DIBL [mm/an] Extraction of SS swing \_sp po,high' po.lov 10-2 V<sub>ds, high</sub> V<sub>ds, low</sub> Max derivative **€**δV<sub>gs</sub> 10--2 V<sub>gs</sub> [V] -4 -3 0 -1

Fig. 2-15. SCEs visible in the IV characteristics.

Fig. 2-16. Extraction of DIBL and SS from  $I_{ds}$ - $V_{gs}$  data.

#### 2.2.4 Downscaling of InAl(Ga)N-based HEMTs

As described in 2.1.2, the sheet carrier concentration depends on the barrier thickness and the size of the built-in polarization field. Since InAlN has a stronger polarization field compared to conventional AlGaN (with an Al content up to around 30 %), the required layer thickness for a given  $n_s$  is smaller. The realization of InAlN barrier layers has therefore offered a way to circumvent the limitations in the downscaling of AlGaN. It has been shown that Ga is easily incorporated during the growth of InAlN, generally attributed to residual Ga in the growth chamber [64]. This presumably means that some reported results on InAlN-based heterostructures may in fact be quaternary InAlGaN. Both InAlN and InAlGaN have been evaluated as barrier layers in this work, collectively addressed as InAl(Ga)N.

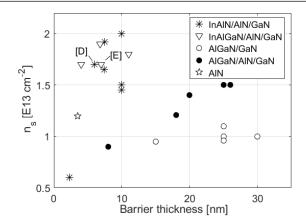

The dependence of  $n_s$  on the barrier thickness is illustrated for different barrier layers in Fig. 2-17. It is shown that AlGaN must be grown thicker to achieve the same 2DEG density as the InAl(Ga)N barrier. A result that stands out is the pure AlN barrier (although capped with a thin GaN layer). Having the highest polarity of the III-nitrides, a mere 3.5 nm thick AlN layer produces an  $n_s$  of  $1.2 \cdot 10^{13}$  cm<sup>-2</sup>.

Fig. 2-17. Charge density as a function of barrier thickness for different material systems [65]–[81], [D], [E].

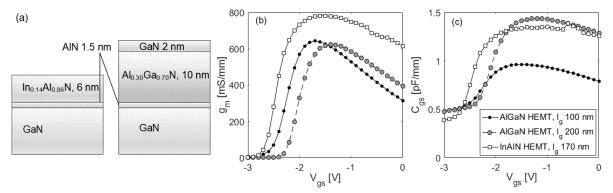

To give an idea of the size of the small-signal equivalent circuit parameters obtained for the HEMTs on a typical epi in this work,  $g_m$  and  $C_{gs}$  for an InAlN HEMT from [F] are plotted in Fig. 2-18. A comparison is made with two HEMTs fabricated on a downscaled AlGaN-based epi. The two heterostructures, shown in Fig. 2-18a, have total barrier thicknesses of 7.5 and 13.5 nm, respectively. The InAlN HEMT has a gate length of 170 nm, while the AlGaN HEMTs have gate lengths of 100 and 200 nm. The HEMTs are biased at a drain voltage of 5 V. The InAlN HEMT exhibits a  $g_m$  around 140 mS/mm higher than that of the AlGaN HEMTs Fig. 2-18b.  $C_{gs}$  of the InAlN HEMT was in the same order as for the AlGaN HEMT with a gate length of 200 nm, Fig. 2-18c. The data are consistent with the general results in this work, in which the maximum  $g_m$  has ranged from 750 to 900 mS/mm, and  $C_{gs}$  from around 1 - 2 pF/mm, largely dependent on the gate length.

Fig. 2-18. The modelled small-signal elements a)  $g_m$  and b)  $C_{gs}$  versus gate bias for HEMTs based on InAlN and AlGaN. The heterostructures are shown to the right.  $V_{ds}$  is 5 V.

#### 2.2.5 Electron trapping

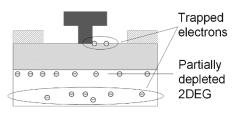

Surface states as well as imperfections in the buffer layer, such as dislocations and impurities, can act as electron traps. Filled electron traps exert the 2DEG to an electric field, which partially depletes the GaN channel layer of electrons (Fig. 2-19). This leads to dispersive effects, generally defined as unwanted variations of device response dependent on frequency or bias conditions. For instance, a parameter extracted from DC characterization may not exhibit the same value under RF operation, or the device exhibits different behavior when transiting from different quiescent bias points.

During large-signal operation, electron trapping manifests mainly in a reduction in the output power, efficiency, and linearity. To counteract electron trapping at the surface, a passivation layer, commonly  $SiN_x$  or  $Al_2O_3$ , can be used, while the mitigation of buffer trapping is mainly a matter of the heterostructure design and growth technique.

There are many phenomena related to trapping effects. Some can be readily observed by pulsed IV characterization. In these measurements, double pulsing of  $V_{gs}$  and  $V_{ds}$  is performed from a quiescent

point ( $V_{gs,Q}$ ,  $V_{ds,Q}$ ) to an active point where the IV data is measured. At certain quiescent voltages, the electrons will be trapped, while at ( $V_{gs,Q}$ ,  $V_{ds,Q}$ ) = (0, 0) V quiescent voltage represents the ideal case, e.g. with no traps activated by an electric field.

Fig. 2-19. Illustration of surface- and buffer traps, depleting the 2DEG.

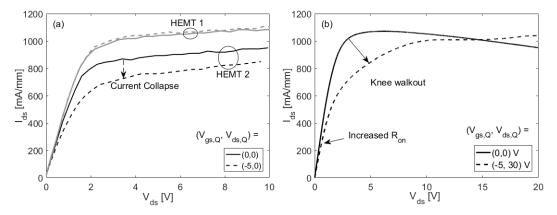

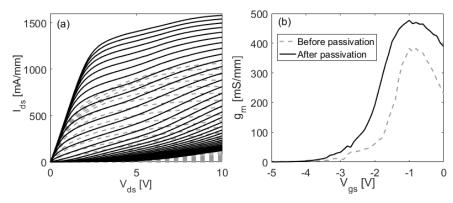

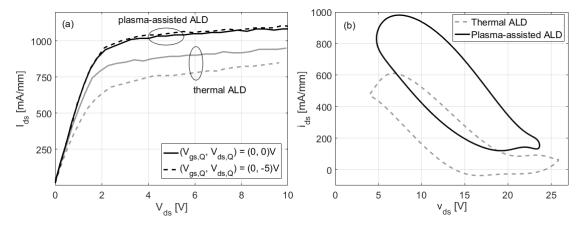

In Fig. 2-20a, the results of pulsed IV characterization of two HEMTs from [D], here denoted HEMT 1 and 2, are shown. A quiescent voltage  $(V_{gs,Q}, V_{ds,Q}) = (-5, 0)$  V is compared to (0, 0) V. HEMT 1 shows no signs of trapping, while HEMT 2 exhibits a lower current for a negative quiescent gate voltage. The phenomenon, known as current collapse, is caused by partial depletion of the 2DEG. The impact of electron trapping by the application of a gate voltage is also known as the gate lag effect. The notion of a virtual gate is also commonly used [82], referring to the impact of filled surface states, which can be regarded as a gate extension.

In Fig. 2-20b, a HEMT from [E] exhibits an increase in the on-resistance for a non-zero quiescent voltage, in this case (-5, 30) V. The phenomenon is caused by depletion of the 2DEG in the channel region and in the adjacent access regions. The HEMT exhibits a simultaneous displacement of the knee of the IV curve, referred to as knee-walkout. Similar to the gate lag effect, dispersion caused by electron trapping incited by a voltage applied to the drain terminal, is referred to as the drain lag phenomenon.

Fig. 2-20. Dispersive effects revealed in pulsed IV measurements. a) Current collapse related to surface trapping [D], and b) Dynamic on-resistance and knee walkout phenomena caused by buffer trapping [E].

A definite distinction between surface- and buffer traps is hard to make. As a rule of thumb, a negative gate voltage fills the surface traps, causing current collapse, while a high drain voltage fills the buffer traps, leading to an increased on-resistance and knee walkout. However, the quiescent voltage must be chosen so that the HEMT is fully pinched in order to avoid any impact from self-heating. For a depletion mode device this means that a negative gate voltage below  $V_{po}$  is applied also when the impact of a quiescent drain voltage is measured, which may add a contribution from surface trapping to the measured results. Further, the drain voltage also increases the field near the gate and may contribute to surface trapping. However, conclusions can often be drawn based on the observed phenomena (e.g. current collapse and knee-walkout), and the design of the experiment.

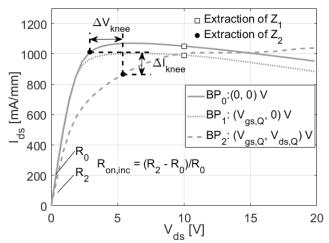

The impact of electron trapping has been quantitatively estimated by a number of figures in this work. They include slump ratios, defined as

$$Z_n = \frac{(I_{ds}(BP_n) - I_{ds}(BP_0))}{I_{ds}(BP_0)} \cdot 100$$

(20)

where  $I_{ds}$  is the current measured in the active point. Under the influence of trapping,  $I_{ds}$  depends on the quiescent bias point  $BP_n = (V_{gs,Q}, V_{ds,Q})$ .  $BP_0$  represents  $(V_{gs,Q}, V_{ds,Q}) = (0, 0)V$ . Further, the impact of trapping can be estimated by the shift in the knee voltage  $\Delta V_{knee}$  and the associated drop in the output current  $\Delta I_{knee}$ . Another very useful measure is the relative increase in the on-resistance,  $R_{on,inc}$ . The extraction of these measures, as performed within this work, is depicted in Fig. 2-21. The figure shows the pulsed IV characteristics from two quiescent bias points  $BP_1$  (for estimation of surface trapping) and  $BP_2$  (for estimation of buffer trapping). The slump ratio  $Z_1$  is extracted at any voltage above the knee, whereas  $Z_2$ ,  $\Delta V_{knee}$ , and  $\Delta I_{knee}$  are extracted at the knee, indicated by the black points.  $R_{on,inc}$  is extracted in the linear region at low drain voltage.

Fig. 2-21. Pulsed IV characterization comparing the bias points  $BP_0$ ,  $BP_1$ , and  $BP_2$ , and an indication of where the parameters  $Z_1$ ,  $Z_2$ ,  $\Delta V_{knee}$ ,  $\Delta I_{knee}$ , and  $R_{on,inc}$  are extracted.

### 2.3 Fabrication process

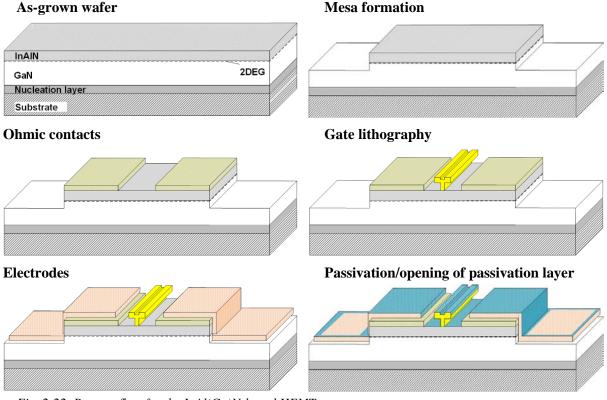

The fabrication of a HEMT includes the definition of an active area, ohmic contacts for the drainand source terminals, gate formation, contact pads, passivation, and opening of the passivation layer to enable probing. The sequence and methods may vary between different process houses. The active area can be defined by mesa formation through dry etching, or by ion implantation, commonly utilized in industrial GaN technologies. Ion implantation relies on heavy ion bombardment of the region outside the active areas, causing crystal damage that renders the material isolating. A wide range of ions can be used, e.g.  $Ar^+$  [83] or and  $O^+$  [84]. Ion implantation is generally preferred due to its planar characteristics, which is favorable for the repeatability of the gate definition and lack of any issues regarding the mesa sidewall [85], [86].

Conventionally, the ohmic contact is formed by annealing of a metal stack to form a tunneling contact on a highly doped layer. Because of the high anneal temperature, the ohmic contact formation is usually performed prior to the gate step. Optical lithography generally meets the demands on the resolution and alignment for the definition of mesas and ohmic contacts. For gates in the range of 100's of nm range, e-beam lithography (EBL) is required. Ni is frequently used as Schottky contact for its good adhesive properties and large work function,  $\Phi_m$ , resulting in a large barrier height. Contact pads may be deposited by sputtering or evaporation.

In conventional GaN HEMT processing, Au is used for coverage of ohmic contacts, gates, and electrodes to avoid oxidation. However, it has been shown that long-term degradation of ohmic contacts may occur if Au diffuses and intermix with Al [87]. An Au-free metallization scheme would improve reliability and reduce the production cost. Furthermore, and Au-free process would be compatible with Si-processing. In particular, ohmic contacts can be challenging to fabricate without Au, as will be discussed in Chapter 3. Suggestions for Au-free Schottky diode metallization schemes include e.g. Al/W [88], pure Ni [89], and Ti/Al/W [90].

Passivation may be performed after the gate formation ("passivation last-process") [91]. In this case, it is important that the deposition temperature does not cause any harm to the device. In a metal-insulator-semiconductor HEMT (MISHEMT), the gate dielectric, which constitutes at least part of the passivation layer, is deposited prior to gate formation [92], [93]. Surface passivation may also be performed as the very first step in the process ("passivation first-process"). In this approach, openings are defined for the gate-, source-, and drain contacts. This is frequently done with SiN<sub>x</sub> passivation (LPCVD) [96]. The advantage is the immediate protection of the semiconductor surface. The most commonly used dielectric for surface passivation is SiN<sub>x</sub>, deposited by plasma-enhanced chemical vapor deposition (PECVD) [97], [98].

In this work, the fabrication process is a basic process, suitable for the evaluation of the epitaxially grown heterostructure, the process modules, and the device performance. The process flow is depicted in Fig. 2-22. Active areas are defined by mesa isolation, performed by optical lithography and a  $Cl_2/Ar$ -based dry-etching process. Ohmic contacts are formed by metallization of the contact area followed by annealing. Details of the work on ohmic contacts are presented in Chapter 3.

Fig. 2-22. Process flow for the InAl(Ga)N-based HEMT process.

Gates are defined by e-beam lithography (EBL), and metallized with a Ni/Pt/Au scheme. The gate length of the fabricated HEMTs range from 50 to 200 nm. Following the gate formation, Ti/Al electrodes are deposited. Notably, Au free contacts are prone to form a surface oxide, resulting in an additional resistance between the contact metal and the electrode. Sputtered electrodes combined with in-situ  $Ar^+$  cleaning has shown to be successful in terms of forming a non-resistive direct connection between the electrode and the ohmic contact. Passivation is performed by the deposition of  $Al_2O_3$  by plasma-assisted atomic layer deposition (ALD), with an exception in [C], where  $SiN_x$  is deposited by PECVD. In the final step, openings in the passivation layer in the regions of the electrodes are defined by optical lithography. The removal of the passivation layer is in the case of  $Al_2O_3$  passivation done by wet etching HF:H<sub>2</sub>O 1:10, and in the case of  $SiN_x$  passivation by dry etching.

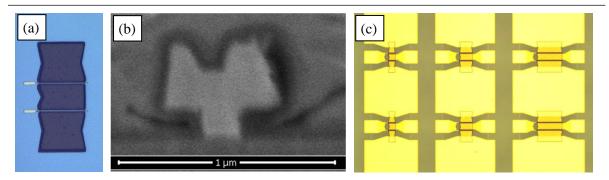

Fig. 2-23. a) Microscope image of the HEMT after the gate step. b) FIB-SEM image showing the cross-section of a gate with an approximate gate length of 170 nm. c) Processed HEMTs with different gate peripheries.

Fig. 2-23 shows three images related to the fabrication process. A microscope image of the HEMT after the gate formation is shown in Fig. 2-23a. Fig. 2-23b shows a FIB-SEM image of the cross section of a HEMT with a gate length of 170 nm. The finalized HEMTs are shown in Fig. 2-23c.

## Chapter 3 Ohmic contacts

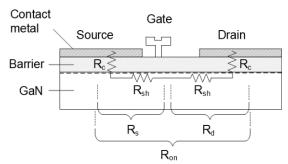

Low on-resistance is key for high frequency operation and efficiency of HEMTs.  $R_{on}$  is determined by the sum of the contact resistances ( $R_c$ ) and access resistances, related to the sheet resistance ( $R_{sh}$ ) of the epi, see Fig. 3-1. Thus, the minimization of  $R_{on}$  necessitates for  $R_c$  to be reduced. For the processed HEMTs within this work,  $R_c$  often constitutes to a significant part of the on-resistance. As an example, a typical 2x50 µm InAl(Ga)N HEMT has an  $R_c$  of 0.4 Ωmm, a material sheet resistance of 230 Ω/square, and a source-drain distance of 1.5 µm. This HEMT has a minimum  $R_{on}$  of 12 Ω, where 8 Ω (67 %) corresponds to the contribution from the ohmic contacts.

Fig. 3-1. Depiction of the elements contributing to the on-resistance

Through its contribution to the on-resistance, the parasitic contact resistance affects the high frequency performance, output power, and efficiency. Some of the highest ever reported values of  $f_T$  and  $f_{max}$  were reported for HEMT with an extremely low  $R_c \leq 0.01 \ \Omega mm$  [99]. By setting the knee of the IV characteristics, the on-resistance limits the RF swing in large-signal operation. Further, the voltage drop over the ohmic contacts results in losses, which reduce the efficiency. The impact can be observed by calculating the extrinsic transconductance,  $g_{m,ext}$ :

$$g_{m,ext} = \frac{g_{m,int}}{1 + R_s g_{m,int}}$$

(21)

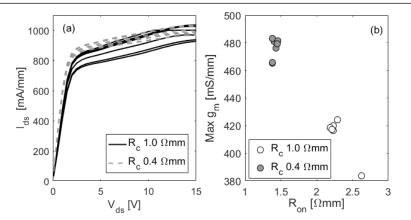

In Fig. 3-2a, an example of the measured IV data of HEMTs processed on two pieces from the same wafer is shown. The samples differed in the contact resistance, which was 1.0 and 0.4  $\Omega$ mm, respectively, resulting in a clear impact on the on-resistance, knee voltage and the maximum current. The extrinsic transconductance is shown for the same devices versus on-resistance in Fig. 3-2b. The transconductance improved from 420 to 480 mS/mm for the piece with the lower contact resistance.

Fig. 3-2. The measured impact of a varying contact resistance on a) the IV characteristics and b) the transconductance.

Despite the numerous publications demonstrating a low  $R_c$ , ohmic contacts to III-nitride heterostructures remains the subject of extensive research. Issues with repeatability and difficulties of achieving a versatile process that works for any heterostructure are revealed in the very wide spread in reported  $R_c$  values. Moreover, these results underline the lack of full understanding of the contact mechanism and the impact on  $R_c$  by tuning the process parameters. Further motivations for continued exploration include requirements on the contact formation step in terms of integration with the full fabrication process. A smooth surface morphology of the contacts is preferred primarily because the alignment marks used for gate definition are most often defined in the ohmic layer. Furthermore, the surface morphology is related to the edge acuity. A sharp edge facilitates the lateral downscaling and prevents device-to-device variations in the breakdown voltage, caused by a spread in the actual sourcedrain distance [100]. A minimized thermal budget during fabrication is also desired because of any impact that it might have on the heterostructure. For example, a high anneal temperature has been associated with a higher vertical leakage through the buffer in [101].

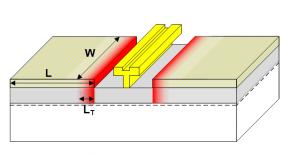

The GaN HEMT is essentially a planar device, thus the major part of the current transfers between the ohmic contact metal and the 2DEG through a window marked in red in Fig. 3-3. This part is very small in comparison to the total length L of the contact. The transfer length ( $L_T$ ) is defined as the part through which a fraction 1/e of the current flows. As long as L is significantly longer than  $L_T$ , the resistance of the contact is independent of L, but scales inversely with the contact width W. Therefore,  $R_c$  is generally normalized to W and given in the unit  $\Omega$ mm. An  $R_c$  below 0.2  $\Omega$ mm is generally considered to be excellent, targeted for instance when optimizing for a high  $f_{max}$ .

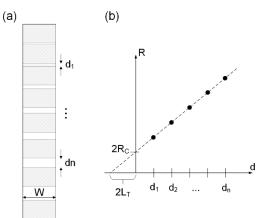

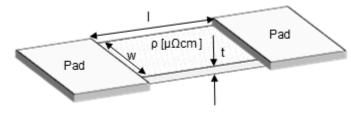

The most straight-forward way of measuring  $R_c$  is by using the transfer length method (TLM). The method uses a test structure consisting of a set of contacts separated by different spacings  $d_1 \dots d_n$ , Fig. 3-4a. Four-point probe measurements are performed, forcing a small current while the voltage drop over each contact pair is measured by a second set of probes.  $R_c$  is found by fitting a line to the data and extrapolate to the point where d = 0, corresponding to the resistance from two contacts, Fig. 3-4b. The slope of the fitted line is determined by the sheet resistance of the epi.  $L_T$  can be determined from TLM measurements since  $2L_T$  corresponds the point where the fitted line and the x-axis intersect. The non-normalized resistance  $R_{tot}$  between two contacts, spaced by a distance  $d_x$ , is written as in Eq. (22). Thus, the slope of the fitted line depends on the sheet resistance of the epi.

$$R_{tot} = 2R_{contact} + R_{sh} \frac{d_x}{W}$$

(22)

Sometimes the specific contact resistance  $\rho_c$ , given in  $\mu\Omega cm^2$ , is used to evaluate contacts and enable comparison to vertical devices.  $\rho_c$  is often calculated using the equation

$$\rho_{\rm c} = R_{\rm sh} L_{\rm T}^2 \tag{23}$$

However, it should be noted that the sheet resistance under the contact is likely not the same as between the contacts, which makes the equation an approximation. Alternatively,  $\rho_c$  can be measured directly on vertical Cross Bridge Kelvin Resistor (CBKR) structures [102], but with limited accuracy

due to the lateral flow in the contacts. A test structure for a more reliable determination of  $L_T$  was proposed in [103], yet such a structure requires a very precise definition of the dimensions.

Fig. 3-3. Illustration of current transfer (red) between the metal contact and the 2DEG, the contact dimensions and transfer length marked out.

Fig. 3-4. TLM test structure and corresponding R versus distance d plot.

The conventional contact is based on a Ti/Al metal scheme and requires annealing at hightemperature. This is still the most extensively used ohmic contact for GaN HEMT technologies. An emerging fabrication is re-growth, a method that utilizes epitaxy to grow highly Si-doped GaN in a recess etched contact region, where both MOCVD and MBE can be utilized. A potentially very low contact resistance can be obtained, yet this more advanced method faces similar problems of repeatability as the conventionally processed contacts, and therefore the results are scattered. For MBEgrown contacts, a contact resistance around 0.1  $\Omega$ mm [104], [105], and 0.26  $\Omega$ mm [106] have been reported, while results on MOCVD grown contacts include 0.23  $\Omega$ mm [107], 0.33  $\Omega$ mm [108], and 0.45  $\Omega$ mm [108]. Notably, recess etching is becoming increasingly common also in conventionally annealed contacts, having shown to enable a lower R<sub>c</sub> compared to planar contacts. With this approach, the annealed contacts have also shown to produce excellent contacts with an R<sub>c</sub> of e.g. 0.17  $\Omega$ mm [109] and even 0.1  $\Omega$ mm [110].

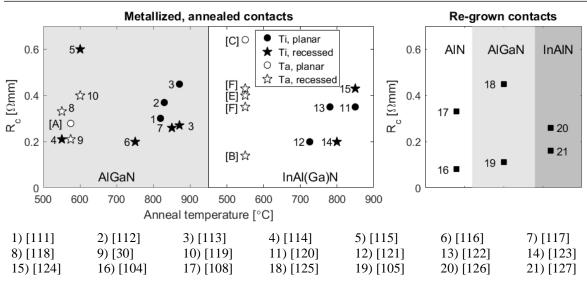

A small selection of reported results of  $R_c$ , that to some degree is representative for ohmic contacts to the III-nitrides is shown in Fig. 3-5. The contacts were formed to AlGaN-, InAlN- and AlN barriers by the different methods discussed in this chapter. Regular metallized - annealed contacts are displayed versus anneal temperature in Fig. 3-5a, whereas Fig. 3-5b shows the results for regrown contacts. The picture is intended to provide an overview of results that are commonly achieved, even though it is not completely fair to compare the fabrication methods for non-identical heterostructures. However, the very low  $R_c$  in [A] for Epi I is deliberately omitted since the AlGaN layer in this heterostructure has a significantly lower Al mole fraction compared to the other references.

Some general conclusions from the figure can be drawn. For a metallized, annealed contact, an  $R_c \leq 0.2 \ \Omega$ mm normally requires recess etching, but has been reported as well for planar contacts. Ta-based ohmic contacts can compete with the conventional Ti-based contacts, which require a higher anneal temperature. The very low  $R_c$  of 0.08  $\Omega$ mm for regrown contacts is very impressive and was achieved for an AlN barrier, for which a planar contact would presumably be highly resistive due to a large  $\Phi_b$ . Although numerous reports have shown that low-resistive ohmic contacts to GaN heterostructures are possible, the challenge of obtaining a repeatable, versatile process with minimum impact on the epi still remains.

Ohmic contacts

Fig. 3-5. Reported values of  $R_c$  for different fabrication methods and different heterostructures.

#### 3.1.1 Ti-based contacts

The primary active element in the conventional Ti-based contact approach is Ti. However, Ti alone does not produce good ohmic contacts, but requires an additional Al layer. Au is generally used to cap the layer stack to avoid oxidation, but Al and Au have a tendency to form highly resistive alloys, which leads to poor surface morphology [128]. Therefore an intermediate layer of e.g. Ni [129], or Mo [112] is generally incorporated. This is often not fully adequate, and therefore, for instance W and TiN have been proposed as substitutes to Au [130]. However, it has often been shown difficult to achieve a low  $R_c$  without Au, which could indicate that the Au layer has a role besides preventing oxidation. It is speculated in [131] that a low work function Au-containing phase at the metal – semiconductor interface promotes current flow, and further that reported optimum Ti/Al layer thickness ratios [132] are highly influenced by which reactions with Ni and Au that occur.

The optimum anneal temperature of the Ti-based contact lies around 800 - 900 °C. The advantages of a lower thermal budget have incited the development of different strategies to reduce the anneal temperature. Recess etching prior to metallization has shown to facilitate ohmic contact formation, and resulted in an R<sub>c</sub> of 0.21  $\Omega$ mm for the Ti-based metal scheme annealed at 550 °C [114]. A recent approach is microwave annealing [133]–[135]. The method has been claimed to locally increase heating by means of the eddy current caused by a varying magnetic field [136].

According to the theory that has gained most acceptance regarding the contact mechanism, ohmic behavior in the conventional contact is obtained by the reaction between the Ti and N, forming TiN [137][138][139] or other phases containing Ti [140]. This creates N vacancies in the barrier layer, which act as n-dopants [141]. The result is a heavily doped barrier layer at the metal-semiconductor interface, and potentially further down into crystal. The heavy doping bends the conduction band, permitting electrons to tunnel between the contact metal and the 2DEG through field emission (FE). The conclusion is based on the identification of the compound(s) adjacent to the semiconductor surface, which can be performed by e.g. TEM/EDX analysis [142] or by XRD [111]. The role of Al is not as clear and has been debated. It has been proposed that Al works as a catalyst for Ti to react with N [143]. It has also been claimed that Al slows down the aggressive reaction in which TiN is formed, based on the observation of voids beneath the TiN when pure Ti is annealed on GaN and AlGaN [144].

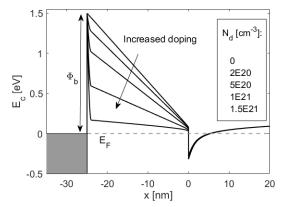

TCAD simulations of a metal/Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN structure was performed for different superficial doping levels N<sub>d</sub> to demonstrate the impact of N vacancies on the conduction band. The barrier height  $\Phi_b$ , equal to

$$\Phi_{\rm b} = \Phi_{\rm m} - \chi \tag{24}$$

#### Ohmic contacts

where  $\chi$  is the electron affinity of the AlGaN, was assumed to be 1.5 eV [145]. The AlGaN is 25 nm thick and the doping of the 1 nm top part is stepped from zero to  $1.5 \cdot 10^{21}$  cm<sup>-3</sup>. For comparison, regrown ohmic contacts have been fabricated with a doping level of 1e19 to 1e20 cm<sup>-3</sup> [105], [126]. For the highest doping level, the conduction band within the AlGaN is approaching E<sub>F</sub>, leaving only a very narrow barrier, which promotes tunneling.

Fig. 3-6. Simulations of a metal -  $Al_{0.25}Ga_{0.75}N/GaN$  contact with an electron barrier of 1.5 eV. The top 1 nm part of the AlGaN is varied from intrinsic to heavily doped at the indicated doping concentrations.

Although the Ti-based contact is essentially a tunneling contact, it does not exclude other factors from having an impact on  $R_c$ . More commonly seen in earlier publications is the reporting of metallic protrusions stretching along dislocations in the barrier layer, thereby forming a direct contact to the 2DEG [116]. Some have emphasized the low work function of TiN (3.74 eV [143]) as being a major contributing factor through the reduction of the effective barrier height [111]. If the band structure looks like in Fig. 3-6, tunneling is facilitated by a higher thermal energy of the electrons. For the highest simulated doping level, an additional energy of around 0.2 eV above  $E_F$  would be required for a high electron tunneling probability. This current mechanism, combining thermionic emission and field emission, is referred to as thermionic field emission, TFE [146]. In [F],  $R_{on}$  showed an increase at very low temperature. Since no increase in the measured  $R_{sh}$  was observed, the increase was concluded to arise from  $R_c$ . This could be an indication of a lower probability of tunneling through the barrier when the thermal energy of the electrons is very low, and that the contact mechanism is TFE, dominated by tunneling.

From the discussion above it is clear that a low  $\Phi_b$  promotes current flow. Since  $\chi$  decreases with the Al mole fraction [147], the benefits of a high Al content in terms of n<sub>s</sub> and electron confinement comes at the cost of a more challenging ohmic contact fabrication. The tuning of  $\Phi_m$  as a way of decreasing  $\Phi_b$  is further complicated, since the main role of the contact metal is the extraction of N, which Ti has shown to do very efficiently, inevitably forming TiN at the interface.

#### 3.1.2 Ta-based contacts

Ta has previously been incorporated in the metallization schemes for ohmic contacts to III-nitrides. It has been used as a diffusion barrier between Al and Au [148], and together with Ti at the bottom of the metal stack [149]. In a patent application by Kanamura et al [150] a Ta/Al-based scheme for ohmic contact formation was proposed. This metallization has also been used previously on n-GaN in [151], and to AlGaN in [152]. The contact mechanism of Ta-based contacts is believed to be similar to that of the Ti-based contact, since TaN has been identified at the interface [153]. A potential disadvantage of using the Ta/Al metallization scheme is that TaN has a larger  $\Phi_b$  (> 4 eV) than TiN [143].

A thorough investigation of Ta/Al as an alternative to Ti/Al was made in [A]. Planar contacts were formed on two AlGaN-based heterostructures, with Al mole fractions of 0.14 and 0.25, respectively. Optimization of the metal layer stack in terms of thicknesses and cap layers was performed, as well as of the anneal temperature and duration. From the discussion on  $\Phi_b$  above it follows that a low R<sub>c</sub> should be more easily obtained on the material with the low Al mole fraction. Indeed, the contacts on this material exhibited a very low  $R_c$  below < 0.1  $\Omega$ mm. Due to the lack of reported results for contacts fabricated on AlGaN/GaN with a similarly low Al mole fraction, it is difficult to make a comparison with the literature. The minimum  $R_c$  of the epi with the higher barrier Al mole fraction was 0.28  $\Omega$ mm, which is in line with what is commonly seen for Ti-based contacts on comparable heterostructures [132][154].

Capping the stack with Au and an interlayer of Ni or Ta like in conventional ohmic contacts generally led to a higher  $R_c$  and a reduced process window in terms of the thickness of the Al layer. TEM/EDX analysis indicated a high level of interdiffusion between the metals, resulting in Ni and Au near the interface, which likely explains the results. A plain Ta/Al/Ta stack on the other hand led to a considerable improvement. The scheme has an  $R_{sh}$  of around 0.5  $\Omega/\Box$ , as measured on test structures. Thereby the contact metal itself constitutes a very small part of the measured  $R_c$ .

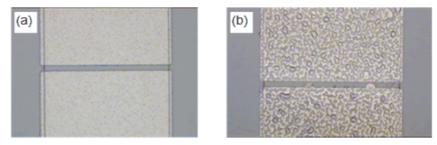

A striking feature of the Ta-based contact is the low optimum anneal temperature of 550 - 575 °C. The absence of Au combined with the low anneal temperature resulted in a very smooth surface morphology. The Ta/Al/Ta metallization has shown to be compatible with early passivation [78], [155]. Fig. 3-7 shows AlGaN/GaN samples with ohmic contacts formed after the deposition- and opening of a SiN<sub>x</sub> passivation layer. The samples were metallized with Ta/Al/Ta and Ti/Al/Ni/Au schemes and annealed at 550 and 830 °C, respectively. As can be seen, the rough morphology of the Ti-based contact has severe consequences for the edge acuity.

Fig. 3-7. Ohmic contacts separated by 3  $\mu$ m, processed after the deposition and opening of a SiN passivation layer. a) A Ta/Al/Ta contact annealed at 550 °C and b) a Ti/Al/Ni/Au contact annealed at 830 °C.

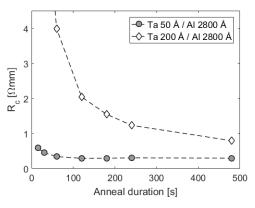

The evolution of  $R_c$  versus anneal duration in [A] shows that the process saturates, with no risk for over-annealing. This opens for a sequential anneal process, interrupted when the contact resistance is no longer decreasing. For a thin bottom Ta layer,  $R_c$  saturates faster, which can be seen in Fig. 3-8, comparing two contacts with Ta thicknesses of 50 and 200 Å, respectively. This could indicate that Al near the interface promotes the contact formation. The Ta/Al/Ta scheme has shown as well to produce good ohmic contacts to InAl(Ga)N/GaN. It was further investigated in [B] combined with recess etching and was utilized as well in [C-F].

Fig. 3-8. Development of  $R_c$  versus time for two different thicknesses of the bottom Ta layer [A].

#### 3.1.3 Recess etching

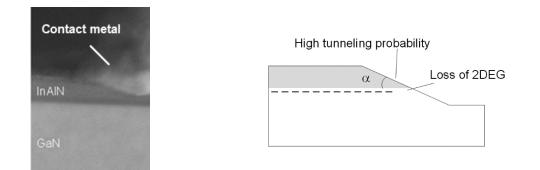

Recess etching provides a way to circumvent the limitations imposed by a high  $\Phi_b$ , since it enables the contact to be formed with a reduced barrier thickness (enhancing tunneling probability), or at the sidewall of the trench, in close proximity to the 2DEG. It has been shown that recessed contacts can reduce  $R_c$  compared to planar contacts [113], and the target  $R_c$  is often in the 0.15 – 0.3  $\Omega$ mm range [156][157]. On the other hand, repeatability is a greater challenge for recessed contacts due to the introduction of more parameters, such as recess depth, sidewall angle, resist hardiness, and etching damage. The recessing is performed by dry-etching, often in a Cl<sub>2</sub> or Cl<sub>2</sub>/BCl<sub>3</sub> plasma [156], [158], but the more mechanical bombardment by Ar sputtering has also been suggested [159]. Full consensus on the optimum recess depth has not been reached. Previous studies have reported scattered results. A minimum  $R_c$  was found by etching part way through the barrier [113], while the complete removal of the barrier provided the best results in [117].

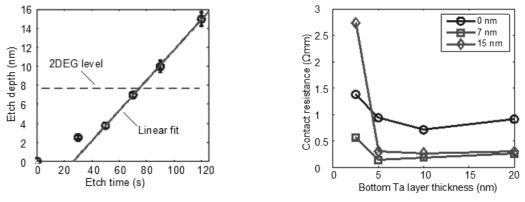

In this work, recessing was performed by the combined inductively couple plasma etching (ICP) and reactive ion etching (RIE) in a Cl<sub>2</sub>/Ar-based plasma. Descumming in a low-power oxygen plasma and subsequent oxide stripping in diluted HCl prior to metallization was performed in order to remove any etching products and superficial oxide. In [B], the Ta/Al/Ta metallization was applied to recess etched contact areas of an InAlN/AlN/GaN heterostructure, with a primary focus of optimizing the recess depth. Recess etching for 5 different durations was performed, spanning a recess depth from 0 (planar contacts) to beyond the 2DEG (8 nm below the surface), see Fig. 3-9. The optimum level was found if etching was interrupted just above the 2DEG, with approximately 1 nm of AlN remaining. At this level, there is presumably still a 2DEG in the recessed region due to the high polarization of AlN. Reduced sensitivity to other parameters such as the bottom Ta layer thickness was observed at the optimum etch depth, A minimum contact resistance was  $0.14 \ \Omega$ mm was obtained.

Fig. 3-9. Recess depth versus etch time [B].

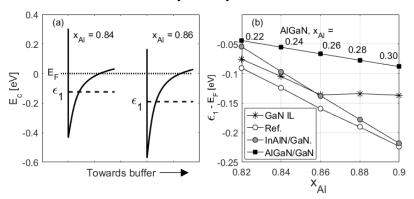

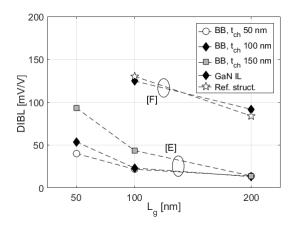

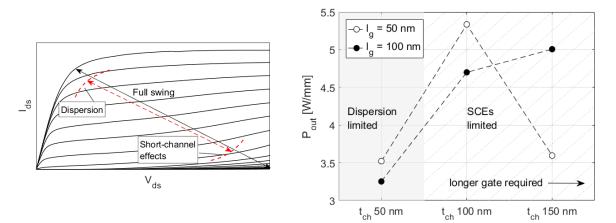

Fig. 3-10. Contact resistance versus bottom Ta layer thickness for three different etch depths [B].