## Rapid Digital Architecture Design of Computationally Complex Algorithms

A Dissertation Accepted by the Faculty of Physics and Electrical Engineering of the University of Bremen in Partial Fulfilment of the Requirements for the Degree of

DOKTOR-INGENIEUR (Dr.-Ing.)

By

Benjamin Andreas Knoop

Referee: Prof. Dr.-Ing. Steffen Paul

Co-Referee: Prof. Dr. Sc. Techn. Andreas Burg 3<sup>rd</sup> Examiner: Prof. Dr.-Ing. Alberto García-Ortiz 4<sup>th</sup> Examiner: Prof. Dr. Angelika Bunse-Gerstner

Date of Dissertation: June 15, 2018 Date of Colloquium: February 7, 2019

## **Summary**

The growing availability of computing power allows for the implementation of algorithms of increasing computational complexity. While this is definitely true for general purpose computers, this also applies to the very-large-scale integration (VLSI) design targeting Field-Programmable Gate Arrays (FPGAs). Yet, traditional digital design techniques hardly keep up with the pace of technological advancements and the rising abundance of programmable circuitry found on such devices.

To this end, this work presents the novel Rapid Data Type-Agnostic Digital Design Methodology (RDAM) to elevate the design perspective of digital design engineers away from the register-transfer level to a higher level of abstraction—the algorithmic level. The proposed methodology is founded on the enormous capabilities of High-Level Synthesis (HLS), which basically is a synthesis step to compile concurrently operating VLSI architectures from sequentially coded algorithms specified, e.g., in C++. By consequently working with data type-agnostic source codes, the RDAM brings significant simplifications to the fixed-point conversion of algorithms and the creation of complex-valued arithmetic.

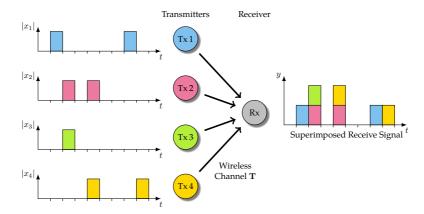

Throughout this dissertation, signal processing applications from the field of Compressed Sensing (CS) will illustrate the efficacy of the RDAM. Algorithmic modifications and improvements are described to incorporate the notion of sparse-coded signals and their recovery in the context of multi-user wireless communications in a wireless sensor network. For instance, a complex-valued digital architecture for the Orthogonal Matching Pursuit (OMP) algorithm with rank-1 updating has successfully been implemented and tested, which can be utilised for the combined multi-user wireless channel estimation and activity detection of sporadically transmitting sensor nodes. Further, sparsity-regularised tree search algorithms will be examined as well as the multi-user data frame detection with a priori unknown user activities based on specifically designed user codes derived from Zadoff–Chu sequences.

## Zusammenfassung

Die zunehmende Verfügbarkeit von Rechenleistung erlaubt die Implementierung von immer rechenintensiveren Algorithmen. Dies trifft sicherlich auf Rechner im Allgemeinen zu, doch ebenso auch auf den Very-Large-Scale-Integration (VLSI) Entwurf für Field-Programmable Gate Arrays (FPGAs). Jedoch können traditionelle Entwurfsmethoden kaum Schritt halten mit der Geschwindigkeit technologischen Fortschritts und der weiter wachsenden Verfügbarkeit von programmierbarer Logik, die solche Chips bieten.

Diese Arbeit präsentiert als Antwort darauf die Rapid Data Type-Agnostic Digital Design Methodology (RDAM), um den Digitalentwurf von der Register-Transfer-Ebene weg auf ein höheres Abstraktionsniveau anzuheben – der algorithmischen Ebene. Die vorgeschlagene Methodik ist auf der Leistungsfähigkeit von High-Level Synthesis (HLS) gegründet, was prinzipiell einen Syntheseschritt darstellt, der aus einem sequentiell programmierten Algorithmus, z.B. mit C++, eine nebenläufige VLSI-Architektur kompiliert. Aufgrund konsequent datentyp-agnostischer Quellcodes führt die RDAM zu deutlichen Vereinfachungen bei der Fest-kommaarithmetik als auch bei komplexwertigen Berechnungen.

Signalverarbeitungsapplikationen aus dem Bereich des Compressed Sensings (CS) dienen als Beispiel um die Effektivität der RDAM zu demonstrieren. Algorithmische Anpassungen und Verbesserungen binden Ideen zur Mehrnutzer-Detektion dünn besetzter Signale in drahtlosen Sensornetzwerken ein. Beispielsweise wurde eine komplexwertige Architektur für Orthogonal Matching Pursuit (OMP) mit Rank-1 Updates erfolgreich implementiert und getestet, die zur gemeinsamen Schätzung von Nutzerkanälen und der Aktivität sporadisch sendender Sensorknoten herangezogen werden kann. Außerdem werden Baumsuchverfahren untersucht, sowie eine Mehrnutzer-Rahmendetektion mit a priori unbekannten Nutzeraktivitäten basierend auf speziell entworfenen Zadoff-Chu-Sequenzen.

### Acknowledgments

There are many persons who influenced and supported this work, whose contributions I would like to acknowledge gratefully.

To begin with, I would like to thank my doctorate thesis supervisor Prof. Dr.-Ing. Steffen Paul (Institute of Electrodynamics and Microelectronics, University of Bremen). His interest in my person and abilities, as early as during my undergraduate studies, set me on the way towards this dissertation, and he generously provided continuous funding for my employment as a research assistant and all the journeys to national and international conferences. What is more, he consistently left enough room to follow one's own scientific creativity.

I would also like to thank Prof. Dr. Sc. Techn. Andreas Burg (École Polytechnique Fédérale de Lausanne) for his outright willingness to serve as an external reviewer of this thesis. With or without knowing him, his scientific work influenced mine beginning with my Diploma thesis, supervised by Dr.-Ing. Till Wiegand. His keen interest in optimised hardware architectures for algorithms such as Sphere Decoding, K-Best detection or Orthogonal Matching Pursuit will find more than one parallel on the pages to come.

My thanks also go to my long-standing office colleague, the soon-tobecome Dr.-Ing. Sebastian Schmale. I enjoyed our time together, experiencing the ups and downs of being doctorate students, and I happily like to look back on our journeys to scientific conferences and the frequent discussions we have had. We certainly share our passion for signal processing algorithms.

Similar things can be said with regard to our postdoc, Dr.-Ing. Jochen Rust. He supported me with his digital design expertise, e.g. relating to the Logarithmic Number System, and I feel that a deep professional relationship has grown over time and during countless discussions accompanied by not only one mug of coffee.

Furthermore, I would like to thank Dr.-Ing. Carsten Bockelmann and Dr.-Ing. Fabian Monsees of the Department of Communications Engineering for the many helpful insights and joint project work.

I would also like to pay tribute to the contributions of all the students listed at the end of this dissertation, who investigated and implemented things I could not find time for.

However, special thanks must be awarded to my family, wife and children, for supporting me throughout this project and especially during the final stages of writing this document.

## **Contents**

| Sı | ımma | ary     |                                               | iii |

|----|------|---------|-----------------------------------------------|-----|

| 1  | Intr | oductio | on and Motivation                             | 1   |

|    | 1.1  | Contr   | ributions to the State of the Art             | 4   |

|    |      | 1.1.1   | Digital Architecture Design                   | 4   |

|    |      | 1.1.2   | Compressed Sensing in Wireless Communications | 5   |

|    | 1.2  |         | ne                                            | 6   |

| I  | Ra   | noid E  | Digital Architecture Design Based on          |     |

|    |      | -       | evel Synthesis (HLS)                          | 9   |

| 2  | Fun  | damen   | tals of High-Level Synthesis                  | 11  |

|    | 2.1  |         | asing Design Complexity as a Driver for HLS   | 11  |

|    |      | 2.1.1   |                                               | 12  |

|    |      |         | 2.1.1.1 Computational Complexity              | 12  |

|    |      |         | 2.1.1.2 Algorithmic Complexity                | 13  |

|    |      |         | 2.1.1.3 Mathematical Complexity               | 14  |

|    |      | 2.1.2   |                                               | 15  |

|    |      |         | 2.1.2.1 Design Entropy                        | 16  |

|    | 2.2  | A Sho   | ort Historical Review                         | 16  |

|    |      | 2.2.1   | Contemporary Developments                     | 17  |

|    | 2.3  | The B   | asic Principles of HLS                        | 18  |

|    |      | 2.3.1   |                                               | 19  |

|    |      |         | 2.3.1.1 Coding Style Guidelines               | 20  |

|    |      |         | 2.3.1.2 Directives for Architecture Design    | 22  |

|    |      | 2.3.2   | <u> </u>                                      | 24  |

|    |      | 2.3.3   |                                               | 25  |

|    | 2.4  | Alteri  | native Digital Design Techniques              | 28  |

|    |      | 2.4.1   | Hardware Description Languages                | 28  |

|    |      | 2.4.2   | Graphical Programming Languages               | 29  |

|   | 2.5 | An Ov<br>2.5.1<br>2.5.2 | verview of Current HLS Tools                   | 30<br>32<br>33 |

|---|-----|-------------------------|------------------------------------------------|----------------|

| 3 | The | Rapid                   | Data Type-Agnostic Digital Design              |                |

|   |     |                         | ogy (RDAM)                                     | 35             |

|   | 3.1 |                         | st Observation on Algorithm Development        | 35             |

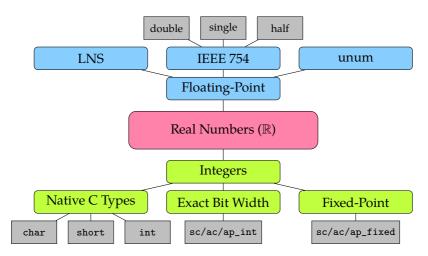

|   | 3.2 |                         | y Number Systems and Their Deficiencies        | 36             |

|   |     | 3.2.1                   | •                                              | 36             |

|   |     |                         | 3.2.1.1 The IEEE Standard 754                  | 38             |

|   |     |                         | 3.2.1.2 The Universal Number Format            | 41             |

|   |     |                         | 3.2.1.3 The Logarithmic Number System          | 43             |

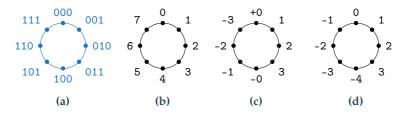

|   |     | 3.2.2                   | Integer and Fixed-Point Numbers                | 44             |

|   |     |                         | 3.2.2.1 Properties of Fixed-Point Numbers      | 46             |

|   |     |                         | 3.2.2.2 The Q Format                           | 48             |

|   |     | 3.2.3                   | Discussion                                     | 50             |

|   | 3.3 | The P                   | rincipal Idea of the RDAM                      | 51             |

|   |     | 3.3.1                   | Advantages                                     | 52             |

|   |     | 3.3.2                   | Augmented Design Space Exploration             | 53             |

|   |     | 3.3.3                   | Prerequisites and Limitations                  | 55             |

|   |     |                         | 3.3.3.1 Prior Algorithmic Transformations      | 56             |

|   |     |                         | 3.3.3.2 The Subset of Synthesisable Code       | 57             |

|   | 3.4 | Metho                   | odological Design Flow                         | 57             |

| 4 | Dat | . T                     | A amosticism for High Level Crypthesis         | 59             |

| ± | 4.1 |                         | Agnosticism for High-Level Synthesis           | 60             |

|   | 4.1 | 4.1.1                   | Example Source Codes                           | 60             |

|   |     | 4.1.1                   | Employed C++ Mechanisms                        | 61             |

|   | 4.2 |                         | application to Complex-Valued Designs          | 64             |

|   | 4.3 |                         | Abstraction of Fixed-Point Design              | 65             |

|   | 1.0 | 4.3.1                   | Unavoidable Manual Intervention                | 66             |

|   |     | 4.3.2                   | Quick Test-Driven Dimensioning of the          | 00             |

|   |     | 1.0.2                   | Fixed-Point Word Lengths                       | 67             |

|   | 4.4 | Funct                   | ion Approximations to Improve HLS Results      | 68             |

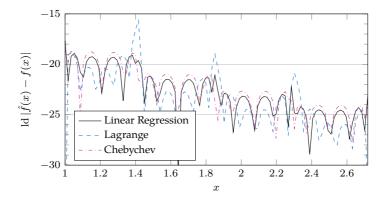

|   |     | 4.4.1                   | Polynomial Function Approximation              | 69             |

|   |     | 4.4.2                   | Piecewise-Linear Function Approximation        | 71             |

|   |     | 4.4.3                   | Application of the Logarithmic Number System . | 72             |

| 5  | <b>Des</b> i 5.1 |          |             | th the RDAM                              | <b>75</b> 75 |

|----|------------------|----------|-------------|------------------------------------------|--------------|

|    |                  | 5.1.1    | The Algo    | orithm                                   | 76           |

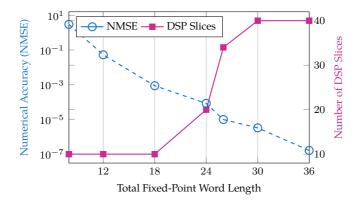

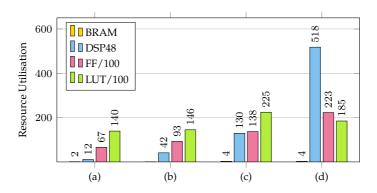

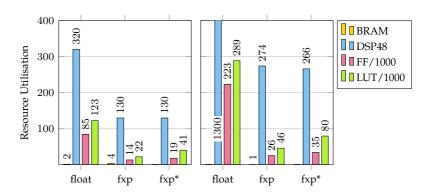

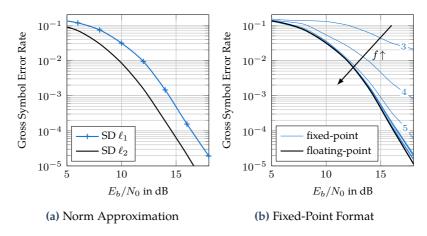

|    |                  | 5.1.2    | Design S    | pace Exploration with Various Data Types | 76           |

|    |                  |          | 5.1.2.1     | Discussion of the Synthesis Results      | 77           |

|    | 5.2              | Examp    | ole 2: Orth | nogonal Matching Pursuit – A             |              |

|    |                  | Comp     | utationall  | y Complex Algorithm                      | 81           |

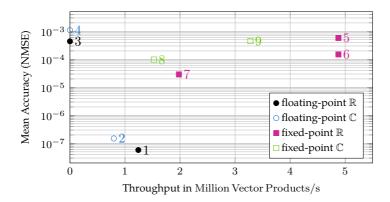

|    |                  | 5.2.1    | A Survey    | y of Related Works                       | 82           |

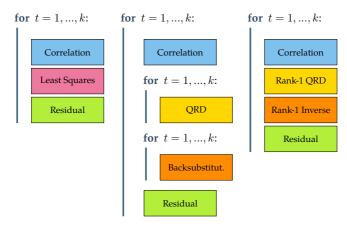

|    |                  | 5.2.2    |             | mic Transformation with Rank-1 Updating  | 86           |

|    |                  | 5.2.3    | High-Le     | vel Synthesis Results                    | 90           |

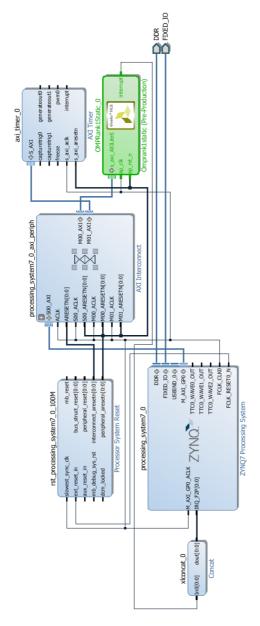

|    |                  | 5.2.4    | System-c    | on-Chip Integration and Testing          | 92           |

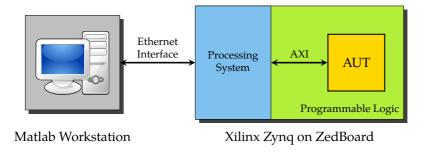

|    |                  |          | 5.2.4.1     | Ethernet-Based Hardware-in-the-Loop      |              |

|    |                  |          |             | Simulations with Matlab                  | 94           |

|    |                  |          | 5.2.4.2     | Hardware Overlay for Xilinx PYNQ         | 96           |

|    |                  |          |             |                                          |              |

| II | Co               | mpres    | ssed Ser    | nsing (CS) Multi-User Wireless           |              |

|    |                  | _        | nication    |                                          | 99           |

|    |                  |          | incution    |                                          |              |

| 6  | Prin             | ciples o | of Compr    | essed Sensing                            | 101          |

|    | 6.1              | The C    | S Framew    | ork                                      | 102          |

|    |                  | 6.1.1    | Sparsity    | and Transform Coding                     | 102          |

|    |                  | 6.1.2    |             | surement Matrix                          | 103          |

|    |                  | 6.1.3    | The CS S    | System Model                             | 104          |

|    |                  | 6.1.4    |             | ecovery                                  | 106          |

|    | 6.2              | Algori   | thms for (  | CS Signal Recovery                       | 107          |

|    |                  | 6.2.1    | Convex 0    | Optimisation Solvers                     | 107          |

|    |                  | 6.2.2    | Greedy A    | Algorithms                               | 109          |

|    |                  | 6.2.3    | Threshol    | ding Algorithms                          | 110          |

|    |                  | 6.2.4    |             | on                                       | 112          |

|    | 6.3              |          |             | of CS to Wireless Communications         | 114          |

|    |                  | 6.3.1    |             |                                          | 114          |

|    |                  | 6.3.2    |             | oduction of Artificial Sparsity          | 115          |

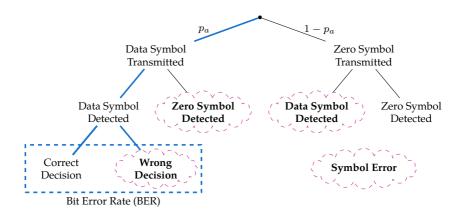

|    |                  | 0.0.2    | 6.3.2.1     | User Activity Probabilities              | 116          |

|    |                  | 6.3.3    |             | «-Valued CS                              | 118          |

|    |                  | 2.2.2    | 6.3.3.1     | Block-Wise Real-Value Decomposition .    | 119          |

|    |                  |          | 6.3.3.2     | Element-Wise Real-Value Decomposition    | 120          |

|    |                  |          |             | in the second solution                   |              |

|   |      | 6.3.4<br>6.3.5 | CDMA for Multi-User Communications The CS Estimation Problem | 121<br>123 |

|---|------|----------------|--------------------------------------------------------------|------------|

|   |      |                | 6.3.5.1 The Finite-Alphabet Constraint                       | 125        |

| 7 |      |                | ware Symbol Detection with Tree Search                       |            |

|   | Alg  |                | s                                                            | 127        |

|   | 7.1  | Joint I        | Data and Activity Detection                                  | 128        |

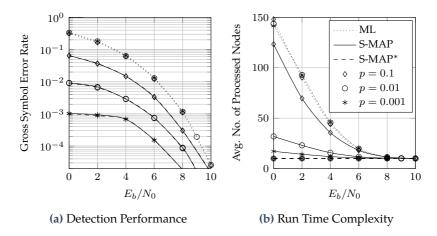

|   |      | 7.1.1          | J                                                            | 130        |

|   | 7.2  |                | ity-Regularised Tree Search Algorithms                       | 131        |

|   |      | 7.2.1          | Sphere Decoding                                              | 131        |

|   |      |                | 7.2.1.1 Mode of Operation                                    | 132        |

|   |      |                | 7.2.1.2 An RDAM-Based Sphere Detector                        | 134        |

|   |      |                | 7.2.1.3 Sparsity-MAP Run Time Complexity                     | 137        |

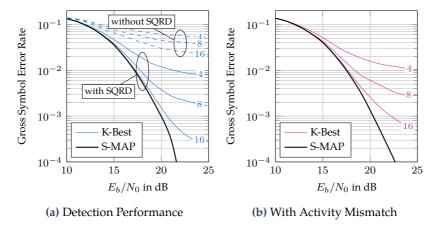

|   |      | 7.2.2          | K-Best Detection                                             | 139        |

|   |      |                | 7.2.2.1 Pre-Processing Steps                                 | 139        |

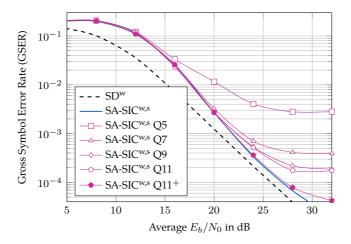

|   |      |                | 7.2.2.2 Numerical Simulation Results                         | 140        |

|   |      |                | 7.2.2.3 Complexity Analysis                                  | 141        |

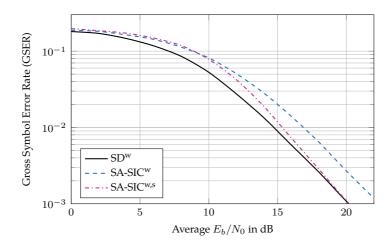

|   |      | 7.2.3          | Successive Interference Cancellation                         | 142        |

|   |      |                | 7.2.3.1 Combined Sorting and Pre-Whitening .                 | 142        |

|   |      |                | 7.2.3.2 Detection Performance                                | 144        |

|   | 7.3  | Discu          | ssion                                                        | 147        |

| 8 | Join |                | i-User Activity and Channel Estimation                       | 149        |

|   | 8.1  | Syster         | m Model                                                      | 150        |

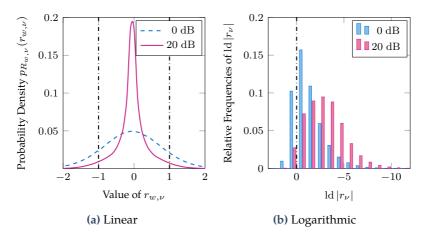

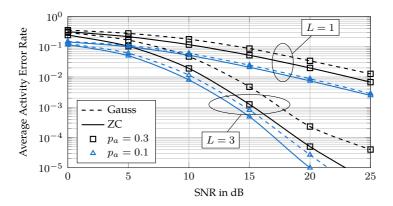

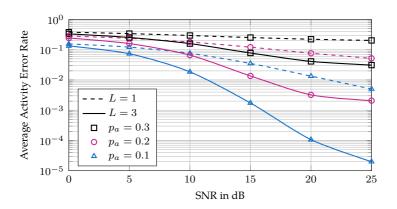

|   |      | 8.1.1          | Zadoff–Chu Sequences as Pilots                               | 152        |

|   | 8.2  |                | ng the Estimation Problem with Block Orthogonal              |            |

|   |      |                | ning Pursuit                                                 | 154        |

|   |      | 8.2.1          | 1 )                                                          | 154        |

|   |      | 8.2.2          |                                                              | 155        |

|   |      | 8.2.3          |                                                              | 156        |

|   | 8.3  | Extens         | sion to Multi-User Frame Synchronisation                     | 159        |

|   |      | 8.3.1          | Neyman–Pearson Detection                                     | 160        |

|   |      | 8.3.2          | RDAM-Based Implementation                                    | 162        |

|   | 8.4  | Discu          | ssion                                                        | 165        |

| 9 | Con  |                | n and Open Research Issues                                   | 167        |

|   | 9.1  |                | DAM                                                          | 167        |

|   | 9.2  | Sparse         | e-Coded Multi-User Communications                            | 169        |

| 9.3 Open Issues for Future Research                                                                                                                                                                                                          | 170                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Appendix A Fixed-Point Arithmetic with the Q Format  A.1 Format Changes Due to Arithmetic Operations  A.1.1 Addition and Subtraction  A.1.2 Repeated Accumulation  A.1.3 Multiplication  A.1.4 Reciprocal  A.1.5 Division  A.1.6 Square Root | 173<br>174<br>175<br>175<br>176<br>177 |

| List of Figures                                                                                                                                                                                                                              | 179                                    |

| List of Tables                                                                                                                                                                                                                               | 183                                    |

| List of Code Listings                                                                                                                                                                                                                        | 185                                    |

| List of Algorithms                                                                                                                                                                                                                           | 187                                    |

| Acronyms and Abbreviations                                                                                                                                                                                                                   | 189                                    |

| Mathematical Notations and Symbols                                                                                                                                                                                                           | 195                                    |

| Supervised Student Work                                                                                                                                                                                                                      | 203                                    |

| Publication List                                                                                                                                                                                                                             | 207                                    |

| Bibliography                                                                                                                                                                                                                                 | 211                                    |

## Chapter 1

### **Introduction and Motivation**

Technological advancements in wireless communications in conjunction with the increased availability of computing power lead to profound changes in how things and human beings communicate with each other. While mobile radio networks and mobile phones can already be found almost everywhere on this globe, the number of communicating machines is on the rise. This development is best described by concepts like the Internet of Things (IoT) or Industry 4.0 [AIF+15; DH14].

However, the anticipated artificially intelligent, autonomously acting and self-organising applications exhibit a principally different communication behaviour, called Machine-Type Communications (MTC), which requires to re-think existing wireless communication schemes and networks.

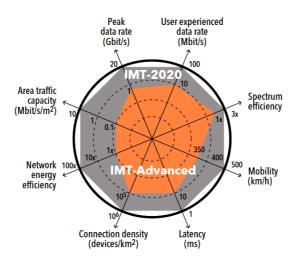

Currently, efforts are made, therefore, to standardise the future fifth generation of digital mobile networks (5G), also known as IMT-2020 by the International Telecommunication Union (ITU) [BB17; 3GPP18]. It shall encompass and support at least three different usage scenarios: massive MTC, ultra-reliable low-latency communications and classical mobile broadband services for human users. A couple of disruptive technologies are being proposed to achieve this goal, e.g. millimetre waves together with small cells, or very large multi-antenna multiple-input multiple-output (MIMO) systems (also called Massive MIMO) together with beam forming [And+14; Boc+14]. This will eventually lead to an improved performance by an order of magnitude for link latency, single user data throughput or the number of devices per area (see Fig. 1.1).

The enhanced bandwidth efficiency and flexibility to accommodate various types of communication services naturally and inevitably result in higher design complexity with regard to the signal processing algorithms

**Figure 1.1:** The expected enhancement of key capabilities of 5G mobile networks (IMT-2020) in comparison to LTE-Advanced (IMT-Advanced) [BB17].

and digital hardware resources needed to enable such high-tech mobile networks in the first place—the complexity increase from one generation to another is a factor of about ten as [HJ09] observes.

Another area completely unrelated to wireless communications where computationally complex algorithms are typically to be encountered are data centres for cloud services offering machine learning with deep neural networks or big data analytics [HM17]. Recently, Field-Programmable Gate Arrays (FPGAs) have become employed in vast numbers in such computing centres as a substantial workforce to speed up computations.

With potent digital circuitry on the one hand, and complex digital signal processing algorithms and applications on the other hand, two worlds come together here.

FPGAs are digital logic devices which operate inherently parallel and concurrently; their programming follows the paradigm of digital hardware design, traditionally with specialised hardware description languages (HDLs), namely VHDL and Verilog. In contrast, software to implement algorithms is usually written with high-level languages (HLLs),

e.g. C/C++, which are sequential in nature. The OpenCL framework, for instance, tries to exploit parallelisms and target heterogeneous computing systems such as graphics processing units (GPUs) or even FPGAs in addition to central processing units (CPUs) [Khr17]. Major FPGA vendors hence are eager to deploy tools for an easy transition from OpenCL to HDL code.

In fact, there is quite a powerful concept involved between the two antipodes of "software" and "hardware": High-Level Synthesis (HLS). HLS denotes the automatic generation or compilation of HDL code from an HLL description. All commercially successful and functionally mature tools support the family of C languages, i.e. C/C++ with support for SystemC, to be precise.

This thesis, therefore, investigates how the capabilities of HLS can be utilised for the creation of sophisticated digital architectures for complex signal processing applications. It consists of two parts, as indicated by its title "Rapid Digital Architecture Design of Computationally Complex Algorithms":

- Firstly, a novel design methodology, called the Rapid Data Type-Agnostic Digital Design Methodology (RDAM), is proposed. It accelerates digital design time and achieves great simplifications with regard to the fixed-point conversion of algorithms and the implementation of complex-valued operations. For instance, one baseline fixed-point format can be applied throughout a digital architecture, which is a rather astonishing result.

- And secondly, a wireless communications scenario supplies examples for computationally complex algorithms. It touches the aforementioned topics such as IoT, Industry 4.0 or 5G. The assumed communication system is a wireless sensor network (WSN) with sporadically active sensor devices (or "users"), which exhibit MTC behaviour. Ideas from the Compressed Sensing (CS) theory are incorporated for a cross-layer optimisation to avoid signalling overhead concerning user activities on higher layers of the protocol stack. This in turn, however, requires the execution of rather complex algorithms for signal recovery.

### 1.1 Contributions to the State of the Art

Both parts of this thesis contain original contributions to the state of the art in their respective fields of study.

### 1.1.1 Digital Architecture Design

The aforementioned observable increase in computational complexity challenges traditional digital design flows. The technological evolution and transistor integration densities scale quite well to accommodate this growth in complexity, but the design capabilities of hardware engineers do not, which is known as the productivity design gap [MS13].

One answer to this challenge certainly is HLS, which accelerates digital architecture design by allowing hardware engineers to work on a higher level of abstraction [Cou^+09]. Instead of describing digital logic on the behavioural register-transfer level (RTL), HLS elevates hardware design to the algorithmic layer of the Gajski–Kuhn chart [GK83]. HLS is especially well-suited for FPGAs as target devices, because they allow for fast design and test cycles. Its capability to create even complicated architectures has already been demonstrated [Con^+11]. And to cite another example, an application-specific integrated circuit (ASIC) developed with HLS for the pre-coding and detection in a  $128\times 8$  Massive MIMO system has been reported on in [Pra17].

This thesis introduces a novel design technique called the Rapid Data Type-Agnostic Digital Design Methodology (RDAM), which drives design abstraction even further by requiring data type-agnostic HLS design entry source codes written in C++ to leverage the polymorphism of that programming language. The concept of data type agnosticism (DTA) itself is not new and has been applied by the Mathworks Fixed-Point Designer for Matlab to switch between normal computations and fixed-point operation, with fixed-point objects being substituted for the default double-precision floating-point data type; no code modifications are needed. And following a different line of reasoning, namely to optimise synthesis results, the HLS tutorial of Xilinx mentions that standard C types can be updated in favour of specialised fixed-point types, requiring some code modifications [Xil-UG871].

These elementary ideas are brought together by the RDAM which produces a synergistic effect. Firstly, it eases fixed-point design and the conversion of algorithms to fixed-point arithmetic, especially with regard to the proper sizing of the finite word lengths. Secondly, it also applies to complex-valued algorithms and can map these to digital logic without any additional manual design steps.

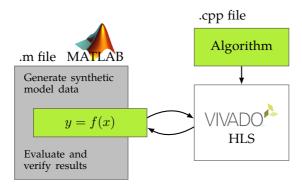

The RDAM has been described for the first time in [Kno<sup>+</sup>16c], where Mathworks Matlab and Xilinx' HLS tool are additionally linked with each other to allow for semi-automatic parametric sweeps to explore the design space. That work also presents, to the best knowledge of the author, the first digital design of the Approximate Conjugate Gradient Pursuit (ACGP) algorithm [BDR12].

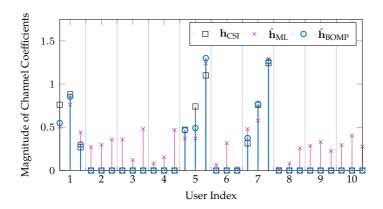

The RDAM was also applied to the well-known Orthogonal Matching Pursuit (OMP), [TG07]. The resulting digital design is compared with other architectures taken from the literature [Kno<sup>+</sup>16a]. Furthermore, rank updates to the QR matrix decomposition (QRD) as well as the Moore–Penrose pseudoinverse were proposed to solve the least squares (LS) optimisation problem within OMP. To the best knowledge of the author, [Kno<sup>+</sup>16a] presents the first complex-valued digital architecture for OMP as an important benefit of the RDAM.

### 1.1.2 Compressed Sensing in Wireless Communications

Following up on the seminal work of Candès, Donoho and others, Compressed Sensing (CS) gained much attention in the signal processing community [CT05a; Don06]. Basically, CS allows for the sub-sampling of a signal below the classical Nyquist–Shannon sampling rate, if and only if the signal of interest is sparse, either directly or in some basis transform domain, e.g. the frequency domain. Hence, it was proposed to incorporate the CS framework into communication applications where sparsity is present, e.g. to exploit sporadic user activities in WSNs to facilitate a joint activity and data estimation [TLL09].

In this work, three closely related tree search algorithms are modified according to the CS sparsity constraint and explored with regard to their detection performance. Results for optimal sparsity-aware Sphere Decoding (SD) have been reported in [KWP12] and a digital design thereof has been published in [Kno<sup>+</sup>17]. The observed run time behaviour of the constrained algorithm led to the exploration of sparsity-aware Successive Interference Cancellation (SIC) detection in [Kno<sup>+</sup>13]. The novel combination of SIC detection with Sorted QRD (SQRD), as it had been invented

for the improved performance in multi-antenna MIMO communication systems [Wüb $^+$ 01], exhibits almost optimal detection performance. Alternatively, the constrained K-Best algorithm was investigated in [Kno $^+$ 14], which constitutes a hardware-friendly trade-off between SIC and SD.

However, it became obvious that, for a practical technology demonstration with Software-Defined Radios (SDRs), the assumed sparsity within the communication system can already (and needs to) be exploited during user-specific channel equalisation [Kno $^+$ 16b]. The cited work, therefore, successfully applies OMP to the derived channel state information (CSI) estimation problem.

Furthermore, the sparse activity pattern of the users in the WSN has direct impact on the frame synchronisation of the received superimposed data frames of the active users. This was investigated in [Zed+17], wherein a special multi-user synchronisation preamble is proposed. This preamble is based on Zadoff–Chu sequences (ZCSs) and utilises their ideal cyclic autocorrelation property to construct an orthogonal basis of user-specific codes.

Starting with an idea for joint activity and symbol detection at the end of the baseband signal processing chain of an (uncoded) digital wireless transceiver, the above summarised incremental research steps brought the notion of sparsity closer to the radio frequency (RF) front-end and within reach for a practical implementation.

### 1.2 Outline

The following chapters are grouped into two parts, according to the two areas of research this thesis contributes to.

The first part describes the fundamentals to motivate and explain the novel RDAM in detail:

- Chapter 2 clarifies terminology with regard to "complexity" and gives a brief introduction to contemporary HLS and how it evolved. Alternative digital design techniques are compared and current HLS tools examined for their support of the RDAM.

- Chapter 3 surveys various common data types for digital signal processing applications and explains why data types can be abstracted in general. Furthermore, the principal advantages and limitations

- of the RDAM are discussed. Its climax surely is Sec. 3.4, which lists the necessary methodological design steps belonging to the RDAM.

- Chapter 4 describes the DTA and gives an in-depth illustration thereof. It is further discussed how the RDAM applies to complexvalued algorithms and how it abstracts and simplifies fixed-point arithmetic. The chapter concludes with a section on function approximation to obtain optimised (fixed-point) HLS compilation results for the implementation of mathematically complicated functions, e.g. the square root or logarithm.

- Chapter 5 at the end of Part I lists and discusses synthesis results for two design examples: a simple scalar vector product and OMP, representing a computationally complex algorithm. It concludes with a hardware-in-the-loop (HIL) simulation and embedded test of the devised architectures.

### Part II deals with CS and sparse coding in a WSN:

- Chapter 6 summarises the theoretical foundations of CS and explains the two steps involved: compressive measurement and reconstruction. A survey of algorithms for sparse signal recovery is given. Afterwards, in Sec. 6.3, the CS framework is applied to digital communication systems with regard to their particular constraints. A multi-user uplink in a WSN is described as a baseline system model for the chapters to come.

- Chapter 7 presents sparsity-constrained tree search algorithms, namely SD, K-Best and SIC, and evaluates their performance for joint user activity and data detection.

- Chapter 8 shifts the attention to combined multi-user wireless channel and user activity estimation. An extended system model with data frames is introduced to enable channel estimation and timing synchronisation at the receiver, which takes sporadic activities of the users into account.

Chapter 9 finally summarises and concludes this thesis.

### Part I

## Rapid Digital Architecture Design Based on High-Level Synthesis

## **Chapter 2**

# Fundamentals of High-Level Synthesis (HLS)

The Rapid Data Type-Agnostic Digital Design Methodology (RDAM), which forms the essence of this work, is founded on the power of High-Level Synthesis (HLS) tools.

The following therefore briefly sketches the idea of HLS before the advantages and disadvantages of the added DTA are discussed in the next chapter. This chapter furthermore motivates the need for an elevated digital design perspective and also discusses some alternatives to HLS. It will conclude with an overview of contemporary commercial and academic HLS design tools.

# 2.1 Increasing Design Complexity as a Driver for High-Level Synthesis

The design of faster and more bandwidth-efficient communication systems goes hand in hand with the development of more than ever sophisticated signal processing algorithms. This has direct impact on the quantity of needed hardware resources for practical implementations. For ASIC designs this translates to silicon area and for FPGA designs to the number of utilised logic cells to create adders, multipliers, etc.

As [HJ09] formulates it, "the tremendous complexity increase from one technology generation to its successor...is roughly a factor of ten [in wireless communications,] while time-to-market has to be preserved for the sake of competitiveness." This statement directly addresses the central problem which has to be solved—to increase design productivity and

thereby enable digital hardware designs for complex signal processing applications.

Before that can be elaborated in detail, it must be explained what exactly "complex" digital architectures and algorithms are.

### 2.1.1 The Definition of Complexity

The word "complexity" has ambiguous meanings which makes it necessary to clarify terminology within this dissertation.

### 2.1.1.1 Computational Complexity

First and foremost, there is the *computational complexity* which can be expressed as the number of required arithmetic operations.

Although such a definition is short and clear, it is quite vague in practice. For floating-point designs, there is the count of floating-point operations (FLOPs) which is accurate as long as all computations are performed with floating-point arithmetic. HLS explicitly supports and allows for floating-point architectures (see Sec. 2.2), but even though, digital designs are commonly created with fixed-point arithmetic for reasons of efficiency, at least until nowadays. A FLOP count cannot represent actually needed hardware resources for such systems, because not all arithmetic operations cause the same computational impact. A hardware multiplier is of course larger than an adder, not to mention the square root operation which would probably be implemented within a design of its own.

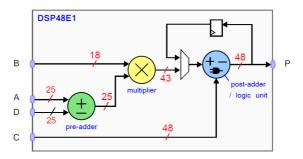

A very important part in digital signal processing applications play multiply-and-accumulate operations (MACs), and modern FPGAs have plentiful of DSP slices for those available. The Xilinx DSP48E1 slice of the 7 series devices (shown in Fig. 2.1), e.g., consists of a full-custom 18  $\times$  25 bit two's-complement multiplier, a 48 bit accumulator and a powerful arithmetic logic unit (ALU) to compute ten different logic functions of two operands and dual 24 bit additions or subtractions [Xil-UG479]. Therefore, most of the fixed-point arithmetic will preferably be mapped to such DSP slices and, hence, the actual DSP slice count will constitute a somewhat invariant and thus reliable estimate of the computational complexity for digital FPGA designs.

The design examples presented in Sec. 5.2.4 will demonstrate that the DSP slice utilisation is the only invariant figure between pre-RTL

**Figure 2.1:** Simplified block diagram highlighting the arithmetic capabilities of the Xilinx DSP48E1 slice [Cro<sup>+</sup>14].

synthesis, i.e. the HLS estimate, and post-RTL synthesis with Xilinx Vivado.

### 2.1.1.2 Algorithmic Complexity

The computational complexity is closely related to the *algorithmic complexity*. The latter is well-defined and can be expressed by the so-called big O notation, which classifies algorithms according to their run time or memory storage requirements.

If these are expressed by functions  $f, g : \mathbb{N} \to \mathbb{R}^+$ , then

$$\mathcal{O}(g(n)) = \left\{ f \mid \exists c \in \mathbb{R}^+, \exists n_0 \in \mathbb{N}, \forall n \ge n_0 : f(n) \le c \cdot g(n) \right\}$$

(2.1)

formally defines the set  $\mathcal{O}(g(n))$ , which contains all functions with a growth rate less than g(n), [CLC09]. n is a parameter of the algorithm, e.g. the size of an input vector or a list to be sorted. g(n) is an upper bound scaled by some positive constant c. That means, the big O notation makes only a case for the behaviour  $n \to \infty$ , i.e. it is an asymptotic upper bound.

Depending on the choice of g, algorithms can be categorised into classes of complexity. These are among others and in order of increasing growth rate:

• constant complexity, i.e. no dependence on n, O(1),

- logarithmic complexity,  $\mathcal{O}(\log(n))$ ,

- linear complexity,  $\mathcal{O}(n)$ ,

- polynomial complexity,  $\mathcal{O}(n^k)$  for some k > 0, and

- exponential complexity,  $O(k^n)$ , k > 0.

Concerning the digital design of algorithms, the limited availability of resources has to be taken into account to judge upon feasibility. Algorithms belonging to any class of complexity will of course be technically feasible for a sufficiently small n, although n might be larger for smaller growth rates. At all times the generally unknown constant c has to be factored in.

An exact count of arithmetic operations differs from the algorithmic complexity such that it is a tight bound with known constant, at least approximately. And it gives reliable information even for small  $n \ll n_0$ . The asymptotically tight bound is formally defined as

$$\Theta(g(n)) = \{ f \mid \exists c_1, c_2 \in \mathbb{R}^+, \exists n_0 \in \mathbb{N}, \forall n \ge n_0 : \\ 0 \le c_1 g(n) \le f(n) \le c_2 g(n) \} .$$

(2.2)

There are also an asymptotic lower bound  $\Omega(\cdot)$  and asymptotically tight upper/lower bounds,  $o(\cdot)$  resp.  $\omega(\cdot)$ , [CLC09].

### 2.1.1.3 Mathematical Complexity

The extension of the set of real numbers  $\mathbb R$  by imaginary numbers with the help of the imaginary unit j creates the set of *complex numbers*  $\mathbb C$ . Often, DSP applications make extensive use of complex numbers, e.g. in wireless communications. If that is the case, the adjective "complex-valued" will be used within this text. A complex-valued digital design utilises complex numbers and complex-valued additions, multiplications, etc., but can be fairly simple at the same time because it must not be a computationally complex system.

Additionally, there are *mathematically complex functions* from the perspective of a fixed-point digital design. Such functions can very well be real-valued but complicated to be computed with binary logic. The square root or trigonometric functions are good examples, since their implementation usually requires an algorithm of its own, e.g. the Coordinate Rotation Digital Computer (CORDIC) [Vol59; Wal71].

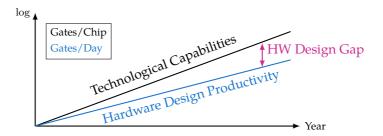

Figure 2.2: The productivity design gap [EMD09].

### 2.1.2 The Productivity Design Gap

The technological evolution scales quite well to accommodate the above mentioned growth in computational complexity. The famous Moore's law, that the number of transistors which can be integrated on a single chip doubles every 18 months, has been valid for decades by now although being questioned more frequently recently [Moo65; Moo98]. This leads nonetheless to an increased transistor density on the die area and the availability of more logic resources with every latest semiconductor process technology node. Contemporary FPGAs thus can offer hundreds (some even thousands) of dedicated DSP slices for the fast and efficient implementation of MACs and other operations.

But the engineer's design capabilities do not scale at the same rate. This is called the *productivity design gap* and is illustrated in Fig. 2.2. In contrast to the increasing technological capabilities according to Moore's law, the hardware design productivity increases only by a factor of 1.6 every 18 months [EMD09]. This leads to a gap which can only be closed by improved design performance.

Recently, the pace of the technological development is slowing, because the miniaturisation is approaching some physical limits and effects on the nanometre scale lead to a decreased return of investment and rising costs. Far from signaling an end to progress, this gradual "end of Moore's law" will open a new era in information technology as the focus of research and development shifts from miniaturisation of long-established technologies to the coordinated introduction of new devices, new integration technologies, and new architectures for computing [TW17]. This will

definitely have an impact on how devices and digital architectures are going to be programmed and HLS will presumably play a part here as well.

### 2.1.2.1 Design Entropy

In [MS13], the view has been advanced that the productivity design gap is caused by the structure of an algorithm itself, which can be measured in terms of what the authors call *design entropy*: the more irregular a hardware architecture, the higher is the design entropy.

On the one hand, memories are highly regular structures and of low entropy. Therefore, huge memories can be designed quickly and are usually the first applications for the latest technology node. On the other hand, general purpose processors, like CPUs, are examples for high-entropy designs, because of their largely irregular structure of the control logic, which consumes most of the chip area. Modern complex signal processing algorithms with irregular data paths and much control overhead, e.g. caused by loops or if-else branches, are of high entropy and, hence, more difficult to design.

In order to overcome this productivity design gap, it was proposed to introduce further tools into the design flow which are capable of automating certain implementation aspects, and especially shift the design perspective to a higher, more abstract level [MS13]. In other words, the coding of hardware architectures must be elevated to the algorithmic layer—away from traditional HDLs and the RTL.

HLS does accelerate digital architecture design by allowing hardware engineers to work on a higher level of abstraction, as desired.

### 2.2 A Short Historical Review

There has been a shift of meaning regarding the term "High-Level Synthesis". Whereas years ago this meant the possibility to synthesise *behavioural* HDL code [GR94], in recent times it is understood as an automated design compilation process that interprets an algorithmic description in an HLL, like C/C++ or SystemC, and synthesises a synchronous RTL description in an HDL [Cou $^+$ 09].

HLS tools have been in practice since the 1950s and attracted considerable interest when early commercialisation efforts were made in the last decades [Con<sup>+</sup>11]. The development and evolution of HLS tools can roughly be divided into three generations [MS09].

- 1980s to early 1990s. First research was conducted on HLS but with a failed commercialisation of such tools. RTL synthesis with HDLs was upcoming and HLS tools required the users to learn obscure design languages. The quality of results was poor.

- 1990s to early 2000s. Major companies like Synopsys, Cadence and Mentor Graphics offered their tools and HLS was tried out by quite a number of users. However, this tool generation could not convince out of several reasons. For example, HDLs were used as design languages for HLS and thus competing with existing RTL synthesis tools, obtained results were highly variable and hard to validate, and simulation times were almost as long as with RTL synthesis.

- 2000s to 2010s. While some tools are still dataflow or DSP domainspecific, most tools adopt C, C++ or SystemC as an HLL design input. The quality of results is improved stemming from compilerbased optimisations. Yet, a major impact made the rise of FPGAs, which changed the measurement criteria for a good design. The hardware architecture simply has to be fast enough and must fit within its capacity when targeting an FPGA. Last but not least, the increased computational complexity of signal processing applications had further raised the need for improved electronic systemlevel (ESL) tools meanwhile.

Nowadays, the tools of the third generation have matured and are capable not only to synthesise data paths but also control logic. The familiar C programming language and its variants as design inputs accommodate the skills of algorithm designers and embedded software engineers.

### 2.2.1 Contemporary Developments

There a two significant and game-changing developments taking place currently [HM17]:

HLS becomes integrated into even more abstract ESL tools. Xilinx, e.g., sells the SDSoC tool which targets software development with custom hardware acceleration on a System-on-Chip (SoC). System-level profiling identifies computationally intensive functions which can then be implemented with HLS in programmable logic as hardware accelerators. The integration into the SoC is automated to a great extent.

The Open Computing Language (OpenCL) framework maintained by the Khronos Group finds support with HLS tool vendors [Khr17]. OpenCL is an interface based on C to program diverse parallel computing devices, foremost GPUs. However it is not restricted to GPU computing and targets heterogeneous architectures built with FPGAs as well. Commercially supported is this, e.g., by Intel's FPGA SDK for OpenCL (formerly by Altera) and Xilinx' SDAccel.

Underlying these trends is the fact that these tools natively support single-precision floating-point numbers compliant with the IEEE Standard 754 [IEEE-754], which will be discussed in detail later on in Sec. 3.2.1.1 for this reason. HLS is used to generate dedicated floating-point architectures which makes a seamless integration into software applications possible.

Intel's Arria and Stratix FPGAs even consist of *hardened* floating-point (!) DSP slices [Alt14; Sin17] while Xilinx Vivado HLS (VHLS) maps such floating-point operations to optimised soft cores consisting of a number of DSP48E1 slices, the exact number thereof depending on the respective operation.

Because of this, FPGAs have already become a major workforce in large-scale data centres for high-performance and cloud computing, e.g. for deep learning or other machine learning applications [HM17].

# 2.3 The Basic Principles of High-Level Synthesis

The classical design flow of complex digital signal processing applications requires a hardware engineer to devise a detailed architecture that meets system specifications, and then to manually code a RTL design in an HDL, usually VHDL or Verilog. This is an iterative process indeed, and often many design iterations are necessary. A minor re-design of the architecture can lead to substantial changes of the RTL description.

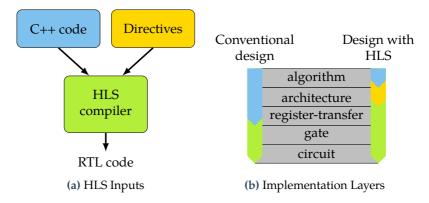

**Figure 2.3:** Architectural HLS compiler directives complement the design abstraction of a high-level algorithmic description.

In contrast to this, the HLS-based digital design flow still needs an algorithmic specification but the architectural design is vastly simplified and the following implementation with an HDL is fully automated. Fig. 2.3 emphasises this fact as it will be explained below.

### 2.3.1 Inputs to an High-Level Synthesis Design

The HLS compiler commonly needs two inputs (Fig. 2.3a).

- The first input, of course, is the algorithm that is to be synthesised and supposed to be supplied in an HLL. Throughout this work this code is assumed to be a vanilla C++ source code. A considerable number of HLS tools support the family of the C programming languages (see Sec. 2.5). On the one hand, C++ lacks hardware-related features, like the explicit timing of operations or fixed-point data types. But on the other hand, the lack thereof leads to a design abstraction—as intended.

- Some of those drawbacks can very well be mitigated by the second input to the HLS compiler: The HLS synthesis process can be controlled by compiler directives, also called pragmas. These directives mainly influence the synthesised architecture. This endows the

hardware engineer with an abstracted, qualitative control over the architectural HLS output.

Nonetheless, hardware expertise is still necessary to generate efficient digital architectures, as is the adherence to HLS coding guidelines.

Fig. 2.3b shows an excerpt of the Gajski–Kuhn Y chart, namely the functional view only [GK83]. While the conventional design methodology requires manual design steps from the top down to the RTL, the HLS approach solely needs an untimed functional algorithmic specification which of course has to be given in a supported input programming language. The coding of synthesisable RTL code is completely automated and architectural design decisions may or may not be constrained with a small set of directives. The default optimisation of HLS compilers usually is for minimal resource utilisation and sequential operation.

The iterative design process mentioned above is accelerated tremendously because an HLS compiler can "mould" the desired algorithmic functionality into an architecture, and generation of RTL code is a matter of minutes or even seconds. This makes a rapid design space exploration feasible (see Sec. 3.3.2), i.e. the same high-level algorithmic specification can be reused and compiled for different implementation technologies or changed constraints. Problem sizes and even data types become configurable parameters. Additionally, the concept of a selfchecking and re-usable test bench as well as fast bit-accurate C-based RTL simulations contribute to a rapid design time. The automated and correct-by-construction synthesis process reduces the occurrence of lowlevel implementation bugs that are routine in RTL codes, which improves the overall design productivity significantly [Ren14].

The shift of the design perspective to a more abstract implementation layer is often likened to the development of HLLs themselves: Today, nobody would even think of programming a complex software application solely by using assembly language [Cou<sup>+</sup>09]. The gain in coding efficiency by HLLs outweighs the advantages of Assembler by far, such that assembly code still exists but only in niche applications.

### 2.3.1.1 Coding Style Guidelines

The adherence to a suitable coding style is mandatory to obtain efficient RTL designs. [FB10] puts it the following way:

"One of the common misconceptions held by people is that synthesizing hardware from C++ provides users the freedom of expressing their algorithms using any style of C++ coding that they desire. When designing using high-level C++ synthesis, it is important to remember that we are still describing hardware using C++, and a "poor" description can lead to a sub-optimal RTL implementation."

Probably the most severe limitation is that variables can only be allocated on the stack. Due to this restriction, the HLS tool can infer the needed amount of registers to store their values, which is especially important with regard to arrays, the sizes of which need to be fully determined at compile time. The reason why variables cannot be allocated on the heap memory (i.e. with the C/C++ commands malloc, calloc, free, new or delete) is simple: There is no operating system to control dynamic memory usage on an FPGA or ASIC.

Nonetheless, there are applications which require a variable sizing of arrays or other parameters. A viable solution is to resort to function and class templates. A template is instantiated with a set of constant parameters, a process which is called specialisation. For instance, function recursion is prohibited because the recursion depth is generally undefined at compile time, however tail recursion with a templatised function and additionally a tail specialisation for the final call is possible [Xil-UG902].

Further, data dependencies are potentially problematic and can lead to performance bottlenecks. Hence, sometimes the order of computations needs to be changed to allow for better parallelism. This requires manual intervention to rewrite certain pieces of a source code, yet the HLS test bench checks for—and therefore ensures—functional equivalence.

A significant benefit of HLS is its capability to generate RTL microarchitectures of loop statements (for, while, do...while), but variable loop bounds are to be avoided. It is highly recommendable that the initialisation of the loop iterator is a constant, that the test condition is against a constant, and that the iterator increment is a constant. This allows for an efficient control logic with small bit widths since the value range of the iterator can be determined during synthesis [FB10].

Additional details on other possible design optimisation are given, e.g., in [FB10] and [Xil-UG902]. As a last remark, specialised HLS code libraries are made available by the tool vendors for certain common

problems, e.g. to efficiently compute non-trivial mathematical functions or to solve linear algebra problems.

### 2.3.1.2 Directives for Architecture Design

Digital architecture design is certainly one of the greatest strengths of HLS with regard to synchronous very-large-scale integration (VLSI) design. There are directives to control basic properties of the generated microarchitectures like area, latency or throughput. A fine-grained application of directives is possible to the top-level function, named sub-functions, variables and interfaces.

**Figures of Merit** Whereas area can be expressed in terms of Gate Equivalent (GE) for ASIC designs, it is impossible or at least unfair to reuse this metric for FPGA designs, the reason being the largely heterogeneous building blocks of them. Therefore, most works in the literature give figures pertaining the utilisation of certain resources, as also recommended in [Xil-UG902]. *Resource utilisation* is usually stated as a quadruple (BRAM, DSP, FF, LUT), where the abbreviations stand for Block RAM, specialised DSP slices with hardware multipliers (e.g. DSP48E1 by Xilinx), flip-flops and look-up tables, respectively.

Latency is the number of clock cycles from the first input to the first valid output. And throughput can be computed as the inverse of the number of cycles per data item. The clock cycles per data item differ from the latency because digital designs are pipelined in general. In HLS parlance, the "clock cycles per data item" is termed *Initiation Interval* (II) and defined as the number of clock cycles before a function can accept new input data and the next loop iteration is started. An II = 1 means a new loop iteration is started every clock cycle [Xil-UG902; FB10].

**Architectural Equivalence Transforms** Three basic equivalence transforms can universally be applied to an algorithm of combinatorial computations to improve latency and throughput or to exploit parallelism [Kae08]:

• **Decomposition** of a function consisting of a number of calls to an identical smaller sub-function, which can then be executed sequentially with a smaller hardware footprint.

| Directive          | Description                                             |

|--------------------|---------------------------------------------------------|

| ALLOCATION         | Limits the number of resources such as DSP slices.      |

| ARRAY_PARTITION    | Partitions an array into smaller arrays or registers.   |

| DATA_PACK          | Aggregates multiple variables into a single word.       |

| DATAFLOW           | Enables concurrent execution of functions or loops.     |

| EXPRESSION_BALANCE | Balances logic depth, e.g. to create adder trees.       |

| INLINE             | Inlines a function and thus improves latency.           |

| INTERFACE          | Specifies top-level RTL ports and protocols.            |

| LATENCY            | Sets a latency constraint.                              |

| PIPELINE           | Enables function or loop pipelining.                    |

| RESOURCE           | Constraints a specific HLS library core to be used.     |

| STREAM             | Declares an array to be implemented as FIFO.            |

| UNROLL             | Unrolls loops fully or partially (replicates the body). |

|                    |                                                         |

Table 2.1: Selected directives of Xilinx Vivado HLS [Xil-UG902]

- Pipelining of operations to improve throughput by reducing combinatorial depth and by introducing parallelism.

- Replication of a functional entity to process several data elements concurrently.

With regard to HLS, resource sharing is implicitly performed during synthesis (see Sec. 2.3.3) and effectively identical to decomposition. It is safe to assume that design C/C++ code is written maximally compact and a repeatedly executed sub-function would definitely be called from within a loop body with a single line of code. Since HLS keeps loops rolled by default, i.e. a sequential architecture will be synthesised, further decomposition is not possible. Hence, the main attention of HLS architecture design is how to pipeline and replicate certain combinatorial data paths with directives.

Exemplarily, Tab. 2.1 lists an excerpt of all HLS directives supported by VHLS. An optimisation to begin with is pipelining to reduce latency and increase throughput. The PIPELINING directive allows for an optional parameter with a target II, and it can be applied to loops and functions. Further, task-level parallelism can be exploited by specifying the DATAFLOW directive: Normally, sequential statements are scheduled sequentially, but with data flow optimisation they can be executed in parallel as far as data dependencies permit. Loop unrolling by UNROLL

replicates the loop body, and the directive allows for an optional factor to partly unroll loops. This drastically increases throughput (and area). For most designs, only the most inner loops become unrolled for a good area—throughput trade-off. Nonetheless, unrolling often creates data access bottlenecks with BRAM which has a single or dual port for read/write operations. Therefore, this directive goes hand in hand with the partitioning of arrays into several BRAMs or even into registers each element to increase data concurrency. Last but not least input-output (I/O) interface options can be specified to the top-level function. This includes certain handshake protocols or even Advanced Extensible Interface (AXI) buses to integrate the generated Intellectual Property (IP) core into a SoC later on.

**Estimated Clock Frequency** Additional constraints can be set to configure resets and (target) clocks. Most importantly, VHLS can only estimate the maximal operating frequency, because HLS resorts to a HLS component library (for multiplications, additions, and so on) with expected timing information depending on the configured target devices. The C/C++ code is synthesised into an RTL code and then, again, by RTL synthesis into a gate-level description. A timing margin is reserved for the design steps to come including place and route.

#### 2.3.2 C-Based Test Benches for Verification

The created hardware architecture is correct-by-construction and bit-accurate C-based simulations of the RTL are possible with the C/C++ or SystemC design files. However, verification generally is simulation-based and formal equivalence checking is still a challenge [Ren14].

This leads to the notion of self-checking test benches. Some HLS tools require a C/C++ test bench to be associated with each design which compares the results with given or random inputs to the HLS-designed entity against pre-computed values ("golden device") or a software model. The choice is with the designer what to check precisely for a successful verification.

Even if later code changes are necessary, e.g. to rearrange the order of computations or rewrite some loop constructs to enable further HLS compilation optimisations, the test bench ensures functional verification as long as the test passes.

Most of the HLS tools integrate the functionality to generate RTL test benches automatically from C test benches, which makes another manual implementation step obsolete. VHLS, e.g., uses a C-to-RTL transactor and generates besides Verilog and VHDL design files also a bit-accurate and cycle-accurate SystemC RTL design to speed up simulation times [Con+11]. Although formal equivalence checking is not yet solved fully, the much wider simulation coverage of HLS and the possibility for in-system simulations are especially helpful with FPGA hardware (HW) targets.

This powerful test bench concept is utilised by the RDAM, as described later, to ensure functionality even if data types change, e.g. during the transition from floating-point to fixed-point arithmetic.

A modern paradigm of software engineering is test-driven development. This means, that the test bench for functional verification is created first, i.e. before the actual software. The software is then written until the specified target functionality is met. Similarly, the HLS test bench can test for a set of pre-defined verification requirements.

### 2.3.3 The High-Level Synthesis Compilation Process

Very good introductions into the internals of HLS compilation can be found in [Cou<sup>+</sup>09; GR94; Ren14]. It is a research topic of its own and can, therefore, only sketched briefly here.

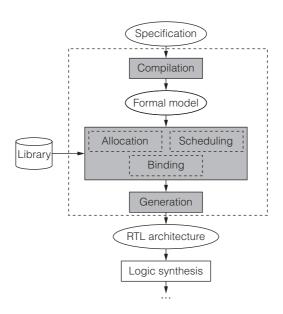

The HLS compilation process consists of three main steps: compilation, optimisation and RTL generation, as shown in Fig. 2.4 with shaded blocks. A more detailed explanation of every step follows below.

The synthesis process always starts with the *code compilation* of the design entry sources. This relies to a great extent on the capabilities of the employed compiler. For C/C++ based designs this is the GNU C Compiler of the GNU Compiler Compilation (GCC) or a C/C++ frontend (e.g. Clang) for the Low Level Virtual Machine (LLVM) framework [Zho+16; Ren14]. This step includes code optimisations such as constant folding, loop transformations or simply dead-code elimination.

**Figure 2.4:** The basic HLS compilation process [Cou<sup>+</sup>09].

To give an example, the modern LLVM framework consists of three stages [LA04; Lat12]. The first stage is the language frontend, which transforms the input source code into an intermediate representation (IR), the LLVM assembly language. This is a static single assignment (SSA) representation that provides type safety, low-level operations and flexibility. The second stage is the LLVM optimisation, i.e. all code optimisations are performed on the IR. And the consecutive third stage, the backend, maps the IR onto the instruction set of the hardware target, e.g. an x86 or Advanced RISC Machine (ARM) architecture.

The LLVM is well-suited for HLS due to this modular design. In particular, the IR is fully bit-accurate and not limited to bit widths of native C types which are multiples of 8 bits in alignment with common micro-architectures. Code optimisations like memory reuse, array partitioning, automatic loop unrolling and function inlining can be exploited directly [Con<sup>+</sup>11].

- 2. Data dependencies can be *modelled formally* with a data flow graph (DFG) where nodes represent arithmetic operations and edges are variables. To model control structures like if and switch statements or loops, the DFG model is extended by a control graph resulting in the control and data flow graph (CDFG). Edges within a CDFG represent the control flow while nodes are either control constructs or so-called basic blocks which contain DFG models. Further optimisations are applied to exploit data parallelism within basic blocks and inter-dependencies between these.

- 3. Based on the formal CDFG model, *allocation* of resources is performed. "Resources" are functional entities or storage units within this context. For each (arithmetic) operation a component is selected from the RTL component library. The allocation thereby depends on the given design constraints and must satisfy those.

- 4. Then, operations are *scheduled*. Variables of the DFGs must be loaded and stored and operations take a certain amount of clock cycles. This can either be resource-constrained or time-constrained.

- 5. Consecutively, *binding* happens. It is not until then that functional resources are mapped to actual hardware units as they are provided by the target hardware platform (FPGA or ASIC). The binding task

- assigns the operations and memory accesses within each clock cycle to available units. A hardware unit will be shared and reused if access to a functional resource is mutually exclusive.

- 6. As a last step, synthesisable *RTL generation* follows, usually with a control and data path. A single or several finite state machines (FSMs) control the inputs and outputs of the data paths within the basic blocks. Also, I/O interface logic is added, e.g. for an AXI bus or simpler handshaking protocols.

All these steps are executed automatically without further intervention by the user apart from the boundary conditions set by the applied HLS compiler directives. The amount of information about the synthesised digital design which the compiler outputs depends on the very HLS tool used, but is in any way critical in identifying design bottlenecks and thus obtaining increased performance with another design iteration.

# 2.4 Alternative Digital Design Techniques

HLS is not the only solution to cope with increased digital design complexity. Competing alternatives are graphical tools, and extensions to traditional HDLs can also improve design efficiency.

# 2.4.1 Hardware Description Languages

The two most widespread HDLs are Verilog, specified as IEEE Standard 1364 [IEEE-1364], and VHDL, specified as IEEE Standard 1076 [IEEE-1076]. There is still support to write structural RTL code, but even in the early 1990s behavioural RTL synthesis had already been introduced, as mentioned above in Sec. 2.2. Behavioural RTL synthesis is able to infer logic and can therefore be considered to be an abstraction step of its own. The capabilities depend on the respective synthesis tools but have steadily improved since then.

An advantage of HLS is the simplicity with which algorithmic parameters can be changed, like constant sizes or even data types. This is possible with HDLs as well albeit requiring more time to write. Common to Verilog and VHDL are so-called generics. In Verilog, the line

```

parameter PARAMETER_NAME = VALUE;

```

defines a constant with the help of the parameter keyword. This could be used for varying input sizes or fixed-point word lengths, and can later be changed and also passed on to instantiated modules. A parameter of a module can be set by the syntax

```

#(.PARAMETER_NAME(VALUE));

```

after instantiation. Alike, VHDL allows to define generic constants and generic types with the generic and generic map keywords during entity declaration resp. component instantiation.

Additionally, VHDL supports generic packages. This is at the heart of the predefined standard packages, foremost the fixed\_generic\_pkg for fixed-point arithmetic and math\_complex for complex-valued mathematical operations [Ash08]. However, some functionalities have only been introduced with the latest revision of the standard in 2008, and its adoption by behavioural synthesis tools has been slow.

Therefore the well-known HDLs can offer basic generic functionality as required by the RDAM, but nonetheless the usual disadvantages apply. On the RTL level, design space exploration, especially regarding the exploration of different degrees of parallelisms, is slow and error-prone due to the needed number of changed lines of code. In every case, the implementation quality depends on the skills of the digital design engineer as it is the case with HLS.

In conclusion, the intentional input abstraction with an HLL speeds up design time for highly flexible digital architectures with HLS. The compiler has to fill in for the missing fine-grained control over the details of hardware design.

# 2.4.2 Graphical Programming Languages

Another solution being proposed to the hardware design productivity challenge are graphical programming languages. To begin with, National Instruments offers the possibility to program their FPGA products with LabVIEW graphically. Then there is Mathworks Simulink as a standalone product or in conjunction with another tool, which can either be Xilinx' Vivado System Generator for DSP or the Altera DSP Builder Advanced Blockset which Intel markets now under the name DSP Builder for FPGAs.

The Simulink-based tools offer a library of functional blocks which can be utilised to create DSP algorithms. The DSP blocks are modelled

and written in C and have hand-crafted and optimised RTL architectures associated with them. Hence, the quality of results is quite good by design. A major strength of these tools is the convenient support for fixed-point data types with varying bit widths and easy functional design verification.

Nonetheless, common to these tools are the limitations of the graphical design entry. It is mostly data flow oriented and the overview suffers for large designs. When it comes to architectural changes, e.g. exploiting parallelisms, the graphs have to be remodelled substantially, which is time-consuming and tedious. Furthermore and most importantly, the graphical programming languages are non-standardised and subject to change from version to version to come.

These disadvantages are HLS's advantages. Not only are C programming languages well standardised, but also the RTL output in VHDL, Verilog or as a packed IP core in the IP-XACT format is standardised [Xil-UG902]. The architectural design is vastly simplified by a handful of compiler directives and does not require any code modifications most of the time.

# 2.5 An Overview of Current High-Level Synthesis Tools

The market for HLS tools is steadily changing. Some tools had originated with academic research and were then bought and advertised commercially, often accompanied by a product name change. Others have been discontinued. [Mee+12; Nan+16; RJ16] comprehensively survey, list and compare known HLS tools.

Selected tools will be mentioned below, which are multi-domain and can synthesise American National Standards Institute (ANSI) C and possibly C++ or SystemC code. Tab. 2.2 gives an overview over these tools and judges their qualification with respect to the RDAM. All tools do support some kind of DTA either founded in the polymorphism and object orientation of C++/SystemC or, as a baseline, the typedef keyword of all C dialects. (More on this later in Chap. 4.) However, there are differences regarding the availability of floating-point (floating-point) or fixed-point (fixed-point) data types.

Table 2.2: An overview of several commercial and academic HLS tools and an assessment of their suitability for the RDAM

|     | Name                              | Developer             | Input           | FPGA | ASIC FLP FXP | FLP | FXP | RDAM |

|-----|-----------------------------------|-----------------------|-----------------|------|--------------|-----|-----|------|

| I   | Catapult HLS                      | Mentor Graphics       | C, C++, SystemC | 7    | 7            | ×   | >   | 2    |

| sia | HLS Compiler                      | Intel Corporation     | C, C++, SystemC | >    | ×            | 7   | 7   | >    |

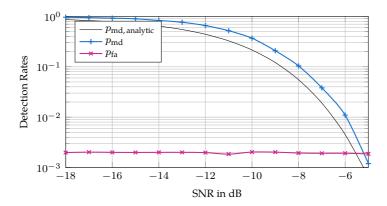

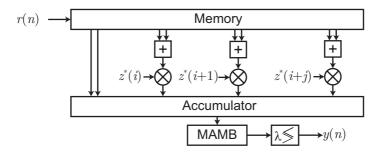

| JƏU | LegUp 5.0                         | LegUp Computing       | O               | 7    | ×            | 7   | ×   | 2    |