## Feasibility of Geiger-mode avalanche photodiodes in CMOS standard technologies for tracker detectors

Eva Vilella Figueras

Aquesta tesi doctoral està subjecta a la llicència <u>Reconeixement- NoComercial 3.0. Espanya de</u> <u>Creative Commons</u>.

Esta tesis doctoral está sujeta a la licencia <u>Reconocimiento - NoComercial 3.0. España de</u> <u>Creative Commons.</u>

This doctoral thesis is licensed under the <u>Creative Commons Attribution-NonCommercial 3.0.</u> <u>Spain License.</u> Universitat de Barcelona

Departament d'Electrònica

## Feasibility of Geiger-mode avalanche photodiodes in CMOS standard technologies for tracker detectors

Doctoral dissertation in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering and Advanced Technologies

by Eva Vilella Figueras

Barcelona, October 2013

Advisor: Dr. Angel Diéguez Barrientos

Doctoral program: Engineering and Advanced Technologies

Research line: Instrumentation Systems and Communications (SIC)

## Table of contents

| Acknowledgements i                                                   |

|----------------------------------------------------------------------|

| Preface and organizationiii                                          |

| 1. Future linear lepton colliders and other potential applications 1 |

| 1.1 Current state of particle colliders                              |

| 1.2 Proposals for future linear lepton colliders                     |

| 1.2.1 The International Linear Collider 4                            |

| 1.2.2 The Compact Linear Collider 5                                  |

| 1.3 Detector systems in future linear colliders                      |

| 1.3.1 Tracking system requirements 8                                 |

| 1.3.2 Tracking technology options11                                  |

| 1.3.2.1 DEPFETs                                                      |

| 1.3.2.2 MAPS                                                         |

| 1.3.2.3 FPCCDs                                                       |

| 1.3.2.4 Chronopixels                                                 |

| 1.3.2.5 Timepix                                                      |

| 1.3.2.6 GAPDs                                                        |

| 1.3.2.7 SOI                                                          |

| 1.3.2.8 3D                                                           |

| 1.4 Detector systems in other particle colliders                     |

| 1.5 Other applications                                               |

| References                                                           |

| 2. Geiger-mode avalanche photodiodes in CMOS technologies            |

| 2.1 Principle of operation                                           |

| 2.2 Figures of merit                                                 |

| 2.2.1 Dark count rate                                                |

| 2.2.2 Afterpulsing                                                   |

| 2.2.3 Crosstalk                                                      |

| 2.2.4 High energy particle detection                                 |

| 2.2.5 Photon detection probability                                   |

| 2.2.6 Timing resolution                                              |

| 2.3 State-of-the-art                                                 |

| 2.3.1 Custom GAPDs 50                                                |

| 2.3.2 CMOS GAPDs                                                                         | 2 |

|------------------------------------------------------------------------------------------|---|

| 2.4 Front-end electronics                                                                | 4 |

| 2.4.1 Quenching and recharge circuits                                                    | 4 |

| 2.4.2 Modes of operation                                                                 | 8 |

| 2.4.3 Readout circuits                                                                   | 0 |

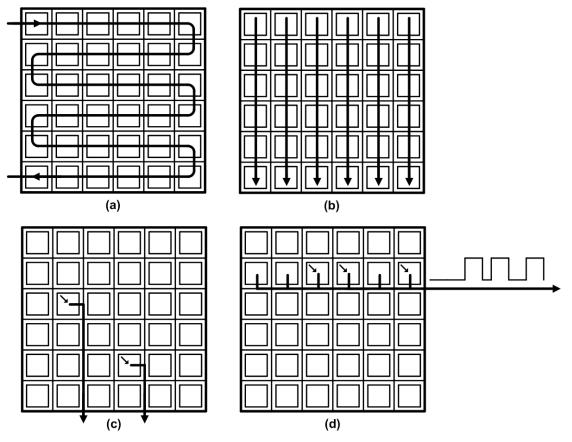

| 2.4.4 Array architectures                                                                | 2 |

| References                                                                               | 4 |

| 3. Design and characterization of single pixels and small arrays in a HV-CMOS process 69 | 0 |

| 3.1 Single pixels with different voltage-mode readout circuits                           |   |

| 3.1.1 Design                                                                             |   |

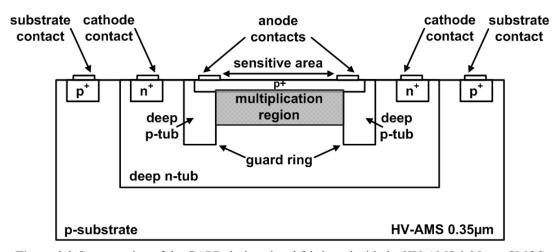

| 3.1.1.1 Geiger-mode avalanche photodiodes in a 0.35 μm process and mode of               | Ū |

| operation                                                                                | 0 |

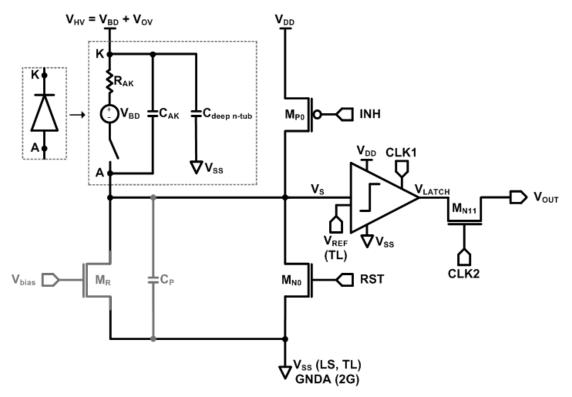

| 3.1.1.2 2-grounds                                                                        |   |

| 3.1.1.3 Level-shifter                                                                    |   |

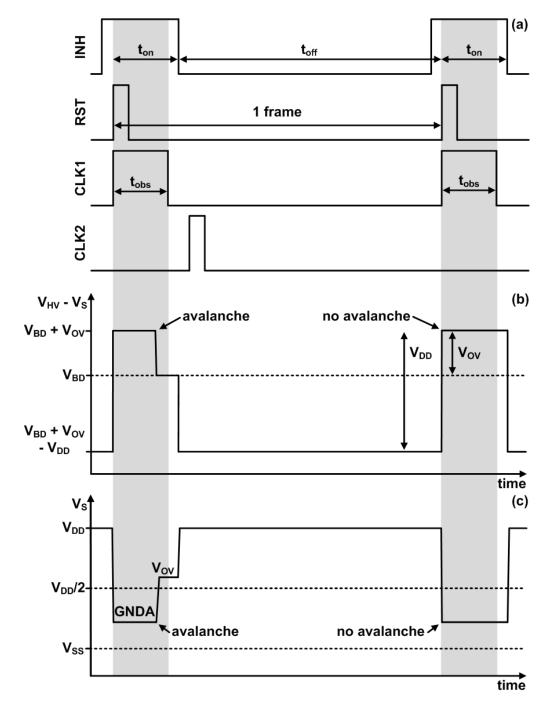

| 3.1.1.4 Track-and-latch comparator                                                       |   |

| 3.1.2 Characterization                                                                   |   |

| 3.2 Single pixel with a current-mode readout circuit                                     |   |

| 3.2.1 Design                                                                             |   |

| 3.2.2 Characterization                                                                   | 3 |

| 3.3 Array of 3 x 3 pixels                                                                | 5 |

| 3.3.1 Design                                                                             | 5 |

| 3.3.2 Characterization                                                                   | 6 |

| 3.4 Array of 1 x 5 pixels                                                                | 7 |

| 3.4.1 Crosstalk in time-gated arrays that share the well                                 | 8 |

| 3.4.2 Characterization                                                                   | 0 |

| 3.5 Discussion                                                                           | 4 |

| References                                                                               | 6 |

| 4. Design and characterization of large arrays in a HV-CMOS process                      | 0 |

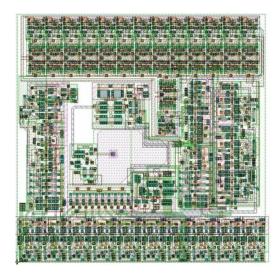

| 4.1 Design of a time-gated array of 10 x 43 pixels                                       |   |

| 4.2 Characterization                                                                     |   |

| 4.2.1 I-V curve                                                                          |   |

| 4.2.2 Afterpulsing                                                                       |   |

| 4.2.3 Dark count rate                                                                    |   |

| 4.2.4 Photon detection probability                                                       |   |

| 4.2.5 Dynamic range                                                                      |   |

| 4.2.6 2D imaging                                                                         |   |

| 4.2.7 Thermal effects 10                                                              | )8         |

|---------------------------------------------------------------------------------------|------------|

| 4.2.8 Radiation effects 11                                                            | 5          |

| 4.2.9 Power consumption12                                                             | 20         |

| 4.3 High energy particle detection                                                    | 23         |

| 4.4 Discussion                                                                        | 0          |

| References                                                                            | 3          |

| 5. Further improvements for GAPD technologies 13                                      | 57         |

| 5.1 3D vertical integration with the Global Foundries 130 nm/Tezzaron 3D process 13   | ;7         |

| 5.1.2 Geiger-mode avalanche photodiodes in a 130 nm process 13                        | 8          |

| 5.1.3 Array design                                                                    | 9          |

| 5.1.3.1 Sensor and mode of operation14                                                | 0          |

| 5.1.3.2 Readout circuit                                                               | 1          |

| 5.1.3.3 Array architecture                                                            | 2          |

| 5.2 Time-gated operation as an effective method to extend the sensitivity of dSiPM 14 | 4          |

| 5.3 Improvement of the dynamic range in vision systems based on GAPDs                 | 52         |

| 5.4 Discussion                                                                        | ;9         |

| References                                                                            | ;9         |

| Conclusion                                                                            | <b>i</b> 3 |

| Resum                                                                                 | 57         |

| List of publications                                                                  | <b>19</b>  |

## Acknowledgements

I would like first of all to express my gratitude to my supervisor Dr. Angel Diéguez and the Department of Electronics of the University of Barcelona for giving me the opportunity to do this thesis. I appreciate Dr. Angel Diéguez for his inspiration and guidance during all these years of hard work.

I am enormously grateful to Dr. Oscar Alonso and Andreu Montiel, who developed part of the test set-up used in the characterization of the sensor. Very special thanks to Dr. Oscar Alonso for designing and laying out the PCBs that were used to test the sensor at the Microelectronics Laboratory of the Department and also during the beam-tests. I must also recognize him for his excellent work with the FPGAs as well as closing the first chip of GAPDs in which I participated. My most sincere gratitude to Andreu Montiel for the wonderful software that he developed to watch in real time the images captured by the sensor. Thanks a lot to both of them for never saying no in the seek of the best set-up configuration.

I could not forget to mention Dr. Anna Arbat, who started the work with GAPD sensors at the Department. Not only she was of great help during the first days of this thesis, but also she was always there to provide an answer when questions arose.

I must also acknowledge Dr. Anna Vilà for the time she spent with me discussing about the physical aspects of the sensor. Her guidance during the characterization of the sensor with the FIB-SEM machine was also of great value.

Thanks also go out to Dr. Mauricio Moreno for letting me use the Optics Laboratory of the Department and supplying great help in handling optical components. His kind willingness and interest in my work always impressed me.

I am very pleased to Dr. Sergi Hernández and Julià López for being so generous with their time. Thank you for helping me in the management of the spectrophotometer and also for letting me use the lasers of the Photonics Laboratory of the Department.

I am also grateful to Jose García, who provided enormous help with the correction techniques for the improvement of the dynamic range of the sensor.

Many thanks to Dr. Toni Pardo, who let me use the climatic chamber of the Department for the thermal characterization of the sensor.

My deepest appreciation to the people of the Halbleiterlabor (German for Semiconductor Laboratory) of the Max Planck Society in Munich, especially to Christian Jendrysik, Stefan Petrovics, Michal Tesař, Dr. Andreas Wassatsch, Dr. Jelena Ninković and Dr. Hans-Günther Moser. I am grateful for the opportunity to do a research stay and also be part of the lab.

I would also like to thank those colleagues, friends and family who have somehow supported me over the years. This thesis has been definitively achieved with the unconditional support and loving care of my parents, Joan and Maria Gràcia. Under no circumstances could I finish this acknowledgements section without mentioning David. His patience is unbelievable. Thanks for being always there, either to face the tough times or share the joy of the successes.

I acknowledge the funding of the Spanish National Program for Particle Phyiscs under the projects FPA2008-05979-C04-02 and FPA2010-21549-C04-01, and also of the European Commission within the Framework Programme 7 Capacities Specific Programme under Grant Agreement 262025.

## **Preface and organization**

Each generation of particle colliders is built with the purpose to perform a series of HEP (High Energy Physics) experiments so as to explore a specific area of particle physics. The experiments conducted at the LHC (Large Hadron Collider), the most powerful particle collider ever built, confirmed the existence of a new particle, presumably the Higgs boson, in 2012. Nevertheless, to determine the properties of the new particle with high precision, refine measurements need to be done. Despite the extraordinary capabilities of the LHC, this machine is not suited for such a target since its precision is intrinsically limited by its proton synchrotron nature.

To solve this issue, the HEP community has already started to look at the post LHC-era. There is a global consensus that it will be characterized by linear lepton colliders, where the collisions between electrons and positrons will allow to probe deeply into the new particle. At present time, there are two alternative projects underway, namely the ILC (International Linear Collider) and CLIC (Compact LInear Collider). From the detector point of view, the physics aims at these particle colliders impose such extreme requirements, that there is no sensor technology available in the market that can fulfill all of them. As a result, several new detector systems are being developed in parallel with the accelerator. The concept of the ILC and CLIC machines is reviewed in Chapter 1, together with a summary of the requirements on tracking detector systems and the main features of the tracking detector candidates proposed so far. Other potential applications apart from particle tracking at future linear colliders, such as the TOTEM experiment at LHC and biomedical imaging, are also outlined in Chapter 1.

This thesis presents the development of a GAPD (Geiger-mode Avalanche PhotoDiode) pixel detector aimed mostly at particle tracking at future linear colliders. GAPDs offer outstanding qualities to meet the challenging requirements of ILC and CLIC, such as an extraordinary high sensitivity, virtually infinite gain and ultra-fast response time, apart from compatibility with standard CMOS technologies. In particular, GAPD detectors enable the direct conversion of a single particle event onto a CMOS digital pulse in the sub-nanosecond time scale without the utilization of either preamplifiers or pulse shapers. As a result, GAPDs can be read out after each single bunch crossing, a unique quality that none of its competitors can offer at the moment. In spite of all these advantages, GAPD detectors suffer from two main problems. On the one side, there exist noise phenomena inherent to the sensor, which induce noise pulses that cannot be distinguished from real particle events and also worsen the detector occupancy to unacceptable levels. On the other side, the fill-factor is too low and gives rise to a

reduced detection efficiency. The most important aspects of the GAPD technology are reviewed in Chapter 2.

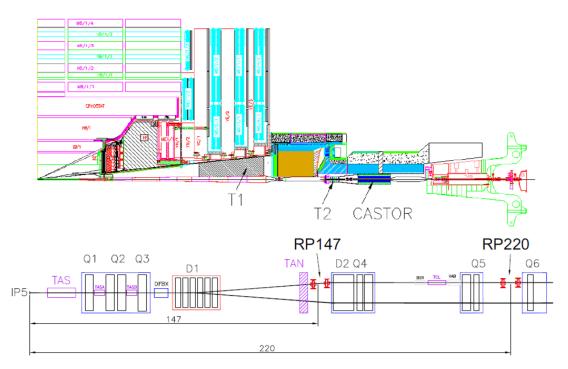

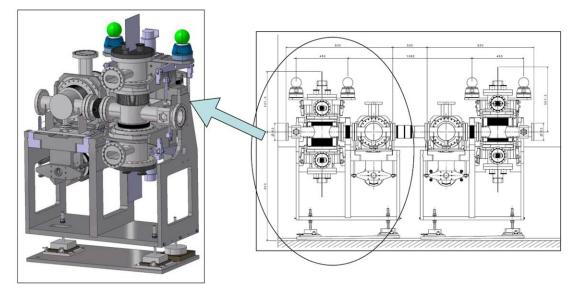

Solutions to the two problems commented that are compliant with the severe specifications of the next generation of particle colliders have been thoroughly investigated. Chapter 3 presents the design and characterization of several single pixels and small arrays that incorporate some elements to reduce the intrinsic noise generated by the sensor. The sensors and the readout circuits have been monolithically integrated in a conventional HV-CMOS 0.35 μm process. Concerning the readout circuits, both voltage-mode and current-mode options have been considered. Moreover, the time-gated operation has also been explored as an alternative to reduce the detected sensor noise. Chapter 4 deals about the design and characterization of a prototype GAPD array, also monolithically integrated in a conventional 0.35 µm HV-CMOS process. The detector consists of 10 rows x 43 columns of pixels, with a total sensitive area of 1 mm x 1 mm. The array is operated in a time-gated mode and read out sequentially by rows. The efficiency of the proposed technique to reduce the detected noise is shown with a wide variety of measurements. Further improved results are obtained with the reduction of the working temperature. Finally, the suitability of the proposed detector array for particle detection is shown with the results of a beam-test campaign conducted at CERN-SPS (European Organization for Nuclear Research-Super Proton Synchrotron). In Chapter 5, a series of additional approaches to improve the performance of the GAPD technology are proposed. The benefits of integrating a GAPD pixel array in a 3D process in terms of overcoming the fillfactor limitation are examined first. The design of a GAPD detector in the Global Foundries 130 nm/Tezzaron 3D process is also presented. Moreover, the possibility to obtain better results in light detection applications by means of the time-gated operation or correction techniques is analyzed too.

Finally, the conclusion section summarizes the most significant results presented over the different chapters of this thesis.

**Key words:** Geiger-mode avalanche photodiode, APD, afterpulsing, beam-test, CLIC, CMOS, crosstalk, dark count rate, fill-factor, future linear lepton colliders, GAPD array, ILC, image sensor, low-noise, non-uniformities correction techniques, readout circuit, SiPM, SPAD, time-gated operation, tracker detector, 3D technologies.

### **Chapter 1**

# Future linear lepton colliders and other potential applications

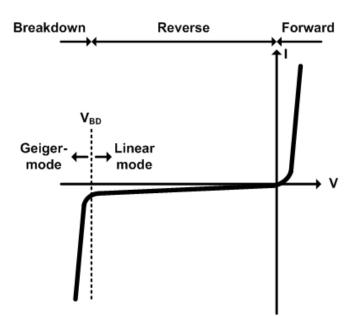

A linear lepton collider operating in the TeV energy scale is needed to study in great detail the underlying physics of the discoveries made at the LHC (Large Hadron Collider) just recently. To fully exploit the physics potential of this endeavor, detector systems capable of unprecedented performance are required. Amongst other technology options, sensors based on APDs (Avalanche PhotoDiodes) and aimed at particle tracking at the next generation of particle colliders are being developed. An APD is implemented as a photodiode reverse biased near or above the breakdown voltage of the junction. When an APD is biased below breakdown, it is known as proportional or linear APD. Linear APDs show a limited optical gain and therefore they can be used to detect only clusters of photons or particles. In contrast, when biased above breakdown, the optical gain of these sensors becomes virtually infinite and they are capable to detect single photons and particles. APDs operating in this regime, known as Geiger-mode, are called GAPDs (Geiger-mode Avalanche PhotoDiodes) or SPADs (Sinlge-Photon Avalanche Diodes).

This chapter reviews the current state of particle colliders and also introduces the proposals for the future linear lepton colliders, namely ILC (International Linear Collider) and CLIC (Compact LInear Collider). Special attention is paid to the requirements demanded on tracking detector systems. Moreover, the several tracking technology options proposed so far are examined, detailing in each case the extent of fulfillment of the demanded requirements. Finally, other potential applications such as experiments at other particle colliders and biomedical imaging are also outlined.

#### 1.1 Current state of particle colliders

HEP (High Energy Physics) is the branch of science that seeks the understanding of the smallest constituents of Nature. In particular, the SM (Standard Model) of particle physics provides a good description of the fundamental particles as well as the interactions between them [1-3]. A fundamental or elementary particle is a particle not known to have any substructure, then it is one of the building blocks of the Universe from which all other particles

are made. According to the SM, there are 6 quarks (known as the flavors up, down, charm, strange, top and bottom), 6 leptons (known as the flavors electron, muon, tau, electron neutrino, muon neutrino and tau neutrino), 4 gauge bosons (photon, gluon, W and Z) and 1 Higgs boson, which together with the quarks, leptons and W boson antiparticles as well as the quarks and gluon colors make a total of 61 elementary particles. The fundamental interactions described by this theory are the electromagnetic, weak and strong forces. The SM was developed in the early 1970's and today it is a well tested model thanks to the large variety of HEP experiments that have been carried out since then.

HEP experiments are conducted using particle accelerators and detectors. Accelerators boost beams of particles to GeV energies before they are made to collide with each other. Detectors observe and record the results of these collisions. At present time, there exist two types of high energy accelerators. On the one hand, synchrotrons, where the accelerated particles follow a high energy constant radius in a time varying magnetic field. On the other hand, linear accelerators, where particles have a linear motion. The accelerated beams of particles are made to collide in the detector region. Usually, the detector, which is composed of several subdetectors performing different purposes, presents a cylindrical symmetry.

Currently, the world's most powerful particle accelerator is the LHC, which is located at CERN (European Organization for Nuclear Research) near Geneva (Switzerland) [4]. In this machine, two beams of hadrons (either protons or heavy ions) are accelerated in opposite directions in a 27 km ring buried underground. The beams are guided around the accelerator ring by a strong magnetic field, achieved using superconducting electromagnets. In the final state of the LHC, the accelerated beams of hadrons will reach the unprecedented energy of 7 TeV each at a nominal luminosity (i.e. the number of particles per unit area per unit time) of  $1 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. The collisions take place inside the four main detectors placed over ring, which are ATLAS, CMS, ALICE and LHCb. Three further experiments, TOTEM, LHCf and MoEDAL, are respectively positioned near the CMS, ATLAS and LHCb detectors. Amongst other discoveries and findings, experiments conducted at the LHC confirmed the existence of a new particle in 2012. The new particle is presumably the Higgs boson, the last missing piece of the SM model that is responsible for the intrinsic mass of particles [5, 6], and it needs to be studied in great detail to precisely determine its properties. However, despite the extraordinary capabilities of the LHC, the precision of this machine is intrinsically limited because it collides hadrons against hadrons. Hadrons are not fundamental particles. Instead, they are made up of quarks, antiquarks and the gluons that hold them together. In these non-fundamental particles, the energy is shared out between its partons in a constantly changing way. Therefore, the initial energy of the two colliding beams in an hadron collider such as the LHC cannot be determined very accurately. Moreover, due to strong interactions, the signal to background ratio is very low.

In order to provide a better description of the discoveries performed at the LHC, refiner measurements need to be done at a new particle collider. Steps towards the post-LHC era have already started. At the beginning of the millennium, the HEP community reached the consensus that a new lepton collider should be the next major facility for HEP experiments. In lepton colliders the accelerated particles are fundamental particles, basically electrons and positrons. Therefore, the energy of each particle is known. Precision measurements of interactions in a detector are possible, balancing the energy before the event with the energy observed afterwards. Hadrons and lepton machines compliment each other. Hadron colliders are useful for discovering new physics or searching for new particles. Differently, lepton colliders can be used for precision measurements of particles after having probed their existence.

However, building a circular lepton machine is not an option. When a particle is accelerated in a circular path, it suffers from energy losses in the form of electromagnetic radiation. These energy losses are known as synchrotron radiation. The synchrotron radiation is inversely proportional to the fourth power of the particle mass and the bending radius of the accelerator. As a proton is a heavy particle (~1836 times heavier than an electron), it is almost not affected by the synchrotron radiation. However, because the electron is so light, circular electron accelerators of only a few hundred GeV would suffer such large synchrotron radiation losses, that unfeasible energy compensations would be necessary to reach the nominal center-of-mass energy. For instance, the old LEP (Large Electron-Positron Collider), a circular lepton collider built at CERN that was operative from 1989 to 2000, precised an extra energy of 0.4 GeV to supply the 104 GeV nominal center-of-mass energy. By extension, a 500 GeV circular lepton collider with the same size as LEP would require an extra energy higher than 200 GeV. The severe increase of the orbit radius of the ring is also unviable due to the costs of such a civil engineering.

For all these reasons, the HEP community has chosen an e+e- linear collider as the next accelerator-based facility to complement and expand the discoveries emerged from the LHC. Moreover, it is also agreed that the nominal center-of-mass energy of this collider has to be in the TeV scale. Regarding the only experience with linear colliders operated so far, the 100 GeV SLAC (Stanford Linear Accelerator Center) National Accelerator Laboratory, researchers have now carried out more than two decades of research to study various solutions. At present time, there are two alternative proposals underway that could fulfill the requirements envisaged for future linear colliders: ILC and CLIC. The HEP community set up a new organization under the umbrella of ICFA (International Committee for Future Accelerators) in February 2013, the LCC (Linear Collider Collaboration), the aim of which is to coordinate the efforts towards the realization of a linear collider. Both machine concepts, ILC and CLIC, are represented in this new organization.

#### 1.2 Proposals for future linear lepton colliders

A linear collider mainly consists of two opposing linear accelerators, which are named linacs. The particles are accelerated following a straight path in each linac, since they are extracted from the particle sources until they are smashed at the center-of-mass energy in the central IP (Interaction Point) located inside the detector. The particles reach their final energy in one go, and therefore very high accelerating gradients of several MeV/m are required in order to limit the length of the collider. Following the acceleration, the two beams collide only once. The particles are grouped together in the so-called bunches of particles. Then, each collision is typically referred as bunch crossing or BX. Several BXs separated by a short temporal gap form a bunch train.

The required luminosity for the target particle physics experiments can be reached only through the appropriate repetition rate (i.e. the frequency of the BXs), number of BXs in a bunch train, number of particles on each of the two colliding bunches, beam cross-section at the IP and mutual beam-beam interaction (i.e. each bunch is affected by the magnetic field created by the other one). In an e+e- collision, both particles feel attraction to each other because of the opposite charge, which enhances the luminosity. However, this attraction provokes a deflection in the trajectory of the particles, which causes them to radiate photons in a phenomenon known as beamstrahlung process. The beamstrahlung photons increase the beam-induced background hits, which are not related to particles created in genuine e+e- physics events and therefore unwanted. The beam-induced hits lead to high occupancies in the inner layers and must be coped with readout techniques or small area pixels.

A brief description of the ILC and CLIC proposals is provided in the following paragraphs. In Table 1.1, a summary of the main beam parameters for the ILC and CLIC colliders is presented.

#### **1.2.1 The International Linear Collider**

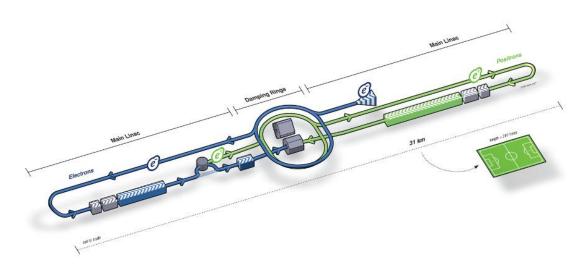

The ILC accelerator is designed to collide electrons and positrons towards each other at a nominal center-of-mass energy of 500 GeV, which could be increased to 1 TeV in a second phase. This accelerator covers a total length of 31 km, extendable to 50 km in the machine upgrade. The ILC project foresees a linear collider consisting of two sources of electrons and positrons, two damping rings with a circumference of 6.7 km each to pre-accelerate the particles, two 11 km long linacs and a 4.5 km beam delivery system to focus the beams to their final sizes and to bring them to collision [7]. The overall layout of ILC is shown in Fig. 1.1. The linacs are based on 1.3 GHz SCRF (SuperConducting Radio-Frequency) accelerating cavities

| Beam parameters                                                  | ILC           | CLIC          |  |

|------------------------------------------------------------------|---------------|---------------|--|

| Center-of-mass energy                                            | 500GeV (1TeV) | 500GeV (3TeV) |  |

| Luminosity (•10 <sup>34</sup> cm <sup>-2</sup> s <sup>-1</sup> ) | 1.49 (2.70)   | 2.3 (5.9)     |  |

| Train repetition rate (Hz)                                       | 5             | 50            |  |

| Bunches/train                                                    | 2820          | 354 (312)     |  |

| Bunch separation (ns)                                            | 337           | 0.5           |  |

| Number of particles/bunch (·10 <sup>9</sup> )                    | 7.5           | 6.8 (3.72)    |  |

| Horizontal beam size (nm)                                        | 640           | 200 (40)      |  |

| Vertical beam size (nm)                                          | 5.7           | 2.26 (1)      |  |

Table 1.1 Comparison between the ILC and CLIC machines.

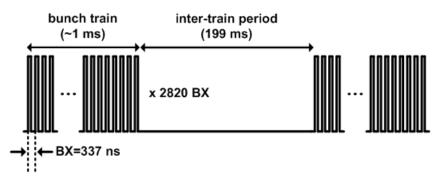

working at 2 K, which provides an average accelerating gradient of 31.5 MeV/m with an energy spread less than 0.1% [8]. The SCRF cavities are hollow structures that are filled with an electric field, the voltage of which changes from plus to minus with a certain frequency (the radio-frequency) to maximize the electric field while maintaining the power consumption within reasonable limits. The luminosity goal is around  $2 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. ILC will operate in a pulsed mode: 0.95 ms long bunch trains of electrons and positrons will collide every 200 ms. At a value of 2820 bunches per train, BXs will occur every 337 ns. The bunch structure of the beam is plotted in Fig. 1.2. At the IP the bunches will have horizontal and vertical sizes of 640 nm and 5.7 nm, respectively.

ILC is currently the most advanced linear collider project, both in terms of advanced and tested acceleration technology as well as from an organizational point of view. In parallel to the machine design, an international study group has prepared the DBD (Detailed Baseline Design), explaining the physics capability of the machine and describing the detector concepts [7]. Although the host country has not been decided yet, the Japanese physics community has presented an initiative to host the ILC collider in Japan. If a positive decision is made within a few years, ILC could be ready for data taking before 2030.

#### **1.2.2** The Compact Linear Collider

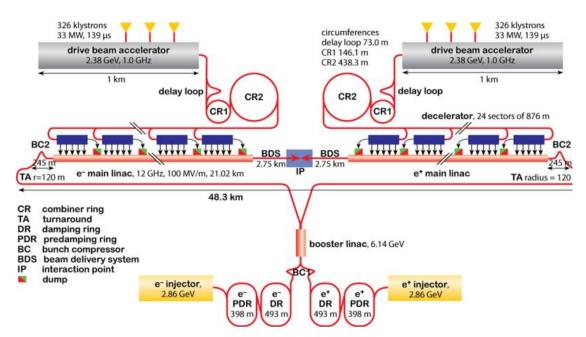

CLIC is a much more challenging project that proposes to collide electrons and positrons at a nominal center-of-mass energy of 500 GeV, which is intended to be later upgraded to 3 TeV. In order to reach this energy in a realistic and cost efficient way, an accelerating gradient of 100 MeV/m has to be applied. However, such a high value is outside the reach of any available SCRF technology. As a solution, the CLIC project proposes a novel two-beam acceleration technique in which 12 GHz RF (Radio-Frequency) pulses are extracted from a high current low

Figure 1.1 Overall layout of the ILC collider [7].

Figure 1.2 ILC beam structure.

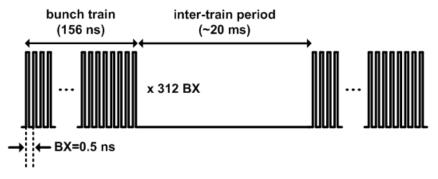

energy electron beam (named drive beam) running parallel to the main linac [9]. The drive beam is decelerated in special PETS (Power Extraction and Transfer Structures), producing an RF power that is transferred to the main beam. It is planned that a single drive beam will provide about 70 GeV to the main beam, which means that 22 drive beams will be needed to achieve a beam energy of 3 TeV. This concept leads to a quite simple tunnel, which covers a total length of up to 48 km. Two IPs are foreseen, one for e+e- collisions and another one for γ-γ collisions. A schematic layout of the CLIC accelerator is shown in Fig. 1.3. The luminosity peak of CLIC is around  $2 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> during the first stage and increased to almost  $6 \cdot 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup> after the upgrade. The CLIC machine will also operate in a pulsed mode: 156 ns long bunch trains of electrons and positrons will collide every 20 ms. With 312 bunches per train, BXs will occur every 0.5 ns. The beam has the bunch structure plotted in Fig. 1.4. This bunch structure, together with the higher center-of-mass energy, puts additional demands on future detectors. After the upgrade, at the IP the bunches will have horizontal and vertical sizes of 40 nm and 1 nm, respectively.

Figure 1.3 Overall layout of the CLIC collider at a center-of-mass energy of 3 TeV [10].

Figure 1.4 CLIC beam structure.

A CDR (Conceptual Design Report) describing the detector and physics issues of the CLIC accelerator was published in 2012 [10]. A decision for the final location has not been made yet, however site studies have shown that CLIC could be constructed underground in the CERN area. The construction of first stage could be accomplished in the years 2023-30, with commissioning starting in 2030.

#### 1.3 Detector systems in future linear colliders

Physics aims at the ILC and CLIC projects put highly challenging requirements on detector systems, which are intended to the reconstruction of the generated events. Particularly complex areas are the impact parameter resolution, track momentum measurement, jet flavor identification and jet energy reconstruction. These issues have been addressed for ILC in two

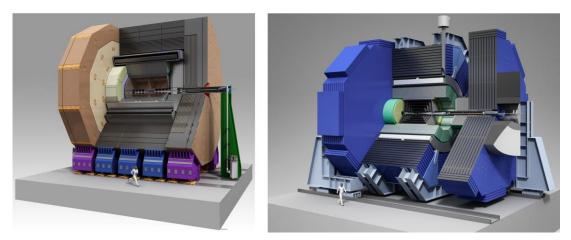

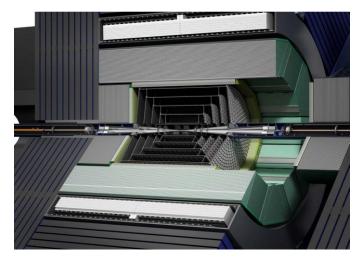

detector proposals based on a common structure but complementary technologies, the validated ILD (International Linear Detector) [11] and SiD (Silicon Detector) [12]. Fig. 1.5 shows the two detector prototypes. A detailed view of the SiD detector system can be seen in Fig. 1.6. Although the CLIC accelerator is based on a more ambitious concept, it also requires suitable detectors for the particular environment of a TeV scale e+e- collider. Therefore, CLIC has adopted the ILD and SiD detector proposals as well. Nevertheless, these have been modified to meet the more demanding specifications of CLIC.

Both ILD and SiD detectors are composed of several sub-systems, which proceed as follows. The innermost detector is the vertex detector, which consists of a multilayer barrel section of silicon pixels surrounding the beam pipe. The vertex detector is aimed to measure the displaced vertices (i.e. the charged particles coming out from a secondary vertex) of the heavy flavor particles and help in the track reconstruction. It is complemented by forward and backward silicon pixel disks to ensure tracking down to small angles. Then, the tracker detector, based on a gaseous TPC (Time Projection Chamber) surrounded by silicon strip and pixel layers for ILD and an all-silicon system for SiD, reconstructs the tracks of the charged particles and measures their momentum. The electromagnetic and hadronic calorimeters, located outside the tracker detector, are dedicated to energy measurements through the PFA (Particle Flow Algorithm) approach [13]. This precise but complicated technique involves the identification of energy deposits in the calorimeter and the association of these deposits with the charged particle tracks measured in the tracker detector. Both ILD and SiD proposals are also equipped with muon systems to identify isolated muons from the interaction point. Table 1.2 summarizes the technologies of the several sub-systems of ILD and SiD proposals.

#### 1.3.1 Tracking system requirements

To record the particle events in presently operating HEP facilities such as the LHC, hybrid pixel detectors are used. The readout circuits are fabricated in commercial CMOS technologies and connected to the sensors via bump bonding techniques. Since most of the present readout chips are built in 0.25  $\mu$ m CMOS technologies, this architecture sets a lower limit on the pixel cell size, which together with bump bonding constraints prevents a reduction of the pixel pitch below 50  $\mu$ m. Nevertheless, the goals of the ILC and CLIC physics programs impose such stringent requirements on the tracking detector system that exceed those met by any previous system. These requirements on the tracking system can be categorized as follows:

• A single point resolution ( $\sigma_{point}$ ) better than 5  $\mu$ m

Figure 1.5 ILD (left) [11] and SiD (right) [12] detector prototypes for ILC.

Figure 1.6 Detailed view of the SiD detector system, where it is possible to distinguish the several barrels and disks.

• A material budget below 0.15% (ILD) or 0.30% (SiD)  $X_0$  per layer, where  $X_0$  is the radiation length, to minimize the Coulomb multiple scattering

- A high granularity for good particle separation

- Single bunch crossing resolution

- An occupancy below 1%, including the background hits

- Radiation tolerance

- Average power less than a few  $mW/cm^2$

- EMI (ElectroMagnetic Interference) immunity

- An affordable cost

| ILD p           | roposal                     | SiD proposal                 |                                                                                                                 |  |

|-----------------|-----------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Sub-system      | Technology                  | Sub-system                   | Technology                                                                                                      |  |

|                 | Silicon pixels              |                              | Silicon pixels                                                                                                  |  |

| Vertex detector | - 3 barrel double<br>layers | Vertex detector              | <ul> <li>- 5 barrel layers</li> <li>- 4 forward disks</li> <li>- 4 backward disks</li> <li>- 3 disks</li> </ul> |  |

| SIT             | Silicon strips              |                              | Silicon string                                                                                                  |  |

| 511             | - 2 layers                  |                              | Silicon strips                                                                                                  |  |

| SET             | Silicon strips              | Tracker detector             |                                                                                                                 |  |

| SE I            | - 2 layers                  |                              | - 5 barrel layers<br>- 4 disks                                                                                  |  |

| ТРС             | MPGD readout                |                              | i dibito                                                                                                        |  |

| ECAL            | W absorber                  | ECAL                         | Silicon pixels-W                                                                                                |  |

| HCAL            | Fe absorber                 | HCAL                         | RPC-steel                                                                                                       |  |

| Coil            | 35 T field                  | Solenoid                     | 5 Tesla SC                                                                                                      |  |

| Muon            | Scintillator layers         | Flux return<br>(muon system) | Scintillator-steel                                                                                              |  |

Table 1.2 Technologies of the different subdetector systems (barrel) of the ILD and SiD proposals.

SIT stands for Silicon Internal Tracker, SET for Silicon External Tracker, TPC for Time Projection

Chamber, ECAL for Electromagnetic CALorimeter, HCAL for Hadron CALorimeter, MPGD for

Micro-Pattern Gas amplification Detectors, RPC for Resistive Plate Chamber and SC for

SemiConductor.

These specifications drive the design of the future tracking systems. In particular, the need for an accurate particle track reconstruction implies excellent single point resolution and minimum multiple scattering. Thus, the requirement on a 5  $\mu$ m single point resolution, set by the multilayer barrel geometry, implies a pixel size of 17  $\mu$ m as it is inferred from

$$\sigma_{point} \le pixel \ size / \sqrt{12} \ . \tag{1.1}$$

To reduce the multiple scattering on the quantity of material crossed by the particles, and hence reduce the uncertainty in the reconstruction of the traces, the overall material budget of the system has to be minimized. Therefore, considering a maximum 0.15-0.30%  $X_0$  per layer in the central region of the tracker, the thickness of the silicon detectors has to be 150 µm or 300 µm at the most. Moreover, because the detector has to be built with the lowest material budget possible to reduce the multiple scattering, no active cooling is allowed inside the acceptance region. Thus, the cooling system relies on forced cold air.

A high granularity is required for good particle separation, i.e. to deal with high particle fluxes and reduce the influence of overlapping events.

Another issue to be handled by the future tracking systems is the timing resolution, which is dictated by the bunch train time structure and the required pixel occupancy. If the detector is not fast enough to read each single bunch crossing, then the signals may be integrated and read out multiple times in one train (technique known as time slicing) to keep the occupancy below 1%. Alternatively, time-stamping can be performed to divide the bunch train into several timebuckets, each of which corresponds to one bunch crossing. The occupancy is mainly generated by beam-induced background events, which are dominated by beamstrahlung photons, and varies with the radius of the layer. According to the studies on ILC performed by the ILD group, the typical background events will range from 0.019 hits/cm<sup>2</sup>/BX in the first layer to 0.001 hits/cm<sup>2</sup>/BX in the last layer of the tracker detector at a nominal energy of 1 TeV [11]. Thus, at the ILC accelerator, with 2820 bunches/train, 337 ns bunch-spacing and 5 Hz repetition rate, an occupancy low enough not to affect the pattern recognition should be achievable by reading the detector 20 times per bunch train (each 50  $\mu$ s) for a sensor size of 25  $\mu$ m x 25  $\mu$ m. However, the requirement on the occupancy is more challenging at CLIC given the increased background events due to the higher energy of the accelerator and the shorter bunch-spacing. A background level of 0.87 hits/cm<sup>2</sup>/BX is foreseen in the tracker detector of CLIC [14]. The CLIC bunchspacing of 0.5 ns and the train length of 156 ns are too short to achieve a reduction of the backgrounds by fast readout. Instead, time-stamping capabilities need to be available for the tracker detectors. The time-stamping technique could reduce the pile-up from two photon background events to  $\leq 20$  bunch crossings.

The required radiation tolerance follows entirely from the beam-induced backgrounds, which is expected to affect predominantly the innermost layer. This way, a maximum TID (Total Ionizing Dose) of up to 1 kGy/year and a neutron fluence or NIEL (Non-Ionizing Energy Loss) of approximately  $10^{11}$  n<sub>eq</sub>/cm<sup>2</sup>/year is expected near the ILC beam pipe. In contrast, the TID and NIEL for CLIC are 200 Gy/year and  $10^{10}$  n<sub>eq</sub>/cm<sup>2</sup>/year, respectively. These data include some safety margin.

The power consumption should be low enough to minimize the material budget of the cooling system inside the detector sensitive volume. An affordable cost should be considered, since large-area detectors are foreseen.

#### 1.3.2 Tracking technology options

The requirements on the tracker detector system of the future linear e+e- collider outlined in the previous section are at least challenging. At present time, there is no mature technology available in the market that can fulfill all of them and new detector systems are being developed in parallel with the accelerator. The detectors that concentrate most of the R&D (Research and Development) carried out worldwide are based on CMOS pixel technologies, either monolithic, hybrid or 3D. Leading sensor techniques are DEPFETs (DEPleted Field Effect Transistors) [15], MAPS (Monolithic Active Pixel Sensors) [16] and FPCCDs (Fine Pixel Charge Coupled Devices) [17]. Alternative approaches are based on Chronopixels [18], Timepix [19] and GAPDs [20]. Yet another approach is to exploit the new emerging technologies for tracking sensors, which include the SOI (Silicon-On-Insulator) [21] and 3D [22] technologies. The main features of the proposed tracker detectors are summarized in Table 1.3.

#### **1.3.2.1 DEPFETs**

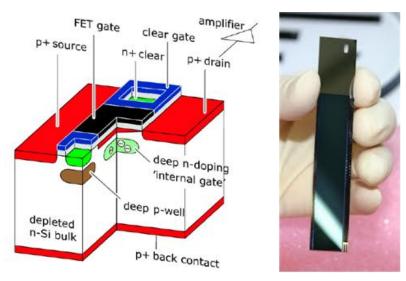

The DEPFET concept integrates a pMOS field effect transistor in each pixel of a fully depleted n-substrate to be used as a sensing and amplifying element (Fig. 1.7 for schematic view of the structure). The transistors also incorporate an internal gate, which is accomplished by an additional deep n-doped implantation situated underneath the transistor channel at approximately 1 µm depth. The internal gate creates a local potential minimum for majority carriers (electrons in the case of an n-substrate). If a ionizing particle enters the sensor, electron-hole pairs are created in the depleted substrate. The holes drift to the backside contact of the substrate, but the electrons are collected and stored by the internal gate. The charge collected leads to a change in the potential of the internal gate, which results in a modulation of the detector. After readout, the charge collected is removed from the internal gate by applying a positive voltage at a clear contact. The extremely low capacitance (10-20 fF) of the internal gate ensures low noise operation. In addition, a 100% fill-factor (i.e. the ratio between the sensitive area and

| Detector                   | DEPFET      | MAPS                                                        | FPCCD                                            | Chrono.  | Timepix                   | GAPD             | SOI              |

|----------------------------|-------------|-------------------------------------------------------------|--------------------------------------------------|----------|---------------------------|------------------|------------------|

| σ <sub>point</sub><br>(μm) | ~1          | ~3                                                          | -                                                | ~3       | 2.3                       | ~5               | ~1               |

| Mat. budg.<br>(μm)         | 50          | 50                                                          | 50                                               | 50 - 100 | 300                       | 250              | 70               |

| Gran.<br>(μm x μm)         | 20 x 20     | 18.4 x 18.4                                                 | 5 x 5                                            | 10 x 10  | 55 x 55                   | 20 x 100         | 13.75 x<br>13.75 |

| Timing                     | integration | integration                                                 | integration                                      | stamping | stamping                  | single-<br>bunch | integration      |

| Radiation<br>tolerance     | 10 kGy      | $\frac{10 \text{ kGy}}{10^{13} \text{ n}_{eq}/\text{cm}^2}$ | 10 <sup>12</sup> e <sup>-</sup> /cm <sup>2</sup> | —        | 4 Mgy                     | -                | 1 kGy            |

| Power                      | 5 W         | 250 mW/cm <sup>2</sup>                                      | 16 mW/ch                                         | _        | 886<br>mW/cm <sup>2</sup> | _                | _                |

| Fill-factor<br>(%)         | 100         | 100                                                         | 100                                              | 100      | 87                        | 67               | 100              |

Table 1.3 Main features of the proposed tracker detectors for the future linear colliders.

the total area occupied by the detector) can be achieved with this detector.

The DEPFET concept was proposed in 1987 by Kemmer and Lutz. Since 2002, intense R&D of this technology has been carried out by an international collaboration named the DEPFET collaboration. As a result, the DEPFET detector has now reached some level of maturity, including their performance in beam-tests at CERN [23] and DESY [24]. The first production of DEPFET sensors took place in 2004 and several generations with different configurations have already been fabricated at the Semiconductor Laboratory of the Max Planck Society. Matrices with up to 64 x 256 pixels and small sensors of 20 µm x 20 µm have been successfully produced in 50 µm thickness wafers. However, the development of larger matrices with the required sensor area is still ongoing. DEPFET prototypes for the future tracker detectors are based on a ladder structure (Fig. 1.7), with the sensitive area placed in the central region and steering and readout ASICs bump bonded at the balconies. The chips, fabricated in three different standard CMOS technologies, are used to operate and read out the DEPFET matrix in a rolling shutter mode with zero suppression and correlated double sampling. Nevertheless, the current readout speed of 80 ns/row has to be improved to achieve a frame readout time of 50 µs and satisfy the ILC requirements. The main results from the DEPFET beam-tests are a SNR (Signal-to-Noise Ratio) better than 110, a detection efficiency of 99.96% and an intrinsic spatial resolution around 1  $\mu$ m [23]. The power consumption of the active area of the DEPFET sensors is very low since the pixels passively collect the charge and only need power during the readout cycle. A total power consumption of 5 W is foreseen for the whole DEPFET tracker detector. The results from several irradiation campaigns show a remarkable radiation tolerance to 10 kGy. At current time, it is established that the DEPFET technology will

Figure 1.7 Schematic view of a DEPFET pixel structure (left) and mechanical sample of the ladder structure (right).

be used as an inner detector in the Belle II experiment at the Japanese SuperKEKB factory, starting at 2015.

#### 1.3.2.2 MAPS

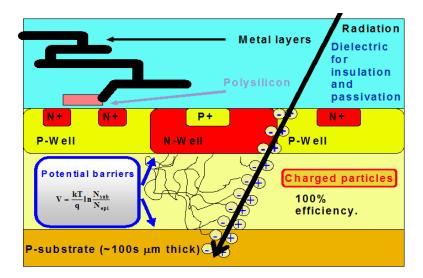

MAPS sensors are based on an n-well/p-epi diode implemented in a standard CMOS technology (Fig. 1.8). These devices use the lightly doped p-epitaxial layer on a low resistive p-substrate as the active detector volume. The charge generated by the impinging particles in the epitaxial layer reaches the n-well diode contacts by diffusion, which results in long collection times around 100 ns and considerable charge spread over several pixels. The epitaxial layer is thin, and this yields only small signals. Thus, for instance, about 1000 electron-hole pairs produced by a MIP (Minimum Ionizing Particle) are collected with an epitaxial layer of some 10-20 µm thickness. On the other hand, the intrinsic capacitance of these devices is very low and excellent SNRs have been reported [25]. A three-transistor readout circuit does the amplification and row/column selection of the respective pixel. MAPS detectors are usually read out in rolling shutter mode at a typical speed of 200 ns/row. Because the readout circuit is placed on top of the active volume, a 100% fill-factor is possible.

MAPS were re-invented in the early 1990's on both sides of the Atlantic with the establishment of the CMOS process. These sensors have become so far one of the leading technologies in the imaging field. Aimed to particle physics experiments, several MAPS prototypes named MIMOSA (Minimum Ionizing particle MOS Active pixel) have been fabricated since the 2000's. In particular, the MIMOSA-26 [26] sensor equips the final version of the EUDET beam telescope [27], which at present time is an essential part of the beam-test set-ups of novel tracking detector technologies. This chip was fabricated in the AMS (Austrian Micro Systems) 0.35 µm OPTO technology in 2009. The pixel matrix is composed of about 0.7 million pixels distributed in 1152 columns and 576 rows. It has a total sensitive surface of 2.2  $cm^2$  (pixel size of 18.4 µm x 18.4 µm). Rows are read one by one in a rolling shutter mode while amplification and correlated double sampling are implemented inside each pixel. The chip also incorporates pixel output discrimination for binary readout and zero suppression circuits at the matrix periphery to stream only the fired pixels out. The address and length of consecutive fired pixels is stored in embedded memories. The memories are serially read out with two 80 Mbits/s outputs, which allow to read out the whole pixel matrix in 112  $\mu$ s. This prototype has shown a 99.5% detection efficiency for an average fake rate below  $10^{-4}$  fake hits per pixel, combined with a spatial resolution close to 3  $\mu$ m, radiation tolerance of up to 10 kGy of ionizing dose and  $10^{13} n_{eq}/cm^2$  fluence, and power consumption of 250 mW/cm<sup>2</sup>. The MIMOSA-26 is also the sensor of choice for the upgrade of the inner detector in the STAR (Solenoidal Tracker

Figure 1.8 Schematic cross-section of a MAPS sensor.

At RHIC) experiment at the RHIC (Relativistic Heavy Ion Collider) accelerator [28], which is the first application of a MAPS detector at a collider.

#### 1.3.2.3 FPCCDs

The fundamental sensing element of CCD pixels is a MOS (Metal Oxide Semiconductor) capacitor, which is implemented by means of a polysilicon gate, a thin film of silicon dioxide  $(SiO_2)$  and a weakly doped p-epitaxial layer (~15 µm thickness) laid on top of a highly doped psubstrate. Moreover, an n-type implantation is added to the epitaxial layer in the form of a buried channel at approximately 1 µm beneath the Si/SiO<sub>2</sub> interface to create a potential minimum for minority carriers (electrons in the case of a p-substrate). During the so-called integration time, a positive bias voltage is applied to the gate electrode to create a depletion region in the upper volume of the epitaxial layer. The electrons generated due to the passage of a ionizing particle are transported by drift to the potential minimum. The charge collected is confined within the potential well by means of a superior surrounding potential, which is generated by neighboring gates (termed barriers) biased at a negative voltage. Although there exist several strategies to transfer the charge packets to the readout node, the three-phase CCD clocking approach is the most common. In this configuration, every third electrode of a matrix of CCD pixels is connected to the same voltage. By pulsing the gates in an appropriate sequence through a shift register, the charge packets are transferred in parallel down the detector one row at a time. The lowest line is connected to a serial readout register, which runs orthogonally to the columns of the sensing matrix. The serial register feeds an output amplifier connected to an ADC (Analog to Digital Converter).

CCDs were invented in 1969 by Boyle and Smith at the Bell Telephone Laboratory to be used as computer memories [29], although their huge imaging capabilities were immediately recognized. Today, these devices are regarded as one sensor of choice for both commercial and research applications. Concerning particle physics experiments, CCD detectors also have a large experience. They demonstrated, for instance, a successful performance at the SLAC facilities with the SLD (SLAC Large Detector) experiment [30, 31]. However, this technology cannot fulfill the requirements of the future generation of e+e- colliders, mainly due to its low speed operation and radiation intolerance. To address this issue, several CCD-based approaches are being developed at present time, such as the CPCCD (Column Parallel CCD) [32] and ISIS (In-Situ Storage) [33] by the LCFI (Linear Collider Flavor Identification) collaboration or the FPCCD (Fine Pixel CCD) [17] by the ILC-FPCCD vertex group. In particular, the FPCCD concept makes use of finely segmented sensors of 5  $\mu$ m x 5  $\mu$ m to achieve a low hit occupancy below 1% even integrating the detector over a full bunch train. Moreover, the extreme granularity also results in a sub-micron single point resolution and excellent two track separation capability. However, because of the small sensor size, there is a large number of pixels in one channel (20000 x 128). Therefore, the readout speed must be above 10 Mpix/s to read all the pixels in the inter-train time (199 ms). Another inconvenience of using such a small sensor size is the reduced number of electrons ( $\sim$ 500) that will be produced if a ionizing particle penetrates the detector horizontally. A total noise level below 50 electrons is desirable. Consequently, this technology requires a low-noise multi-channel readout ASIC, which employs an amplifier, a low pass filter, correlated double sampling circuitry and two ADC converters [34]. The power consumption of the detector should be below 16 mW/ch. In addition, cooling at  $\sim -40$  °C will be needed to reduce the thermal noise due to the relatively long readout time and suppress the effects of radiation damage. The fabrication of the first sensor and ASIC prototypes took place in 2007 and their development is still ongoing.

#### 1.3.2.4 Chronopixels

The chronopixel technology is based on the same sensing mechanism as MAPS. However, this concept includes additional in-pixel electronics to record the time (i.e. to put a time-stamp) of each hit with enough precision to assign it to one particular bunch crossing of an entire bunch train. Thus, the occupancy is reduced to negligible levels, even reading the chip out during the 199 ms quiet gap between bunch trains.

The development of this detector is being carried out by the Oregon University and Yale University in collaboration with the SARNOFF Corporation since 2004. So far, the chronopixel architecture has been defined and two prototypes have been designed and fabricated [35]. To store the time of each hit, the in-pixel electronics comprise a voltage comparator, a local counter, a digital memory and a reset transistor. The detector proceeds as follows. After each bunch crossing, the signal of each pixel is compared to a preset calibrated threshold level set at 200 electrons/pixel. If the signal is above the threshold (i.e. a ionizing particle has crossed the sensitive layer), the memory is enabled to latch in its first 14-bit slot the time-stamp data supplied by a global counter. Then, the sensor is reset, the memory pointer is advanced by the local counter and the pixel is ready for the following bunch crossing. Up to a total of four hits per bunch train can be time-stamped in the memory, since the Poisson probability of more than 4 impacts per pixel and train is less than  $>10^{-4}$ . The stored non-zero time-stamp data of hit pixels is read out in random access mode during the 199 ms gap between bunch trains. To squeeze the 645 transistors that are necessary to operate the chronopixel in a 10 µm x 10 µm pixel (needed to achieve a precision of 3-4  $\mu$ m), a still extremely expensive 45 nm process technology is required. Instead, the first prototype with 50 µm x 50 µm pixels was fabricated in the TSMC 180 nm technology in 2008 (Fig. 1.9). Alternatively, the second prototype was built on the TSMC 90 nm technology in 2012, which allowed to reduce the pixel size to 25  $\mu$ m x 25  $\mu$ m. Although these choices lead to poor efficiency, they have permitted to show that the general concept of the device is working and also to prove the main assumptions on noise level, power consumption and digital circuitry flexibility. Plans for a third prototype are already set. In the final design, the detector will consist of 12500 rows per 2000 columns of pixels, divided into 40 readout regions of 50 columns each. At the end of the bunch train, the 40 regions will be read out in parallel and temporarily stored in a FIFO before leaving the chip, requiring about 8 ms to read out the entire detector. According to estimations, the analog parts of the circuit (i.e. the sensor and the comparator) will consume around 15 mW/mm<sup>2</sup>, which represents most of the power. Nevertheless, the average power consumption can be reduced to 0.4 W per chip, or

Figure 1.9 Image of the 645 transistor pixel design [18].

about 100 W for the whole detector, by switching off the analog power between bunch trains.

#### 1.3.2.5 Timepix

The Timepix is a pixel readout chip intended for a TPC, the gaseous main particle tracker of the ILD detector concept. The design of the Timepix chip is derived from the Medipix2 [36], a chip from the Medipix family that was devised for single photon counting in imaging and medical applications in the early 2000's. The idea was to keep the Timepix as similar as possible to the Medipix2 in order to benefit from large prior effort and reduce the risk of chip failure. The development of the Timepix chip took place at CERN by the Medipix2 collaboration with support of the EUDET project.

In very broad terms, the performance of a TPC tracker detector is described next. Similarly to silicon tracker detectors, a charged particle passing through the sensitive gas volume contained in a TPC produces a primary ionization path along its track. Then, the electrons from the ionization drift towards a readout anode plate, where they are collected. Mounted on top of the anode plate typically stands a gain grid system, which is used for charge amplification prior to processing. The Timepix readout chip has been proposed as a novel solution for a pixilated charge collecting anode. It has shown very promising results when coupled to GEM [37] (Gas Electron Multiplier) or Micromegas [38] (MICRO Mesh GASeous detector) gain grids. The Timepix chip consists of an array of 256 rows x 256 columns of 55  $\mu$ m x 55  $\mu$ m pixels, with an 87% detection area. Each pixel is equipped with a preamplifier, a discriminator with a globally adjustable threshold, mode control logic and a 14-bit counter. The Timepix chip can be configured in one of four different operation modes: masked, counting, TOT (Time Over Threshold) and TOA (Time Of Arrival). In the masked mode, the pixels are off. In all the others, the pixels are activated by a binary signal called the shutter signal. During the shutter time, the pixel counter is triggered when the signal from the preamplifier crosses the threshold level of the discriminator. The counting mode, also named the medipix mode, is used to count the number of hits. In contrast, in the TOT and TOA modes the counter is used to count the number of clock cycles provided by a reference clock with a frequency of up to 100 MHz. In the TOT mode, the value of the counter is equal to the number of clock cycles elapsed during the time that the signal pulse was above the threshold. The value of the counter is an indication of the total energy deposited. Finally, in the TOA or Timepix mode, the counter records the number of clock cycles counted during the time between the first hit and the end of the shutter time. The TOA mode is used to associate hits to the correct bunch crossing via time-stamping.

The first prototype was fabricated in the IBM 0.25  $\mu$ m technology in 2006. The entire chip is read out after the shutter signal goes down by means of either on-chip LVDS drivers in ~5 ms or a 32-bit parallel bus in ~300  $\mu$ s. The power consumption of the analogue and digital parts is respectively 440 mW and 450 mW. A detection efficiency greater than 99.5%, pointing resolution around 2  $\mu$ m and time resolution in the nanosecond scale have been demonstrated in several beam-test campaigns using 300  $\mu$ m thick devices. The radiation tolerance has been tested to be 4 Mgy. Moreover, the Timepix chip together with the Medipix2 chip equip a prototype telescope aimed to particle tracking [39]. An improved version of the Timepix chip, the Timepix3 [40], is being developed by the Medipix3 collaboration. It will be fabricated in the IBM 130 nm technology in 2013. This chip will allow simultaneous measurements in the TOT and TOA modes, zero suppression, data driven readout (each hit is time-stamped, labeled and send off-chip immediately) and power pulsing to reduce the consumption to 886 mW/cm<sup>2</sup>. The Timepix technology is also being considered for the LHCb VELOpix upgrade [41].

#### 1.3.2.6 GAPDs

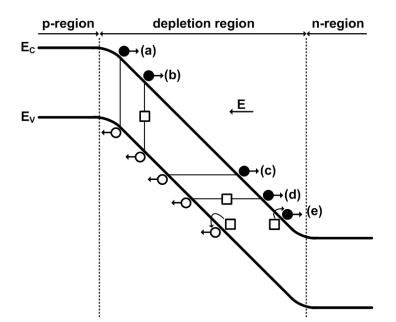

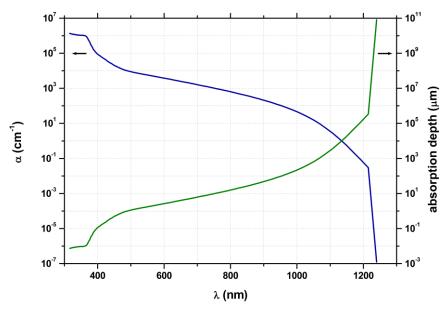

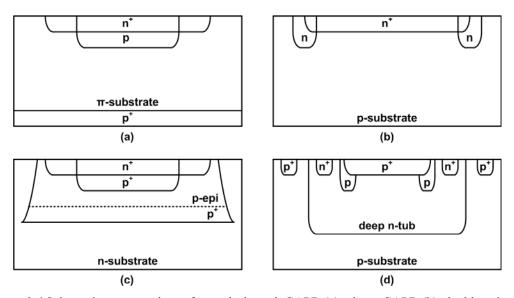

In conventional CMOS technologies, GAPD detectors are typically implemented by means of a  $p^{+}/n$ -well junction on a p-substrate, even though  $n^{+}/p$ -well junctions inside a deep n-well for isolation from the substrate are also possible. These photodiodes are reverse biased above the breakdown voltage of the junction to operate the Geiger-mode, condition at which impinging radiation being absorbed by the multiplication region can trigger an avalanche process of generation of electron-hole pairs. As a result, a macroscopic current pulse (gain 10<sup>5</sup>-10<sup>6</sup>) that can be detected by the readout electronics is generated in a few hundred picoseconds. A simple CMOS inverter is generally used as an avalanche discriminator and digitizer. Preamplifiers or pulse shapers are therefore unnecessary. However, avalanche events are due not only to the absorbed radiation, but also to the noise phenomena generated by the sensor. Since the noise avalanches cannot be distinguished from real events, low SNRs and high occupancies may be anticipated unless power pulsing and/or cooling are applied. On the other hand, GAPD detectors can be read out in a number of different ways, such as random access, sequential by rows or columns, event-driven and pipelined. For a fixed array size, the whole GAPD detector can be read after each bunch crossing if a proper readout strategy is implemented in a fast enough technology process. Given that only the junction area is sensitive to impinging radiation, a 100% fill-factor is not possible with this sensor technology.

Although the first studies on the avalanche multiplication phenomenon in p-n junctions started in the 1960's at the Shockley laboratory [42, 43], it was not until the 1990's that solid-state avalanche detectors became available in a CMOS compatible process [44]. However, only

the monolithic integration of a GAPD sensor and the front-end electronics on a single CMOS die in 2003 [45] opened the way to commercial applications. Since then, intense R&D of this technology has been conducted by several research groups. Good proof of this is the great number of prototype GAPD cameras that have been produced in different standard CMOS technologies in the last ten years, aimed mostly to single-photon detection. In spite of this, the behavior of GAPDs in the detection of high energy particles was not explored until recently. Beam-tests started in 2012 at the SPS (Super Proton Synchrotron) area of CERN and are still ongoing [46]. The radiation tolerance of a GAPD detector fabricated in a HV-AMS 0.35  $\mu$ m CMOS technology has been tested to be around 1 kGy for gamma rays and around 100 Gy for protons [47]. More details about the characteristics of this sensor technology as well as a complete description and characterization of the first GAPD detector aimed at HEP experiments will be given in the next chapters.

#### 1.3.2.7 SOI

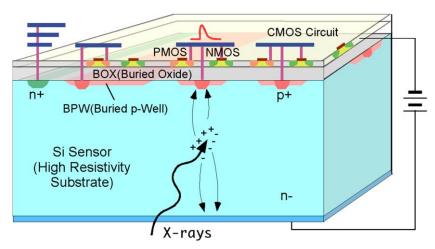

In the SOI technology, a thin buried oxide (BOX) is used to electrically insulate the CMOS readout electronics from the high resistivity charge-collecting substrate (Fig. 1.10). The CMOS electronics is implanted on a 40 nm thin silicon layer, which is fully depleted at typical operational voltages, on top of a 200 nm thick BOX layer. Vias are etched through the buried oxide to contact the transistor layer to the detector substrate, so that topside reverse bias of the n-substrate can be applied and  $p^+$  pixel implantations that collect the charge signal can be contacted. The isolation between the transistor layer and the detector substrate ensures high latch-up immunity as well as a reduced junction capacitance. The substrate can be back-thinned to 70 µm, which together with the low junction capacitance improves the speed and power consumption. However, the reverse bias applied to the detector substrate induces a potential below the CMOS electronics layer, which typically shifts the threshold voltage of the CMOS transistors. This phenomenon, known as back-gating effect, was observed in the first prototypes and limited the charge collection. It has already been addressed by implanting a BPW (Buried P-Well) region beneath the BOX, which screens the potential applied to the substrate.

The SOI pixel detector is developed by the SOIPIX collaboration, the members of which are distributed amongst Asia, America and Europe. A number of prototypes have been designed by different research groups and fabricated by Lapis Semiconductor Co. Ltd. (formerly OKI Semiconductor) in MPW (Multi-Project Wafer) runs since 2006. The first set of prototypes was manufactured in a standard 0.15  $\mu$ m CMOS technology on fully depleted SOI wafers. However, the shutdown of this process line in 2007 forced migration to a 0.20  $\mu$ m process. Some examples of the prototypes under development are the INTPIX (INtegration-Type PIXel

#### SOI Pixel Detector

Figure 1.10 Cross-section of the SOI monolithic pixel device [48].

detector) and CNTPIX (CouNting-Type PIXel detector) series [48] by KEK (High Energy Accelerator Research Organization), the LDRD-SOI (Laboratory Directed Research and Development-SOI) [49] and SOImager [50] series mainly by LBNL (Lawrence Berkeley National Laboratory) and INFN (Instituto Nazionale di Fisica Nucleare) and the MAMBO (Monolithic Active pixel Matrix with Binary cOunters) series [51] by FNAL (Fermi National Accelerator Laboratory). In particular, the SOImager-2 chip, fabricated in 2010, contains a matrix of 256 x 256 pixels arrayed on a 13.75  $\mu$ m pitch. The in-pixel analog readout electronics employs a reset transistor, a source follower and a transmission gate for row selection. The pixels are read out through four parallel arrays of 64 columns each in a rolling shutter mode with 1-1.5 kframes/s (656  $\mu$ s integration time). This chip has been successfully tested in a beamtest at CERN with 300 GeV pions, showing a detection efficiency of 99% and an intrinsic single point resolution around 1  $\mu$ m. The SOI technology is immune to SEEs (Single Event Effects) given the reduced thickness of the transistor layer, but not to TID (Total Ionizing Dose) due to the presence of the BOX layer. The tolerance of the SOI technology to total dose effects has been measured to be 1 kGy.

#### 1.3.2.8 3D

In microelectronics, the 3D-IC (3D-Integrated Circuit, i.e. a vertically integrated circuit) technology concept refers to the stacking of multiple thin logic dies (named tiers) equipped with deep metal vias (named TSVs as Through-Silicon-Vias) to form a monolithic device. The potential of this technology lies in the fact that it allows to split the sensor, readout electronics and digital blocks into different layers in order to overcome some of the intrinsic limitations of the tracker detector candidates, while still preserving the fabrication with standard CMOS

processes. At the same time, it also allows to achieve higher densities of integration without having to use nanometer technologies, which complicate the design of analog circuits and suffer from high technologic deviations. Thus, for instance, due to the utilization of n-well diodes as a charge collection device, MAPS may take advantage of the 3D-IC alternative to go beyond the prohibition of pMOS transistors inside the sensing area [52], which severely limits the choice of the readout electronics circuitry. Moreover, there exist groups working with the traditional HEP hybrid pixel approach in 3D (ATLAS effort for 3D integration) with the goal of reducing the pixel size while keeping the 130 nm feature size. Nevertheless, the 3D-IC option can also be used as a solution to increase the fill-factor of GAPD detectors [53], which rarely exceeds the 10% when fabricated in conventional 2D technologies. Although the 3D-IC technologies are being pursued in many different forms, they can be classified into two main categories depending on the nature of the interconnection process between tiers. Essentially, 3D-ICs can be manufactured by independently fabricating the 2D logic dies corresponding to the different tiers in separate wafers, then aligning and interconnecting them through TSVs. However, TSVs may be an integral part of the foundry process, being formed before or right after the FEOL (Front-End-Of-Line) processing, or may be added as the last step after wafer bonding in the areas being free of active circuits. The first approach is called via-first and the second one via-last [54].

The VIP (Vertically Integrated Pixel) chip, the first readout chip fabricated in a 3D-IC approach inside the HEP community, was conceived as a demonstration of 3D-IC technologies aimed at ILC. The first version of this chip (named VIP1) was produced in a 3-tier 180 nm FD-SOI process at MIT-LL (Massachusetts Institute of Technology-Lincoln Laboratory) [55]. The design was submitted for fabrication in October 2006. However the first set of dies was not delivered until November 2007, which reflects the complexity of the 3D endeavor undertaken by a non-commercial VLSI line. The VIP1 prototype features 20  $\mu$ m x 20  $\mu$ m pixels, which are laid out in an array of 64 x 64 elements. In-pixel electronics to perform analog and digital operations are distributed between the three tiers, so that the critical analog functions consisting of integration, discrimination and correlated double sampling are on the top tier (closest to the detector), and the digital readout with zero suppression is on the bottom tier (farthest from the detector). The intermediate layer is used for implementing the time-stamping circuitry. In the present technology, TSVs are added in a via-last process. Moreover, stacked TSVs from the bottom tier to the top one are allowed. Bonding from the intermediate tier to the bottom one is done face-to-face, while from the top tier to the intermediate one is done face-to-back. Although a very low yield and some problems related to flaws in the processing of individual tiers were found amongst the fabricated devices, the tests performed on the VIP1 chip showed a correct functional operation of the structure. All the interconnections between the circuit layers worked, which was considered as a major success.

In spite of the MIT-LL efforts to produce 3D-IC devices, a 3D-IC Consortium led by FNAL was formed in 2008 to explore various issues associated with vertical integration [22]. This consortium promotes MPW runs in the Global Foundries (previously Chartered Semiconductor)/Tezzaron 3D process, which typically consists of two logic dies fabricated in the Global Foundries 130 nm technology and vertically integrated by Tezzaron. Global Foundries uses a via-first approach to add 6 µm deep TSVs to a standard 130 nm CMOS technology. The TSVs are then used to interconnect the logic circuitry to the backside I/O pad cells of the top tier. Tezzaron performs the 3D stacking using face-to-face wafer-to-wafer bonding through the top copper metal layer of the technology, thus allowing the connection of relaying signals between tiers. Although the designs for the first MPW run in the Global Foundries/Tezzaron 3D process organized by the 3D-IC Consortium were initially completed in May 2009, they were not accepted for fabrication until March 2010 due to numerous problems related with the utilization of different versions of the design kit provided by Tezzaron, misinterpretation of the design rules or shifting requirements of Global Foundries [56]. Moreover, the transition from Chartered Semiconductor to Global Foundries also slowed the wafer fabrication process. Last but not least, the first lot of wafers was misaligned for 3D bonding and 2D performance could be tested only after delivery in November 2010. The tests of these devices at several laboratories confirm a good correspondence to simulations and show a similar behavior between chips with and without TSVs. The first 3D wafer was delivered in November 2011 and tests are ongoing. However, due to the mentioned technical difficulties, more time and funding will be required for this 3D-IC technology to reach maturity. More details on the Global Foundries/Tezzaron 3D process will be given in Chapter 5.

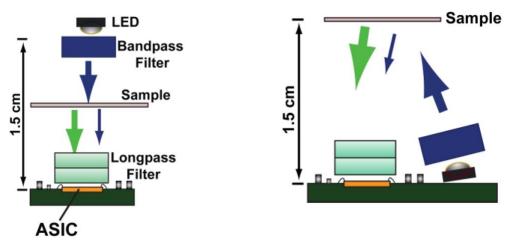

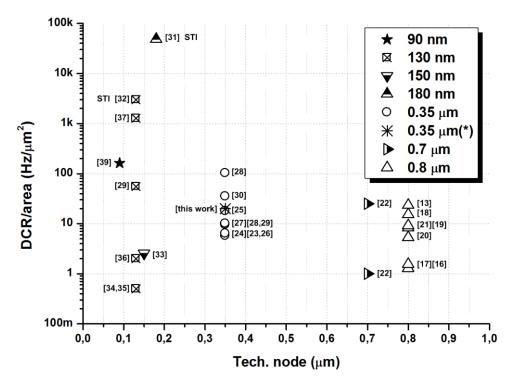

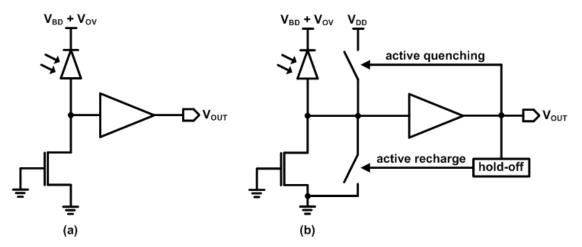

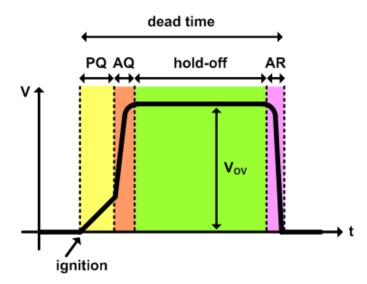

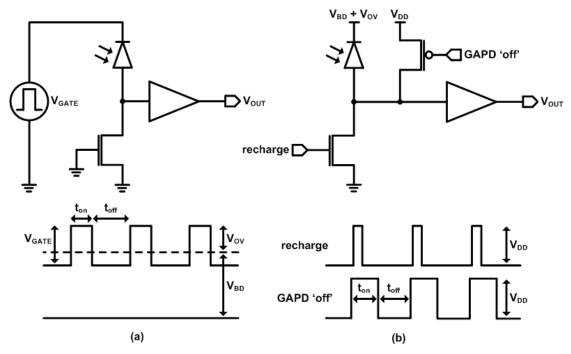

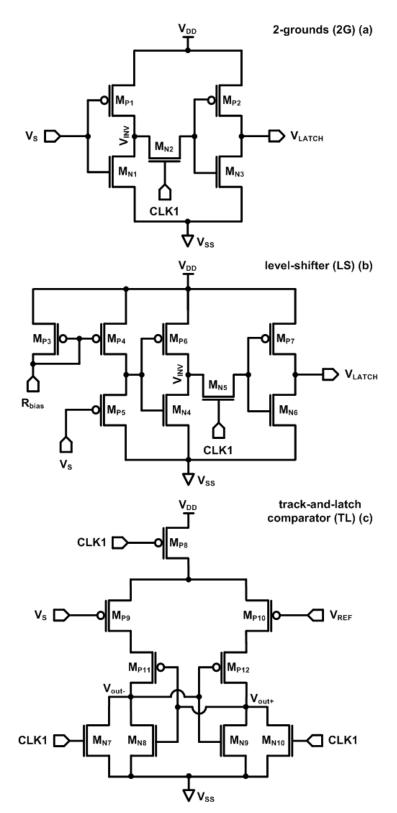

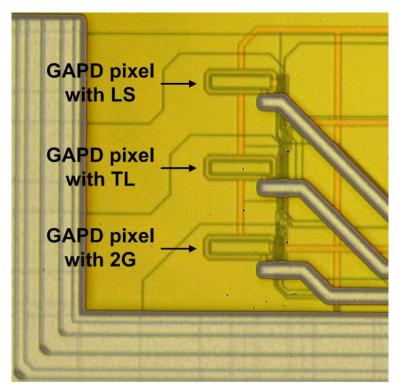

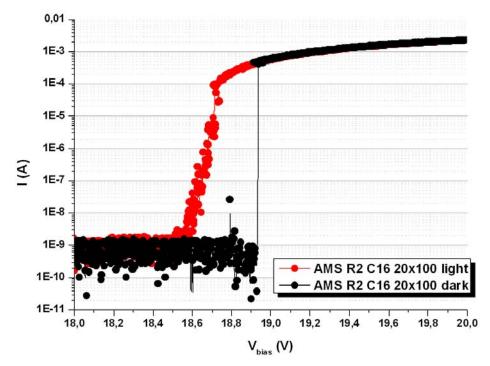

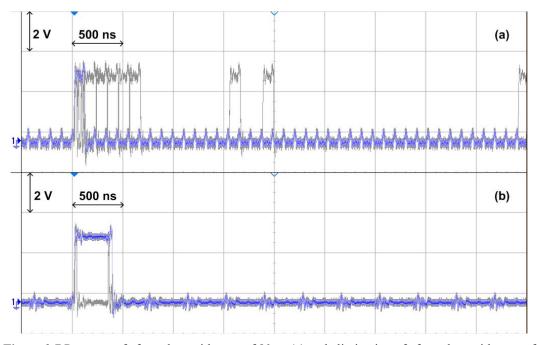

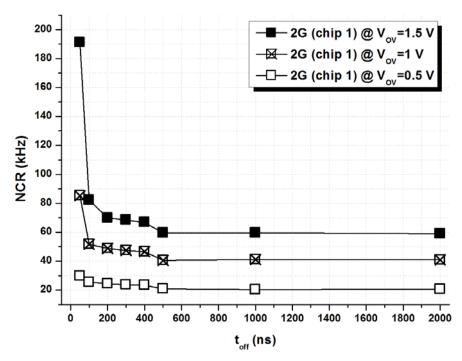

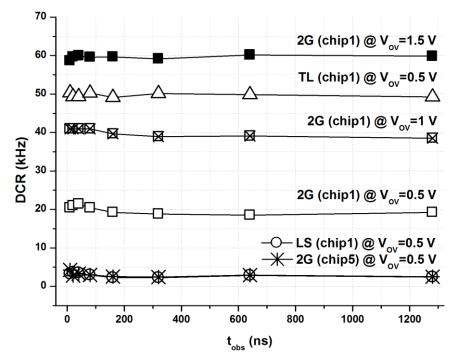

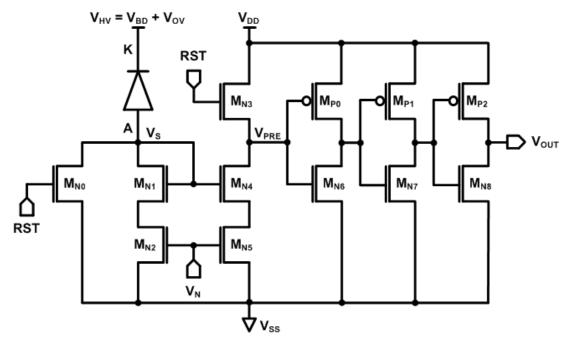

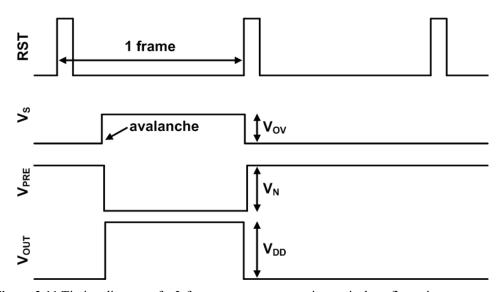

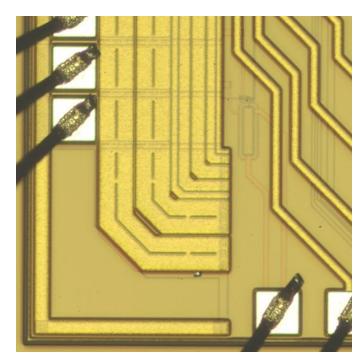

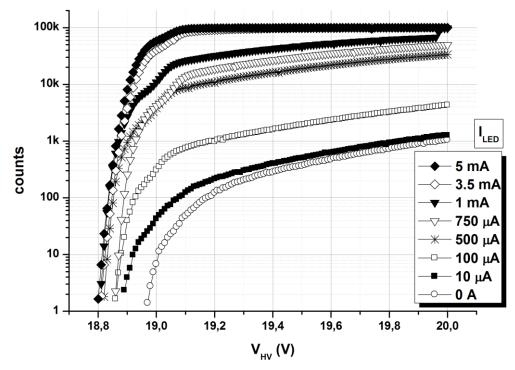

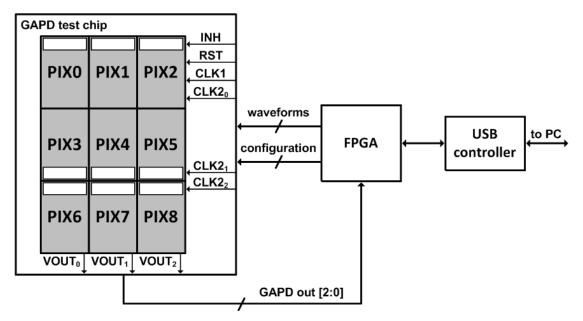

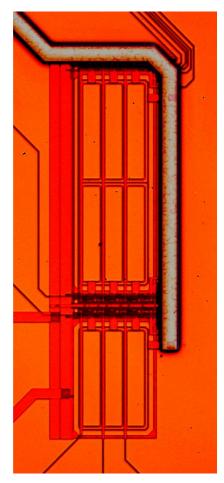

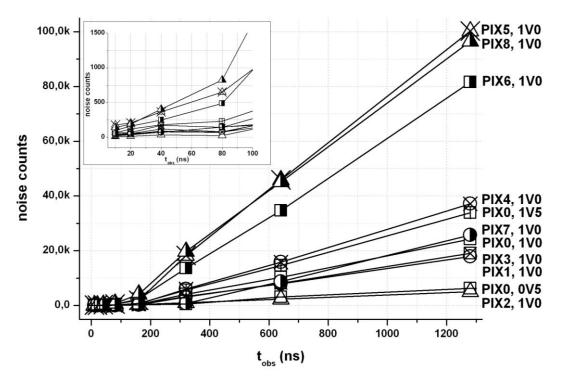

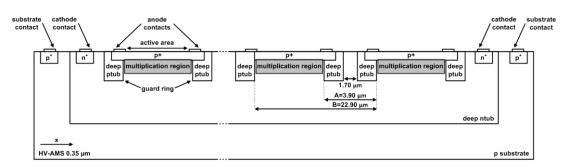

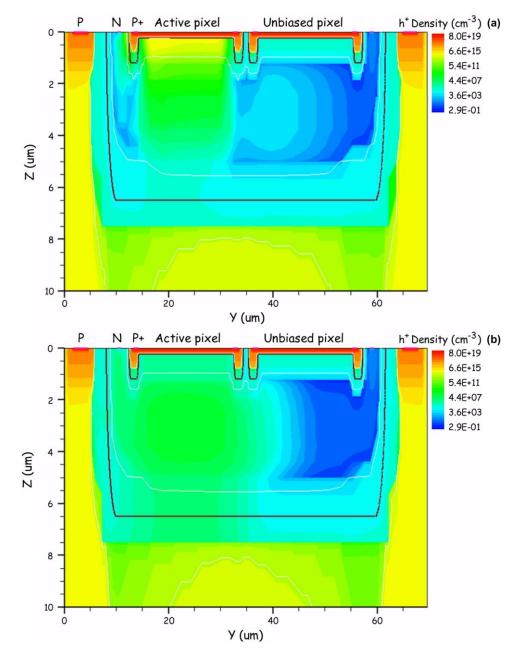

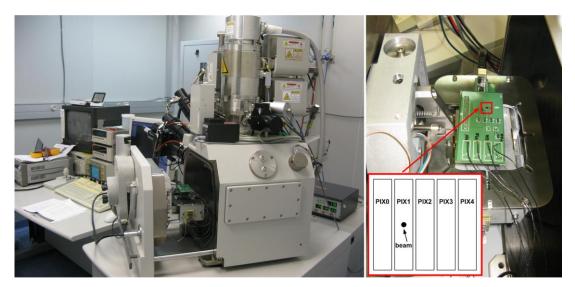

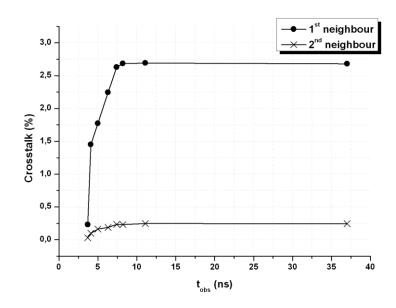

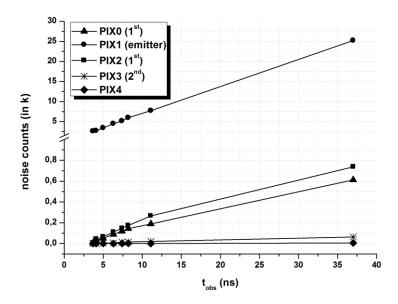

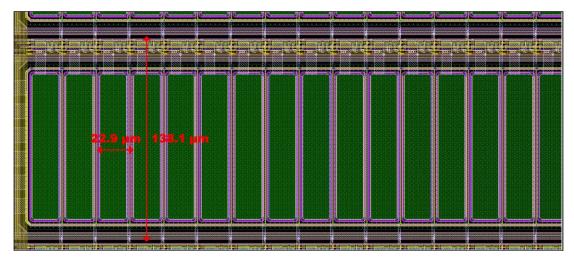

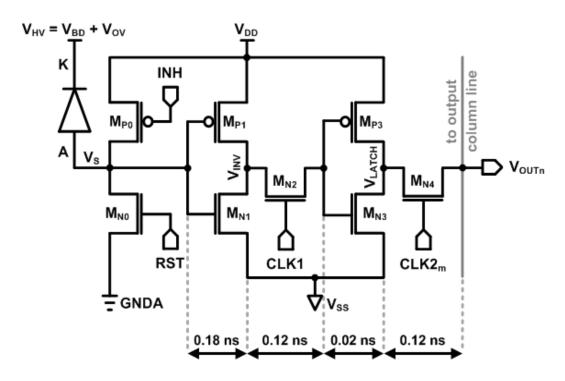

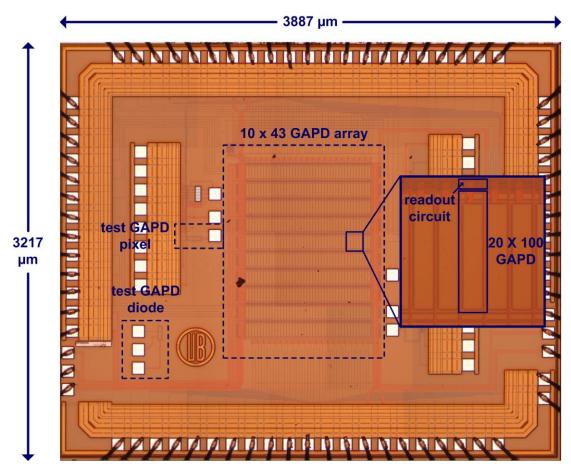

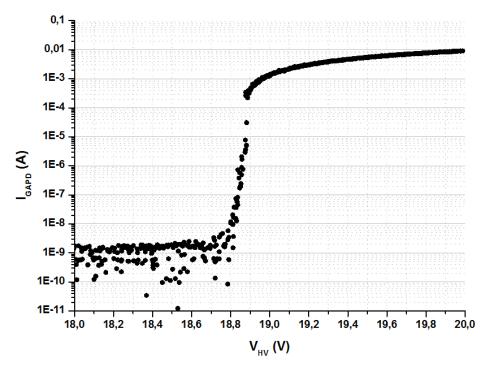

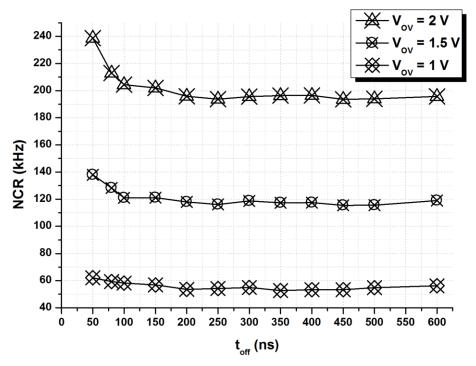

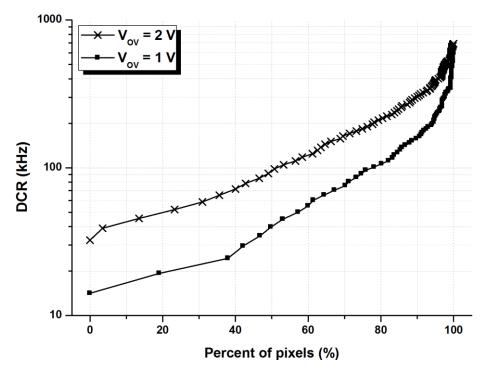

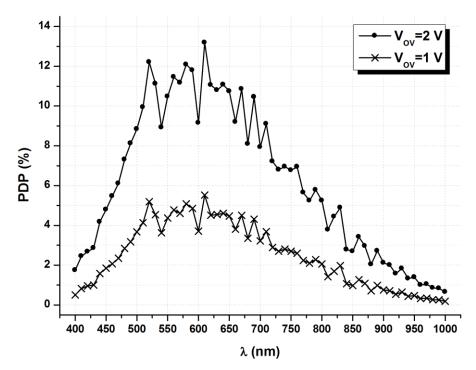

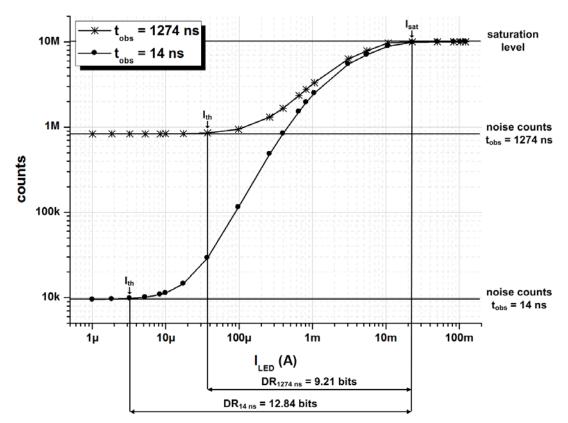

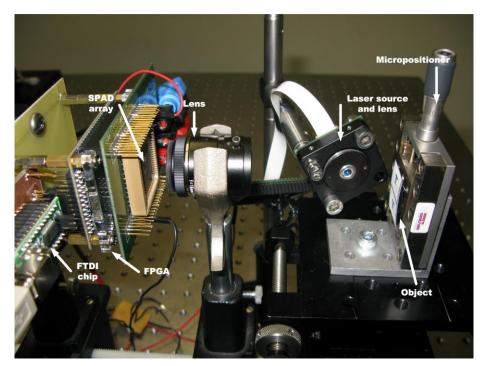

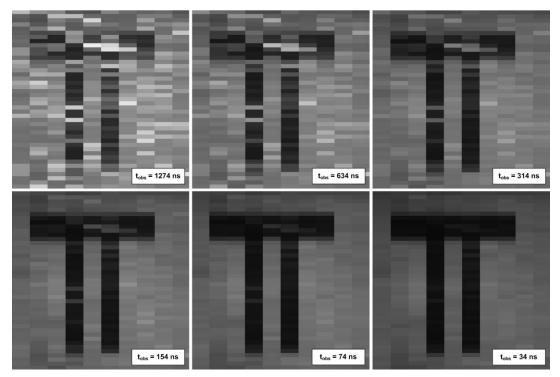

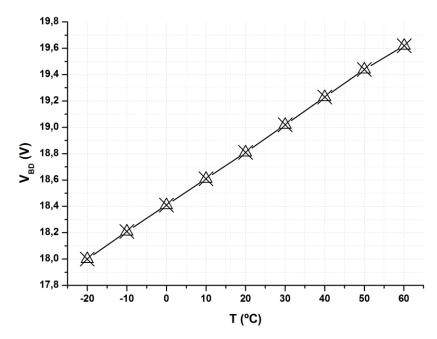

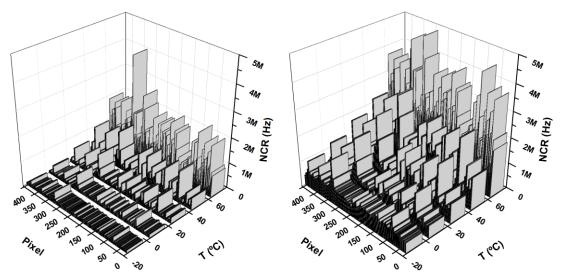

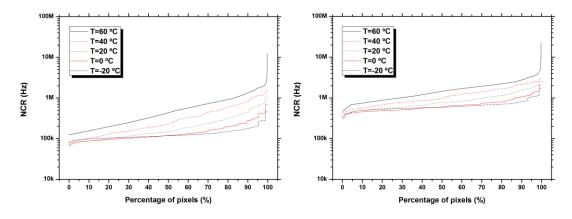

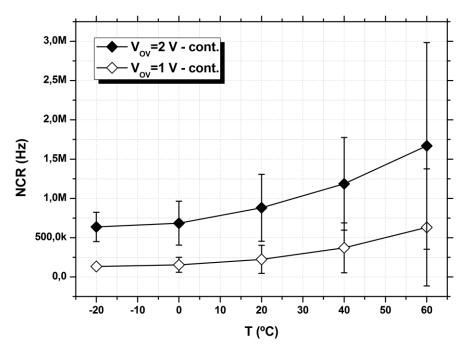

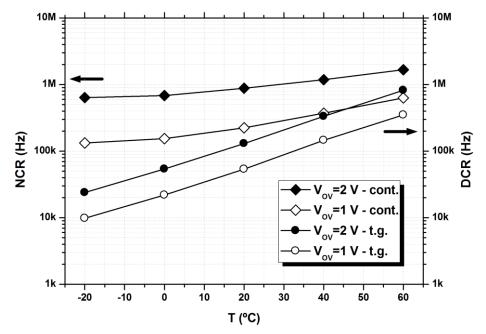

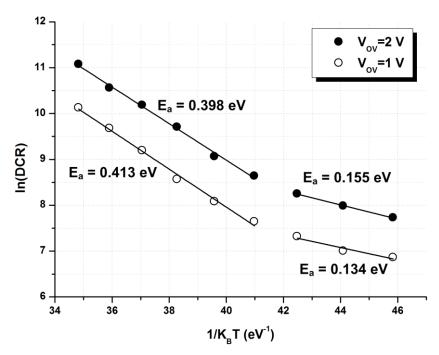

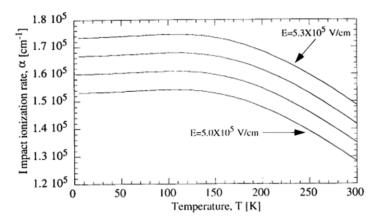

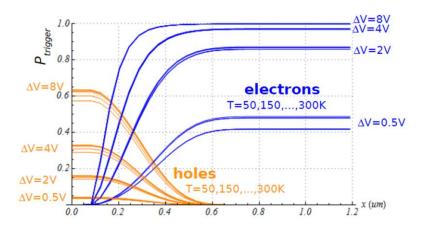

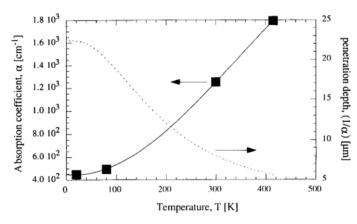

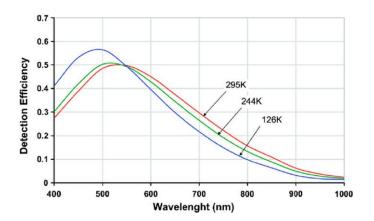

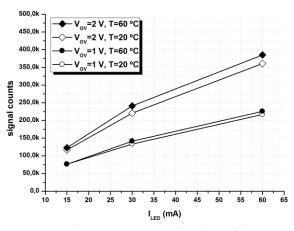

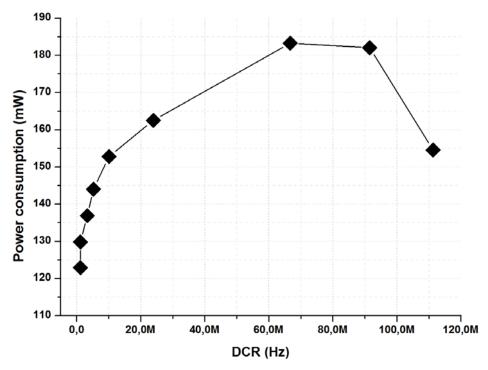

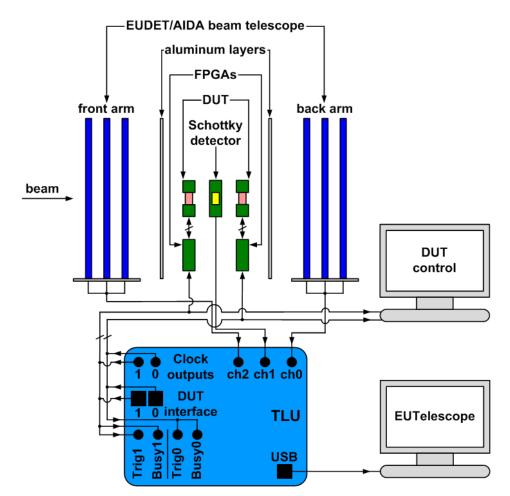

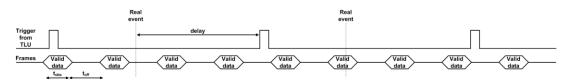

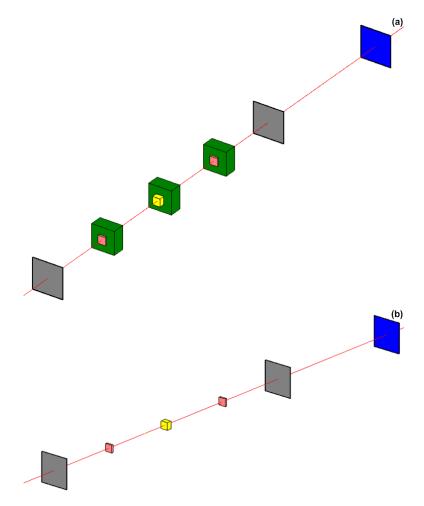

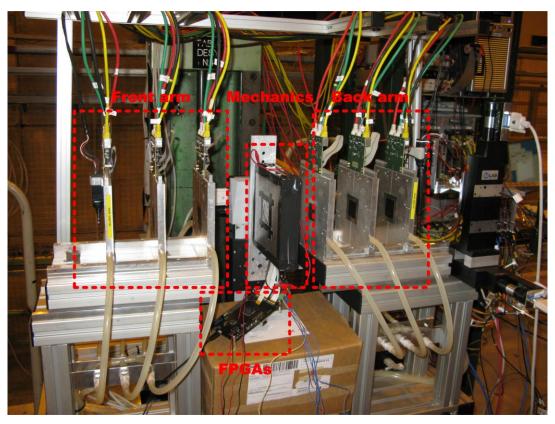

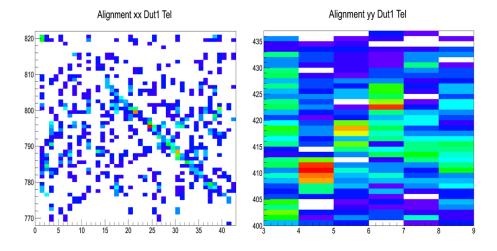

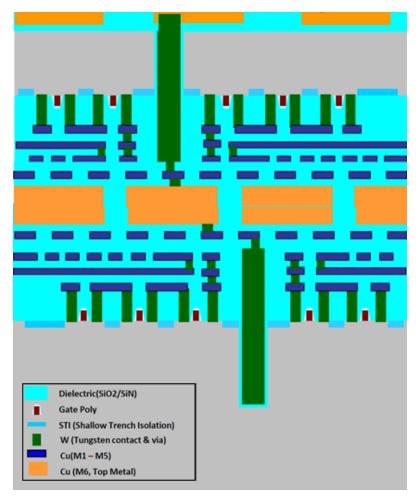

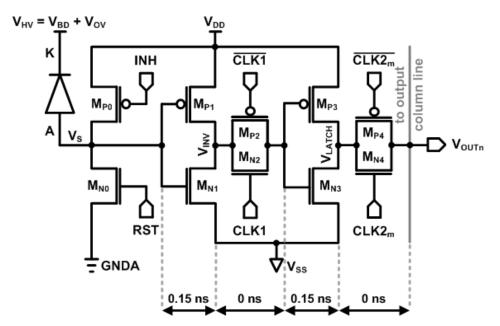

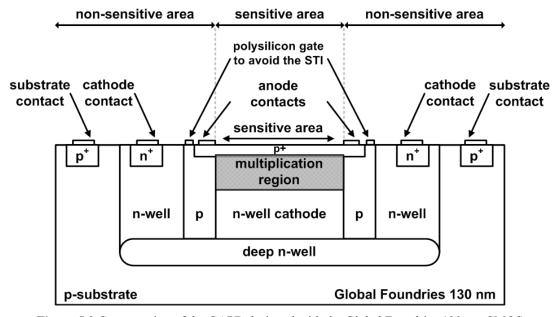

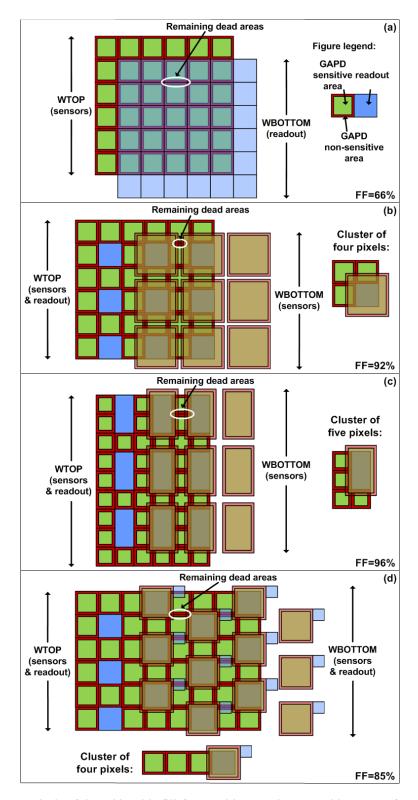

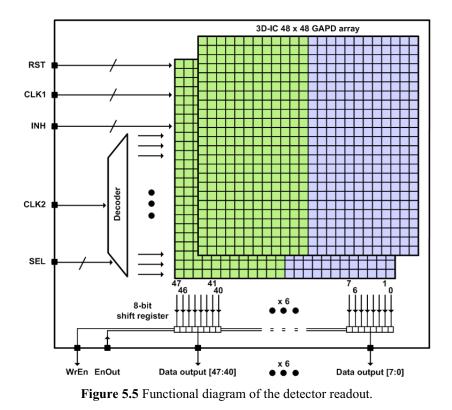

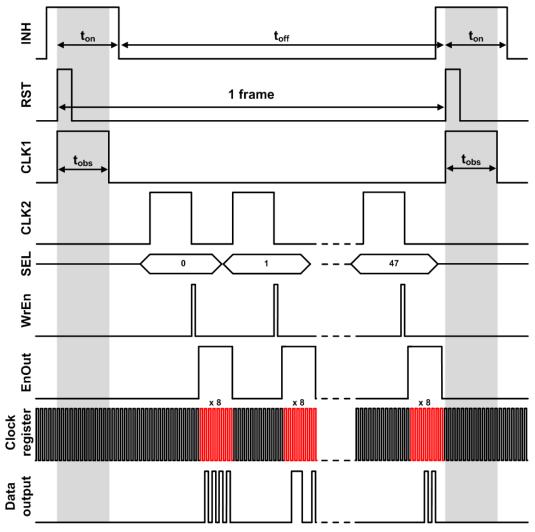

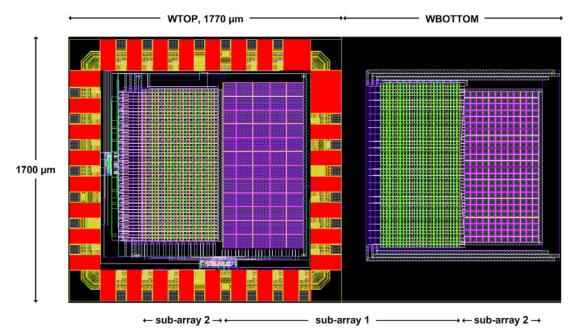

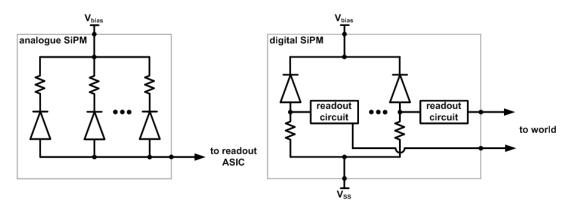

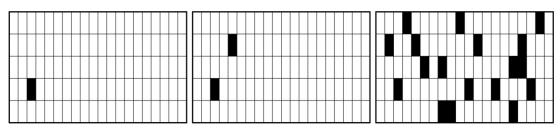

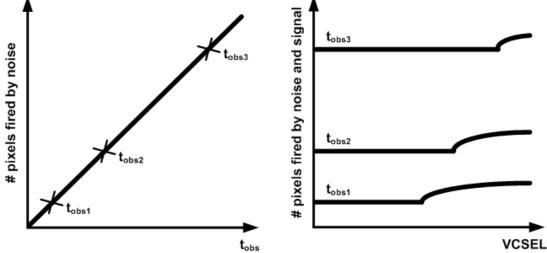

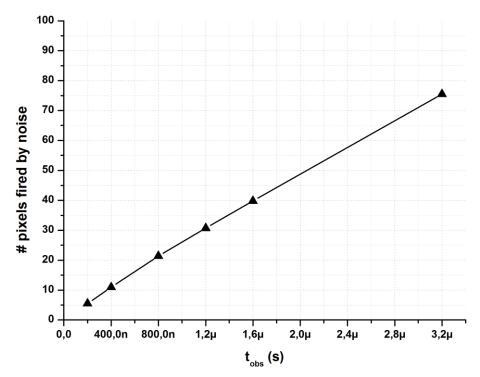

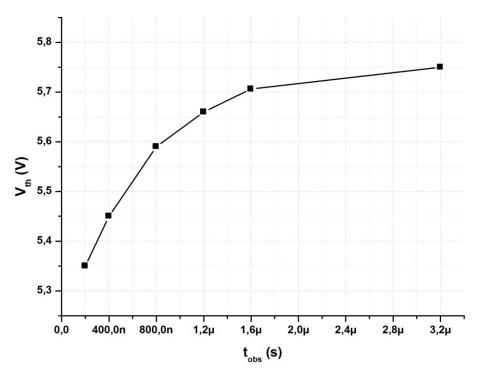

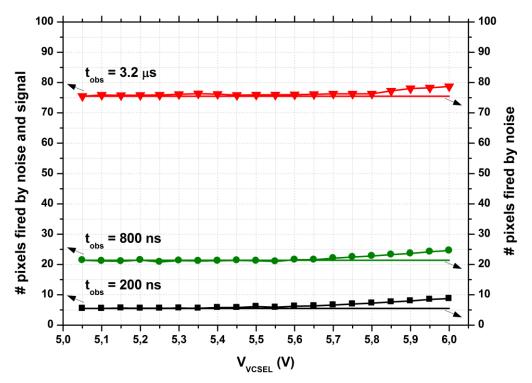

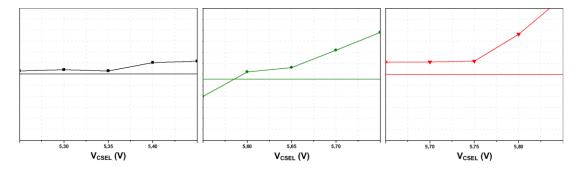

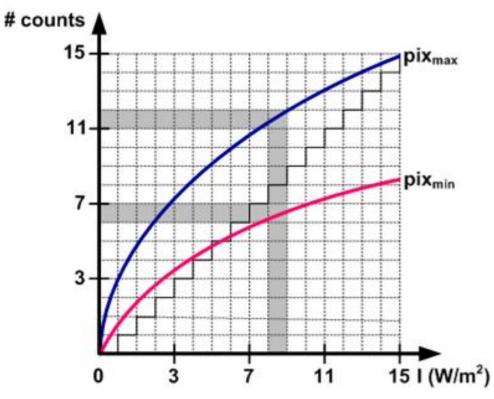

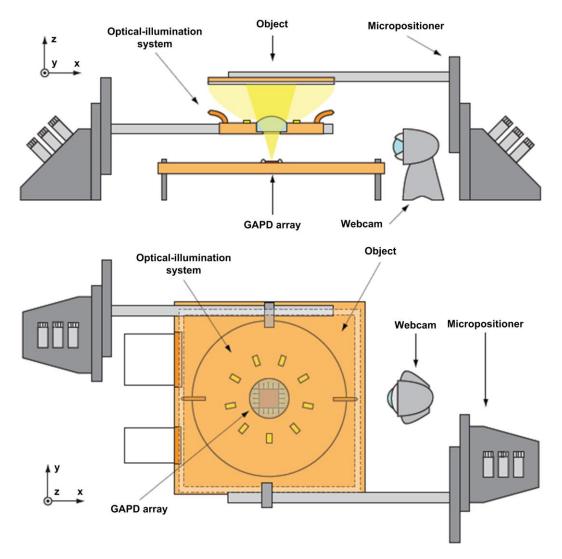

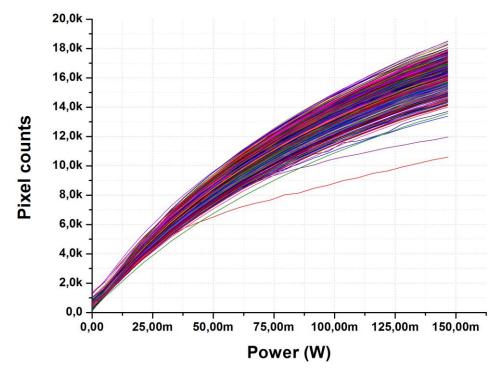

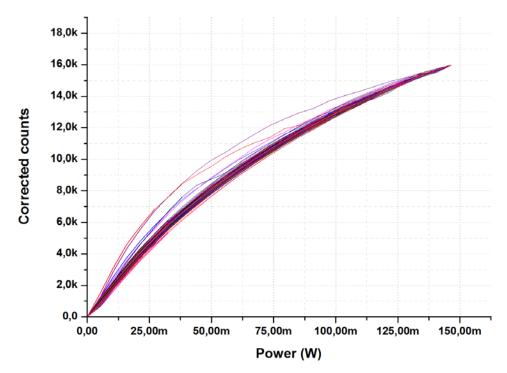

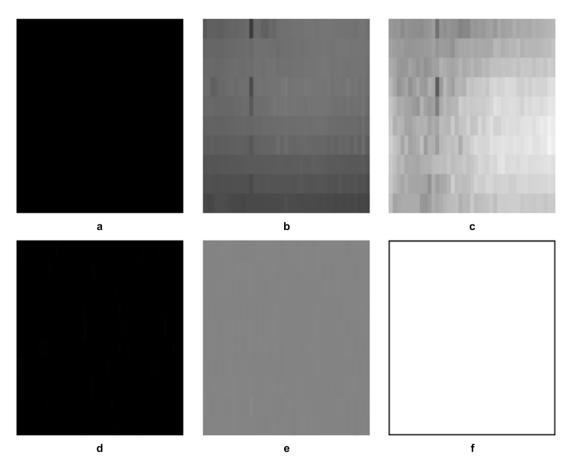

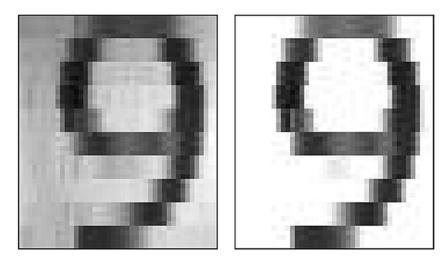

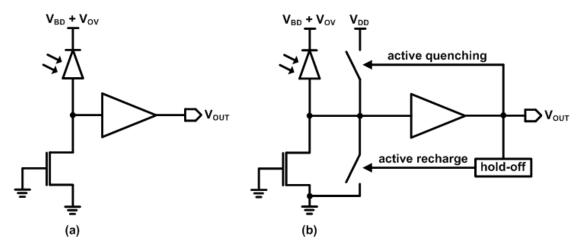

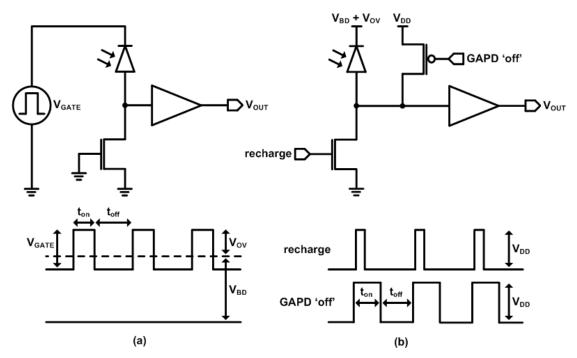

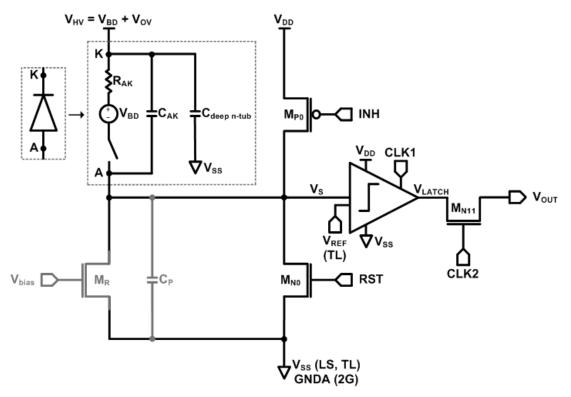

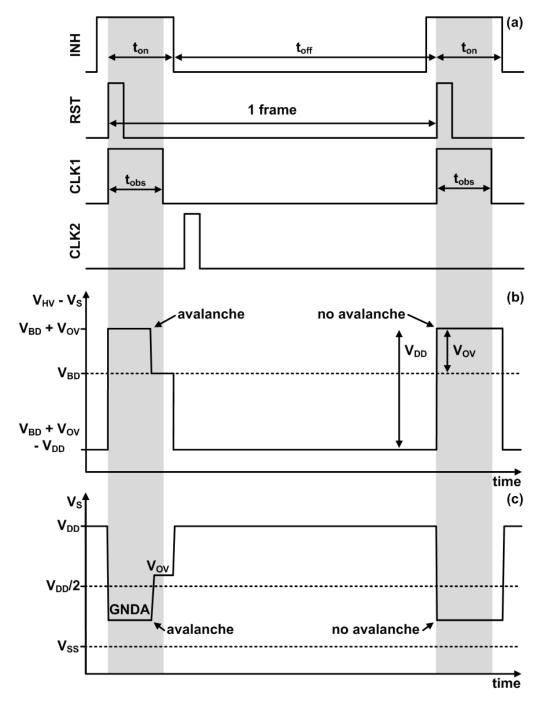

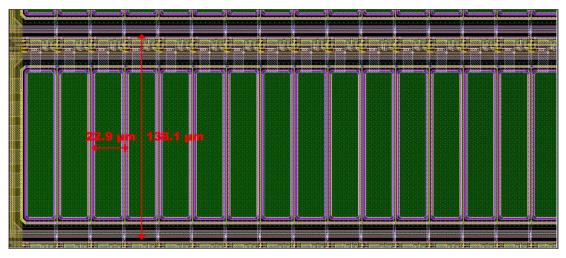

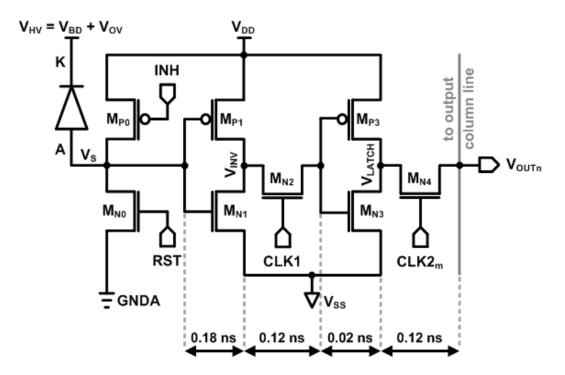

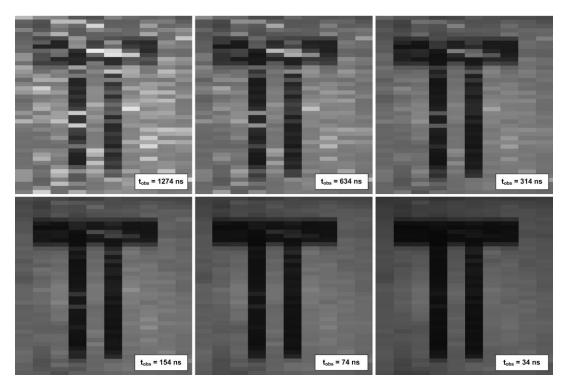

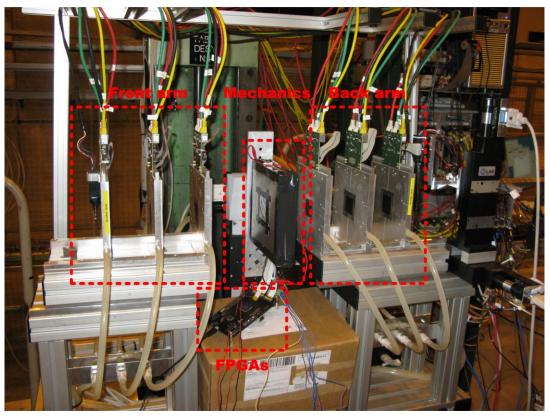

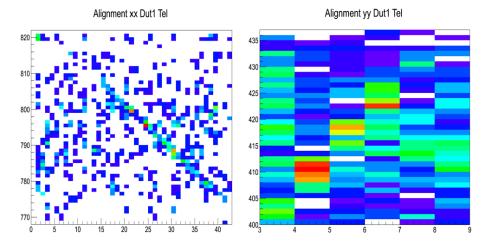

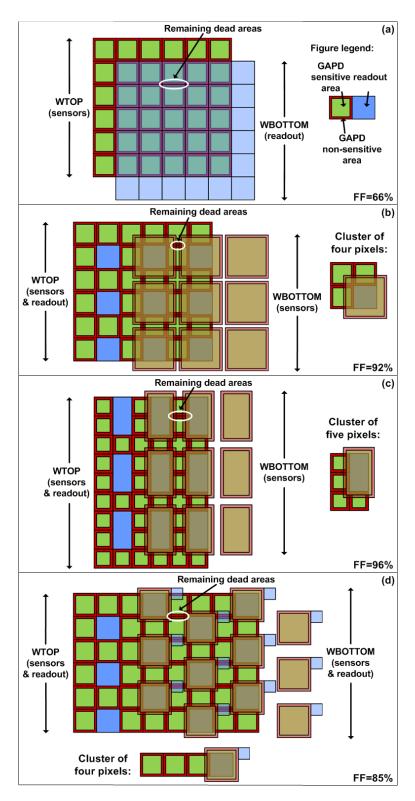

#### 1.4 Detector systems in other particle colliders