**ADVERTIMENT.** L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

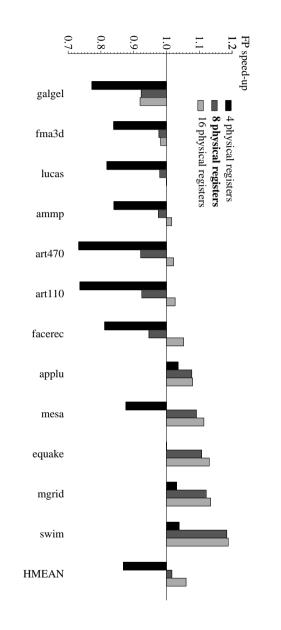

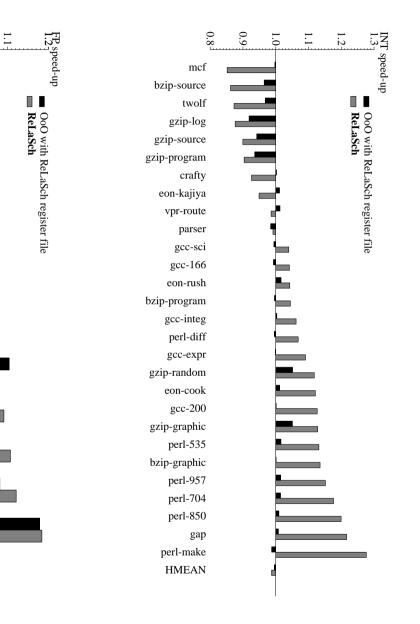

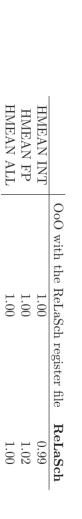

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

### Reusing cached schedules in an out-of-order processor with in-order issue logic

Oscar Palomar

Directors: Toni Juan i Juan. J. Navarro

Departament d'Arquitectura de Computadors

Tesi presentada per obtenir el títol de Doctor per la Universitat Politècnica de Catalunya

Març 2011

Al Graeki, per ser com eres. Et recordarem sempre.

Für Neus. Danke für die deine Geduld, du hast sehr viel! Danke auch für die gemeinsame Zeit, wir werden viel mehr Zeit zusammen verbringen. Ich liebe dich.

A mi madre y al resto de la familia, por vuestra paciencia y los ánimos.

Als meus directors Toni i Juanjo, per tot el que m'heu ensenyat, pels bons consells i l'ajuda en els moments difícils.

To the people in the BSC office. It is great to work with you!

A tots els amics, que no m'heu tingut en compte que sigui tant car veure'm. No us ho he posat fàcil.

This work has been supported by the Ministry of Science and Technology of Spain under contract TIN2007-60625.

Ok Here's what we're going to do We all know the numbers right? From zero to infinity Whatever Some other number with a mess of zeros behind it Here's what we're going to do We're gonna change the order of these numbers to make things interesting Ok here we go: 1 Million and 1 Sixty-six 1 Billion, twenty-five, seventy-five thousand 1 Billion and eight, six, something Zero 1 Million 1 Twenty-two Seventy-five Eleven Eleven Ok this is the new order The New Number Order

New number order, from the album "1000 hurts" by Shellac

# Contents

| 1 Introduction                          |                                   |                                                                                                                | 11              |  |  |  |

|-----------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

|                                         | 1.1                               | Objective                                                                                                      | 11              |  |  |  |

|                                         | 1.2                               | Out-of-order processors: an overview                                                                           | 11              |  |  |  |

|                                         |                                   | 1.2.1 Concept                                                                                                  | 12              |  |  |  |

|                                         |                                   | 1.2.2 Classification                                                                                           | 12              |  |  |  |

|                                         |                                   | 1.2.3 Motivation $\ldots$     | 12              |  |  |  |

|                                         |                                   | 1.2.4 Implementation $\ldots$ | 13              |  |  |  |

|                                         |                                   | 1.2.5 Issue logic                                                                                              | 14              |  |  |  |

|                                         |                                   | 1.2.6 Main problems                                                                                            | 15              |  |  |  |

|                                         | 1.3                               | Repeated issue in the out-of-order processors                                                                  | 15              |  |  |  |

|                                         | 1.4                               | Proposal and thesis outline                                                                                    | 15              |  |  |  |

|                                         | 1.5                               | Scope and results summary                                                                                      | 17              |  |  |  |

|                                         |                                   |                                                                                                                |                 |  |  |  |

| <b>2</b>                                | Mo                                | tivation                                                                                                       | 19              |  |  |  |

|                                         | 2.1                               | Reference processors                                                                                           | 19              |  |  |  |

|                                         | 2.2                               | Contribution of dynamic scheduling to performance                                                              | 20              |  |  |  |

|                                         |                                   | 2.2.1 Quantitative analysis of the behavior of the dynamic-scheduling logic                                    | 22              |  |  |  |

|                                         | 2.3                               | Reusing the dynamic schedules                                                                                  | 23              |  |  |  |

| 3                                       | Cor                               | neral description                                                                                              | 27              |  |  |  |

| 0                                       | 3.1                               | The pipeline                                                                                                   | 27              |  |  |  |

|                                         | 3.1<br>3.2                        | Execution modes                                                                                                | 30              |  |  |  |

|                                         | 0.2                               | 3.2.1 Scheduler                                                                                                | 31              |  |  |  |

| 3.3 How does the ReLaSch processor work |                                   |                                                                                                                | 31              |  |  |  |

|                                         |                                   | 3.3.1 Dependences and register renaming                                                                        | 31              |  |  |  |

|                                         |                                   | 3.3.2 Resource assignment                                                                                      | 31              |  |  |  |

|                                         |                                   | 3.3.3 Memory latency and aliasing prediction                                                                   | 32              |  |  |  |

|                                         |                                   | 3.3.4 Branch prediction                                                                                        | 32              |  |  |  |

|                                         |                                   | 3.3.5 Bad rgroups                                                                                              | 33              |  |  |  |

|                                         |                                   | 3.3.6 Rgroup identification                                                                                    | 33              |  |  |  |

|                                         |                                   | 3.3.7 Rules to close an rgroup                                                                                 | 33              |  |  |  |

|                                         |                                   |                                                                                                                | 00              |  |  |  |

| <b>4</b>                                | The                               | he Rcreate logic 35                                                                                            |                 |  |  |  |

|                                         |                                   |                                                                                                                | ~ ~             |  |  |  |

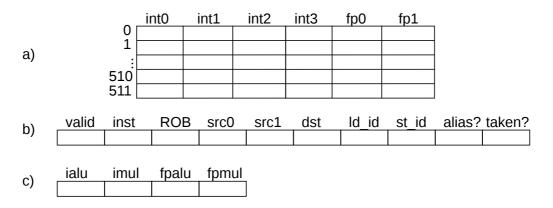

|                                         | 4.1                               | Storage structures                                                                                             | 35              |  |  |  |

|                                         | 4.1                               | Storage structures                                                                                             | $\frac{35}{35}$ |  |  |  |

|                                         | 4.1                               |                                                                                                                |                 |  |  |  |

|                                         | <ul><li>4.1</li><li>4.2</li></ul> | $4.1.1$ Rcreate_input buffer                                                                                   | 35              |  |  |  |

| CONTENTS |  |

|----------|--|

|          |  |

|   |      | 4.2.2 Reorder Buffer                                                                                                                                                      |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 4.2.3 Deadlocks                                                                                                                                                           |

|   |      | 4.2.4 Issue-groups                                                                                                                                                        |

|   | 4.3  | Improving the performance of the schedule                                                                                                                                 |

|   |      | 4.3.1 Functional Units                                                                                                                                                    |

|   |      | 4.3.2 Safe_pos values                                                                                                                                                     |

|   | 4.4  | Memory instructions                                                                                                                                                       |

|   |      | 4.4.1 Identifiers                                                                                                                                                         |

|   |      | 4.4.2 Addresses                                                                                                                                                           |

|   |      | 4.4.3 Latency                                                                                                                                                             |

|   | 4.5  | Control instructions                                                                                                                                                      |

|   |      | 4.5.1 Branch prediction                                                                                                                                                   |

|   | 4.6  | Conditional move instructions                                                                                                                                             |

|   | 4.7  | Closing the rgroup                                                                                                                                                        |

|   |      | 4.7.1 Compacting logic                                                                                                                                                    |

|   | 4.8  | Rgroup identification                                                                                                                                                     |

|   | 4.9  | The Scheduling mode and the Idle mode                                                                                                                                     |

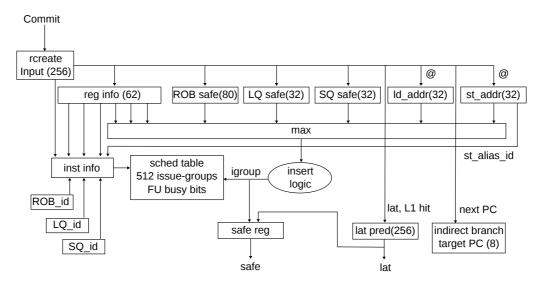

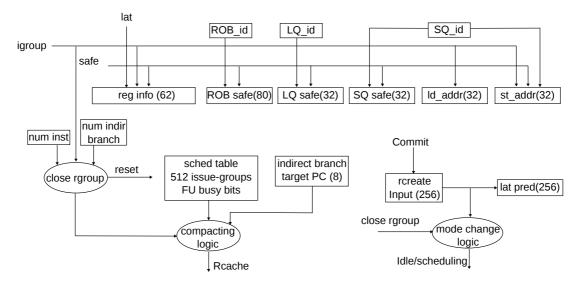

|   | 4.10 | Block diagram                                                                                                                                                             |

|   | _    |                                                                                                                                                                           |

| 5 |      | e Rcache 65                                                                                                                                                               |

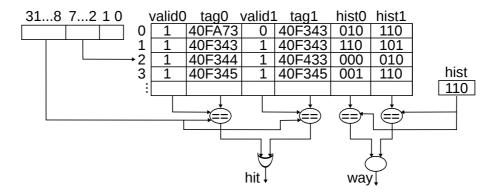

|   | 5.1  | Rgroup identifier                                                                                                                                                         |

|   |      | 5.1.1 Early retirement                                                                                                                                                    |

|   |      | 5.1.2 Index and tag                                                                                                                                                       |

|   |      | 5.1.3 Replacement policy                                                                                                                                                  |

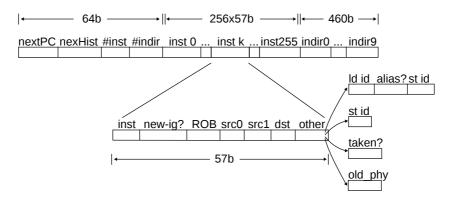

|   | 5.2  | Reache line format                                                                                                                                                        |

|   | 5.3  | Counters                                                                                                                                                                  |

|   | 5.4  | Area and latency                                                                                                                                                          |

| 6 | The  | Rfront-end 71                                                                                                                                                             |

| 0 | 6.1  | Rfetch and Rdecode   71                                                                                                                                                   |

|   | 6.2  | The Rmap logic with an empty ROB                                                                                                                                          |

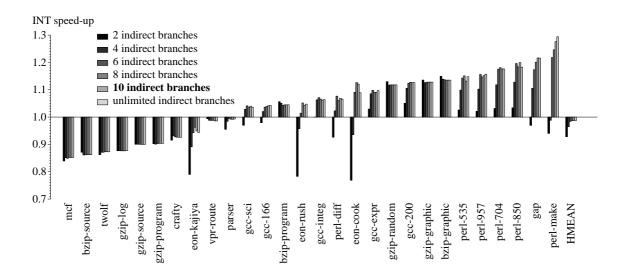

|   | 0.2  | 6.2.1       Indirect branches       73                                                                                                                                    |

|   |      | 6.2.2 Identification of the rgroup                                                                                                                                        |

|   | 6.3  | The Rmap logic without restrictions on the ROB state                                                                                                                      |

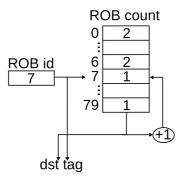

|   |      | 6.3.1 Adapting the identifiers                                                                                                                                            |

|   |      | 6.3.2 Updating the structures                                                                                                                                             |

|   |      |                                                                                                                                                                           |

| 7 | The  | e Issue stage 77                                                                                                                                                          |

|   | 7.1  | The out-of-order issue logic                                                                                                                                              |

|   | 7.2  | The in-order issue logic                                                                                                                                                  |

|   |      | 7.2.1 Waking up the dependent instructions                                                                                                                                |

|   |      | 7.2.2 Separated integer and floating point buffers                                                                                                                        |

|   |      | 7.2.3 Tag broadcasting                                                                                                                                                    |

|   |      | 7.2.4 Conditional move instructions                                                                                                                                       |

|   |      | 7.2.5 Issue buffer of issue-groups $\ldots \ldots \ldots$ |

#### CONTENTS

| 8  | Oth  | er elements                                                                                                                                                                | 83  |  |  |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| 0  | 8.1  |                                                                                                                                                                            | 83  |  |  |

|    | 0.1  | ů,                                                                                                                                                                         | 84  |  |  |

|    | 8.2  |                                                                                                                                                                            | 84  |  |  |

|    | 8.3  |                                                                                                                                                                            | 84  |  |  |

|    | 8.4  |                                                                                                                                                                            | 85  |  |  |

|    | 0.1  |                                                                                                                                                                            | 00  |  |  |

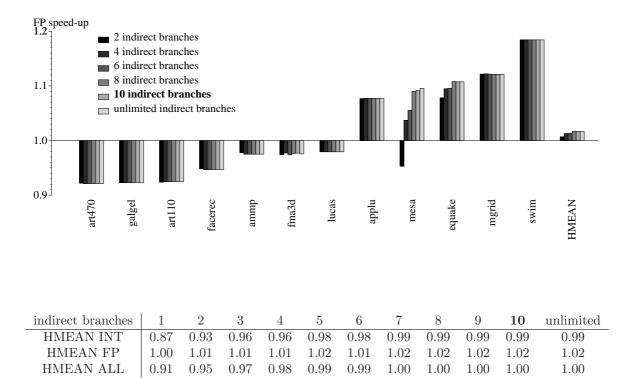

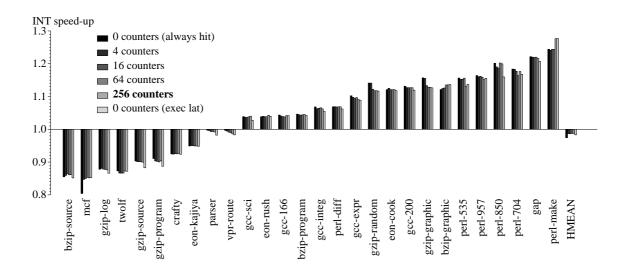

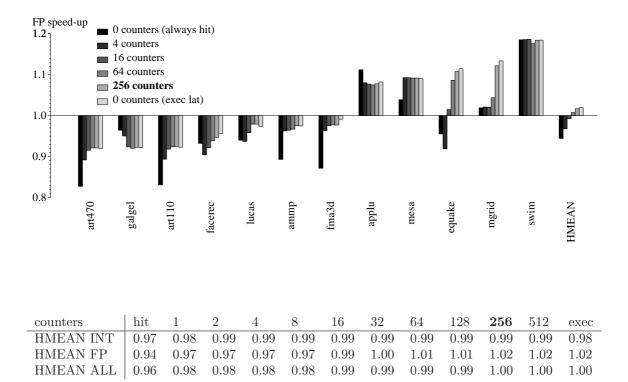

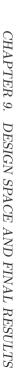

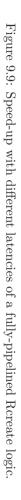

| 9  | Des  | gn space and final results                                                                                                                                                 | 87  |  |  |

|    | 9.1  | Experimental set-up                                                                                                                                                        | 87  |  |  |

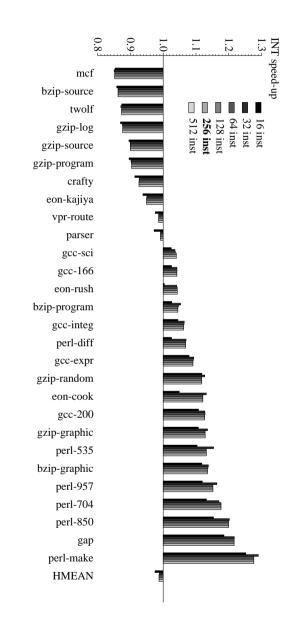

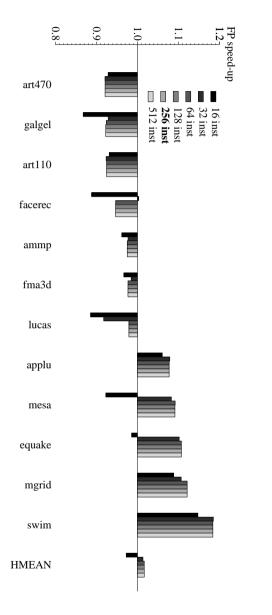

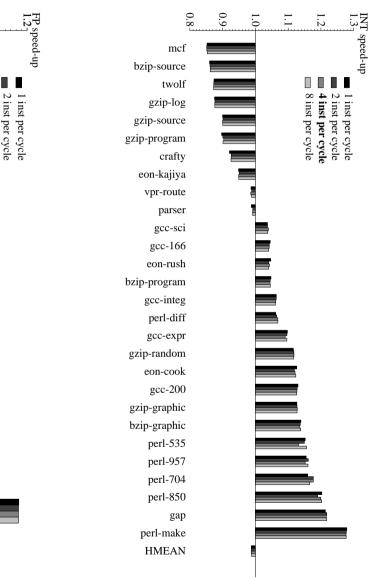

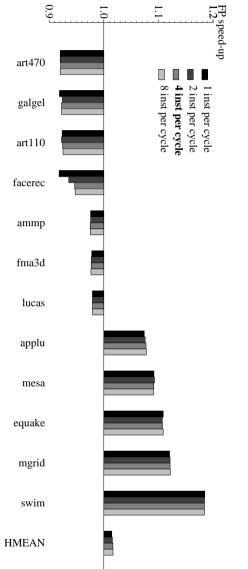

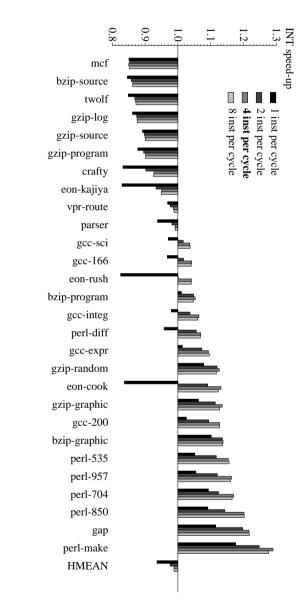

|    | 9.2  | The Rcreate logic                                                                                                                                                          | 89  |  |  |

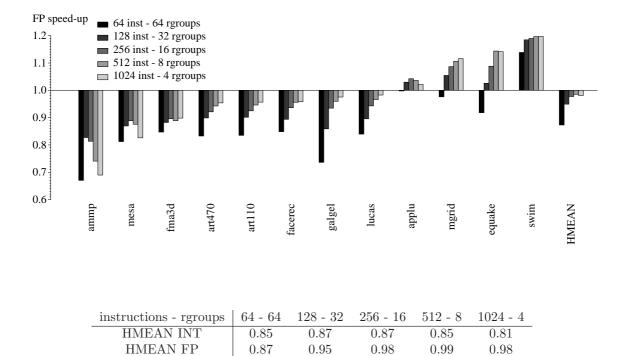

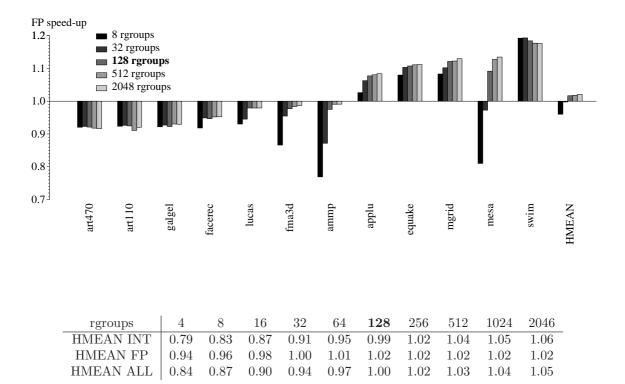

|    |      | 9.2.1 Rgroup size                                                                                                                                                          | 89  |  |  |

|    |      |                                                                                                                                                                            | 93  |  |  |

|    |      |                                                                                                                                                                            | 93  |  |  |

|    |      |                                                                                                                                                                            | 93  |  |  |

|    |      |                                                                                                                                                                            | .01 |  |  |

|    |      | 1 0                                                                                                                                                                        | .01 |  |  |

|    |      |                                                                                                                                                                            | 01  |  |  |

|    |      | 0                                                                                                                                                                          | .06 |  |  |

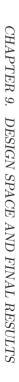

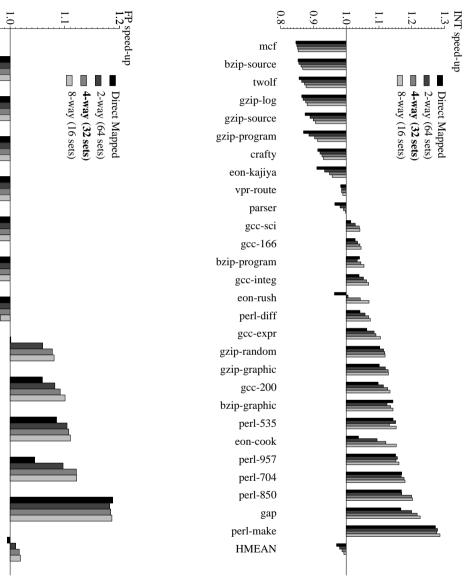

|    | 9.3  |                                                                                                                                                                            | .00 |  |  |

|    | 9.0  |                                                                                                                                                                            | .00 |  |  |

|    |      |                                                                                                                                                                            | .00 |  |  |

|    |      | v                                                                                                                                                                          |     |  |  |

|    |      | 0 1                                                                                                                                                                        | 09  |  |  |

|    |      | v                                                                                                                                                                          | 09  |  |  |

|    | 0.4  |                                                                                                                                                                            | 13  |  |  |

|    | 9.4  | 0                                                                                                                                                                          | 13  |  |  |

|    |      | 0 1                                                                                                                                                                        | 13  |  |  |

|    |      |                                                                                                                                                                            | 18  |  |  |

|    | 9.5  |                                                                                                                                                                            | 18  |  |  |

|    |      |                                                                                                                                                                            | 18  |  |  |

|    |      |                                                                                                                                                                            | 21  |  |  |

|    |      |                                                                                                                                                                            | 24  |  |  |

|    |      | 9.5.4 Icache size                                                                                                                                                          | 24  |  |  |

|    |      | 9.5.5 Branch predictor $\ldots \ldots \ldots$              | 29  |  |  |

|    |      | 9.5.6 ROB size                                                                                                                                                             | 29  |  |  |

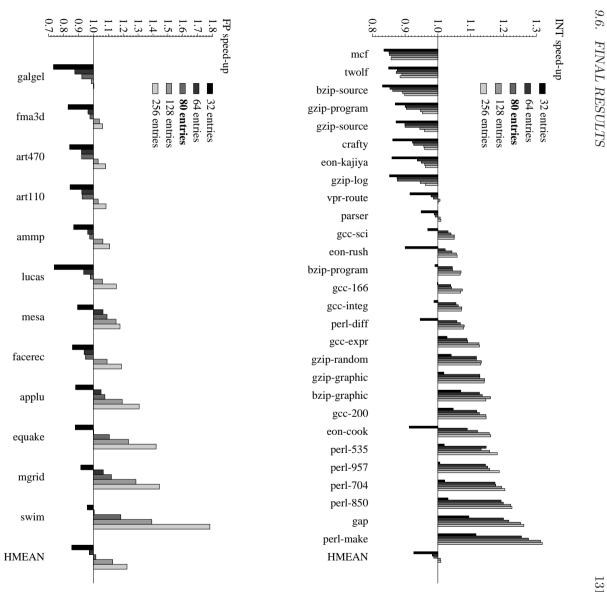

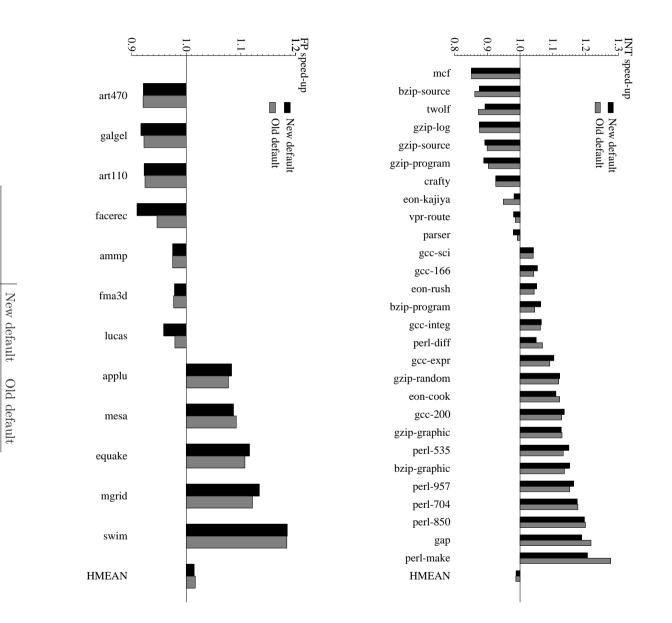

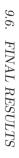

|    | 9.6  | Final results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                                                                                             | 29  |  |  |

|    |      |                                                                                                                                                                            |     |  |  |

| 10 |      |                                                                                                                                                                            | 37  |  |  |

|    | 10.1 | OT T                                                                                                                                                                       | 37  |  |  |

|    |      | -                                                                                                                                                                          | 37  |  |  |

|    |      |                                                                                                                                                                            | .39 |  |  |

|    |      |                                                                                                                                                                            | 40  |  |  |

|    |      |                                                                                                                                                                            | 41  |  |  |

|    |      |                                                                                                                                                                            | 42  |  |  |

|    |      |                                                                                                                                                                            | 44  |  |  |

|    |      | 01 1                                                                                                                                                                       | 44  |  |  |

|    | 10.2 | 01 1                                                                                                                                                                       | 45  |  |  |

|    |      | 10.2.1 Loop-based instruction reuse $\ldots \ldots \ldots$ | 45  |  |  |

|    |      | 10.2.2 Simplified issue                                                                                                                                                    | 46  |  |  |

|    | 10.3 | Summary                                                                                                                                                                    | 47  |  |  |

9

#### CONTENTS

| <ul> <li>11.1 Conclusions</li></ul>                                                                                                                                                                                                                                                                               | 149 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Common register file         A.1 Description of the register file         A.2 WAR and WAW hazards         A.2 I Twice as many physical registers as identifiers in the ROB         A.2.2 As many physical registers as identifiers in the ROB         A.2.3 Less physical registers than identifiers in the ROB | 149 |

| <ul> <li>A.1 Description of the register file</li></ul>                                                                                                                                                                                                                                                           | 150 |

| <ul> <li>A.2 WAR and WAW hazards</li></ul>                                                                                                                                                                                                                                                                        | 155 |

| <ul><li>A.2.1 Twice as many physical registers as identifiers in the ROB A.2.2 As many physical registers as identifiers in the ROB</li></ul>                                                                                                                                                                     | 155 |

| <ul><li>A.2.2 As many physical registers as identifiers in the ROB</li></ul>                                                                                                                                                                                                                                      | 157 |

| A.2.3 Less physical registers than identifiers in the ROB                                                                                                                                                                                                                                                         | 158 |

|                                                                                                                                                                                                                                                                                                                   |     |

|                                                                                                                                                                                                                                                                                                                   | 160 |

| A.3 The Rfront-end and the Rcreate logic with an empty ROB                                                                                                                                                                                                                                                        |     |

| A.3.1 The Rcreate logic                                                                                                                                                                                                                                                                                           | 160 |

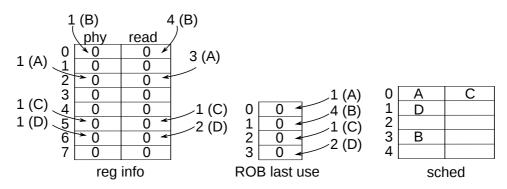

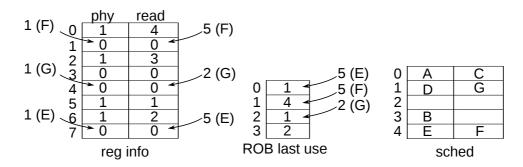

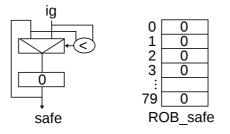

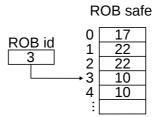

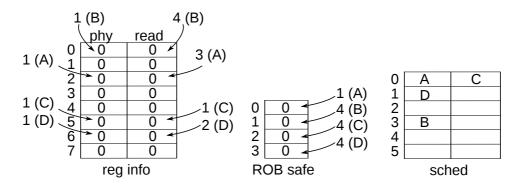

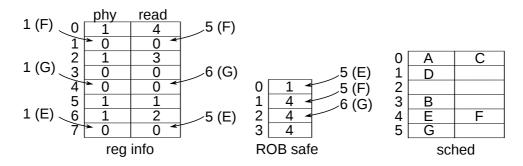

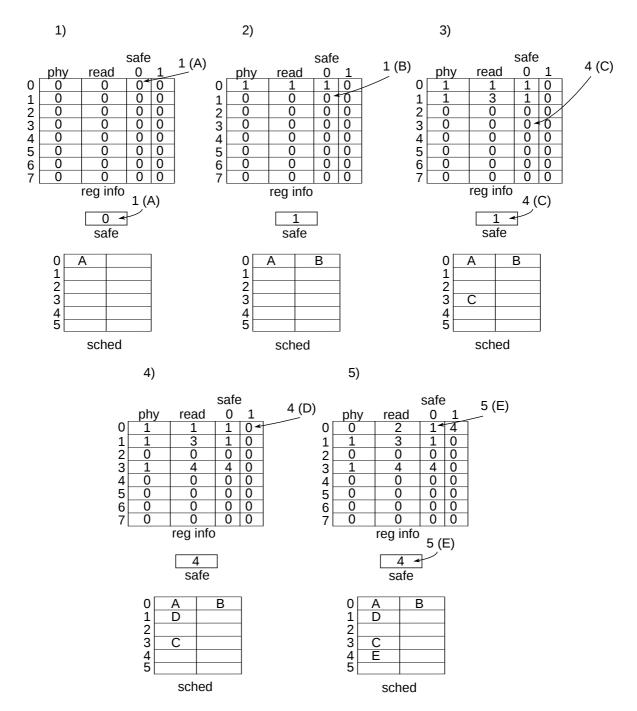

| A.3.2 The Rmap logic                                                                                                                                                                                                                                                                                              | 165 |

| A.4 The Rfront-end and the Rcreate logic with a non-empty ROB                                                                                                                                                                                                                                                     | 165 |

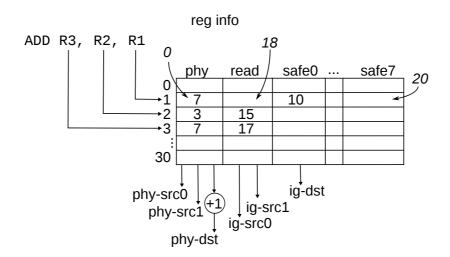

| A.4.1 The Rcreate logic                                                                                                                                                                                                                                                                                           | 165 |

| A.4.2 The Rmap logic                                                                                                                                                                                                                                                                                              | 166 |

| A.5 The Reache                                                                                                                                                                                                                                                                                                    | 170 |

| A.6 Experimental results                                                                                                                                                                                                                                                                                          | 170 |

| B The 21264 Alpha processor                                                                                                                                                                                                                                                                                       | 173 |

| B.1 The Alpha ISA                                                                                                                                                                                                                                                                                                 | 173 |

| B.1.1 Memory accesses                                                                                                                                                                                                                                                                                             |     |

| B.2 The 21264 Alpha processor                                                                                                                                                                                                                                                                                     |     |

| B.2.1 The pipeline                                                                                                                                                                                                                                                                                                |     |

| B.2.2 Slots and Functional Units                                                                                                                                                                                                                                                                                  |     |

| B.2.3 Branch prediction                                                                                                                                                                                                                                                                                           |     |

| B.2.4 Memory accesses                                                                                                                                                                                                                                                                                             |     |

| B.2.5 Register renaming                                                                                                                                                                                                                                                                                           |     |

| B.2.6 Conditional moves                                                                                                                                                                                                                                                                                           |     |

| B.3 The sim-alpha simulator                                                                                                                                                                                                                                                                                       | 176 |

#### C Benchmarks

179

10

# Chapter 1

# Introduction

Modern processors use out-of-order processing logic to achieve high performance in Instructions Per Cycle (IPC) but this logic has a serious impact on the achievable frequency. In order to get better performance out of smaller transistors there is a trend to increase the number of cores per die instead of making the cores themselves bigger. Moreover, for throughput-oriented and server workloads, simpler in-order processors that allow more cores per die and higher design frequencies are becoming the preferred choice (IBM's Power6<sup>1</sup> [1], Sun's Niagara 3 with 16 cores [5, 6]). Unfortunately, for other workloads this type of cores result in a lower single thread performance.

There are many workloads where it is still important to achieve good single thread performance. In this thesis we present the ReLaSch processor; its aim is to enable high IPC cores capable of running at high clock frequencies by processing the instructions using simple superscalar in-order issue logic and caching instruction groups that are dynamically scheduled in hardware after commit, that is, out of the critical path and only when really needed.

#### 1.1 Objective

This thesis has several research goals:

- To show that the dynamic scheduler of a conventional out-of-order processor does a lot of redundant work because it ignores code repetitiveness.

- To propose a complete superscalar out-of-order architecture that reduces the amount of redundant work done by creating the schedules once in dedicated hardware, storing them in a cache of schedules and reusing the schedules as much as possible.

- To place the scheduler out of the critical path of execution, which should be enabled by the reduction of work that the scheduler must do. Thus, the execution path of our proposed processor can be simpler than that of a conventional out-of-order processor.

#### 1.2 Out-of-order processors: an overview

This section presents a short introduction to out-of-order processors. It describes the concepts involved in the rationale behind our proposal. This overview is not intended to be a survey of all the

<sup>&</sup>lt;sup>1</sup>Using a technology independent model, the Power6 processor doubles the frequency of the out-of-order Power5 [1]. The Power7 processor is out-of-order [2]. However, in its initial release its maximum available frequency (4.25GHz as of October 2010 [3]) is lower than that of the Power6 (5GHz as of April 2010 [4]).

possible ways to implement an out-of-order processor. It is a well-known topic in the computer architecture area, so we just give a short overview of the motivation to use them, an insight on the key implementation issues and a description of their main problems.

#### 1.2.1 Concept

Out-of-order processors are able to execute the instructions of a program in a different order than that specified by the programmer. As long as the out-of-order processor respects the dependences between instructions, the outcome of the program will be indistinguishable from the result produced by a sequential (in-order) execution, that is, in the original order of the instructions.

#### 1.2.2 Classification

- **In-order processors (IO).** Also known as statically-scheduled processors. For this group of processors, all the instruction scheduling is done by the compiler. The microarchitecture issues groups of independent instructions that are consecutive in program order. At execution time, there are no changes on the order chosen by the compiler at compilation time and hence this mechanism is called statically-scheduled.

- **Out-of-order processors (OoO).** Also known as dynamically-scheduled processors. On top of the static instruction scheduling performed by the compiler, the processor performs a second level of dynamic scheduling. Instructions are fetched following the predicted sequential order and put into an instruction queue. The microarchitecture groups the best independent instructions from the window dynamically and issues them for execution in a better order than the one chosen by the compiler based on the resources available.

On one hand, out-of-order processors can extract more instruction level parallelism (ILP) from the instruction stream. Furthermore, existing binaries can benefit from changes in the microarchitecture without recompiling. On the other hand, in-order processors are simpler and, therefore, smaller; additionally, they consume less power and either have a lower number of pipeline stages (lower penalties) or can be designed to run at higher frequencies.

#### 1.2.3 Motivation

Out-of-order processors are attractive because they can achieve high speed-ups in IPC and execution time with respect to in-order cores. Whenever there is a data dependence with a long latency instruction, out-of-order processors are able to continue executing younger independent instructions, whereas in-order processors stall.

The compiler can schedule the instructions statically for a well-known in-order processor and remove these stalls, but still there are two important scenarios in which it is impossible:

- a. The presence of instructions with variable latency, such as the accesses to the memory hierarchy, that have very different latencies on a miss and on a hit. Although the introduction of pre-fetch mechanisms can mitigate the problem, there is still much uncertainty in the latency of such instructions. Moreover, these instructions have a significant share of the instruction mix and their impact cannot be neglected. The flexibility of out-of-order processors enables them to find independent instructions that can be executed while waiting for cache misses.

- b. Speculative execution through branch prediction. When instructions are executed speculatively the chances of finding additional independent instructions in the speculated path increase, which out-of-order processors can exploit. On the other hand, compilers must be conservative to

#### 1.2. OUT-OF-ORDER PROCESSORS: AN OVERVIEW

preserve the semantics of the program. They don't move instructions across basic blocks unless it is safe to do the optimization. Therefore, in most cases the independent instruction will not be statically rescheduled. With the use of techniques like predication the compiler can work around this problem, but it comes with an overhead in the code size and the total number of instructions executed.

To summarize, the flexibility of dynamic scheduling allows to adapt to changing situations such as variable instruction latency and changing execution paths that static scheduling cannot manage efficiently.

#### 1.2.4 Implementation

This section presents the main structures needed to implement a generic out-of-order processor.

#### Dependences

The first thing to consider is what is a dependence and when instructions can be considered independent. Figure 1.1 illustrates the possible cases. The examples show cases in which only registers are involved. Memory and control dependences are left aside here for simplicity.

Both output and anti-dependences are considered "false" or "name dependences" since we can eliminate the dependence by changing the registers used by the instruction. On the other hand, a data dependence cannot be removed using this technique: the dependent instruction must wait until the needed value is produced.

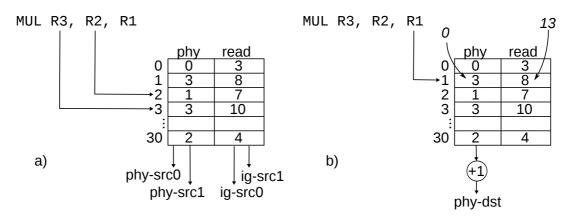

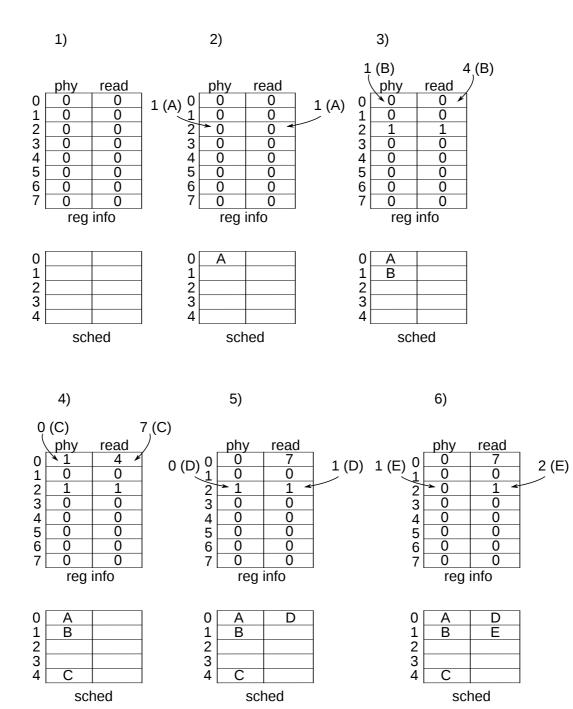

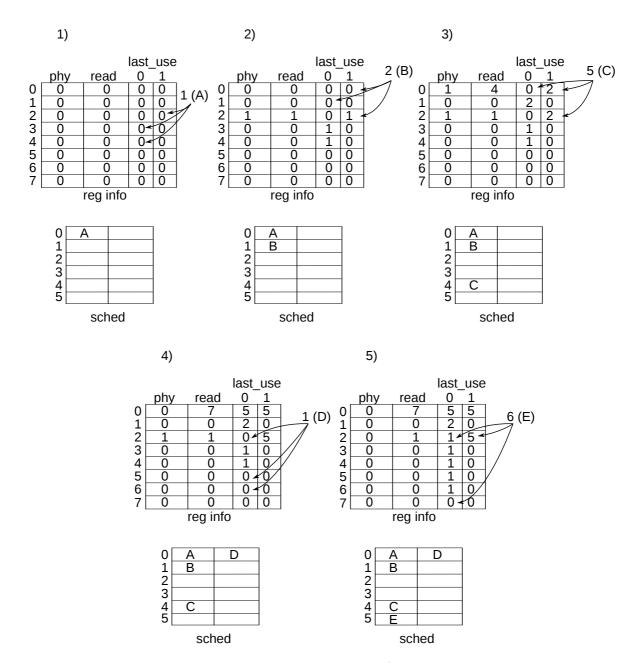

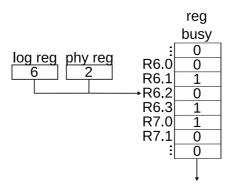

#### **Register Renaming**

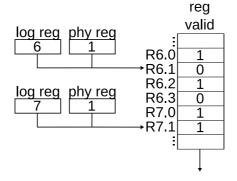

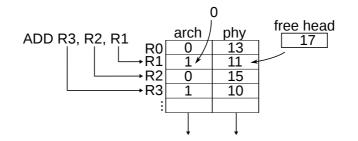

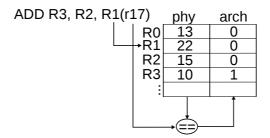

The register renaming logic eliminates the false dependences while preserving the semantics of the program. It maps the logical registers (the ones specified in the Instruction Set Architecture or ISA) to a larger set of physical registers. There can be several instances of the same logical register, although just one stores the architectural value. A new physical register is assigned to each destination logical register, while all reads to a given logical register are renamed to its most recently mapped physical register. Thus, the data dependences are preserved whereas false dependences are removed.

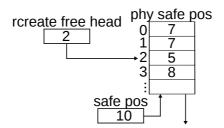

Physical registers are recycled after they are no longer needed. Depending on the implementation, that happens after the retirement of the instruction that writes the register or after the last read to the register.

The structures commonly used to implement register renaming are: a) the rename table with the most recent mapping of each logical register; b) the architectural rename table with the physical register that currently stores the architectural value of each logical register; and c) the free list that contains the free physical registers, that is, the registers available to be mapped to incoming instructions.

An important problem of register renaming is that two consecutive instructions may be dependent, so the renaming state after the first instruction is processed must be known to rename the second correctly. The consequence is that the renaming logic grows in complexity in superscalar processors, since the renaming logic must check any dependence between all instructions being mapped at the same time and rename them accordingly. Furthermore, the outcome of the renaming logic at a given cycle is used the next cycle. Such tight loop makes it challenging to pipeline the renaming logic without having an impact in performance.

| a) Data dependence        | b) Output dependence     | c) Anti-dependence        | d) Independent code |

|---------------------------|--------------------------|---------------------------|---------------------|

| A: MUL R1, R2, <b>R3</b>  | A: MUL R1, R2, <b>R3</b> | A: MUL <b>R1</b> , R2, R3 | A: MUL R1, R2, R3   |

| B: ADD <b>R3</b> , R4, R5 | B: ADD R4, R5, <b>R3</b> | B: ADD R4, R5, <b>R1</b>  | B: ADD R1, R4, R5   |

Figure 1.1: The examples of code show, from left to right: a) Data or real dependence. If the instructions have the chance to execute out-of-order there is a Read-After-Write (RAW) hazard. b) Output dependence. The hazard it can create is called Read-After-Write (RAW). c) Anti-dependence. It is related with Write-After-Read (WAR) hazards. d) Independent code. The instructions can be freely reordered. The instructions in the examples indicate the destination register in the right-most position.

#### In-order retirement

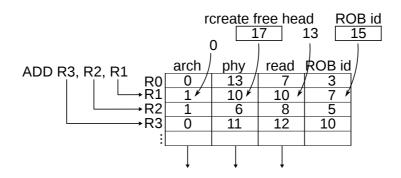

All modern out-of-order processors retire the instructions in the original program order. The use of branch prediction already forces them to wait until the branch is resolved to retire the speculated instructions, even if they have finished execution many cycles before. Moreover, retiring the instructions in order forces exceptions to be precise. An exception is imprecise if the architectural state seen by the exception handler has been modified by instructions younger than the one that raised the exception, or if the state has not been modified by an older instruction. Both cases can occur in an out-of-order processor if instructions are allowed to retire out-of-order.

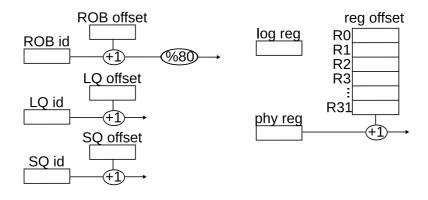

After instructions are renamed, they are inserted in the Re-Order Buffer (ROB), a First-In First-Out (FIFO) structure. An instruction stays in the ROB until it reaches the head of the buffer and it has completed execution with no exception or mis-speculation. The instruction retires (what is known as the Commit stage), updating the architectural state: that is, the destination register and the PC. It also updates the memory if the instruction is a store.

The architectural rename table tracks which physical registers hold the architectural state. The architectural rename table is updated in the Commit stage. Alternatively, dedicated architectural registers can be used. Additionally, the store queue keeps the information of all in-flight (non-committed) stores, including the address that is going to be accessed and the value that will be written. This is needed in order to update memory in the Commit stage.

A load instruction accesses the store queue before accessing the cache and checks if there is any older store that accesses the same address, a situation known as memory aliasing. If such an aliasing exists, the data is bypassed directly from the store queue instead of accessing the cache. In an out-of-order processor, memory instructions may calculate the addresses out-of-order too. To avoid stalling until the addresses of all older accesses are known, load instructions usually access the cache speculatively. When a store resolves its address, it checks if there is any younger load that has speculatively accessed the same address. The load is re-executed in case of an aliasing, typically forcing a pipeline flush. Thus, there is also a load queue that tracks all in-flight loads. The load and the store queues are sometimes merged into just one queue. Usually there is also a prediction mechanism to prevent speculative execution of loads that have been re-executed previously and thus reduce the number of pipeline flushes.

#### 1.2.5 Issue logic

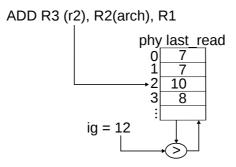

The issue logic is responsible for sending the instructions to the functional units (FU) when they are ready. The instructions are inserted in the issue queue after that have been renamed. The issue logic has to implement two main functionalities:

a. Wake-up: It tracks which instructions are ready to be executed (i.e. all its operands are available). This means that whenever there is a new result available, the logic has to check if it is the operand of any instruction that is present in the issue queue. A common implementation uses comparators in each entry of the issue queue. It compares the physical register of each new result produced by the FUs with the physical source registers of the instructions in the queue. The tags that identify the instructions that produce each result are broadcasted to all the entries of the issue queue.

b. Select: From all the ready instructions in the queue in a given cycle, it has to select a group of them to execute in the FUs. The selection must respect the FU allocation rules to prevent any structural hazard. i.e., the number and type of FUs, the issue latency of operations previously sent to them, clustering of FUs, etc. The maximum number of instructions than can be selected per cycle defines the issue width of the processor. If more than one instruction can be selected, the processor is considered a superscalar core.

#### 1.2.6 Main problems

It becomes apparent that out-of-order processors require several complex structures. Even worse, a technique like register renaming introduces a tight loop in the critical path of execution, since the physical register used by the instructions renamed in a given cycle are needed when renaming the instructions in the next cycle. This makes difficult to pipeline the renaming logic. Also, its complexity make these structures power-hungry.

An even more important problem is scalability. It has been shown that these structures don't scale well with quadratic increments in latency when the issue width or the length of the queues is increased [7].

#### **1.3** Repeated issue in the out-of-order processors

Functions and loops are basic structures used to code algorithms. Most of the time, out-of-order issue logic processes a reduced amount of different instructions and many cycles it ends up issuing together the same groups of independent instructions. Eventually, the schedule adapts to new situations such as a cache miss or a change in the executed path.

The issue logic of an out-of-order processor is a mechanism designed to find each cycle the maximum available parallelism. All current implementations do not remember any information about the parallelism found before, the latencies of the memory instructions or the dependences found in the past. They do not benefit from the repetitive behavior of code, unlike other processor elements, e.g. caches or branch predictors, that indeed rely on this characteristic of the programs to perform as expected. The issue logic is the only part of the processor designed to efficiently execute valid random code.

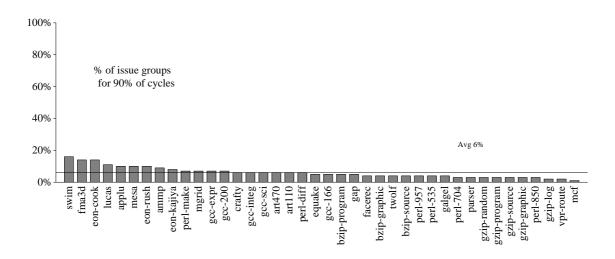

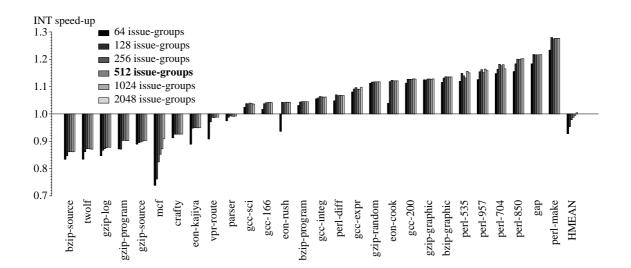

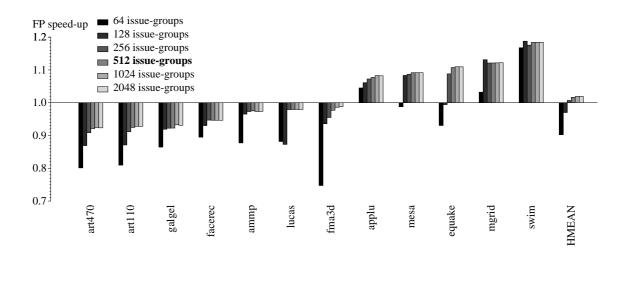

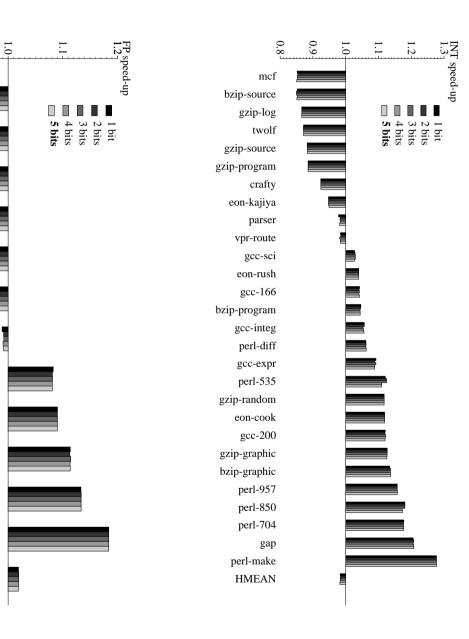

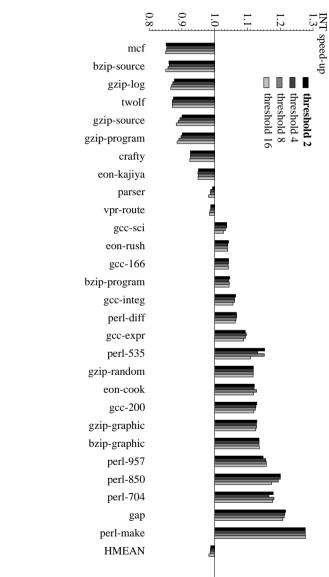

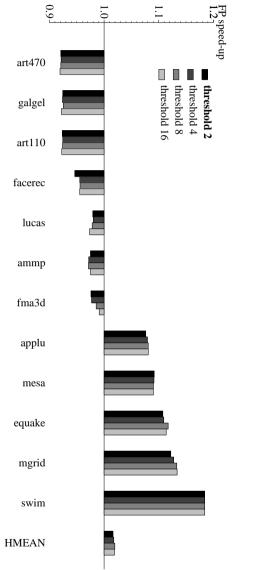

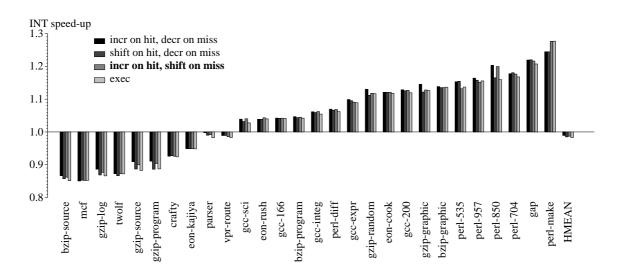

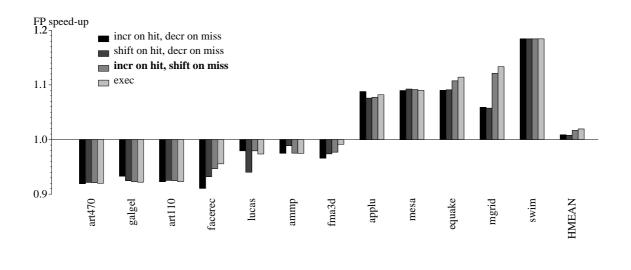

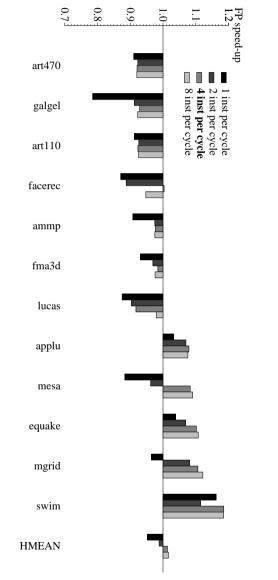

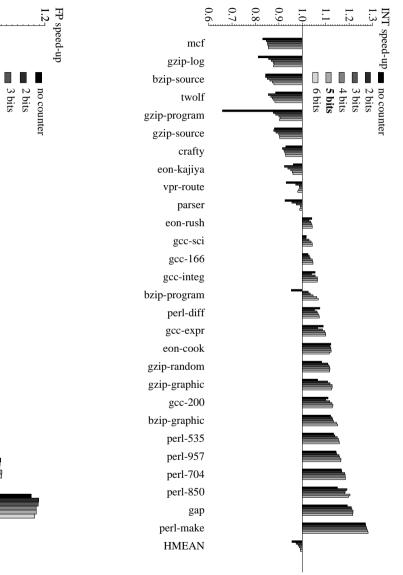

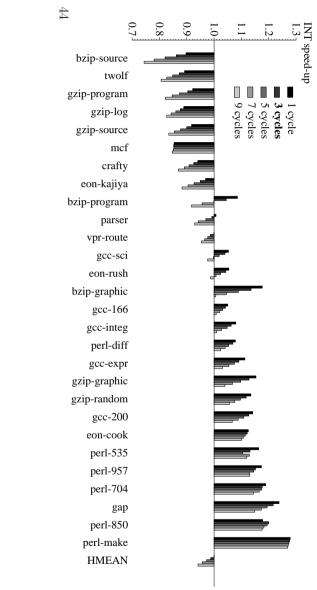

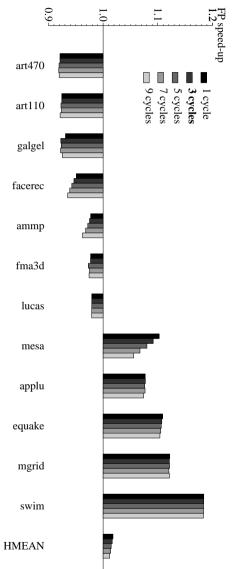

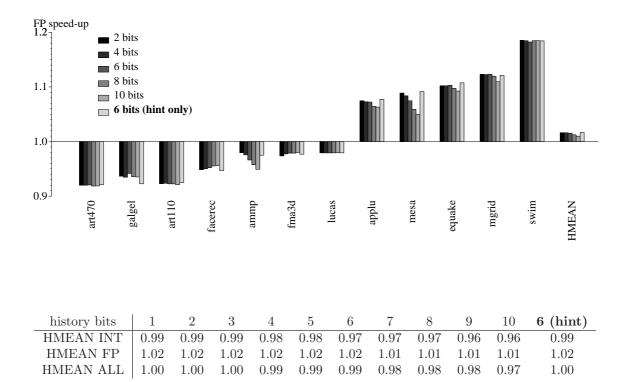

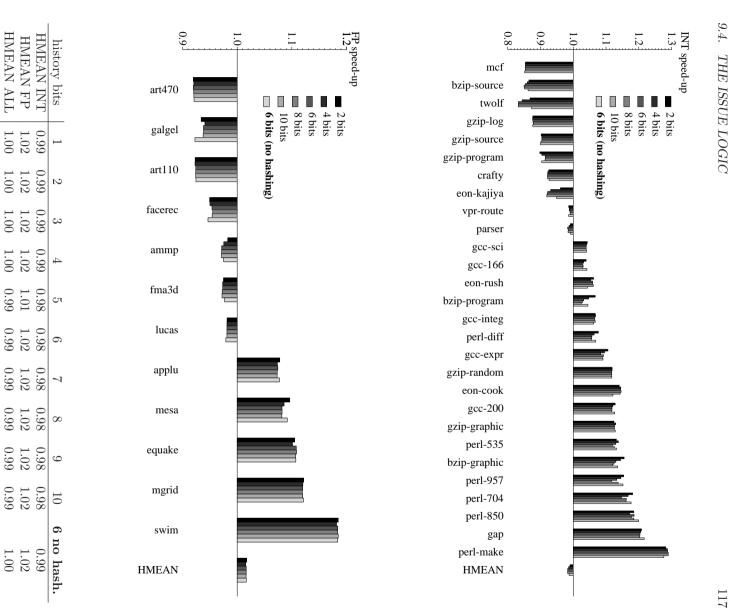

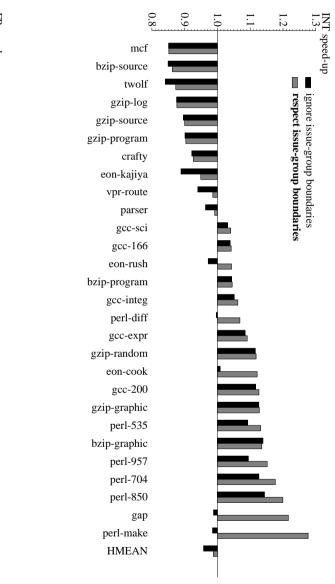

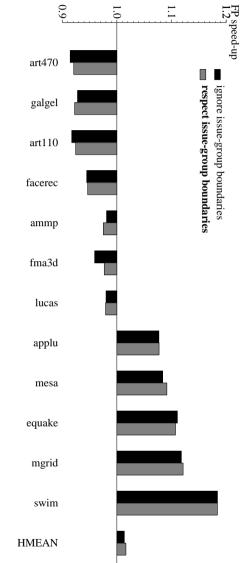

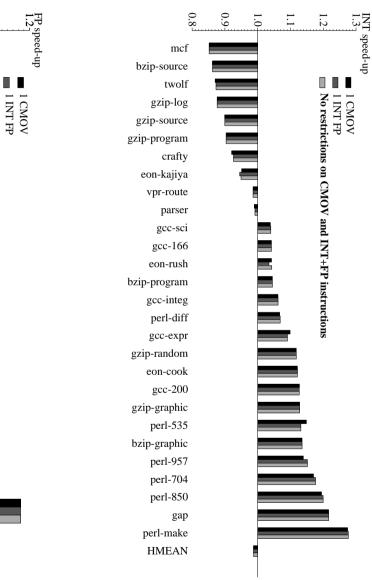

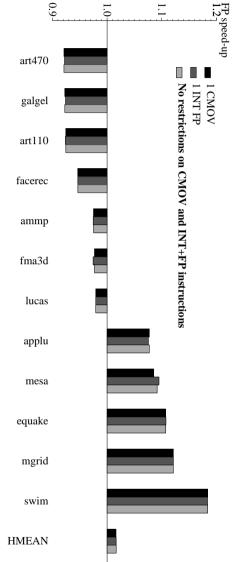

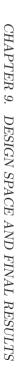

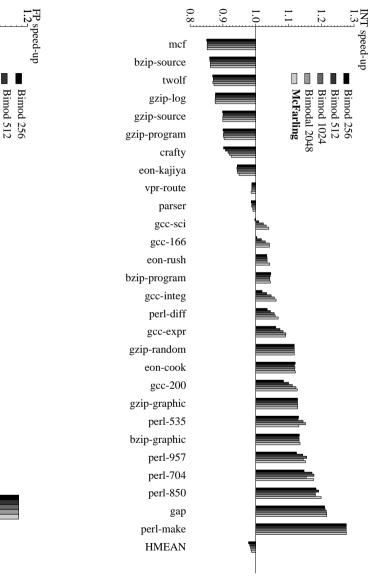

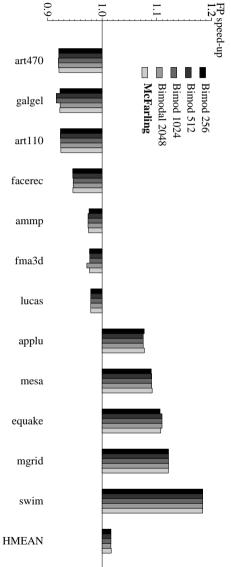

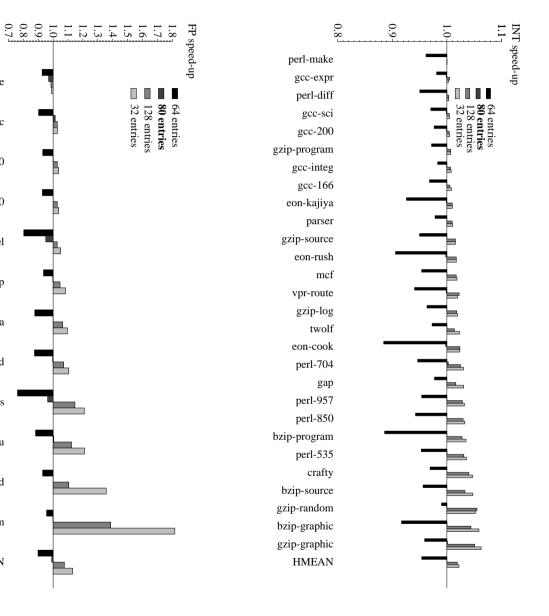

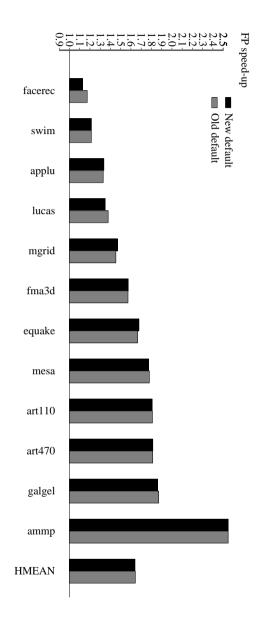

To show that the issue logic repeats most of its work, we have captured the **issue-groups** (instructions issued in the same cycle) created by an out-of-order processor on simulations of the SPECcpu2000 benchmarks for 100 millions of instructions. The experimental environment is presented in detail in section 9.1. Figure 1.2 shows the percentage of unique issue-groups that add up 90% of the cycles. From this data, a 90/10-like rule of thumb can be postulated: 6% of the issue-groups appear 90% of the cycles. Regrettably, the issue logic is constantly creating the same issue-groups in the critical path of execution. These experiments are examined in more detail in chapter 2.

#### 1.4 Proposal and thesis outline

We present the **ReLaSch** processor, named after Reused Late Schedules, in which the creation of issue-groups is removed from the critical path of execution. It uses a simple and small in-order

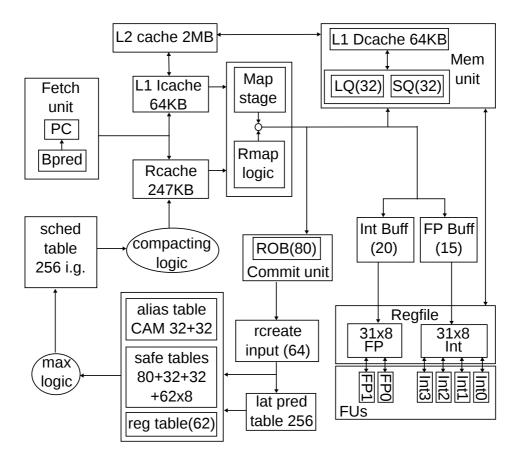

issue logic. It just wakes-up and selects the instructions of a single issue-group each cycle, instead of processing the instructions of a whole issue queue. The size of the issue-group is limited by the issue-width (four integer and two floating point instructions in the default ReLaSch and our reference processors), much smaller than the issue queue (20 integer and 15 floating point instructions in our reference out-of-order processor). Chapter 3 provides a general description of the ReLaSch processor.

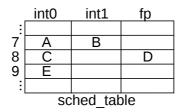

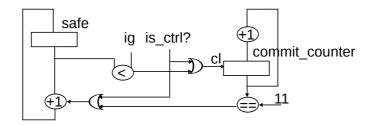

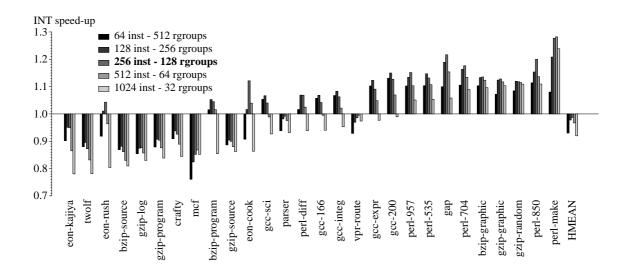

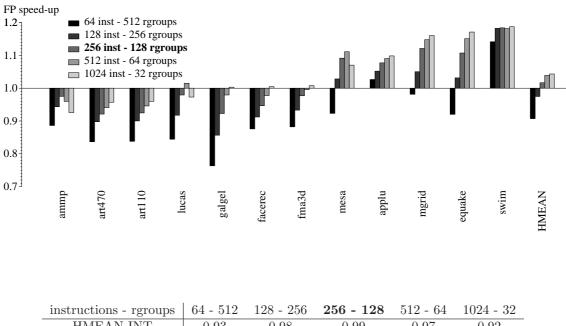

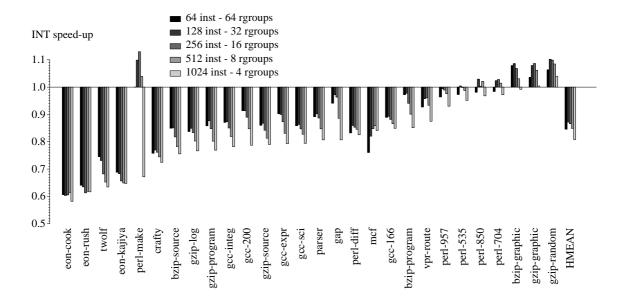

A new logic at the end of the conventional pipeline schedules the committed instructions into **rgroups** (which are sequences of issue-groups). The default configuration of ReLaSch uses 256-instruction rgroups, with issue-groups that include up to four integer and two floating point instructions each. The new scheduler can be complex since it is not in the critical path of execution: our experiments show that even using a 20-stage scheduler does not affect the IPC achieved. Chapter 4 describes the scheduler.

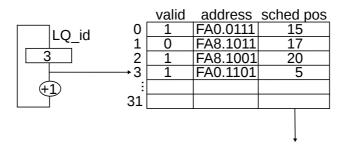

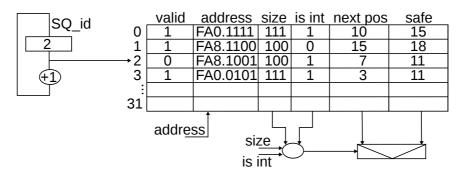

The rgroups are stored in a cache. Whenever it is possible, an rgroup is read and its instructions executed; the schedules are reused, thus lowering the pressure on the scheduling logic. The cache is presented in chapter 5, while the new front-end that reads the rgroups is described in chapter 6. The in-order issue logic is detailed in chapter 7, while a description of the rest of elements of the processor is included in chapter 8.

In some cases, the ReLaSch processor is able to outperform a conventional out-of-order processor, because the post-commit scheduler has a broader vision of the code. For instance, while ReLaSch can schedule together two independent instructions that are distant in the code, a conventional out-oforder processor only issues them in the same cycle if both are present at the same time in the issue queue.

Conventional out-of-order processors use branch prediction and memory aliasing speculation to find more available instructions. Besides that, their issue logic adapts to variable latency instructions. The ReLaSch processor predicts the branch targets, memory aliases and latencies at scheduling time, out of the critical path. The prediction is based on the most recent executions seen at scheduling time. Conventional branch predictors make their prediction at execution time and can adapt it faster than ReLaSch. ReLaSch average branch misprediction rate is slightly higher than that of a conventional branch predictor.

Out-of-order issue logic reacts immediately to changes in code behavior. ReLaSch relies on the repetitive nature of the code. Therefore, on a change the schedule mispredicts or stalls due to an

Figure 1.2: Number of unique issue-groups created by an out-of-order issue logic.

#### 1.5. SCOPE AND RESULTS SUMMARY

unexpected latency. To reduce the ammount of wasted cycles, it detects and replaces the rgroups that continuously fail.

The ReLaSch processor retains many techniques and elements from conventional out-of-order processors. It has a Reorder Buffer and a Commit stage to retire instructions in-order and provide precise interrupts. Additionally, it performs registers renaming to eliminate false dependences. Since the instructions of an issue-group are independent by construction, the renaming logic can process all the instructions of the issue-group in parallel and is simpler than the renaming logic of conventional out-of-order processors. ReLaSch doesn't detect the dependences between the instructions renamed in the same cycle.

Furthermore, most of the renaming process is performed by the scheduler and is removed from the execution pipeline. In particular, there is no loop in the renaming logic of the front-end; the instructions of an issue-group are renamed independently of the instructions of the previous issuegroup. The absence of a tight loop reduces the complexity of this logic and eases pipelining it if required. An alternative design for the register file is shown in appendix A.

There is previous work that proposes moving the scheduling logic out of the critical path and/or trying to reuse instruction schedules [8], [9], [10], [11]. Other approaches simplify the issue logic of an out-of-order processor or reduce the size of its issue queue. In chapter 10 the main differences and similarities of ReLaSch with these proposals are highlighted.

The work presented here has been already partially published. [12] presents a study on the issuegroups generated by conventional out-of-order and in-order processors. [13] describes the whole Re-LaSch processor and presents some experimental results. [14] provides an overview of ReLaSch and a preliminary study on the use of statically configurable maximum length of the rgroups.

#### 1.5 Scope and results summary

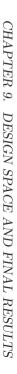

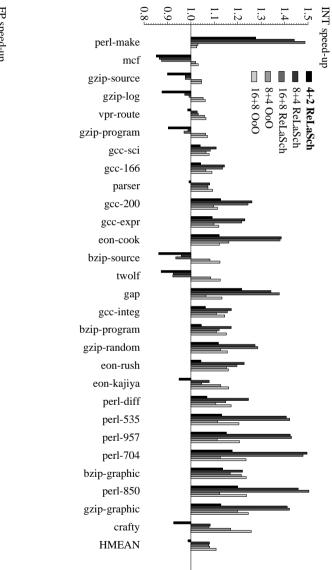

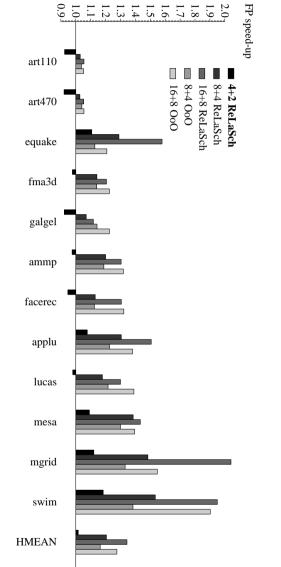

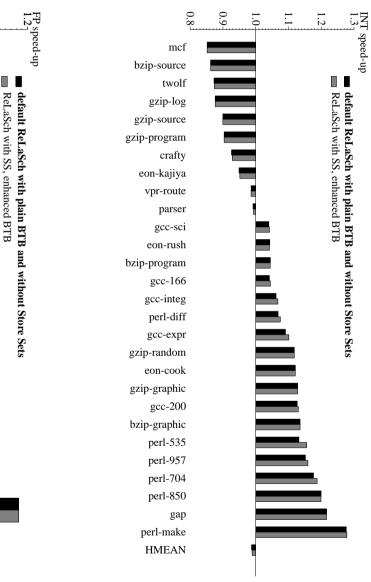

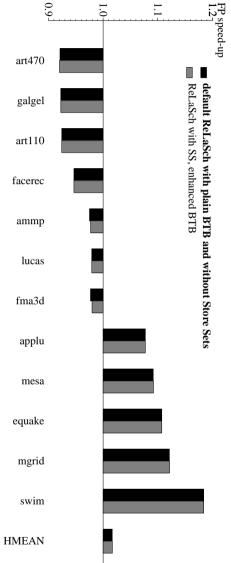

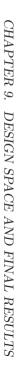

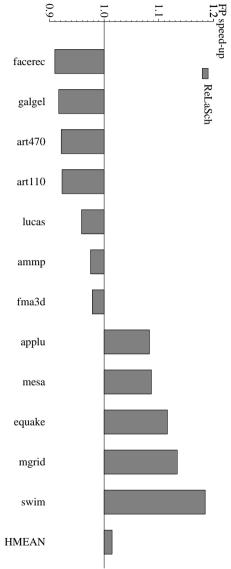

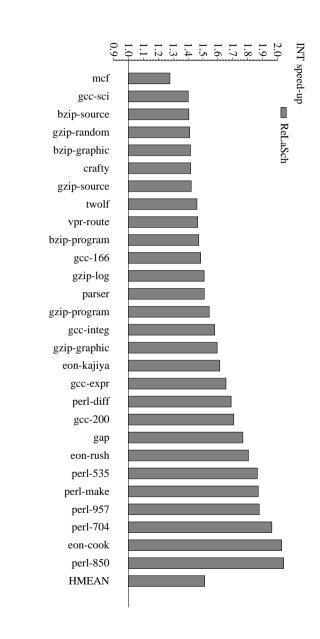

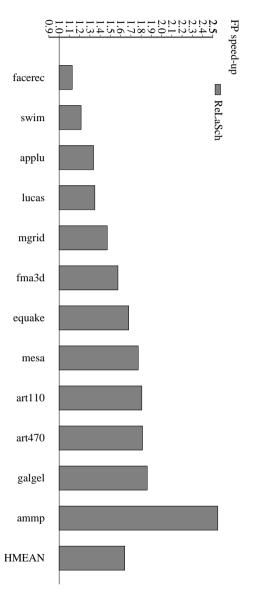

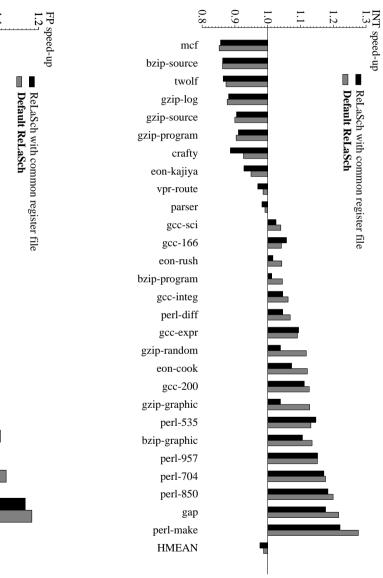

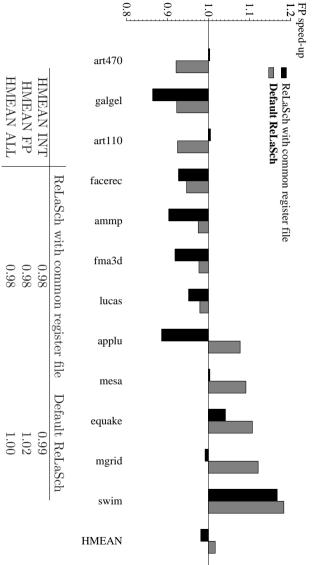

Our experiments show that the ReLaSch processor achieves the same average IPC as our reference out-of-order processor and is clearly better than the reference in-order processor (1.55 speed-up). In all cases it outperforms the in-order processor and in 23 SPEC benchmarks out of 40 it has a higher IPC than the reference out-of-order processor. Chapter 9 presents the experiments that we have conducted in order to explore the design space of the many parameters of the ReLaSch processor. It also presents the experimental results of ReLaSch when compared with the reference in-order and out-of-order processor. Chapter 11 presents the conclusions.

The performance results presented in this work assume that all the processors use the same frequency. However, it would be reasonable to assume that the in-order processor and our proposed ReLaSch processor can achieve a higher frequency. This would translate into a higher performance speed-up over the reference out-of-order processor than the IPC speed-up shown here. We do not evaluate cycle time but describe the microarchitecture and compare the IPC. It is a proof of concept in order to validate the potential of our proposal.

After our experiments show good IPC results and back up our proposal, power consumption should also be taken into consideration. Power is not evaluated in this thesis, but it is part of the future work presented in chapter 11. We must take into account both the positive and negative impact in the power requirements of ReLaSch. On one hand, the in-order issue logic of ReLaSch is much simpler and it is very likely to be much less power-hungry than the issue logic of a conventional out-of-order processor. Moreover, the scheduler is not required to work each cycle, which can result in less energy consumed. On the other hand, the cache of schedules is a new source of energy consumption and is not present in a conventional out-of-order processor. Additionally, the structures needed by the scheduler increase our energy consumption. We expect that the reduction due to the in-order issue logic and the reduced criticality of the scheduler will outweigh the new sources of energy consumption.

To support this expectation, there is the fact that we have reduced the complexity in the critical

path of execution while adding new structures in a scheduler out of this critical path. Thus, aggressive power- and energy- saving techniques can be applied to the scheduler since they are unlikely to have a significant impact in performance. The exception is the cache of schedules that is a new source of energy consumption in the execution path. However, in this case we can also easily apply powerand energy- saving techniques when power consumption and battery lifetime have higher priority than performance. It is very simple to switch off portions of the cache and trade-off energy for performance. Also the scheduler can be switched off even when it would be possible to create new schedules. These power-saving techniques have some granularity and would be simple to implement. Finally, the scheduler can be designed to place the instructions following power-saving techniques. Taken all these ideas into account, we consider that ReLaSch has potential to be power-efficient.

18

### Chapter 2

# Motivation

In this chapter we study the repetitiveness of the groups of instructions that are selected by the issue logic. This repetitiveness enables designing a processor that reuses schedules that are created just once.

#### 2.1 Reference processors

This section presents the reference processors used in this study.

#### The OoO processor

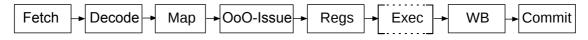

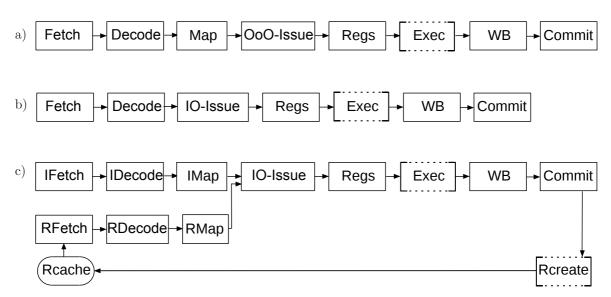

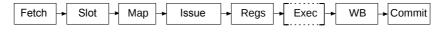

Figure 2.1 shows the pipeline of an improved out-of-order processor (OoO) based on the 21264 Alpha [15] (see appendix B), enhanced with better memory alias detection and branch target prediction. The pipeline is much like in the 21264 Alpha processor.

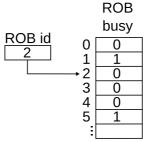

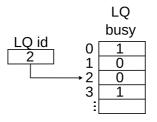

The Fetch stage reads the instructions from the instruction cache (Icache) and accesses the branch predictor. The result of the prediction is not known until one cycle later. The next stage completes the branch prediction and decodes the instructions. The Map stage renames the instructions and inserts them in the Reorder Buffer (ROB), in the issue queue and in the Load and Store queues (LQ and SQ) if needed. The integer and floating point instructions use separated issue queues. These three first stages process the instructions in-order.

The Issue stage wakes-up and selects out-of-order instructions that are present in the issue queue. It selects up to four integer and two floating point instructions per cycle. An instruction can be selected if its source registers are ready and a suitable Functional Unit is available. Older instructions in the queue have higher priority. Registers are read in the next stage and execution happens in the corresponding functional unit afterwards. Once the execution in the functional unit finishes, the registers are written during the Writeback (WB) stage, where the loads also start the access to the data cache (Dcache). The Writeback stage also checks for memory ordering violations with the help of the LQ and SQ.

Finally, instructions are retired in-order in the Commit stage. Once a completed instruction reaches the head of the ROB, the Commit stage sets its destination physical register as the architectural register for the corresponding logical register, checks for mispredictions and frees the entry used by the instruction in the ROB and in the LQ or the SQ if needed. It also performs the access to memory of store instructions.

Our OoO reference processor improves the original microarchitecture of the Alpha 21264 in two ways: First, the BTB is enhanced with a path-indexed table, used to predict the multi-target indirect branches. Second, the StWait bits, that are used in the 21264 Alpha to reduce the number of loads

that must be re-executed due to memory order violations, are substituted in the OoO processor by a better mechanism: the Store Sets [16]. With Store Sets, a load waits only until the aliased stores have committed, instead of waiting for all the in-flight stores, with a corresponding performance gain.

The ROB has 80 entries, the instruction queue has 20 entries for integer instructions and 15 for floating point instructions. The integer register file has 72 physical registers and the floating point register file has another 72. The LQ and the SQ have 32 entries each. The issue logic can process up to four integer and two floating point instructions per cycle. A complete description of the architectural parameters is shown in table 9.1 of chapter 9.

Figure 2.1: The pipeline of the OoO processor.

#### The IO processor

Figure 2.1 shows the pipeline of the in-order processor (IO) that we use as reference. It is also based on the 21264 Alpha but it has an in-order Issue stage. Besides, it does not rename the instructions, so the Map stage is removed from the pipeline. In the Decode stage, the instructions are inserted in the ROB (to support speculation) and in the issue buffer, that substitutes the issue queue of the Alpha 21264 processor. The issue logic selects up to four integer and two floating point instructions per cycle. The Commit stage is still needed to check the correctness of the branch prediction and the ROB is also used to allow the multi-cycle instructions to write the results out-of-order while maintaining precise exceptions. It uses the same Store Sets and the enhanced BTB of our reference OoO processor.

Figure 2.2: The pipeline of the IO processor.

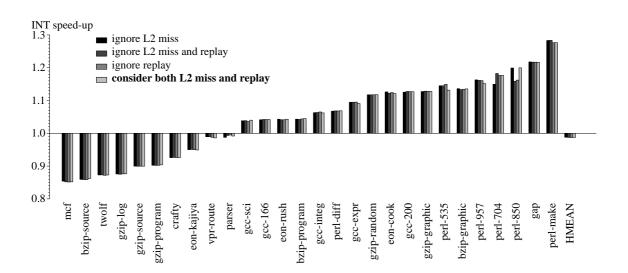

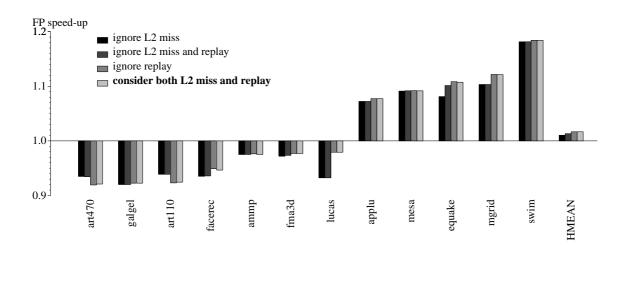

#### 2.2 Contribution of dynamic scheduling to performance

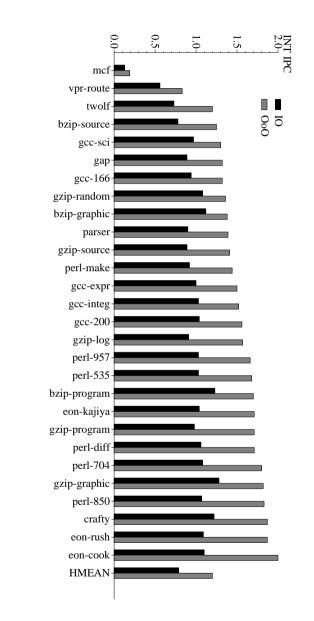

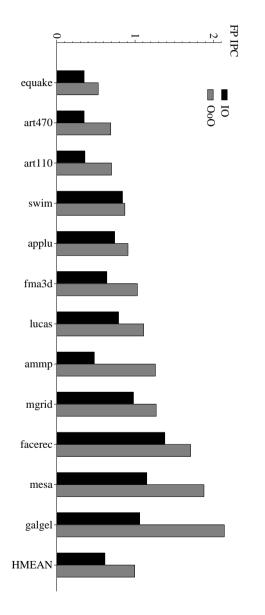

Figure 2.3 shows the IPC achieved by the two processors. In average, the IPC of the OoO processor is 56% higher than the IPC of the IO processor.

In the static scheduling approach, if an instruction stalls waiting for an operand that is not available yet, the processor does not allow any younger instruction to start its execution. In order to improve performance, the compiler takes into account the latencies when scheduling the dependent instructions, placing independent instructions between the producer and the dependent instructions. However, many times it does not find enough independent instructions to eliminate all the stalls in the IO processor. Furthermore, there are instructions with variable latency, such as memory instructions, which the compiler has to schedule assuming a fixed latency. While the OoO processor can adapt the schedule to the actual latency of these instructions, the IO processor stalls each time the actual latency is larger than the one expected by the compiler (for example, when a load misses in the Dcache but was scheduled assuming hit).

An additional problem is that a processor can issue together instructions from different basic blocs using a branch predictor. Both in-order and out-of-order processor can benefit from branch prediction. However, when the processor uses a branch predictor and executes instructions speculatively, new dependences appear across the basic blocks. Which dependences appear at execution time depend on

Figure 2.4: Distribution of the issue-group size depending on the instruction scheduling policy, in a four-integer and two-floating point issue processor.

which path follow the branches. The compiler cannot create an efficient schedule for all the possible combinations of basic blocs, so the in-order processor stalls often whereas the out-of-order processor is able to adapt its schedule to the actual dependences of the predicted path.

The register renaming logic assigns a new physical register each time a logical register is used as destination. Dependent instructions that use the logical register as source operand actually read the renamed physical register. Thus false dependences are eliminated. Dynamically-scheduled processors hugely benefit from this technique, since it is able to find much more independent instructions per cycle.

To regularly find enough ready instructions each cycle, the issue logic of out-of-order processors needs a large issue queue, from which it selects the instructions to issue. The issue queue stores the instructions after they are decoded and renamed and until they are issued. Instructions wait there for their source operands to become ready. The wake-up logic notifies to the instructions in the issue queue that a register is available. With a large issue queue, the issue logic finds more ready instructions per cycle, but it also grows the complexity of the wake-up and select logic [7].

#### 2.2.1 Quantitative analysis of the behavior of the dynamic-scheduling logic

In a superscalar processor, a high IPC is achieved by issuing together as many instructions as possible. To measure how much of that work is redundant, we keep track of the issue-groups that are created during execution. We define an issue-group as the instructions that are issued in the same cycle. The issue-groups may include instructions from a mispredicted path.

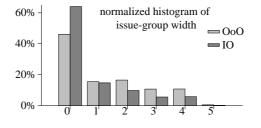

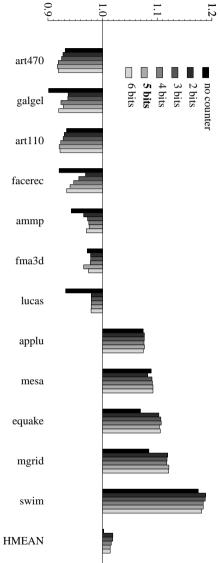

Figure 2.4 shows the normalized histogram of the size of the issue-groups, for the IO and the OoO processors. Both processors can issue up to four integer and two floating point instructions per cycle. The ability of the dynamic scheduler to find independent instructions allows the OoO processor to have larger issue-groups in average. Besides, the in-order issue logic stalls frequently and most of the cycles is not able to issue any instruction at all.

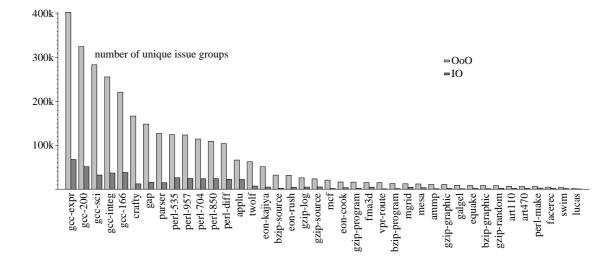

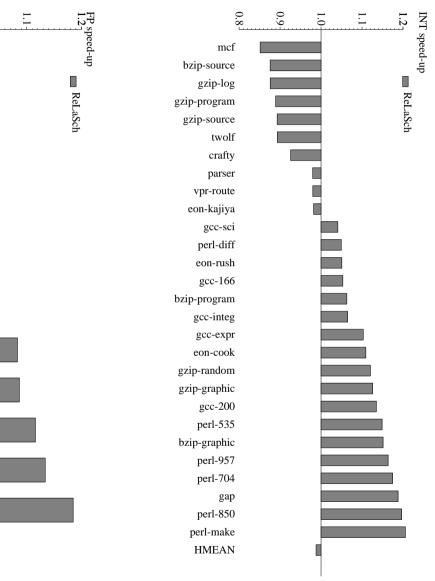

We consider two issue-groups to be equal if they have the same number of instructions and the PCs of the instructions of both issue-groups match. Figure 2.5 shows how many unique issue-groups are created during the execution of each benchmark (100M instructions per benchmark). The figure is ordered by decreasing number of issue-groups created by the OoO processor. The rest of figures in this chapter follow this same order. From the figure, we can see that the number of issue-groups is much smaller than the total number of cycles. Having less restrictions to issue the instructions, the OoO processor creates a higher number of unique issue-groups during the execution of each benchmark.

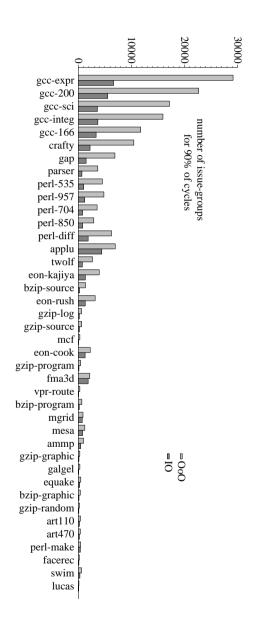

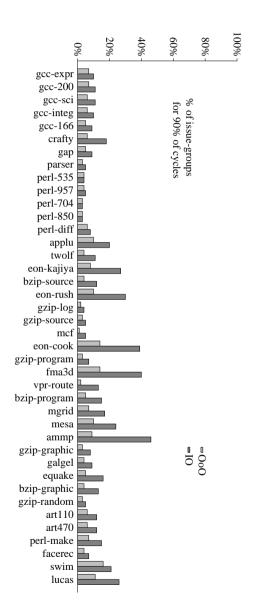

Not all the issue-groups are executed the same number of times and we expect that a small percentage of issue-groups are executed frequently than the rest. Figure 2.6 shows how many unique issue-groups are needed to accumulate the 90% of the cycles (excluding the cycles where no instruction is issued). Figure 2.7 shows the same information as a percentage of the total number of unique issue-

Figure 2.5: Number of unique issue-groups created by the OoO and IO processors (up to four integer and two floating point instructions per cycle).

groups created for each benchmark. As expected due the repetitive nature of code, the experiments show that the dynamic scheduler is constantly creating a reduced set of issue-groups, which appear again and again. Only from time to time it creates different issue-groups. In average, the 90% of the execution is covered with only a 6% of the total unique issue-groups.

#### 2.3 Reusing the dynamic schedules

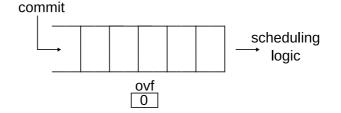

Given that most of the time the issue logic repeats the selection of instructions that it schedules, it seems reasonable that a new processor could use a dynamic scheduler only when new instructions are executed or there is change in the behavior of the code (for example, when a branch changes its behavior or a load misses in data cache). The issue-groups created then would be cached and the processor would read the issue-groups from the cache the rest of the time. When the issue-groups are not available in the cache, the processor would issue the instructions in-order, using a simple issue logic.

Such a processor is expected to achieve the IPC of an out-of-order processor when the issue-groups are read from the cache and the IPC of an in-order processor when the required issue-group is not available in the cache. There would be some additional penalties for changing the execution mode. So such a processor needs a high hit-rate in the issue-group cache to achieve a high IPC.

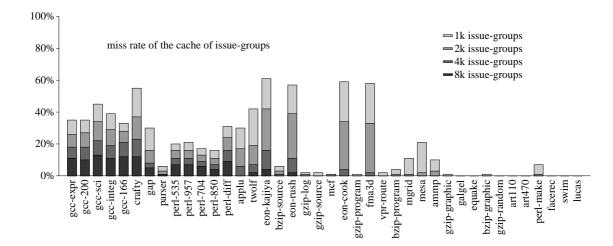

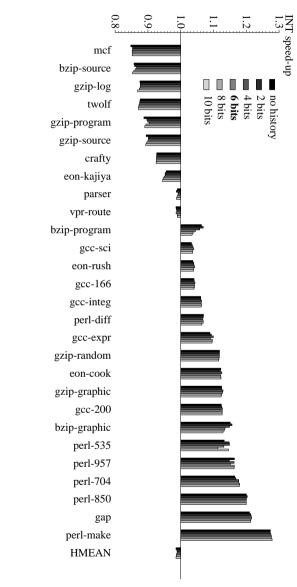

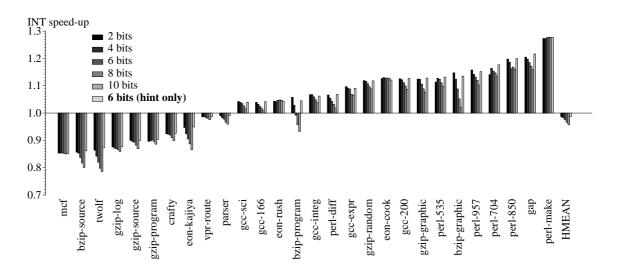

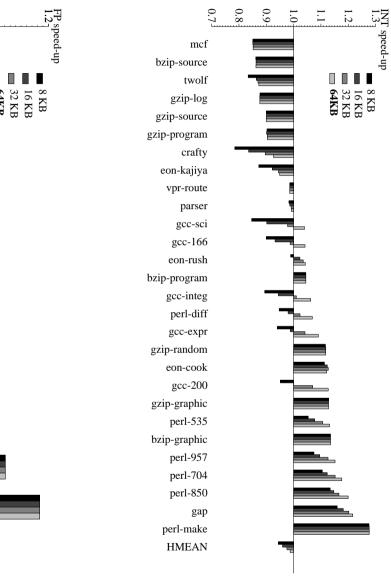

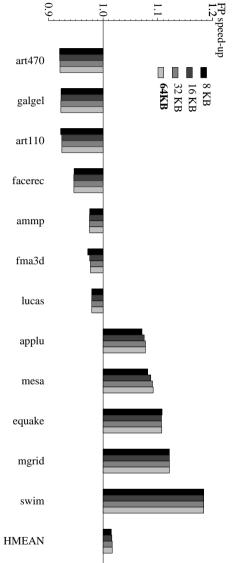

We have evaluated the miss-rate of a cache that stores the issue-groups as they are created by the issue-logic of the OoO processor (with a four-integer and two-floating point wide issue logic). The cache is not used in the experiment to feed the processor but it is just used to study the locality of the issue-groups. The PCs of the instructions in the issue-group are hashed. The result of the hash is used to index the cache. The cache is four-way set-associative and the number of issue-groups it can store varies from 1K to 8K.

Figure 2.8 shows the miss-rate of the cache. The results for the different sizes of the cache are shown overlapped in the figure. The results show that there is some degree of locality in the issue-groups created: in average, the 4K-issue-group cache has a 6% miss rate.

For each instruction in an issue-group the cache should store the PC and the encoded instruction. The encoded instruction is needed to execute it. We are assuming that the processor would use some

is sue-groups created by the IO and the OoO processors. Figure 2.6: Number of unique issue-groups responsible of 90% of the total number of not-empty

Figure 2.7: Percentage of unique issue-groups responsible of 90% of the total number of not-empty issue-groups created by the IO and the OoO processors.

Figure 2.8: Miss rate of an issue-group cache for the OoO processor.

kind of prediction to decide which is the next issue-group to fetch and execute. Thus, the PC would be needed to check on the Commit stage whether the instruction is in the correct path and it should be actually executed. Therefore, the cache has to store 32 bits for the instruction and 46 bits for the PC, according to the Alpha 21264 parameters. With four integer and two floating point instructions per issue-group, that adds up to 468 bits per issue-group. The 4K-issue-group cache needs 234KB. The rest of configurations used in the experiments need between 58KB and 468KB.

#### Sequences or stand-alone issue-groups

The cache of issue-groups studied above stores the issue-groups individually. It is possible to design a processor that executes the issue-groups from such a cache. However, it yields much better results to store together sequences of issue-groups, that are always executed in the order that they are stored.