# SPECULATIVE VECTORIZATION FOR SUPERSCALAR PROCESSORS

A Dissertation Presented

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Doctor per la Universitat Politècnica de Catalunya

by Alex Pajuelo González July 2005

# SPECULATIVE VECTORIZATION FOR SUPERSCALAR PROCESSORS

Alex Pajuelo González

Thesis advisors:

Antonio González

Mateo Valero

Departament d'Arquitectura de Computadors

Universitat Politècnica de Catalunya, 2005

A mi familia. A Laura.

#### ABSTRACT

Traditional vector architectures have been shown to be very effective in executing regular codes in which the compiler can detect data-level parallelism, i.e. repeating the same computation over different elements in the same code-level data structure.

A skilled programmer can easily create efficient vector code from regular applications. Unfortunately, this vectorization can be difficult if applications are not regular or if the programmer does not have an exact knowledge of the underlying architecture.

The compiler has a partial knowledge of the program (i.e. it has a limited knowledge of the values of the variables). Because of this, it generates code that is safe for any possible scenario according to its knowledge, and thus, it may lose significant opportunities to exploit SIMD parallelism. In addition to this, we have the problem of legacy codes that have been compiled for former versions of the ISA with no SIMD extensions, which are therefore not able to exploit new SIMD extensions incorporated into newer ISA versions.

In this dissertation, we will describe a mechanism that is able to detect and exploit DLP at runtime by speculatively creating vector instructions for prefetching and precomputing data for future instances of their scalar counterparts. This process will be called *Speculative Dynamic Vectorization*.

A more in-depth study of this technique reveals a very positive characteristic: the mechanism can easily be tailored to alleviate the main drawbacks of current superscalar processors, particularly branch mispredictions and the memory gap. In this dissertation, we will describe how to rearrange the basic Speculative Dynamic Vectorization mechanism to alleviate the branch misprediction penalty based on reusing control-flow independent instructions. The memory gap problem will be addressed with a set of mechanisms that exploit the stall cycles due to L2 misses in order to virtually enlarge the instruction window.

Finally, more refinements of the basic Speculative Dynamic Vectorization mechanism will be presented to improve its performance at a reasonable cost.

#### ACKNOWLEDGEMENTS

First of all, I would like to thank to my thesis advisors Antonio González and Mateo Valero all these years of hard work and unconditional support. In particular, to show me two different points of view of the same thing.

My family has been a great support. This document is the answer to your repetitive question. Specially, I thank Laura for her infinite patience during all these years. Finally, I have finished it!

The PhD students of the Computer Architecture Department have proved to be very good friends. In any order: Jaume Abella, Javier Verdu, Francisco Cazorla, Oliver Santana, Jordi Guitart, Josep Maria Codina, Tanausu Ramírez, Carmelo Acosta, Ayose Falcon, Germán Rodríguez, Marco Galluzi, Enric Gibert, Josep Aguilar, Victor Mora, Jaume Vila, José Lorenzo Cruz, Ramon Canal, Joan Manel Parcerisa, Daniel Jiménez and Alex Settle. Thanks for all those coffee breaks and for those launch parties.

David López, thank you for show me that a researcher is always a person. Thank you for teach me how to teach. I hope I recover my peace within as you did!

Of course, I would like to thank all those anonymous reviewers who accept/reject my papers. All their comments are valuables and have been had into account to improve the work.

Finally, I would like to thank you, anonymous reader, for your time reading this dissertation. I hope you enjoy it as much as I enjoyed write it.

This work has been partially supported by the Ministry of Education and Science under grants TIN2004-07739-C02-01 and TIN2004-03072, the CICYT project TIC2001-0995-C02-01, the Feder Funds, Intel Corporation and the European Network of Excellence on High Performance Embedded Architecture and Compilation (HiPEAC).

# TABLE OF CONTENTS

| 1 Intro | oduction 1                                                                                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1     | Motivation $\ldots \ldots 3$                                                                    |

|         | 1.1.1 Speculative execution                                                                                                                                    |

|         | 1.1.2 Vector execution $\ldots \ldots 5$                                                        |

|         | 1.1.3 Thesis objectives $\ldots \ldots \ldots$ |

| 1.2     | Thesis overview                                                                                                                                                |

|         | 1.2.1 Speculative dynamic vectorization                                                                                                                        |

|         | 1.2.2 Reducing the penalty of branch mispredictions                                                                                                            |

|         | 1.2.3 Overcoming the memory gap                                                                                                                                |

|         | 1.2.4 Cost-effective dynamic vectorization                                                                                                                     |

|         | 1.2.5 Mechanism comparison $\ldots \ldots 12$                       |

| 1.3     | Structure of this work                                                                                                                                         |

|         |                                                                                                                                                                |

|         | form and Benchmarks 15                                                                                                                                         |

| 2.1     | Introduction                                                                                                                                                   |

| 2.2     | Reference platform                                                                                                                                             |

|         | 2.2.1 Scalar pipeline                                                                                                                                          |

|         | 2.2.2 Vector capabilities $\dots \dots \dots$                  |

| 2.3     | Benchmarks                                                                                                                                                     |

|         | 2.3.1 Irregular codes $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                                               |

|         | 2.3.2 Regular codes $\ldots \ldots 22$                                                          |

| 2.4     | Simulation framework                                                                                                                                           |

| 3 Spec  | culative Dynamic Vectorization 25                                                                                                                              |

| 3.1     | Introduction                                                                                                                                                   |

| 3.2     | Motivation                                                                                                                                                     |

| 3.3     | Related work                                                                                                                                                   |

| 3.4     | Overview                                                                                                                                                       |

| 3.5     | First approach: Dynamic Vectorization with vector resources 32                                                                                                 |

| 0.0     | 3.5.1 Instruction vectorization                                                                                                                                |

|         | 3.5.2 Vector registers                                                                                                                                         |

|         | 3.5.3 Vector data path                                                                                                                                         |

|         | 3.5.4 Branch mispredictions                                                                                                                                    |

|         | and control-flow independence                                                                                                                                  |

|         | ▲<br>▲                                                                                                                                                         |

|         | - 3 5 5 VIEWOLV DISAMDIGUATION                                                                                                                                 |

|         | 3.5.5       Memory disambiguation       38         3.5.6       Wide bus       39                                                                               |

| 36      | 3.5.6 Wide bus                                                                                                                                                 |

| 3.6     | 3.5.6 Wide bus                                                                                                                                                 |

| 3.6     | 3.5.6Wide bus                                                                                                                                                  |

| 3.6     | 3.5.6Wide bus39Second approach: Dynamic39Vectorization with scalar resources393.6.1Motivation39                                                                |

| 3.6     | 3.5.6Wide bus                                                                                                                                                  |

|              | The Scalar Register Set Map Table                                                                       | 41 |

|--------------|---------------------------------------------------------------------------------------------------------|----|

|              | Issue logic                                                                                             | 44 |

|              | Branch mispredictions                                                                                   | 44 |

|              | Memory disambiguation                                                                                   | 45 |

|              | Wide bus                                                                                                | 45 |

|              | Replica register file                                                                                   | 46 |

| 3.7          | Performance evaluation                                                                                  |    |

|              | 3.7.1 Dynamic Vectorization performance                                                                 | 48 |

|              | Management of the memory system                                                                         |    |

|              | Reuse of precomputed data                                                                               |    |

|              | Virtual enlargement of the instruction window                                                           |    |

|              | Control-flow independence reuse                                                                         |    |

| 3.8          | Summary                                                                                                 |    |

| 4 Cont       | rol-Flow Independence Reuse                                                                             | 57 |

| 4.1          | Introduction                                                                                            |    |

| 4.2          | Motivation                                                                                              |    |

| 4.3          | Related work                                                                                            |    |

| 4.4          | The approach                                                                                            |    |

| 1.1          | 4.4.1 Control flow independent instructions                                                             |    |

|              | 4.4.2 Overview of the mechanism                                                                         |    |

|              | 4.4.3 First step: hard-to-predict branches                                                              | 02 |

|              | and re-convergent point detection                                                                       | 64 |

|              | 4.4.4 Second step: control-flow independent instruction detection                                       | 01 |

|              | and filtering                                                                                           | 66 |

|              | 4.4.5 Third step: instruction replication                                                               |    |

|              | 4.4.6 Fourth step: data validation                                                                      |    |

| 4.5          | Performance evaluation                                                                                  |    |

| 1.0          | Control independence scope                                                                              |    |

|              | Register file pressure                                                                                  |    |

|              | Control independent reuse out of the instruction window                                                 |    |

| 4.6          | -                                                                                                       |    |

| 5 Over       | coming the Memory Gap                                                                                   | 83 |

| 5.1          | Introduction                                                                                            |    |

| $5.1 \\ 5.2$ | Motivation                                                                                              |    |

| 5.3          | Related work                                                                                            |    |

| 5.4          | First approach: L2miss                                                                                  |    |

| 0.4          | 5.4.1 Overview                                                                                          |    |

|              | 5.4.2 First step: strided load propagation                                                              |    |

|              | 5.4.3 Second step: strided load selection                                                               |    |

|              | 5.4.4 Third step: instruction replication                                                               |    |

|              | 5.4.5 Fourth step: data validation                                                                      |    |

|              | $0.4.0$ routin step. data valuation $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 30 |

| 5.5            | Second approach: $L2stall$                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 5.5.1 Overview                                                                                                                                                 |

|                | 5.5.2 First stage: instruction selection                                                                                                                       |

|                | 5.5.3 Second stage: resource allocation                                                                                                                        |

|                | 5.5.4 Third stage: instruction replication $\dots \dots \dots$ |

|                | 5.5.5 Fourth stage: data validation $\dots \dots 98$                             |

| 5.6            | Performance evaluation                                                                                                                                         |

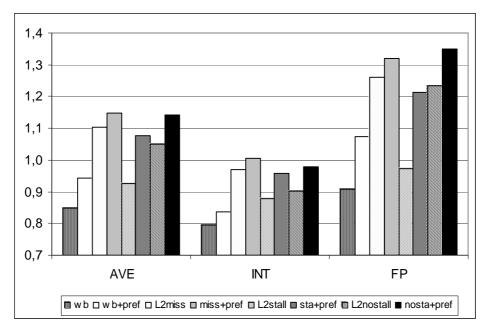

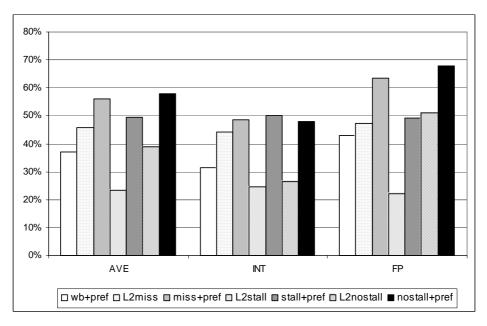

|                | 5.6.1 Performance improvement                                                                                                                                  |

|                | 5.6.2 $L2miss$ versus $L2stall/L2nostall$                                                                                                                      |

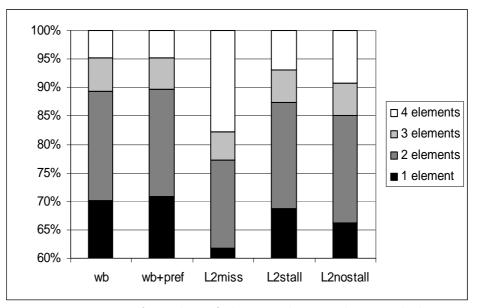

|                | 5.6.3 Virtual enlargement of the instruction window 105                                                                                                        |

| 5.7            | Summary                                                                                                                                                        |

| 6 Cost         | -Effective Dynamic Vectorization 109                                                                                                                           |

| 6.1            | Introduction                                                                                                                                                   |

| 6.2            | Motivation                                                                                                                                                     |

| 6.3            | Dynamic vectorization mispredictions                                                                                                                           |

|                | sources                                                                                                                                                        |

|                | Stride mispredictions                                                                                                                                          |

|                | Wrong construction mispredictions                                                                                                                              |

|                | DAEC mispredictions                                                                                                                                            |

|                | Scalar source operand mispredictions                                                                                                                           |

|                | Replicated source operand mispredictions                                                                                                                       |

| 6.4            | Heuristics                                                                                                                                                     |

|                | 6.4.1 Fine grain heuristics                                                                                                                                    |

|                | Incremental number of replicas                                                                                                                                 |

|                | Decremental number of replicas                                                                                                                                 |

|                | Assignation by halves                                                                                                                                          |

|                | Heuristic based on last reuse                                                                                                                                  |

|                | 6.4.2 Coarse grain heuristics                                                                                                                                  |

|                | Number of iterations                                                                                                                                           |

|                | Dependent load blockade                                                                                                                                        |

|                | Block information                                                                                                                                              |

|                | 6.4.3 Criticality                                                                                                                                              |

| 6.5            | Performance evaluation                                                                                                                                         |

| 6.6            | Summary                                                                                                                                                        |

| <b>-</b> 7 7 1 |                                                                                                                                                                |

|                | nanism Comparison 131                                                                                                                                          |

| 7.1            | Introduction                                                                                                                                                   |

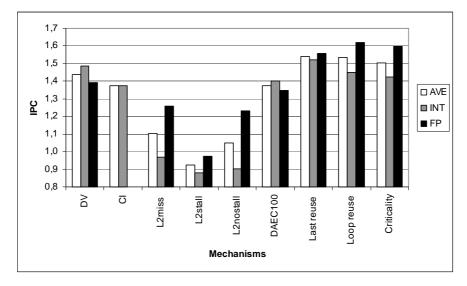

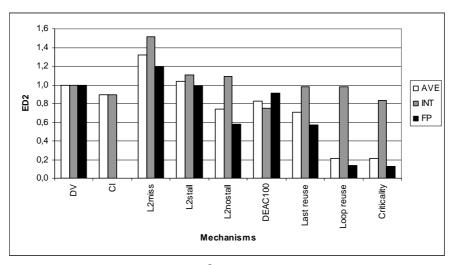

| 7.2            | Mechanism comparison                                                                                                                                           |

|                | 7.2.1 Hardware                                                                                                                                                 |

|                | 7.2.2 Performance $\dots \dots \dots$                          |

| <u> </u>       | 7.2.3 Energy-Delay <sup>2</sup>                                                                                                                                |

| 7.3            | Summary                                                                                                                                                        |

| 8 Conclusions 143   |                                               |     |  |

|---------------------|-----------------------------------------------|-----|--|

| 8.1                 | Fundamentals of this work                     | 145 |  |

|                     | 8.1.1 Background to this thesis               | 145 |  |

|                     | 8.1.2 Objectives of this thesis               | 145 |  |

| 8.2                 | Accomplishments                               | 146 |  |

|                     | 8.2.1 Main contributions                      | 146 |  |

|                     | 8.2.2 Detailed breakdown of the contributions | 148 |  |

| 8.3                 | Remarks and future work                       | 151 |  |

| List of             | tables                                        | 152 |  |

| List of figures 154 |                                               |     |  |

| Referen             | References 15                                 |     |  |

Chapter 1

Introduction

## 1.1 MOTIVATION

Nowadays, the software-hardware cooperation present in current computers seeks to maximize the throughput of applications. On the one hand, a software compiler translates applications from a high-level to a low-level language that the processor can comprehend. Furthermore, during the translation process, the compiler interprets the code in order to apply, if possible, optimizations to improve the performance of the application. However, due to the fact that the compiler has a limited knowledge of the application, the low-level code that is generated is conservative which reduces the opportunities to exploit the parallelism that is available.

On the other hand, hardware processors include mechanisms for efficiently executing the low-level coding of applications. These mechanisms study the code at runtime to detect and exploit several levels of parallelism, even if they are not clearly exposed by the compiler.

This software-hardware cooperation is more effective when the compiler has an extensive knowledge of the applications and/or the target processors. In these cases the compiler can easily detect and pass on semantic information on the application to the processor through a specialized ISA. This information helps the processor to be more effective in executing applications.

Scientific scenarios can be good examples of this cooperation. The main characteristic of scientific applications is that large amounts of *Data Level Parallelism* (DLP) are exposed by the high level language. This parallelism consists in repeating the same computation on different elements in large data structures such as vectors or matrices. This DLP can easily be detected by a vectorizing compiler that is able to pass this semantic information through a *Single Instruction Multiple Data* (SIMD) ISA to a vector processor. This processor is very effective in executing this kind of code since it provides wide resources in which several elements of a vector can be held and computed in parallel.

Superscalar processors are a good alternative for executing applications with a

moderate amount of DLP. These processors rely on compilers to expose *Instruction Level Parallelism* (ILP). This fine-grain parallelism seeks to execute small sections of the code, usually instructions, in parallel. Furthermore, these processors include mechanisms for speculatively executing portions of the code to expose more ILP. Recently, vector-like resources have been included in these processors to efficiently exploit the DLP exposed by the compiler in multimedia applications.

Finally, multithreading, multicore or multiprocessor approaches all benefit from DLP and ILP and, furthermore, they exploit *Thread Level Parallelism* (TLP) in which large sections of the code can be executed in parallel.

This dissertation describes a hardware enhancement of a superscalar processor to dynamically expose and exploit the DLP of codes in which the compiler failed to detect this parallelism. This mechanism searches for vector patterns in the code to create speculative vector instructions that will prefetch and precompute data for non-speculative instructions. This preexecution exploits the newly discovered ILP and DLP and thus improves the performance of applications.

#### 1.1.1 Speculative execution

One way of optimizing execution in scenarios with limited parallelism is to include speculative execution mechanisms in the processor. Tasks that are likely to be executed in the future can be speculatively performed in advance to reduce the latency of non-speculative instructions.

This way of executing instructions can produce a net increase in the processor's performance when speculation is correct since all the speculative work can be reused by non-speculative instructions.

Unfortunately, when a misspeculation is detected, a mechanism for rolling back the speculative work must be provided to ensure the code has been executed correctly.

This useless speculative execution is not for free since squashed instructions have allocated resources and consumed energy. Therefore, it is necessary to find a trade-off between speculation, efficiency, performance and resource usage. An excessive amount of speculative instructions can overload the execution stage of the processor delaying non-speculative instructions and reducing performance. However, if speculative work is negligible or non-existent and hardly increases the throughput of the system, it may be pointless to complicate the design of the processor by including speculative mechanisms.

Branch prediction and data prefetch are the most common speculative mechanisms in current processors.

#### 1.1.2 Vector execution

Vector processors [ea95] [Asa98] [Esp97] [LD97] [Rus78] are the best choice for executing scientific applications in which a large amount of DLP is present, this is performing the same computations over different elements in a large storage structure such as vectors or matrices. Vector compilers [ZC90] [AK87] detect this parallelism and pass the semantic information through a *SIMD ISA* to the processor. The main characteristic of SIMD instructions is that a single instruction deals with a set of elements in a given structure, which improves the ratio between the fetching and execution of instructions. Therefore, vector processors rely on the vector compiler to create a code that executes efficiently. Speculative mechanisms, other than branch prediction, are rarely used in vector scenarios.

Furthermore, vector architectures overcome many of the problems present in superscalar processors. Vector ISAs are the best and easiest way to manage large amounts of hardware. Vector memory accesses are capable of hiding the memory latency by efficiently using the available memory bandwidth. Finally, since conditional branches can be replaced by vector mask registers and predicated execution, branch mispredictions are reduced.

Nowadays, scientific applications are used in particular environments. The general purpose processors that are used in personal computers are not usually used to execute this kind of application. At this point, one may legitimately think that it would be pointless to make the effort to detect and exploit DLP. However, this is not so. A few years ago due to the evolution of the technology, a new kind of application appeared on the scene: *Multimedia Applications*. These applications transform streamed data into video, music and/or still images. In these transformation processes, as in scientific applications, the storage structures that are typically used are vectors and matrices.

Processor manufacturers noticed this and decided to include vector-like functional units, called *Multimedia Extensions* in general purpose processors. These extensions are aimed at increasing the performance of multimedia applications by exploiting the inherent DLP. MMX [Int99], SSE and SSE2 [Int02] by Intel Corp. and 3DNow! [AMD99] by AMD are examples of this.

However, when the compiler fails to detect DLP multimedia extensions become useless. From Chapter 3 onwards, a mechanism that dynamically exposes DLP will be presented. This mechanism is able to create speculative vector instructions that are executed in multimedia extensions, which boosts the performance of any application.

#### 1.1.3 Thesis objectives

Are integer applications really non-vectorizable? The fact that a specialized compiler is not able to detect vector patterns does not necessarily mean that these patterns are not present. Usually, a compiler does not have enough knowledge of a given application to detect the underlying DLP.

In this dissertation we claim firstly that all applications, even if they are not vectorizable, present vector patterns. Secondly, we show that these patterns can easily be detectable at runtime using speculative techniques. We prove that mixing the best of the two worlds (speculation and vector execution) results in an explosion of ILP and DLP that improves the usage of the memory bandwidth and therefore the performance of the processor.

To accomplish this we describe a novel mechanism that is able to find vector

#### Introduction

patterns dynamically in codes in which the compiler failed to detect DLP. This mechanism takes advantage of vector functional units to speculatively execute the vector instructions created.

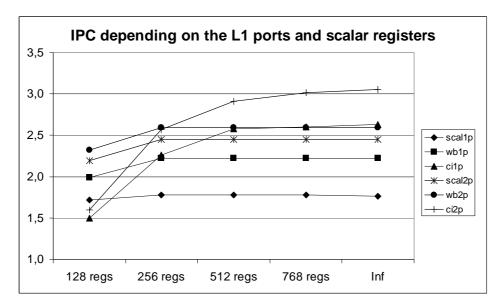

We will then show that vector instructions can be dispensable. A scalar implementation of the presented mechanism, i.e. without vector resources, simplifies the processor without penalizing the performance of the original vector mechanism.

Later on, we show that the mechanism presented can easily be tailored to deal with critical performance degrading sources in current processors. In particular, branch misprediction and the memory gap will be alleviated by rearranging of the basic mechanism.

Finally, in order to show that the mechanism presented can easily be implemented in current processors, we describe successive power and resource aware refinements of the mechanism.

#### **1.2 THESIS OVERVIEW**

This dissertation describes all the work done in this thesis: firstly, designing and improving the *Speculative Dynamic Vectorization* (SDV) mechanism, and secondly, rearranging the mechanism to alleviate the main sources of performance degradation in current superscalar processors.

For the sake of readability, we base the explanation of the following sections on the code in Figure 1.1.

#### **1.2.1** Speculative dynamic vectorization

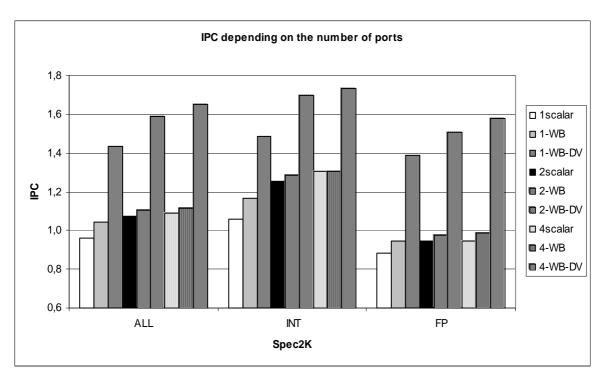

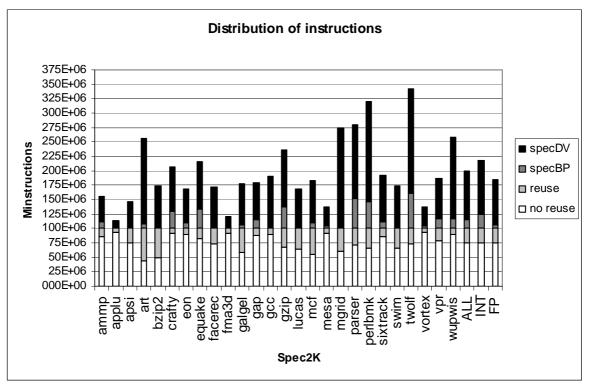

We motivate this thesis providing statistics that show that, on average, in codes compiled for a superscalar processor, independently of the nature of the application, 30% of the scalar instructions can be translated into vector code. The first [PGV02] and second Speculative Dynamic Vectorization mechanisms developed in this thesis are described. These mechanisms will speculatively create vector instructions,

Chapter 1.

| <pre>for (i=0; i<n; i++)<="" pre=""></n;></pre> | IO:  | MOV | R4, 0        |

|-------------------------------------------------|------|-----|--------------|

| {                                               | I1:  | LD  | R1, R0[n]    |

| a+=elem->n;                                     | I2:  | ADD | R2, R2, R1   |

| if (a%2==0)                                     | I3:  | AND | R3, R2, Ox1  |

| {                                               | I4:  | CMP | R3, 0        |

| a++;                                            | I5:  | BNE | 17           |

| }                                               | I6:  | INC | R3           |

| a+=b[i];                                        | 17:  | LD  | R5, b[R4]    |

| <pre>elem=elem-&gt;next;</pre>                  | I8:  | ADD | R3, R3, R5   |

| }                                               | I9:  | LD  | RO, RO[next] |

|                                                 | I10: | INC | R4           |

|                                                 | I11: | CMP | R4, N        |

|                                                 | I12: | BL  | I1           |

|                                                 |      |     |              |

(a) Original code (b) Assembler transformation

Figure 1.1: Example code

| IO:  | MOV   | R4, 0        |

|------|-------|--------------|

| I1:  | LDV   | V1, R0[n]    |

| I2:  | ADDVS | V2, R2, V1   |

| I3:  | ANDV  | V3, V2, 0x1  |

| I4:  | CMPV  | V3, 0        |

| I5:  | BNE   | 17           |

| I6:  | INCV  | V3           |

| 17:  | LDV   | V5, b[R4]    |

| I8:  | ADDV  | V3, V3, V5   |

| I9:  | LD    | RO, RO[next] |

| I10: | INC   | R4           |

| I11: | CMP   | R4, N        |

| I12: | BL    | I1           |

| IO:  | MOV  | R4, 0        |

|------|------|--------------|

| I1:  | LD   | R1, R0[n]    |

| I2:  | ADD  | R2, R2, R1   |

| I3:  | AND  | R3, V2, 0x1  |

| I4:  | CMP  | R3, 0        |

| I5:  | BNE  | 17           |

| I6:  | INC  | R3           |

| 17:  | LDV  | V5, b[R4]    |

| I8:  | ADDV | R3, R3, V5   |

| I9:  | LD   | RO, RO[next] |

| I10: | INC  | R4           |

| I11: | CMP  | R4, N        |

| I12: | BL   | I1           |

|      |      |              |

17 BNE I5: I6: VЗ R5, b[R4] 17: LD R3. V3. R5 I8: ADD RO, RO[next] I9: LD I10: INC R4 I11: CME R4, N I1 I12 BL

MOV

I.DV

ADDVS

ANDV

CMPV

R4, 0

V3. 0

V1. RO[n]

V2, R2, V1

V3, V2, 0x1

IO:

T1:

T2:

13:

I4:

(a) Dynamic Vectorization result code

(c) Memory gap selection code

Figure 1.2: Possible transformations of the DV mechanism

(b) CI-selection code

whenever a vector pattern is detected. For the mechanisms, a vector pattern begins with a strided load.

Furthermore, we evaluate the mechanisms for a wide range of configurations enumerating the sources of benefit: prefetch, preexecution, DLP efficiency through wide resources and virtual enlargement of the instruction window.

In the example code in Figure 1.1 a vector compiler does not create vector code since it does not know a priori, at compile time, the memory position for every elem of the structure. However, this detection can easily be performed at runtime since the memory address of every *elem* is known. The procedure is simple. The Speculative Dynamic Vectorization mechanism studies the effective addresses of every executed load and as soon as a strided pattern is detected, for example the strided load in instruction I1, a speculative vector instruction is created. Dependent instructions (12, 13, 14, 16, 17 and 18) are also vectorized by propagating the characteristic of "vectorization" down the dependence graph. The resulting code is shown in Figure 1.2(a). Further details are available in Chapter 3.

#### 1.2.2 Reducing the penalty of branch mispredictions

We show that the SDV mechanism can easily be re-targeted to alleviate the effects of some performance degrading sources in current processors.

The mechanism is tailored to select *control-flow and data independent* instructions for vectorization [PGV05a]. We introduce the concept of *Selective Speculative Dynamic Vectorization*. In this case, only Control-Flow independent instructions are selected for vectorization.

This selection decreases the number of speculative computations the mechanism performs and thus reduces the resource requirements.

Moreover, we justify why control-flow and data independent instructions are the best choice for applying the SDV mechanism.

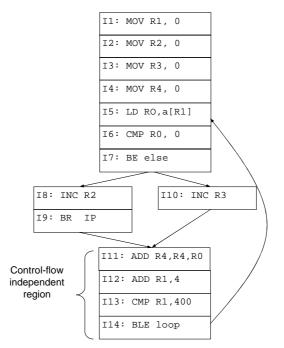

The Control-Flow independent scheme will only vectorize those strided loads whose dependent instructions are control-independent. In the example code in Figure 1.1, Instruction I6 and all its dependent instructions are control-dependent. Therefore, the selection mechanism will prevent these instructions from being vectorized.

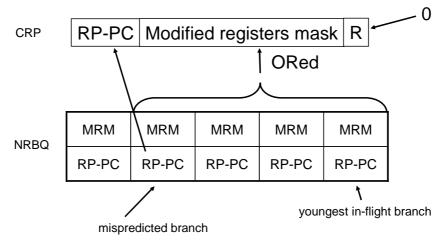

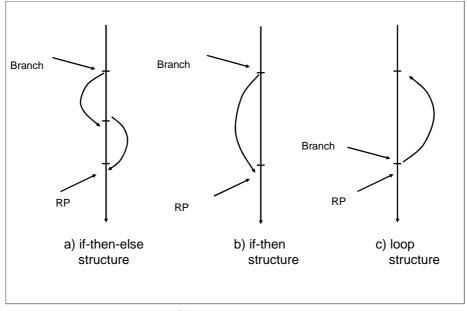

To accomplish this, only instructions after the *Reconvergence Point* (instruction I7) of a hard-to-predict branch (instruction I5) are considered vectorization. Of these instructions, only those that are data-independent (I7 and I8) will be vectorized. To vectorize these instructions, the mechanism will vectorize the strided load that creates the source operands of these instructions. The resulting code is shown in Figure 1.2(b). Further details can be found in Chapter 4.

## 1.2.3 Overcoming the memory gap

The memory gap [WM95] is one of the most critical performance degrading sources in current processors.

We show how to take advantage of the stall cycles of the processor that result from a long latency load. We describe the third implementation of the *Speculative Dynamic Vectorization* mechanism. In this case, a small separated core that implements the mechanism is presented.

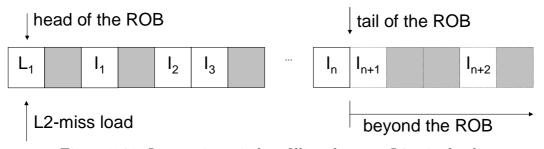

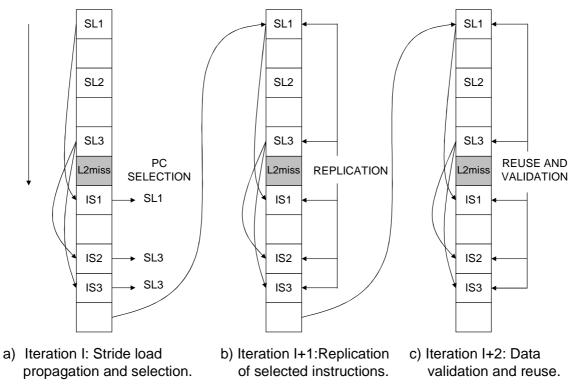

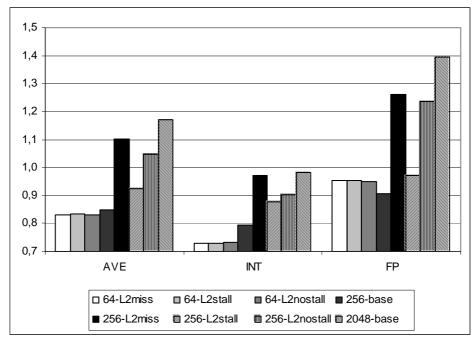

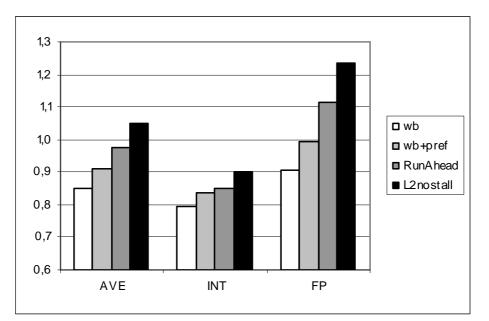

To alleviate the memory penalty we provide two different mechanisms [PGV05c] [PGV04]. The first mechanism is based on the control-flow independence mechanism but selection and vectorization are performed as soon as the delinquent load is detected. The second mechanism waits until an L2 miss load becomes the oldest instruction in the instruction window to fire the vectorization. Both mechanisms only vectorize the independent instructions of the L2 miss load that fired the mechanism.

We show in the evaluation of this part that even if the performance obtained for every mechanism is nearly equal, the second mechanism is the best choice since it is resource-aware.

Supposing that in Figure 1.1 instruction I7 is the L2 miss load, the mechanism will only select those instructions I1, I2, I3, I4, I6 and I8 that are independent of that delinquent load. As in the other mechanisms, only instructions dependent of a strided load can be vectorized. Figure 1.2(c) shows the final transformation of the code in Figure 1.1 when the selection scheme is applied to alleviate the memory gap. Further details can be found in Chapter 5.

#### **1.2.4** Cost-effective dynamic vectorization

Speculation mechanisms are not perfect. Misspeculations can degrade performance if they are not correctly and efficiently rolled back.

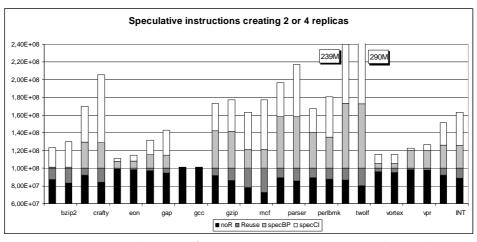

In this chapter the main sources of misspeculations of the Speculative Dynamic Vectorization mechanism are enumerated. Heuristics for reducing these sources are presented and evaluated to enhance the effects of the dynamic vectorization mechanisms[PGV05b].

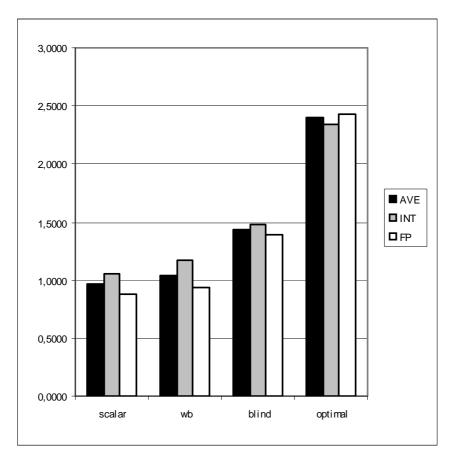

#### 1.2.5 Mechanism comparison

In order to conclude this dissertation, since many implementations are described, we provide a brief comparison to evaluate which is the best mechanism in terms of performance, hardware requirements and energy consumption.

Since the motivation for every proposal is different, a global ranking of the mechanisms will not be provided.

## 1.3 STRUCTURE OF THIS WORK

The structure of this dissertation is as follows:

- Chapter 2 presents our simulation environment. The reference platform for this work is presented, as well as the benchmarks and tools used in this thesis.

- Chapter 3 describes the basic *Speculative Dynamic Vectorization* mechanism. The second part of the chapter justifies and presents an evolved scalar version of the basic mechanism. A completed evaluation of the scalar version is provided in the third part of the chapter.

- Chapter 4 introduces the concept of *Selective Dynamic Vectorization*. This chapter proposes some modifications to the mechanism to alleviate branch penalties by detecting and preexecuting control-flow independent instructions.

- Chapter 5 focuses on the memory gap. To alleviate this problem we provide a set of mechanisms that exploit the processor stall cycles caused by an L2 miss load to virtually enlarge the instruction window.

- Chapter 6 analyzes the sources of misspeculation in the mechanism. Based on this study, a set of heuristics for reducing the register requirement of the basic DV mechanism will be provided. This reduction will be reflected in terms of extra instructions.

- Chapter 7 summarizes this dissertation by comparing all the mechanisms presented in this dissertation in terms of hardware, performance and energy consumption.

- Chapter 8 concludes this dissertation by remarking on the most important points of this thesis and providing a brief future work.

Chapter 1.

Chapter 2

# **Platform and Benchmarks**

## 2.1 INTRODUCTION

This chapter describes the baseline processors in our study. Firstly, we consider that the baseline processor is a superscalar processor with vector capabilities. It is assumed that these extensions are used to execute SIMD instructions belonging to the processor's ISA. It is out of the scope of this dissertation to simulate these instructions. Instead, we assume that these instructions are available but that the compiler has not been able to find vector patterns in the code to insert them.

The second proposal of the *Speculative Dynamic Vectorization* mechanism is based on a superscalar processor without vector capabilities. We will show in subsequent chapters that vector resources are indeed not needed to maintain the performance benefits of the first mechanism.

Later on, we will discuss the reason behind the choice of benchmarks. The main characteristics of each set of benchmarks will be explained to justify the following evaluations. We will see why SpecINT2K and SpecFP2K are radically different and how their characteristics fit into the scope of this thesis.

# 2.2 REFERENCE PLATFORM

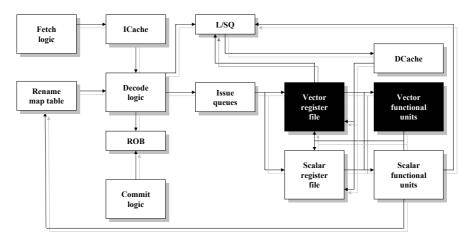

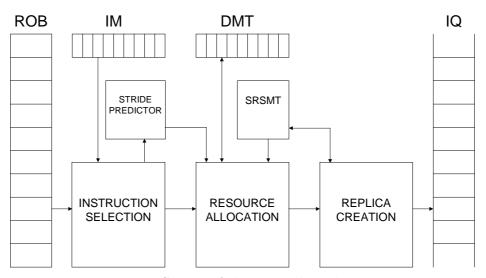

As mentioned in the introduction, this dissertation presents a mechanism that is able to create speculative vector instructions for prefetching and precomputing data for non-speculative instructions. The first design of the mechanism is built on top of an out-of-order superscalar processor with vector capabilities. A scheme of this processor is depicted in Figure 2.3.

#### 2.2.1 Scalar pipeline

The scalar pipeline of the processor is divided into 6 stages: fetch, decode, issue, execution, writeback and commit. All the stages, except execution, take 1 cycle to complete. Execution latency depends on the instruction.

Figure 2.3: Baseline processor with vector capabilities

As we will show in subsequent chapters, the Speculative Dynamic Vectorization mechanism can easily be accommodated in this pipeline. The main structures (stride predictor and SRSMT) of the SDV mechanism are out of the critical path, which allows long latencies when they are being accessed. Furthermore, since they are addressed with the PC of an instruction, and the data provided must be supplied to the decode logic, the access to these structures can be overlapped with the fetch and decode of the instructions. Therefore, the access to the DV structures can be overlapped with the fetch and decode of the instructions.

Nowadays technology allows latencies of 2 cycles when structures of 8Kbytes in a 3Ghz processor are accessed. In the DV mechanism, the largest structure measures 10Kbytes and it is accessed from the fetch to the decode stage, which means that there is a minimum latency of 2 cycles. Superpipelining of these stages allows longer latencies for these structures, which leads us to believe that our design is easily affordable for current and future processors. In fact, figures obtained with Cacti3.0 [SJ01] show that these structures can be accommodated in a 5Ghz processor implemented in 0.13 nanometers (IBM-Sony [ea05] plan to release the The Cell processor with a 4.5Ghz clock frequency). To standardize the baseline, we will suppose that the processor's clock raises 2.4Ghz.

The configuration of the scalar pipeline is summarized in Table 2.1. Parameters

| Parameter               | Value                                                  |

|-------------------------|--------------------------------------------------------|

| Fetch Width             | 8 instructions (up to 1 taken branch)                  |

| I-Cache                 | 64KB, 2-way set associative, 64 byte lines, 1 cycle    |

|                         | hit, 6 cycle miss time                                 |

| Branch Predictor        | Gshare with 64K entries                                |

| Inst. Window Size       | 256 entries                                            |

| Load/store queue        | 64 entries with store-load forwarding                  |

| Issue mechanism         | 8-way out of order issue; loads may execute when       |

|                         | prior store addresses are known                        |

| Scalar functional units | 6 simple $int(1)$ ; 3 int mult/div (2 for mult and 12  |

| (latency in brackets)   | for div); 4 simple $FP(2)$ ; 2 FP mult/div (4 for mult |

|                         | and 14 for div); 1 load/store                          |

| D-cache                 | 64KB, 2-way set associative, 32 byte lines, 2 cycle    |

|                         | hit time, write-back, 10 cycle miss time, up to 16     |

|                         | outstanding misses                                     |

| L2 cache                | 256KB, 4-way set associative, 64 byte lines, 10 cy-    |

|                         | cle hit time, 1000 cycle miss time                     |

| Commit Width            | 8 instructions                                         |

Table 2.1: Configuration parameters

remain unchanged for all evaluations except when explicitly stated otherwise.

# 2.2.2 Vector capabilities

It may seem striking that the baseline processor presents real vector resources and not just multimedia extensions. One of the main drawbacks of current multimedia extensions is the limited range of computable values that they allow (only up to 32 bits can be used per value). The lack of 64-bit support should not be blamed on the processors' designers: the main target for multimedia extensions is mainstream multimedia software, especially 3D games, in which the precision difference between 32-bit and 64-bit FP computations would hardly be noticeable. However, for scientific applications, in which precision is important, more powerful floating point functional units are required. For this reason, we really believe that future processors will enhance their multimedia extensions to provide more developed vector support.

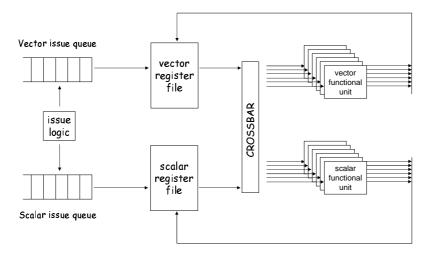

A detailed scheme of the processor's execution engine is provided in Figure 2.4.

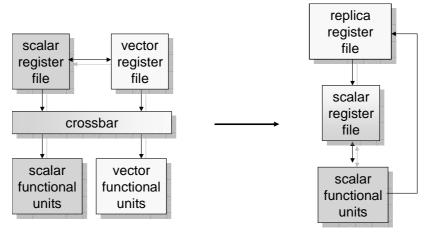

Figure 2.4: Detail of the execution engine

To completely separate the scalar and vector engine, two issue queues are implemented, one for scalar instructions and the other for vector instructions. These queues are not connected and therefore bypasses among instructions of different kinds are disallowed. Scalar instructions only get vector results from the vector register file. Vector instructions that need scalar values, obtain them from the scalar register file.

The baseline processor has a complete vector register file with 64-bit 4 element vector registers connected to the vector and scalar functional units through an issuebound crossbar. Vector functional units are designed as scalar functional units, i.e. only one element per register can be computed at once. Neither vector nor scalar functional units can write results in the other register file.

From this design one can see that the execution engine has become extremely

complex since two kinds of register files and functional units are interconnected in order to extend the processor with vector capabilities. This will be explained in further detail in Chapter 3 and will justify the complete removal of these vector extensions.

## 2.3 BENCHMARKS

Benchmark behavior definition is an important aspect that must be defined to understand how performance is achieved. The base *Dynamic Vectorization* mechanism described in this thesis is not tailored to fulfill the characteristics of a particular kind of application but rather it is designed to work in a wide range of different codes.

The following rearrangements of the technique exploit relevant characteristics that must be taken into account.

Our performance figures are obtained by simulating the whole Spec2K benchmark suite. This set of applications includes a wide range of codes with different behaviors, although they can be grouped into two subsets: irregular and regular codes. A summary of their main characteristics is provided.

#### 2.3.1 Irregular codes

This group includes the most typical applications used in desktops. Since this is a large group it must be taken into account when our mechanism is being tested. It would not be advisable that for *Dynamic Vectorization* to lose performance when it executes these applications since this would decrease the chances of incorporating the mechanism into general purpose processors, such as those that are provided in desktop computers.

Due to their behavior, this group of codes is the main challenge and the most important justification for the mechanisms proposed. The most important characteristics of these codes are as follows:

• Loops: Small with an irregular number of iterations (6,5 iterations on average).

Thanks to compilation optimization techniques such as inlining, loop bodies can be large.

- Branches: Unpredictable behavior for a considerable percentage of branches: about 4% of the total.

- DLP: Memory structures are, in most cases, small and easily allocatable in the available on-chip memory. L2 misses are not frequent.

- Vectorization: Memory instructions do not present vector patterns at compile time. Vectorization is not possible.

- Benchmarks: SpecINT2000 [Spe00].

## 2.3.2 Regular codes

Scientific and multimedia applications are the most representative sets that constitute this group. Scientific applications are employed in very restricted environments but multimedia is present in the day-to-day use of a desktop computer. Audio and video stream, 3D games and photo editors are typical applications in this group. Since these applications are easily vectorizable, one may argue that using *Dynamic Vectorization* in this context is tricky. Note that these applications are basically compiled with a scalar compiler that is not good at detecting vector patterns. However, it is possible that the source code of vectorizable applications will not be available for recompiling it to allow vector support. For these reasons, *Dynamic Vectorization* could help by creating vector code at runtime in order to use those idle multimedia extensions.

The main characteristics of this group of applications are as follows:

• Loops: Large and usually with a constant number of iterations. The loop of the body consists of hundreds of instructions.

- Branches: Most of the branches are easily predictable since they are branches that finish the loop body.

- DLP: Large vector and/or matrices are the most typical structures found. DLP is clearly present since loops traverse these structures element by element.

- Vectorization: Since loops are regular and DLP is exposed in high level languages, vector compilers are very effective in creating optimized vector code.

- Benchmarks: SpecFP2000 [Spe00].

# 2.4 SIMULATION FRAMEWORK

To evaluate our proposal we use SimpleScalar v3.0d [BA97] as a microarchitectural simulator. SimpleScalar simulates an out-of-order superscalar processor with a pipeline of 6 stages: fetch, decode, issue, execution, writeback and commit. Each stage takes 1 cycle, except for execution whose latency depends on the instruction. This simulator has been extended to implement the mechanisms described.

SimpleScalar is able to execute Alpha applications by emulating the ISA, which is a highly representative *instruction set architecture* of a current *RISC* processor. In order to generate code for it, we used gcc 2.8.1 for Digital Unix. All Spec2K benchmarks were compiled with all the optimizations enabled, using the following flags: *-non\_shared -ifo -O3*.

For simulations, we chose the following procedure: for every benchmark we skipped the initialization part and simulated the next 100M of instructions. No Spec was executed until completion.

Chapter 2.

Chapter 3

# Speculative Dynamic

Vectorization

# 3.1 INTRODUCTION

This chapter motivates the basis of the work developed in this thesis. Figures will show that both irregular and regular codes present at runtime enough vector patterns, represented as strided loads, to make dynamic vectorization worth. As said in Chapter 2 all the benchmarks are compiled with a superscalar compiler. This means that we are simulating that the compiler has not been able to find vector patterns to create vector instructions even if the processor provides vector resources.

The two main implementations of the proposal are provided. The first architecture is based on the baseline with vector resources. The second overcomes the hardware drawback of having two different register files. Moreover, vector functional units are also removed from the baseline. This new layout oblige to change how the mechanism works, although the philosophy underneath remains unmodified. In this case, the mechanism will not *vectorize* but *replicate*.

# 3.2 MOTIVATION

Strided memory loads [Gon00] are the instructions that fire the proposed speculative dynamic vectorization mechanism. To identify a strided load, at least three dynamic instances of the static load are needed. The first dynamic instance sets the first memory address that is accessed. The second dynamic instance computes the initial stride, subtracting the memory address of the first dynamic instance from the current address. The third dynamic instance checks if the stride is repeated computing the current stride and comparing it with the first computed stride.

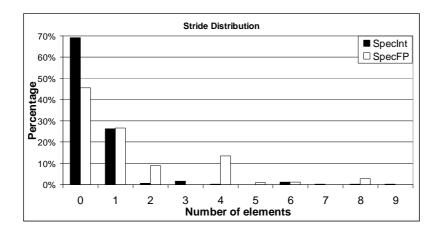

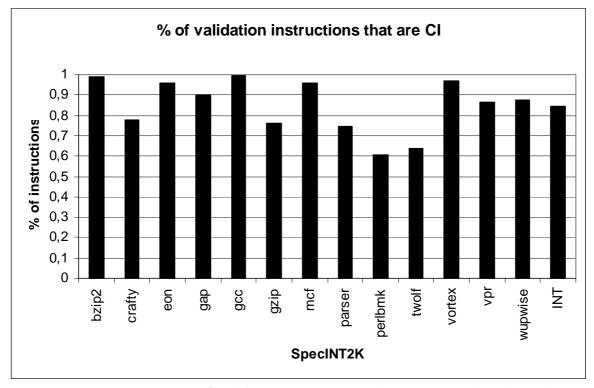

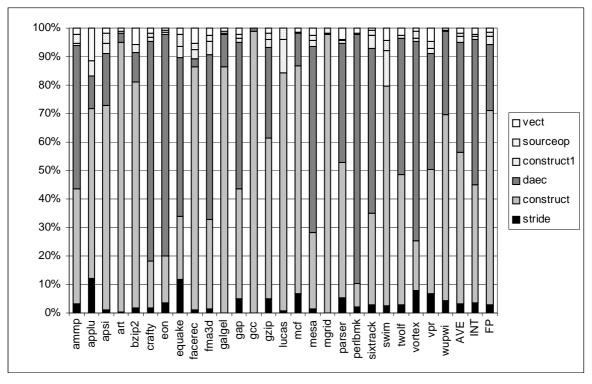

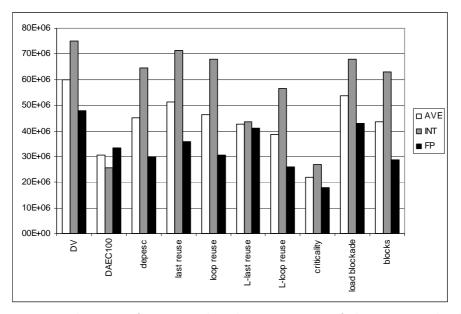

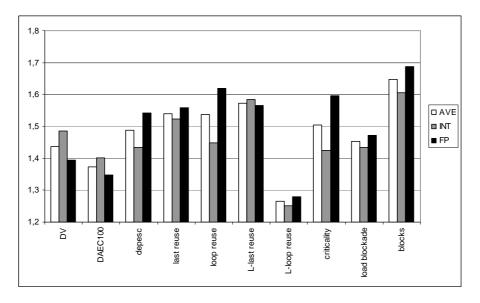

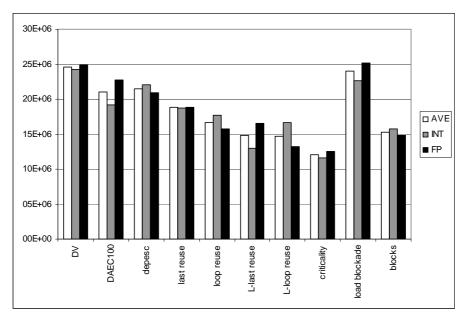

Figure 3.5 shows the stride distribution for SpecINT2K and SpecFP2K (for this figure, the stride is computed dividing the difference of memory addresses by the size of the accessed data).

As shown in Figure 3.5, the most frequent stride for SpecINT2K and SpecFP2K is 0. This means that dynamic instances of the same static load access the same

Figure 3.5: Stride distribution for Spec2K

memory address. For SpecINT this stride is due, mainly, to the accesses of local variables and memory addresses referenced through pointers. For SpecFP the stride 0 is mainly due to spill code.

Usually, for SpecFP, the most frequent stride is stride 1 because these applications execute the same operations over every element of some array structures. However, due to the code optimizations [BGS93] [Ken78] included by the scalar compiler, such as loop unrolling, some stride 1 accesses become stride 2, 4 or 8. The bottom line of this statistics is that strided accesses are quite common both in integer and FP applications.

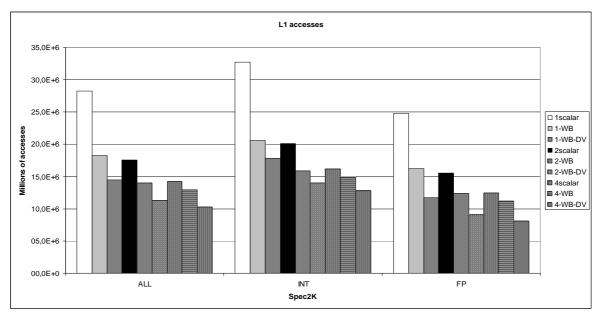

The results in Figure 3.5 also suggest that a wide bus to the L1 data cache can be very effective at reducing the number of memory requests. For instance, if the cache line size is 4 elements, multiple accesses with stride lower than 4 can be served with a single request if the bus width is equal to the line size. These types of strides represent 97,9% and 81,3% of the total strided loads for SpecInt2K and SpecFP2K respectively.

# 3.3 RELATED WORK

Dynamic vectorization is not a very extended topic at literature. In fact, only two proposals can be referred as related work on this subject: dynamic vectorization in trace processors and the CONDEL architecture.

Vajapeyam [VJM99] presents a dynamic vectorization mechanism based on trace processors. The mechanism executes in parallel some iterations of a loop. This mechanism tries to enlarge the instruction window capturing in vector form the body of the loops. The whole loop body is vectorized provided that all iterations of the loop follow the same control flow. The mechanism proposed in this paper is more flexible/general in the sense that it can vectorize just parts of the loop body and may allow different control flows in some parts of the loop.

The CONDEL architecture [Uht92] proposed by Uht captures a single copy of complex loops in a static instruction window. It uses state bits per iteration to determine the control paths taken by different loop iterations and to correctly enforce dependences.

The use of wide buses has been previously considered to improve the efficiency of the memory system for different microarchitectures [RTDA97][WD94b][WO01].

Rotenberg et al. present a mechanism to exploit control flow independence in superscalar [RJS99] and trace [RS99] processors. Their approach is based on identifying control independent points dynamically, and a hardware organization of the instruction window that allows the processor to insert the instructions after a branch misprediction between instructions previously dispatched, i.e., after the mispredicted branch and before the control independent point.

Lopez et al. [LLVA98] propose and evaluate aggressive wide VLIW architectures oriented to numerical applications. The main idea is to take advantage on the existence of stride one in numerical and multimedia loops. The compiler detects load instructions to consecutive addresses and combines them into a single wide load instruction that can be efficiently executed in VLIW architectures with wide buses. The same concept is applied to groups of instructions that make computations. In some cases, these wide architectures achieve similar performance, compared to architectures where the buses and functional units are replicated, but at reduced cost.

# 3.4 OVERVIEW

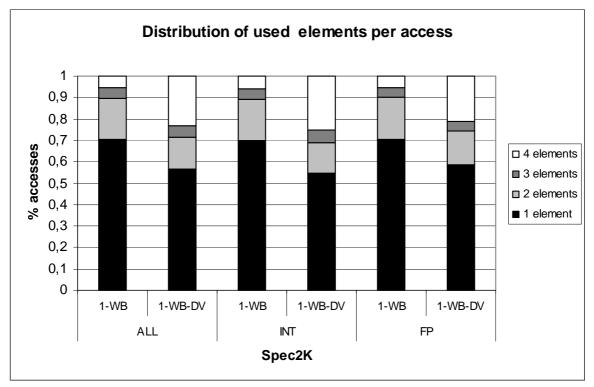

Speculative dynamic vectorization begins when a strided load is detected. When this happens, a vectorized instance of the instruction is created and it is executed in a vector functional unit storing the results in a vector register. Next instances of the same static instruction are not executed but they just validate if the corresponding speculatively loaded element is valid. This basically consists in checking that the predicted address is correct and the loaded element has not been invalidated by a succeeding store. Every new instance of the scalar load instruction validates one element of the corresponding destination vector register.

Arithmetic instructions are vectorized when any of the source operands is a vector register. Succeeding dynamic instances of this instruction just check that the corresponding source operands are still valid vector elements (details on how the state of each element is kept is later explained).

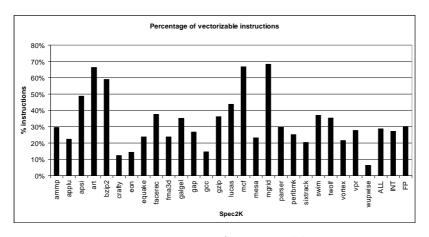

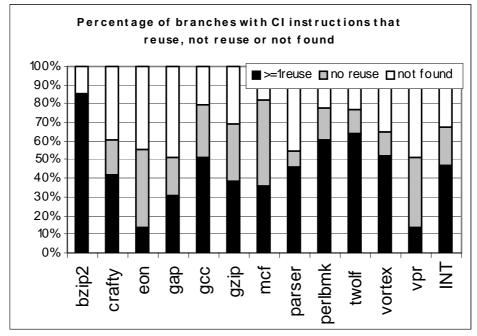

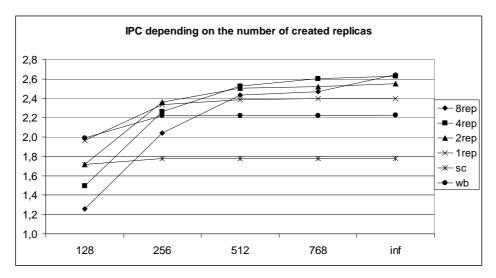

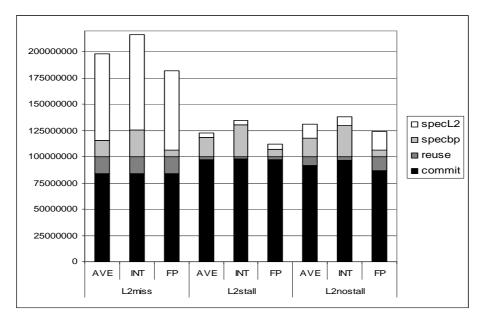

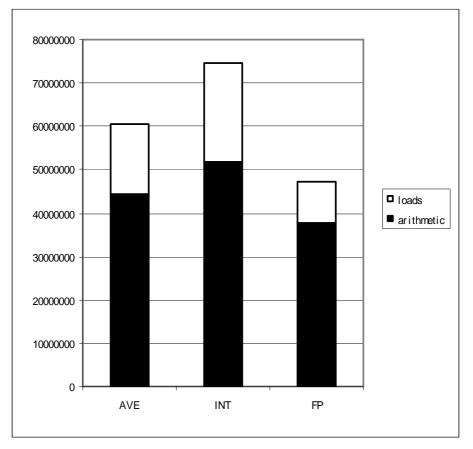

When a validation fails, the current and following instances of the corresponding instruction are executed in scalar mode, until the vectorizing engine detects again a new vectorizable pattern. With this dynamic vectorization mechanism, as shown in Figure 3.6, with unbounded resources, 29% of the SpecINT2K instructions and 30% of the SpecFP2K instructions, on average, can be vectorized. It is important to note that the percentage of vectorizable instructions varies significantly from one benchmark to another.

The following example shows how the mechanism works. Imagine we have a code like that in Figure 3.7.

Figure 3.7(a) shows the typical code a superscalar compiler will create. In this

Figure 3.6: Percentage of vectorizable instructions

| I1: | LD R1, a[R0]   | I1: 1 | LD V1, a[RO]   |

|-----|----------------|-------|----------------|

| I2: | LD R2, b[R1]   | I2: 1 | LD V2, b[V1]   |

| I3: | ADD R3, 3, R1  | I3:   | ADD V3, 3, V1  |

| I4: | ADD R4, R1, R2 | I4:   | ADD V4, V1, V2 |

| I5: | ST c[R0], R3   | I5: S | ST c[R0], V3   |

| I6: | ADD RO, 4      | I6:   | ADD RO, 4      |

| I7: | CMP R0, 1000   | I7: ( | CMP R0, 1000   |

| I8: | JNE I1         | I8: . | JNE I1         |

|     |                |       |                |

(a) Original code (b) Transformed code

Figure 3.7: Dynamic vectorization transformation

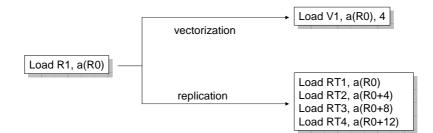

code, the stride predictor will detect instruction  $I_1$  as a strided load, which offset is 4 bytes, but not  $I_2$  since it presents an irregular access pattern. As soon as the DV mechanism detects that  $I_1$  is a strided load, a vector register ( $V_1$  in the example) is allocated. Dependent instructions of this load ( $I_2$ ,  $I_3$  and  $I_4$ ) will be also vectorized since the "vectorization" characteristic is propagated down the dependence graph. A vector register will be also allocated for these instructions.

Stores are not vectorized since it could be difficult to rollback a memory change. But the mechanism must be able to supply the corresponding position inside a vector register to these instructions. For this reason, the renaming logic of the decode stage is modified to deal with both vector and scalar registers.

Branches are neither vectorized to simplify the design of the mechanism.

After applying our mechanism to code in Figure 3.7(a) the new code looks like the one shown in Figure 3.7(b) where vector instructions are created to precompute speculative data for being used later by their scalar counterpart.

# 3.5 FIRST APPROACH: DYNAMIC VECTORIZATION WITH VECTOR RESOURCES

As previously said, the first implementation of the mechanism is built on a superscalar processor with vector capabilities to execute the speculatively created vector instructions.

# **3.5.1** Instruction vectorization

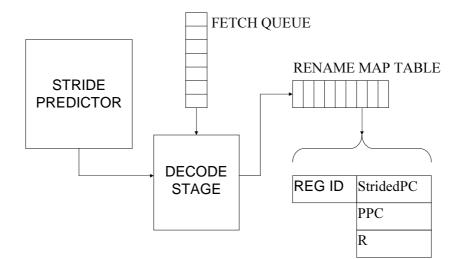

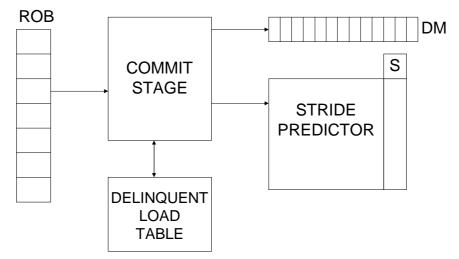

The first step to create vector instances of an instruction is detecting a strided load. To do this, it is necessary to know the recent history of memory accesses for every load instruction. To store this history the processor includes a stride predictor where, for every load, the PC, the current address, the stride and a confidence counter are stored as shown in Figure 3.8.

| PC | Last Address | Stride | Confidence Counter |

|----|--------------|--------|--------------------|

|    |              |        |                    |

Figure 3.8: Entry of the stride predictor

When a load instruction is decoded, it looks for its PC in the stride predictor. If the PC is not in this table, the last address field is initialized with the current address of the load and the stride and confidence counter fields are set to 0.

Next dynamic instances compute the new stride and compare the result with the stride stored in the table, increasing the confidence counter when both strides are equal or resetting it to 0 otherwise. When the confidence counter is 2 or higher, a new vectorized instance of the instruction is generated. The last address field is always modified with the current memory address of the dynamic instance.

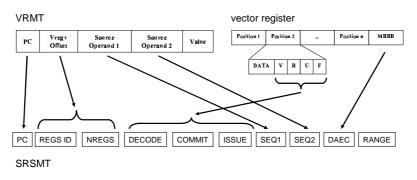

When a vectorized instance of an instruction is generated, the processor allocates a vector register to store its result. The processor maintains the associations of vector registers and vector instructions in the *Vector Register Map Table*. This table contains, for every vector register the PC of the associated instruction, the vector element (*offset*) corresponding to the last fetched scalar instruction that will validate (or has validated) an element of this vector, the source operands of the associated instruction, and, if the instruction is vectorized with one scalar operand and one vector operand, the value of the scalar register is also stored, as shown in Figure 3.9.

| PC | Offset | Source<br>Operand 1 | Source<br>Operand 2 | Value |

|----|--------|---------------------|---------------------|-------|

|----|--------|---------------------|---------------------|-------|

Figure 3.9: Entry of the Vector Register Map Table

Every time a scalar instruction is fetched, this table is checked and if its PC is found the instruction is turned into a validation operation. In this case, the *offset* field determines which vector element must be validated and then, the *offset* is incremented. In the case that the *offset* is equal to the vector register length, another vectorized version of the instruction is generated and a free vector register is allocated to it. The VRMT table entry corresponding to this new vector register is initialized with the content of the entry corresponding to the previous instance, excepting the field *offset*, which is set to 0.

The register rename table is also modified (see Figure 3.10) to reflect the two kind of physical registers (scalar and vector). Every logical register is mapped to either a physical scalar register or a physical vector register, depending on whether the last instruction that used this register as destination was vectorized or not. Every entry of the table contains a V/S flag to mark if the physical register is a scalar or a vector register and the field offset indicates the latest element for which a validation has entered in the pipeline.

|   | PC | Offset | Source<br>Operand 1 | Source<br>Operand 2 | Value |

|---|----|--------|---------------------|---------------------|-------|

| I |    |        |                     |                     |       |

Figure 3.10: Entry of the modified rename map table

When every instruction is decoded the V/S flags (vector/scalar) of their source operands are read and if any of the two is set to V, the instruction is vectorized. In parallel, the VRMT table is accessed to check if the instruction was already vectorized in a previous dynamic instance. If so, the instruction is turned into a validation operation. Validation is performed by checking if the source operands in the VRMT table and those in the rename table are the same. If they differ, a new vectorized version of the instruction is generated. Otherwise, the current element pointed by *offset* is validated and this validation is dispatched to the reorder buffer in order to be later committed (see next section for further explanation). Besides, if the validated element is the last one of the vector, a new instance of the vectorized instruction is dispatched to the vector data-path.

Arithmetic instructions that have been vectorized with one vector source operand and one scalar register operand, wait in the decode stage, blocking the next instructions, until the value of the physical register associated to the scalar source operand is available. Then, it checks if the value of the register matches the value found in the VRMT and if so, a validation is dispatched to the reorder buffer. Otherwise, a new vectorized instance of the instruction is created. This stalls do not impact much performance since the number of vectorized instructions with one scalar operand that is not ready at decode is low.

Note that the cost of a context switch is not increased since only the scalar state of the processor needs to be saved. The additional structures for vectorization are just invalidated on a context switch. When the process restarts again the vectorization of the code starts from scratch at the point where the process was interrupted.

### 3.5.2 Vector registers

Vector register is one of the most critical resources in the processor because they determine the number of scalar instructions that can be vectorized. Vector registers can be regarded as a set of scalar registers grouped with the same name.

A vector register is assigned to an instruction in the decode stage when this instruction is vectorized. If no free vector register is available, the instruction is not vectorized, and continues executing in a scalar mode.

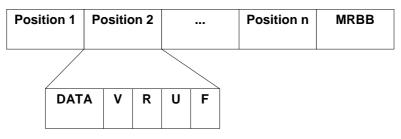

To manage the allocation/deallocation of vector registers, each register contains a global tag and each element includes a set of flags of bits as shown in Figure 3.11.

Figure 3.11: Modified vector register

The V (Valid) flag indicates whether the element holds committed data. This bit is set to 1 when the validation associated to the corresponding scalar instruction commits.

The R (Ready) flag indicates whether the element has been computed. Depending on the kind of instruction the data will be ready when is brought from memory or computed by a vector functional unit.

When a validation of an element has been dispatched but not committed yet, the U (Used) flag is set to 1. This prevents the freeing of the physical register until the validation is committed (details on the conditions to free a vector register are described below).

The F (Free) flag indicates whether the element is not longer needed. This flag is set to 1 when the next scalar instruction having the same logical destination register or its corresponding validation commits. A vector register will be release when all its computed elements have been freed (i.e. are not needed any more). Besides, a register is also released if all validated elements are freed and no more elements need to be produced. In order to estimate when no more elements will be computed, we assume that this will happen when the current loop is terminated. For this purpose, the processor includes a register that is referred to as GMRBB (Global Most Recent Backward Branch) that holds the PC of the last backward branch that has been committed [TG98]. Each vector register stores in the MRBB (Most Recent Backward Branch) tag the PC of the most recently committed backward branch when the vector register was allocated. This backward branch, usually, coincides with the last branch of a loop, associating a vector register to an instruction during some iterations.

A vector register is freed when one of the following two conditions holds:

- 1. All vector elements have the flags R and F set to 1. This means that all elements have been computed and freed by scalar instructions.

- 2. Every element with the flags V set, has the flag F set, and all the elements have the flag R set and flag U cleared, and the content of the tag MRBB is different of the register GMRBB. This means that all the validated elements have been freed. Furthermore, all elements have been computed and no element is in use by a validation instruction. It is very likely that the loop where the vector operation that allocated the register was, has been terminated.

# 3.5.3 Vector data path

Vector instructions wait in the vector instruction queues until their operands are ready and a vector functional unit is available (i.e. instruction are issued out-oforder). Vector functional units are pipelined and hence can begin the computation of a new vector element every cycle. Every time an element is calculated, the vector functional unit sets to 1 the flag R associated to that position, allowing others functional units to use it. Vector functional units can compute operations having one vector operand and one scalar operand. To do this, the functional units must have access to the scalar register file and the vector register file. In the case of the scalar register, the element is read just once.

Note that some vector instruction can be executed having a different initial offset for their source vector operands. This can happen, for example, when two load instructions begin vectorization in different iterations and their destination vector registers are source operands of an arithmetic instruction. To deal with these cases, vector functional units compare these offsets to obtain the greatest. The difference between this offset and the vector register length determines the number of elements to compute. Fortunately, the percentage of the vector instructions whose source operands' offsets are different from 0 is very low, about 4,5%.

# 3.5.4 Branch mispredictions and control-flow independence

When a branch misprediction is detected, a superscalar processor recovers the state of the machine by restoring the register map table and squashing the instructions after the branch.

In the proposed microarchitecture, the scalar core works in the same way as a conventional processor, i.e. a precise state is recovered, but vector resources are not modified: vector registers are not freed, and no vector functional unit aborts the execution because they can be computing data that can be used in the future. The objective is to exploit control-flow independence. When the new path enters again in the scalar pipeline, the source operands of each instruction will be checked again, and if it happens that the vector operands are still valid, the instruction does not need to be executed. Our studies show that the percentage of instructions in the 100 instructions (100 is a size arbitrarily chosen) that follow a mispredicted branch that do not need to be executed since they were executed in vector mode and continue to

have the same source operands after the misprediction, are 20% for SpecInt2K and 6% for SpecFP2K. SpecFP percentage is lower since branches are easily predictable so, control-flow independence is hardly present.

Note that when a scalar instruction in a wrongly predicted speculative path is vectorized, the vector register may remain allocated until the end of the loop to which the instruction belongs. This wastes vector registers but fortunately only happens for less than 1% of the vector instructions in our benchmarks.

## 3.5.5 Memory disambiguation

To ensure memory disambiguation, stores are critical instructions because these instructions make changes in memory that the processor cannot recover. For this reason, a store instruction modifies the memory hierarchy only when it commits.

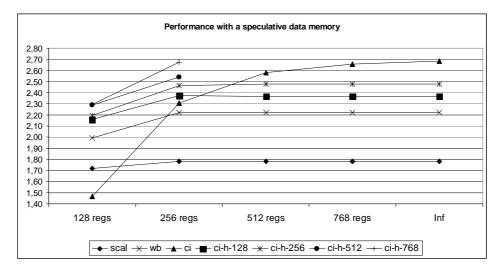

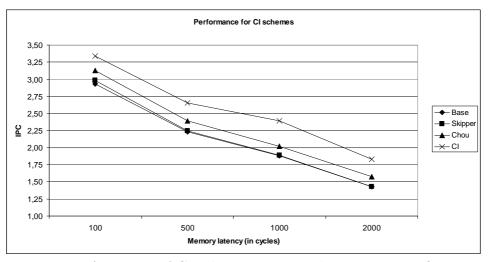

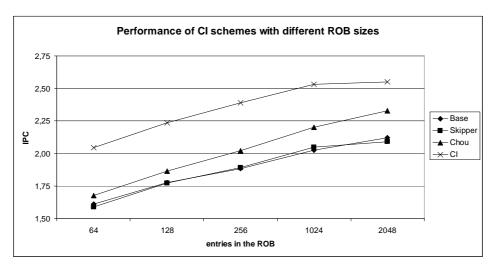

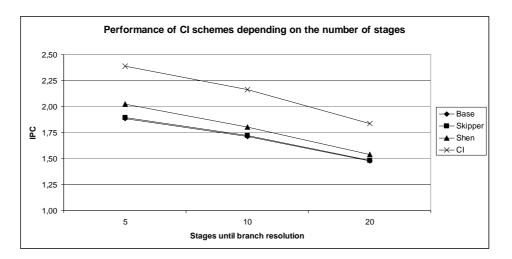

A vectorized load copies memory values into a register. However, there may be intervening stores before the scalar load operation that would have made the access in a non-vectorized implementation. Thus, stores must check the data in vector registers to maintain coherence.