# SMART MEMORY MANAGEMENT THROUGH LOCALITY ANALYSIS

#### Jesús Sánchez

DEPT. OF COMPUTER ARCHITECTURE UNIVERSITAT POLITÈCNICA DE CATALUNYA Barcelona (SPAIN)

A THESIS SUBMITTED IN FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

Doctor en Informática

## **ABSTRACT**

Cache memories were incorporated in microprocessors in the early times and represent the most common solution to deal with the gap between processor and memory speeds. However, many studies point out that the cache storage capacity is wasted many times, which means a direct impact in processor performance. Although a cache is designed to exploit different types of locality, all memory references are handled in the same way, ignoring particular locality behaviors. The restricted use of the locality information for each memory access can limit the effectivity of the cache. In this thesis we show how a data locality analysis can help the researcher to understand where and why cache misses occur, and then to propose different techniques that make use of this information in order to improve the performance of cache memory. We propose techniques in which locality information obtained by the locality analyzer is passed from the compiler to the hardware through the ISA to guide the management of memory accesses.

We have developed a static data locality analysis. This analysis is based on reuse vectors and performs the three typical steps: reuse, volume and interfere analysis. Compared with previous works, both volume and interference analysis have been improved by using profile information as well as a more precise interference analysis. The proposed data locality analyzer has been inserted as another pass in a research compiler. Results show that for numerical applications the analysis is very accurate and the computing overhead is low. This analysis is the base for all other parts of the thesis. In addition, for some proposals in the last part of the thesis we have used a data locality analysis based on cache miss equations. This analysis, although more time consuming, is more accurate and more appropriate for set-associative caches. The usage of two different locality analyzers also shows that the architectural proposals of this thesis are independent from the particular locality analysis.

After showing the accuracy of the analysis, we have used it to study the locality behavior exhibited by the SPECfp95 programs. This kind of analysis is necessary before proposing any new technique since can help the researcher to understand why cache misses occur. We show that with the proposed analysis we can study very accurately the locality of a program and detect where the hot spots are as well as the reason for these misses. This study of the locality behavior of different programs is the base and motivation for the different techniques proposed in this thesis to improve the memory performance.

Thus, using the data locality analysis and based on the results obtained after analyzing the locality behavior of a set of programs, we propose to use this analysis in order to guide three different techniques: (i) management of multi-module caches, (ii) software prefetching for modulo scheduled loops, and (iii) instruction scheduling for clustered VLIW architectures.

The first use of the proposed data locality analysis is to manage a novel cache organization. This cache supports bypassing and/or is composed of different modules, each one oriented to exploit a particular type of locality. The main difference of this cache with respect to previous proposals is that the decision of caching or not, or in which module a new fetched block is allocated is managed by some bits in memory instructions (locality hints). These hints are set at compile time using the proposed locality analysis. Thus, the management complexity of this cache is kept low since no additional hardware is required. Results show that smaller caches with a smart management can perform as well as (or better than) bigger conventional caches.

We have also used the locality analysis to study the interaction between software pipelining and software prefetching. Software pipelining has been shown to be a very effective scheduling technique for loops (mainly in numerical applications for VLIW processors). The most popular scheme for software pipelining is called modulo scheduling. Many works on modulo scheduling can be found in the literature, but almost all of them make a critical assumption: they consider an optimistic behavior of the cache (in other words, they use the hit latency when a memory instruction is scheduled). Thus, the results they present ignore the effect of stalls due to dependences with memory instructions. In this part of the thesis we show that this assumption can lead to schedules whose performance is rather low when a real memory is considered. Thus, we propose an algorithm to schedule memory instructions in modulo scheduled loops. We have studied different software prefetching strategies and finally proposed an algorithm that performs prefetching based on the locality analysis and the shape of the loop dependence graph. Results obtained shows that the proposed scheme outperforms other heuristic approaches since it achieves a better trade-off between compute and stall time than the others

Finally, the last use of the locality analysis studied in this thesis is to guide an instruction scheduler for a clustered VLIW architecture. Clustered architectures are becoming a common trend in the design of embedded/DSP processors. Typically, the core of these processors is based on a VLIW design which partitionates both register file and functional units. In this work we go a step beyond and also make a partition of the cache memory. Then, both inter-register and inter-memory communications have to be taken into account. We propose an algorithm that performs both graph partition and instruction scheduling in a single step instead of doing it sequentially, which is shown to be more effective. This algorithm is improved by adding an analysis based on the cache miss equations in order to guide the scheduling of memory instructions in clusters with the aim of reducing not only inter-register communications, but also cache misses.

## **AGRADECIMIENTOS**

Me gustaría agradecer la confianza depositada en mí por Antonio González, mi director de tesis, el cual me ha guiado durante todo este camino. Gracias por su paciencia y por todas las cosas que me ha enseñado.

Gracias a toda mi familia: a mis padres, Paco y Juani, a mi abuela, Carmen, y a mi hermano, Carlos, y a todo el resto de familia que han creido en mi y me han apoyado durante todo este tiempo, y muy especialmente a Lorena, que ha aparecido en mi vida en el último año de tesis y que me ha iluminado desde entonces con su sonrisa. Te quiero, osita! ;-)

Agradecer el apoyo y ayuda de toda la gente del departamento que en algún u otro momento me han echado una mano. Prefiero no poner una lista de nombres porque estaríais todos, pero muy especialmente a mis amigos Profesor Titular Pepe González, con quien comencé toda esta aventura, y Manolo Fernández, por todos esos buenos ratos dentro y fuera de la Universidad.

Por último, no quisiera olvidarme de todos mis amigos fuera de la Universidad con los que he pasado tan buenos momentos y con los que siempre he conseguido olvidarme un poco de procesadores, compiladores y rollos de esos.

# **CONTENTS**

| 1. Introduction  |                                        | 1  |

|------------------|----------------------------------------|----|

| 1.1. Мот         | IVATION                                | 2  |

| 1.2. BACE        | KGROUND                                | 4  |

|                  | 1.2.1. HARDWARE-BASED TECHNIQUES       | 5  |

|                  | 1.2.2. SOFTWARE-BASED TECHNIQUES       | 8  |

| 1.3. Con         | TRIBUTIONS OF THIS THESIS              | 10 |

| 1.3. Orga        | ANIZATION OF THIS THESIS               | 11 |

| 2. DATA LOCALITY | ANALYSIS                               | 13 |

| 2.1. Intro       | ODUCTION                               | 14 |

|                  | 2.1.1. DYNAMIC ANALYSIS                | 15 |

|                  | 2.1.2. STATIC ANALYSIS                 | 16 |

| 2.2. BACI        | KGROUN DEFINITIONS                     | 17 |

| 2.3. STAT        | IC AND PROFILED DATA LOCALITY ANALYSIS | 18 |

|                  | 2.3.1. COMPILER AND PROFILER PHASES    | 18 |

|                  | 2.3.2. LOCALITY ANALYZER               | 19 |

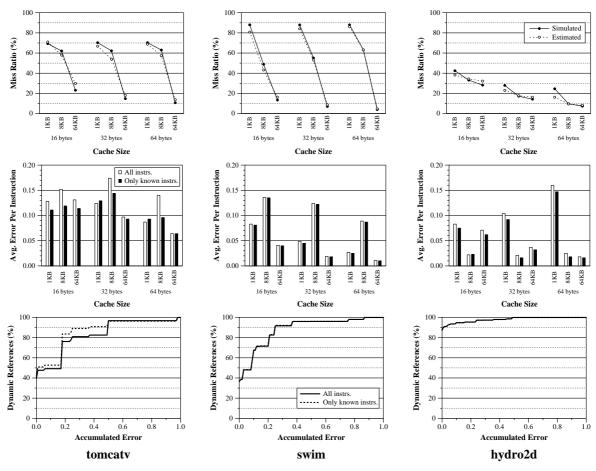

|                  | 2.3.3. VALIDATION                      | 24 |

| 2.4. FAST        | CACHE MISS EQUATIONS                   | 27 |

|                  | 2.4.1. ANALYTICAL MODEL                | 27 |

|                  | 2.4.2. IMPLEMENTATION                  | 28 |

| 2.5. Chai        | PTER SUMMARY                           | 29 |

| 3. Lo        | OCALITY ANALYSIS OF SPECFP95                       | 31 |

|--------------|----------------------------------------------------|----|

|              | 3.1. Introduction                                  | 32 |

|              | 3.2. DATA LOCALITY IN THE SPECFP95                 | 32 |

|              | 3.2.1. Intrinsic Reuse                             | 33 |

|              | 3.2.2. QUANTIFYING TYPES OF MISSES                 | 36 |

|              | 3.2.3. CONFLICTING DATA STRUCTURES                 | 41 |

|              | 3.2.4. Critical Code Sections                      | 43 |

|              | 3.3. Chapter Summary                               | 43 |

| <b>4.</b> Lo | OCALITY SENSITIVE CACHES                           | 45 |

|              | 4.1. Introduction                                  | 46 |

|              | 4.2. Related Work                                  | 48 |

|              | 4.3. SELECTIVE AND DUAL DATA CACHES                | 51 |

|              | 4.3.1. CACHE ARCHITECTURES                         | 51 |

|              | 4.3.2. Locality Analysis                           | 52 |

|              | 4.3.3. EVALUATION                                  | 55 |

|              | 4.4. MULTIMODULE CACHE                             | 58 |

|              | 4.4.1. CACHE ARCHITECTURE                          | 59 |

|              | 4.4.2. Locality Analysis                           | 61 |

|              | 4.4.3. EVALUATION                                  | 64 |

|              | 4.5. Chapter Summary                               | 72 |

| <b>5.</b> So | OFTWARE PREFETCHING FOR MODULO SCHEDULED LOOPS     | 75 |

|              | 5.1. Introduction                                  | 76 |

|              | 5.2. BACKGROUND ON MODULO SCHEDULING               | 77 |

|              | 5.3. Adding Software Pfetching                     | 80 |

|              | 5.3.1. MOTIVATING EXAMPLE                          | 80 |

|              | 5.3.2. Basic Schemes to Schedule Memory Operations | 81 |

|              | 5.3.3. CACHE SENSITIVE MODULO SCHEDULING           | 83 |

|              | 5.4. EVALUATION                                    | 85 |

|              | 5.4.1. Architecture Model                          | 86 |

|              | 5.4.2. Experimental Framework                      | 86 |

|              | 5.4.3. Early Scheduling                            | 87 |

|              | 5.4.4. Inserting Prefetch Instructions             | 90 |

|              | 5.5. Chapter Summary                               | 94 |

| 6. Instruction | N SCHEDULING FOR CLUSTERED VLIW ARCHITECTURES  | 95  |

|----------------|------------------------------------------------|-----|

| 6.1. I         | NTRODUCTION                                    | 96  |

| 6.2. P         | Previous Work                                  | 97  |

| 6.3. S         | CHEDULING FOR A SEMI-DISTRIBUTED ARCHITECTURE  | 99  |

|                | 6.3.1. Architecture                            | 99  |

|                | 6.3.2. BASIC SCHEDULING ALGORITHM              | 101 |

|                | 6.3.3. ADDING LOOP UNROLLING                   | 105 |

|                | 6.3.4. EVALUATION                              | 106 |

| 6.4. S         | CHEDULING FOR A FULLY-DISTRIBUTED ARCHITECTURE | 113 |

|                | 6.4.1. Architecture                            | 113 |

|                | 6.4.2. MOTIVATION                              | 115 |

|                | 6.4.3. SCHEDULING ALGORITHM                    | 118 |

|                | 6.4.4. EVALUATION                              | 120 |

| 6.5. C         | CHAPTER SUMMARY                                | 124 |

| 7. CONCLUSION  | NS AND FUTURE WORK                             | 127 |

| 7.1. C         | Conclusions                                    | 128 |

| 7.2. F         | UTURE WORK                                     | 130 |

| REFERENCES     |                                                | 133 |

# **LIST OF FIGURES**

| CHAPTER 1                                                                                 |              |

|-------------------------------------------------------------------------------------------|--------------|

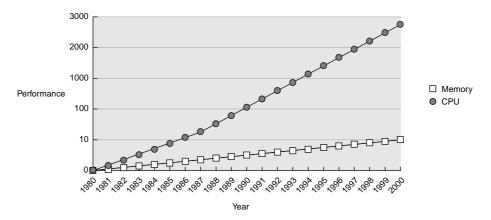

| 1.1. Evolution in the performance of memory and CPU speeds during last 20 years           | 2            |

| CHAPTER 2                                                                                 |              |

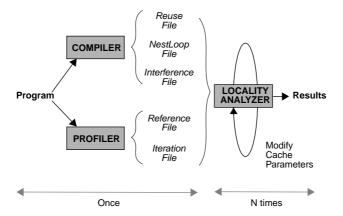

| 2.1. Global scheme                                                                        | 19           |

| 2.2. Algorithm to quantify intrinsic reuse                                                | 20           |

| CHAPTER 3                                                                                 |              |

| 3.4. Intrinsic reuse                                                                      | 34           |

| 3.5. Percentage of instructions with just one type of reuse: no reuse (NR), temporal (TR) | or spatial   |

| (SR).                                                                                     | 36           |

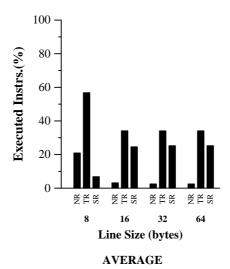

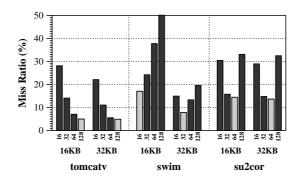

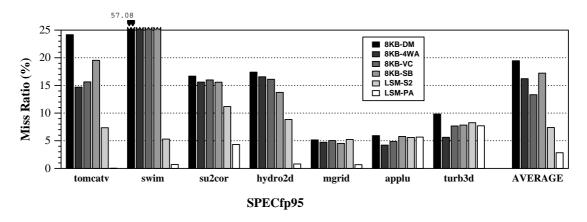

| 3.6. Different kinds of cache misses                                                      | 37           |

| 3.7. Exploiting temporal reuse only                                                       | 39           |

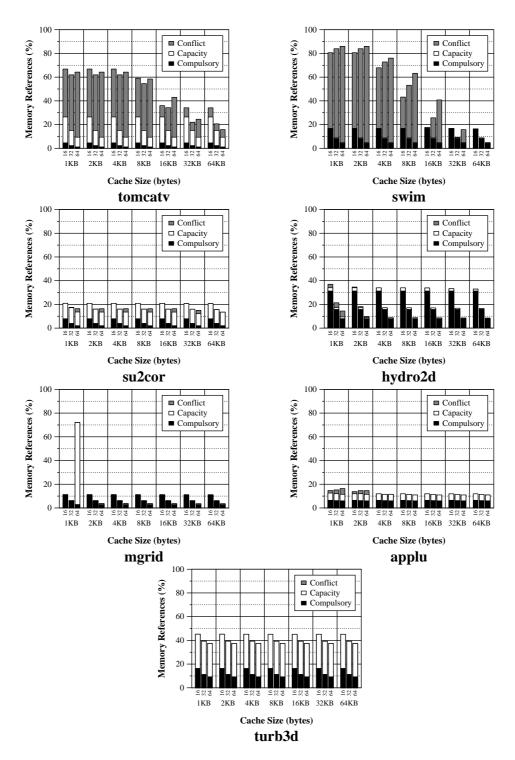

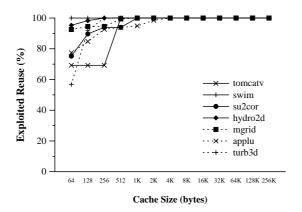

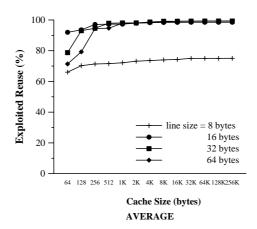

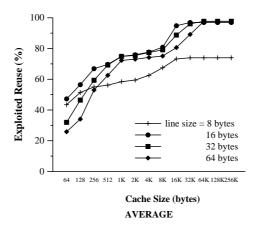

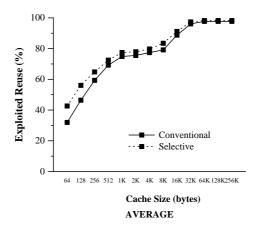

| 3.8. Percentage of reuse exploited with a varying cache size without interferences        | 40           |

| 3.9. Percentage of reuse exploited with a varying cache size considering interferences    | 41           |

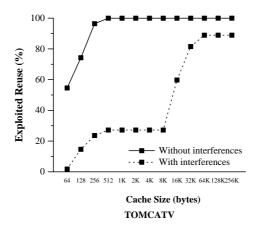

| 3.10. Percentage of reuse exploited with a varying cache size with/without interferences  | for tomcatv. |

| 41                                                                                        |              |

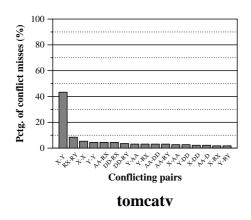

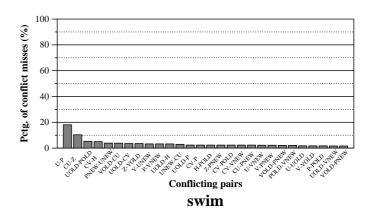

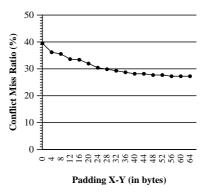

| 3.11. Percentage of conflict misses between data structures                               | 42           |

| 3.12. Reduction in conflict miss ratio after padding                                      | 42           |

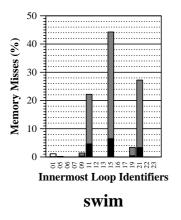

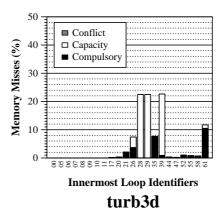

| 3.13. Cache misses per innermost loop                                                     | 43           |

| CHAPTER 4                                                                                 |              |

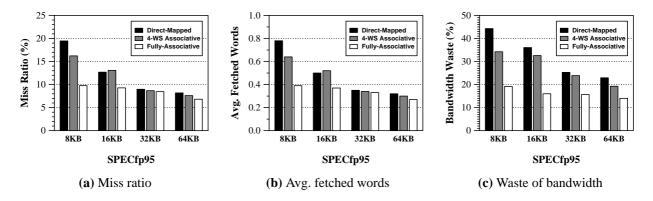

| 4.1. Performance of conventional cache architectures averaged for all SPECfp95            | 47           |

| 4.2. Impact of cache line size on total miss ratio for some SPECfn95 benchmarks           | 18           |

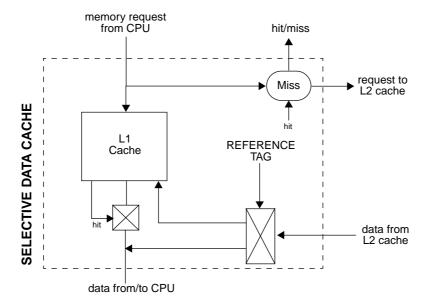

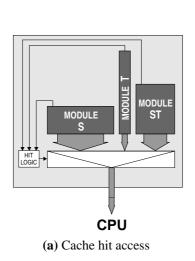

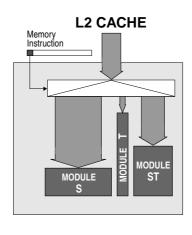

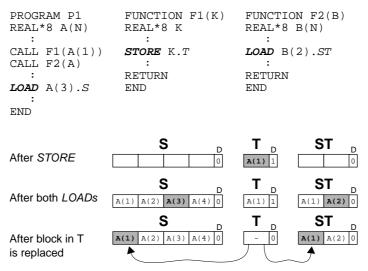

| 4.3. Block diagram of the selective data cache                                                | 51        |

|-----------------------------------------------------------------------------------------------|-----------|

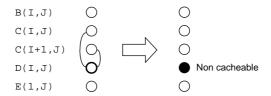

| 4.4. Sample code.                                                                             | 52        |

| 4.5. Interference analysis for code of Figure 4.4                                             | 54        |

| 4.6. Comparison among conventional, selective and dual data caches                            | 57        |

| 4.7. Percentage of reuse exploited with a selective cache, varying the cache size and compare | ed with a |

| conventional cache.                                                                           | 58        |

| 4.8. Hardware architecture of the LSMCache                                                    | 59        |

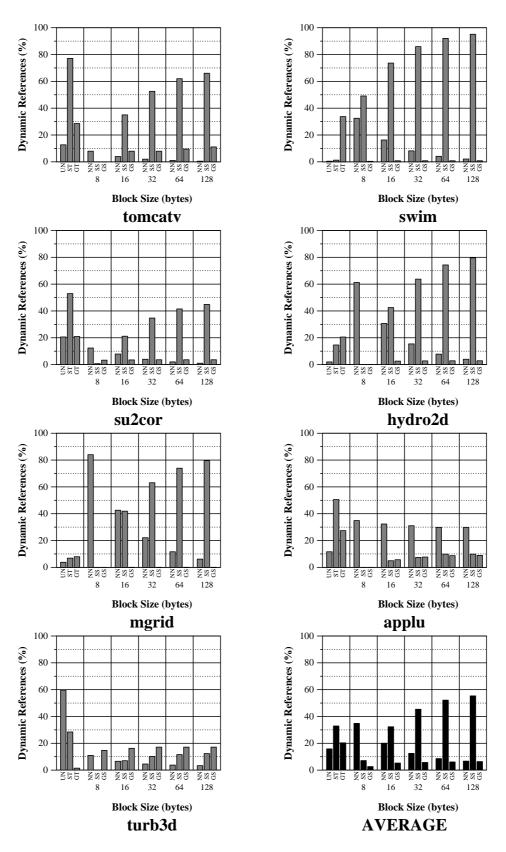

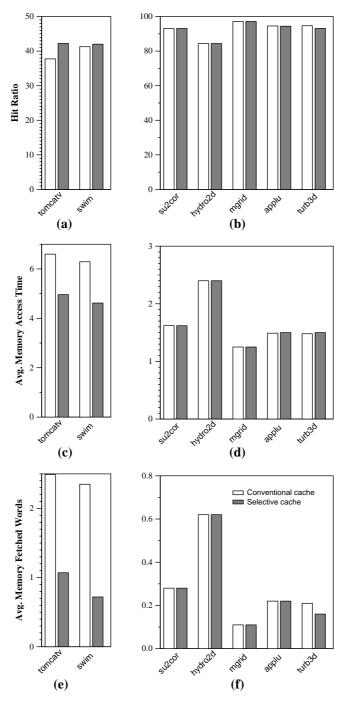

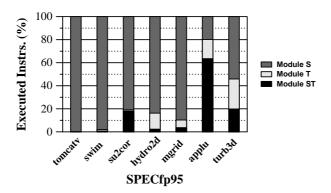

| 4.9. Percentage of dynamic memory instructions allocated to each module                       | 66        |

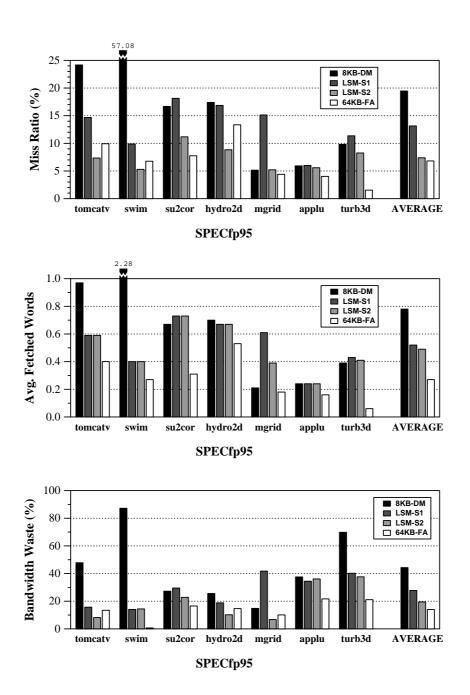

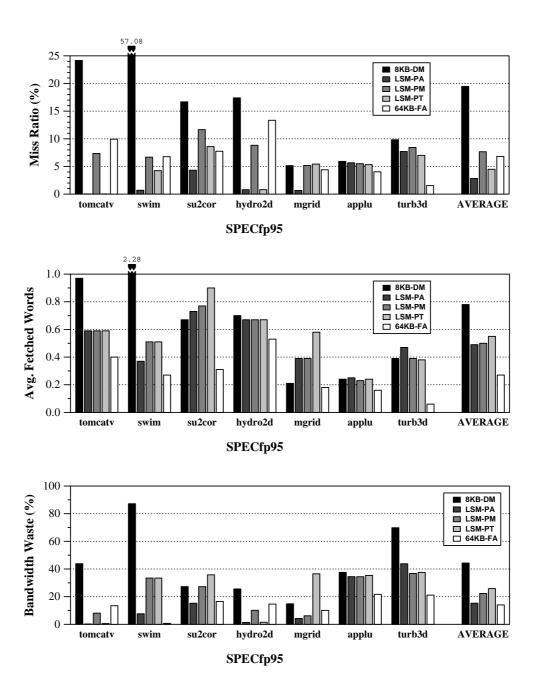

| 4.10. Comparison of LSMCache without prefetching against two conventional caches              | 67        |

| 4.11. Comparison of LSMCache schemes with prefetching against two conventional caches         | 69        |

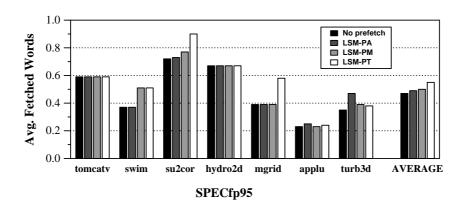

| 4.12. Impact of prefetching on fetched words                                                  | 70        |

| 4.13. Comparison of the LSMCache with other multi-module caches                               | 72        |

| CHAPTER 5                                                                                     |           |

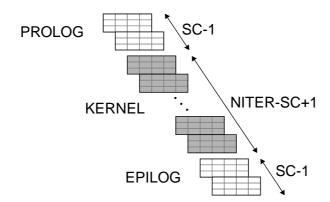

| 5.1. Execution stages of a modulo scheduled loop                                              | 79        |

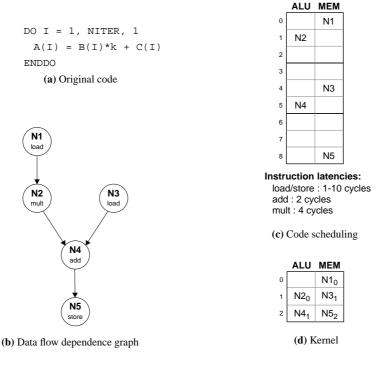

| 5.2. A sample scheduling                                                                      | 80        |

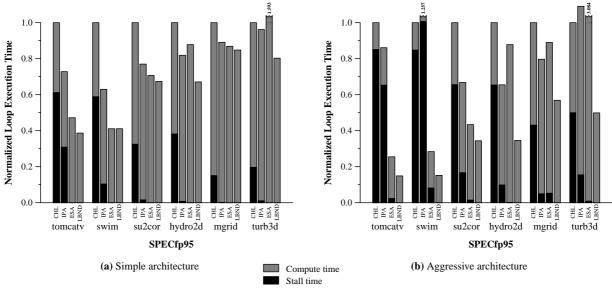

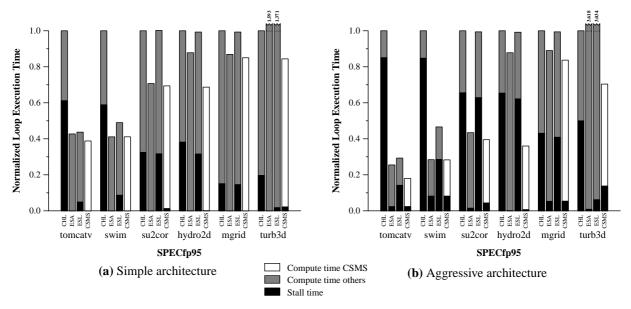

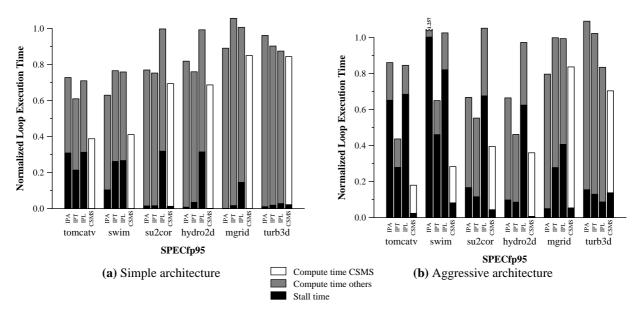

| 5.3. Basic schemes performance                                                                | 82        |

| 5.4. CSMS algorithm                                                                           | 84        |

| 5.5. CSMS algorithm compared with early scheduling                                            | 87        |

| 5.6. CSMS algorithm compared with inserting prefetch instructions                             | 91        |

| CHAPTER 6                                                                                     |           |

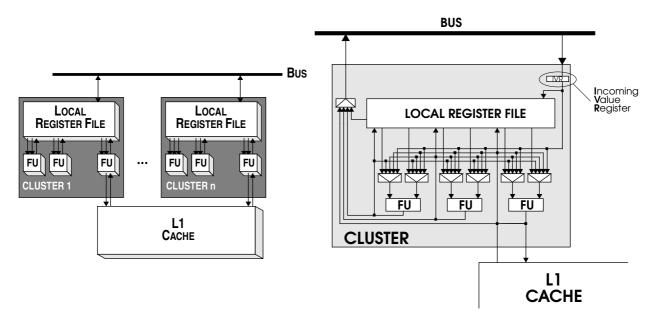

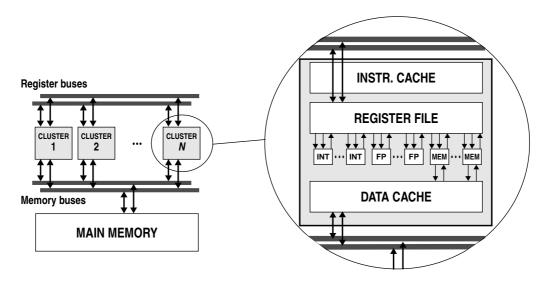

| 6.1. VLIW clustered architecture and detailed architecture of a single cluster                | 99        |

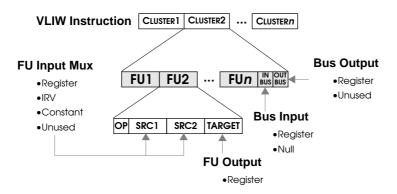

| 6.2. VLIW instruction format                                                                  | 100       |

| 6.3. Basic scheduling algorithm                                                               | 102       |

| 6.4. Relative performance of VLIW clustered architectures assuming the same cycle time        | 104       |

| 6.5. Selective unrolling algorithm                                                            | 105       |

| 6.6. Example of how to unroll a loop                                                          | 107       |

| 6.7. IPC results for all the SPECfp95 benchmarks and a 2-cluster configuration                | 109       |

| 6.8. IPC results for all the SPECfp95 benchmarks and a 4-cluster configuration                | 110       |

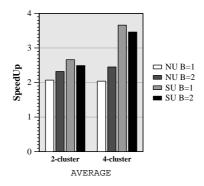

| 6.9. Speedup of clustered architectures with respect the unified one (bus latency=1 cycle)    | 112       |

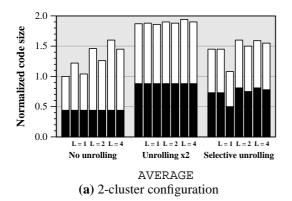

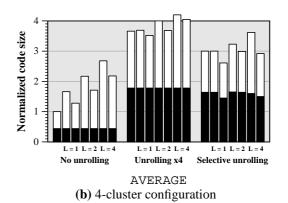

| 6.10. Impact of loop unrolling in the code size                                               | 113       |

| 6.11. Microarchitectures of a MultiVLIWProcessor                                              | 114       |

| 6.12. Motivating example                                                                 | 116   |

|------------------------------------------------------------------------------------------|-------|

| 6.13. RMCA modulo scheduling step by step                                                | 119   |

| 6.14. Results obtained for an unbounded number of buses (averaged for all benchmarks)    | 123   |

| 6.15. Results obtained when the number of buses is limited (averaged for all benchmarks) | . 125 |

# LIST OF TABLES

| CHAPTER 1                                                                                          |      |

|----------------------------------------------------------------------------------------------------|------|

| 1.1. Cache hierarchy configuration in current microprocessors                                      | 4    |

| CHAPTER 2                                                                                          |      |

| 2.1. Summary of locality analysis tools                                                            | . 17 |

| CHAPTER 3                                                                                          |      |

| CHAPTER 4                                                                                          |      |

| 4.1. Locality results for the selective cache                                                      | 56   |

| 4.2. Basic LSMCache configurations                                                                 | 65   |

| 4.3. LSMCache architectures with prefetching                                                       | 68   |

| 4.4. Averaged number of cache accesses per reference                                               | . 71 |

| CHAPTER 5                                                                                          |      |

| 5.1. Modeled architectures                                                                         | 86   |

| 5.2. Relative speed-up                                                                             | 88   |

| 5.3. CSMS compared with LBND scheduling                                                            | 89   |

| 5.4. Increment of compute time and decrement of stall time in relation to the CHL (in percentage)  | .89  |

| 5.5. Percentage of additional memory references                                                    | 92   |

| 5.6. Increment of compute time and decrement of stall time for schemes based on inserting prefetch | h    |

| instructions (in percentage)                                                                       | 92   |

| 5.7. Miss ratio for the CHL and the different prefetching schemes                                  | . 93 |

| CHAPTER ( | 6 |

|-----------|---|

|-----------|---|

| 6.1. Clustered VLIW configurations and latencies | 107  |

|--------------------------------------------------|------|

| 6.2. Cycle times according to Palacharla model   | 11   |

| 6.3. Clustered VLIW configurations and latencies | . 12 |

A mis padres, Paco y Juani, por todo su apoyo.

### **INTRODUCTION**

Cache memories are fast and small memories that current microprocessors include in order to mitigate the gap between processor and memory speeds. The basic idea is to design a hierarchy of memories (one or several levels) between the processor and the main memory such that a memory access may be solved by one of these levels much faster than by the main memory. The effectiveness of this solution strongly depends on the proper usage of the cache hierarchy. The ability of a cache to store the most useful data is based on exploiting the locality exhibited by memory references. In this chapter we review different techniques, both hardware and software, to improve the behavior of cache memories, especially techniques focused on the first level cache, and then we introduce the work developed in this thesis.

Figure 1.1. Evolution in the performance of memory and CPU speeds during last 20 years

#### 1.1. MOTIVATION

One of the main problems that computer architects have to face is the gap between processor and memory speeds. Advances in the design of microprocessors have experienced notable improvements over the last 15 years and this tendency is likely to hold for the next years. The most important improvements have been done in both clock rates and execution parallelism. By reducing the minimum feature size, new technologies pack more logic in a single chip, and allow transistor to switch faster. Furthermore, *instruction-level parallelism* (ILP), exploited by both hardware and compiler technology, has also been key for this performance growth. However this trend has not been experienced by memory technology. Whereas microprocessor performance has improved 55% per year since 1987, and 35% per year until 1986, the improvement in memory latency is only a 7% per year. This discrepancy in the evolution of processor and memory performances can be seen in Figure 1.1., extracted from [43].

This discrepancy in speed has fostered many studies to mitigate this gap. The most extended solution is the inclusion of a memory hierarchy, and then the concept of *cache memory* is introduced [109]. Cache memories are small and fast buffers that are used to store recently-used information. The basic idea behind a memory hierarchy is to put a cache memory between the processor and the main memory. Thus, a memory access from the processor first tries in the cache, and if the information is found, the access is quickly solved. This allows the processor not to wait for the information to be brought from main memory. Otherwise, if the information is not found in cache, it is fetched from memory and temporary stored there. So that a possible future access to this information can be solved with minimum latency. Cache memories are usually provided for data and instructions separately in the first level. Memory hierarchies with two or three levels of cache between the processor and the main memory are common in existent computers. Cur-

Introduction 3

rent designs have the first level cache (and even the second) inside the same chip as the processor in order to achieve a low access latency.

The performance of this scheme highly depends on the ability of the cache to keep the information that will be used in a near future. Guesses about future references rely on the concept of *locality* [43]. The ability of the processor to exploit the locality depends on both the cache architecture and the reference patterns generated by the program.

As we will see in this chapter and during the rest of the thesis, many heuristics have been proposed in order to improve the performance of the basic cache architecture. Some of these techniques consist of code transformations or data reorganizations that are done by the compiler, whereas some other techniques rely on some additional hardware. We can also find in the literature some hybrid techniques that combine software and hardware mechanisms. All heuristics proposed are based on the exploitation of some particular locality features that have been observed in programs. However not all of them make use of a locality analysis that indicates when this heuristic has to be applied. It is shown in some works and in some parts of this thesis that a "blind" use of many of these heuristics can lead to an underutilization of the cache and can even degrade its performance. For instance, it is shown that an unconditional use of prefetching contributes to the pollution of the cache with useless blocks that can replace useful blocks. A better knowledge of the locality of programs, defining more precisely where the problems are and what are their causes is a key factor for an effective usage of many techniques.

In this thesis we show that data locality of programs can be accurately analyzed. For numeric applications, this analysis can be performed almost statically by the compiler, obtaining then a very fast and very accurate analysis. Moreover, the information that a static analysis can offer is very wide, identifying clearly the hot points in the program. This analysis is used to propose different alternatives in the management of the cache in order to efficiently use the storage space. We explore different techniques that "communicate" the locality information to some particular cache organizations, obtaining then techniques that, based on explicit locality information, make a smarter use of the bare cache scheme.

The organization of this chapter is the following one. First we will review some basic cache concepts as well as different classical techniques (both hardware and software) proposed to improve the performance of the basic cache scheme. Then, we will highlight the contributions of this thesis and finally the organization of the remaining chapters.

#### 1.2. BACKGROUND

Typical caches are characterized by three different parameters: (i) capacity, (ii) block size, and (iii) associativity. The capacity of a cache corresponds to the amount of information (measured in bytes) that is able to store. This capacity is commonly divided into blocks (also referred as lines). A cache block is the amount of contiguous information that is brought, when necessary, from the next level of the hierarchy. Then, the block size is the size of one of these blocks. Finally, the associativity of a cache represents the number of different locations (in this case, blocks) in which a new block brought from the next hierarchy level can be stored. This parameter, thus, also indicates the number of positions in which we have to search for each access. If the associativity is one, the cache is called *direct-mapped*. On the other extreme, if a new block can be stored in any block of the cache, it is called *fully-associative*. Finally, intermediate configurations are called *n-way set-associative* caches, where *n* represents the associativity.

All current general-purpose processors are implemented with at least one cache level. Table 1.1 shows different examples with their features. Even in the scenario of embedded/DSP processors, that have typically been designed without a memory hierarchy, we can nowadays find commercial microprocessors with the inclusion of one or more levels of cache [102].

|         |               | L1        |        |           |        | L2        |          |

|---------|---------------|-----------|--------|-----------|--------|-----------|----------|

| Family  | Model         | DA        | TA     | INSTRU    | CTIONS | (inside t | he chip) |

|         |               | Size (KB) | Assoc. | Size (KB) | Assoc. | Size (KB) | Assoc.   |

| Intel   | Pentim II     | 16        | 4      | 16        | 4      | -         | -        |

|         | Pentium III   | 16        | ?      | 16        | ?      | 256       | 8        |

| AMD     | K7            | 64        | 2      | 64        | 2      | -         | -        |

| PowerPC | 620           | 32        | 8      | 32        | 8      | -         | -        |

| Sparc   | UltraSparc II | 16        | 2      | 16        | 1      | -         | -        |

| Alpha   | 21164         | 8         | 1      | 8         | 1      | 96        | ?        |

|         | 21264         | 64        | 2      | 64        | 2      | -         | -        |

|         | 21364         | 64        | 2      | 64        | 2      | 1.5MB     | 6        |

| MIPS    | R10000        | 32        | 2      | 32        | 2      | -         | -        |

| HP      | PA-7200       | -         | -      | 64        | 2      | -         | -        |

|         | PA-7300       | 64        | 2      | 64        | 2      | -         | -        |

|         | PA-8500       | 1MB       | 4      | 0.5MB     | 4      | -         | -        |

Table 1.1. Cache hierarchy configuration in current microprocessors

Many techniques and proposals can be found in the literature to improve the behavior of a cache. These techniques could be grouped into three different kinds, depending on their aim:

Introduction 5

- Reduce the penalty on a cache miss

- Reduce the number of misses

- Reduce the number of memory accesses

Among all these different techniques, some of them are implemented just by hardware so that the original code is not affected, whereas some other proposals are based on code transformations, with some possible support of the hardware. In the following subsections we review some of the most classical techniques. Due to the huge number of proposed techniques, this review will probably miss some techniques that some readers may consider very important. Other techniques more related to particular proposals of this thesis are reviewed in the following chapters where the proposals are presented.

#### 1.2.1. Hardware-Based Techniques

Hardware approaches are implemented by modifying the organization of the cache core itself or by adding new submodules with a special goal. The main advantage of these schemes is that no requirement from the instruction set nor from the user/compiler is required.

#### **Higher associativity**

As many studies point out, one of the reasons why memory references miss in cache is due to the mapping function. In a *direct-mapped* cache, each block that is brought to the cache has just one possible location. This means that if several blocks that are used in the same interval of time are mapped onto the same location, each one will alternatively replace the other, provoking then cache misses. The basic solution to this problem is to increase the associativity of the cache. Some different algorithms can be found in order to select which one of the multiple locations is chosen if any block has to be replaced (the most common algorithm is called LRU - Least Recently Used).

However, the main drawback of increasing the associativity of a basic cache is that the complexity of the cache is increased as well. This fact produces an increment in both the access time and the area of the cache. Then, one of the roles of the designer is to choose the best trade-off among these terms. Typical organizations in modern high-performance processors are 2-way or 4-way set associative caches.

#### Larger block size

Another way to reduce the miss rate is to increase the block size of the basic cache. Larger block sizes take advantage of spatial locality and at the same time reduce compulsory misses. However, an important remark is the fact that a cache is designed to exploit an average of the temporal and spatial reuse. Note that

6 Chapter 1

temporal reuse does not benefit from larger block sizes but from having more cache blocks. With the same cache capacity, a larger block means less number of blocks, and then, we have here another trade-off to deal with. Typical cache blocks in modern microprocessors are 32 or 64 bytes.

#### Second-level caches

The most common way to reduce the penalty of a cache miss is to introduce one or two levels of caches between the first level cache and the main memory. These caches could be placed inside the processor chip or outside. An example of microprocessors with several levels of cache is the Alpha 21364 [40]. This processor has a 64KB L1 data cache, a 64KB L1 instruction cache and a 1.5MB L2 unified second cache on-chip, and a can have an L3 cache off-chip.

#### Write buffers

In a simple cache organization, the CPU must wait for stores if the block to be updated is not in cache. The simple policy is waiting until the block is fetched from the next memory level and then updated. A common optimization to reduce stalls due to store operation is the addition of a write buffer. A write buffer consists on a small (typically fully-associative) buffer in which write requests are temporary stored until they are written to cache or memory. It allows the CPU to wait just until the request has been written onto the write buffer, reducing then the store latency. Once the request is in the write buffer, the cache takes profit of inactive cycles to deal with entries in the buffer. On later cache accesses, both cache and write buffers are tried in parallel. If a block is in both the cache and the write buffer, the request is resolved by the latter, since it has the most recently updated block.

#### Victim caches

The *victim cache*'s [52] primary goal is to remove conflict misses. The basic idea is to have a small fully-associative module where blocks discarded from the main cache are placed. If a hit occurs in the victim cache, a swapping of blocks between the victim and the main cache is performed. A similar cache architecture is the PA-7200 *assist cache* [15]. The management of the two modules is somewhat different, the software-controlled selective swapping being its most important difference. Memory instructions in the PA-7200 have a flag that is set by the compiler for those instructions that are expected to exhibit only spatial reuse. The data accessed by these instructions are brought into the assist cache but are not later moved to the main cache.

Introduction 7

#### Hardware prefetching

Data prefetching techniques basically consist of bringing memory blocks to cache before they are referenced. Basic hardware prefetching techniques appeared practically in conjunction with the earlier proposals of caches memories. In fact, a conventional cache implements implicitly a mechanism of hardware prefetching since on a miss, a memory block (instead of just a single data) is fetched, taking then profit of the spatial locality.

The first interesting hardware prefetching schemes were proposed by A. J. Smith [94]. He proposed a techniques called *one block lookahead (OBL)*, that is, on an access to block i, the block i+1 is prefetched, taking then profit from spatial locality. He also proposed alternative approaches to performing the prefetching: (1) always on a cache access, (2) on a cache miss, and (3) tagged prefetch. This last option works as follows: on a miss, the current and next blocks are fetched, and this last one is tagged with zero. When an access to a block with tag zero is performed, the tag is set to one, and the prefetch to the next line is performed (in this case, if the new line is not in cache, it is tagged with zero).

With the years, new hardware prefetching techniques have been proposed. Lookahead schemes try to solve the problem when the stride of the access is large. However, maybe the most well-known scheme are the stream buffers. Stream buffers were proposed by N. Jouppi [52]. They consist of FIFO queues added between the L1 and L2 caches where some consecutive memory blocks are stored. On an access to memory, both the L1 cache and the tops of each stream buffers are tried in parallel. If the access hits on the cache, the stream buffers remain untouched. However, on a miss in cache, if the access hits in a stream buffer, the corresponding block is moved to the cache. Then, the stream buffer prefetches the next block in the next level of the memory hierarchy. When there is miss in both the L1 cache and the stream buffers, a new stream buffer (if any) is reserved and the next blocks are prefetched. As the prefetched data are stored in buffers apart from the L1 cache, the scheme avoids the possible pollution contributed by the prefetched data. Nevertheless, stream buffers behave well for small strides and when programs do not deal at the same time with more structures (e.g., arrays or matrices) than available stream buffers.

#### Non-blocking caches

On a typical memory access, a miss on the first level cache provokes all the CPU to stall until the data is returned to the target register, even if this data is not used immediately.

Non-blocking caches where originally proposed by Kroft [60] and since then, some studies about the possible implementation [26] and its impact in the performance [16] have been proposed. The main idea

8 Chapter 1

behind a non-blocking cache (also known as lockup-free cache) is that instructions that miss do not stall the system, that is, the memory access will be served in parallel with the execution of subsequent instructions, including other memory accesses, that do not need the data. Moreover, a common feature in non-blocking caches is the possibility of dealing with multiple outstanding misses concurrently.

Non-blocking caches are very common in current processors. Examples of processors that use them are the MIPS R1000, the PowerPC 620, the HP-PA8000 or the Alpha 21164.

#### 1.2.2. Software-Based Techniques

Another family of techniques are those performed at compile time. In this case, the compiler is the responsible for transforming the code with the goal of taking the maximum profit to the memory hierarchy.

#### **High-level code transformations**

High-level code transformations aim to restructure some parts of the code in order to increase the memory performance. These transformations can be performed in the high-level representation of the code. Each technique is typically oriented to exploit a particular feature of the memory access patterns, and then, a typical optimization pass is composed of several of these transformations. Some of the more common are:

- *Loop interchange*: it consists of exchanging the position of two loops in a loop nest by moving one of the outer loop to inner positions. This transformation can improve the performance in many different ways. Regarding the improvement of the data locality, it can help to reduce the stride of the access (ideally to stride one), and then exploiting spatial locality in a cache block.

- Loop blocking (or tiling): this transformation helps to improve the locality of accesses when it is limited by the cache capacity. Blocking is accomplished by modifying the order in which the iteration space is traversed so that reuses of data occur at a shorter distance in time. Thus, the storage requirements to exploit the locality is relaxed.

- *Loop unrolling*: a loop is unrolled when the body of the loop is replicated a number of times *u*. The benefits of unrolling are multiple: reduction of the loop overhead, increment of the instruction level parallelism, improvement of register, data cache and TLB locality, etc. However, the main disadvantage on loop unrolling is the code expansion.

- *Loop fusion*: joining two different loops in one may increase the register and cache locality since many times it requires less memory accesses and can do a better usage of the registers. This optimization also allows to reduce loop overhead.

Introduction 9

• *Variable padding*: conflicts when accessing variables depend on the initial addresses of each variable and the initial addresses of each of their dimensions. By separating two conflicting arrays in the memory space (inter-array padding) or by adding some dummy elements to some array dimensions (intra-array padding), conflict misses can be reduced.

- *Merging arrays*: this technique helps to reduce the number of misses by improving spatial locality. It consists of combining different matrices (that are referenced with the same pattern) into a single compound array. The basic idea is that a single cache block will contain the desired elements, avoiding then the possible interferences among each other.

- Copying: this technique is based on adjusting the data layout in cache by copying array tiles to temporary arrays that exhibit better cache behavior.

These are just a some examples of different techniques that can be found in the literature. All of them can be very beneficial is some cases, but at the same time they can degrade the generated code if they are not used properly. Thus, all of them require an in-depth analysis of the code, and in particular the locality properties.

#### Software prefetching

Software prefetching is another different technique proposed to tolerate memory latency. The main objective of this technique, like hardware prefetching, is to bring data to higher levels of the memory hierarchy (typically the first level cache) before these data are demanded by the processor. so that the accesses can be solved with shorter latency.

In software prefetching, the compiler is the responsible of, following certain criteria, introducing special prefetching instructions in the user code. These instructions will fetch the necessary data so that lately, when the actual load/store instruction is executed, the data can be found in cache. The basic idea is that these kind of instruction will not block the processor on a miss, and then these accesses can be served in parallel with the execution of the following instructions. Then, the basic hardware requirements to support software prefetching are: (1) non-blocking caches, and (2) a prefetch instruction. Non-blocking caches were previously reviewed in this section. A prefetch instruction has three properties:

- It has no target register, since the data is fetched to cache.

- It does not block the processor, and then it can be overlapped with other memory references or computations (this is accomplished with the non-blocking cache).

10 Chapter 1

• It does not provoke exceptions, since software prefetching speculates on certain memory addresses that may not be valid and provoke, for instance, page or protection faults.

The majority of current microprocessors incorporate in their instruction sets operations to perform software prefetching. For instance, the MIPS R10000 [75] has an instruction called *PREF* that can fetch data to the L1 or the L2 caches, and, using a special hint, can determine in which set of the cache the data has to be allocated (since it is 2-way set-associative). The PowerPC620 [19] offers instructions called *TOUCH* that allow to pre-charge data in the cache. The Alpha 21164 [21] allows two modalities of prefetching instructions: *FETCH* (normal prefetching) and *FETCH\_M* (permits modifications in some or all blocks to be anticipated). Finally, the HP-PA8000 [47] does not offer any special instruction to prefetch data, but it is done by loading data in the register zero. In case this instruction provokes a trap, then it is executed as a *NOP*.

An alternative to having special prefetch instructions is using longer latencies to schedule memory operations. It consists of scheduling selected load instruction with long latencies so that the consumer can find the data as soon as it is scheduled for execution. In the literature this second alternative is called *binding prefetching* (since the prefetch has a target register), whereas software prefetching using prefetch instructions is called *non-binding prefetching*.

#### 1.3. CONTRIBUTIONS OF THIS THESIS

In this thesis we propose some techniques to improve the performance of the cache by making use of a versatile data locality analysis. The main difference between the techniques proposed in this work and the rest of proposals is the explicit use of data locality information in order to guide the optimization. We claim that the non-homogeneous management of all memory references may be key to performance. With this aim, and with the help of the locality information, each memory instruction will be handled by the compiler in the particular way that best suits the underlying cache organization.

The main contributions of this thesis are listed below:

- We propose and make use of a novel data locality analysis that is performed statically with the help of some simple profiling information. In this analysis, a simple but efficient interference analysis is included, which makes the analysis more accurate.

- The information obtained by the locality analysis is passed to the hardware through some special hints in memory instructions in order to manage some specialized hardware added to the simple cache model.

Introduction 11

• We propose a novel explicit management of multi-module caches using the hints previously mentioned to decide, according to locality information, the best way of using these storage modules.

- We propose a software prefetching technique to be used in modulo scheduled loops. This technique is shown to find the best trade-off between processor's compute and stall time.

- Finally, we propose a novel clustered VLIW architecture where the L1 cache is distributed among the different clusters. An algorithm to effectively schedule instructions in this architecture is also proposed.

#### 1.4. ORGANIZATION OF THIS THESIS

The different chapters of this thesis are organized in the following way. In Chapter 2, the data locality analyzers used in the rest of the work are presented. We have used in this thesis two different locality analysis: (i) SPLAT, and (ii) Fast CME. Both analysis have in common that obtain their results statically (that is, without the necessity of simulating the program) with the usage of some simple profiling information. This makes both tools very fast, flexible and accurate. The objective of using two different analysis is also to show that the techniques proposed in the rest of chapters are independent of the locality analysis itself.

In Chapter 3, the SPLAT locality analysis is used to obtain characterize the locality of the SPECfp95 programs, which is later used as a motivation for the different techniques proposed in the rest of the thesis.

In Chapter 4, the first technique that make use of the locality analysis is presented. It consists of a multi-module cache with explicit management based on hints that are set by the compiler. The cache is composed of different modules, each one configured to exploit a particular type of locality. Some hints in the memory instructions indicate the hardware in which module a new fetched has to be allocated. These hints are set by the compiler using the data locality analysis.

In Chapter 5, the second proposal that makes use of the locality analysis is described. This chapter presents a study of the interaction between two different techniques: software pipelining and software prefetching. The first one is a very effective technique proposed to schedule loops with the objective of increasing the ILP. On the other hand, software prefetching, as previously commented, is a technique used to tolerate memory latency. After evaluating different alternatives, a novel algorithm to perform software prefetching in software pipelined loops is proposed. This algorithm takes into account both the shape of the dependence graph and the locality properties of the different memory instructions using the data locality analysis.

In Chapter 6, the last application of the locality analysis is presented. In this chapter the locality analysis will be used to schedule instructions in a proposed clustered VLIW architecture. After developing an effective approach to scheduling instructions ignoring memory effects in a clustered architecture with a distributed register file, an algorithm to schedule instructions in an clustered architecture with a distributed cache is proposed. This algorithm will use the locality analysis (in this case, the Fast CME) to select in which cluster is more beneficial to schedule a memory operation.

Finally, Chapter 7 summarizes the main conclusions of this thesis and outlines the future work.

## **DATA LOCALITY ANALYSIS**

Data locality analysis is the process by means of which the intrinsic access pattern of memory instructions and their behavior on a given memory hierarchy are studied. This kind of analysis is commonly used to improve the performance of some locality optimizations performed by the compiler (such us blocking, loop interchange, etc.) as well as to study the locality properties of different programs in order to propose new memory architectures. In this chapter we propose a data locality analysis (called *SPLAT*) that will be used to support some of the techniques proposed in this thesis. Moreover, we review a second data locality analysis (called *FastCMEs*) that, although not proposed in this thesis, is used in one of the proposals.

#### 2.1. Introduction

Memory penalties are one of the main reasons why computers performance is quite below peak performance for most applications. Understanding the source of the problems is the first step towards devising new hardware organizations and/or new code transformations to overcome them.

The user may be interested in quantifying the memory penalties but this information is not enough in many cases. A more detailed explanation of the different causes for these penalties is sometimes required in order to investigate the appropriate optimization. In order to tune a program, a programmer may be interested in knowing its performance, locating those critical parts where most of the memory penalties are produced, identifying which data structures are responsible for most of the cache misses, etc. Examples of the type of information that the user may be interested in are listed below:

- Classifying the different types of cache misses into the three commonly used categories (compulsory, capacity, conflict) can be important to choose among different types of optimizations. Capacity misses could be best reduced by blocking [31][12]; conflict misses by padding [85]; and compulsory misses by prefetching [9][76], among other possibilities.

- Identifying the parts of the program that are responsible for most penalties may help to reduce the optimization effort by focusing on such cases.

- Conflict misses are the dominant type of misses for many numerical applications. Identifying which data structures are responsible for these conflicts may be required in order to eliminate them by means of padding [85] or copying [99], among other possibilities.

- Quantifying the intrinsic reuse of a program can be used as an upper bound of the locality that can be exploited. This is a useful measure in order to know how far from optimal the current performance is.

- Evaluating the memory performance for a variety of cache architectures for a set of applications can

be interesting for the design of an embedded processor with a cache memory customized for a particular workload.

- Including some bits in the memory instructions so that the compiler can provide some hints to the hardware regarding the locality exhibited by each memory instruction is becoming a common practice. For instance, the PA7200 has a bit in order to identify memory instructions with only spatial locality [15]. The PowerPC provides the possibility of identifying instructions that do not exhibit much locality and thus, to bypass the cache for such instructions [97]. Having different cache memories specialized in exploiting different types of locality may be a promising alternative to increase the cache

Data Locality Analysis 15

performance as we will see in Chapter 4. In all these cases, the compiler is responsible for providing the information that is codified in the memory instruction and that will determine during execution the proper action that the hardware must take.

The process of obtaining information of the locality characteristics of a given program is known as *data locality analysis*. This analysis has been performed traditionally either at compile-time or at run-time. The former approach has a low overhead but it is relatively inaccurate since there is much information that the compiler does not know. The latter usually takes the form of a memory hierarchy simulator, which is quite accurate but very slow.

Different approaches to analyze the data locality of programs may be found in the literature. These approaches can be classified into three families of techniques:

- Memory simulation.

- Tools based on hardware-counters provided by some microprocessors. Examples of such microprocessors are the Pentium Pro [81], the UltraSparc [103] or the MIPS R10000 [112].

- Static locality.

The following subsections review some previous work on data locality analysis.

#### 2.1.1. Dynamic Analysis

Any data locality analysis methodology or tool can be assessed through three basic criteria: a) *accuracy*; b) *speed*; and c) *flexibility*. By this later term we mean the amount of different information that the analysis may provide and the possibility to analyze different memory architectures.

Memory simulation techniques are very accurate and flexible in general, but they are very slow. Traditionally memory simulators are based on a trace-driven approach [57][34][74][98][32][67][35][5][72]. They cause a significant slowdown in the execution of the analyzed program, which may be of several orders of magnitude. For instance, the slowdown exhibited by all the simulators surveyed in [105] is in the range of 45-6250. This slowdown is obviously unaffordable for some real applications.

More recently, some innovative methods to perform memory simulation have been proposed with the main objective of reducing the exhibited slowdown. The basic idea behind these methods is to find special cases where a memory reference does not affect the simulated memory state, and avoid or keep very low the overhead in these cases. For instance, if we are interested only in the miss ratio, references that cause a

cache hit do not require any processing. The hit detection can be performed by software, as it is the case of MemSpy [70], Fast-cache [64], and Embra [110], or it can be done by hardware, as it is the case of WWT [84]. The slowdown exhibited by these techniques depends on the miss ratio. The lowest slowdown has been reported for WWT, which can be as low as 1.4 for caches with very low miss ratios, but it is greater than 30 or 40 for caches smaller than 32 KBytes [63]. The other three techniques exhibit a slowdown of 2-21, which is still quite high, especially if one considers that the locality analysis usually is a part of an iterative process in which multiple analysis and optimization steps are applied repeatedly. Besides, if the required information is more than just the miss ratio (e.g. type of reuse exhibited or type of misses), it may require to process most or all memory references, which will result in a slowdown similar to that of tracedriven simulation approaches. In other words, these innovative methods trade-off flexibility for speed.

Tools based on hardware counters (e.g. [3]) are fast and accurate but they lack of flexibility, since they can only analyze the memory architecture of the actual microprocessor, and they can just provide a limited set of results which depend on the particular counters provided by a particular machine. Important results like number of conflict misses per each pair of data structures cannot be obtained with current hardware counters, unless they are combined with a type of memory simulator.

#### 2.1.2. Static Analysis

Static analysis techniques (e.g. [100][33]) are fast and flexible, but they can have a low accuracy. This loss of accuracy is caused by the unknown information at compile time. For instance, unknown loop bounds or unknown initial addresses of data structures can be rather detrimental to the accuracy of the results.

The static/dynamic approach taken by the SPLAT tool achieves the best trade-off among the three performance criteria: accuracy, speed and flexibility. It is flexible since the static analysis can track many different information among memory references and different memory architectures can be considered. It is accurate (for numerical programs which are the target of the tool), since the information that is unknown at compile time is provided by a profiling. Finally, it is fast since the profiling information is quite simple and it must be generated just once for multiple analysis of the same program. The slowdown of the tool for the analyzed bechmarks ranges from 0.0 to 0.1<sup>1</sup>. As its main drawback, we should mention that the SPLAT tool is not capable of monitoring multi-process workloads or the operating system kernel.

The main characteristics of the different types of tools are summarized in Table 2.1.

<sup>1.</sup> On a SuperSPARC/60 workstation

Data Locality Analysis 17

|                    | Accuracy  | Speed             | Flexibility  |

|--------------------|-----------|-------------------|--------------|

| Simulation         | Very high | Slow-<br>Moderate | High-<br>Low |

| Hardware counters  | Very high | Fast              | Low          |

| Static<br>analysis | Moderate  | Fast              | High         |

Table 2.1. Summary of locality analysis tools

## 2.2. BACKGROUND DEFINITIONS

Before presenting the data locality analysis, we first define some memory related terms that are used all along this chapter. The first definition is related to the terms *reuse* and *locality*. Reuse (also called *intrinsic reuse*) is a measure that is inherent in a given program and depends on neither the order in which instructions are executed nor the cache configuration. A reuse occurs whenever a memory instruction references the same data as a previous instruction (that can either be the same instruction or another one). However, when these instructions are executed, some factors may inhibit the exploitation of this reuse in a given memory hierarchy level (for instance, the limited storage of the cache memory). The amount of reuse that is actually exploited by a given memory hierarchy level is referred to as locality of the program with respect to that memory level.

The different types of reuse/locality used in this chapter are defined in [111]. Temporal reuse occurs when the same memory location is accessed several times. It is called *self-temporal* or *group-temporal* reuse/locality depending on whether it is accessed by the same memory instruction or by different instructions respectively. On the other hand, spatial reuse appears when different nearby memory locations are accessed. It is called *self-spatial* or *group-spatial* reuse/locality depending on whether it is accessed by the same memory instruction or by different instructions respectively. Note that an instruction in a loop nest can have a different type of reuse/locality for each loop on the nest

Finally, the last set of terms that we use in this chapter refers to the different types of cache misses. Misses are traditionally classified into three categories [44]: compulsory, capacity and conflict misses. *Compulsory misses* occur the first time a cache block is accessed. This type of misses are also called cold start misses. On the other hand, both capacity and conflict misses can be considered as replacement misses (in other words, the data was in cache, but when it is actually accessed, it is not). Capacity misses happen because the cache cannot contain all the blocks needed during the execution of a program, whereas conflict misses occur in set-associative caches (including direct-mapped) when too many blocks map to the same set.

18 Chapter 2

For the locality analyzer presented in this chapter, the reuse of each memory instruction is computed following the methodology described in [111]. The results are represented as a vector space that identifies the loops in which reuse is found (each dimension corresponds to a loop). We distinguish between two types of temporal and spatial reuse:

- a) Unitary: the vector has only one element different from zero, that is, vector  $(0,...,0,n_i,0,...,0)$  indicates that this reference has reuse after  $n_i$  iterations of loop i.

- **b)** *Combined*: the vector has more than one elements different from zero, that is, vector  $(0,...,0,n_i,n_{i+1},...,n_N)$  indicates that this reference has reuse after  $n_i$  iterations of loop  $i, n_{i+1}$  iterations of loop i+1 and so on.

The result of this study is a list of the different reuses exhibited for each reference indicating the loop(s) for which each reuse holds.

# 2.3. STATIC AND PROFILED LOCALITY ANALYSIS

This section describes the proposed tool for data locality analysis, which is called *SPLAT* (Static-Profiled data Locality Analysis Tool). The locality analysis is performed through some static information computed by the compiler and some dynamic information obtained by a simple profiling (see Figure 2.1).

#### 2.3.1. Compiler and Profiler Phases

The static information is aimed at computing the different types of misses that will happen during the execution. Compulsory misses require to compute the intrinsic reuse of data. Capacity misses require in addition to compute the volume of data referenced by each loop iteration. Finally, conflict misses are identified by computing interferences among data references. All this information is summarized in three files:

- Reuse file: for each memory instruction and each loop in which it is enclosed, it stores its type of reuse (unknown, none, self-temporal, self-spatial, group-temporal or group-spatial). If the reuse is spatial it also stores the stride (i.e., the difference between the effective address of two consecutive executions). If the reuse is group-temporal or group spatial, it also contains the *distance*, which is defined as the number of iterations before the reuse takes place.

- *Nest loop file*: this file is intended to represent the loop structure of the program. For each loop it stores its parent, which is defined as the loop that encloses it.

Data Locality Analysis 19

Figure 2.1. Global scheme

• *Interference file*: for each pair of memory instructions (with the same nesting level and without any other loop in between) that have the same reference pattern, it contains their initial addresses if they are known at compile-time<sup>1</sup>. Two instructions have the same reference pattern if their corresponding variables have the same number of dimensions, the size of each dimension is the same in both references, and the expressions that represent the indexing functions for each dimension differ only in a constant value.

The profiling consists of just the number of executions of each basic block, which is a facility provided by many current compilers (e.g., the Sun f77 compiler). From this information, the number of executions of each memory instruction and the average number of iterations of each loop can be derived. These data are stored in the *reference file* and the *iteration file* respectively.

# 2.3.2. Locality Analyzer

This static and dynamic information is used as an input to the locality analyzer. The locality analysis is divided into three phases: (i) reuse phase, (ii) volume phase, and (iii) interference phase. The first phase identifies all the reuse exhibited by the program. This information is the basis for computing misses. In particular, compulsory misses do not require any additional analysis: they consist of all references without any reuse. The volume phase is targeted to identify capacity misses. Finally, the interference phase computes the conflict misses.

<sup>1.</sup> In the SPECfp95 benchmark suite, about 75% of all memory references have their initial address and dimension sizes known at compile-time

```

function greuse (int i) {

NN_{i}[N] = 1;

ST_{i}[N] = SS_{i}[N] = GT_{i}[N] = GS_{i}[N] = 0;

for j=N-1 to 0 do {

switch (SELFReuse[j]) {

case NONE:

\begin{array}{lll} & & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &

break;

case TEMPORAL:

break;

case SPATIAL:

Tacker Strike:

factor = stride / blocksize;

NN<sub>i</sub>[j] = (factor * NGIt<sub>j</sub>) * NN<sub>i</sub>[j+1];

ST<sub>i</sub>[j] = TIt<sub>j</sub> * ST<sub>i</sub>[j+1];

SS<sub>i</sub>[j] = (factor * TIt<sub>j</sub>) * SS<sub>i</sub>[j+1] +

((1-factor) * TIt<sub>j</sub>) * ATIt<sub>j</sub>;

break;

GT_{i}[j] = NGIt_{j} * GT_{i}[j+1];

GS_{i}[j] = NGIt_{j} * GS_{i}[j+1];

switch (GROUPReuse[j]) {

case NONE:

break;

case TEMPORAL:

GT<sub>i</sub>[j] += GIt<sub>j</sub> * ATIt<sub>j</sub>;

break;

case SPATIAL:

GS<sub>i</sub>[j] += GIt; * ATIt;

break;

}

```

Figure 2.2. Algorithm to quantify intrinsic reuse

# Reuse phase

In this phase, the different types of reuse exhibited by each reference are quantified. The input to this phase is the *reuse file* that is computed at compile-time following the methodology described by Wolf and Lam in [111].

The quantification of the reuse is performed basically through the function qreuse(i) showed in Figure 2.2, which is applied to each memory instruction except for those with unknown reuse<sup>1</sup> (they correspond to references outside loops, or inside loops but with non-linear expressions, or expressions with variables that are not loop indices). The i parameter represents the instruction identifier. The analysis starts from the innermost loop and finishes with the outermost loop that includes the instruction i, which are denoted by N-1 and 0 respectively.

<sup>1.</sup> References with unknown reuse are assumed to always miss in cache. They represent a 15% of the total number of memory references in the SPECfp95.

Data Locality Analysis 21

The function computes for each particular memory instruction in a particular loop j the following values:

- GIt;: number of iterations with group reuse in loop j.

- NGIt; number of iterations without group reuse in loop *j*.

- TIt;: total number of iterations of loop j.

- ATIt<sub>j</sub>: number of executions per each iteration of loop j. It is computed as  $\prod_{i=j+1}^{N-1} T_i t_i$ .

The quantification of each type of reuse for each loop in which the reference is enclosed is stored in the vectors NN (no reuse), ST (self-temporal), SS (self-spatial), GT (group-temporal) and GS (group-spatial). For instance,  $ST_{i}[j]$  represents the number of executions of instruction i that exhibit self-temporal reuse considering all the iterations of loop j. Each type of intrinsic reuse identified by the compiler is quantified as follows (see Figure 2.2):

- Section A: the instruction does not have any kind of self reuse in loop j. In this case, for each iteration of j without group reuse, the number of executions without any reuse is the number of executions without reuse in the loop j+1 (i.e.,  $NN_i[j]=NGIt_j*NN_i[j+1]$ ). For each iteration of loop j, the number of executions with self-temporal or self-spatial reuse is the number of executions with such reuse in loop j+1 (i.e.,  $ST_i[j]=TIt_j*ST_i[j+1]$ ).

- Section B: the instruction has self-temporal reuse in loop j. In this case, the first iteration of loop j has the same number of no-reuses as the whole execution of loop j+1 and the executions corresponding to the remaining iterations reuse the data of the first iteration. Therefore  $NN_{i}[j]=NN_{i}[j+1]$ . Self-temporal reuse is exploited by all executions except for the first iteration. For this iteration, the number of self-temporal reuses corresponds to that exhibited by the next inner loop. Finally, self-spatial reuse is computed as in section A.

- Section C: the instruction has self-spatial reuse in loop j. In this case, a value called factor that represents the percentage of references that access a new cache block is computed. Then, for each iteration of j without group reuse that references a new cache line, the number of executions without any reuse is the number of executions without reuse in the loop j+1. Self-temporal reuse is computed as in section A. Finally, self-spatial reuse is computed as follows. For those iterations of j such that i references a new block, the number of self-spatial reuses are the same as those in the next inner loop; and for the remaining iterations, all the executions exhibit self-spatial reuse.

22 Chapter 2

• Section D: group reuse is computed as follows (spatial and temporal are treated in the same way). First, for those iterations of j such that i does not exhibit group reuse, the number of executions with group reuse is the same as that of the next inner loop. For the remaining iterations, all executions exhibit group reuse.

After computing the function qreuse(i),  $NN_i[0]$  contains the number of *compulsory misses* of instruction i.

# Volume phase

A factor that may inhibit the exploitation of reuse is the limited storage of cache memory. In other words, if the amount of different data blocks that are referenced between two consecutive reuses of the same block is higher than the cache capacity (in block units), this reuse cannot be exploited by an LRU fully-associative cache. The resulting cache miss is called a *capacity miss*.

This requires to determine the amount of data that is used by each reference in each loop. This amount of data depends on:

- a) Type of reuse: calculated in the previous step.

- **b)** Loop bounds: obtained from the profiling information.

In this phase, the volume (in cache blocks) that each memory instruction contributes to the total volume of the loops that enclose it is computed. This can be obtained directly from the data computed in the previous phase. For a given loop j each execution of instruction i that does not exhibit any type of reuse will bring a new block into cache. On the other hand, if a particular execution of an instruction has any type of reuse, it does not bring any additional data into cache. Therefore, the value of  $NN_i[j]$  expresses the volume contributed by the instruction i to the loop j.

Once the volume of every loop has been computed, some reuses are marked as non-exploitable:

- If an instruction has self reuse in loop *j* (either temporal or spatial), but the volume of loop *j* is greater than the total number of cache blocks, this reuse will likely not be exploited by a conventional cache.

- If an instruction has group reuse (either temporal or spatial) and the volume corresponding to *distance* (see beginning of section 2) iterations of the loop is greater than the total number of cache blocks, this reuse will likely not be exploited either.

Data Locality Analysis 23

Then, the function greuse is computed again but without considering the reuses marked as non-exploitable. The new computed  $NN_{i}[0]$ , as in the previous phase, represents the cache misses of instruction i and the difference with its previous value is the number of *capacity misses* of instruction i.

#### **Interference phase**

Another factor that influences the locality is the effect of interferences. Typically, interferences or *conflict misses* are defined as those misses that occur in a direct-mapped or *n*-way set-associative cache but not in a fully-associative cache. This kind of misses may have a high impact for cache memories with a low degree of associativity, specially for direct-mapped caches.

The behavior of conflict misses is hard to predict because it depends on various dynamic factors such as memory addresses, instruction order, etc. Interferences may be of two different types: *self-interferences* and *cross-interferences*. Self-interferences occur when different data blocks referenced by the same instruction are mapped onto the same cache location, whereas cross-interferences occur among different memory instructions. The analysis proposed in this section detects a subset of these interferences. The interference analysis is currently implemented for direct-mapped caches. Its extension to set-associative caches is left as future work.

For every array reference and every loop for which it does not exhibit temporal locality, self-interferences are assumed to occur if the following condition is met:

where *N* represents the number of iterations of the loop. The *stride\_family\_in\_blocks* is related to the stride of the reference in the analyzed loop, expressed in cache block units. If the stride is not an integral number of blocks, the stride is rounded up to the next integer. The *stride\_family* defined by *x* is the set of strides  $\sigma \cdot 2^x$  with  $\sigma$  odd [42]. All the strides belonging to the same family (e.g.,  $12=3\cdot 2^2$  and  $20=5\cdot 2^2$  belong to family 2) have the same behavior from the point of view of self-interference.

For each reference and each loop, a *self-conflict ratio* is computed, which denotes the percentage of the *N* iterations of the loop that produce self-interferences. The amount of reuses in outer loops is reduced by this factor due to self-interferences.

Regarding cross-interferences, we focus on what is usually called ping-pong interferences, that is, a pair of instructions that reference different data blocks that map onto the same cache block for every execution. These interferences will inhibit completely the exploitation of any reuse exhibited by the interferences.

24 Chapter 2

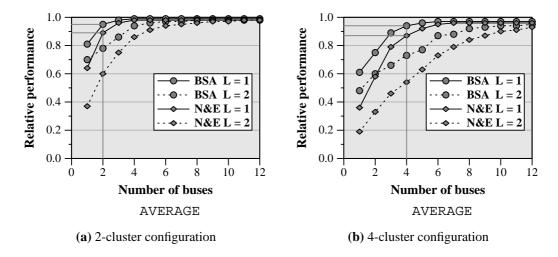

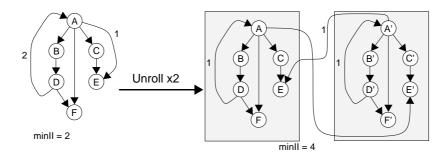

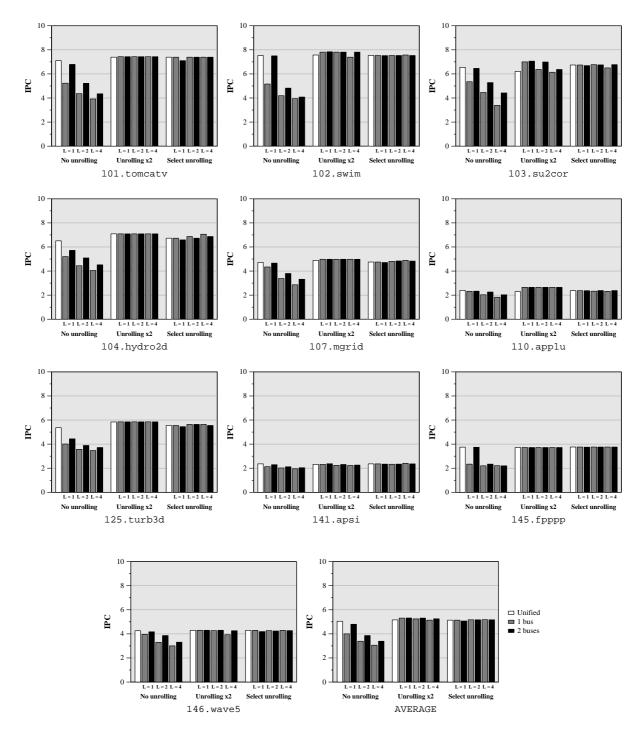

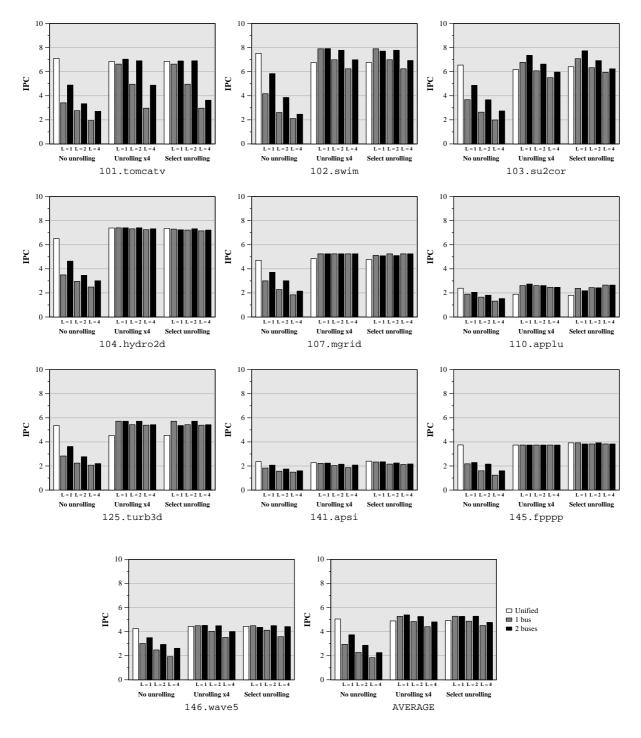

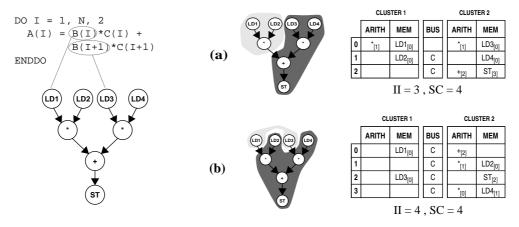

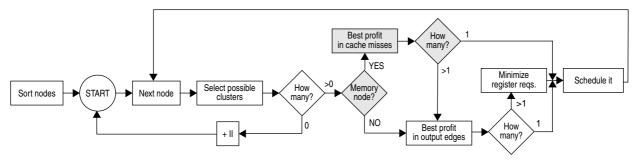

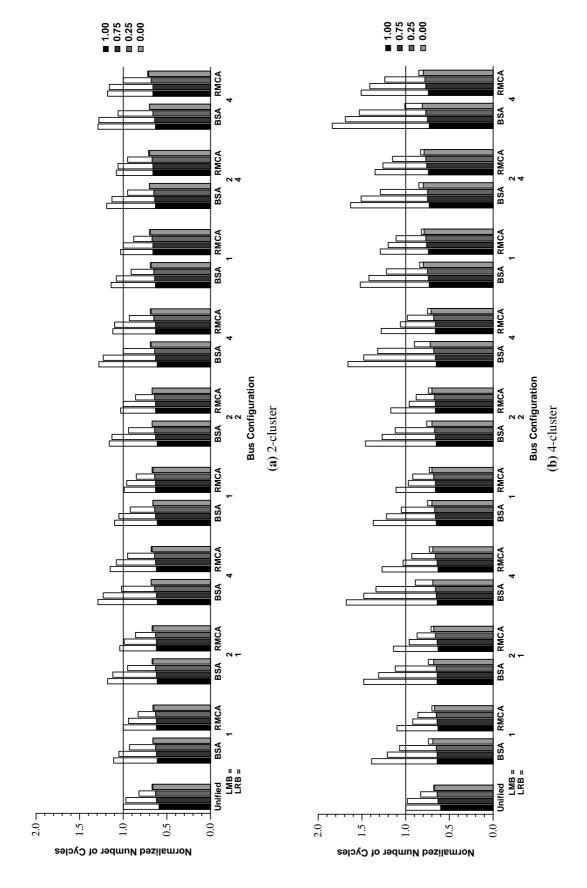

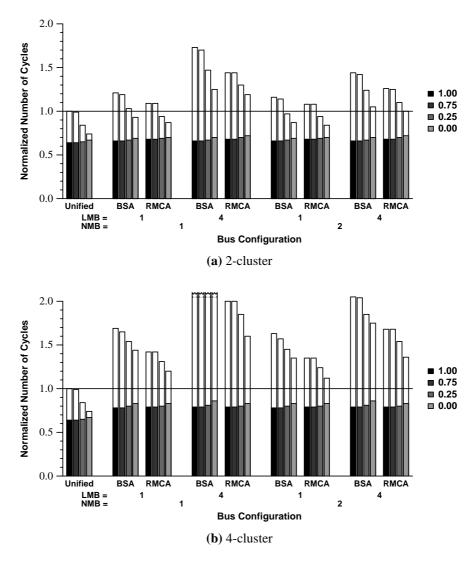

ing instructions. This type of conflicts is analyzed for each pair of memory instructions that meet the following conditions: