# DESIGN OF MULTI-MODULATION BASEBAND MODULATOR AND DEMODULATOR FOR SOFTWARE DEFINED RADIO

**CHYE YIN HUI**

UNIVERSITI SAINS MALAYSIA

2011

# DESIGN OF MULTI-MODULATION BASEBAND MODULATOR AND DEMODULATOR FOR SOFTWARE DEFINED RADIO

By

# **CHYE YIN HUI**

# Thesis submitted in fulfillment of the requirements for the degree of Master of Science

**DECEMBER 2011**

## SCHOOL OF ELECTRICAL AND ELECTRONIC ENGINEERING

**UNIVERSITI SAINS MALAYSIA**

#### ACKNOWLEDGEMENTS

There are lots of people whom I wish to thank for contributing to the completion of this thesis. First of all, my greatest gratitude goes to my supervisor, Associate Professor Dr. Mohd Fadzil Ain, at School of Electrical and Electronic Engineering, USM, for his valuable advices and suggestions, continuous supports and encouragement in helping me solve all the problems during this research.

I would like to thank Dean, Professor Dr. Mohd Zaid Abdullah; Deputy Dean of Postgraduate and Research, Associate Professor Dr. Kamal Zuhairi Zamli; and all the staffs and technicians at School of Electrical and Electronic Engineering, USM, for providing supports, good services and environment during my research in laboratories.

Special thanks to PhD student, Mr. Majid Salal Naghmash, who is working on IF processing of SDR for frequently exchanging points of view with me that always result in useful inspirations to my works.

I would also like to thank to Mr. Mazlaini Yahaya from TMRD (Telekom Malaysia Research and Development) for giving precious guidance and information related to Xilinx FPGA implementation.

My appreciation also goes to my friends and family for their emotional caring and supports in helping me relieve the stress and restore self-confidence to face and overcome all the difficulties throughout the period of this research.

The work in this thesis was supported in part by Malaysia Communication and Multimedia Commission (MCMC) SCIENCE FUND grant and USM Fellowship.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTSii                                          |

|-------------------------------------------------------------|

| TABLE OF CONTENTS                                           |

| LIST OF TABLES vii                                          |

| LIST OF FIGURES ix                                          |

| LIST OF ABBREVIATIONS xii                                   |

| LIST OF SYMBOLS                                             |

| ABSTRAKxxiv                                                 |

| ABSTRACT                                                    |

| CHAPTER 1 INTRODUCTION1                                     |

| 1.1 General Overview1                                       |

| 1.2 Problem Statements                                      |

| 1.3 Objectives                                              |

| 1.4 Scope of Works                                          |

| 1.5 Contribution of Research                                |

| 1.6 Thesis Outline                                          |

| CHAPTER 2 LITERATURE REVIEW                                 |

| 2.1 Introduction                                            |

| 2.2 Software Defined Radio (SDR) Overview10                 |

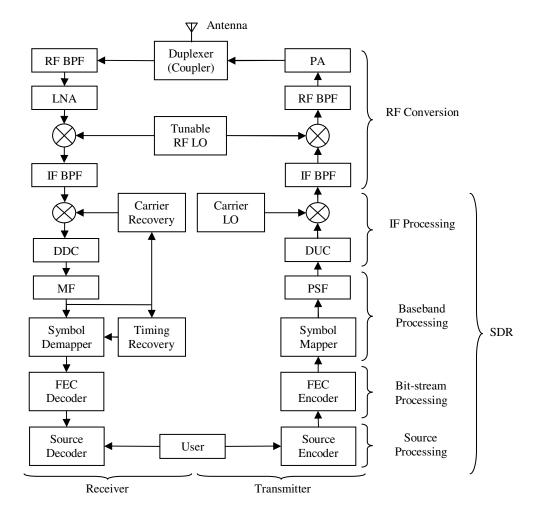

| 2.2.1 Functional Architecture of SDR11                      |

| 2.2.2 Baseband Processing Segment in SDR12                  |

| 2.2.3 Suitability of FPGA as Implementation Platform of SDR |

| 2.3 Digital Linear Modulations                              |

| 2.3.1 Pulse Amplitude Modulation (PAM)16                    |

| 2.3.2 Phase Shift Keying (PSK)                              |

| 2.3.3 Quadrature Amplitude Modulation (QAM)                 |

| 2.4                                                 | Digit  | al Pulse Shaping Filter (PSF)2                | 4  |

|-----------------------------------------------------|--------|-----------------------------------------------|----|

| 2.4.1 Raised Cosine (RC) Pulse Shaping Filter (PSF) |        | 4                                             |    |

| 2.4.2                                               |        | Digital Implementation of RC Filter2          | 9  |

| 2.5 Symbol Timing Recovery (STR)                    |        |                                               | 0  |

| 2.                                                  | 5.1    | Schemes of STR                                | 0  |

| 2.                                                  | 5.2    | Configurable STR                              | 3  |

| CHA                                                 | PTER   | 3 DESIGN CONCEPT                              | 5  |

| 3.1                                                 | Intro  | duction3                                      | 5  |

| 3.2                                                 | Finite | e Impulse Response (FIR) Filter               | 5  |

| 3.                                                  | 2.1    | Odd-Tap Symmetric Direct Form (DF) FIR Filter | 7  |

| 3.                                                  | 2.2    | Odd-Tap Symmetric Systolic FIR Filter         | 9  |

| 3.3                                                 | Samp   | ble Rate Conversion (SRC)4                    | 2  |

| 3.                                                  | 3.1    | Interpolation Filter                          | 3  |

| 3.                                                  | 3.2    | Polyphase Interpolator                        | 5  |

| 3.4                                                 | Gard   | ner Timing Error Detector (TED)4              | 7  |

| 3.5                                                 | Pseuc  | lo-Random (PR) Binary Number Generator4       | .9 |

| CHA                                                 | PTER   | 4 METHODOLOGY                                 | 1  |

| 4.1                                                 | Intro  | luction5                                      | 1  |

| 4.2                                                 | Instal | lation of Software Tools5                     | 3  |

| 4.3                                                 | High   | Level DSP Modeling                            | 4  |

| 4.                                                  | 3.1    | Signal Delay5                                 | 6  |

| 4.                                                  | 3.2    | Multi-Modulation Baseband Modulator (MMBM)5   | 9  |

|                                                     | 4.3.2  | 1 Auxiliary Blocks                            | 0  |

|                                                     | 4.3.2  | 2 Input and Output Blocks                     | 0  |

|                                                     | 4.3.2  | 3 PR Bit Generator Subsystem                  | 2  |

|                                                     | 4.3.2  | 4 Symbol Mapper Subsystem6                    | 3  |

|                                                     | 4.3.2  | .5 Interpolation Filter Subsystem             | 4  |

|                                                     | 4.     | 3.2.5.1 2xMA FIR Multi Interpolator Subsystem | 5  |

| 4   | .3.3  | Multi-   | Modulation Baseband Demodulator (MMBD)                 | 67 |

|-----|-------|----------|--------------------------------------------------------|----|

|     | 4.3.3 | .1 Au    | xiliary Blocks                                         |    |

|     | 4.3.3 | .2 Inp   | ut and Output Blocks                                   |    |

|     | 4.3.3 | .3 RR    | C Filter Subsystem                                     |    |

|     | 4.    | 3.3.3.1  | Multi Odd-Tap Systolic FIR Filter Subsystem            | 72 |

|     | 4.    | 3.3.3.2  | Reset Delay Subsystem                                  |    |

|     | 4.3.3 | .4 Tin   | ning Recovery Subsystem                                | 73 |

|     | 4.    | 3.3.4.1  | TED Subsystem                                          | 74 |

|     | 4.    | 3.3.4.2  | Search Min Error Subsystem                             | 76 |

|     | 4.    | 3.3.4.3  | Data and Timing Updates Subsystem                      | 77 |

|     | 4.    | 3.3.4.4  | Data Capture Subsystem                                 | 78 |

|     | 4.3.3 | .5 Syr   | nbol Demapper Subsystem                                | 79 |

|     | 4.3.3 | .6 Pul   | se Shaping Subsystem                                   | 80 |

| 4.4 | Com   | pilation | of HDL Netlists of DSP Models                          |    |

| 4.5 | HDL   | Design   | of Setup Configuration Module                          |    |

| 4   | .5.1  | Config   | gurations of ADC and DAC                               | 84 |

| 4   | .5.2  | Config   | guration of Clock Synthesizer                          | 87 |

| 4.6 | HDL   | Integra  | tion of DSP Models with Setup Configuration Module     |    |

| 4.7 | Synth | nesis of | HDL Integrated Modules                                 | 89 |

| 4.8 | FPG   | A Imple  | mentation of Synthesized Integrated Modules            |    |

| 4.9 | Hard  | ware Im  | plementation and Verification Using FPGA, ADC and DAC  | 91 |

| CHA | APTER | 5 RE     | SULTS AND DISCUSSIONS                                  | 94 |

| 5.1 | Intro | duction  |                                                        | 94 |

| 5.2 | Simu  | lation R | esults in Xilinx System Generator/Simulink Environment | 94 |

| 5   | .2.1  | Top Lo   | evel MMBM                                              |    |

| 5   | .2.2  | -        | evel MMBD                                              |    |

|     | .2.3  | _        | MMBMD                                                  |    |

|     | .2.4  |          | oped FPGA Utilization                                  |    |

|     |       |          |                                                        |    |

| 5.3                                             | Simul  | ation Results in ModelSim Environment105                 |

|-------------------------------------------------|--------|----------------------------------------------------------|

| 5.                                              | 3.1    | HDL Simulations of MMBM and MMBD Netlists105             |

| 5.                                              | 3.2    | HDL Simulation of Setup Configuration Module112          |

| 5.                                              | 3.3    | HDL Simulation of Integrated Modules114                  |

| 5.4                                             | Synth  | esis Results in Synplify Pro Environment120              |

| 5.5                                             | Repor  | ts Generated in Xilinx ISE Environment121                |

| 5.                                              | 5.1    | FPGA Device Utilization                                  |

| 5.                                              | 5.2    | Post PAR Static Timing Report                            |

| 5.                                              | 5.3    | Power Estimation Report                                  |

| 5.6                                             | Hardv  | vare Outputs during Program Running in FPGA127           |

| 5.                                              | 6.1    | Baseband Modulated Signals                               |

| 5.                                              | 6.2    | Smoothed Bit                                             |

| 5.7                                             | Effici | ency Evaluation of FPGA Utilization131                   |

| 5.                                              | 7.1    | Symbol Mapper and Demapper131                            |

| 5.                                              | 7.2    | Pulse Shaping Filter (PSF) and Matched Filter (MF)133    |

| 5.                                              | 7.3    | Symbol Timing Recovery (STR)                             |

| 5.                                              | 7.4    | Baseband Modulator (BM) and Demodulator (BD)139          |

| CHA                                             | PTER   | 6 CONCLUSION AND FUTURE WORKS141                         |

| 6.1                                             | Concl  | usion141                                                 |

| 6.2                                             | Future | e Works                                                  |

| REF                                             | ERENC  | CES                                                      |

| LIST                                            | OF PL  | JBLICATIONS                                              |

| APP                                             | ENDIX  | A In Depth DSP Models and Parameter SettingsA1           |

| APP                                             | ENDIX  | B Determination of Optimum Binary Points for DAC and ADC |

| APP                                             | ENDIX  | C Serial Programming Interface (SPI) Timing              |

| APPENDIX D Verilog Codes of Setup Configuration |        |                                                          |

| APP                                             | ENDIX  | E Verilog Codes of Integrated Module and Test-Fixture    |

## LIST OF TABLES

| Table 1.1:       Wireless Standards with Modulations and Data Rates (Rappaport, 2002) |

|---------------------------------------------------------------------------------------|

| Table 4.1:    Selection Values for Digital Modulation Scheme    55                    |

| Table 4.2: Delay Samples for Input Message Bit    57                                  |

| Table 4.3: Delay Samples for Symbol Integer    58                                     |

| Table 4.4:    Delay Samples for I/Q Symbols    58                                     |

| Table 4.5:    Latency of MMBM                                                         |

| Table 4.6:    Latency of Symbol Mapper Subsystem                                      |

| Table 4.7:    Design Parameters of Multi-Rate Interpolation Filter (MRIF)65           |

| Table 4.8: Design Parameters of Polyphase Interpolator of MRIF                        |

| Table 4.9:    Latency of MMBD    68                                                   |

| Table 4.10: Latency of RRC Filter Subsystem    71                                     |

| Table 4.11: Design Parameters of MOSSF                                                |

| Table 4.12: Latency of <i>Timing Recovery</i> Subsystem                               |

| Table 4.13: Latency of Symbol Demapper Subsystem                                      |

| Table 4.14: Design Parameters of RC Interpolation Filter (RCIF)                       |

| Table 4.15: Required Files Generated by System Generator Block                        |

| Table 4.16: Required Pins of ADS5500 ADC (Avnet, 2006; Texas Instruments, 2007)85     |

| Table 4.17: Required Pins of DAC5687 DAC (Avnet, 2006; Texas Instruments, 2005)85     |

| Table 4.18: SPI Codes for ADS5500 ADC (Texas Instruments, 2007)                       |

| Table 4.19: SPI Codes for DAC5687 DAC (Texas Instruments, 2005)                       |

| Table 4.20: Required Pins of ICS8442 Clock Synthesizer (Avnet Memec, 2005)87          |

| Table 5.1: Unmapped FPGA Utilization of MMBM103                                       |

| Table 5.2:    Unmapped FPGA Utilization of MMBD    103                                |

| Table 5.3:    Additional Files Required by Test-bench File                            |

| Table 5.4:    Simulation Timing of MMBM in ModelSim vs. Sys Gen                       |

| Table 5.5:       Simulation Timing of MMBD in ModelSim vs. Sys Gen                    |

| Table 5.6:       ADC/DAC Timing of Setup Configuration in ModelSim       113          |

| Table 5.7:  | Timing of Integrated Modules in ModelSim1                     | 19 |

|-------------|---------------------------------------------------------------|----|

| Table 5.8:  | Estimated Timing Report of Synthesis                          | 20 |

| Table 5.9:  | Device Utilization Summary of Integrated Module of MMBM12     | 21 |

| Table 5.10: | Device Utilization Summary of Integrated Module of MMBD       | 22 |

| Table 5.11: | FPGA Utilization of Configurable MMBM12                       | 23 |

| Table 5.12: | FPGA Utilization of Configurable MMBD12                       | 23 |

| Table 5.13: | Post-PAR Static Timing Report for Integrated Module of MMBM12 | 25 |

| Table 5.14: | Post-PAR Static Timing Report for Integrated Module of MMBD12 | 25 |

| Table 5.15: | Estimated Power Report for Integrated Modules                 | 26 |

| Table 5.16: | Comparison of Real-time and Simulation Results for MMBM12     | 28 |

| Table 5.17: | Comparison of Real-time and Simulation Results for MMBD       | 30 |

| Table 5.18: | Unmapped FPGA Utilization of Symbol Mapper12                  | 31 |

| Table 5.19: | Unmapped FPGA Utilization of Symbol Demapper1                 | 32 |

| Table 5.20: | Unmapped FPGA Utilization of PSF1                             | 33 |

| Table 5.21: | Unmapped FPGA Utilization of MF1                              | 33 |

| Table 5.22: | Unmapped FPGA Utilization of STR1                             | 36 |

| Table 5.23: | FPGA Utilizations of Proposed STR vs. Existing STR1           | 37 |

| Table 5.24: | Unmapped FPGA Utilization of BM1                              | 39 |

| Table 5.25: | Unmapped FPGA Utilization of BD                               | 39 |

## LIST OF FIGURES

| Figure 2.1:                                                                                                                                                       | Functional Architecture of SDR (Mitola, 1995)11                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

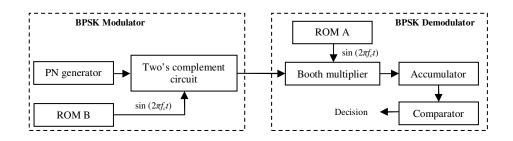

| Figure 2.2:                                                                                                                                                       | Simple BPSK Modem (Ahamed and Scarpino, 2005)19                                                                                                                                                                                                                                                                                                                          |

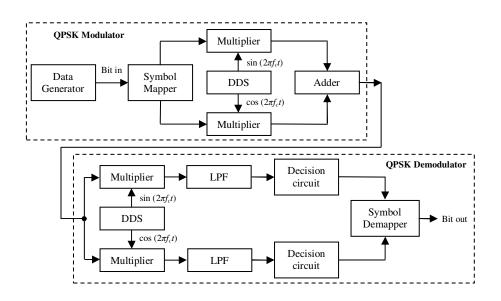

| Figure 2.3:                                                                                                                                                       | Simple QPSK Modem (Song and Yao, 2010)20                                                                                                                                                                                                                                                                                                                                 |

| Figure 2.4:                                                                                                                                                       | Spectrum of Rectangular Symbol Pulse (Gentile, 2002)25                                                                                                                                                                                                                                                                                                                   |

| Figure 2.5:                                                                                                                                                       | Frequency Responses of RC Filter and Rectangular Pulse (Gentile, 2002)26                                                                                                                                                                                                                                                                                                 |

| Figure 2.6:                                                                                                                                                       | Time Responses of RC Filter and Rectangular Pulse (Gentile, 2002)27                                                                                                                                                                                                                                                                                                      |

| Figure 2.7:                                                                                                                                                       | Architectures of Feedback STR. A: Synchronous (Sciagura et al., 2007);<br>B: Asynchronous (Jian et al., 2005)                                                                                                                                                                                                                                                            |

| Figure 2.8:                                                                                                                                                       | Architecture of Feedforward STR (Zhu et al., 2005)                                                                                                                                                                                                                                                                                                                       |

| Figure 2.7:                                                                                                                                                       | Configurable Multi-Symbol-Rate STR (Tachwali et al., 2009)34                                                                                                                                                                                                                                                                                                             |

| Figure 3.1:                                                                                                                                                       | Direct Form (DF) FIR Filter Structure (Oppenheim et al., 1999)                                                                                                                                                                                                                                                                                                           |

| Figure 3.2:                                                                                                                                                       | Odd-Tap Symmetric FIR Filter Structure (Oppenheim et al., 1999)38                                                                                                                                                                                                                                                                                                        |

| Figure 3.3:                                                                                                                                                       | Odd-Tap Transposed Symmetric FIR Filter Structure                                                                                                                                                                                                                                                                                                                        |

| Figure 3.4:                                                                                                                                                       | Odd-Tap Symmetric Systolic FIR Filter Structure (adapted from Xilinx,                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                   | 2008)                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 3.5:                                                                                                                                                       | 2008)                                                                                                                                                                                                                                                                                                                                                                    |

| -                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:                                                                                                                                                       | Interpolation (Hentschel, 2002)43                                                                                                                                                                                                                                                                                                                                        |

| Figure 3.6:<br>Figure 3.7:                                                                                                                                        | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:                                                                                                                         | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:                                                                                                          | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:                                                                                           | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:<br>Figure 4.3:                                                                            | Interpolation (Hentschel, 2002)43Polyphase Interpolator (adapted from Hentschel, 2002)46Gardner TED (Sciagura et al., 2007)47Linear-Feedback Shift Register (adapted from Cagigal and Bracho, 1986)50General Flow of Design and Implementation51Development Flow of Design and Implementation53                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:<br>Figure 4.3:<br>Figure 4.4:                                                             | Interpolation (Hentschel, 2002)43Polyphase Interpolator (adapted from Hentschel, 2002)46Gardner TED (Sciagura et al., 2007)47Linear-Feedback Shift Register (adapted from Cagigal and Bracho, 1986)50General Flow of Design and Implementation51Development Flow of Design and Implementation53DSP Model of MMBMD in Sys Gen/Simulink54                                  |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:<br>Figure 4.3:<br>Figure 4.4:<br>Figure 4.5:                                              | Interpolation (Hentschel, 2002)43Polyphase Interpolator (adapted from Hentschel, 2002)46Gardner TED (Sciagura et al., 2007)47Linear-Feedback Shift Register (adapted from Cagigal and Bracho, 1986)50General Flow of Design and Implementation51Development Flow of Design and Implementation53DSP Model of MMBMD in Sys Gen/Simulink54DSP Model of Signal Delay Block56 |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:<br>Figure 4.2:<br>Figure 4.3:<br>Figure 4.4:<br>Figure 4.5:<br>Figure 4.6:                | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 4.1:<br>Figure 4.2:<br>Figure 4.3:<br>Figure 4.3:<br>Figure 4.4:<br>Figure 4.5:<br>Figure 4.6:<br>Figure 4.7: | Interpolation (Hentschel, 2002)                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.10: DSP Model of 2xMA FIR Multi Interpolator Subsystem       | 66  |

|-----------------------------------------------------------------------|-----|

| Figure 4.11: DSP Model of MMBD in Sys Gen/Simulink                    | 67  |

| Figure 4.12: DSP Model of RRC Filter Subsystem                        | 70  |

| Figure 4.13: DSP Model of Multi Odd-Tap Systolic FIR Filter Subsystem | 72  |

| Figure 4.14: DSP Model of <i>Reset Delay</i> Subsystem                | 73  |

| Figure 4.15: DSP Model of <i>Timing Recovery</i> Subsystem            | 73  |

| Figure 4.16: DSP Model of <i>TED</i> Subsystem                        | 75  |

| Figure 4.17: DSP Model of Search Min Error Subsystem                  | 76  |

| Figure 4.18: DSP Model of <i>Data and Timing Updates</i> Subsystem    | 77  |

| Figure 4.19: DSP Model of <i>Data Capture</i> Subsystem               | 78  |

| Figure 4.20: DSP Model of Symbol Demapper Subsystem                   | 79  |

| Figure 4.21: DSP Model of <i>Pulse Shaping</i> Subsystem              | 80  |

| Figure 4.22: Settings of System Generator Block. A: MMBM; B: MMBD     | 82  |

| Figure 4.23: Hardware Implementation of FPGA and P240                 | 91  |

| Figure 4.24: Hardware Assembly for Testing and Measurement            | 93  |

| Figure 5.1: Simulation of <i>MMBM</i> in Sys Gen for BPSK             | 95  |

| Figure 5.2: Simulation of <i>MMBM</i> in Sys Gen for 4-PAM            | 96  |

| Figure 5.3: Simulation of <i>MMBM</i> in Sys Gen for QPSK             | 96  |

| Figure 5.4: Simulation of <i>MMBM</i> in Sys Gen for 16-QAM           | 97  |

| Figure 5.5: Simulation of <i>MMBD</i> in Sys Gen for BPSK             | 98  |

| Figure 5.6: Simulation of <i>MMBD</i> in Sys Gen for 4-PAM            | 99  |

| Figure 5.7: Simulation of <i>MMBD</i> in Sys Gen for QPSK             | 99  |

| Figure 5.8: Simulation of <i>MMBD</i> in Sys Gen for 16-QAM           | 100 |

| Figure 5.9: Simulation of Ideal MMBMD in Sys Gen for BPSK             | 101 |

| Figure 5.10: Simulation of Ideal MMBMD in Sys Gen for 4-PAM           | 101 |

| Figure 5.11: Simulation of Ideal MMBMD in Sys Gen for QPSK            | 102 |

| Figure 5.12: Simulation of Ideal MMBMD in Sys Gen for 16-QAM          | 102 |

| Figure 5.13: HDL Simulation of MMBM for BPSK                          | 106 |

| Figure 5.14: HDL Simulation of MMBM for 4-PAM                         | 106 |

| Figure 5.15: HDL Simulation of MMBM for QPSK                          | 107 |

| Figure 5.16: HDL Simulation of MMBM for 16-QAM1                                   | 07  |

|-----------------------------------------------------------------------------------|-----|

| Figure 5.17: HDL Simulation of MMBD for BPSK1                                     | 08  |

| Figure 5.18: HDL Simulation of MMBD for 4-PAM1                                    | 108 |

| Figure 5.19: HDL Simulation of MMBD for QPSK1                                     | 09  |

| Figure 5.20: HDL Simulation of MMBD for 16-QAM1                                   | 09  |

| Figure 5.21: HDL Simulation of Setup Configuration Module1                        | 12  |

| Figure 5.22: HDL Simulation of Integrated Module of MMBM for BPSK1                | 15  |

| Figure 5.23: HDL Simulation of Integrated Module of MMBM for 4-PAM1               | 15  |

| Figure 5.24: HDL Simulation of Integrated Module of MMBM for QPSK1                | 16  |

| Figure 5.25: HDL Simulation of Integrated Module of MMBM for 16-QAM1              | 16  |

| Figure 5.26: HDL Simulation of Integrated Module of MMBD for BPSK1                | 17  |

| Figure 5.27: HDL Simulation of Integrated Module of MMBD for 4-PAM1               | 17  |

| Figure 5.28: HDL Simulation of Integrated Module of MMBD for QPSK1                | 18  |

| Figure 5.29: HDL Simulation of Integrated Module of MMBD for 16-QAM1              | 18  |

| Figure 5.30: Real-time Results of MMBM. A: BPSK; B: 4-PAM; C: QPSK;<br>D: 16-QAM1 | 127 |

| Figure 5.31: Real-time Results of MMBD. A: BPSK; B: 4-PAM; C: QPSK;<br>D: 16-QAM1 | 129 |

## LIST OF ABBREVIATIONS

| AAF    | Anti-Aliasing Filter                     |

|--------|------------------------------------------|

| A/D    | Analog-to-Digital                        |

| ADC    | Analog-to-Digital Converter              |

| Addr   | Address                                  |

| AIF    | Anti-Imaging Filter                      |

| AMS    | Add-Multiply-Sum                         |

| ASICs  | Application Specific Integrated Circuits |

| ASK    | Amplitude Shift Keying                   |

| ASP    | Analog Signal Processing                 |

| ASR    | Addressable Shift Register               |

| BD     | Baseband Demodulator                     |

| BM     | Baseband Modulator                       |

| BPF    | Bandpass Filter                          |

| BPSK   | Binary Phase Shift Keying                |

| BRAMs  | Block Random Access Memories             |

| С      | Current (sample)                         |

| CDMA   | Code Division Multiple Access            |

| Coef   | Coefficient                              |

| Concat | Concatenate                              |

| DA     | Distributed Arithmetic                   |

| DAC    | Digital-to-Analog Converter              |

| DDC    | Digital Down Converter                   |

| DDS    | Direct Digital Synthesizer               |

| DF     | Direct Form                              |

| DLL   | Delay Locked Loop                                    |

|-------|------------------------------------------------------|

| DQPSK | Differentially-encoded Quadrature Phase Shift Keying |

| DRC   | Design Rule Check                                    |

| DSP   | Digital Signal Processing                            |

| DSPs  | Digital Signal Processors                            |

| DTFT  | Discrete-Time Fourier Transform                      |

| DUC   | Digital Up Converter                                 |

| Е     | Early (sample)                                       |

| EDIF  | Electronic Design Interchange Format                 |

| EMs   | Embedded Multipliers                                 |

| FEC   | Forward Error Correction                             |

| FFs   | Flip-Flops                                           |

| FFT   | Fast Fourier Transform                               |

| FIFO  | First-In-First-Out                                   |

| FIR   | Finite Impulse Response                              |

| FPGA  | Field Programmable Gate Array                        |

| FSK   | Frequency Shift Keying                               |

| Gen   | Generator                                            |

| GF(2) | Galois Field of 2 elements                           |

| GMSK  | Gaussian Minimum Shift Keying                        |

| GPPs  | General Purpose Processors                           |

| GUI   | Graphical User Interface                             |

| HDL   | Hardware Description Language                        |

| HEX   | HEXadecimal                                          |

| HSDPA | High-Speed Downlink Packet Access                    |

| Ι     | In-phase                                            |  |

|-------|-----------------------------------------------------|--|

| IF    | Intermediate Frequency                              |  |

| I/O   | Input / Output                                      |  |

| IOBs  | Input / Output Blocks                               |  |

| ISE   | Integrated Software Environment                     |  |

| ISI   | Inter-Symbol Interference                           |  |

| L     | Late (sample)                                       |  |

| LF    | Loop Filter                                         |  |

| LFSR  | Linear-Feedback Shift Register                      |  |

| LMS   | Least-Mean Square                                   |  |

| LNA   | Low Noise Amplifier                                 |  |

| LO    | Local Oscillator                                    |  |

| LP    | Linear Phase                                        |  |

| LPF   | Lowpass Filter                                      |  |

| LSB   | Least Significant Bit                               |  |

| LUTs  | Look-Up Tables                                      |  |

| LVTTL | Low Voltage Transistor-Transistor Logic             |  |

| MA    | Multiply-Add                                        |  |

| MAC   | Multiply-ACcumulate                                 |  |

| MF    | Matched Filter                                      |  |

| ML    | Maximum Likelihood                                  |  |

| MMBD  | Multi-Modulation Baseband Demodulator               |  |

| MMBM  | Multi-Modulation Baseband Modulator                 |  |

| MMBMD | Multi-Modulation Baseband Modulator and Demodulator |  |

| MOSSF | Multi-Odd-tap Symmetric Systolic Filter             |  |

- MRIF Multi-Rate Interpolation FilterMSB Most Significant BitMult MultiplierMux Multiplexer

- NCD Native Circuit Description

- NCO Numerically-Controlled Oscillator

- NGD Native Generic Database

- OQPSK Offset Quadrature Phase Shift Keying

- OS Operating System

- PA Power Amplifier

- PACE Pinout Area Constraints Editor

- PAM Pulse Amplitude Modulation

- PAR Place And Route

- PC Personal Computer

- PLL Phase-Locked Loop

- PN Pseudo-Noise

- PR Pseudo-Random

- PSF Pulse Shaping Filter

- PSK Phase Shift Keying

- Q Quadrature

- QAM Quadrature Amplitude Modulation

- QMC Quadrature Modulator Correction

- QoS Quality of Service

- QPSK Quadrature Phase Shift Keying

- RAMs Random Access Memories

RC **Raised Cosine** RCF **Re-Construction Filter** RCIF **Raised Cosine Interpolation Filter** RF Radio Frequency ROM Read-Only Memory RRC **Root-Raised Cosine** Software Defined Radio SDR SER Symbol Error Rate SFDR Spurious Free Dynamic Range **SNR** Signal-to-Noise Ratio SPI Serial Programming Interface SR Software Radio SRC Sample Rate Conversion STR Symbol Timing Recovery Sys System TDM **Time-Division Multiplexing** TED Timing Error Detector ΤI **Texas Instruments** UCF User Constraints File UMTS Universal Mobile Telecommunications System WCDMA Wideband Code Division Multiple Access **WLAN** Wireless Local Area Network Xilinx Synthesis Technology XST

## LIST OF SYMBOLS

| $A_i$                  | Signal amplitude of index <i>i</i>                                      |

|------------------------|-------------------------------------------------------------------------|

| $A_{i, I}$             | Signal amplitude in I channel                                           |

| $A_{i, Q}$             | Signal amplitude in Q channel                                           |

| $A_{sym}$              | Symbol amplitude                                                        |

| A <sub>sym, I</sub>    | Symbol amplitude in I channel                                           |

| $A_{sym, Q}$           | Symbol amplitude in Q channel                                           |

| $b_n$                  | Binary sequence at instant <i>n</i>                                     |

| $b_{n-\lambda}$        | Delayed binary sequence at instant $n - \lambda$ with $\lambda$ latency |

| $c_{\lambda}$          | Coefficient associated with $\lambda$ -latency binary sequence          |

| $C_{\sigma}$           | Filter coefficient for segment $\sigma$                                 |

| $C_{	au}$              | Filter coefficient at tap $\tau$                                        |

| $d_{ ho,\ i}$          | Output data in level $\rho$ for previous segment <i>i</i>               |

| $d_{ ho,\;\sigma}$     | Output data in level $\rho$ for segment $\sigma$                        |

| $d_I(mT_{sym})$        | Data samples in I channel at instant $m$ , symbol period $T_{sym}$      |

| $d_I[n]$               | Data samples in I channel at instant <i>n</i>                           |

| $d_Q(mT_{sym})$        | Data samples in Q channel at instant $m$ , symbol period $T_{sym}$      |

| $d_Q[n]$               | Data samples in Q channel at instant $n$                                |

| D <sub>1-2-split</sub> | Latency of 1-to-2 Splitter subsystem                                    |

| $D_{1-4-split}$        | Latency of 1-to-4 Splitter subsystem                                    |

| $D_{2-1-comb}$         | Latency of 2-to-1 Combiner subsystem                                    |

| $D_{2xMA}$             | Latency of 2xMultiply-Add subsystem                                     |

| D <sub>4-1-comb</sub>  | Latency of 4-to-1 Combiner subsystem                                    |

| $D_{4xMA}$             | Latency of 4xMultiply-Add subsystem                                     |

| $D_{add}$              | Latency of Add block (or adder)                                         |

|                        |                                                                         |

| $D_{add-mult}$         | Latency of Add-Multiply subsystem                                |  |

|------------------------|------------------------------------------------------------------|--|

| D <sub>AMS-A</sub>     | Latency of Add-Multiply-Sum A subsystem                          |  |

| D <sub>AMS-B</sub>     | Latency of Add-Multiply-Sum B subsystem                          |  |

| $D_{bit}$              | Latency for synchronizing input message and recovered bits       |  |

| D <sub>bit-comb</sub>  | Latency of Bit Combiner subsystem                                |  |

| $D_{capt}$             | Latency of Data Capture subsystem                                |  |

| $D_{ch}$               | Channel delay                                                    |  |

| $D_{ch1}$              | Channel delay in modulo symbol period $T_{sym}$                  |  |

| Dcompen                | Compensated channel delay                                        |  |

| $D_{ctrl}$             | Latency of Control subsystem                                     |  |

| $D_{ctrl1}$            | Latency of Controll subsystem                                    |  |

| $D_{CB}$               | Latency of Coef Buffer subsystem                                 |  |

| $D_{CB1}$              | Latency of Coef Buffer1 subsystem                                |  |

| D <sub>data-ctrl</sub> | Latency of Data Control subsystem                                |  |

| $D_{delay}$            | Latency of <i>Delay</i> block                                    |  |

| D <sub>demap</sub>     | Latency of Symbol Demapper subsystem (overall)                   |  |

| $D_{demap1}$           | Latency of Symbol Demapper subsystem (without TDM)               |  |

| $D_{DB}$               | Latency of Data Buffer subsystems                                |  |

| $D_{DB1}$              | Latency of Data Buffer1 subsystem                                |  |

| $D_{DTU}$              | Latency of Data and Timing Updates subsystem                     |  |

| $D_{gr}$               | Group delay of RRC filter                                        |  |

| $D_{gr1}$              | Group delay of RC filter                                         |  |

| D <sub>int</sub>       | Latency for synchronizing original and recovered symbol integers |  |

| D <sub>I-demap</sub>   | Latency of <i>I Demap</i> subsystem                              |  |

| D <sub>I-map</sub>     | Latency of I Map subsystem                                       |  |

|                        |                                                                  |  |

| $D_{IPF}$              | Latency of Interpolation Filter subsystem                         |  |

|------------------------|-------------------------------------------------------------------|--|

| D <sub>IQ-in</sub>     | Initial delay of peak of I/Q input signal                         |  |

| $D_{map}$              | Latency of Symbol Mapper subsystem                                |  |

| $D_{mult}$             | Latency of <i>Mult</i> block (or multiplier)                      |  |

| D <sub>mult</sub> -sum | Latency of Multiply-Sum subsystem                                 |  |

| D <sub>MOSSF</sub>     | Latency of Multi Odd-Tap Systolic FIR Filter subsystem (or MOSSF) |  |

| D <sub>MRIF</sub>      | Latency of 2xMA FIR Multi Interpolator subsystem (or MRIF)        |  |

| D <sub>PRBG</sub>      | Latency of PR Bit Generator subsystem                             |  |

| $D_{PS}$               | Latency of Pulse Shaping subsystem                                |  |

| $D_{Q\text{-}demap}$   | Latency of <i>Q Demap</i> subsystem                               |  |

| $D_{Q-map}$            | Latency of <i>Q Map</i> subsystem                                 |  |

| D <sub>recov</sub>     | Latency of Timing Recovery subsystem                              |  |

| D <sub>RCIF</sub>      | Latency of 4xMA FIR Interpolator subsystem (or RCIF)              |  |

| $D_{RRC}$              | Latency of RRC Filter subsystem                                   |  |

| D <sub>set-0</sub>     | Latency of Set Zero subsystem                                     |  |

| $D_{symb}$             | Latency for synchronizing original and recovered I/Q symbols      |  |

| D <sub>SME</sub>       | Latency of Search Min Error subsystem                             |  |

| D <sub>TED</sub>       | Latency of TED subsystem                                          |  |

| $D_I(z)$               | Z-transform of data samples $d_I[n]$ in unit cycle z              |  |

| $D_Q(z)$               | Z-transform of data samples $d_Q[n]$ in unit cycle z              |  |

| е                      | Timing error                                                      |  |

| $e_{min}$              | Minimum timing error                                              |  |

| $e(mT_{sym})$          | Timing error at instant $m$ , symbol period $T_{sym}$             |  |

| <i>e</i> [ <i>n</i> ]  | Timing error at instant <i>n</i>                                  |  |

| E(z)                   | Z-transform of timing error $e[n]$ in unit cycle $z$              |  |

| f                           | Frequency                                                               |  |

|-----------------------------|-------------------------------------------------------------------------|--|

| $f_c$                       | Carrier frequency                                                       |  |

| $f_{co}$                    | Cut-off frequency                                                       |  |

| $f_N$                       | Nyquist frequency                                                       |  |

| $f_s$                       | Sampling frequency or sample rate                                       |  |

| $f_{s1}$                    | Input (lower) sampling frequency or rate                                |  |

| $f_{s2}$                    | Output (higher) sampling frequency or rate                              |  |

| f(x)                        | Polynomial function in terms of <i>x</i>                                |  |

| $G_{ch}$                    | Channel gain                                                            |  |

| $h(nT_{s2})$                | Impulse response at instant $n$ , sampling period $T_{s2}$              |  |

| h[n]                        | Impulse response at instant n                                           |  |

| $h_{RC}(t)$                 | Impulse response of RC filter at time <i>t</i>                          |  |

| $h_{RRC}(t)$                | Impulse response of RRC filter at time t                                |  |

| $H(e^{j2\pi fTs^2})$        | DTFT of signal $h(nT_{s2})$ in frequency $f$ , sampling period $T_{s2}$ |  |

| H(z)                        | System function in unit cycle $z$                                       |  |

| $H_{DF}(z)$                 | System function of DF FIR filter in unit cycle $z$                      |  |

| $H_{S}(z)$                  | System function of systolic FIR filter in unit cycle $z$                |  |

| $H_{RC}\left(\omega\right)$ | Frequency response of RC filter in radian frequency $\omega$            |  |

| $H_{RRC}\left(\omega ight)$ | Frequency response of RRC filter in radian frequency $\omega$           |  |

| Int                         | Symbol integers                                                         |  |

| k                           | Number of bits                                                          |  |

| $K_i$                       | Integral gain                                                           |  |

| $K_p$                       | Proportional gain                                                       |  |

| L                           | Upsampling (oversampling) factor or interpolation rate                  |  |

| т                           | Sampling instant at lower sampling rate; symbol instant                 |  |

| М                       | Filter order; number of shift register stages; degree of binary sequence |  |

|-------------------------|--------------------------------------------------------------------------|--|

| $M_{DIP}$               | 9-bit value of the first black DIP switch                                |  |

| $M_o$                   | Modulation order                                                         |  |

| n                       | Sampling instant at higher or single sampling rate; timing index         |  |

| <i>n<sub>capt</sub></i> | Capture instant                                                          |  |

| $n_{lim1}$              | Lower limit of timing index                                              |  |

| n <sub>lim2</sub>       | Upper limit of timing index                                              |  |

| n <sub>lock</sub>       | Locking instant                                                          |  |

| non                     | On-state timing for valid triggering of update loading                   |  |

| <i>n</i> <sub>opt</sub> | Optimum sampling instant                                                 |  |

| n <sub>reload</sub>     | Reload instant                                                           |  |

| <i>n<sub>upd</sub></i>  | Updated timing index                                                     |  |

| Ν                       | Filter length or filter taps                                             |  |

| N <sub>DIP</sub>        | 2-bit value of the second black DIP switch                               |  |

| $N_o$                   | Optimized filter taps                                                    |  |

| $N_s$                   | Segmented filter taps                                                    |  |

| N <sub>sym</sub>        | Offset symbol period or interval                                         |  |

| <i>OV</i> <sub>th</sub> | Over-threshold state                                                     |  |

| 0                       | Over filter phase taps                                                   |  |

| p(t)                    | Pulse waveform at time t                                                 |  |

| $p_{rect}(t)$           | Rectangular pulse waveform at time <i>t</i>                              |  |

| $ P_H $                 | Absolute value (or modulus) of higher pulse peak                         |  |

| $ P_L $                 | Absolute value (or modulus) of lower pulse peak                          |  |

| q                       | Filter phase taps or number of taps in each phase sub-filter             |  |

| $q_o$                   | Optimized filter phase taps                                              |  |

|                         |                                                                          |  |

| R                       | Sample rate-change factor                                                   |  |

|-------------------------|-----------------------------------------------------------------------------|--|

| $R_b$                   | Bit rate                                                                    |  |

| <b>R</b> <sub>sym</sub> | Symbol rate                                                                 |  |

| $s_i(t)$                | Signal waveform of index <i>i</i> at time <i>t</i>                          |  |

| S <sub>sym</sub>        | Number of samples per symbol                                                |  |

| S <sub>sync</sub>       | Synchronous state of stable optimum sampling instant $n_{opt}$              |  |

| t                       | Time                                                                        |  |

| $t_p$                   | Pulse interval                                                              |  |

| $t_{p(min)}$            | Minimum pulse interval                                                      |  |

| $T_b$                   | Bit period or interval                                                      |  |

| $T_{b1}$                | First bit interval                                                          |  |

| $T_R$                   | Period of linear recurring sequence $b_n$                                   |  |

| $T_s$                   | Sampling period or interval, or unit sample time                            |  |

| $T_{s1}$                | Input (higher) sampling period or interval                                  |  |

| $T_{s2}$                | Output (lower) sampling period or interval                                  |  |

| T <sub>sym</sub>        | Symbol period or interval                                                   |  |

| U                       | Downsampling factor or decimation rate                                      |  |

| <i>v<sub>init</sub></i> | Initial condition                                                           |  |

| $w(nT_{s2})$            | Discrete-time intermediate signal at instant $n$ , sampling period $T_{s2}$ |  |

| $W(e^{j2\pi fTs2})$     | DTFT of signal $w(nT_{s2})$ in frequency $f$ , sampling period $T_{s2}$     |  |

| x(t)                    | Analog or continuous-time input signal at time t                            |  |

| $x(mT_{s1})$            | Discrete-time input signal at instant $m$ , sampling period $T_{s1}$        |  |

| x[n]                    | Discrete-time input signal at instant <i>n</i>                              |  |

| $X(e^{j2\pi fTs1})$     | DTFT of signal $x(mT_{s1})$ in frequency $f$ , sampling period $T_{s1}$     |  |

| y(t)                    | Analog or continuous-time output signal at time t                           |  |

|                         |                                                                             |  |

| $y(nT_{s2})$          | Discrete-time output signal at instant $n$ , sampling period $T_{s2}$                      |

|-----------------------|--------------------------------------------------------------------------------------------|

| $y_{\phi} (mT_{s1})$  | Discrete-time output signal of phase $\phi$ at instant <i>m</i> , sampling period $T_{s1}$ |

| <i>y</i> [ <i>n</i> ] | Discrete-time output signal at instant <i>n</i>                                            |

| $y_{\sigma}[n]$       | Discrete-time output signal for segment $\sigma$ at instant $n$                            |

| $Y(e^{j2\pi fTs^2})$  | DTFT of signal $y(nT_{s2})$ in frequency $f$ , sampling period $T_{s2}$                    |

| Z.                    | Unit cycle dimension, equivalent to $e^{j\omega}$                                          |

| α                     | Roll-off factor                                                                            |

| β                     | Shape parameter for Kaiser window method                                                   |

| $\delta[n]$           | Unit sample (or impulse) sequence at instant $n$                                           |

| $\Delta t$            | Time difference between cursors 1 and 2 in oscilloscope display                            |

| $	heta_0$             | Phase offset                                                                               |

| λ                     | Index of shift register stage; latency in LFSR                                             |

| μ                     | Scaling factor                                                                             |

| ρ                     | Level index of filter structure                                                            |

| σ                     | Filter segment index                                                                       |

| τ                     | Filter tap index                                                                           |

| $	au_p$               | Polyphase filter tap index                                                                 |

| χ                     | Filter segments                                                                            |

| ω                     | Radian frequency                                                                           |

| $\omega_{co}$         | Cut-off radian frequency                                                                   |

| $\omega_p$            | Passband radian frequency                                                                  |

| $\omega_s$            | Stopband radian frequency                                                                  |

| ø                     | Filter phase index                                                                         |

| Øs                    | Sampling phase                                                                             |

# REKABENTUK PEMODULAT DAN PENYAHMODULAT JALUR-DASAR PELBAGAI-MODULASI BAGI RADIO TERTAKRIF PERISIAN

### ABSTRAK

Berlainan daripada radio berasaskan perkakasan yang hanya menyampaikan satu perkhidmatan komunikasi menggunakan piawaian tertentu, radio tertakrif perisian (SDR) menawarkan pelantar yang amat boleh-dikonfigurasi-semula untuk menyepadukan pelbagai fungsi bagi sistem komunikasi wayarles yang pelbagaimodulasi, pelbagai-jalur dan pelbagai-piawaian. Tetapi, projek ini hanya berdasarkan SDR pelbagai-modulasi, iaitu 4-PAM, BPSK, QPSK dan 16-QAM. Pemodulat (MMBM) dan penyahmodulat (MMBD) jalur-dasar pelbagai-modulasi yang bolehdikonfigurasi direkabentuk dengan menggunakan algoritma pemprosesan isyarat digit (DSP) berdasarkan ciri-ciri umum yang dikongsi oleh struktur-struktur satumodulasi, dan seterusnya dilaksanakan dalam FPGA Virtex-4 Xilinx. Perbandingan keputusan masa nyata dan simulasi menunjukkan bahawa pemasaan adalah setara, dan perubahan tanda dan magnitud adalah ketara. Tambahan pula, sekurangkurangnya 17% penggunaan FPGA telah dijimat bagi MMBM dan MMBD yang boleh-dikonfigurasi tersebut berbanding dengan pemodulat and penyahmodulat jalurdasar berkumpulan-modulasi masing-masing, yang diubahsuai daripada kerja-kerja terdahulu. Di samping itu, penukar digit-ke-analog (DAC) dan penukar analog-kedigit (ADC) boleh ditukar untuk aplikasi lain dengan menyepadukan konfigurasi persediaan bagi DAC dan ADC ke dalam MMBM dan MMBD yang bolehdikonfigurasi tersebut masing-masing. Selain itu, MMBM dan MMBD yang bolehdikonfigurasi tersebut boleh diubahsuai selanjutnya untuk merangkumi modulasi PSK, PAM dan QAM yang M-ary lebih tinggi.

# DESIGN OF MULTI-MODULATION BASEBAND MODULATOR AND DEMODULATOR FOR SOFTWARE DEFINED RADIO

## ABSTRACT

In contrast to hardware-based radio that only delivers single communication service using particular standard, the software defined radio (SDR) provides a highly reconfigurable platform to integrate various functions for multi-modulation, multiband and multi-standard wireless communication systems. However, this project is only based on multi-modulation SDR, such as 4-PAM, BPSK, QPSK and 16-QAM. The configurable multi-modulation baseband modulator (MMBM) and demodulator (MMBD) are designed using digital signal processing (DSP) algorithms based on common features shared by single-modulation structures, and then implemented into Xilinx Virtex-4 FPGA. Comparing the real-time and simulation results shows that the timings are equivalent, and the sign and magnitude changes are significant. Furthermore, at least 17% FPGA utilizations have been saved for the configurable MMBM and MMBD as compared to the grouped-modulation baseband modulator and demodulator respectively, which are modified from the previous works. Moreover, digitalto-analog converter (DAC) and analog-to-digital converter (ADC) can be changed for different applications by integrating setup configuration for DAC and ADC into the configurable MMBM and MMBD respectively. Besides, the configurable MMBM and MMBD can be further modified to include higher M-ary modulations of PSK, PAM and QAM.

#### **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 General Overview

Multi-modulation is one of the multi functionalities applicable to software defined radio (SDR) in wireless communication systems besides multi-standard and multi-band functionalities. The multi modulations used in the project of this thesis are pulse amplitude modulation (PAM), binary phase shift keying (BPSK), quadrature phase shift keying (QPSK) and quadrature amplitude modulation (QAM). The digital amplitude modulation is PAM, digital phase modulations are BPSK and QPSK, and digital amplitude-phase modulation is QAM. The exclusion of digital frequency modulation such as frequency shift keying (FSK) and Gaussian minimum shift keying (GMSK), is because of nonlinear modulation scheme whereas the PAM, PSK and QAM are linear modulation schemes (Proakis and Salehi, 2008).

The configurable multi-modulation baseband modulator (MMBM) and demodulator (MMBD) for SDR is developed by using digital signal processing (DSP) algorithms, and is highly dependent on the common features as stated below:

- a) Schemes of digital amplitude, phase and amplitude-phase modulations for symbol mapper and demapper.

- b) Filter design parameters, coefficients and structures for pulse shaping filter (PSF) and matched filter (MF).

- c) Detection of timing error (*e*) and acquisition of optimum sampling instant ( $n_{opt}$ ) for symbol timing recovery (STR).

The operations and implementations of symbol mapper and demapper, PSF, MF and STR in baseband modulation and demodulation, will be presented and described in detailed in Chapters 2 to 4.

Due to continuous-time radio frequency (RF) signal still remains prominence in propagating through air interface (channel), the conversions between continuoustime and discrete-time domains using analog-to-digital converter (ADC) and digitalto-analog converter (DAC), have become an important implementation issue, in order to optimize the performance of data sampling in terms of bandwidth, signal-tonoise ratio (SNR), precision, and timing constraints (Friedman, 1990; Harris, 1998; Walden, 1999). Therefore, effective signal transformations are required before and after field programmable gate array (FPGA) by using ADC and DAC respectively. Ignoring the implementation issues of interfacing FPGA with ADC and DAC would possibly cause undesired data losses before and after processing of FPGA respectively, and adversely affect the overall system performance. Therefore, setup configuration module is also proposed for configuring ADC and DAC as well as FPGA onboard clock synthesizer, in order to avoid the undesired data losses.

The configurable MMBM and MMBD together with the setup configuration module are implemented using Xilinx Virtex-4 FPGA MB Board and P240 Analog Module (ADC and DAC). The model name of Xilinx Virtex-4 FPGA is xc4vsx35-10ff668. The ADC and DAC contained in P240 Analog Module are Texas Instruments (TI) ADS5500 (14-bit, 125 MSps) and TI dual-channel DAC5687 (16bit, 500 MSps, 2x-8x interpolation) respectively.

#### **1.2 Problem Statements**

Wireless communications have become pervasive since the past two decades, such as universal mobile telecommunications system (UMTS) and wireless local area network (WLAN) (Rappaport, 2002). The rapid growth of wireless communication systems has led to the development of newer wireless systems and standards for high speed data services and voice calls. Traditional hardware-based radio deliver only single communication service using particular standard and cannot support multistandard wireless communication system due to its limited cross-functionality. Moreover, its upgrade via physical intervention would result in high development and production costs. However, the emerging software radio (SR) and software defined radio (SDR) has overcome the problems by providing re-configurability and programmability of different physical layer functions in one piece of hardware with lower costs (Mitola, 1995; Software Defined Radio Forum, 2009).

The SDR concept employs intensively the DSP techniques to perform signal processing tasks which are traditionally performed by the analog components in transmitter and receiver (Mitola, 1995; Harris 1998). The DSP advantages of low complexity, high configurability, high speed, small size, low power consumption, low development time and low production cost, have become keys for substituting the sophisticated analog signal processing (ASP) (Mitola, 1995; Harris, 1998; Oppenheim and Schafer, 1999). However, the scalability, flexibility and multifunctionality of SDR would require complicated DSP-based signal processing tasks, thus leading to the issues of hardware and timing constraints in the implementation platform of SDR (Baines, 1995; Cummings, 2004).

Multi wireless standards are associated with different digital modulations and data rates (in chips or bits per second) as listed in Table 1.1 (Rappaport, 2002). Thus, a SDR platform with integration of different modulations and data rates can be reused for multi standards and would save considerable development time and costs (Hatai and Chakrabarti, 2010). However this would increase the complexity of SDR, thus larger size and higher power consumption. Therefore, a novel compression technique with optimization for the integration is proposed in this thesis.

Table 1.1: Wireless Standards with Modulations and Data Rates (Rappaport, 2002)

| Standard          | Modulation      | Data Rate   |

|-------------------|-----------------|-------------|

| CDMA2000          | BPSK, QPSK      | 1.2288 Mcps |

| WCDMA             | QPSK, 16-QAM    | 3.84 Mcps   |

| HSDPA             | QPSK, 16-QAM    | 3.6 Mbps    |

| IEEE802.11 (WLAN) | QPSK, 16/64-QAM | 12 Mbps     |

## 1.3 Objectives

The aim of this thesis is to design multi-modulation baseband modulator (MMBM) and demodulator (MMBD) for software defined ratio (SDR). To achieve the aim, several objectives have to be fulfilled such as stated below:

- To design and simulate MMBM and MMBD with configurable-modulations of BPSK, 4-PAM, QPSK and 16-QAM.

- 2. To design and simulate setup configuration module for configuring ADC, DAC and FPGA onboard clock synthesizer.

- 3. To implement the integrated modules of MMBM and MMBD (with setup configuration) into FPGA devices with ADC and DAC.

- 4. To analyze system performances of configurable MMBM and MMBD in terms of timings, pulse peaks, and FPGA utilization.

#### 1.4 Scope of Works

The works in this thesis focus on the designs of: digital signal processing (DSP) models of multi-modulation baseband modulator (MMBM) and demodulator (MMBD); setup configuration module for ADC, DAC and FPGA onboard clock synthesizer; and the integrated modules of MMBM and MMBD (with setup configuration).

The first design is to develop a combination of pseudo-random (PR) bit generator, symbol mapper and root-raised cosine (RRC) pulse shaping filter (PSF), and a combination of RRC matched filter (MF), symbol timing recovery (STR), symbol demapper and raised cosine (RC) PSF, as the DSP models of MMBM and MMBD respectively, with configurable-modulations of BPSK, 4-PAM, QPSK and 16-QAM. The design includes simulations of models and hardware description language (HDL) Verilog codes, in Xilinx System Generator/Simulink and ModelSim environments respectively, and comparison between both results in term of timing.

The second design is to develop a combination of configurations of ADC, DAC and FPGA onboard clock synthesizer as setup configuration module. The design includes simulation of HDL Verilog codes in ModelSim environment and verification of serial programming interface (SPI) timing characteristics.

The third design is to develop the integration of DSP model of MMBM (and MMBD) with setup configuration module as the integrated module of MMBM (and MMBD respectively). The design includes simulation of HDL Verilog codes,

synthesis and implementation in ModelSim, Synplify Pro and Xilinx ISE environments respectively. The real-time implementation results are compared with the simulation results in terms of pulse interval and pulse peaks, in order to prove that the thesis objectives are satisfied.

## **1.5** Contribution of Research

The main contributions of this thesis are stated as below:

- The development of baseband modulator (BM) and demodulator (BD) with configurability of multi digital amplitude and/with phase modulations such as BPSK, 4-PAM, QPSK and 16-QAM, which expands the software defined radio (SDR) applications.

- 2. The development of pulse-shaping filter (PSF) with configurability of multi interpolation rate (*L*) corresponding to the selected digital modulation, which reduce complexity of sample rate conversion (SRC) in multi-rate processing.

- 3. The improvement of the efficiencies of configurable multi-modulation baseband modulator (MMBM) and demodulator (MMBD) to reduce hardware size or FPGA utilization, thus leading to lower power consumption.

- 4. The development of setup configuration module for analog-to-digital converter (ADC) and digital-to-analog converter (DAC), which offers configurability and changeability of ADC and DAC in order to interface with various analog signals for various applications of communication systems.

#### **1.6 Thesis Outline**

**Chapter 1:** General overview of this thesis, problem statements, objectives, scope of works and contribution of thesis, are presented.

**Chapter 2:** Literature review starts with software defined radio (SDR) concept including functional architecture and implementation platform. The second section is basics of digital linear modulation (PAM, PSK and QAM) and the recent researches using FPGA. The third section is theory and implementation of raised cosine (RC) pulse shaping filter (PSF). The last section is schemes of symbol timing recovery (STR), and the recent researches of STR.

**Chapter 3:** Design concept elaborates implementation techniques, starting with theory and structures of finite impulse response (FIR) filter. The second section is theory and polyphase architecture of interpolation filter in sample rate conversion (SRC). The third section is theory and structure of Gardner timing error detector (TED). The last section is theory and structure of pseudo-random (PR) bit generator.

**Chapter 4:** The first section is development flow of design and implementation of multi-modulation baseband modulator (MMBM) and demodulator (MMBD) for SDR. The second section is the required software and versions. The third until eighth sections are: development of DSP models of *MMMM* and *MMBD* then compiled as HDL netlists using Xilinx System Generator/Simulink software; HDL design of setup configuration module for ADC, DAC and clock synthesizer, and its integration with the DSP models using ModelSim software; synthesis and implementation of the

integrated module of MMBM (and MMBD) using Synplify Pro and Xilinx ISE software respectively. The last section is hardware implementation and verification of the integrated modules of MMBM and MMBD using FPGA, ADC and DAC.

**Chapter 5:** Initially, simulation results of DSP models run in System Generator (Sys Gen) are discussed and compared to verify functionality. In the second section, HDL simulation results run in ModelSim are analyzed and compared with the Sys Gen simulation results in term of timing for overall behavioral verification. The third section is verification of timing constraints with estimated timing after synthesis of the integrated modules using Synplify Pro. The fourth section is FPGA performances for implementing the integrated modules using ISE, in terms of device utilization, speed and power consumption. In the fifth section, real-time results are compared with the simulation results in terms of pulse interval and peaks for verifying system functionality. In the last section, efficiencies of symbol mapper, symbol demapper, PSF, matched filter (MF), STR, MMBM and MMBD are evaluated in term of FPGA utilization.