# DESIGN OF TUNABLE SINGLE BAND AND CONCURRENT LOW NOISE

### AMPLIFIER

by

# HAMIDREZA AMERI ESHGHABADI

Thesis submitted in fulfillment of the requirements

for the degree of

**Master of Science**

November 2015

#### ACKNOWLEDGMENTS

It is my great pleasure to express my deepest gratitude to everyone who supported me throughout this research. Undoubtedly, it was impossible to finish the thesis without their warm helps, unsparing guidance, and illuminating advices.

First and foremost, I wish to express my deepest sincere, regards and thanks to my supervisor, Dr. Mohd Tafir Mustaffa, for his excellent guidance, invaluable suggestions, and consistent encouragement during my Master study. Despite of the troubles of having a part-time student, he accepted me with opened-arms and motivated me to further my studies beside my career in industry. His trust and confidence in me along with his conscientiously guidance shaped any achieved success of this work. It was my great pleasure to have the opportunity to know him and work under his supervision.

I would like to extend my deepest appreciation to Dr. Norlaili Mohd Noh, and Dr. Asrulnizam Abd Manaf as the members of AISDe, for conducting the fruitful discussions on LNA design and to prepare the facilities of this research work as well as their kind supports during my study.

Also, I would like to thank the staffs of microelectronic design excellence centre (*CEDEC*) at USM who supported me during this research. Without their helps, it was not possible to conduct the on-die measurements of the fabricated LNAs easily. I would like to mention: Mr. Shukri Korakkottil Kunhi Mohd, Mr. Mohd Hasnirol Baharom, Mr. Mohd Kusairay Musa, Ms. Nuha A.Rhaffor, Mr. Ruhaifi Abdullah Zawawi and Mr. Mohd Fazlan Md. Radzi. Moreover, I cannot forget the opportunity of fabrication with Silterra (M) Sdn.Bhd. and the supports from Mr. Yusman Mohd. Yusof (Manager), Mr. Shahrolhafiz Sayed Ibrahim (Senior Engineer2), Dr. Subhash Chander Rustagi (Senior Manager), and Mr. Mohd Hafis Mohd Ali (Engineer).

I would like to thanks my good friends, Mr. Farshad Eshghabadi and Ms. Fatemeh Banitorfian, for sharing their illuminating ideas on LNA design with me. Also Farshad helped me a lot during the design, tape-out, and measurement of all three fabricated LNAs. Furthermore, I wish to appreciate Ms. Awatif Amir's supports during the tape-out and measurement of the LNAs in both Silterra and CEDEC labs.

I would like to extend my gratitude to Dr. Vahid Toosi, the founder and CEO of SiTune.Corp who gave me the opportunity to further my studies in RF design. Also, I wish to thank Dr. Saeid Mehrmanesh, the director of RFIC team at SiTune.Corp for his invaluable comments on the LNA design.

Above all, I am blessed with such a caring family. I extend my deepest gratitude to my wife and my parents, for their love, motivations, encouragements, and supports. This accomplishment would not have been possible without them.

Special acknowledgments to Universiti Sains Malaysia Research University (RU) grant No. 1001/PELECT/814107 as well as the short term research grant No. 304/PELECT/60311021 for financial support of this research.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS       | ii   |

|-----------------------|------|

| TABLE OF CONTENTS     | iv   |

| LIST OF FIGURES       | viii |

| LIST OF TABLES        | xii  |

| LIST OF ABBREVIATIONS | xiii |

| ABSTRAK               | XV   |

| ABSTRACT              | xvii |

# **CHAPTER 1: INTRODUCTION**

| 1.1 Introduction to Wireless Standards | 1 |

|----------------------------------------|---|

| 1.2 Motivations on LNA Design          | 4 |

| 1.3 Problem Statement                  | 5 |

| 1.4 Research Objectives                | 6 |

| 1.5 Scope of Work                      | 6 |

| 1.6 Contributions                      | 7 |

| 1.7 Organization of the Thesis         | 8 |

## **CHAPTER 2: BACKGROUND OF STUDY**

| 2.1 Introduction                    | 9  |

|-------------------------------------|----|

| 2.2 ISD Cascode Topology            | 9  |

| 2.3 S-Parameters                    | 13 |

| 2.4 Linearity                       | 14 |

| 2.5 Noise                           | 14 |

| 2.5.1 Noise Optimization Techniques | 15 |

| 2.6 Summary                         | 22 |

# **CHAPTER 3: LITERATURE REVIEW**

| 3.1 LNA Designs       | 23 |

|-----------------------|----|

| 3.1.1 Multiband LNAs  | 23 |

| 3.1.2 Wide-band LNAs  | 27 |

| 3.1.3 Tunable LNAs    | 32 |

| 3.1.4 Concurrent LNAs | 36 |

| 3.2 Summary           | 42 |

## **CHAPTER 4: DESIGN METHODOLOGY**

| 44 |

|----|

| 45 |

| 47 |

| 48 |

| 49 |

| 52 |

| 55 |

| 58 |

| 59 |

| 65 |

| 66 |

| 67 |

| 70 |

| 72 |

| 74 |

|    |

# **CHAPTER 5: RESULT AND DISCUSSION**

| 5.1 Introduction                                 | 75 |

|--------------------------------------------------|----|

| 5.2 PCSNIM ISD Cascode with Gain Enhancer (LNA1) | 76 |

| 5.2.1 LNA1 Simulation Results                              | 76  |

|------------------------------------------------------------|-----|

| 5.2.2 LNA1 Measurement Results                             | 80  |

| 5.2.3 Discussion of LNA1 Results                           | 83  |

| 5.3 Tunable 2.45 GHz LNA with Programmable Gain (LNA2)     | 86  |

| 5.3.1 LNA2 Simulation Results                              | 87  |

| 5.3.2 LNA2 Measurement Results                             | 95  |

| 5.3.3 Discussion of LNA2 Results                           | 100 |

| 5.4 Dual-band (2.45/5.2 GHz) Concurrent LNA (LNA3)         | 102 |

| 5.4.1 LNA3 Pre-layout Simulation Results                   | 103 |

| 5.4.2 LNA3 Post-layout Simulation Results                  | 105 |

| 5.4.3 LNA3 Measurement Results                             | 107 |

| 5.4.4 Discussion of LNA3 Results                           | 111 |

| 5.5 Tunable Dual-band (2.45/5.2 GHz) Concurrent LNA (LNA4) | 114 |

| 5.5.1 LNA4 Pre-Layout Simulation Results                   | 114 |

| 5.5.2 Discussion of LNA4 Results                           | 118 |

| 5.6 Comparison on the Results of Designed LNAs             | 119 |

| 5.6.1 Comparison Based on Gain Performance                 | 120 |

| 5.6.2 Comparison of Noise Performances                     | 120 |

| 5.6.3 Comparison in Terms of Input/Output Matching         | 121 |

| 5.7 Comparison with Previous Works                         | 121 |

| 5.8 Summary                                                | 123 |

| CHAPTER 6: CONCLUSIONS                                     |     |

| 6.1 Summary and Achievements of the Research               | 124 |

| 6.2 Recommendation for Future Works                        | 121 |

| LIST OF PUBLICATIONS                                       | 120 |

| REFERENCES                                                 | 127 |

| APPENDICES                                                 | 123 |

|                                                            | 155 |

**Appendix A: LNA Performance Parameters**

**Appendix B: NMOS Varactors**

Appendix C: RF Analyses and Simulations Set Ups

Appendix D: Measurement Set Ups

Appendix E: Calculations of Concurrent Load Circuit

## LIST OF FIGURES

|                                                                                    | Page |

|------------------------------------------------------------------------------------|------|

| Figure 1.1: Receiver structures; (a) Heterodyne, (b) Super, Homodyne, and          |      |

| Concurrent                                                                         | 3    |

| Figure 2.1: The evolution process of ISD cascode                                   | 10   |

| Figure 2.2: PCSNIM technique, (a) circuit model, (b) small-signal noise equivalent | 19   |

| Figure 3.1: Dual-band LNA                                                          | 24   |

| Figure 3.2: Multi-mode LNA                                                         | 25   |

| Figure 3.3: 1.8/2.14 GHz dual-band LNA                                             | 26   |

| Figure 3.4: multiband LNA                                                          | 26   |

| Figure 3.5: Reconfigurable multi-mode LNA                                          | 27   |

| Figure 3.6: Wide-band LNA based on resistive feedback                              | 28   |

| Figure 3.7: UWB LNA with AI                                                        | 29   |

| Figure 3.8: Wide-band (0.15 to 1 GHz)                                              | 30   |

| Figure 3.9: Transformer based multi-mode LNA                                       | 31   |

| Figure 3.10: UWB LNA                                                               | 31   |

| Figure 3.11: 3-5 GHz UWB wide-band LNA                                             | 32   |

| Figure 3.12: Tunable wide-band LNA                                                 | 33   |

| Figure 3.13: Tunable differential LNA                                              | 34   |

| Figure 3.14: Tunable LNA with scalable input active inductor                       | 35   |

| Figure 3.15: Tunable-LNA with binary-weighted input                                | 36   |

| Figure 3.16: 2.45/5.24 GHz concurrent LNA                                          | 37   |

| Figure 3.17: BiFET concurrent LNA                                                  | 38   |

| Figure 3.18: Concurrent dual-band SiGe BiCMOS LNA                                  | 39   |

| Figure 3.19: multi-notches concurrent LNA                                          | 40   |

| Figure 3.20: Triple-band concurrent LNA with shunt-peaking technique               | 40   |

| Figure 3.21: Concurrent LNA with output buffer stage                               | 41   |

| Figure 3.22: Switchable pseudo concurrent LNA                                      | 42   |

| Figure 4.1: Design flowchart of PCSNIM LNA with gain enhancer                  | 46 |

|--------------------------------------------------------------------------------|----|

| Figure 4.2: Proposed PCSNIM ISD cascode with gain enhancer                     | 47 |

| Figure 4.3: ISD cascode input network                                          | 50 |

| Figure 4.4: MOSFET capacitors at high-frequency                                | 52 |

| Figure 4.5: Small-signal equivalent circuit of second stage                    | 53 |

| Figure 4.6: Small-signal equivalent of first stage                             | 54 |

| Figure 4.7: small-signal equivalent of input circuit (including Miller effect) | 56 |

| Figure 4.8: Layout of the proposed PCSNIM single-band LNA                      | 59 |

| Figure 4.9: Proposed tunable 2.45 GHz LNA with programmable gain               | 60 |

| Figure 4.10: Small-signal equivalent of output stage                           | 62 |

| Figure 4.11: Layout of the proposed tunable single-band LNA                    | 64 |

| Figure 4.12: Proposed Concurrent dual-band (2.45/5.2 GHz) LNA                  | 65 |

| Figure 4.13: Input of concurrent LNA                                           | 66 |

| Figure 4.14: Concurrent load                                                   | 68 |

| Figure 4.15: Layout of the proposed concurrent LNA                             | 69 |

| Figure 4.16: Block diagram of GPAPU                                            | 70 |

| Figure 4.17: GPAPU circuit implementation                                      | 71 |

| Figure 4.18: New tunable concurrent LNA                                        | 73 |

| Figure 5.1: Input/output return-losses of LNA1 (simulation)                    | 77 |

| Figure 5.2: Gain and isolation of LNA1 (simulation)                            | 78 |

| Figure 5.3: NF of LNA1; (a) pre-layout, (b) post-layout                        | 79 |

| Figure 5.4: Linearity performance of LNA1; (a) P1dB, (b) IIP3                  | 80 |

| Figure 5.5: Micrograph from die of LNA1                                        | 81 |

| Figure 5.6: Measurement set-up for LNA1                                        | 81 |

| Figure 5.7: Input/output return-losses of LNA1 (measurement)                   | 82 |

| Figure 5.8: Gain and isolation of LNA1 (measurement)                           | 83 |

| Figure 5.9: Measured NF of LNA1                                                | 83 |

| Figure 5.10: Gain versus input return-loss of LNA2 (pre-layout simulation)     | 87  |

|--------------------------------------------------------------------------------|-----|

| Figure 5.11: Gain versus input return-loss of LNA2 (post-layout simulation)    | 88  |

| Figure 5.12: Gain versus output return-loss of LNA2 (pre-layout simulation)    | 89  |

| Figure 5.13: Gain versus output return-loss of LNA2 (post-layout simulation)   | 90  |

| Figure 5.14: Programmable gain feature of LNA2 (pre-layout simulation)         | 91  |

| Figure 5.15: Effects of programmable gain on NF (pre-layout simulation)        | 92  |

| Figure 5.16: NF of LNA2 (variable VTUNE_IN, pre-layout)                        | 92  |

| Figure 5.17: NF of LNA2 (variable VTUNE_IN, post-layout)                       | 93  |

| Figure 5.18: P1dB of LNA2 (pre-layout)                                         | 94  |

| Figure 5.19: IIP3 of LNA2 (pre-layout)                                         | 94  |

| Figure 5.20: Micrograph from die of LNA2                                       | 95  |

| Figure 5.21: Gain versus input matching of LNA2 (measurement)                  | 96  |

| Figure 5.22: Gain versus output matching of LNA2 (measurement)                 | 97  |

| Figure 5.23: NF of LNA2 (measurement)                                          | 98  |

| Figure 5.24: P1dB of LNA2 (measurement)                                        | 99  |

| Figure 5.25: IIP3 of LNA2 (measurement)                                        | 99  |

| Figure 5.26: S-parameters of LNA3 (pre-layout)                                 | 103 |

| Figure 5.27: NF of LNA3                                                        | 104 |

| Figure 5.28: P1dB and IIP3 of LNA3 at lower band (pre-layout)                  | 105 |

| Figure 5.29: P1dB and IIP3 of LNA3 at upper band (pre-layout)                  | 105 |

| Figure 5.30: S-parameters of LNA3 (post-layout)                                | 106 |

| Figure 5.31: NF of LNA3 (post-layout)                                          | 106 |

| Figure 5.32: Micrograph from die of LNA3                                       | 107 |

| Figure 5.33: Input/output return losses of LNA3 (measurement)                  | 108 |

| Figure 5.34: Gain and isolation of LNA3 (measurement)                          | 108 |

| Figure 5.35: NF of LNA3 (measurements); (a) NF at lower-band, (b) NF at upper- | 109 |

| band                                                                           |     |

| Figure 5.36: P1dB and IIP3 of LNA3 at lower band (measurements) | 110 |

|-----------------------------------------------------------------|-----|

| Figure 5.37: P1dB and IIP3 of LNA3 at upper band (measurements) | 111 |

| Figure 5.38: GPAPU functionality                                | 114 |

| Figure 5.39: NF of LNA4                                         | 115 |

| Figure 5.40: Tunable gain of LNA4                               | 116 |

| Figure 5.41: Tunable output matching of LNA4                    | 116 |

| Figure 5.42: Input return-loss of LNA4                          | 117 |

| Figure 5.43: Linearity performance of lower-band                | 118 |

| Figure 5.44: Linearity performance of upper-band                | 118 |

## LIST OF TABLES

|                                                                       | Page |

|-----------------------------------------------------------------------|------|

| Table 1.1: Wireless standards                                         | 2    |

| Table 3.1: Previous works at a glance                                 | 43   |

| Table 4.1: Target specifications of PCSNIM ISD LNA with gain enhancer | 45   |

| Table 4.2: biasing values of PCSNIM with gain enhancer LNA            | 49   |

| Table 4.3: Calculated values for input circuit                        | 51   |

| Table 4.4: Values of the load circuit components                      | 57   |

| Table 4.5: Operating modes of LNA2                                    | 62   |

| Table 4.6: Tunable LNA values                                         | 64   |

| Table 4.7: Values of the components – Concurrent LNA                  | 68   |

| Table 4.8 Component values of GPAPU                                   | 72   |

| Table 4.9 Component values of LNA4                                    | 74   |

| Table 5.1 Results of LNA1 (at 2.45 GHz)                               | 84   |

| Table 5.2 Best performance summary of LNA1                            | 86   |

| Table 5.3: LNA2 performance results                                   | 102  |

| Table 5.4: LNA3 results (lower-band)                                  | 113  |

| Table 5.5: LNA3 results (upper-band)                                  | 113  |

| Table 5.6: LNA4 results                                               | 119  |

| Table 5.7: Performance summary of the fabricated LNAs                 | 120  |

| Table 5.8: Comparison with previous works                             | 122  |

# LIST OF ABBREVIATIONS

| AC     | Alternating-Current                               |  |  |  |

|--------|---------------------------------------------------|--|--|--|

| ADC    | Analog to Digital Converter                       |  |  |  |

| AI     | Active Inductor                                   |  |  |  |

| BiCMOS | Bipolar Complementary Metal Oxide semiconductor   |  |  |  |

| BPF    | Band-Pass Filter                                  |  |  |  |

| BW     | Bandwidth                                         |  |  |  |

| CG     | Common-Gate                                       |  |  |  |

| CMOS   | Complementary Metal-Oxide-Semiconductor           |  |  |  |

| CNM    | Classical Noise Matching                          |  |  |  |

| CS     | Common-Source                                     |  |  |  |

| dB     | Decibel                                           |  |  |  |

| DC     | Direct-Current                                    |  |  |  |

| GHz    | Gigahertz                                         |  |  |  |

| GPAPU  | General Purpose Analog Programmable Unit          |  |  |  |

| GSG    | Ground-Signal-Ground                              |  |  |  |

| GSM    | Global System for Mobile                          |  |  |  |

| HBT    | Heterojunction Bipolar Transistor                 |  |  |  |

| IC     | Integrated Circuit                                |  |  |  |

| IEEE   | Institute of Electrical and Electronics Engineers |  |  |  |

| IF     | Intermediate-Frequency                            |  |  |  |

| IIP2   | Input-Referred Second-Order intermodulation point |  |  |  |

| IIP3   | Input-Referred Third-Order Intermodulation Point  |  |  |  |

| IM     | Inter-Modulation                                  |  |  |  |

| ISD    | Inductive Source Degenerated                      |  |  |  |

| LNA    | Low Noise Amplifier                               |  |  |  |

| LO           | Local Oscillator                                          |

|--------------|-----------------------------------------------------------|

| LPF          | Low-Pass Filter                                           |

| MHz          | Megahertz                                                 |

| NF           | Noise Figure                                              |

| NMOS         | N-Metal Oxide Semiconductor                               |

| OIP3         | Output-Referred Third-Order Intermodulation Point         |

| PCNO         | Power-Constrained Noise Optimization                      |

| PCSNIM       | Power-Constrained Simultaneously Noise and Input Matching |

| PDK          | Process Design Kit                                        |

| PLS          | Post-Layout Simulations                                   |

| PMOS         | P-Metal Oxide Semiconductor                               |

| PSS          | Periodic Steady State                                     |

| Q-factor     | Quality Factor                                            |

| RC           | Resistor-capacitor                                        |

| RF           | Radio-Frequency                                           |

| RLC          | Resistor-inductor-capacitor                               |

| SiGe         | Silicon Germanium                                         |

| SNIM         | Simultaneous Noise and Input Matching                     |

| SOC          | System-on-Chip                                            |

| S-parameters | Scattering Parameters                                     |

| UWB          | Ultra Wide Band                                           |

| VLSI         | Very Large-Scale Integration                              |

| WCDMA        | Wide-band Code Division Multiple Access                   |

| WLAN         | Wireless Local Area Network                               |

# REKA BENTUK JALUR TUNGGAL BOLEH TALA DAN SEREMPAK PENGUAT HINGAR RENDAH

### ABSTRAK

Penguat hingar rendah (LNA) merupakan kunci utama binaan blok rantaian penerimaan kerana ia bertujuan untuk menguatkan isyarat sambil menambah hingar seminima yang mungkin. Sehubungan itu, beberapa jenis teknik bagi meminimumkan hingar LNA diperkenalkan. PCSNIM (kuasa terhad dengan hingar dan input sepadan serempak) dilihat antara teknik yang banyak diberikan perhatian. Namun, berdasarkan kepada kajian sebelum ini, ia menghadkan keupayaan gandaan LNA. Bagi menyelesaikan permasalahan ini dan menyokong keperluan pelbagai jalur, tesis ini mempersembahkan empat jenis rekaan LNA (LNA1 hingga LNA4) berdasarkan sumber induktif merosot (ISD) untuk meliputi jalur tunggal (contoh: IEEE802.11.b/g, Bluetooth) dan serempak (contoh: WIFI). LNA1 disasar untuk menyelesaikan isu gandaan yang rendah bagi jalur tunggal LNA dengan penambahbaikan pada keluarannya. Bagi mendapatkan penerimaan serempak untuk dua jalur frekuensi (24.5/5.2 GHz piawaian WIFI), LNA3 direka berasaskan topologi yang sama untuk LNA1. LNA ini dilaksanakan dalam struktur penuh-bersepadu untuk menyahkan penggunaan komponen luaran cip. Rekaan LNA2 dan LNA4 terhasil daripada masalah anjakan frekuensi selepas proses fabrikasi LNA1 dan LNA3. Bagi menangani isu ini, struktur boleh tala menggunakan varaktor digunakan pada padanan masukan/keluaran LNA2 dan sistem baru GPAPU (unit analog boleh program kegunaan umum) diperkenal dan dilaksana kepada struktur penguat boleh tala-serempak (LNA4). Kesemua kaedah dibuktikan secara simulasi dan pengukuran. LNA1, LNA2 dan LNA3 difabrikasi menggunakan teknologi 0.13 µm CMOS manakala LNA4 direka hanya pada tahap pra susun atur simulasi. Untuk LNA1, pengukuran gandaan hadapan dan hingar memberikan nilai 19.84 dB dan 2.59 dB. Bagi masukan/keluaran sepadan, nilai diperolehi adalah -9.39 dB dan -39.23 dB. LNA1 menggunakan arus terus 4 mA daripada bekalan kuasa 1.2 V. Sementara itu, terdapat

anjakan frekuensi sebanyak 260 MHz pada keluaran LNA1. Ini disebabkan proses toleransi semasa fabrikasi. Nilai pengukuran bagi gandaan hadapan dan hingar bagi LNA2 adalah 14.62 dB dan 3.73 dB dengan kuasa arus terus 5 mW. Untuk julat talaan, 140 MHz pada masukan dan 50 MHz pada keluaran berjaya dicapai untuk padanan masukan/keluaran. Berdasarkan kepada struktur talaan varaktor pada masukan dan keluaran LNA2, nilai dapatan (terutamanya NF) berubah-ubah bergantung kepada padanan masukan/keluaran. Ini bertujuan untuk mencapai fungsi boleh tala jika dibandingkan dengan LNA1. Nilai pengukuran yang diperoleh bagi gandaan hadapan LNA3 ialah 17.11 dB pada 2.45 GHz dan 10.42 dB pada 5.2 GHz dengan kuasa arus terus 4.8 mW. Nilai pengukuran bagi padanan masukan dan keluaran pula adalah -19.48 dB dan -39.23 dB bagi jalur rendah manakala -25.51 dB dan -10.46 dB bagi jalur tinggi. Nilai hingar yang diukur untuk LNA3 ialah 4.09 dB pada jalur rendah dan 10.47 dB untuk jalur tinggi. Nilai yang diperoleh bagi bacaan gandaan dan nilai hingar berbeza daripada jangkaan awal. Ini kerana, terlihatkan anjakan frekuensi sebanyak 1 GHz pada jalur atas yang dipengaruhi oleh proses perubahan semasa fabrikasi. Daripada hasil simulasi, LNA4 menunjukkan gandaan hadapan yang dicapai bagi jalur rendah ialah 21 dB dan jalur tinggi 18 dB. Untuk nilai hingar, 2.53 dB diperolehi bagi jalur rendah dan 2.96 dB bagi jalur tinggi dengan kuasa arus terus 5.5 mW. Bagi rangkaian keluaran untuk LNA4, julat nilai boleh tala yang diperolehi ialah 300 MHz. Kesimpulannya, kaedah penambahbaikan gandaan yang digunakan bagi LNA1 berfungsi dengan jayanya dan isu nilai gandaan yang rendah berasaskan teknik PCSNIM dapat diselesaikan. Begitu juga masalah anjakan frekuensi dalam penguat jalur tunggal diatasi menggunakan struktur boleh tala LNA2. Tambahan pula, penguat PCSNIM serempak penuh-bersepadu (LNA3) yang direka dan dilaksanakan berjaya menerima frekuensi-frekuensi bagi piawaian WIFI secara serempak. Akhir sekali, struktur boleh tala yang baru (GPAPU) diperkenalkan dan terbukti berfungsi berdasarkan kepada keputusan simulasi LNA4.

# DESIGN OF TUNABLE SINGLE BAND AND CONCURRENT LOW NOISE AMPLIFIER

### ABSTRACT

Low noise amplifier (LNA) is one of the key building blocks in receiving chain as they aimed to amplify the signal while adding minimum possible noise to it. Thus, several noise optimization techniques were proposed by researchers to minimize the noise of LNAs. Among these techniques, the PCSNIM (power constrained simultaneous noise and input matching) is found to be a popular approach; however, it limits the gain of the LNA according to literature. Therefore, to tackle the mentioned issue and to support the requirement for multi-band, this thesis presents the design of four LNAs (LNA1 to LNA4) based on inductive source degenerated (ISD) to cover single-band (e.g. IEEE 802.11.b/g, Bluetooth) and concurrent (e.g. WIFI) applications. LNA1 is targeted to solve the reducedgain issue of single-band LNA by utilizing a gain-enhancer at the output of LNA. To obtain the concurrent reception of two frequency bands (2.45/ 5.2 GHz in WIFI standard), LNA3 is designed based on the same topology of LNA1. This LNA is implemented in fully-integrated structure to eliminate the off-chip components. Meanwhile, the design of LNA2 and LNA4 are resulted from the problem of frequency shift that occurred after the fabrication of LNA1 and LNA3. Hence, to tackle the issue, a tunable structure using varactors is used at the input/output matching of LNA2 and a new system (GPAPU-general purpose analog programmable unit) is introduced and implemented to the concurrent structure to obtain the tunable-concurrent amplifier (LNA4). For this work, LNA1, LNA2, and LNA3 were fabricated in 0.13 µm CMOS technology while LNA4 was designed only up to pre-layout simulation level. The measured forward gain and noise figure (NF) values for LNA1 are 19.84 dB and 2.59 dB respectively, while achieving the input/output return losses of -9.39 dB and -39.23 dB. LNA1 consumes 4 mA of dc current from 1.2 V supply. Meanwhile, 260 MHz frequency-shift was observed at the output of LNA1 due to the process tolerances

during fabrication. The measured forward gain and NF values of LNA2 are 14.62 dB and 3.73 dB respectively, while consuming 5 mW of dc power. Moreover, the tuning ranges of 140 MHz at the input and 50 MHz at output are accomplished by LNA2 for the input/output matching. Due to the varactor-based tuning structure at the input and output of LNA2, the gain (and respectively NF) was traded-off with input/output matching to achieve tunable function comparing to LNA1. LNA3 is measured with the forward gain values of 17.11 and 10.42 dB at 2.45 and 5.2 GHz frequencies respectively, while consuming 4.8 mW of dc power. Also, the obtained values for input and output return losses are -19.48 and -39.23 dB respectively at the lower band and -25.51 and -10.64 dB respectively at upper band. The measured NF of this LNA3 is 4.09 dB at the lower-band and 10.47 dB at the upper band. The achieved gain and NF are different from the expected simulation results due to the observed 1 GHz frequency-shift at upper-band due to process variation during fabrication. From the simulation results of LNA4, the forward gain values obtained for lower and upper bands are 21 and 18 dB respectively. Also, the achieved NF values are 2.53 and 2.96 dB respectively in the mentioned bands while consuming 5.5 mW of dc power. In addition, the output network of the LNA4 can be tuned in range of 300 MHz. In conclusion, the implemented method of gain-enhancer in LNA1 works perfectly and the reduced-gain issue of PCSNIM technique is solved. Also, the problem of frequency-shift in single-band amplifier was tackled using the tunable structure of LNA2. Furthermore, a fully-integrated concurrent PCSNIM amplifier (LNA3) is designed and implemented successfully to receive simultaneous frequency bands of WIFI standard. Finally, a new tunable structure (GPAPU) was introduced and theoretically proved to be functional based on the simulation results of LNA4.

### **CHAPTER 1**

### **INTRODUCTION**

This chapter provides an introduction to this research work and explains the motivations and challenges on the state of the art in LNA design. Then, the problem statements, objectives, scope and contributions of this work are discussed. Finally, an overview of the thesis organization ends this chapter.

### 1.1 Introduction to Wireless Standards

The history of radio communication starts from early 20<sup>th</sup> century when Guglielmo Marconi successfully established the first radio contact over the Atlantic Ocean (Vidojkovic, 2008). The prospect of this demonstration predicted an exciting future for telecom industry by replacing the wired telegraph and telephone communication with radio waves. The developments of Shannon's information theory and the concept of cellular systems along with the invention of transistor, paved the way for low-cost wireless communications. Furthermore, due to the computer-aided design and powerful IC design tools (e.g. Cadence IC design suite) and utilizing new techniques (e.g. photolithography); the dream of very large-scale integration (VLSI) of the transistors on a tiny piece of silicon die became true. These developments lead to cost-effective mass production of the electronic components and system on-chips (SOCs) that allows people to enjoy low-cost wireless communication (Razavi, 1998; Tasić, Serdijn, & Long, 2007).

According to the increasing market demands for wireless services and the variety of wireless applications, many standards have been developed to fulfill the user's requirements by the standardization committee. Table 1.1 shows some of the famous standards with their specifications as: centre frequency, bandwidth, duplex type, data rate, modulation and the receiver architecture. For instance, Bluetooth standard is defined to work at 2.44 GHz centre frequency and it needs to cover a bandwidth range of 80 MHz (from 2.4 to 2.48 GHz). It

uses TDD (Time Division Duplexing scheme) and GFSK (Gaussian Frequency Shift Keying) modulation. In addition, the data rate of Bluetooth is 0.723 Mb/s and it can be down-converted using both low-IF and zero-IF architectures.

| Standard      | Freq (GHz)<br>/BW (MHz) | Duplex  | Data Rate  | Modulation           | Architecture               |

|---------------|-------------------------|---------|------------|----------------------|----------------------------|

| GSM           | 0.947 / 25              | FDD     | 14.4 kb/s  | GMSK                 | zero-IF/high-<br>IF/low-IF |

| DCS1800       | 1.842 / 75              | FDD     | 14.4 kb/s  | GMSK                 | zero-IF/low-<br>IF/high-IF |

| IS-95         | 1.96 / 60               | FDD     | 14.4 kb/s  | QPSK, OQPSK          | high-IF                    |

| WCDMA         | 2.14 / 60               | FDD,TDD | 2-10 Mb/s  | QPSK,<br>16QAM,      | zero-IF                    |

| WCDMA<br>3GPP | 1.967 / 115             | TDD     | 2-10 Mb/s  | QPSK, 8PSK           | zero-IF                    |

| DECT          | 2.44 / 80               | TDD     | 1.152 Mb/s | GFSK                 | low-IF<br>zero-IF/high-    |

| Bluetooth     | 2.44 / 80               | TDD     | 0.723 Mb/s | GFSK                 | low-IF/zero-IF             |

| 802.11b(g)    | 2.44 / 80               | TDD     | 11(54)Mb/s | BPSK, QPSK<br>(OFDM) | zero-IF<br>low-IF/high-IF  |

| 802.11a       | 5.15-5.825              | TDD     | 54 Mb/s    | BPSK, QPSK           | zero-IF<br>low-IF/high-IF  |

| UWB           | 3-10 / NA               | -       | 600 Mb/s   | BPSK, QPSK,<br>OFDM  | -                          |

| ZIGBEE        | 2.44 / 80               | -       | 250 kb/s   | QPSK                 | -                          |

Table 1.1: Wireless standards (Tasić, Serdijn, & Long, 2007).

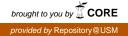

Based on the mentioned wireless standards, many receiver structures (Figure 1.1), including but not limited to, heterodyne, super-heterodyne, homodyne and concurrent have been introduced to respond to the user's requirements in both single-band and multiband applications.

(d)

Figure 1.1: Receiver structures; (a) Heterodyne (Tasić, et al., 2007), (b) Super-heterodyne (Tasić, et al., 2007), (c) Homodyne (Razavi, 1998), (d) Concurrent (Hashemi & Hajimiri,

2002).

Generally, the receiving process of the RF signal can be divided into two main tasks as: amplification and down-conversion. According to Figure 1.1, in most of the proposed topologies, low noise amplifier (LNA) is the first active block after the antenna in receiving path. Therefore, the main role of the LNA is to amplify the RF signal while adding as less as possible noise to it. In some structures (e.g. heterodyne), LNAs are followed by a bandselection filter at the input and an image-rejection filter at the output. The former enables LNA to select and amplify the desired range of frequency and the latter helps to suppress the unwanted interferences from the adjacent channels (Tasić, et al., 2007). Then, the received signal is passed to down-converter which is usually consists of a mixer and local-oscillator. Depending on the used architecture, one or few down-conversion steps are carried out (by receivers) to prepare the signal for baseband section.

In this research work, the interest is on first task of the receiver (low-noise amplification of the RF signal), therefore, some design methodologies are presented in order to investigate the existed issues in amplification step.

### 1.2 Motivations on LNA Design

Typically, the first active block (after antenna) in receiving chain is a low noise amplifier (LNA) and its main duty is to amplify the received signals without adding any noise to them. Also, the level of amplification (gain of the LNA), should be high enough to overcome the noise of subsequence stages.

Undoubtedly, the noise figure (NF) is the most important parameter in LNA design procedure, as it contributes to the overall noise performance of the receiver. In addition, the sensitivity of the receiver is also determined by the NF and gain of LNA (Lee, 2004).

According to the receiver's architecture (such as super heterodyne), it is necessary to implement some filters at the input and output of LNA (for instance, band-selection and image-rejection filters). Therefore, it is essential to consider the impedance matching requirements in order to maximize the transferred power from source to load (Li, 2012). On the other hand, the optimum noise impedance point is different from proper input matching point. Hence, important trade-offs between noise matching and input matching of LNA should be taken into the account during the design optimization process (Nguyen, Kim, Ihm, Yang, & Lee, 2004).

LNA also plays an important role in the linearity performance of the system (Lee, 2004), it should accommodate large signals without distortions. Meanwhile, it needs to maintain high stability and isolation to prevent oscillations.

Finally, the power consumption and the size of the LNA should be accounted during the design procedure; as the former determines maximum swing (linearity), gain and noise performance of the LNA (Razavi, 1998) and the latter impacts the costs of implementation.

From above discussion, it can be inferred that LNA is one of the most interesting and challenging circuits as its performance parameters involved with critical trade-offs (e.g. gain, noise, matching, linearity and power consumption).

### 1.3 Problem Statement

Inductive source degenerated (ISD) cascode is one of the popular LNA topologies that used in both single-band and multiband applications. Although the LNAs based on this topology achieve high-gain, but their noise performance needs further improvements. Thus, several optimization techniques (see Section 2.5.2) have been proposed by researchers to minimize the noise factor of these LNAs. The PCSNIM (power constrained simultaneous noise and input matching) method is found as an appropriate approach compared to the other techniques for this work. But, the gain performance of LNA is degraded utilizing this technique, because of the additional components at the input of the LNA (Hashemi & Hajimiri, 2002) as well as the generated parasitic after the physical implementation. Therefore, it is important to modify the topology in order to alleviate this gain issue while maintaining the simultaneous noise and input matching under the power constraint.

Another prevalent problem in single-band LNAs is the shift of frequency from desired operating point. The main reason of this issue is not pointed clearly in available literatures; but, the PDK (process design kit) model uncertainties, fabrication process variations and in-complete modeling of parasitic (especially at high frequencies) can be named as the culprits of this issue in single-band amplifiers. Furthermore, this problem is not only affecting the single-band LNAs but also degrades the performance of concurrent structures. Therefore, it is essential to implement a mechanism to enable frequency tuning post fabrication while maintaining the performance parameters of both LNAs.

Finally, based on the limited number of fixed-air probes during the measurement of the tunable-LNA, it was not feasible to connect as many as desired control voltages to tune the circuit at the desired mode. This issue is highlighted more, when a capacitor (or resistor) switch-bank is implemented into the LNA as it requires more control bits. Therefore, it is necessary to design a tunable structure with minimum number of tuning voltages with no penalty on noise, gain and power consumption of the LNAs.

### 1.4 Research Objectives

- To design and implement a single-band PCSNIM LNA with enhanced gain performance for IEEE 802.11.b/g (2.45 GHz) applications.

- To design and implement a fully-integrated PCSNIM concurrent LNA for WIFI (2.45/5.2 GHz) applications.

#### **1.5** Scope of the Work

In this research, after a brief review on background knowledge of LNA design and related literature, the design methodologies of four LNAs for single-band and concurrent applications are presented. Three of the LNAs (single-band, tunable and concurrent) are targeted for fabrication and measurements while the new tunable-concurrent LNA is designed (up to pre-layout step only) as a theoretical proof of the idea. Also, for each design,