# LOW NOISE AND LOW POWER ECG AMPLIFIER USING CMOS $0.13\mu m$ TECHNOLOGY

ZULFADLI BIN KAMARUZZAMAN

UNIVERSITI TEKNOLOGI MALAYSIA

# LOW NOISE AND LOW POWER ECG AMPLIFIER USING CMOS $0.13 \mu m$ TECHNOLOGY

## ZULFADLI BIN KAMARUZZAMAN

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Computer and Microelectronic System)

Faculty of Electrical Engineering Universiti Teknologi Malaysia

JUNE 2018

Specially dedicated to every person who is behind me through the highs and lows.

#### **ACKNOWLEDGEMENT**

First of all, Alhamdulillah, all praise to Allah, who ease the burden when things get difficult, who bestowed me strength and courage to complete project.

My sincere thanks and appreciation goes to my project supervisor, Dr Yusmeeraz binti Yusof. Indeed, I am grateful to her for the time, patience, guidance, knowledge and continuous support that she gave me throughout the process to completing this project. Frankly, without her supervision and guidance, it is impossible for me to completing this.

I also want to thanks my family who have been really supportive to me. They always be there when the time get rough, keeping me sane when I am about to lose my grip. I really grateful for having them by my side.

Lastly, I thank my friend and colleague, who have help me directly or indirectly in the successful completion of my project. Thanks for being so understanding and supportive to me. Again, thanks to all, I really indebted to all of you guys, only God can repay your good deeds to me.

#### **ABSTRACT**

Through the scaling down of modern VLSI technologies, the realization of CMOS based electrocardiogram (ECG) device becoming wearable to its user is possible. Yet, this transition introduces more constraints to its analog circuits. This is due to the measured electrical signal of ECG devices, or known as ECG signal possessed characteristics that are low in frequency (0.1 to 150Hz) and amplitude (<5mV), thus it lead to every ECG devices suffered from flicker noise for low frequency cardiac signal acquisition at the front-end of its sensor, 50 Hz power line electromagnetic interference, and the large unstable input offsets due to the improper attachment of electrode-skin interface. Therefore, to encounter this problem, the frontend of ECG devices, which is amplifier needed to be enhance so it able to accurately detect the ECG signals. Besides that, the amplifier must able to operate at low voltage and less power consumption so that it can be used in wearable device. In this work, a high performance CMOS amplifier for ECG sensors that improves the noise issue and suitable for low power wearable cardiac screening is designed. The designed circuit adopts the folded cascode topology to achieve high gain and less susceptible to noise. This work uses 0.13 µm CMOS process technology from Silterra and Mentor Graphics Pyxis as the design tool. This successfully achieve high CMRR which is 160dB. Besides that, this work also able to reduce the noise at the front-end amplifier system down to  $1.28 \text{nV}/\sqrt{\text{Hz}}$ . The power consumption of the designed amplifier is 3  $\mu\text{W}$ , which is low and suitable to be implemented on design for wearable ECG devices.

#### **ABSTRAK**

Kemajuan dalam teknologi VLSI moden telah membolehkan peranti elektrokardiogram (EKG) yang berasaskan CMOS menjadi satu sistem mudah alih. Namun begitu, peralihan sistem EKG kepada peranti mudah alih akan membebankan litar analognya. Hal ini kerana signal elektrik yang diukur oleh peranti EKG, atau lebih dikenali sebagai signal EKG mempunyai ciri-ciri signal yang berfrekuensi dan amplitud yang rendah. Ini menyebabkan setiap peranti EKG mengalami gangguan kerlipan pada frekuensi rendah pada bahagian hadapan penguat EKG ketika meperoleh signal EKG, gangguan elektromagnet daripada 50 Hz talian kuasa, dan ketidakstabilan masukan ofset yang besar disebabkan oleh penyambungan antara muka elektrod dan kulit yang tidak sempurna. Untuk mengatasi masalah ini, bahagian hadapan peranti ECG iaitu penguat perlu di pertingkatkan untuk memperoleh signal EKG dengan tepat. Selain itu, penguat tersebut hendaklah beroperasi dalam kadar voltan dan kuasa yang rendah supaya ia boleh digunakan dalam peranti mudah alih. Dalam projek ini, Di dalam projek ini, penguat yang mampu untuk mengatasi masalah gangguan signal dan berkuasa rendah untuk peranti EKG dicadangkan. Penguat ini mengadaptasi topologi kaskod terlipat yang mempunyai daya stabil yang tinggi. Dengan menggunakan teknologi CMOS 0.13 µm daripada Silterra, keputusan simulasi menunjukkan bahawa bahagian hadapan litar ini berupaya mencapai nisbah penolakan mod sepunya (CMRR) yang tinggi iaitu 160 dB. Selain itu, penguat ini mencapai tahap gangguan isyarat masukan yang rendah iaitu  $1.28 \text{nV} / \sqrt{\text{Hz}}$ . dan jumlah lesapan kuasa penguat ini hanyalah sebanyak 3 µW yang mejadikan ia sesuai digunakan bersama bahagian belakang yang memproses dan mengklasifikasi isyarat lanjutan untuk peranti mudah alih EKG.

## **TABLE OF CONTENTS**

| CHAPTER |                   | TITLE                       | PAGE |

|---------|-------------------|-----------------------------|------|

|         | $\mathbf{D}$      | ECLARATION                  | ii   |

|         | $\mathbf{D}$      | EDICATION                   | iii  |

|         | $\mathbf{A}^{0}$  | CKNOWLEDGEMENT              | iv   |

|         | $\mathbf{A}$      | BSTRACT                     | v    |

|         | $\mathbf{A}$      | BSTRAK                      | vi   |

|         | TABLE OF CONTENTS |                             | vii  |

|         | L                 | IST OF TABLES               | X    |

|         | L                 | IST OF FIGURES              | xi   |

|         | L                 | IST OF ABBREVIATIONS        | xiii |

|         | L                 | IST OF SYMBOLS              | xiv  |

| 1       | INTRO             | DDUCTION                    | 1    |

|         | 1.1               | Background of Study         | 1    |

|         | 1.2               | Problem Statement           | 2    |

|         | 1.3               | Objectives                  | 3    |

|         | 1.4               | Scope                       | 4    |

|         | 1.5               | Organization                | 4    |

| 2       | LITE              | RATURE REVIEW               | 6    |

|         | 2.1               | Electrocardiogram           | 6    |

|         | 2.2               | ECG Signal                  | 7    |

|         | 2.3               | Amplifier Design Topology   | 8    |

|         | 2.3.1             | Two-Stage Cascade Topology  | 8    |

|         | 2.3.2             | Telescopic Cascode Topology | 9    |

|   | 2.3.3   | Folded Cascode Topology                     | 10 |

|---|---------|---------------------------------------------|----|

|   | 2.4     | Highlighted Concern in ECG Amplifier Design | 11 |

|   | 2.4.1   | ECG Signal acquisition Noise                | 11 |

|   | 2.4.2   | CMRR                                        | 12 |

|   | 2.4.3   | Input Referred Noise                        | 14 |

|   | 2.5     | Recognized Solution to ECG Amplifier Design | 14 |

|   |         | Problem                                     |    |

|   | 2.5.1   | Low Supply Voltage Current Mirror Design    | 14 |

|   | 2.5.2   | Low Noise Amplifier Design Technique        | 17 |

|   | 2.5.2.1 | PMOS as Input Device                        | 18 |

|   | 2.5.2.2 | Subthreshold Biasing                        | 19 |

|   | 2.6     | Related Works                               | 20 |

|   | 2.6.1   | Performance Comparison Summary for          | 21 |

|   |         | Related Works                               |    |

| 2 | MEGNI   |                                             | 22 |

| 3 |         | ODOLOGY                                     | 22 |

|   | 3.1     | Project Workflow                            | 22 |

|   | 3.2     | Gantt Chart                                 | 24 |

|   | 3.3     | Design Tools                                | 25 |

|   | 3.4     | CMOS Process Technology                     | 25 |

|   | 3.5     | Chosen Topology                             | 26 |

|   | 3.6     | Proposed Folded Cascode Topology            | 27 |

|   | 3.7     | Performance Parameters                      | 28 |

| 4 | RESUL   | TS AND DISCUSSIONS                          | 29 |

|   | 4.1     | Designed circuit                            | 29 |

|   | 4.2     | Simulation Result                           | 31 |

|   | 4.2.1   | Transient Analysis                          | 31 |

|   | 4.2.2   | AC Analysis                                 | 32 |

|   | 4.2.3   | Common Mode Rejection Ratio                 | 33 |

|   | 4.2.4   | Input Referred Noise Analysis               | 34 |

|   | 4.4     | Performance Comparison                      | 35 |

|   |         |                                             |    |

| 5        | CON  | CONCLUSIONS |    |

|----------|------|-------------|----|

|          | 5.1  | Conclusions | 36 |

|          | 5.2  | Future Work | 37 |

|          |      |             |    |

|          |      |             |    |

| REFERE   | NCES |             | 38 |

| Appendix | A    |             | 42 |

## LIST OF TABLES

| TABLE NO. | TITLE                                           | PAGES |

|-----------|-------------------------------------------------|-------|

| 2.1       | Performance Comparison of Related Work          | 21    |

| 3.1       | Initial Design Parameter                        | 27    |

| 3.2       | Performance Specification                       | 28    |

| 3.3       | ECG Characteristic                              | 28    |

| 4.1       | Transistor Sizing                               | 30    |

| 4.2       | Performance Comparison                          | 35    |

| 5.1       | Comparison between Specification and Simulation | 37    |

## LIST OF FIGURES

| FIGURE NO. | TITLE                                         | PAGES |

|------------|-----------------------------------------------|-------|

| 1.1        | Project Scope                                 | 4     |

| 2.1        | Normal ECG Signal Complexes and Peaks         | 7     |

| 2.2        | Two Stage Cascade Operational Amplifiers      | 8     |

| 2.3        | Telescopic Cascode Operational Amplifier      | 9     |

| 2.4        | Folded Cascode Operational Amplifier          | 10    |

| 2.5        | Block Diagram of Single Ended Differential    | 12    |

|            | Amplifier                                     |       |

| 2.6        | Input Referred Noise Modelling                | 14    |

| 2.7        | Biasing Current Generated by Resistor Divider | 15    |

| 2.8        | Current Source Designed Using Current Mirror  | 15    |

|            | Design                                        |       |

| 2.9        | Cascode Current Mirror                        | 16    |

| 2.10       | Modified Current Mirror                       | 17    |

| 3.1        | Project Flow Chart                            | 23    |

| 3.2        | Project Gantt Chart                           | 24    |

| 3.3        | Referenced Folded Op-Amp Design Topology      | 26    |

| 3.4        | Proposed Design Topology                      | 27    |

| 3.5        | Optimization technique using Gm/Id            | 28    |

| 4.1        | Designed Circuit Schematic                    | 30    |

| 4.2        | Transient Response with Maximum Input         | 31    |

| 4.3        | Transient Response with Minimum Input         | 31    |

|     |                                       | xii |

|-----|---------------------------------------|-----|

| 4.4 | AC Analysis Setup                     | 32  |

| 4.5 | AC Response of Amplifier              | 32  |

| 4.6 | Common Mode Gain Simulation Setup     | 33  |

| 4.7 | Common Mode Gain                      | 33  |

| 4.8 | Input Referred Noise                  | 34  |

| 4.9 | Input Referred Noise Simulation Setup | 34  |

## LIST OF ABBREVIATIONS

AA - Arrhythmia, Amyloid

AgCl - Silver Chloride

AL - Amyloid Light-Chain

BSIM4 - Berkeley Short-channel Insulated Gate Field-Effect

Transistor Model version 4

BW - Baseline Wander

CMRR - Common Mode Rejection Ratio

DC - Direct Current

ECG - Electrocardiogram

EM - Electrode Motion

HRV - Heart Rate Variability

MA - Muscle Artifacts

PLI - Power Line Interference

xiv

## LIST OF SYMBOLS

A - Ampere

Ad - Differential Gain

Ac - Common Gain

$C_{ox}$  - Oxide Capacitance

dB - Decibel

f - Frequency

gm - Transconductance

Hz - Hertz

V - Volt

$V_{TH}$  - Threshold Voltage

W - Watt

$\mu_n$  - Mobility

## **CHAPTER 1**

### INTRODUCTION

This thesis presents the ECG signal amplifier design using folded cascode operational amplifier topology. This chapter discusses the overview of the knowledge of the project, problem statement, project objective, scope, and thesis organization respectively.

#### 1.1 Introduction

The rapid growth in medical technology, alongside with advancement in semiconductor industry, make it possible for traditional biomedical instrument, which usually bulky in size to be redesign to become smaller and even portable and wearable. Therefore, many efforts have been done to perform continuous yet comfortable health monitoring in daily life through a wearable system [1]. There are various biomedical signal such as body fat, heart rate, electromyogram, and electroencephalogram are now available to be monitored in commercialized wearable biomedical devices [1]. Among these, the most vital biomedical instrument is ECG monitoring device as

cardiovascular diseases are the major cause of death worldwide [2]. This have led to increase of the need to have wearable ECG monitoring in homecare and clinical setting to prevent cardiovascular disease or detect symptomatic signs for patients with uncommon events.

To realise wearable ECG monitoring device, a lot of things needed to be put into consideration. The main concern on wearable ECG monitoring device is the device is battery operated [3], thus it inherently require very low power circuitry to operate as good as conventional ECG monitoring device. This show that every block in wearable ECG monitoring device should be optimize, especially the most important block which is ECG front end amplifier, which require high signal to noise ratio output for further processing of subsequent block in the device.

#### 1.2 Problem Statement

Currently, battery operated devices, suffered various constrain in its analog circuitry due to more complex digital circuit and clock frequency introduced to the system. The portable ECG signal acquisition system is not excluded in this matter. The analog circuitry in portable ECG signal is the front end amplifier. This front end amplifier is the most important part in the system because the degree of reliability of ECG signal acquisition system heavily rely on the quality of the signal been produce by this front end amplifier.

In portable ECG monitoring system, low power front end ECG amplifier are very prone to noisy environment. The noisy environment are contributed by several factors. First factor is powerline magnetic field interference ranging in 50Hz, [3, 14-17]. Second factor is flicker noise. Flicker noise is very dominant in low-frequency band due to its fluctuations in carrier mobility. This two noises can easily interfered

with ECG signal obtain from the electrode feed to front end ECG amplifier because ECG signal is typically in range of amplitude and frequency less than 5mV and 250Hz respectively. Besides that, DC offset created by skin-electrode interface also contributed to noisy environment. The DC offset can reach as high as  $\pm 100\text{mV}$ . This noise can easily saturate the amplifier and lead to limited amount of gain can be applied to ECG amplifier. These noise and offset is should not happened in portable ECG monitoring system because it can compromise the system quality.

This issues greatly challenge the design of precise ECG front end amplifier. The, designing process must feature high common mode rejection ratio (CMRR), high signal to noise ratio, high input impedance, DC offset suppression and low power consumption in order to realize the single-chip portable ECG monitoring system.

## 1.3 Objective

As the noisy environment and low frequency noise is the main problem in portable ECG signal acquisition system, therefore the main objective of this project is to design the most impacted block by this problem which is ECG signal amplifier. In addition to that, as the nature of trade-off in analog amplifier design, some amplifier parameter will put to top priority in trade of others parameter. Those parameter are CMRR and amplifier gain. This is due to accuracy and precision are very important aspect in handling medical application, therefore by prioritizing this parameter will help to achieve it [4]. Besides that, the amplifier design must be low power as it will be uses in wearable devices. In a nutshell, in this project the ECG signal amplifier is designed to have low power, high CMRR, and low noise one lead ECG signal amplifier by using 0.13 µm CMOS process technology.

## 1.4 Scope

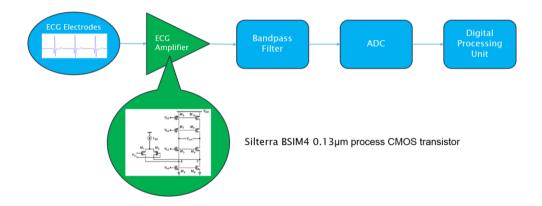

This project scope is limited only to amplifier design, without considering other backend components of ECG signal acquisition system such as filter, analog to digital converter, and digital processing unit. The ECG amplifier design in this project are based on one of the low noise amplifier design which is folded cascode amplifier. The technology node used for this project is BSIM4 0.13 µm CMOS transistor process technology. The tool being used for the circuit design are Pyxis Schematic and the simulation are done through ELDO simulation software. Figure 1.1 depicted scope of this project, which is highlighted in green colour.

Figure 1.1: Project Scope

### 1.5 Organization

The content of this report is organized into a total of five chapters. The first chapter consists of the background and information of this project, the problem statement, project objectives and the project scope. Chapter 2 consists of the literature review which includes the discussion of the background and the works from other researchers that are related to this project. The Chapter 3 is discussing about the

methodology that is the method, hardware, tools, software and the design algorithms that are used to develop this project. While the Chapter 4 is discussing about the project design simulated result and output. The last chapter which is Chapter 5 discussing the conclusion and future works that are required to further enhance the current design.

#### REFERENCES

- 1. Kosack, Cara S, Anne-Laure Page, and Paul R Klatser. "A Guide to Aid the Selection of Diagnostic Tests." *Bulletin of the World Health Organization*, 2017.

- 2. Roth, Gregory A., et al. "Global, regional, and national burden of cardiovascular diseases for 10 causes, 1990 to 2015." *Journal of the American College of Cardiology* 70.1: 1-25, 2017.

- 3. Levkov, Chavdar, et al. "Removal of power-line interference from the ECG: a review of the subtraction procedure." *BioMedical Engineering OnLine* 4.1,50, 2007.

- 4. Degen, Thomas, Simon Torrent, and Heinz Jackel. "Low-noise two-wired buffer electrodes for bioelectric amplifiers." *IEEE transactions on biomedical engineering* 54.7: 1328-1332, 2007.

- 5. Goldberger, Ary L., Zachary D. Goldberger, and Alexei Shvilkin. *Clinical Electrocardiography: A Simplified Approach E-Book*. Elsevier Health Sciences, 2017.

- 6. Piper, Cornelia, et al. "How to diagnose cardiac amyloidosis early: impact of ECG, tissue Doppler echocardiography, and myocardial biopsy." *Amyloid* 17.1: 1-9, 2010.

- 7. Ng, Kian Ann, and Pak Kwong Chan. "A CMOS analog front-end IC for portable EEG/ECG monitoring applications." *IEEE Transactions on Circuits and Systems I: Regular Papers* 52.11: 2335-2347, 2005.

- 8. B. Razavi, Design of analog CMOS integrated circuits. McGraw-Hill, 2001.

- 9. C. A. Holt, Electronic circuits: digital and analog. John Wiley & Sons, 1978.

- 10. Z. Kun and W. Di, "A high-performance folded cascode amplifier," *Energy Procedia*, vol. 13, pp. 4026–4029, 2011.

- 11. M. Z. U. Rahman, G. Karthik, S. Fathima, and A. Lay-Ekuakille, "An efficient cardiac signal enhancement using time–frequency realization of leaky adaptive noise cancelers for remote health monitoring systems," *Measurement*, vol. 46, no. 10, pp. 3815–3835, 2013.

- 12. R. M. Abdullah, *A High CMRR Instrumentation Amplifier for Biopotential Signal Acquisition*. PhD thesis, Texas A&M University, 2011.

- 13. A. Bharadwaj and U. Kamath, "Techniques for accurate ecg signal processing," *EE Times*, vol. 14, 2011.

- 14. J. G. Lau and A. bin Marzuki, "A low power low noise cmos amplifier for portable ecg monitoring application," *ARPN Journal of Engineering and Applied Sciences*, vol. 9, no. 12, pp. 2448–2453,2014.

- 15. F. Moulahcene, N.-E. Bouguechal, I. Benacer, and S. Hanfoug, "Design of cmos two-stage operational amplifier for ecg monitoring system using 90nm technology," *system*, vol. 7, pp. 13–16, 2014.

- 16. X. Yang, Q. Cheng, L.-f. Lin, W.-w. Huang, and C.-d. Ling, "Design of low power low noise amplifier for portable electrocardiogram recording system applications," in *Anti-Counterfeiting, Security and Identification (ASID), 2011 IEEE International Conference on*, pp. 89–92, IEEE, 2011.

- 17. S. KARNIK, P. K. JAIN, and D. AJNAR, "Design of cmos instrumentation amplifier for ecg monitoring system using 0.18  $\mu$ m technology,"

- 18. Y. Shouli and E. Sanchez-Sinencio, "Low voltage analog circuit design techniques: A tutorial," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. 83, no. 2, pp. 179–196,2000.

- 19. X. Zou, X. Xu, L. Yao, and Y. Lian, "A 1-v 450-nw fully integrated programmable biomedical sensor interface chip," Solid-State Circuits, IEEE Journal of, vol. 44, no. 4, pp. 1067–1077, 2009.

- 20. H. Movahedi-Aliabad, M. Maymandi-Nejad, E. Shadkami, N. Khorashahian, and M. Mianji, "Design of an ecg signals amplifier with programmable gain and bandwidth based on a new method in pseudoresistor circuits," 2014.

- 21. Y. Nemirovsky, I. Brouk, and C. G. Jakobson, "1/f noise in cmos transistors for analog applications," Electron Devices, IEEE Transactions on, vol. 48, no. 5, pp. 921–927, 2001.

- 22. R. Vaddi, S. Dasgupta, and R. Agarwal, "Device and circuit design challenges in the digital subthreshold region for ultralow-power applications," *VLSI Design*, vol. 2009, p. 1, 2009.

- 23. G. Duzenli, Y. Kilic, H. Kuntman, and A. Ataman, "On the design of low-frequency filters using cmos otas operating in the subthreshold region," *Microelectronics Journal*, vol. 30, no. 1, pp. 45–54, 1999.

- 24. K. Sanapala, K. Madhuri, and M. S. Sanju, "Exploring emos logic families in sub-threshold region for ultra low power applications,"

- 25. L. George, G. D. Gargiulo, T. Lehmann, and T. J. Hamilton, "Concept design for a 1-lead wearable/implantable ecg front-end: Power management Sensors, vol. 15, no. 11, pp. 29297–29315, 2015.

- 26. C. Nanda, J. Mukhopadhyay, D. Mandal, and S. Chakrabarti, "A cmos instrumentation amplifier with low voltage and low noise for portable ecg monitoring systems," in *Semiconductor Electronics*, 2008. ICSE 2008. IEEE International Conference on, pp. 54–58, IEEE, 2008.

- 27. H. Liu, K.-T. Tang, J.-Y. Wu, and G. Wang, "A digitally trimmable low-noise low-power analog front-end for eeg signal acquisition," in *Biomedical and Health Informatics (BHI)*, 2012 IEEE-EMBS International Conference on, pp. 208–211, IEEE, 2012.

- 28. B. Wedro, "What is an electrocardiogram," January 2016.

- 29. I. Skaliora, M. Mavroidis, and E. Kouvelas, "Basis of cell excitability and cardiac conduction system," in *Introduction to Translational Cardiovascular Research*, pp. 31–47, Springer, 2015.

- 30. S. Emma, "A brief look at ecg sensor technology," *Retrieved on 6th January 2015, fromwww.mdtmag.com/article/2011/08/brief-look-ecg-sensor-technology*.

- 31. G. B. Moody and R. G. Mark, "The impact of the mit-bih arrhythmia database," *Engineering in Medicine and Biology Magazine, IEEE*, vol. 20, no. 3, pp. 45–50, 2001.

- 32. A. Reyners, B. Hazenberg, W. Reitsma, and A. Smit, "Heart rate variability as a predictor of mortality in patients with aa and al amyloidosis," *European heart journal*, vol. 23, no. 2, pp. 157–161,

2002.

- 33. J.-S. Wang, W.-C. Chiang, Y.-T. C. Yang, and Y.-L. Hsu, "An effective ecg arrhythmia classification algorithm," in *Bio-Inspired Computing and Applications*, pp. 545–550, Springer, 2011.

- 34. P. A. Laplante, *Comprehensive dictionary of electrical engineering*. CRC Press, 2005.

- 35. A. Goel and G. Singh, "Novel high gain low noise cmos instrumentation amplifier for biomedical applications," in *Machine Intelligence and Research Advancement (ICMIRA)*, 2013 International Conference on, pp. 392–396, IEEE, 2013.

- 36. K. Tretter, "Analogue techniques for extending battery life," *ELECTRONICS WORLD*, vol. 120, no. 1940, pp. 12–13, 2014.

- 37. M. Z. U. Rahman, G. Karthik, S. Fathima, and A. Lay-Ekuakille, "An efficient cardiac signal enhancement using time—frequency realization of leaky adaptive noise cancelers for remote health monitoring systems," *Measurement*, vol. 46, no. 10, pp. 3815–3835, 2013.

- 38. A. Bharadwaj and U. Kamath, "Techniques for accurate ecg signal processing," *EE Times*, vol. 14, 2011.

- 39. I. Toihria and T. Tixier, "Improved psrr and output voltage swing characteristics of folded cascode ota," 2015.

- 40. Y. Tseng, Y. Ho, S. Kao, and C. Su, "A 0.09 w low power front-end biopotential amplifier for biosignal recording," *Biomedical Circuits and Systems, IEEE Transactions on*, vol. 6, no. 5, pp. 508–516, 2012

- 41. Bandyopadhyay, Sayan, Mukherjee, Deep and Chatterjee, Rajdeep (2014), "Design of Two Stage CMOS Operational Amplifier in 180nm Technology with Low Power and High CMRR", Int. J. of Recent Trends in Engineering & Technology, Vol. 11, June 2014, ACEEE.

- 42. Kargaran, E., Khosrowjerdi, H. and Ghaffarzadegan, K. (2010), "A 1.5 v High Swing Ultra-Low-Power Two Stage CMOS OP-AMP in 0.18 μm Technology", in Mechanical and Electronics Engineering (ICMEE), 2010 2nd International Conference, Vol. 1, pp. V1-68–V1-71, 1-3 Aug. 2010, doi: 10.1109/ICMEE.2010.5558594

- 43. Kar, Sougata Kumar and Sen, Siddharta (2012), "A Highly Linear CMOS Transconductance Amplifier in 180 nm Process Technology", Analog Integr Circ Sig Process, Vol. 72, pp. 163–171, Springer

- 44. Luca, M., Francesco, A.A., Felice, C., Gregorio, C. and Giuseppe, I. (2012), "Design of a 75-nW, 0.5V Subthreshold Complementary Metal-oxidesemiconductor Operational Amplifier", International Journal of Circuit Theory & Applications, 2012.

- 45. Gupta, A., Mishra, D.K., Khatri, R., Chandrawat, U.B.S. and Jain, P. (2010), "A Two Stage and Three Stage CMOS OPAMP with Fast Settling, High DC Gain and Low Power Designed in 180nm Technology," in Computer Information Systems and Industrial Management Applications (CISIM), 2010 International Conference on , pp. 448–453, 8-10 Oct. 2010 doi: 10.1109/CISIM.2010.5643497

- 46. Zhang, J.Y. et al. (2009), "Design of Low-offset Low-power CMOS Amplifier for Biosensor Application", J. of Biomedical Science and Engineering, Vol. 2, pp. 538–542.

- 47. Zhang, L., Yu, Z. and He, X. (2009), "Design and Implementation of Ultralow Current-mode Amplifier for Biosensor Applications", IEEE Transaction on Circuits and Systems II: Express Briefs, Vol. 56, pp. 540–544, July 2009.

- 48. Chatterjee, S., Tsvidis, Y. and Kinget, P. (2005), "0.5V Analog Circuit Techniques and their Application in OTA and Filter Design", IEEE Journal of Solid State Circuits, Vol. 40(12), pp. 2373–2387.