# CHARGE-BASED COMPACT MODEL OF GATE-ALL-AROUND FLOATING GATE NANOWIRE WITH VARIABLE OXIDE THICKNESS FOR FLASH MEMORY CELL

MUHAMMAD AFIQ NURUDIN BIN HAMZAH

UNIVERSITI TEKNOLOGI MALAYSIA

# CHARGE-BASED COMPACT MODEL OF GATE-ALL-AROUND FLOATING GATE NANOWIRE WITH VARIABLE OXIDE THICKNESS FOR FLASH MEMORY CELL

### MUHAMMAD AFIQ NURUDIN BIN HAMZAH

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JUNE 2018

To my beloved family and friends.

#### ACKNOWLEDGEMENT

I would like to express my deepest appreciation to whom I owe a debt in completing this Phd work.

First, I would like to express my very great appreciation to my supervisor, Professor Dr. Razali Bin Ismail for such valuable advice and wonderful mentoring. Through his experience in man-management and enthusiasm, he paved the path for me in becoming a well-around academician and researcher. He tirelessly giving valuable advice and encouragement to become success in academia by rapidly and continually to publish academic work. He always quoted "*publish or perish*" has been a taboo and benchmark for me in pursuing success.

Secondly, I also thank to my co-supervisor, Dr. Nurul Ezaila Bt. Alias for all the technical support and advice that inevitably improved the quality of my work. Her endearing supervision has made me even more motivated in delivering positive and quality output for my research work.

My companions in the Computational Nanoelectronic Research lab for all the support in variety of ways. Special thanks to Lim Wei Hong, Fatimah Khairiah and Sakinah for sharing their ideas and giving significant contribution in improving my works. Not to forget Mr. Zulkifli, Maryati Morsin, Adila Syaidatul, Zuriana and Wei How for their support.

Million thanks to my family, especially to my parents, for all their understandings and emotional supports for giving me the encouragement to go forth in my career and life.

I would like to thank the Universiti Teknologi Malaysia (UTM) for the Zamalah Scholarship and it has been a privilege staying here. Last but not least, to the Ministry of Science, Technology and Industry (MOSTI) for providing funds for conference travels and publication charges.

#### ABSTRACT

Due to high gate electrostatic control and introduction of *punch* and *plug* process technology, the gate-all-around (GAA) transistor is very promising in, and apparently has been utilized for, flash memory applications. However, GAA Floating Gate (GAA-FG) memory cell still requires high programming voltage that may be susceptible to cell-to-cell interference. Scaling down the tunnel oxide can reduce the Program/Erase (P/E) voltage but degrades the data retention capability. By using Technology-Computer-Aided-Design (TCAD) tools, the concept of tunnel barrier engineering using Variable Oxide Thickness (VARIOT) of low-k/high-k stack is utilized in compensating the trade-off between P/E operation and retention characteristics. Four high-k dielectrics ( $Si_3N_4$ ,  $Al_2O_3$ ,  $HfO_2$  and  $ZrO_2$ ) that are commonly used in semiconductor process technology are examined with  $SiO_2$  as its low-k dielectric. It is found that by using  $SiO_2/Al_2O_3$  as the tunnel layer, both the P/E and retention characteristics of GAA-FG can be compensated. About 30% improvement in memory window than conventional SiO<sub>2</sub> is obtained and only 1% of charge-loss is predicted after 10 years of applying gate stress of -3.6V. Compact model of GAA-FG is initiated by developing a continuous explicit core model of GAA transistor (GAA Nanowire MOSFET (GAANWFET) and Juntionless Nanowire Transitor (JNT)). The validity of the theory and compact model is identified based on sophisticated numerical TCAD simulator for under 10% maximum error of surface potential. It is revealed that with the inclusion of partial-depletion conduction, the accuracy of the core model for GAANWFET is improved by more than 50% in the subthreshold region with doping-geometry ratio can be as high as about 0.86. As for JNT, despite the model being accurate for doping-geometry ratio upto 0.6, it is also independent of fitting parameters that may vary under different terminal biases or doping-geometry cases. The compact model of GAA-FG is completed by incorperating Charge Balance Model (CBM) into GAA transistor core model where good agreement is obtained with TCAD simulation and published experimental work. The CBM gives better accuracy than the conventional capacitive coupling approach under subthreshold region with approximately 10% error of floating gate potential. Therefore, the proposed compact model can be used to assist experimental work in extracting experimental data.

#### ABSTRAK

Oleh kerana kawalan elektrostatik get yang tinggi dan pengenalan kepada teknologi proses tebuk dan plak, transistor get-silinder-menyeluruh (GAA) sangat meyakinkan, dan telah digunakan dalam aplikasi memori *flash*. Walaubagaimanapun, GAA get terapung (GAA-FG) masih memerlukan voltan program yang tinggi yang mungkin terdedah kepada gangguan cell-to-cell. Pengecilan-skala terowong oksida dapat mengurangkan voltan program/padam (P/E) tetapi menyebabkan kemerosotan kepada daya-pengekalan datanya. Dengan menggunakan perisian rekabentukberbantukan-teknologi-komputer (TCAD), konsep Kejuruteraan Terowong Penghadang Oksida Boleh-ubah (VARIOT) k-rendah/k-tinggi telah digunakan dalam konteks mengimbangi kurang-lebih antara operasi program/padam dan daya-pengekalan data. Empat dielektrik k-tinggi (Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>) yang kebiasaannya terdapat dalam industri semikonduktor dianalisa dengan SiO<sub>2</sub> sebagai dielektrik k-rendah. Hasil simulasi menunjukkan gabungan SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> sebagai lapisan terowong GAA-FG dapat mengimbangi kurang-lebih antara operasi program/padam dan dayapengekalan data. Sebanyak 30% peningkatan jendela memori berbanding SiO<sub>2</sub> dan hanya 1% kehilangan cas dijangkakan selapas 10 tahun dikenakan voltan-get setinggi -3.6V. Model kompak bagi GAA-FG dimulai dengan penghasilan model eksplisit berterusan untuk transistor GAA (GAANWFET dan JNT). Kesahihan antara teori dan model kompak dipastikan berdasarkan perisian simulasi TCAD bagi ralat maksimum beza-upaya permukaan sebanyak 10%. Hasil menunjukkan, dengan mengambil kira kesan konduksi separa-habis dapat meningkatkan ketepatan model-teras GAANWFET sebanyak lebih daripada 50% dalam kawasan sub-ambang untuk nisbah dopan-geometri sehingga 0.86. Bagi JNT pula, disamping model kompaknya tepat untuk nisbah dopan-geometri sehingga 0.6, ia juga tidak bergantung kepada parameter-cubaan yang mungkin berubah-ubah bagi voltan-terminal atau nisbah dopan-geometri yang berbeza. Model kompak GAA-FG disempurnakan hasil gabungan model pengimbang-cas (CBM) dan model kompak transistor GAA yang mana ketepatannya teruji baik dengan simulasi TCAD dan hasil eksperimen yang sudah diterbit. CBM memberikan ketepatan yang lebih baik berbanding kaedah kapasitif-gandingan konvensional pada bahagian sub-ambang dengan ralat bezaupaya get-terapung sebanyak 10%. Oleh itu, model kompak yang dihasilkan dapat digunaakan untuk membantu kerja-kerja eksperimen bagi mengekstrak nilai parameter.

# TABLE OF CONTENTS

| CHAPTER |        | TITLE                                          | PAGE   |

|---------|--------|------------------------------------------------|--------|

|         | DECLA  | ARATION                                        | ii     |

|         | DEDIC  | ATION                                          | iii    |

|         | ACKN   | OWLEDGEMENT                                    | iv     |

|         | ABSTR  | RACT                                           | v      |

|         | ABSTR  | AK                                             | vi     |

|         | TABLE  | C OF CONTENTS                                  | vii    |

|         | LIST C | OF TABLES                                      | xi     |

|         | LIST C | <b>FFIGURES</b>                                | xii    |

|         | LIST C | <b>DF ABBREVIATIONS</b>                        | xxii   |

|         | LIST C | <b>DF SYMBOLS</b>                              | XXV    |

|         | LIST C | <b>DF APPENDICES</b>                           | xxviii |

| 1       | INTRO  | DUCTION                                        | 1      |

|         | 1.1    | Research Background                            | 1      |

|         | 1.2    | Flash Memory Scaling Challenges and Motivation | 3      |

|         | 1.3    | Problem Statements                             | 8      |

|         | 1.4    | Research Objectives                            | 11     |

|         | 1.5    | Research Scopes                                | 12     |

|         | 1.6    | Research Contribution                          | 12     |

|         | 1.7    | Thesis Organization                            | 13     |

| LITERATURE REVIEW |         | 15                                        |    |

|-------------------|---------|-------------------------------------------|----|

| 2.1               | Introdu | iction                                    | 15 |

| 2.2               | Gate-A  | ll-Around Floating Gate (GAA-FG) Structu- |    |

|                   | res     |                                           | 15 |

|                   | 2.2.1   | Planar GAA-FG Cell                        | 16 |

|                   | 2.2.2   | Vertical Channel GAA-FG cell              | 18 |

|                   |         |                                           |    |

2

|      |         | 2.2.2.1      | Conventional-Floating            |    |

|------|---------|--------------|----------------------------------|----|

|      |         |              | Gate/Stacked-Surrounding         |    |

|      |         |              | Gate Transistor (C-FG/S-SGT)     | 18 |

|      |         | 2.2.2.2      | Dual Control Gate-Surrounding    |    |

|      |         |              | Floating Gate (DC-SF)            | 19 |

|      |         | 2.2.2.3      | Separated-Sidewall Control       |    |

|      |         |              | Gate (S-SCG)                     | 20 |

|      |         | 2.2.2.4      | Sidewall Control Pillar (SCP)    | 22 |

| 2.3  | Barrier | Engineeri    | ng Concept                       | 23 |

|      | 2.3.1   | Crested      | Barrier                          | 24 |

|      | 2.3.2   | VARIab       | le Oxide Thickness (VARIOT)      | 27 |

|      | 2.3.3   | Crested      | Barrier versus VARIOT            | 30 |

| 2.4  | Device  | Modeling     |                                  | 31 |

|      | 2.4.1   | Overvie      | w of GAANWFET Core Models        | 35 |

|      | 2.4.2   | Overvie      | w of Junctionless Nanowire Tran- |    |

|      |         | sistor (J    | NT) Core Models                  | 44 |

|      | 2.4.3   | Explicit     | Solution to Core Model           | 51 |

|      | 2.4.4   | Floating     | Gate Potential Models            | 57 |

| 2.5  | Summa   | ary          |                                  | 63 |

| RESE | ARCH M  | ETHODO       | LOGY                             | 64 |

| 3.1  | Introdu | iction       |                                  | 64 |

| 3.2  | Resear  | ch Activitie | es                               | 65 |

| 3.3  | Device  | Optimizat    | ion and Characterization Appro-  |    |

|      | ach     | Ĩ            |                                  | 67 |

| 3.4  |         | Compact      | Modeling Approach                | 71 |

| 3.5  | Summa   | -            |                                  | 73 |

| GAA- | FG WITH | I VARIOT     | TUNNEL LAYER DESIGN              | 75 |

| 4.1  | Introdu |              |                                  | 75 |

| 4.2  | Parame  | eter Optimi  | zation of Asymmetric VARIOT      | 75 |

| 4.3  |         | FG Simulat   | -                                | 83 |

|      | 4.3.1   | Validati     | on Work of GAA-FG Memory         |    |

|      |         | Cell         |                                  | 83 |

|      | 4.3.2   | Device       | Performances of GAA-FG Cell      |    |

|      |         | Incorpo      | rating VARIOT Tunnel Layer       | 91 |

| 4.4  | Summa   | ary          |                                  | 96 |

| CHAI | RGE-BAS | ED COMPACT MODELING OF GAA-             |           |

|------|---------|-----------------------------------------|-----------|

| FG   |         |                                         | <b>98</b> |

| 5.1  | Introdu | iction                                  | 98        |

| 5.2  | Charge  | -Based Compact Model of GAANWFET        | 99        |

|      | 5.2.1   | Implicit Continuous Charge-Based Model  | 100       |

|      | 5.2.2   | Explicit Solution of Unified Charge     |           |

|      |         | Control Model (UCCM)                    | 104       |

|      | 5.2.3   | Current-Voltage (I-V), Charge-Voltage   |           |

|      |         | (Q-V) and Capacitance-Voltage (C-V)     |           |

|      |         | Characteristics                         | 109       |

|      | 5.2.4   | Partial-Depletion Conduction of GAAN-   |           |

|      |         | WFET                                    | 116       |

| 5.3  | Charge  | -Based Compact Model of Junctionless    |           |

|      | Nanow   | ire Transistor (JNT)                    | 124       |

|      | 5.3.1   | Implicit Continuous Charge-Based Model  | 125       |

|      | 5.3.2   | Explicit Solution of Unified Charge     |           |

|      |         | Control Model (UCCM)                    | 129       |

|      | 5.3.3   | Current-Voltage (I-V), Charge-Voltage   |           |

|      |         | (Q-V) and Capacitance-Voltage (C-V)     |           |

|      |         | Characteristics                         | 133       |

| 5.4  | Floatin | g Gate Potential Model of GAA-FG Memory |           |

|      | Cell    |                                         | 141       |

| 5.5  | Summa   | ary                                     | 147       |

| CON  | CLUSION | AND RECOMMENDATION                      | 149       |

| 6.1  | Introdu | iction                                  | 149       |

| 6.2  | Summa   | ary and Conclusion                      | 149       |

|      | 6.2.1   | TCAD simulation on optimization of      |           |

|      |         | VARIOT tunnel layer                     | 149       |

|      | 6.2.2   | TCAD simulation on GAA-FG perfor-       |           |

|      |         | mances using VARIOT tunnel layer        | 150       |

|      | 6.2.3   | Charge-based compact model of GAAN-     |           |

|      |         | WFET                                    | 150       |

|      | 6.2.4   | Charge-based compact model of JNT       | 151       |

|      | 6.2.5   | Charge-based compact model GAA-FG       |           |

|      |         | memory cell                             | 152       |

| 6.3  | Future  | Works                                   | 153       |

5

6

ix

| REFERENCES       | 157       |

|------------------|-----------|

| Appendices A – C | 172 – 192 |

# LIST OF TABLES

### TABLE NO.

### TITLE

### PAGE

| 2.1 | Common MOSFET models available in circuit simulators.                                        | 32  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | GAANWFET core models.                                                                        | 43  |

| 2.3 | Development of JNT core models.                                                              | 50  |

| 3.1 | Flash memory operational constraints.                                                        | 69  |

| 4.1 | Parameters for different dielectric materials used in simula-                                |     |

|     | tion.                                                                                        | 76  |

| 4.2 | Optimized parameters and extracted F-N coefficients for                                      |     |

|     | device characterization purpose.                                                             | 82  |

| 4.3 | Parameters used in simulation work and experimental GAA-                                     |     |

|     | FG cell in Lee et al., (2013).                                                               | 85  |

| 4.4 | VARIOT physical thickness and EOT used in simulation.                                        | 91  |

| A.1 | Parameters and data for SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> extracted from TCAD |     |

|     | simulation.                                                                                  | 172 |

| A.2 | Parameters and data for SiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> extracted from TCAD |     |

|     | simulation.                                                                                  | 174 |

| A.3 | Parameters and data for SiO <sub>2</sub> /HfO <sub>2</sub> extracted from TCAD               |     |

|     | simulation.                                                                                  | 176 |

| A.4 | Parameters and data for SiO <sub>2</sub> /ZrO <sub>2</sub> extracted from TCAD               |     |

|     | simulation.                                                                                  | 178 |

### LIST OF FIGURES

### FIGURE NO.

### TITLE

### PAGE

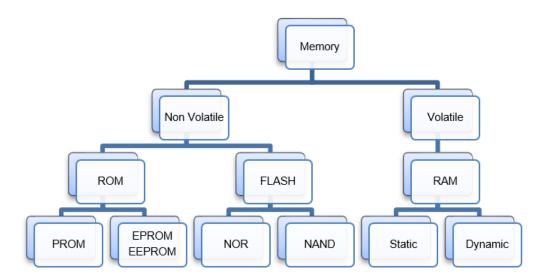

| 1.1 | The memory device based on Complementary Metal-                 |   |

|-----|-----------------------------------------------------------------|---|

|     | Oxide-Semiconductor (CMOS) technology divided into two          |   |

|     | categories, which are volatile and non-volatile.                | 1 |

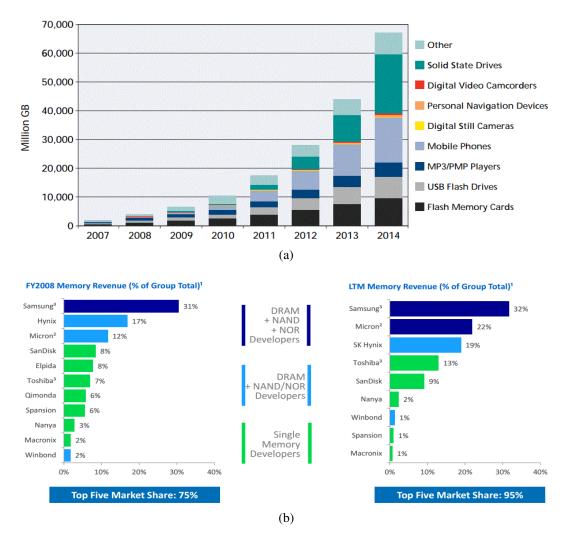

| 1.2 | (a) Number of storage capacity exponentially increase           |   |

|     | throughout the years with storage application devices is        |   |

|     | the highest. (Source from Forward Insight). (b) Memory          |   |

|     | revenue on some of the companies manufacturing various          |   |

|     | memory devices and the top five companies consolidation         |   |

|     | in memory industry, majorly dominated by companies that         |   |

|     | sold flash memory (source from Micron 2014 Winter Analyst       |   |

|     | Conference).                                                    | 3 |

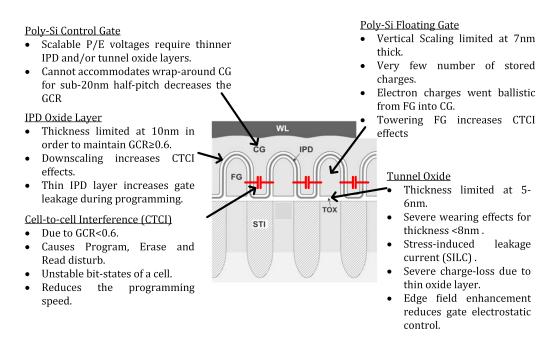

| 1.3 | Summarized the downscaling issues in term of performance        |   |

|     | related to the gate stack of the conventional wraparound FG     |   |

|     | cell in NAND flash memory.                                      | 4 |

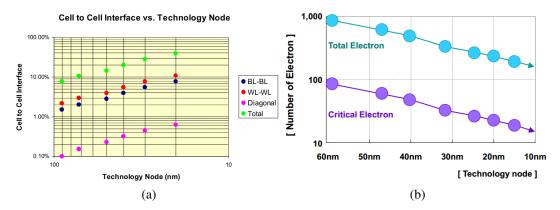

| 1.4 | Scaling limitation of 2-D NAND flash. (a) Increments in         |   |

|     | cell-to-cell interference of a victim cell across BL, WL and    |   |

|     | diagonal FGs and (b) decrements in number of electron in        |   |

|     | floating gate.                                                  | 5 |

| 1.5 | Roadmap from top semiconductor foundries for scaling 2-D        |   |

|     | and 3-D NAND flash architectures (source from ICinsight,        |   |

|     | 2014).                                                          | 6 |

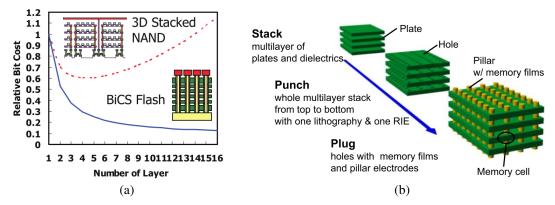

| 1.6 | (a) Comparison of relative bit cost of 3-D architecture NAND    |   |

|     | flash between the stacking of conventional 2-D planar NAND      |   |

|     | and Bit-Cost Scalable (BiCS) NAND technology as the             |   |

|     | number of layer increases. (b) BiCS fabrication method.         | 7 |

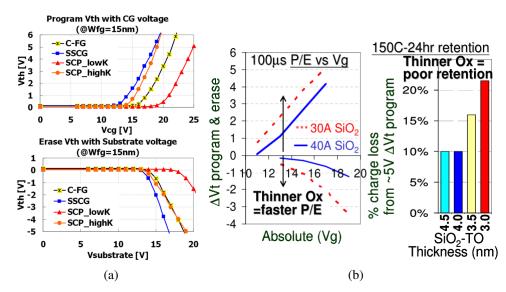

| 1.7 | (a) Comparison of threshold voltage shift after program with    |   |

|     | control gate voltage (Vcg) and after bulk erase between C-FG,   |   |

|     | S-SCG and SCP 3-D NAND cells. (b) Trade-off between P/E         |   |

|     | scalability and retention characteristics for differents tunnel |   |

|     | oxide thickness.                                                | 9 |

| 2.1 | (a) Fabrication steps for GAA-FG memory cell and (b) the cross-section of the device consists of control gate (CG), floating gate (FG), SiO <sub>2</sub> tunnel oxide, SiO <sub>2</sub> IPD layer and |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | poly-Si channel.                                                                                                                                                                                      | 16 |

| 2.2 | Electric field of (a) GAA-SONOS charge trapping and (b)                                                                                                                                               |    |

|     | GAA-FG during program at $10^{-6}$ and $10^{-3}$ s.                                                                                                                                                   | 17 |

| 2.3 | (a) Fabrication process steps for IMFT 3-D NAND flash C-                                                                                                                                              |    |

|     | FG memory cell and (b) the cross-section of its memory cell                                                                                                                                           |    |

|     | consists of control gate (CG), floating gate (FG), IPD oxide                                                                                                                                          |    |

|     | layer, tunnel oxide and poly-Si channel.                                                                                                                                                              | 19 |

| 2.4 | (a) Fabrication process steps for SK Hynix 3-D NAND flash                                                                                                                                             |    |

|     | DC-SF memory cell and (b) the cross-section of the memory                                                                                                                                             |    |

|     | cell showing the poly-Si floating gate (FG) and its two poly-Si                                                                                                                                       |    |

|     | control gates (CGs) with IPD oxide layer separating between                                                                                                                                           |    |

|     | them.                                                                                                                                                                                                 | 20 |

| 2.5 | (a) Fabrication process steps for SK Hynix 3-D NAND flash                                                                                                                                             |    |

|     | with S-SCG memory cell and (b) the cross-section of the                                                                                                                                               |    |

|     | memory cell showing the two SCGs act as electrical S/D                                                                                                                                                |    |

|     | layer.                                                                                                                                                                                                | 21 |

| 2.6 | (a) Fabrication process steps for SK Hynix 3-D NAND flash                                                                                                                                             |    |

|     | with SCP memory cell and (b) the cross-section of the                                                                                                                                                 |    |

|     | memory cell showing the poly-Si pillar and its dimension of                                                                                                                                           |    |

|     | length, $L_{scp}$ and width, $W_{scp}$ .                                                                                                                                                              | 22 |

| 2.7 | Shows the conduction band diagram of (a) typical uniform                                                                                                                                              |    |

|     | height barrier, (b) and (c) are the ideal form of symmetric                                                                                                                                           |    |

|     | and asymmetric crested barrier respectively. (d) and (e) are                                                                                                                                          |    |

|     | the actual form of symmetric and asymmetric crested barrier                                                                                                                                           |    |

|     | respectively. Parameter $e, V, U, U', d$ and $d'$ are the electron                                                                                                                                    |    |

|     | charge, applied bias, low-k energy barrier, high-k energy                                                                                                                                             |    |

|     | barrier, low-k layer thickness, and high-k layer thickness.                                                                                                                                           | 24 |

| 2.8 | Conduction band diagram between (a) typical uniform                                                                                                                                                   |    |

|     | barrier, (b) symmetric crested barrier and (c) asymmetric                                                                                                                                             |    |

|     | crested barrier during retention (no applied bias $V$ ) and after                                                                                                                                     |    |

|     | applied bias V. U is the low-k barrier height and U' is the                                                                                                                                           |    |

|     | high-k barrier height.                                                                                                                                                                                | 25 |

| 2.9 | The current density (dashed lines) and the gate recharging                                                                                                                                            |    |

|     | time (lines) of the crested barriers and single-layer barrier                                                                                                                                         |    |

|     | with various physical thickness. The notations of the plot (a)-                                                                                                                                       |    |

|     | (e) are in accordance to Figure 2.7.                                                                                                                                                                  | 26 |

|     |                                                                                                                                                                                                       |    |

xiii

| 2.10 | Comparison of $J_G$ against applied bias for crested and single-<br>layer barriers with same EOT of 5nm. Y <sub>3</sub> O <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> and ZrO <sub>2</sub> |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | have been used as the outer layer of crested barriers being                                                                                                                                  |    |

|      | $Al_2O_3$ and $SiO_2$ as the middle layer.                                                                                                                                                   | 27 |

| 2.11 | Schematic shows the stacking of (a) symmetric VARIOT and                                                                                                                                     |    |

|      | (b) asymmetric VARIOT with their respective band diagram                                                                                                                                     |    |

|      | at flat-band condition.                                                                                                                                                                      | 28 |

| 2.12 | Comparison of the conduction band diagram for (a)                                                                                                                                            |    |

|      | asymmetric and (b) symmetric VARIOT structures with the                                                                                                                                      |    |

|      | single-layer SiO2 barrier during retention and applied bias $V$ .                                                                                                                            | 28 |

| 2.13 | (a) Comparison of $J_G - V$ characteristics between VARIOT                                                                                                                                   |    |

|      | and single layer $SiO_2$ . (b) Summarizes the advantages of                                                                                                                                  |    |

|      | VARIOT (straight line) having steeper slope than $SiO_2$ (dotted                                                                                                                             |    |

|      | line) for EOT=5nm.                                                                                                                                                                           | 29 |

| 2.14 | Comparison of (a) $J_G - V_{FG}$ characteristics for various                                                                                                                                 |    |

|      | combinations of crested barrier and VARIOT with EOT=5nm.                                                                                                                                     |    |

|      | (b) Sketch of the conduction band diagram of symmetric                                                                                                                                       |    |

|      | VARIOT showing electron injection in both elastic and                                                                                                                                        |    |

|      | ineleastic limits.                                                                                                                                                                           | 31 |

| 2.15 | Definition of compact modeling with its analytical approa-                                                                                                                                   |    |

|      | ches and solution.                                                                                                                                                                           | 34 |

| 2.16 | Schematic cross-section of GAANWFET and its related variables.                                                                                                                               | 36 |

| 2.17 | Comparison of drain current between model and TCAD                                                                                                                                           |    |

|      | simulation (Circles) for $R = 10$ nm from intrinsic to high                                                                                                                                  |    |

|      | body concentration upto $1 \times 10^{19}$ cm <sup>-3</sup> .                                                                                                                                | 40 |

| 2.18 | (a) Normalized potential for intrinsic to body concentration                                                                                                                                 |    |

|      | of $3 \times 10^{18}$ cm <sup>-3</sup> . (b) Comparison of drain current between                                                                                                             |    |

|      | model in Zhang et. al., (2009) (Red lines) and Liu et. al.,                                                                                                                                  |    |

|      | (2008) (Black lines) with TCAD simulation (Squares) for                                                                                                                                      |    |

|      | R = 10nm.                                                                                                                                                                                    | 42 |

| 2.19 | Comparison of schematic structure between JNT device to                                                                                                                                      |    |

|      | the conventional inversion-mode (IM) transistor. JNT has                                                                                                                                     |    |

|      | identical dopant concentration in the body to that of the S/D                                                                                                                                |    |

|      | regions $(n^{+}/n^{+}/n^{+})$ .                                                                                                                                                              | 44 |

| 2.20 | Transfer characteristics and its operation regimes of (a)                                                                                                                                    |    |

|      | Junctionless Nanowire Transistor and (b) conventional                                                                                                                                        |    |

|      | inversion-mode GAANWFET.                                                                                                                                                                     | 45 |

|      |                                                                                                                                                                                              |    |

xiv

| 2.21 | Comparison of CV characteristics at gate terminal between<br>compact model developed by Oana <i>et al.</i> , (2014) with<br>TCAD Atlas simulation results for (a) various high-dopant |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | concentration and (b) small-radii.                                                                                                                                                    | 49 |

| 2.22 | Schematic of CCCM floating gate cell, where $C_{cg}$ , $C_{ox}$ , $C_d$ ,<br>and $C_s$ are the capacitances between FG and CG, channel,<br>drain and source respectively.             | 58 |

| 2.23 | · ·                                                                                                                                                                                   | 50 |

| 2.23 | I-V curves of reference (R) and floating gate devices (F) for $V = 0.1V$ (B1 and E1) and $V = 0.6V$ (B2 and E2). S is the                                                             |    |

|      | $V_d = 0.1$ V (R1 and F1) and $V_d = 0.6$ V (R2 and F2). S is the subthreshold along of the EC call and S is the subthreshold                                                         |    |

|      | subthreshold slope of the FG cell and $S_0$ is the subthreshold                                                                                                                       | 60 |

| 2.24 | slope of the reference cell.                                                                                                                                                          | 00 |

| 2.24 | Schematic of CBM FG memory cell, consists of control                                                                                                                                  |    |

|      | gate capacitance $C_{cg}$ , MOS transistor equivalent to the                                                                                                                          |    |

|      | memory cell, and voltage-controlled voltage source (VCVS)                                                                                                                             | (1 |

| 2.1  | of floating gate, $V_{fg}$ .                                                                                                                                                          | 61 |

| 3.1  | Research methodology flowchart of GAA-FG memory cell                                                                                                                                  |    |

|      | with VARIOT tunnel layer and GAA devices compact                                                                                                                                      |    |

|      | modeling.                                                                                                                                                                             | 66 |

| 3.2  | Flowchart for device simulation work.                                                                                                                                                 | 67 |

| 3.3  | Parameters involved in simulation of GAA-FG cell using                                                                                                                                |    |

|      | asymmetric VARIOT tunnel oxide with its comparative study.                                                                                                                            | 71 |

| 3.4  | Flowchart for device modeling work.                                                                                                                                                   | 72 |

| 4.1  | Metal-Oxide-Semiconductor (MOS) capacitor structure with                                                                                                                              |    |

|      | low-k/high-k stack as its gate oxide.                                                                                                                                                 | 76 |

| 4.2  | JV characteristics of $SiO_2/Si_3N_4$ for EOT=4nm. The                                                                                                                                |    |

|      | horizontal dashed-lines are the imposed constraints during                                                                                                                            |    |

|      | program, read-disturb and retention. The red dashed-lines just                                                                                                                        |    |

|      | to show the boundaries of electron tunneling mechanism for                                                                                                                            |    |

|      | $T_{ox}$ =3nm depending of $V_{tr}$ and $V_{fn}$ .                                                                                                                                    | 77 |

| 4.3  | $V_g - T_{ox}$ plot of program constraint for (a) SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> (b)                                                                                |    |

|      | $SiO_2/Al_2O_3$ (c) $SiO_2/HfO_2$ and (d) $SiO_2/ZrO_2$ .                                                                                                                             | 79 |

| 4.4  | $V_g - T_{ox}$ plot of read-disturb and retention constraints for (a)                                                                                                                 |    |

|      | $SiO_2/Si_3N_4$ (b) $SiO_2/Al_2O_3$ (c) $SiO_2/HfO_2$ and (d) $SiO_2/ZrO_2.$                                                                                                          |    |

|      | The upper plot $(V_g > 0)$ is after imposing the read-disturb                                                                                                                         |    |

|      | constraint at $J_g = 7 \times 10^{-11} \text{A/cm}^2$ and the lower plot                                                                                                              |    |

|      | $(V_g \leq 0)$ is after imposing the retention constraint at $J_g =$                                                                                                                  |    |

|      | $2 \times 10^{-16}$ A/cm <sup>2</sup> . The symbols are consistent with legend in                                                                                                     |    |

|      | Figure 4.3.                                                                                                                                                                           | 80 |

|      |                                                                                                                                                                                       |    |

| 4.5  | Optimized gate voltage for each EOT of all asymmetric VARIOTs due to (a) retention constraint of > -1.5V  and (b) a more restrictive read-disturb constraint of >3.6V.                                                                                                    | 81 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | <ul> <li>(a) The cross-section of experimental GAA-FG with triangular nanowire.</li> <li>(b) The cross-section of GAA-FG structure showing silicon nanowire channel and source/drain region with its electrode, and poly-Si FG being surrounded by</li> </ul>             |    |

|      | SiO <sub>2</sub> .                                                                                                                                                                                                                                                        | 84 |

| 4.7  | Comparison of transfer characteristics between 3-D simula-<br>tion with experimental data by Lee <i>et al.</i> , (2013) for drain bias<br>of 0.1V and 1.0V. Device simulation with (line) and without<br>(dashed-line) definition of interface traps near the conduction  |    |

|      | are also shown.                                                                                                                                                                                                                                                           | 86 |

| 4.8  | Comparison of P/E characteristics between simulation and<br>experimental data in Lee <i>et al.</i> , (2013) for a given P/E<br>voltages of 10/-8V up to 10ms. P/E characteristics of GAA-<br>FG cell with $T_{ox}$ scaling limit of 6nm SiO <sub>2</sub> to indicate fast |    |

|      | charging.                                                                                                                                                                                                                                                                 | 87 |

| 4.9  | Electric field distribution along the radial direction of GAA-                                                                                                                                                                                                            |    |

|      | FG cell in (a) simulation and (b) extracted experimental result                                                                                                                                                                                                           |    |

|      | in Lee <i>et al.</i> , (2013).                                                                                                                                                                                                                                            | 88 |

| 4.10 | Comparison of retention characteristics between GAA-FG cell of 8nm and 11nm SiO <sub>2</sub> with experimental data (black) in Lee <i>et al.</i> , (2013) after a P/E cycle for P/E voltages of 10/-8V and P/E time of 5/2ms. The lines are the 10 years                  |    |

|      | extrapolation results of threshold voltage using Power's law.                                                                                                                                                                                                             | 90 |

| 4.11 | (a) Fabrication process of C-FG cell with an additional deposition of high-k dielectric before low-k and poly-Si channel were form. (b) Schematic diagram of GAA-FG cell with asymmetric VARIOT as tunnel oxide layer. $T_{ox}$ and $T_{H}$                               |    |

|      | are the thickness for low-k and high-k dielectric materials.                                                                                                                                                                                                              | 91 |

| 4.12 | JV characteristics for various low-k/high-k tunnel layer. All stacks have physical thickness of 11nm. The 6nm and 8nm $SiO_2$ layer are the control device to indicate high program current and retention characteristics. Steeper slope and gate                         |    |

|      | current density are achieved with decreasing of EOT.                                                                                                                                                                                                                      | 92 |

|      |                                                                                                                                                                                                                                                                           |    |

xvi

| 4.13 | (a) C-V curves for various low-k/high-k tunnel layer. (b) Electric field profile of GAA-FG cells across the gate stack. $SiO_2/Al_2O_3$ stack yield the utmost surface field at Si/SiO <sub>2</sub>        |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | interface.                                                                                                                                                                                                 | 93  |

| 4.14 | Comparison of P/E characteristics of GAA-FG cell using<br>VARIOT tunnel layer with GAA-FG of 6nm SiO <sub>2</sub> . indicates<br>faster P/E operation but higher voltage is required for erase             |     |

|      | operation.                                                                                                                                                                                                 | 94  |

| 4.15 | Retention characteristics of GAA-FG with VARIOT tunnel<br>layer of (a) $SiO_2/Si_3N_4$ (b) $SiO_2/Al_2O_3$ , (c) $SiO_2/HfO_2$ and (d)<br>$SiO_2/ZrO_2$ under gate stress of -3.6/3.6V. Data retention for |     |

|      | GAA-FG of 8nm SiO <sub>2</sub> is plotted to benchmark 20% charge-<br>loss under similar gate stress.                                                                                                      | 96  |

| 4.16 | Performance comparison of GAA-FG incorporating VARIOT                                                                                                                                                      | 90  |

| 4.10 | tunnel layer with experimental results in Lee <i>et al.</i> , (2013).                                                                                                                                      | 97  |

| 5.1  | Schematic diagram for n-channel GAANWFETs with                                                                                                                                                             | 21  |

|      | cylindrical coordinate system. The diagram also shows the                                                                                                                                                  |     |

|      | distribution of interface trap densities, $D_{it}$ and fixed oxide                                                                                                                                         |     |

|      | charges, $Q_f$ .                                                                                                                                                                                           | 100 |

| 5.2  | Comparison of mobile charge density between explicit expression of Equation (5.16) with iterative/implicit solution                                                                                        |     |

|      | of Equation (5.13).                                                                                                                                                                                        | 105 |

| 5.3  | Comparison of $Q_m$ against $V_g$ curves at $V_d = 0$ V between                                                                                                                                            | 100 |

|      | explicit model (5.19) and implicit model from intrinsic ( $N_A =$                                                                                                                                          |     |

|      | $1.45 \times 10^{10} \text{cm}^{-3}$ ) to higher doping concentration of 1 ×                                                                                                                               |     |

|      | $10^{19} \text{cm}^{-3}$ .                                                                                                                                                                                 | 107 |

| 5.4  | Comparison of $Q_m$ against $V_g$ curves at $V_d = 0$ V between                                                                                                                                            |     |

|      | explicit model (5.19) and implicit UCCM for a wide range of                                                                                                                                                |     |

|      | $R$ in (a) intrinsic and (b) higher doping concentration ( $N_A =$                                                                                                                                         |     |

|      | $1 \times 10^{19} \text{cm}^{-3}$ ).                                                                                                                                                                       | 107 |

| 5.5  | Comparison of $Q_m$ against $V_g$ curves at $V_d = 0.05$ V, between                                                                                                                                        |     |

|      | explicit model (5.19) and implicit UCCM for various range of                                                                                                                                               |     |

|      | $Q_f$ in (a) intrinsic and (b) higher doping concentration ( $N_A =$                                                                                                                                       | 100 |

| 5 6  | $1 \times 10^{19}$ cm <sup>-3</sup> ).                                                                                                                                                                     | 108 |

| 5.6  | Comparison of $Q_m$ against $V_g$ curves at $V_d = 0.05$ V, between<br>explicit model (5.10) and implicit LICCM for various range of                                                                       |     |

|      | explicit model (5.19) and implicit UCCM for various range of $D_{it}$ in (a) intrinsic and (b) higher doping concentration ( $N_A =$                                                                       |     |

|      | $D_{it}$ in (a) mutual and (b) higher doping concentration ( $N_A = 1 \times 10^{19} \text{ cm}^{-3}$ ).                                                                                                   | 108 |

|      | 1 / 10 VIII <i>]</i> ,                                                                                                                                                                                     | 100 |

| 5.7  | Assuming zero trap state density ( $Q_f = 0$ , and $\eta = 1$ ), (a) shows the $I_{ds} - V_g$ curves of GAANWFET from intrinsic to high doping concentration and (b) the $I_{ds} - V_d$ curves with with a space of exercise sector curves are exercised with 2D |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | wide range of operating gate voltage are verified with 3D device simulation.                                                                                                                                                                                     | 110 |

| 5.8  | Given $Q_m$ from (5.19), comparison of $I_{ds} - V_g$ for (a)                                                                                                                                                                                                    |     |

|      | fixed oxide charges and (b) interface trap densities against                                                                                                                                                                                                     | 110 |

| 5.9  | numerical simulation are in good agreement.                                                                                                                                                                                                                      | 110 |

| 5.9  | Comparison between explicit models in Cheralathan <i>et al.</i> , (2011) and (5.19) with implicit UCCM solution for $N_A = 1 \times$                                                                                                                             |     |

|      | $10^{17}$ cm <sup>-3</sup> and $N_A = 1 \times 10^{19}$ cm <sup>-3</sup> . (a) Shows the $Q_m$ against $V_g$                                                                                                                                                     |     |

|      | curves and (b) $I_{ds}$ against $V_g$ at $V_d = 1.0$ V.                                                                                                                                                                                                          | 111 |

| 5.10 | Comparison between analytical model with numerical TCAD                                                                                                                                                                                                          |     |

|      | simulation of (a) normalized transconductance and (b)                                                                                                                                                                                                            |     |

|      | conductance for $V_d$ =0.05V and 1.0V. Terminal charges of                                                                                                                                                                                                       |     |

|      | GAANWFET (c) against $V_g$ and (d) against $V_d$ for $N_A$ =                                                                                                                                                                                                     |     |

|      | $3 \times 10^{18}$ cm <sup>-3</sup> . The parameters are consistent for all figures.                                                                                                                                                                             | 113 |

| 5.11 | Comparison of intrinsic capacitances across (a)-(c) gate                                                                                                                                                                                                         |     |

|      | voltage and (b) drain voltage between analytical models with                                                                                                                                                                                                     |     |

|      | numerical TCAD simulation results for heavily doped body                                                                                                                                                                                                         |     |

|      | of $N_A=3\times10^{18}$ cm <sup>-3</sup> . Analytical models fairly predict the                                                                                                                                                                                  |     |

|      | transition region for a given accurate explicit solution of the<br>mobile charge expression. Symbols are consistent for both                                                                                                                                     |     |

|      | plots.                                                                                                                                                                                                                                                           | 115 |

| 5.12 | Surface potential due to dopant carrier in partial-depletion                                                                                                                                                                                                     | 115 |

| 0112 | conduction of Equation (5.36) and full-depletion conduction                                                                                                                                                                                                      |     |

|      | of Equation (5.37) for (a) FD-GAANWFET and (b) PD-                                                                                                                                                                                                               |     |

|      | GAANWFET. The partial-depletion conduction is shown to                                                                                                                                                                                                           |     |

|      | be affected by (c) dopant concentration and (d) radius.                                                                                                                                                                                                          | 118 |

| 5.13 | Surface and center potentials of GAANWFET with                                                                                                                                                                                                                   |     |

|      | $N_A = 1 \times 10^{19} \text{ cm}^{-3}$ computed using unified function of N                                                                                                                                                                                    |     |

|      | for (a) $N=4$ and (b) $N=12$ . Optimum value of N is obtained                                                                                                                                                                                                    |     |

|      | by comparing with TCAD simulation.                                                                                                                                                                                                                               | 120 |

| 5.14 | Optimum value of $N$ extracted by comparison with TCAD                                                                                                                                                                                                           |     |

|      | simulation. The proposed model for $N$ (red-line) fit well                                                                                                                                                                                                       |     |

|      | with extracted data (dot-symbol). Inset shows the error of                                                                                                                                                                                                       |     |

|      | analytical model with referenced to TCAD simulation results<br>for varying $aN \cdot P^2/4c_{T}$ ratio                                                                                                                                                           | 120 |

|      | for varying $qN_AR^2/4\epsilon_{Si}$ ratio.                                                                                                                                                                                                                      | 120 |

| 5.15 | Surface potential model with and without the inclusion of<br>partial-depletion conduction compared to TCAD simulation<br>for (a) different dopant concentration and (b) its percentage                                           |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | error; for (c) different radii and (d) its percentage error.                                                                                                                                                                     | 121 |

| 5.16 | Comparison of (a) mobile charge density and (b) transfer characteristics for various dopant concentration.                                                                                                                       | 122 |

| 5.17 | Transfer characteristics with various radii for dopant con-<br>centration of (a) $N_A=1\times10^{16}$ cm <sup>-3</sup> and (b) $N_A=1\times10^{18}$ cm <sup>-3</sup> .<br>Output characteristics for dopant concentration of (c) |     |

|      | $N_A = 1 \times 10^{16} \text{ cm}^{-3}$ and (d) $N_A = 1 \times 10^{18} \text{ cm}^{-3}$ respectively.                                                                                                                          | 123 |

| 5.18 | Schematic diagram for JNT with cylindrical coordinate system. The diagram also shows the interface trap densities, $D_{it}$ and the fixed oxide charges, $Q_f$ are assume to be uniformly distributed along the                  |     |

|      | channel.                                                                                                                                                                                                                         | 125 |

| 5.19 | Assessment of UCCM model for all operating regions of JNT at $V_d = V_s = 0V$ . The red vertical lines denote the threshold                                                                                                      |     |

|      | and flat-band voltages to indicate the boudaries of operating                                                                                                                                                                    |     |

|      | region from full-depletion (FD), partial-depletion (PD) and accumulation (ACC).                                                                                                                                                  | 129 |

| 5.20 | Mobile charge density for depletion $(Q_{DP})$ and comple-                                                                                                                                                                       | 12) |

|      | mentary $(Q_C)$ parts at $V_d$ =0V. The total mobile charge $Q_m$                                                                                                                                                                |     |

|      | agreed well with numerical simulation by making $Q_C$ as                                                                                                                                                                         |     |

|      | complementary charge to $Q_{DP}$ .                                                                                                                                                                                               | 131 |

| 5.21 | (a) Comparison of surface potential computed using                                                                                                                                                                               |     |

|      | analytical model with referenced to TCAD simulation and (b)                                                                                                                                                                      |     |

| 5 00 | its error.                                                                                                                                                                                                                       | 132 |

| 5.22 | Comparison of mobile charge density between proposed model with Duarte <i>et al.</i> , (2012) that was solved using                                                                                                              |     |

|      | iterative method for various (a) dopant concentration and (b)                                                                                                                                                                    |     |

| 5.00 | radius.                                                                                                                                                                                                                          | 133 |

| 5.23 | Transfer characteristics of JNT for various (a) high dopant<br>concentration and (b) radius compared to numerical TCAD                                                                                                           |     |

|      | simulation.                                                                                                                                                                                                                      | 135 |

| 5.24 | Output characteristics for R=10nm at dopant concentration of<br>(a) $N_D = 5 \times 10^{18} \text{ cm}^{-3}$ and (b) $N_D = 1 \times 10^{19} \text{ cm}^{-3}$ .                                                                  | 136 |

| 5.25 | Comparison of (a) transconductance, (b) conductance and                                                                                                                                                                          |     |

|      | terminal charges against (c) gate voltage and (d) drain voltage.                                                                                                                                                                 | 139 |

- 5.26 Comparison of all the capacitances (i.e.:- self-capacitances and transcapacitances) across (a)-(c) gate voltage and (d) drain voltage between analytical models with numerical TCAD simulation results for dopant concentration of  $N_D=1\times10^{19}$  cm<sup>-3</sup>. Analytical models fairly predict the partial depletion region. Symbol and parameter are consistent for all plots.

- 5.27 Cross-section of a symmetrical GAA-FG. R is the radius, L<sub>g</sub> is the gate length while T<sub>ox</sub> and T<sub>IPD</sub> are the tunnel oxide and IPD oxide thicknesses respectively. C<sub>cg</sub> is the FG-CG capacitance, C<sub>ox</sub> is the tunnel oxide capacitance and the intrinsic capacitances with respect to floating gate terminal are denoted as C<sub>gd</sub> and C<sub>gs</sub>. The channel charge, Q<sub>ch</sub> is equal to the total charge across the gate stack that sum as Q<sub>fg</sub> + C<sub>cg</sub> (V<sub>cg</sub> V<sub>fg</sub>).

5.28 Floating gate potential for various (a) drain voltage and

- (b) predefined  $Q_{fg}$ . For CCCM, fixed capacitive ratios of  $\alpha_{cg}$ =0.64 and  $\alpha_d$ =0.18 are re-used from CBM to fit with TCAD simulation as well as total capacitance given as  $C_{tot}=C_{cg}+C_{ox}+C_d+C_s$ , with  $C_d$  and  $C_s$  are extracted from TCAD simulation as 0.038fF and 0.12fF respectively. 143 5.29 Transfer characteristics of GAA-FG for various (a) drain

- voltage and (b) predefined  $Q_{fq}$ . 143 (a) Comparison of proposed model with experimental data. 5.30 All parameters remain the same as in Table 4.2 except for  $Q_f$  and interface traps parameter  $\eta$  that are treated as fitting parameter. (b) Comparison of floating gate potential between proposed model and CCCM approach with referenced to TCAD simulation. Fixed capacitive ratio of  $\alpha_{cq}$ =0.73 and  $\alpha_d$ =0.14 from CBM is re-used in CCCM approach. 145 5.31 (a) Control gate coupling  $(\alpha_{cq})$  and (b) drain coupling  $(\alpha_d)$ ratios of GAA-FG for  $Q_{fg}=0$  and varying  $V_{cg}$  and  $V_d$  using  $V_{fq}$  calculated from the charge balance model. 146 5.32 Comparison of GCR at  $V_d$ =0V for VARIOT tunnel layer with referenced to conventional 11nm SiO<sub>2</sub> tunnel layer of GAA-

FG fabricated in Lee et al., (2013).

140

142

147

| 6.1 | An array of 3-D FG-NAND that consists of four FG cell                                               |     |

|-----|-----------------------------------------------------------------------------------------------------|-----|

|     | and two select transistors. Capacitances show the coupling                                          |     |

|     | between selected FG cell with neigbouring-FG (NFG),                                                 |     |

|     | control gate and neighbouring control gate (NCG).                                                   | 154 |

| 6.2 | (a) Block diagram of read path-circuit and its (b) sense                                            |     |

|     | amplifier.                                                                                          | 156 |

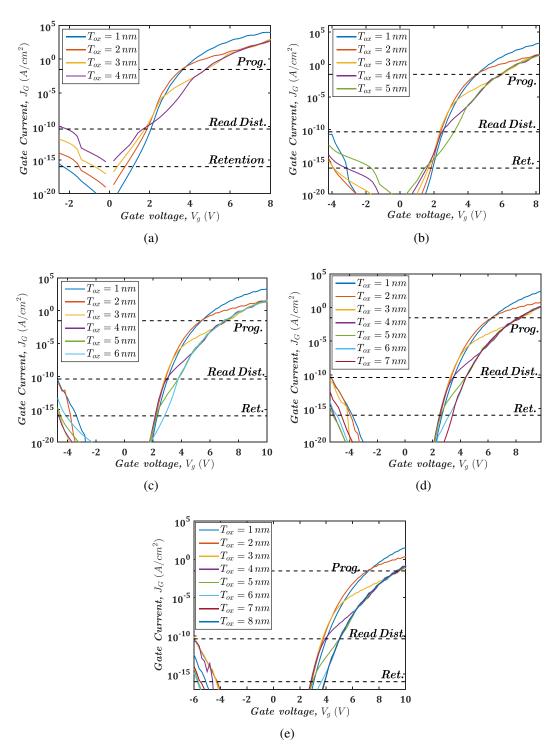

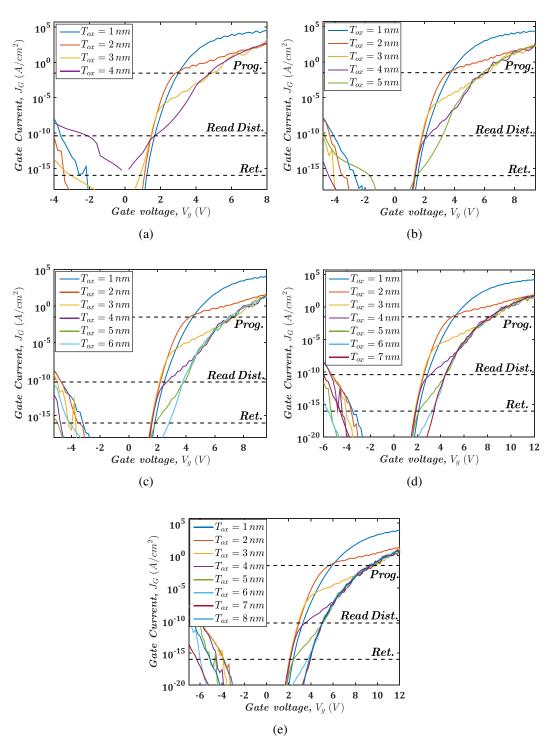

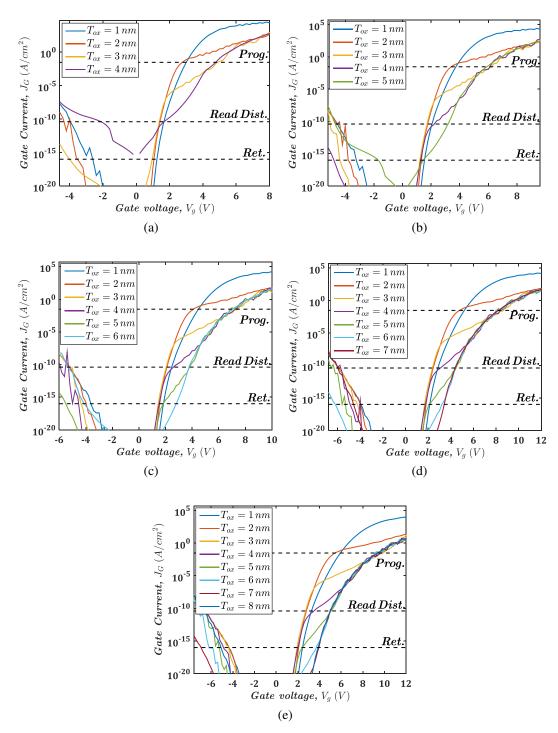

| A.1 | $J_g - V_g$ characteristics of SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> for EOT (a) 4nm (b) |     |

|     | 5nm (c) 6nm (d) 7nm and (e) 8nm.                                                                    | 173 |

| A.2 | $J_g - V_g$ characteristics of SiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> for EOT (a) 4nm (b) |     |

|     | 5nm (c) 6nm (d) 7nm and (e) 8nm.                                                                    | 175 |

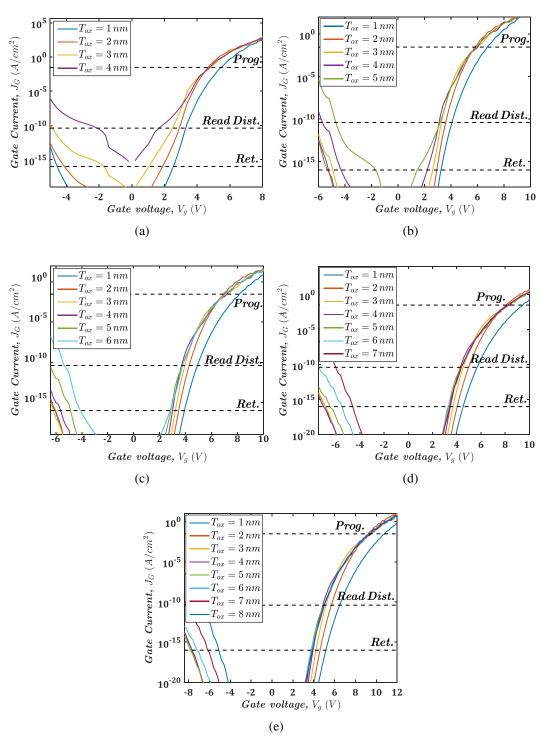

| A.3 | $J_g - V_g$ characteristics of SiO <sub>2</sub> /HfO <sub>2</sub> for EOT (a) 4nm (b) 5nm           |     |

|     | (c) 6nm (d) 7nm and (e) 8nm.                                                                        | 177 |

| A.4 | $J_g - V_g$ characteristics of SiO <sub>2</sub> /ZrO <sub>2</sub> for EOT (a) 4nm (b) 5nm           |     |

|     | (c) 6nm (d) 7nm and (e) 8nm.                                                                        | 179 |

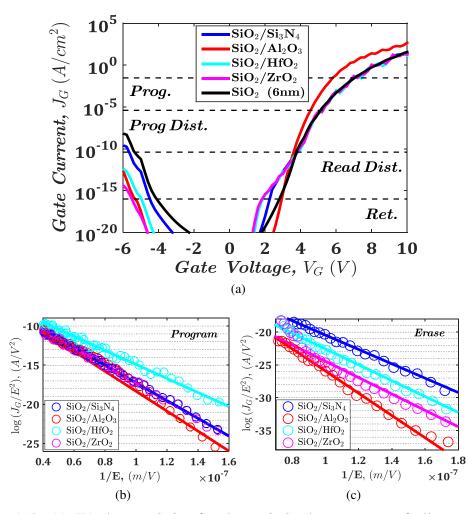

| A.5 | (a) JV characteristics for the optimized parameters of all                                          |     |

|     | asymmetric VARIOTs conducted. F-N plot of all asymmetric                                            |     |

|     | VARIOTs conducted for (b) programming and (c) erase                                                 |     |

|     | operations.                                                                                         | 180 |

# LIST OF ABBREVIATIONS

| ACM      | - | Adcanced Compact MOSFET                             |

|----------|---|-----------------------------------------------------|

| ALCVD    | - | Atomic Layer Chemical Vapor Deposition              |

| AT       | - | Above Threshold                                     |

| BiCS     | - | Bit-Cost Scalable                                   |

| BIOS     | - | Basic Input Output Storage                          |

| BT       | - | Below Threshold                                     |

| BSIM     | - | Berkeley Short-Channel IGFET Model                  |

| CBM      | - | Charge Balance Model                                |

| CCCM     | - | Capacitive Coupling Coefficient Model               |

| C-FG     | - | Conventional-Floating Gate                          |

| CD-ROM   | - | Compact-Disk Read-Only-Memory                       |

| CLM      | - | Channel Length Modulation                           |

| CMOS     | - | Complementary Metal-Oxide-Semiconductor             |

| СТ       | - | Charge Trapping                                     |

| CTCI     | - | Cell-to-Cell Interference                           |

| DC-SF    | - | Dual-Control Gate Surrounding-Floating Gate         |

| DIBL     | - | Drain Induced Barrier Lowering                      |

| DRAM     | - | Dynamic Random Access Memory                        |

| DVD-ROM  | - | Digital-Versatile-Disc Read-Only-Memory             |

| DQT      | - | Direct Quantum Tunneling                            |

| EEPROM   | - | Electrically Erasable Programmable Read-Only-Memory |

| EKV      | - | Enz-Krummenacher-Vittoz                             |

| EPROM    | - | Erasable Programmable Read-Only-Memory              |

| EOT      | - | Effective Oxide Thickness                           |

| ETOX     | - | EPROM Tunnel Oxide                                  |

| FG       | - | Floating Gate                                       |