# DESIGN AND ANALYSIS OF A 2.5-GHz OPTICAL RECEIVER ANALOG FRONT-END USING GEIGER MODE PHOTODIODE IN A 0.13 µm CMOS PROCESS

LEONG CHOON WEI

UNIVERSITI TEKNOLOGI MALAYSIA

# DESIGN AND ANALYSIS OF A 2.5-GHz OPTICAL RECEIVER ANALOG FRONT-END USING GEIGER MODE PHOTODIODE IN A 0.13 µm CMOS PROCESS

## LEONG CHOON WEI

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Computer and Microelectronic Systems)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JUNE 2018

Specially dedicated to my supervisor and family who encouraged me throughout my journey of education.

#### ACKNOWLEDGEMENT

First and foremost, I would like to express my sincerest gratitude to Senior Lecturer **Dr.Suhaila Binti Isaak**, who is my final year project supervisor, for spending her invaluable time to give guidance in the execution of this project. Her constructive advise, ideas and suggestions have helped me to always stay focus on the main direction and objective of the project. Moreover, she also assumed responsibility on the debugging design tool and infrastructure issues together with me; suggests workarounds and provides solutions to help me overcome those obstacles so that I can continue working on the project and finally, completed the thesis.

Secondly, I would like to thank **Mr Izam Bin Kamisian**, lecturer, for his help in providing advises and tutorial material on the circuit layout work of this project. I also want to thank the examiners of this work, **Dr Nurul Ezaila Binti Alias** and **Dr Masture Shafinaz Binti Zainal Abidin** for their comments of improvement given in the project presentation session.

Last but not least, I would like to express my appreciation to my family, friends and colleagues for their constant support and encouragement given.

#### ABSTRACT

The optical receiver analog front-end using geiger mode photodiode have several design challenges, especially in high-speed application. The parasitic capacitance (CPD) of the geiger mode photodiode (PD) is large, can be several pico farads which significantly limits the bandwidth (BW) of the geiger mode photodiode. In addition, a very weak current signal which is generated by the geiger mode photodiode limits the number of photon count by the receiver circuit. To address this problem, the amplification stage followed the geiger mode photodiode must be designed to amplify the detected signal using a low voltage CMOS process device. Hence, low input impedance amplifier topologies such as common gate (CG) transimpedance amplifier (TIA) is usually employed. The applications of optical receiver are in high-speed optical communication system. Therefore, it is essential for the analog front-end (AFE) receiver (RX) which consists the PD and TIA to have a large bandwidth, usually in the range of several GHz. This project aims to design a 2.5 GHz optical AFE RX using PD in a 0.13 µm CMOS process. To comprehend the limitation of previous TIA topologies which have designed by the other researcher, these topologies are designed and simulated in lower supply voltage at 1.2 V and 0.13 µm CMOS process to assist the characterization of proposed TIA circuit for this project. Pre-layout simulation is performed and the circuit performance is analysed to define the topology that give the best performance to be used. Post layout simulation is performed on the chosen design. CG TIA is justified to be used in this project as the literature shows that it can achieve BW larger than 2.5 GHz compared to common source (CS) TIA. As a result, two TIAs which are the CG with common source active feedback (CSFB) and regulated cascode (RGC) are compared. With ideal resistor and ideal current source, the RGC outperformed CSFB in term of BW and gain. Hence, this project employed RGC topology to achieve the objective. The ideal circuit components are replaced with CMOS circuit to improve area and make the entire circuit fully on-chip. The BW achieved by the designed RGC TIA is 2.47 GHz with a TI gain of 53.8 dB $\Omega$  under large C<sub>PD</sub> of 2 pF. It is proven by this work that the RGC TIA is capable operating in the GHz frequency range with large  $C_{PD}$  even the process shrink to 0.13 µm and the supply reduced to 1.2 V.

#### ABSTRAK

Penerima optik hadapan depan analog (RX AFE) menggunakan fotodiod mempunyai beberapa cabaran reka bentuk. Kapasitans parasit (paraCap) fotodiode (PD) yang besar menghadkan jalur lebar (BW) fotodiode. Di samping itu, isyarat arus yang sangat lemah yang dijana oleh fotodiode mengehadkan bilangan pengiraan foton oleh litar penerima. Untuk menangani masalah ini, tahap penguatan diikuti fotodiod mesti direka untuk menguatkan isyarat yang dikesan menggunakan peranti proses CMOS voltan rendah. Oleh itu, topologi penguat bagi impedans pemasukan yang rendah seperti penguat transimpedans (TIA) get sepunya (CG) biasanya digunakan. Aplikasi penerima optik berada dalam komunikasi optik berkecepatan tinggi. Oleh itu, adalah penting bagi penerima yang terdiri daripada PD dan TIA mempunyai jalur lebar yang besar, biasanya dalam pelbagai GHz. Projek ini bertujuan untuk merekabentuk AFE RX optik 2.5 GHz menggunakan PD dalam proses CMOS 0.13 µm. Untuk memahami batasan topologi TIA yang telah direka oleh para penyelidik yang lain sebelum ini, beberapa topologi TIA itu telah disimulasikan dalam voltan bekalan rendah pada 1.2 V dan 0.13 µm CMOS proses. Ini adalah untuk membantu pencirian litar TIA untuk projek ini. Simulasi pra-pelan reka bentuk dilakukan dan prestasi litar dianalisis bagi menentukan topologi yang memberikan prestasi terbaik dipilih untuk digunakan. Simulasi pasca pelan reka bentuk juga dilakukan. Akhirnya, penambahbaikan dibuat berdasarkan hasil poslay sim. CG TIA adalah wajar untuk digunakan dalam projek ini kerana sastera menunjukkan bahawa ia boleh mencapai BW lebih besar daripada 2.5 GHz berbanding dengan pemancar sepunya (CS) TIA. Akibatnya, dua CG TIA yang bername CG dengan maklum balas pemancar sepunya (CSFB) dan caskod terkawal (RCG) dibandingkan. Dengan perintang ideal dan sumber arus yang ideal, RGC mengatasi CSFB dari segi BW dan keuntungan. Oleh itu, projek ini mencadangkan CG dengan RGC diguna untuk mencapai matlamat projeck ini. Komponen litar yang ideal akan diganti dengan litar CMOS untuk mengurangkan kawasan permukaan cip dan menghasilkan seluruh litar bersepadu pada cip. BW yang dicapai oleh RGC TIA direka adalah 2.47 GHz di bawah CPD besar 2 pF.

# TABLE OF CONTENTS

| CHAPTER | TITLE  |                   |                                          | PAGE |  |

|---------|--------|-------------------|------------------------------------------|------|--|

|         |        |                   |                                          | iv   |  |

|         | ABSTR  | ACT               |                                          | v    |  |

|         | ABSTR  | AK                |                                          | vi   |  |

|         | TABLE  | TABLE OF CONTENTS |                                          |      |  |

|         | LIST O | LIST OF TABLES    |                                          |      |  |

|         | LIST O | F FIGUI           | RES                                      | xi   |  |

|         | LIST O | F ABBR            | EVIATION                                 | xiii |  |

| 1       | INTRO  | DUCTIO            | DN                                       | 1    |  |

|         | 1.1    | Introdu           | iction                                   | 1    |  |

|         | 1.2    | Problem           | n background                             | 1    |  |

|         | 1.3    | Problem           | n statement                              | 3    |  |

|         | 1.4    | Object            | ives                                     | 5    |  |

|         | 1.5    | Scope             |                                          | 5    |  |

|         | 1.6    | Thesis            | outline                                  | 5    |  |

| 2       | LITER. | ATURE             | REVIEW                                   | 7    |  |

|         | 2.1    | Introdu           | iction                                   | 7    |  |

|         | 2.2    | Photod            | iode                                     | 7    |  |

|         |        | 2.2.1             | PIN diode                                | 9    |  |

|         |        | 2.2.2             | Avalanche photodiode (APD)               | 10   |  |

|         | 2.3    | Transir           | npedance Amplifier                       | 12   |  |

|         |        | 2.3.1             | Review of recent proposed TIA topologies | 15   |  |

|   | 2.4  | Conclus                                           | ion                                                |                           | 25 |  |

|---|------|---------------------------------------------------|----------------------------------------------------|---------------------------|----|--|

| 3 | METH | METHODOLOGY                                       |                                                    |                           |    |  |

|   | 3.1  | Introduc                                          | Introduction                                       |                           |    |  |

|   | 3.2  | TIA top                                           | TIA topologies and PD simulation model             |                           |    |  |

|   |      | 3.2.1                                             | 3.2.1 CG TIA topologies                            |                           |    |  |

|   |      | 3.2.2                                             | Geiger mode photo                                  | odiode simulation circuit |    |  |

|   |      |                                                   | model                                              |                           | 29 |  |

|   | 3.3  | Transist                                          | or characteristics of S                            | Siltera 0.13 µm CMOS      |    |  |

|   |      | process                                           |                                                    |                           | 30 |  |

|   | 3.4  | TIA per                                           | TIA performance comparison                         |                           |    |  |

|   | 3.5  | Circuit                                           | Circuit design                                     |                           |    |  |

|   |      | 3.5.1                                             | Circuit analysis                                   |                           | 33 |  |

|   |      |                                                   | 3.5.1.1 TI gain                                    |                           | 33 |  |

|   |      |                                                   | 3.5.1.2 Input im                                   | npedance                  | 34 |  |

|   |      |                                                   | 3.5.1.3 Transfer                                   | Function                  | 34 |  |

|   |      | 3.5.2                                             | Circuit layout                                     |                           | 37 |  |

|   | 3.6  | Design                                            | Design improvement                                 |                           |    |  |

|   | 3.7  | Conclus                                           | ion                                                |                           | 38 |  |

| 4 | RESU | RESULT AND DISCUSSION                             |                                                    |                           |    |  |

|   | 4.1  | Introduc                                          | Introduction                                       |                           |    |  |

|   | 4.2  | Transist                                          | Transistor Characteristics of Siltera 0.13 µm CMOS |                           |    |  |

|   |      | process                                           |                                                    |                           | 40 |  |

|   | 4.3  | TIA per                                           | TIA performance comparison                         |                           |    |  |

|   | 4.4  | Perform                                           | ance of the designed                               | TIA                       | 49 |  |

|   |      | 4.4.1                                             | Post layout simula                                 | tion result               | 49 |  |

|   |      | 4.4.2                                             | Performance summ                                   | nary of the designed TIA  | 53 |  |

|   | 4.5  | Performance of the design with diode-connected pm |                                                    |                           |    |  |

|   |      | load                                              |                                                    |                           | 54 |  |

|   | 4.6  | Conclus                                           | ion                                                |                           | 57 |  |

| 5 | CONC | CLUSION A                                         | ND SUGGESTION                                      | N                         | 58 |  |

|   | 5.1  | Introduc                                          | tion                                               |                           | 58 |  |

viii

| 5.             | 2 | Conclusion                  | 58    |

|----------------|---|-----------------------------|-------|

| 5.             | 3 | Suggestion for future works | 59    |

| REFERENCES     |   |                             | 60    |

| Appendices A-G |   |                             | 63-69 |

# LIST OF TABLES

# TABLE NO.

# TITLE

# PAGE

| 2-1 | SPAD model parameters in (Cheng et al., 2016)                  | 11 |

|-----|----------------------------------------------------------------|----|

| 2-2 | Fabricated SPAD parameters from previous research works        | 12 |

| 2-3 | Summary of the performance of recent proposed TIAs             | 20 |

| 3-1 | Category of TIA topology                                       | 28 |

| 3-2 | The realistic value of $I_{PD}$ and $C_{PD}$                   | 29 |

| 3-3 | Design Parameters for TIA Input Stage                          | 32 |

| 4-1 | $V_{TH}$ and $I_{D(sat)}$ for hp devices                       | 41 |

| 4-2 | DC operating point of RGC3 & CG4                               | 44 |

| 4-3 | TIA performance comparison                                     | 48 |

| 4-4 | Design Parameters of RGC TIA in this work                      | 49 |

| 4-5 | Performance summary                                            | 53 |

| 4-6 | Design Parameters of RGC TIA with DCPL                         | 55 |

| 4-7 | Prelay simulation result of off-chip resistor load and DCPL    | 56 |

| 4-8 | Performance comparison between off-chip resistor load and DCPL | 56 |

# LIST OF FIGURES

# FIGURE NO.

## TITLE

## PAGE

| 1.1  | Generic optical communication system(Razavi, 2012)         | 2          |

|------|------------------------------------------------------------|------------|

| 1.2  | Complete OC system(Razavi, 2012)                           | 3          |

| 2.1  | Generation of electron and hole pair when PD PN junction i | lluminated |

|      | with light.(Razavi, 2012)                                  | 8          |

| 2.2  | Generic I-V curve of photodiode (Razavi, 2012)             | 9          |

| 2.3  | PIN structure (Razavi, 2012)                               | 10         |

| 2.4  | PD-resistor network(Razavi, 2012)                          | 13         |

| 2.5  | Open-loop TIA (CG TIA) (Razavi, 2012)                      | 14         |

| 2.6  | Current (shunt-shunt) feedback TIA (Li, 2007)              | 14         |

| 3.1  | Project Flow Chart                                         | 27         |

| 3.2  | PD circuit model                                           | 29         |

| 3.3  | Input stage of RGC3                                        | 31         |

| 3.4  | Input stage of CG4                                         | 31         |

| 3.5  | SSM of M1                                                  | 33         |

| 3.6  | SSM of M2                                                  | 33         |

| 3.7  | Complete high-frequency SSM                                | 35         |

| 3.8  | Simplified high-frequency SSM                              | 35         |

| 3.9  | Metal 1 resistor                                           | 38         |

| 3.10 | Poly-silicon resistor                                      | 38         |

| 4.1  | I <sub>D</sub> -V <sub>DS</sub> curve of hp_nm             | 41         |

| 4.2  | I <sub>D</sub> -V <sub>GS</sub> curve of hp_nm             | 42         |

| 4.3  | I <sub>D</sub> -V <sub>DS</sub> curve of hp_pm             | 42         |

| 4.4  | I <sub>D</sub> -V <sub>GS</sub> curve of hp_pm             | 43         |

|      |                                                            |            |

| 4.5  | input stage of RGC3                                                               | 44 |

|------|-----------------------------------------------------------------------------------|----|

| 4.6  | input stage of CG4                                                                | 45 |

| 4.7  | Bode plot of RGC3 input stage                                                     | 46 |

| 4.8  | Bode plot of CG4 input stage                                                      | 46 |

| 4.9  | Input and Output signal of RGC3 input stage                                       | 47 |

| 4.10 | Input and Output signal of CG4 input stage                                        | 47 |

| 4.11 | DC operating point of the designed TIA                                            | 50 |

| 4.12 | Bode plot of designed TIA ( $C_{PD} = 2 \text{ pF}$ )                             | 51 |

| 4.13 | Bode plot of designed TIA ( $C_{PD} = 0.5 \text{ pF}$ )                           | 51 |

| 4.14 | Input and Output signal of designed TIA ( $I_{PD}$ of 1 mA amplitude)             | 52 |

| 4.15 | Input and Output signal of designed TIA (I <sub>PD</sub> of 10 $\mu$ A amplitude) | 52 |

| 4.16 | IRVN at 2.5 GHz with 2 pF C <sub>PD</sub>                                         | 53 |

| 4.17 | RGC TIA with diode-connected pmos load                                            | 55 |

|      |                                                                                   |    |

# LIST OF ABBREVIATION

| AFE                 | - | analog front end                     |

|---------------------|---|--------------------------------------|

| APD                 | - | avalanche photodiode                 |

| BW                  | - | bandwidth                            |

| CD                  | - | common drain                         |

| CG                  | - | common gate                          |

| $C_j$               | - | junction capacitance                 |

| CME                 | - | channel modulation effect            |

| CS                  | - | common source                        |

| CSFB                | - | common source feedback               |

| DCPL                | - | diode-connected pmos load            |

| e-                  | - | electron                             |

| Gb/s                | - | giga-bit per seconds                 |

| h+                  | - | hole                                 |

| I <sub>D(sat)</sub> | - | saturation current                   |

| I <sub>drk</sub>    | - | dark current                         |

| ImC                 | - | immitance converter                  |

| I <sub>PD</sub>     | - | photodiode current                   |

| IRCN                | - | input referred current noise         |

| IRNC                | - | input referred noise current         |

| IRVN                | - | input refered voltage noise          |

| I-V                 | - | current-voltage                      |

| KCL                 | - | Kirchhoff's Current Law              |

| LA                  | - | limiting amplifier                   |

| OC                  | - | optical communication                |

| pCAP                | - | parasitic capacitance                |

| PD                  | - | photodiode                           |

| poslay              | - | post-layout                          |

| pRC                 | - | parasitic resistance and capacitance |

| prelay              | - | pre-layout                           |

|                     |   |                                      |

| PVT                        | - | process, voltage supply and temperature |

|----------------------------|---|-----------------------------------------|

| RCG                        | - | regulated cascode configuration         |

| R <sub>IN</sub>            | - | input impedance                         |

| $\mathbf{R}_{\mathrm{ph}}$ | - | responsivity                            |

| R <sub>T</sub>             | - | transimpedance gain                     |

| RX                         | - | receiver                                |

| sim                        | - | simulation                              |

| spec                       | - | specification                           |

| SSM                        | - | small signal model                      |

| TF                         | - | transfer function                       |

| TI                         | - | transimpedance                          |

| TIA                        | - | transimpedance amplifier                |

| $V_{BD}$                   | - | breakdown voltage                       |

| $V_{\text{TH}}$            | - | threshold voltage                       |

| Xtor                       | - | transistor                              |

## **CHAPTER 1**

## **INTRODUCTION**

## 1.1 Introduction

This chapter aims to provide the background knowledge, motivation, and objectives of this project. First, the background of the problem of optical receiver (RX) analog front end (AFE) using a geiger mode photodiode (PD) is presented. Second, the problem statement which clearly stated the problems that this project aims to solve is presented. Third, the objectives to address the problems are defined. Finally, the scope to make sure all objectives can be achieved within the project timeline is defined.

## **1.2** Problem background

The application of optical receiver is in the high-speed optical communication system. In the era of information, the volumes of data in a telecommunication network are growing rapidly. This drives and motivates the need for faster communication channels such as fiber optics. More than a century ago, the idea of using light as a carrier for signals already exists. Researchers able to demonstrate the utility of optical fiber as a medium for light propagation in the mid-1950s. Initially, fibers suffered from a high signal loss. Nevertheless, the prospect of fibre as a channel for optical signal transmission ignited extensive research in the field of optical communications. The

optical communication system using optic fiber is practically realized in the 1970s (Razavi, 2012).

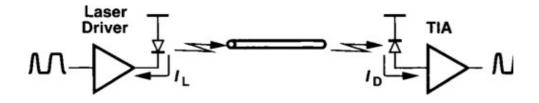

A generic optical communication (OC) system consists three components, just like a typical communication system. These components are the transmitter (TX), transmission channel, and the receiver (RX). The TX is an electro-optical transducer, which converts the electrical signal to optical signal. Fiber is the transmission channel for the optical signal. The RX is a photodetector which senses the optical signal travelled through the fiber from TX end and converts it back to electrical signal. Essentially, the transmitting end includes laser driver and laser diode while the receiving end includes a geiger mode photodiode (PD) and transimpedance amplifier (TIA). Figure 1.1 shows the generic optical communication system. The optical signal will experience a considerable amount of attenuation as it travels from the TX site to RX site. Consequently, high light intensity laser must be used in TX; the PD must be highly sensitive to light; and the current signal from PD must be amplified with low noise and sufficiently wide bandwidth (BW), converting it to voltage domain.

Figure 1.1 : Generic optical communication system(Razavi, 2012)

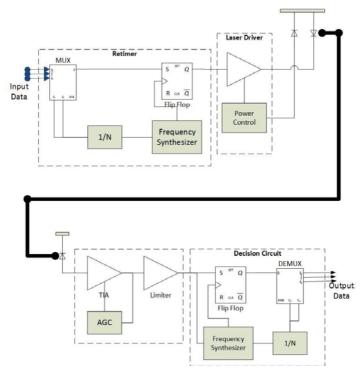

A practical OC system consists many blocks of both the transmitting site and receiving site as shown in Figure 1.2. In the transmitting site, blocks are included to convert low-speed parallel data stream to high-speed serial data stream and to deal with nonidealities behaviour such as jitter. In the receiving site, blocks are included to further improve the output signal swing of TIA and convert serial data stream back to the parallel data stream. The area of focus in the project is the analog front end (AFE) of the RX which consists the PD and TIA only.

The RX AFE presents many design challenges introduced by the demand for high performance. The noise, gain, and BW of the TIA impact the overall speed and sensitivity of the OC directly. As the trend of CMOS IC technologies is to scale down voltage supply to achieve low power requirement, raising the difficulty to design a TIA with low noise, high gain and high BW.

Figure 1.2 : Complete OC system(Razavi, 2012)

## **1.3** Problem statement

The RX AFE have two major problems. First, the parasitic capacitance (pCAP) of the PD is large, usually a few pico Farads. This pCAP is the dominant capacitance to the input of the TIA. Large pCAP means the input pole is small, in other words, the cutoff frequency due to input pole is small. This can be illustrated by the RC limited cut-off frequency equation in (1.1) where the cut-off frequency is inversely proportional to capacitance, $C_d$ . The PD's pCAP effect significantly limited the BW of the entire system. Thus, this effect must be relaxed by designing the input impedance of the TIA to be as small as possible for the system to operate in GHz frequency range.

$$f_{RC} = \frac{1}{2\pi R \frac{C}{L d}} \tag{1.1}$$

where  $f_{RC}$  is the RC limited cut-off frequency,  $R_L$  is resistance and  $C_d$  is capacitances.

The second problem is the current signal from PD usually is very weak, depending on the type of PD, the current magnitude can be as small as a few ten micro Ampere ( $\mu$ A) (Li, 2007). Therefore, it is very sensitive to noise. The large PD's pCAP will introduce considerable large amount of input referred noise current (IRNC) to the input of the TIA (Atef and Zimmermann, 2013). This poses a risk of data loss as the input current signal of the TIA is subjected to noise. To ensure the input current signal to be amplified and converted to voltage signal accurately, the noise and gain performance of the TIA must be designed to be sufficiently robust to separate the weak current signal from the noise. The problems mentioned above are addressed in this work by designing the RX AFE with 2.5 GHz BW with sufficiently large gain, good noise performance and low TIA input impedance.

### 1.4 Objectives

The objectives of this project are:

- 1. To design a 2.5 GHz optical analog front-end receiver using a Geiger mode photodiode and transimpedance amplifier (TIA) topology.

- 2. To analyze the performance of common gate TIA.

- 3. To optimize the performance of the design for very weak photon detection.

### 1.5 Scope

A scope is defined for this project in order to focus on achieving all the objectives stated above within the limited time frame given. First, the process, voltage supply and temperature (PVT) condition of the design are defined. Process technology used is Siltera 0.13  $\mu$ m CMOS technology, supply voltage is 1.2 V and temperature is 300 K (27 °C). The variation of process, voltage supply and temperature is not covered. Second, the design of photodiode is not covered, realistic current and capacitance values will be used in simulation. Third, the common gate (CG) TIA topology is employed in the design. The decision of using CG TIA is justified by mathematical analysis based on literature reviews. Fourth, the layout of the design is drawn using "auto-layout" method of mentor graphic. Parasitic is extracted for post-layout simulation. Finally, this project did not cover the physical implementation of the design, hence that no physical circuit is fabricated.

## 1.6 Thesis outline

The following chapters of this thesis are chapter 2, 3 and 4. Chapter 2 presents the literature review on the PD and TIA. The focus on PD review is on the parameters such as current, dark current, parasitic capacitance (pCAP) and breakdown voltage. This provides insight on the realistic parameter value to be used in the modelling the

PD in circuit simulation. For TIA, various TIA topologies are studied and compared to identify research gap and justified the decision of using CG TIA topology. In chapter 3, the five major steps involved in this project are explained in detail. The result of each of the major steps is presented and discussed in chapter 4. Finally, chapter 5 concludes this work based on all the results obtained and suggestions on future work are provided.

#### REFERENCES

- Abdollahi, B., Akbari, P., Mesgan, B. and Saeedi, S. (2015). A low voltage low noise transimpedance amplifier for high-data-rate optical recievers. *ICEE 2015 Proceedings of the 23rd Iranian Conference on Electrical Engineering*. 10, 1187–1192.

- Arshad, T.S.M., Othman, M. a., Yasin, N.Y.M., Taib, S.N., Ismail, M.M., Napiah, Z. a. F.M., Sulaiman, H. a., Hussain, M.N., Said, M. a. M., Misran, M.H. and Ramlee, R. a. (2013). Comparison on IV characteristics analysis between Silicon and InGaAs PIN photodiode. 2013 3rd International Conference on Instrumentation, Communications, Information Technology and Biomedical Engineering., 70–75.

- Atef, M. and Zimmermann, H. (2013). Optical Receiver Using Noise Cancelling With an Integrated Photodiode in 40 nm CMOS Technology. *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS*. 60(7), 1929–1936.

- Brandl, P., Enne, R. and Zimmermann, H. (2015). Optical wireless receiver circuit with integrated APD and high background-light immunity. *European Solid-State Circuits Conference.*, 48–51.

- Charbon, E., Yoon, H. and Maruyama, Y. (2013). A Geiger Mode APD F Fabricated in Standard 65nm CMOS Te echnology Edoardo Ch. 2013 International Electron Devices Meeting (IEDM)., 675–678.

- Cheng, Z., Zheng, X., Palubiak, D., Deen, M.J. and Peng, H. (2016). A

Comprehensive and Accurate Analytical SPAD Model for Circuit Simulation.

*IEEE Transactions on Electron Devices*. 63(5), 1940–1948.

- Escid Hammoudi, Imad, B. and Mohamed, D. (2012). High Bandwidth 0.35µm CMOS Transimpedance Amplifier. *International Microwave and Optoelectronics Conference*. 1, 1–6.

- Fayed, Ayman, Ismail, M. (2006). On-Chip Resistors and Capacitors, Boston, MA: Springer US.

- Han, L., Yu, M. and Zong, L. (2010). Bandwidth ehancement for transimpedance ampilfier in CMOS process. 2010 3rd International Conference on Biomedical Engineering and Informatics., 2839–2842.

- Khaki, A.M.Z., Omoomi, M. and Borzabadi, E. (2016). An ultra-low-power TIA plus limiting amplifier in 90nm CMOS technology for 2.5 Gb/s optical receiver. 2016 24th Iranian Conference on Electrical Engineering., 1055–1059.

- Kume, E., Ishii, H., Itatani, T., Yamanaka, S., Takada, T., Hata, M., Osada, T., Inoue, T. and Matsumoto, Y. (2014). The Monolithic Heterogeneous Integration of GaAs PIN Photodiode and Si CMOS-based Transimpedance Amplifier. 2014 Conference on Lasers and Electro-Optics., 2–3.

- Li, M. (2007). 5 GHz Optical Front End in 0. 35µm CMOS.

- Lu, Z., Yeo, K.S., Lim, W.M., Do, M.A. and Boon, C.C. (2010). Design of a CMOS broadband transimpedance amplifier with active feedback. *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems. 18(3), 461–472.

- Mofasser, A., Saha, S., Hadi, K.S., Mohammedy, F.M. and El-batawy, Y. (2017).

Modeling of Photocurrent and Dark Count Probability of InGaAs / InP Single

Photon Avalanche Photodiode. 2017 IEEE International Conference on Telecommunications and Photonics (ICTP)., 26–28.

- Ray, S. and Hella, M.M. (2018). A 53 dB ohms 7-GHz Inductorless Transimpedance

Amplifier and a 1-THz + GBP Limiting Amplifier in 0.13-μm CMOS. *IEEE Transactions on Circuits and Systems I: Regular Papers (Early Access ).*, 1–13.

- Razavi, B. (2012). *Design of Integrated Circuits for Optical Communications* Second edi., Wiley.

- Rochas, A., Pauchard, A.R., Besse, P.A., Pantic, D., Prijic, Z. and Popovic, R.S. (2002). Low-noise silicon avalanche photodiodes fabricated in conventional CMOS technologies. *IEEE Transactions on Electron Devices*. 49(3), 387–394.

- Shahdoost, S., Medi, A. and Saniei, N. (2014). Low-Noise Transimpedance Amplifier Design Procedure for Optical Communications. 22nd Austrian Workshop on Microelectronics (Austrochip)., 1–5.

- Taghavi, M.H., Belostotski, L., Haslett, J.W. and Ahmadi, P. (2015). 10-Gb/s 0.13μm CMOS Inductorless Modified-RGC Transimpedance Amplifier. *IEEE Transactions on Circuits and Systems I: Regular Papers*. 62(8), 1971–1980.

- Talarico, C. and Roveda, J.W. (2014). A 60dBΩ 2.9 GHz 0.18 µm CMOS

Transimpedance Amplifier for a Fiber Optic Receiver Application. 2014 IEEE

57th International Midwest Symposium on Circuits and Systems (MWSCAS).,

181–184.

- Zhang, X., Ni, B., Mukhopadhyay, I. and Apsel, A.B. (2012). Improving absolute accuracy of integrated resistors with device diversification. *IEEE Transactions on Circuits and Systems*. 59(6), 346–350.