### Dissertation submitted to the Combined Faculties of the Natural Sciences and Mathematics of the Ruperto-Carola-University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

put forward by

Sebastian Klewin (M.Sc. Physics) born in Friedrichshafen, Germany

Oral examination: April  $17^{\text{th}}$ , 2019

## Development of the FPGA-based Raw Data Preprocessor for the TPC Readout Upgrade in ALICE

Referees: Prof. Dr. Johanna Stachel Prof. Dr. Peter Fischer

# Entwicklung des FPGA-basierten Rohdaten-Vorprozessors für die Aufrüstung der TPC Ausleseeinheiten bei ALICE

ALICE ist eines der vier großen Experimente am Large Hadron Collider (LHC). Es ist das Schwerionenexperiment und untersucht daher in erster Linie das Quark–Gluon-Plasma. Um sich auf die Bedingungen von Blei-Blei-Kollisionen mit einer Rate von 50 kHz am LHC nach der Umrüstphase 2 (2018–2021) vorzubereiten, wird ein umfangreiches Aufrüst-Programm durchgeführt. Ziel ist es, dass die Zeitprojektionskammern kontinuierlich ausgelesen werden können. Die enorme Datenrate von 3,7 TB/s, die durch den aufgerüsteten Detektor erzeugt wird, muss bereits während der Datennahme um den Faktor 60 reduziert werden. Andernfalls würde das Datenvolumen die voraussichtlich verfügbare Bandbreite und Speicherkapazität überschreiten.

In dieser Arbeit wurde ein Online-Cluster-Finder (CF) für FPGAs entwickelt und implementiert, der das gesamte Datenvolumen in Echtzeit bereits während der Detektorauslese verarbeitet. Dies ist der erste Schritt in einer ganzen Reihe von Datenreduktionsschritten, welcher für sich genommen bereits einen Kompressionsfaktor von etwa 5 erreicht, indem nur physikalisch relevante Informationen behalten werden und ein geeigneteres Datenformat verwendet wird. Zusätzlich zum CF wurde auch die gesamte Datenaufbereitungskette konzipiert und implementiert. Diese dekodiert den Eingangsdatenstrom, sortiert die einzelnen Kanäle so um, dass eine Suche von Ladungsclustern überhaupt erst möglich wird und korrigiert die Detektoreffekte in den Eingangssignalen. Alle implementierten Module wurden ausführlich simuliert, um ihre korrekte Funktionalität nachzuweisen. Damit wurde die gesamte Datenverarbeitungskette innerhalb des FPGAs vorbereitet und validiert.

# Development of the FPGA-based Raw Data Preprocessor for the TPC Readout Upgrade in ALICE

ALICE is one of the four major experiments at the Large Hadron Collider (LHC). It is the dedicated heavy-ion experiment and therefore primarily examines the Quark–Gluon Plasma. In order to prepare for the running conditions of 50 kHz lead-lead interactions at the LHC after the Long Shutdown 2 (2018–2021), an extensive upgrade program is carried out. The goal of the upgrade is a continuous readout of the TPC without the need of a trigger. It is essential to reduce the enormous data rate of 3.7 TB/s, generated by the upgraded detector, already during the data taking by a factor of about 60. Otherwise the data volume would exceed the expected available bandwidth and storage capabilities.

In this thesis, an online Cluster Finder (CF) was developed and implemented for FPGAs which processes the whole data volume in real-time during the read out. This is the first step in the data reduction sequence which achieves already a factor of about 5 by keeping only physically relevant information and making use of a better suited data format. In addition to the CF, also the whole data preparation chain was designed and implemented to decode the input data stream, to resort the individual channels to allow for cluster finding and to correct the detector effects in the input signals. All modules which were implemented were extensively simulated to verify their proper functionality. With this, the complete processing chain within the FPGAs was prepared and validated.

# Contents

| 1 | Intro    | oduction and Motivation                           | 1              |

|---|----------|---------------------------------------------------|----------------|

| _ | 1.1      |                                                   | $\overline{3}$ |

|   | 1.2      |                                                   | 4              |

|   | <b>-</b> |                                                   | 6              |

|   |          |                                                   | 6              |

|   |          |                                                   | 6              |

|   |          |                                                   | 7              |

|   | 1.3      | 0                                                 | 8              |

| 2 | тро      | C with a Continuous Readout                       | 9              |

|   | 2.1      | Working principle of Time-Projection Chambers     | 9              |

|   | 2.2      | The ALICE Time-Projection Chamber                 | 0              |

|   |          | -                                                 | 0              |

|   |          | 2.2.2 The MWPC Readout Chambers                   | 1              |

|   | 2.3      | Readout Upgrade of the ALICE TPC                  | 2              |

|   |          | 2.3.1 Upgrade Goals                               | 2              |

|   |          | 2.3.2 GEM based Readout Chambers                  | 2              |

|   |          | 2.3.3 Upgrade of the Front-End Electronics        | 4              |

|   |          | 2.3.4 Towards an Online Track Reconstruction      | 5              |

|   | 2.4      | Timeline of the TPC Upgrade 1                     | 5              |

| 3 | Rea      | dout Strategy for the ALICE TPC 1                 | 7              |

|   | 3.1      | The TDR Baseline                                  | 7              |

|   |          | 3.1.1 The Common Mode Effect                      | 9              |

|   |          | 3.1.2 Application of a loss-less Data Compression | 20             |

|   |          | 3.1.3 Change of the Readout Scheme                | 25             |

|   | 3.2      | The SAMPA Chip                                    | 27             |

|   | 3.3      | The GBT System                                    | 9              |

|   |          | 3.3.1 The Transmission Protocol                   | 9              |

|   |          | 3.3.2 The SAMPA Data within the GBT Frame         | 0              |

|   | 3.4      | The Common Readout Unit                           | 3              |

| 4 | The      | CRU Firmware 3                                    | 9              |

|   | 4.1      | A Modular Firmware Concept                        | 9              |

|   | 4.2                                             | Interfa                                                                                                                                                               | aces to the User Logic $\ldots \ldots 42$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                 | 4.2.1                                                                                                                                                                 | GBT Wrapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                 | 4.2.2                                                                                                                                                                 | DMA Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                 | 4.2.3                                                                                                                                                                 | TTS Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                 |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5 | A 2                                             | D Clust                                                                                                                                                               | ter Finder for the TPC 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.1                                             |                                                                                                                                                                       | iew of the TPC User Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.2                                             | Data 1                                                                                                                                                                | Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                 | 5.2.1                                                                                                                                                                 | Decoding of the GBT Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                 | 5.2.2                                                                                                                                                                 | A Two-Stage Sorting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                 | 5.2.3                                                                                                                                                                 | Common Mode Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                 | 5.2.4                                                                                                                                                                 | Baseline Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 5.3                                             | Cluste                                                                                                                                                                | er Reconstruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                 | 5.3.1                                                                                                                                                                 | Determining the Cluster Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                 | 5.3.2                                                                                                                                                                 | The Concept of the Cluster Finder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                 | 5.3.3                                                                                                                                                                 | The Peak Finding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                 | 5.3.4                                                                                                                                                                 | Width of the Cluster Finder Instances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                 | 5.3.5                                                                                                                                                                 | The Cluster Finder Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                 | 5.3.6                                                                                                                                                                 | Optimising the Cluster Finder Grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                 | 5.3.7                                                                                                                                                                 | Calculating the Cluster Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                 | 5.3.8                                                                                                                                                                 | Cluster Merging Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | ۳.4                                             | Degen                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.4                                             | nesou                                                                                                                                                                 | rce Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | -                                               |                                                                                                                                                                       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6 | -                                               |                                                                                                                                                                       | ce and Validation 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 | -                                               | forman                                                                                                                                                                | ce and Validation       93         mance of the User Logic Modules in Simulation       93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6 | Per                                             | forman                                                                                                                                                                | ce and Validation 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 | Per                                             | f <b>orman</b><br>Perfor                                                                                                                                              | ce and Validation       93         mance of the User Logic Modules in Simulation       93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

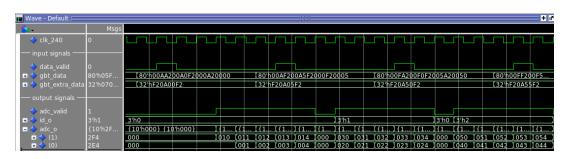

| 6 | Per                                             | f <b>orman</b><br>Perfor<br>6.1.1                                                                                                                                     | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6 | Per                                             | <b>formand</b><br>Perfor<br>6.1.1<br>6.1.2                                                                                                                            | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98                                                                                                                                                                                                                                                                                                                                                                |

| 6 | Per                                             | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3                                                                                                                          | See and Validation     93       mance of the User Logic Modules in Simulation     93       Decoding of the GBT Frames     94       Sorting Algorithm     96       Baseline Correction     98                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | Per                                             | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                                                        | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98                                                                                                                                                                                                                                                                                                                                                                |

| 6 | <b>Per</b><br>6.1                               | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                                                                        | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100                                                                                                                                                                                                                                                                                                                     |

| 6 | <b>Per</b><br>6.1                               | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida                                                                                     | gamma ce and Validation       gamma gamma         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108                                                                                                                                                                                                                                                  |

| 6 | <b>Per</b><br>6.1                               | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2                                                                            | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       109         The Triggered Readout Mode       110                                                                                                                                                                                                                    |

| 6 | <b>Per</b><br>6.1                               | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3                                                                   | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108         The C-RORC as Readout Card       109                                                                                                                                                                                                                    |

| 6 | <b>Perf</b><br>6.1<br>6.2<br>6.3                | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste                                                         | ce and Validation93mance of the User Logic Modules in Simulation93Decoding of the GBT Frames94Sorting Algorithm96Baseline Correction98The individual Cluster Reconstruction Modules98The complete Clusteriser100tion during Test Beam Data Taking108The C-RORC as Readout Card109The Triggered Readout Mode110Validation of the GBT Decoder110validation in Software111                                                                                                                                                                                                                                                                     |

| 6 | <b>Perf</b><br>6.1<br>6.2<br>6.3                | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste                                                         | gamma ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         Validation of the GBT Decoder       110                                                                                                                 |

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con                | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion                                              | ce and Validation93mance of the User Logic Modules in Simulation93Decoding of the GBT Frames94Sorting Algorithm96Baseline Correction98The individual Cluster Reconstruction Modules98The complete Clusteriser100tion during Test Beam Data Taking108The C-RORC as Readout Card109The Triggered Readout Mode110Validation of the GBT Decoder110and Outline115                                                                                                                                                                                                                                                                                |

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con                | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion                                              | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         Attion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         Validation of the GBT Decoder       111         and Outline       115                                                                                       |

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con<br>A           | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion<br>dix<br>Acron                              | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         validation of the GBT Decoder       111         and Outline       115         yms       117                                                                   |

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con<br>A<br>B      | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion<br>Jix<br>Acrony<br>Pad P                    | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         Validation of the GBT Decoder       111         and Outline       115         yms       117         'ane Mapping       121                                    |

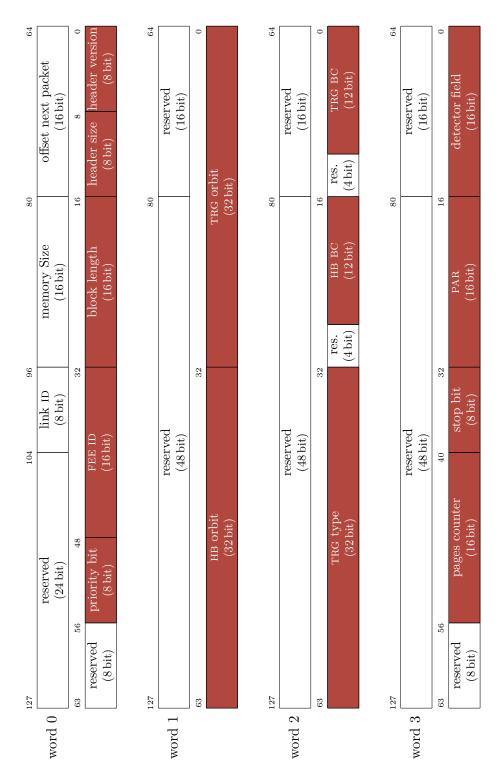

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con<br>A<br>B<br>C | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion<br>Jix<br>Acrony<br>Pad P<br>The R           | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         ttion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         Validation of the GBT Decoder       111         and Outline       115         yms       117         Yame Mapping       121         taw Data Header       127 |

| 7 | Perf<br>6.1<br>6.2<br>6.3<br>Con<br>A<br>B      | Formand<br>Perfor<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>Valida<br>6.2.1<br>6.2.2<br>6.2.3<br>Cluste<br>clusion<br>dix<br>Acrony<br>Pad P<br>The R<br>Biblio | ce and Validation       93         mance of the User Logic Modules in Simulation       93         Decoding of the GBT Frames       94         Sorting Algorithm       96         Baseline Correction       98         The individual Cluster Reconstruction Modules       98         The complete Clusteriser       100         tion during Test Beam Data Taking       108         The C-RORC as Readout Card       109         The Triggered Readout Mode       110         Validation of the GBT Decoder       111         and Outline       115         yms       117         'ane Mapping       121                                    |

# List of Figures

| $1.1 \\ 1.2$             | The CERN accelerator complex                                                                                           | $\frac{3}{5}$          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|

| 2.1<br>2.2<br>2.3<br>2.4 | Schematic view of the ALICE TPC                                                                                        | $10 \\ 11 \\ 13 \\ 14$ |

| $3.1 \\ 3.2 \\ 3.3$      | The main components of the TPC readout chain                                                                           | 18<br>20               |

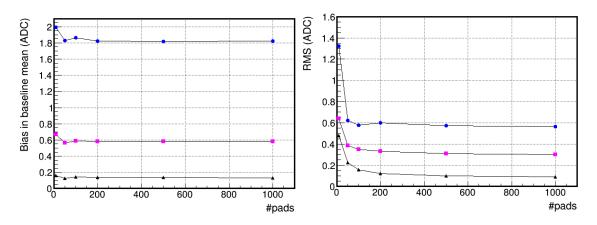

|                          | with the averaging method                                                                                              | 21                     |

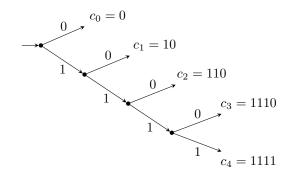

| 3.4                      | Example of a small Huffman tree with only five codes                                                                   | 22                     |

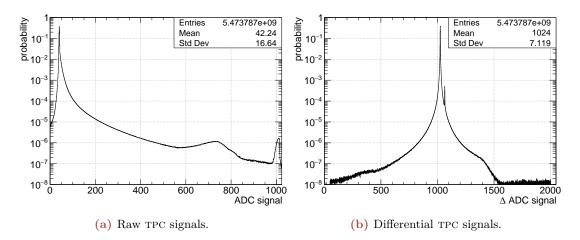

| $3.5 \\ 3.6$             | The probability spectrum of the ADC values of the ALICE TPC Compression factors achieved by the length-limited Huffman | $22 \\ 24$             |

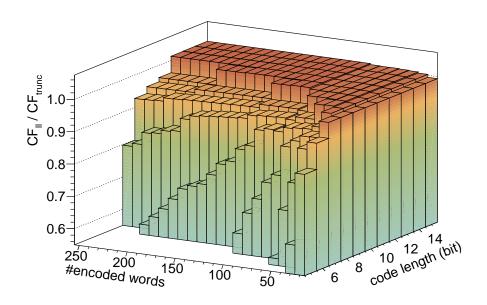

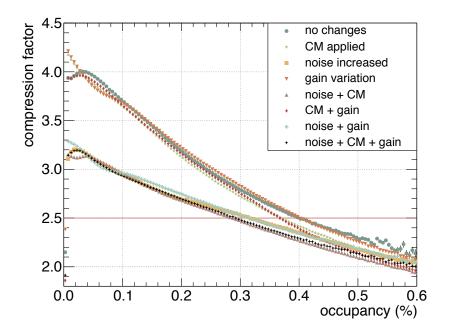

| 3.0<br>3.7               | Compression factor of the Huffman encoding as function of the occupancy .                                              | $\frac{24}{25}$        |

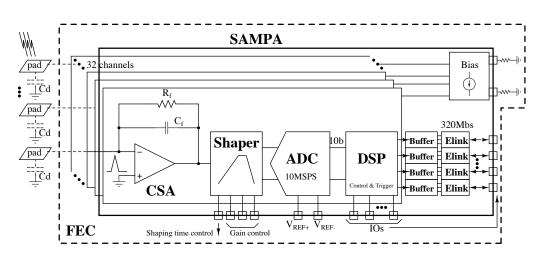

| 3.8                      | Block diagram of the SAMPA ASIC                                                                                        | $\frac{20}{26}$        |

| 3.9                      | The SAMPA synchronisation pattern in DAS mode                                                                          | 28                     |

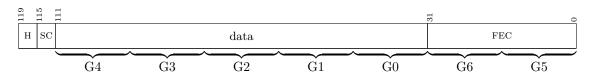

| 3.10                     | The GBT protocol                                                                                                       | 29                     |

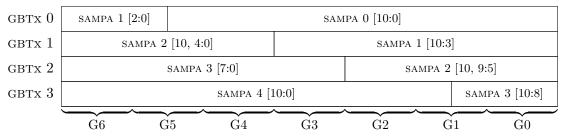

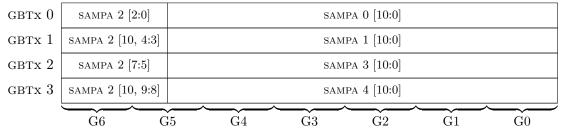

| 3.11                     | Mapping of the SAMPA data into the GBT frame                                                                           | 32                     |

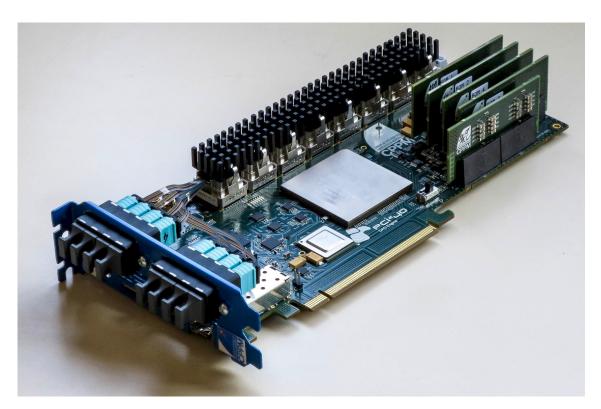

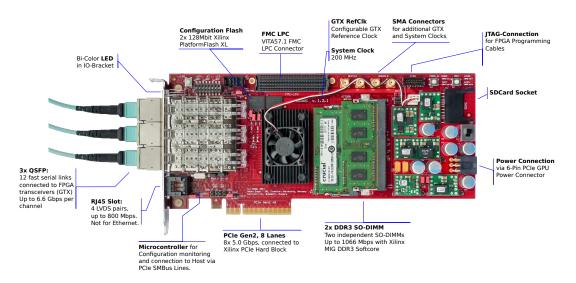

|                          | Image of the CRU version 1                                                                                             | 35                     |

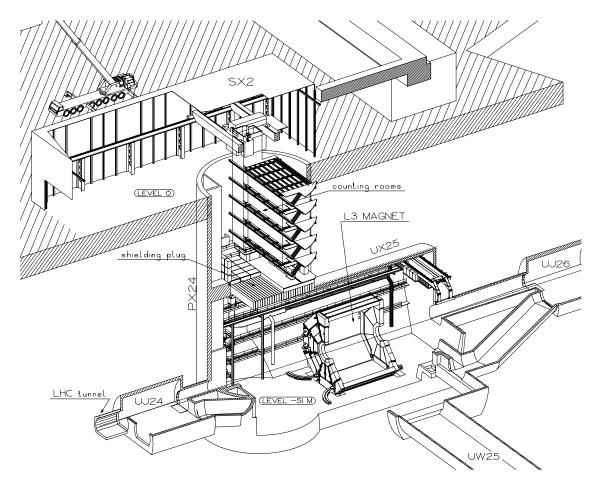

| 3.13                     | Layout of the ALICE underground area                                                                                   | 37                     |

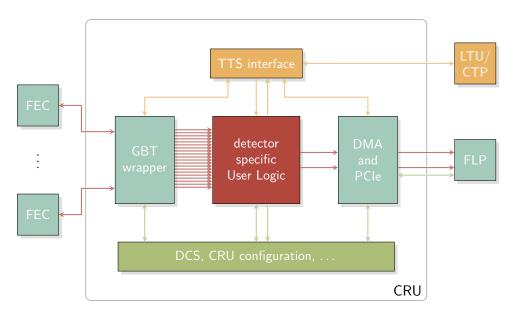

| 4.1                      | The main blocks of the CRU FW                                                                                          | 40                     |

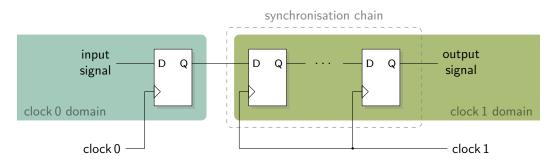

| 4.2                      | Synchronisation register chain                                                                                         | 41                     |

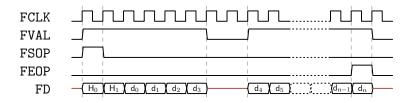

| 4.3                      | The transmission protocol towards the data path wrapper                                                                | 44                     |

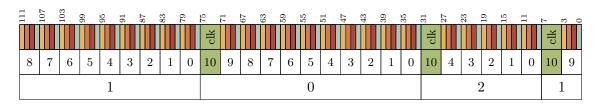

| 4.4                      | Mapping of the data bus into the FLP memory                                                                            | 44                     |

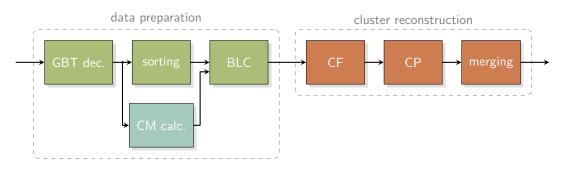

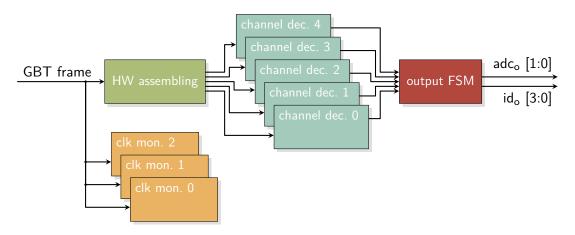

| 5.1                      | A simplified block diagram of the TPC UL                                                                               | 48                     |

| 5.2                      | Detailed mapping of the SAMPA output into the GBT frame                                                                | 50                     |

| 5.3                      | Block diagram of the GBT decoder                                                                                       | 52                     |

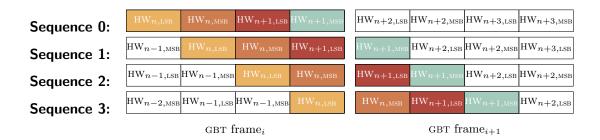

| 5.4                      | The four valid ADC clock sequences                                                                                     | 52                     |

| 5.5                      | The four possible HW sequences                                                                                         | 52                     |

| 5.6                      | Data interface of the GBT decoder                                                                                      | 53                     |

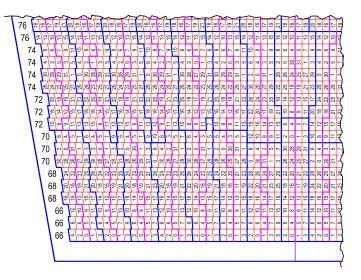

| 5.7                      | Excerpt of the IROC pad plane with the SAMPA channels $\ldots \ldots \ldots \ldots$                                    | 56                     |

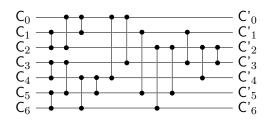

| 5.8                      | Illustration of a sorting network                                                                                      | 57                     |

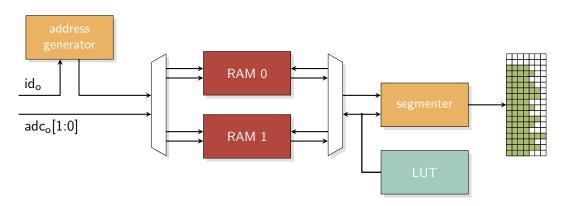

| 5.9  | A configurable pre-sorting module based on a ping-pong RAM                                | 59  |

|------|-------------------------------------------------------------------------------------------|-----|

| 5.10 | Block diagram of the CM calculation module                                                | 61  |

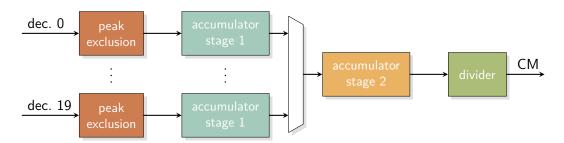

| 5.11 | Block diagram of the Arria10 native FP DSP IP core in three different                     |     |

|      | configuration modes                                                                       | 62  |

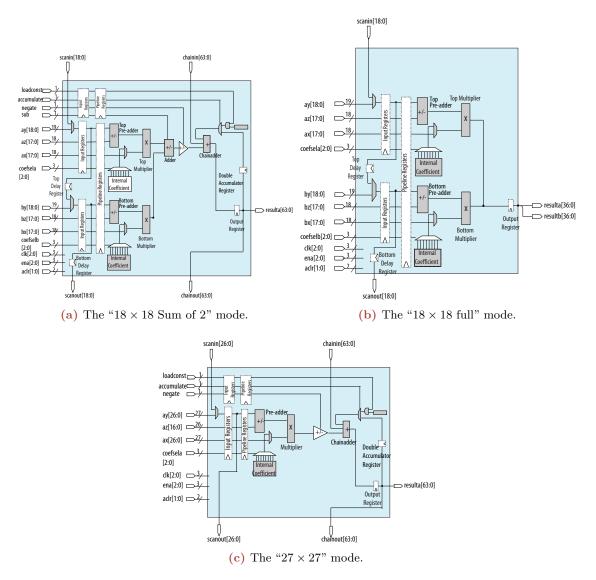

| 5.12 | Block diagram of the BLC module                                                           | 64  |

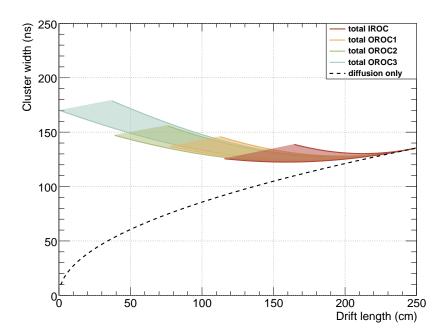

| 5.13 | Extension of the clusters in time direction as a function of the drift length .           | 67  |

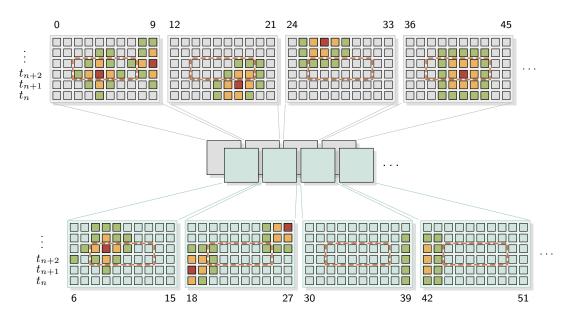

| 5.14 | General concept of the cluster finding approach                                           | 69  |

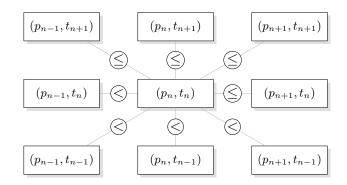

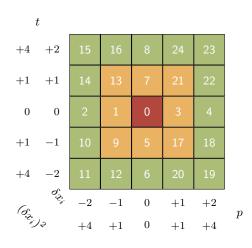

| 5.15 | The definition of a charge peak                                                           | 70  |

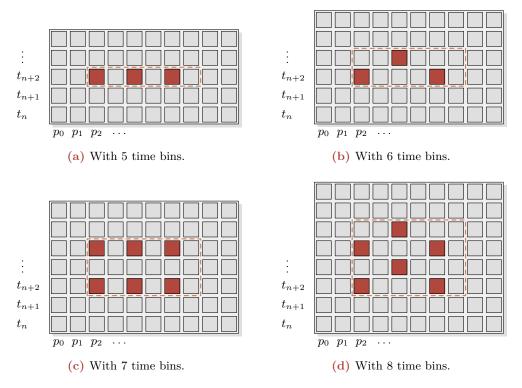

| 5.16 | Maximum number of peaks within a CF instance                                              | 73  |

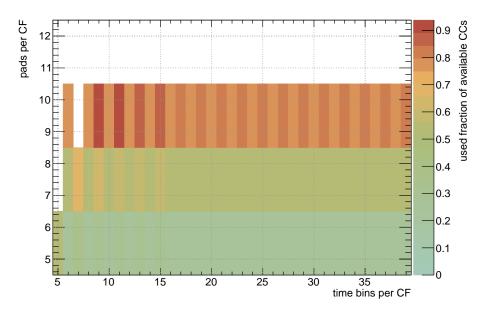

| 5.17 | Used fraction of available ${\rm CCs}$ as a function of pads and time bins per ${\rm CF}$ | 75  |

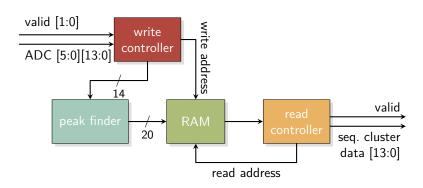

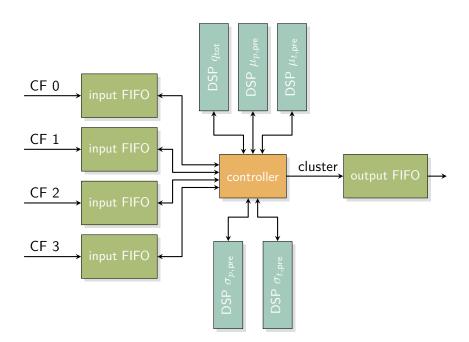

| 5.18 | Block diagram of the CF module                                                            | 76  |

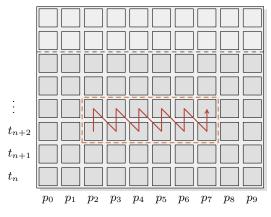

| 5.19 | Reading order of the CF                                                                   | 77  |

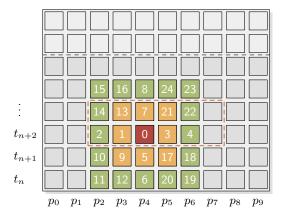

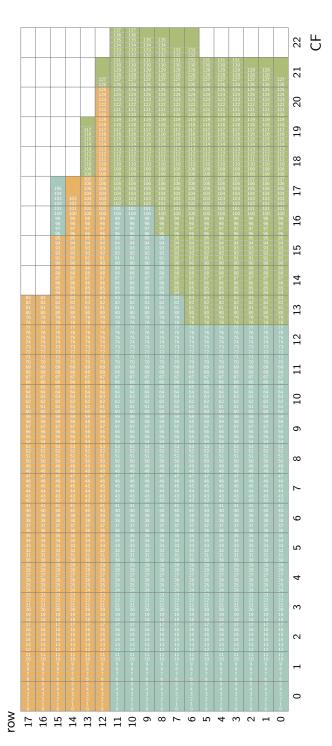

|      | The CF grid covering all required pads                                                    | 79  |

| 5.21 | The Cluster Data Format                                                                   | 83  |

| 5.22 | Block diagram of the CP                                                                   | 84  |

|      | Mapping of the cluster data to the CP input FIFO                                          | 85  |

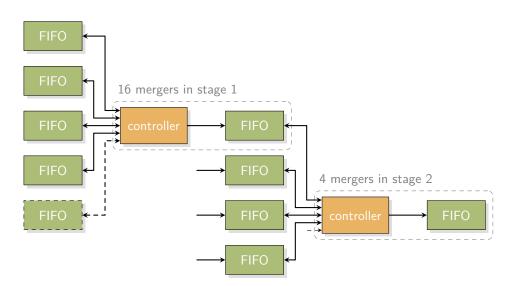

| 5.24 | The FIFO merging network                                                                  | 87  |

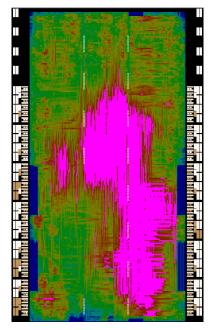

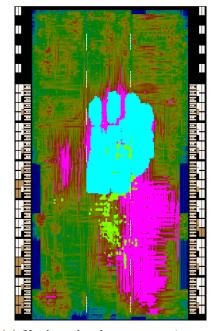

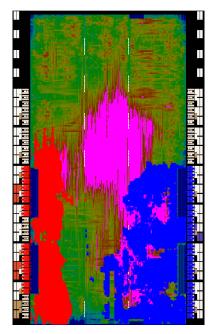

| 5.25 | Visualisation of the utilisation of the FPGA                                              | 92  |

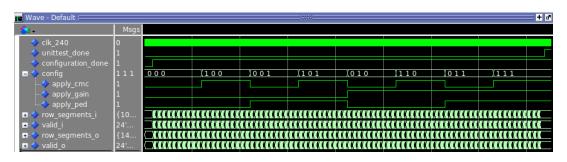

| 6.1  | Simulation of a complete GBT decoder with ModelSim                                        | 95  |

| 6.2  | The content of the pre-sorter mapping files                                               | 97  |

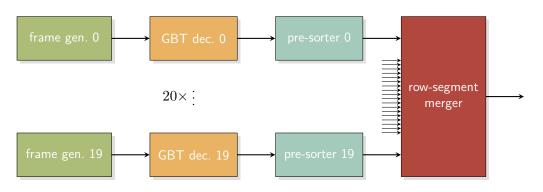

| 6.3  | Setup of the row-segment merger simulation test bench                                     | 98  |

| 6.4  | Simulation of the BLC module with ModelSim                                                | 99  |

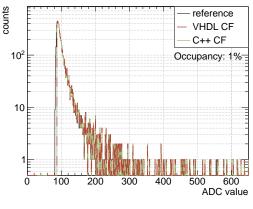

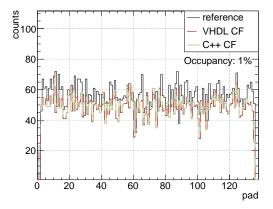

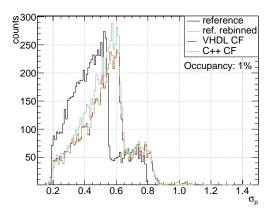

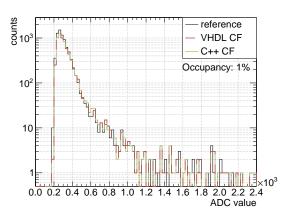

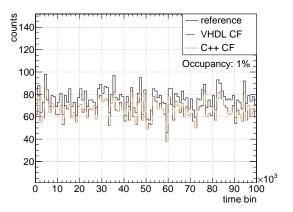

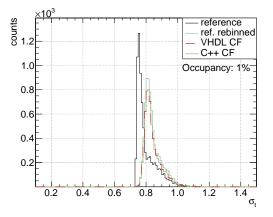

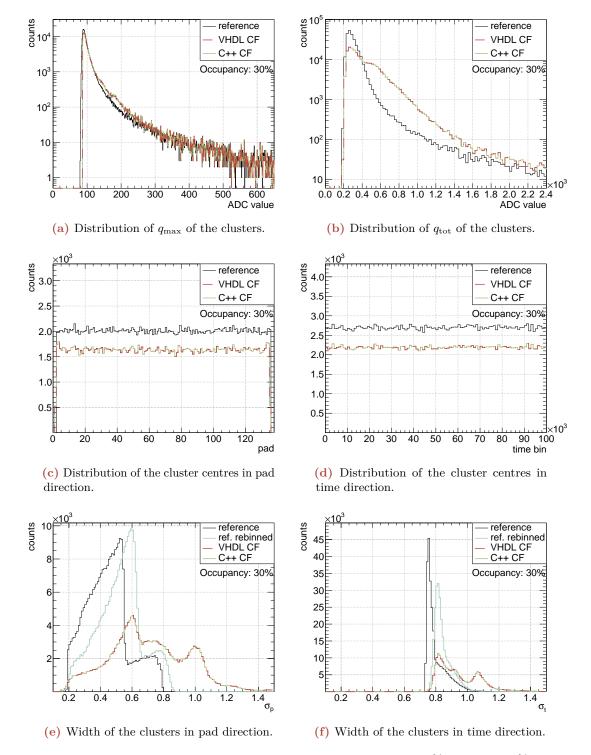

| 6.5  | Distributions of the cluster properties for the simulation system with 23 CF              |     |

|      | instances, an occupancy of $1\%$ and a cut on $q_{\text{max}}$ and the contribution       |     |

|      | threshold                                                                                 | 102 |

| 6.6  | Distributions of the cluster properties for the simulation system with 23 CF              |     |

|      | instances, an occupancy of $30\%$ and a cut on $q_{\text{max}}$ and the contribution      |     |

|      | threshold                                                                                 | 103 |

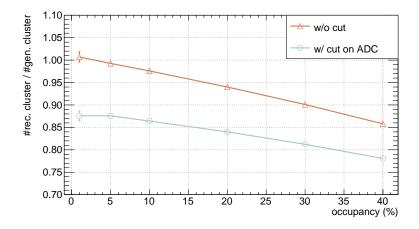

| 6.7  | Efficiency of the clusteriser                                                             | 104 |

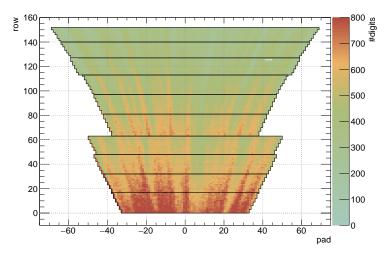

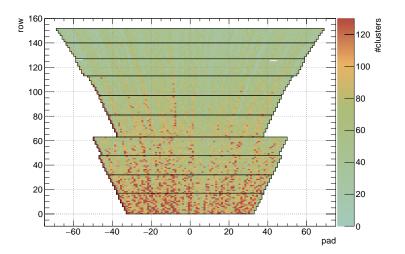

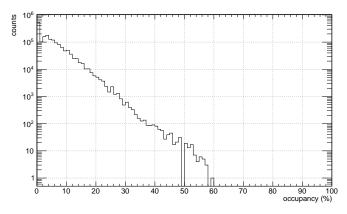

| 6.8  | Input and results of the full clusteriser simulation                                      | 107 |

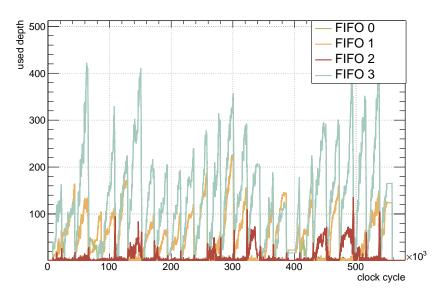

| 6.9  | Filling level of the four final FIFO mergers as a function of time                        | 108 |

| 6.10 |                                                                                           |     |

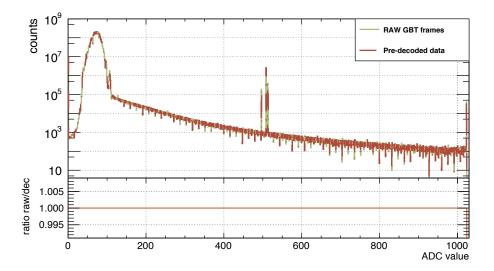

| 6.11 | Spectrum of the ADC values recorded at the test beam                                      |     |

|      | The Callgrind output of the software CF, visualised with KCachegrind $\ldots$             |     |

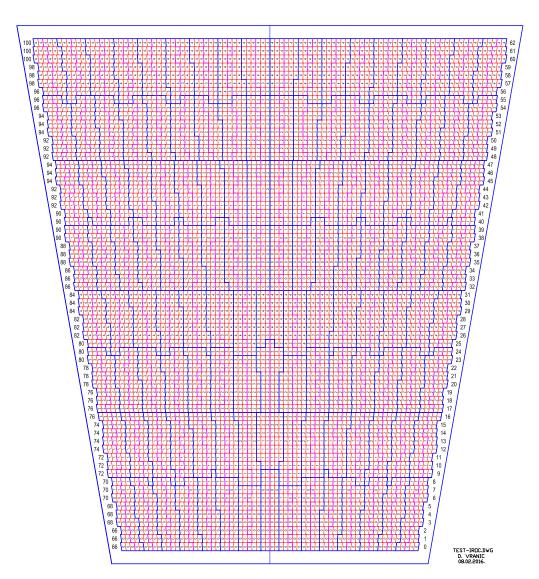

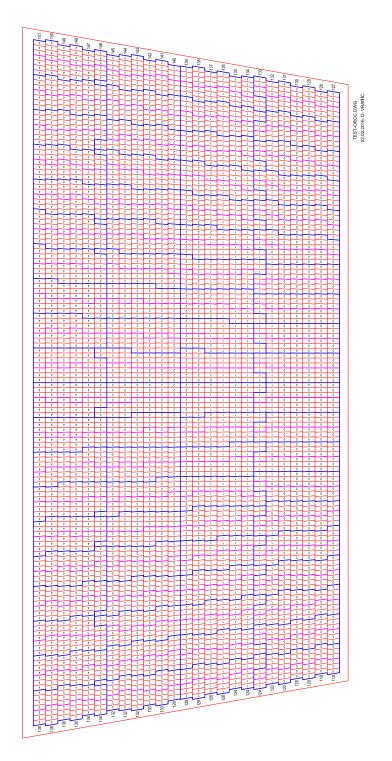

| B.1  | The pad plane of the IROC                                                                 | 123 |

| B.2  | The pad plane of the OROC 1                                                               |     |

| B.3  | The pad plane of the OROC 2                                                               |     |

| B.4  | The pad plane of the OROC 3                                                               |     |

| C.1  | The RDH version 3                                                                         | 129 |

# List of Tables

| 3.1 | The two different transmission modes of the SAMPA in DAS mode $\ldots$ .            | 27  |

|-----|-------------------------------------------------------------------------------------|-----|

| 3.2 | Bits of the GBT frame of the individual data groups in wide bus mode                | 31  |

| 3.3 | Resources of the Intel Arria10 FPGA of the CRU                                      | 34  |

| 5.1 | Content of the GBT decoder data output                                              | 54  |

| 5.2 | Diffusion coefficients and drift velocities for electrons in different gas mixtures | 66  |

| 5.3 | Geometric parameters of the pad plane of a TPC sector                               | 68  |

| 5.4 | Content of the data word stored in the CF memory                                    | 72  |

| 5.5 | Sequence of the CF output data stream                                               | 78  |

| 5.6 | Mapping of the cluster data to the DSP ports                                        | 86  |

| 5.7 | Fit result summary of the complete FW with the TPC UL                               | 88  |

| 5.8 | Resource consumption of the individual modules of the TPC UL $\ldots$ .             | 89  |

| B.1 | Key parameters of the pad plane regions                                             | 122 |

# CHAPTER 1

# Introduction and Motivation

A few microseconds after the formation of the early universe, it is assumed that the medium was in a very high temperature and density state [1]. Under such conditions, matter is expected to exist in a state called Quark–Gluon Plasma (QGP), where the quarks and gluons are deconfined [2]. The only known way to generate this state of matter in a laboratory in order to study it is to collide heavy nuclei at ultra-relativistic energies. One of the few places where this is possible is the Large Hadron Collider (LHC) at CERN (Conseil Européen pour la Recherche Nucléaire, European Organisation for Nuclear Research) [3].

During the first years of LHC operation, the ALICE (A Large Ion Collider Experiment) collaboration was able to confirm the basic picture of the creation of a strongly interacting matter at values of temperatures and densities never seen before in a heavy-ion collision [3]. In order to continue the studies of the QGP by examining its properties such as viscosity, transport coefficients or the temperature evolution, ALICE will focus on rare probes after the Long Shutdown (LS) 2. These rare probes are e.g. heavy-flavour particles and their coupling to the medium. By measuring the azimuthal anisotropy for charmed mesons and baryons as well as beauty particles one can draw conclusions whether the heavy quarks thermalised in the system and thus participated in the collective flow. Another probe is the measurement of jets and their correlation with other probes. The properties of the QGP can be accessed by investigating the energy loss of hard scattered partons in the strongly interacting medium. Measuring the production of different quarkonium states down to very low transverse momentum will help to understand the underlying mechanisms of the formation of those states. The bulk properties and the space-time evolution of the hot and dense medium can be accessed by measurements of low-mass dileptons. It is possible to detect the electromagnetic radiation which is produced during all stages of the heavy-ion collision either as a real photon or a dilepton pair. Since they do not interact strongly with the medium, they carry information about the entire evolution of the system [3]. The LS 2, which gives the experiments the opportunity to upgrade their detectors, started in December 2018 and will end in early 2021 [4].

The excellent tracking performance even in a high-multiplicity environment, as well as the Particle Identification (PID) capabilities over a large momentum range due to the individual detector systems of ALICE are unique at the LHC. However, for many of the physics topics a high event statistics is required for precision measurements. Since many of the anticipated measurements require complex probes at very low transverse momentum on which a traditional triggering approach is not applicable to enhance the statistics, the ALICE experiment will undergo a high-rate detector upgrade. After this upgrade, the experiment will be able to examine practically all heavy-ion collisions delivered by the LHC at a rate of 50 kHz. This is a very different approach compared to the current readout strategy and the one of the other LHC experiments, where possibly interesting events are selected by means of a trigger [3]. With the detector upgrade, ALICE will improve its low-momentum vertexing and tracking capabilities to be able to measure also complex probes at low transverse momentum. The data taking rate will be significantly increased respectively developed into a continuous one without the need of a dedicated trigger. Otherwise, the performance especially the identification of charged particles will be preserved [3].

The upgrade program for the ALICE Time-Projection Chamber (TPC) consist of a new detector readout, including new Readout Chambers (ROCs) based on Gas Electron Multiplier (GEM) technology and a complete new Front-End Electronics (FEE), allowing for a continuous data taking. The continuous readout results in a huge data volume of 3.7 TB/s which must be reduced already during the read out by a factor of about 60. Otherwise it would exceed the expected available bandwidth and storage capabilities of the experiment [5]. The reduction will be done by reconstructing the detector signals online and writing only already processed data to the permanent storage instead of raw detector signals. An essential part of the online reconstruction is the cluster finding, where charge clusters have to be found in the data stream of the TPC before a tracking can be applied. The development of this Cluster Finder (CF) which will run on Field Programmable Gate Arrays (FPGAs) as part of the readout chain was the main topic of this thesis, together with all necessary data preparation steps that must be applied beforehand.

The thesis is divided into seven chapters. The remaining chapter 1 introduces the LHC and provides a short description of the ALICE experiment, together with a few upgrade examples of the detectors. Chapter 2 is dedicated to the description of the TPC and a more detailed explanation of the individual upgrade tasks for this detector to achieve the continues readout, together with an estimated timeline. The following chapter 3 explains the readout chain of the upgraded TPC with its individual components and presents the reasons for a change in the readout strategy with respect to the one described in the Technical Design Report (TDR) for the upgrade [5]. This is followed by a description of the general design concept of the Firmware (FW) for the Common Readout Unit (CRU) in chapter 4. This card will be used to receive the data from the FEE and is responsible for the first preprocessing steps in the readout chain. Chapter 5 contains the description of the individual modules which are needed in the FW to successfully reconstruct 2-dimensional charge clusters in the FPGA. This includes all the data preparation steps like decoding, sorting and a Baseline Correction (BLC), as well as the peak finding, calculation of the cluster properties and concludes with the overall resource consumption of the logic in the chip. In chapter 6, the validation of the previously described modules is presented in simulation and, whenever possible, in addition in a real readout system which was used during a test beam campaign in 2017. The CF, meaning the peak finding and the calculation of the cluster properties, was also implemented in software which is described in the last part of this chapter. The final chapter 7 summarises the achievements of this thesis and gives a short outlook to possible future developments.

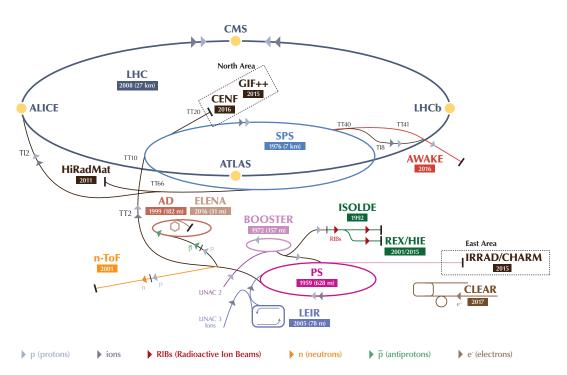

Figure 1.1: The CERN accelerator complex. The LHC is the last step in a cascade of accelerators, starting with the LINAC 2 for protons and LINAC 3 for ions. Protons are further accelerated by the PSB while the ions go to the LEIR. Both continue then with the PS and the SPS before finally reaching the LHC, taken from [7].

## 1.1 The Large Hadron Collider

ALICE is one of the four major experiments of the LHC. It is located at CERN near Geneva, Switzerland. Founded in 1954, CERN has been pursuing its mission to enable research in fundamental physics and to push the frontiers of science and technology. The LHC is the worlds largest collider and reaches the highest energies ever achieved of 13 TeV in proton-proton (pp) and 5.02 TeV/nucleon in lead-lead (PbPb) collisions. It is a superconducting hadron accelerator and collider and was installed in the already existing 26.7 km tunnel of the previous Large Electron Positron (LEP) machine. The LEP tunnel lies between 45 m and 170 m below the surface and its plane has an inclination of 1.4 %, sloping towards the lake Geneva. The *ring* consist actually of eight straight sections and eight arcs in which 1 232 superconducting dipole magnets are build, providing a nominal magnetic field of up to 8.33 T to keep the beams on track [6]. The LHC is the last piece in a series of successive accelerators, each increasing the energy of the particles further. This accelerator chain is shown in figure 1.1.

Protons start from a simple hydrogen gas bottle after which an electric field is used to strip the electrons from the hydrogen atoms to get the naked protons. Those are then accelerated by a linear accelerator (LINAC 2) to 50 MeV after which they are injected into the Proton Synchrotron Booster (PSB) to increase the energy to 1.4 GeV. The PSB is followed by the Proton Synchrotron (PS) to accelerate the protons to 25 GeV. The last step before the LHC is the Super Proton Synchrotron (SPS) to increase the energy further to 450 GeV.

In the LHC the protons are then accelerated to the final energy of up to 6.5 TeV per particle beam. The ions on the other hand take a slightly different path. The lead-ions are generated from a vaporised solid lead block and enter LINAC 3 for a first acceleration, followed by the Low Energy Ion Ring (LEIR) which pushes them from 4.2 MeV to 72 MeV. From here on, they are injected into the PS and follow the same path as the protons to end in the LHC [8].

The particle beams are brought to collision at four interaction points in the LHC, around which the four major experiments are build to study the reaction products of the collisions. These four experiments are:

- **ATLAS (A Toroidal LHC ApparatuS):** A general purpose detector located at interaction point 1. The detector was designed for the search of the, by now discovered, Higgs boson [9, 10]. Also the search for hints of new physics beyond the standard model, such as decays of supersymmetric particles, and extra dimensions are part of the physics program [11].

- **ALICE (A Large Ion Collider Experiment):** The dedicated heavy-ion experiment at the LHC. The detector is installed at interaction point 2 and was designed for the detection and the investigation of the QGP [12]. A more detailed description is given in the following section.

- **CMS (Compact Muon Solenoid):** A general purpose detector as well, installed at interaction point 5. The objectives are similar to those of ATLAS but with different detector techniques for a complementary measurement [13].

- **LHCb (LHC beauty):** The dedicated experiment for heavy flavour physics, located at interaction point 8. The experiment is build to look at CP violation and rare decays of bottom and charmed hadrons to find indirect evidence of new physics. Since these hadrons are predominantly produced at small opening angles with respect to the beam pipe in pp collisions. The construction of the experiment differs strongly from those of the other major experiments: LHCb is build as a single-arm spectrometer [14].

Three more, but smaller experiments can be found at the LHC. LHCf (LHC forward) is located on both sides of interaction point 1 with a distance of approximately 140 m to the collision point. It measures neutral particles, emitted in the very forward directions [15]. TOTEM is located along the beam pipe at distances of  $\pm 147$  m and  $\pm 220$  m from interaction point 5. It measures the total cross-section in pp collisions and studies the elastic and diffractive scattering independent of the luminosity [16]. The last one is the MOEDAL (Monopole and Exotics Detector At the LHC) with the task to look for magnetic monopoles in a direct search. The experiment is build at interaction point 8 [17].

## 1.2 ALICE at the LHC

As the dedicated heavy-ion experiment at the LHC, ALICE is designed to withstand the high particle density environment, expected at such collisions. The high granularity allows to measure charged particle multiplicities of up to  $dN_{\rm ch}/dy \approx 8000$  from a minimum transverse momentum of  $p_{\rm T} \approx 0.15 \,{\rm GeV}/c$  and, due to the individual sub-detector concepts a PID is possible for up to  $20 \,{\rm GeV}/c$  [18].

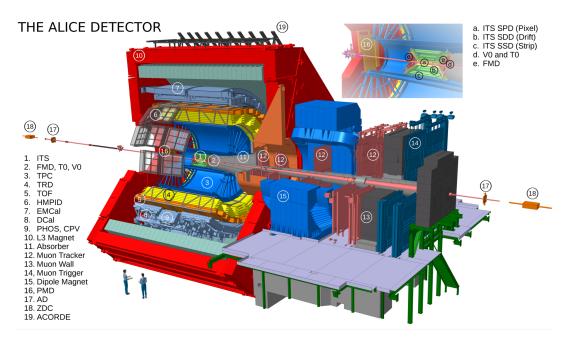

Figure 1.2: A schematic layout of the ALICE detector, showing the individual detectors. On the left side is surrounded by the red L3 solenoid the central barrel and on the right side is the muon spectrometer, taken from [19].

The ALICE detector is divided into the central barrel, fully contained within a solenoid magnet, and the muon arm on the c-side. This layout is shown in figure 1.2. The A-side is the detector part where the anti-clockwise circulation particle beam moves to, whereas the c-side is the opposite half, where the clockwise circulating beam moves to. The solenoid provides a magnetic field of 0.5 T and was inherited from the L3 experiment at LEP. The muon spectrometer starts also inside the central barrel with the hadron absorber, followed by the first two muon tracking stations. A third tracking station is enclosed in a dipole magnet, next to the solenoid. This is followed by two more tracking stations and iron absorber wall. Behind this absorber are the two muon trigger chambers. The beam pipe which has to go through the whole spectrometer is surrounded by low angle absorbers. The detectors of the central barrel are dedicated for tracking and PID. From inside out, there is first the Inner Tracking System (ITS) surrounding the interaction point. The ITS is enclosed by the TPC and the Transition Radiation Detector (TRD), followed by the Time-Of-Flight (TOF) detector, all having a full azimuthal coverage. Further outside with a reduced coverage there are three calorimeters, the ElectroMagnetic CALorimeter (EMCAL), the Di-jet CAL orimeter (DCAL) and the PHOton Spectrometer (PHOS), and a Ring-imaging Cherenkov detector (HMPID, High Momentum Particle IDentification). There are more detectors for the event characterisation, T0, V0 and the Zero Degree Craorimeter (ZDC). The Photon Multiplicity Detector (PMD) and Forward Multiplicity Detector (FMD) are used for particle multiplicity measurements. The ALICE COsmic Ray DEtector (ACORDE), which is located on top of the L3 magnet. It allows to trigger on muons from cosmic ray showers. In the following, the four main detectors of the central barrel are described in more detail.

#### 1.2.1 Inner Tracking System

The ITS is the innermost detector of ALICE. It combines three different technologies of silicon detectors in six cylindrical layers covering a radius from 4 cm to 44 cm. From the inside out there are first two layers of Silicon Pixel Detector (SPD), then two layers of Silicon Drift Detector (SDD) and then two layers of Silicon Strip Detector (SSD). Its main task is to provide the primary vertex reconstruction with a resolution of better than 100  $\mu$ m. In addition, the SDD and SSD can be used for PID via the dE/dx signal of the traversing particles due to the analog readout of the four outer layers [12].

#### 1.2.2 Time-Projection Chamber

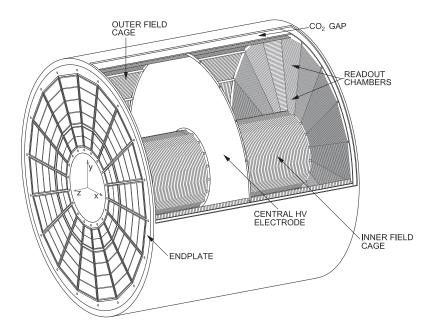

The TPC is the main tracking and PID device of ALICE. It consists of a cylinder whose axis is aligned with the beam axis and ranges from an inner radius of about 85 cm to an outer radius of about 250 cm. The cylinder has a length in z-direction of 500 cm, giving an active volume of ~87 m<sup>3</sup>. The TPC covers the full azimuth and a pseudorapidity range of  $|\eta| \leq 0.9$  for full tracks. The pseudorapidity is defined as

$$\eta = -\ln\left[\tan\left(\frac{\theta}{2}\right)\right],\tag{1.1}$$

with the polar angle  $\theta$  between the positive z and y-axis. The z-axis points from the collision point towards the A-side of the detector, while the y-axis points upwards, to the surface. For completeness, the x-axis points horizontally towards the centre of the colliders.

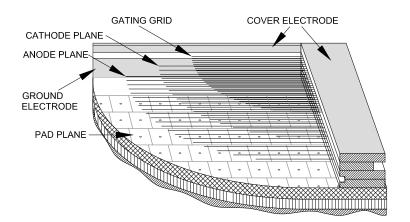

The volume of the TPC is split by a central electrode at 100 kV into two drift regions. This drift field of 400 V/cm leads to a drift time of 94  $\mu$ s for the electrons for the maximum drift length. The ROCs of the TPC are installed on both end plates of the cylinder. During Run 1 (2009–2013) and Run 2 (2015–2018) of the LHC their design was based on Multi-Wire Proportional Chambers (MWPCs) with a cathode pad readout. The replacement of those chambers by new ones based on GEM technology is the essential part of the upgrade program and described in chapter 2. The end plates are subdivided into 18 trapezoidal sectors, each covering 20° in azimuth. Since the track density depends on the radius, the requirements for the ROCs differ as a function of the radius. In order to meet these different requirements, each sector is divided into two separate chambers, an Inner Readout Chamber (IROC) which extends from 84.1 cm to 132.1 cm and an Outer Readout Chamber (OROC) from 134.6 cm to 246.6 cm [20]. The basic working principle of a TPC is described in section 2.1.

#### 1.2.3 Transition Radiation Detector

The TRD is the next detector of the central barrel in radial direction. It covers the full azimuth as well and a pseudorapidity range of  $|\eta| < 0.84$ . The subdivision into 18 sectors, the so called Super-Modules (SMs), was done to follow the segmentation of the TPC. Each SM consists of five stacks in z-direction, each stack of six layers of TRD chambers. This sums up to a total number of 522 individual chambers since the central stack of three SMs were kept empty to reduce the material budget in front of the PHOS detector. The layers are arranged at a radial distance between 2.90 m and 3.68 m from the beam axis. Each

chamber consists of a foam/fibre radiator, followed by a 3 cm drift region and a Xe-CO<sub>2</sub> filled MWPC. The electronics to read out the individual pads is directly mounted on top of the chambers. The radiator is used to generate the Transition Radiation (TR) photons, which are produced when a particle crosses the boundary between two media with different dielectric constants. Since the production probability of the TR at a single boundary is very low — in the order of the fine structure constant  $\alpha = 1/137$  — many boundaries are needed for a significant photon yield. To absorb the TR photons efficiently, which extend into the X-ray domain due to the high  $\gamma$  factor<sup>\*</sup> of the highly relativistic particles, the chamber is filled with a high-Z gas (Xe).

By having a sufficiently high sampling rate, a temporal information is extracted, representing the depth in the drift volume at which the signal is created. With that, the signal of the TR photons, which are preferably absorbed at the entrance of the chamber near to the radiator, can be distinguished from the signals resulting from the specific energy loss of the charged particle. This is uniformly distributed along the crossing particle trajectory.

To separate electrons from other charged particles, in particular pions, the presence of the TR signal respectively the absence of the signal for other particles due to a lower  $\gamma$ factor can be used. An additional criterion for the separation is also the higher dE/dxsignal for electrons due to the relativistic rise of the specific energy loss. The overall momentum resolution of the tracking in the ALICE central barrel is improved by including the six extra space points of the TRD at larger radii. Thanks to the fast readout and the online reconstruction capabilities, the TRD has also been used to trigger on electrons with a high transverse momentum and on jets [21].

#### 1.2.4 Time-Of-Flight detector

Also the TOF detector adapts the segmentation into 18 sectors of the TPC and covers the full azimuth. It is located adjacent to the TRD at radii of 370 cm to 399 cm from the beam axis. As the other central detectors of ALICE, it covers a pseudorapidity range of  $|\eta| \lesssim 0.9$ . The utilised detector technique is that of a Multi-gap Resistive-Plate Chamber (MRPC). The individual chambers consist of resistive glass plates with a high and uniform electric field, due to an applied voltage of 13 kV. Any initial ionisation, generated by a crossing charged particle, starts immediately an avalanche leading to the observed signal on the pick-up electrodes. Since there is no electron drift involved, the time jitter is caused only by the fluctuations in the growth process of the avalanche [12]. With this MRPC technology, a time resolutions of better than 50 ps is achieved [22]. By calculating the time-of-flight between the TOF signal and the collision time — either measured by the T0 detector, the LHC central timing or by TOF itself if enough tracks are present a PID can be done since the flight time is characteristic for each particle species at a given momentum.

<sup>\*</sup>The Lorentz factor is defined as  $\gamma = \sqrt{1 + \left(\frac{p}{m_0 \cdot c}\right)^2} = \frac{E_{\text{tot}}}{m_0}$ , where c is the speed of light, p the momentum,  $m_0$  the mass and  $E_{\text{tot}}$  the total energy of the particle.

### 1.3 Detector and Readout Upgrades for the LHC Run 3

To be able to read out the all PbPb events at an interaction rate of 50 kHz, as it is foreseen for LHC Run 3, and in order to improve the vertexing and tracking capabilities of ALICE, several detector upgrades are foreseen. Those upgrades will be done during the LS 2, ranging from December 2018 to spring 2021. The upgrade program starts with a new beam pipe with a smaller diameter, continues with a completely new, high-resolution and low-material ITS and a major upgrade of the TPC by replacing all MWPC based ROCs with new ones employing the GEM technology. The readout of TRD, TOF, PHOS and the muon spectrometer are upgraded and optimised for the very high rate. The forward trigger detectors are upgraded as well and the software framework for the online systems, the offline reconstruction and the physics analysis is completely rebuild [3]. It is also foreseen to add the new Muon Forward Tracker (MFT) to the acceptance of the muon spectrometer. This is a silicon pixel detector placed in front of the absorber which increases the pointing accuracy of the extrapolated muon tracks to reliably measure their offset with respect to the primary vertex of the collision [23].

One of the key ingredients in improving the general impact parameter resolution of the experiment is the new beam pipe with a reduced radius from previously 29 mm to 18.2 mm. This allows to move the innermost layer of the new ITS closer to the interaction point to a radius of 22.4 mm [24]. This together with a strongly reduced material budget by utilising the Monolithic Active Pixel Sensors (MAPS) technology (radiation length of only  $1.1 \% X_0$  per layer) and an all-pixel ITS with now seven layers at radial distances of 22.4, 30.1 and 37.8 mm for the inner barrel and 194.4, 243.9, 342.3 and 391.8 mm for the outer barrel will improve the track position resolution at the primary vertex by a factor three or better [25].

The exchange of the ROCs for the TPC allows for a continuous readout. With this it will be possible to record all events of the 50 kHz PbPb collision rate but requires new electronics as well. The upgrade will be described in more detail in chapter 2.

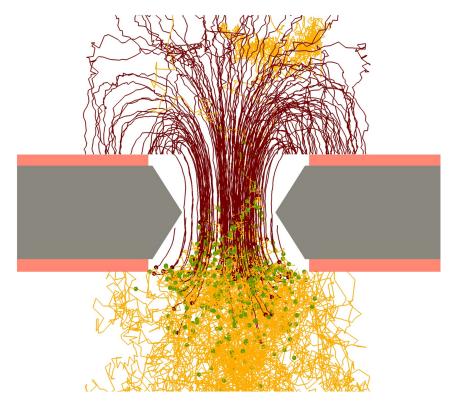

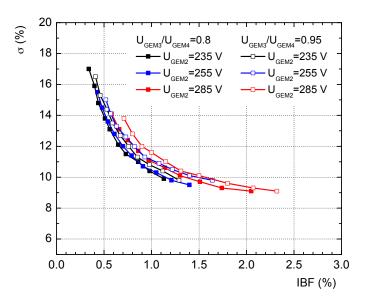

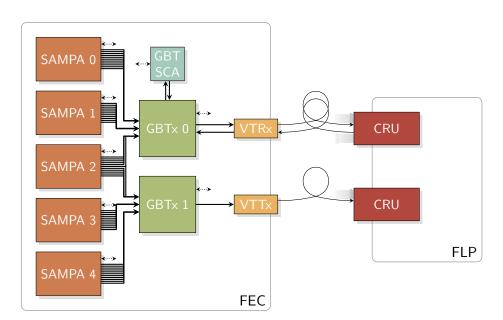

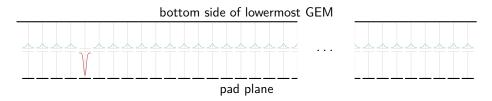

The TRD FEE can only be operated in a triggered, single event readout mode. Implementing a continuous readout would mean to exchange these electronics, requiring a complete disassembly and reconstruction of all the 18 SMs to replace the front-end boards mounted on each chamber. Since this is not realistically feasible, a different approach will be implemented. A reduction in event readout time by reducing the data volume will increase the possible trigger rate of the TRD. By transmitting only the so called *tracklets* (preprocessed track segments in a single detector chamber) instead of the raw data, it will be possible to record more than 70 % of the events in the 50 kHz PbPb collision scenario. Besides that, no issues concerning the detector stability or space charge effects due to the increased multiplicity are expected [26].