Design of complex integrated systems based on networks-on-chip – Trading off performance, power and reliability –

Thesis submitted in partial fulfillment of the requirements for the degree

## of Doktor-Ingenieur (Dr.-Ing.) at the

Faculty of Computer Science and Electrical Engineering, University of Rostock, Germany

Submitted by Claas Cornelius, from Rostock

Rostock, July 9, 2010

#### **Doctoral Advisor:**

Prof. Dr.-Ing. Dirk Timmermann

University of Rostock, Germany

### **Additional Reviewers:**

Prof. Dr.-Ing. Yiannos Manoli Prof. Dr. sc.techn. Andreas Herkersdorf University of Freiburg, Germany Technische Universität München, Germany

Date of submission: July 9, 2010

Date of defense: March 25, 2011

Copyright © 2010 by Claas Cornelius

All rights reserved. No part of the material may be reproduced or reprinted in any form or by any electronic or mechanical means – including photocopying, recording or any information storage and retrieval system– without the prior written permission of the author.

Any of the trademarks, service marks or similar rights that are cited in this work is the property of their respective owners. Their nomination does not imply that you may use them for any other purpose other than for the same or a similar informational use as contemplated here.

## Preface

This thesis originated during my time as scientific coworker at the Institute of applied Microelectronics and Data engineering (Institute MD), University of Rostock. Therefore, my sincere gratitude goes first and foremost to Prof. Dirk Timmermann who called my attention to the exciting field of microelectronics and who gave me the chance to write this thesis. With him as my doctoral advisor, I found myself in an excellent environment to develop own ideas while being attended with constructive criticism. This has been a great inspiration for my scientific and personal development. Moreover, I would like to thank all other professors and colleagues at the Institute MD for numerous fruitful discussions and assistant advice. Two of those colleagues shall be named in particular who already guided me as a student and who have been of invaluable help ever since. Thus, without Dr. Frank Grassert and Dr. Frank Sill this thesis would potentially not have been possible – but definitely not as exciting as it has been.

Beyond that, I would like to gratefully acknowledge those companies that provided detailed insights into their work and organizational structure. In conjunction with the interdisciplinary experiences within the post graduate program, this has remarkably opened my views of both research and society. Finally, I was in the fortunate position to receive feedback and helpful support due to diverse student theses. Hence, I would also like to thank those students who had the confidence in me as the tutor for their respective projects.

Last but not least, my sincere thanks go to my family and friends for their continuous support and patience. The time with them has prepared the ground to keep my ambitions, especially in stressful times. However, there are no words to express the significance of and gratefulness for my parents Karin and Dieter. With no doubt, it is their love and care that has actually brought me here. They not only gave me the freedom to follow my personal believes, but always encouraged me by any conceivable means.

Rostock, June 23, 2010 Claas Cornelius

# Contents

| 1 | INTR   | ODUCTION                                                | 1  |

|---|--------|---------------------------------------------------------|----|

|   | 1.1 M  | OTIVATION AND OBJECTIVES                                | 1  |

|   | 1.2 O  | RGANIZATION OF THIS WORK                                |    |

| 2 | INTE   | GRATED SYSTEMS AND THEIR MAIN CHALLENGES                | 5  |

|   | 2.1 Sc | ALING OF TECHNOLOGY                                     | 6  |

|   | 2.1.1  | Fundamentals of scaling and their impact on performance |    |

|   | 2.1.2  | Physical limits and their connected issues              |    |

|   | 2.2 Pc | OWER CONSUMPTION                                        |    |

|   | 2.2.1  | Constituents of power consumption                       |    |

|   | 2.2.2  | Classification of low-power approaches                  |    |

|   | 2.2.3  | Interim conclusion for viable low-power solutions       |    |

|   | 2.3 RI | ELIABILITY AND ROBUSTNESS                               |    |

|   | 2.3.1  | Terminology and analytical definition                   |    |

|   | 2.3.2  | Categorization of failure causes                        |    |

|   | 2.3.3  | Classification of techniques to raise reliability       |    |

|   | 2.3.4  | Interim conclusion for reliability approaches           |    |

|   | 2.4 Al | CHITECTURES FOR SYSTEM COMMUNICATION                    |    |

|   | 2.4.1  | Point-to-point                                          |    |

|   | 2.4.2  | Bus-based                                               |    |

|   | 2.4.3  | Networks-On-Chip                                        |    |

|   | 2.4.4  | Analytical comparison: Bus vs. NOC                      |    |

|   | 2.5 Ri | ESULTING OBJECTIVES FOR THIS WORK                       |    |

| 3 | COMI   | PONENTS IN ON-CHIP NETWORKS                             |    |

|   | 3.1 SI | GNAL TRANSMISSION ACROSS LINKS                          |    |

|   | 3.1.1  | Fundamentals of wires                                   | 45 |

|   | 3.1.2  | Models for wires and complex links                      |    |

|   | 3.2 AI | PPROACHES TO IMPROVE SIGNAL TRANSMISSION                |    |

|   | 3.2.1  | Repeater insertion                                      |    |

|   | 3.2.2  | Further solutions                                                  |     |

|---|--------|--------------------------------------------------------------------|-----|

|   | 3.3 PA | CKET TRANSMISSION ACROSS ROUTERS                                   | 53  |

|   | 3.3.1  | Router architecture and general functionality                      |     |

|   | 3.3.2  | Switching scheme and flow control                                  |     |

|   | 3.3.3  | Data width and FIFO depth                                          | 61  |

|   | 3.4 Ap | PROACHES TO ENHANCE ROUTER CHARACTERISTICS                         | 63  |

|   | 3.4.1  | Clock and power gating to preserve power                           | 63  |

|   | 3.4.2  | Application of different threshold voltages                        | 65  |

|   | 3.4.3  | Router layout for reduced area costs                               | 68  |

| 4 | ARCH   | ITECTURES AND ALGORITHMS OF NETWORKS-ON-CHIP                       | 71  |

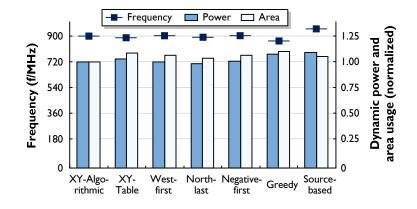

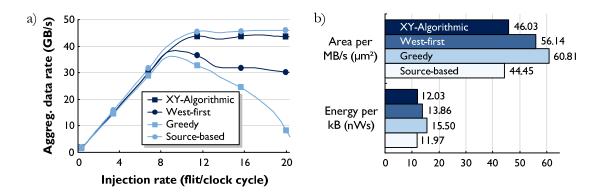

|   | 4.1 Ev | ALUATION OF ROUTING ALGORITHMS                                     | 75  |

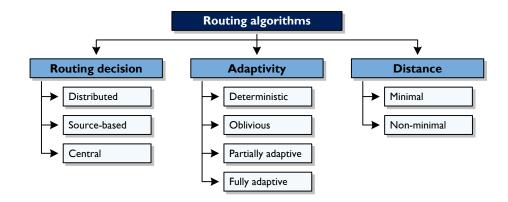

|   | 4.1.1  | Taxonomy of routing schemes                                        | 76  |

|   | 4.1.2  | Communication performance                                          | 79  |

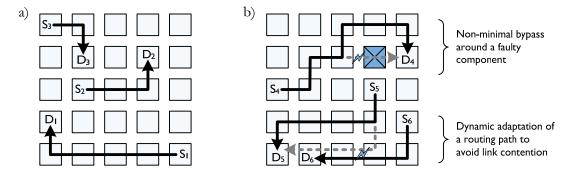

|   | 4.1.3  | System functionality in the presence of failures                   |     |

|   | 4.2 HE | TEROGENEOUS DISTRIBUTION OF PACKET FIFOS                           |     |

|   | 4.2.1  | FIFO depth based on utilization                                    |     |

|   | 4.2.2  | System characteristics for different FIFO distributions            | 90  |

|   | 4.3 CL | USTERED TOPOLOGIES FOR COST SAVINGS                                |     |

|   | 4.3.1  | Setup of advanced topologies                                       | 94  |

|   | 4.3.2  | Network properties and simulation setup                            |     |

|   | 4.3.3  | Communication characteristics and design costs                     |     |

|   | 4.4 Ex | PLOITING ARCHITECTURAL CHARACTERISTICS                             | 104 |

|   | 4.4.1  | Local traffic                                                      |     |

|   | 4.4.2  | Distributed monitoring and control                                 |     |

|   | 4.5 SY | STEM MANAGEMENT                                                    | 113 |

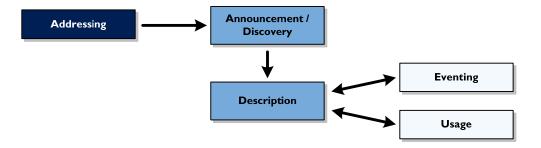

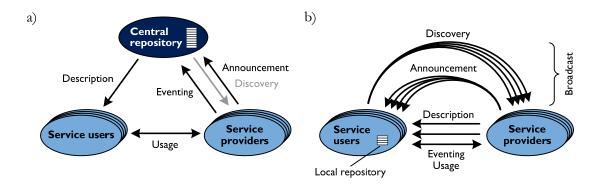

|   | 4.5.1  | Existing approaches                                                | 114 |

|   | 4.5.2  | Service-oriented architectures and their use in integrated systems | 115 |

|   | 4.5.3  | Implementation considerations for SOA                              | 118 |

| 5 | CASE   | STUDIES OF COMPLEX SYSTEMS                                         | 123 |

|   | 5.1 Re | QUIREMENTS FOR EFFICIENT SYSTEM DESIGN                             | 123 |

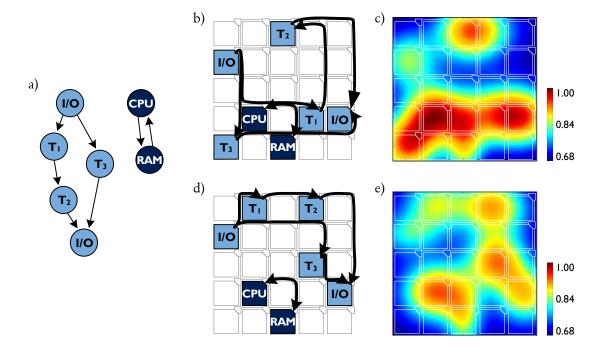

|   | 5.2 ST | UDY I: BROADBAND PACKET PROCESSING                                 | 127 |

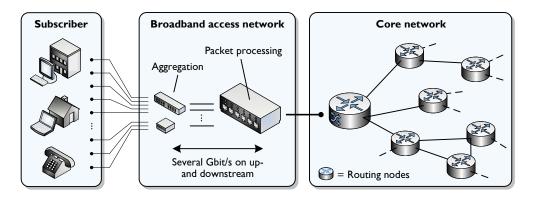

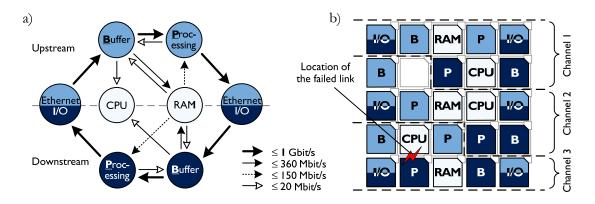

|   | 5.2.1  | Application scenario and system design                             |     |

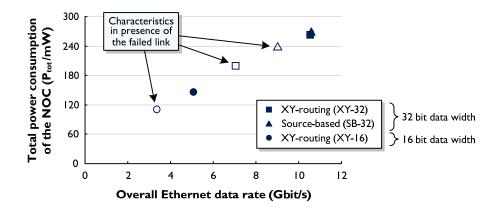

|   | 5.2.2  | Comparison of system characteristics                               | 130 |

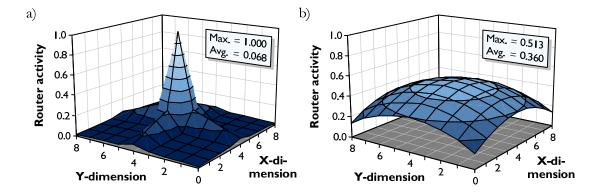

|   | 5.3 ST | UDY II: ADAPTIVE SYSTEM MANAGEMENT                                 | 133 |

|   | 5.3.1  | System setup                                                       |     |

|   | 5.3.2  | Distribution of temperature during operation                       | 135 |

| 6 | CONC   | LUSION AND OUTLOOK                                                 | 139 |

## INDICES

| LIST OF FIGURES           |     |

|---------------------------|-----|

| LIST OF TABLES            | 151 |

| ABBREVIATIONS AND SYMBOLS |     |

| References                |     |

## Chapter 1 Introduction

The concept of digital data has severely influenced humankind by enabling the widespread use of recording, manipulation, transmission and storage of large amounts of information. Corresponding common appliances range from mainframe and personal computers to mobile devices. Beyond that, more and more non-digital application areas are also being implemented by digital electronics due to their advantages in cost and functionality. This shift has opened new markets and generated products that are part of everyday life by now –like the compact disc, digital photography or telecommunication. Thus, such microelectronics is omnipresent in today's society and can be found in plenty of application domains covering for instance automation, computing, entertainment, communication, automotive and medical engineering as well as home appliances.

The major constituent of microelectronics is the **Integrated Circuit** (IC), which is a miniaturized electronic circuitry fabricated on a single substrate. Only half a century after the development of the first prototype, integrated circuits have exponentially increased in functionality and performance, which is recognized most evidently using the example of microprocessors and memory chips. No other industry has gained such a tremendous success, representing a multibillion dollar business that sells more microprocessors every year than there are inhabitants on the Earth [Sem09]. However, consumer expectations have grown similarly to the boost of performance of integrated circuits. Thus, to develop ever faster computers or multi-purpose mobile devices – such as personal digital assistants and mobile phones – remains a highly challenging task for technologists and designers in the future.

## **1.1** Motivation and objectives

The development of the first integrated circuit in 1958 has been the inception of the trend to manufacture ever smaller electronic components. This miniaturization has led to faster and less power-hungry devices while at the same time more components could be integrated on a single substrate at reduced costs. The empirical observation that the number of components per integrated circuit grows exponentially over time was formulated in Moore's Law in 1965 [Moo65] and has become a self-fulfilling prophecy and the driving force of the semiconductor industry. As a result, current commercial products comprise billions of microelectronic components and feature the computing power of former supercomputers. The technical foundation of such products bases on planar manufacturing technology and Complementary Metal Oxide Semiconductor (CMOS) logic. Both concepts were commercially adopted in the 1980s and have not been fundamentally changed ever since. Even though this approach has proven to be successful over the last decades, it is connected with an increasing number of technical problems [Che06]. These issues arise due to the tiny size of current technology with particular dimensions in the range of a few atomic layers. Hence, the further downsizing of microelectronic components is limited and threatens the continuous improvement of integrated circuits. Furthermore, alternative technologies are not at hand to overcome today's severe difficulties of limited performance, growing power and reliability issues as well as the dramatic boost of costs for development and manufacturing. Thus, the investigation of new design methodologies and system architectures is a primary concern of the semiconductor industry [Itr07a].

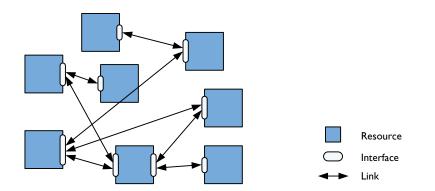

The fundamental shift towards new design paradigms is most evident by the abandonment of increasing clock frequencies in microprocessor design. That is, spatially distributed and concurrent computation is favored now over the acceleration of local and temporal computation. This abstract definition is apparent in commercial products by stagnating clock frequencies but increasing numbers of computation cores – such as Intel's Xeon, AMD's Opteron or Sun's Niagara series. The communication between the various cores within complex integrated circuits bases primarily on proprietary and application-specific communication backbones or bus-based shared media. However, both approaches are not fully scalable, which means that their system characteristics do not change proportional to the number of communication participants. For instance, the average period of use per participant decreases in a shared medium as more participants access the communication backbone. Accordingly, both existing approaches are not appropriate against the background of an increasing number of cores and their requirements to the on-chip communication.

A promising design approach is the application of a **Network-On-Chip** (NOC) to overcome or to mitigate the challenges of current and future technologies. NOCs offer a packet-oriented communication scheme and are characterized by their modular structure and their concurrency of computation as well as communication. However, to this day very few commercial products based on NOC have been released as such a communication-centric design paradigm comes along with a set of new and unsolved questions that have neither been finally answered by the industry nor by the academic community -e.g. design space exploration, reliability or system monitoring and control.

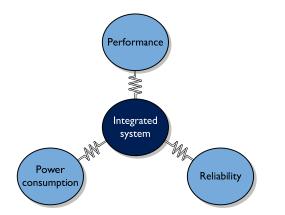

**Objectives**: This thesis aims at contributing to an advanced understanding and an improved implementation of networks-on-chip in nanotechnology. Its special focus is to demonstrate the

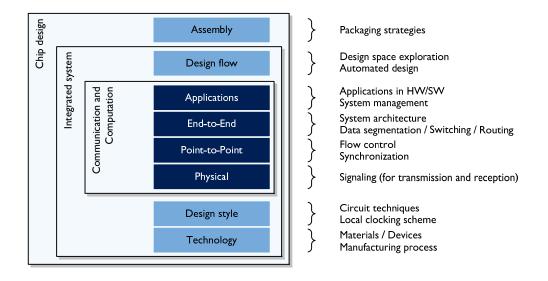

interlocking characteristics of performance, power consumption and reliability since system functionality in the presence of failures has not yet been addressed in-depth. For this purpose, the individual components of on-chip networks will have to be conceptually designed, implemented and characterized. On this basis, improvements shall be developed that demonstrate and exploit the fact that the various abstraction layers of a system are also intertwined and can rarely be regarded separately. Thus, this approach is to prove that efficient system design requires a crosslayered development ranging from the underlying hardware platform to the architecture and the system design.

## 1.2 Organization of this work

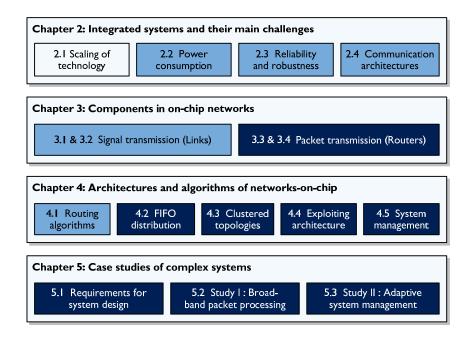

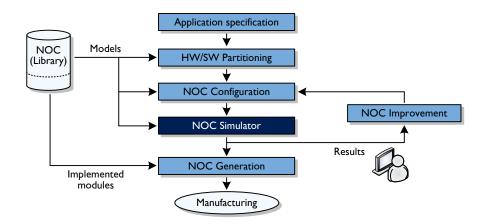

Following the motivation and objectives of the thesis in this chapter, the key aspects of importance are introduced in chapter 2 together with a classification of critical issues and existing design solutions. Moreover, the characteristics of Networks-On-Chip (NOCs) are discussed and analytically compared to conventional bus-based design. After that, the implementation of the fundamental components of NOCs is described in chapter 3 covering the links and routers. Thereby, reference components are derived as well as several approaches to improve system design. Based on the individual components, chapter 4 determines system behavior against the background of different architectures and algorithms. The achieved results lead to various advancements that are also presented and discussed. The subsequent chapter 5 specifies the requirements for the simulation and development of complex systems based on NOC, and

**Figure 1-1 :** Structure of this work with those sections highlighted that contain own contributions (Legend: Contains considerable own contributions, Partly contains own contributions)

#### Chapter 1 – Introduction

presents different case studies considering the findings of the previous chapters. Lastly, chapter 6 concludes this work and gives a brief outlook on future developments. Figure 1-1 illustrates the structure of this work in further detail and highlights the sections containing own contributions.

# Chapter 2 Integrated systems and their main challenges

Early integrated circuits (ICs) comprised the functionality of a specific functional module. Thus, complex systems had to be built by combining different ICs on a printed circuit board. As manufacturing technology advanced, it became possible to integrate more and more system functionality onto a single silicon substrate (also termed die). Tangible examples of such **integrated systems** are today's microprocessors that contain an ever-growing number of diverse functional modules that were previously located in individual dies – as for instance memory controllers, wired and wireless interfaces as well as graphics processors [Amd05, Lia08]. The driving forces to implement such Systems-On-Chip (SOCs) are an overall cost reduction and enhanced system characteristics. Certainly, there is a vast range of applications with diverse requirements including amongst others high-performance computing, portable low-power devices or secure processing. Nonetheless, the International Technology Roadmap for Semiconductors (ITRS) states the following main and general challenges for integrated systems [Itr07a]:

- Manufacturability: This describes the ability to produce refined chips at reasonable costs and feasible schedules. Primary aspects are the continuous scaling and the integration of new materials and devices to sustain the previous performance growth (see section 2.1).

- Power consumption: Considerations have to include all aspects of power consumption (e.g. dynamic power, leakage, power density) across the different design layers ranging from layout over architecture to system management (see section 2.2).

- Reliability: The aim of reliable design is to achieve a system that performs as desired over time and under the influence of temporary and permanent disturbances (see section 2.3).

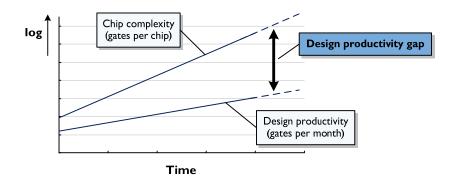

- Design productivity: As technology progresses towards ever more complex integrated circuits, design productivity has to keep with the pace to maintain design quality and

development costs within a feasible range. Key enablers are system integration, high level of abstraction, reuse and modularity (see section 2.4).

A detailed description of the main challenges and their dependencies among one another follows in the next sections. Lastly, section 2.5 concludes the findings and determines the resulting objectives for this work. Thus, this chapter provides the basis for the subsequent investigations that refer to the contemplated challenges.

## 2.1 Scaling of technology

The term scaling denotes the downsizing of miscellaneous parameters in semiconductor technology. Even though other device characteristics are also affected, the prime motivations for scaling are cost reduction and performance increase. For example, when you halve the physical dimensions of a microelectronic component you can fabricate four instances within the same given area. Assuming that manufacturing costs are roughly constant, the price per component is greatly cut down to one fourth. The most important component that such scaling refers to is the transistor, which acts like a voltage-controlled switch. This is what makes the transistor so worthwhile for implementing binary digital logic.

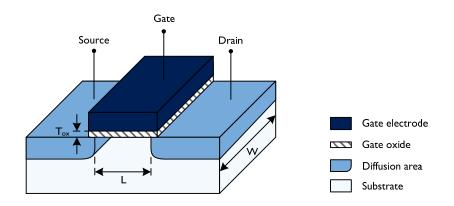

Figure 2-1 depicts the spatial arrangement of a **transistor** in a contemporary planar bulk process with its main physical dimensions. Here, the top layer of the structure is the gate electrode, which is a good conductor. The middle layer is a thin insulating film called the gate oxide. Finally, the bottom layer is a doped silicon substrate with two diffusion areas that are contrary doped to the substrate and are named source and drain. This type of transistor operates as follows in the initial state. As the diffusion areas are contrary doped to the substrate, their intersections form reverse-biased diodes so that no current can flow. However, when a voltage is applied to the gate, the charge concentration underneath the gate oxide can be modulated due to the emerging electric field –just as in a capacitor. Thus, when the gate-source voltage  $V_{gs}$  is sufficiently large (i.e. larger than the threshold voltage  $V_{th}$ ), the charge concentration underneath

**Figure 2-1:** Schematic illustration of the electrical connections and the physical composition of a MOS transistor in a planar bulk process technology

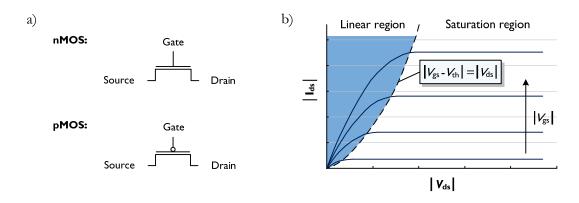

**Figure 2-2 :** a) Schematic symbols of MOS transistors and b) their idealized I-V characteristic based on the first-order transistor model from Shockley [Sho50]

the gate oxide is inverted and forms a channel between source and drain where an electric current can flow. The name for this class of transistors rests upon their primal materials with a metal gate electrode and their operation based on the electric field: Metal Oxide Semiconductor Field Effect Transistor (MOSFET or MOS in short). Moreover, two types of such transistors need to be distinguished with regard to the kind of applied doping. Firstly, transistors with negative charge carriers due to excess free electrons in the diffusion areas are called nMOS. Secondly, transistors with positive mobile charge carriers are called pMOS, respectively. In principle, the structure and mode of operation is the same for nMOS and pMOS but with different polarities for the associated voltages and currents. In a nutshell, the primary evident parameters for transistor operation are the gate length L, the gate width W, the thickness of the gate oxide  $T_{ox}$  (see figure 2-1), the type and strength of doping concentrations as well as the threshold voltage  $V_{th}$ and the gate-source voltage  $V_{es}$ .

The schematic symbols of MOS transistors are illustrated in figure 2-2 together with their idealized current-voltage (I-V) characteristic. The diagram relates the drain-source current  $I_{ds}$  for different gate-source voltages  $V_{gs}$  against the drain-source voltage  $V_{ds}$ . The point of origin for the characteristic and the following analytical description is based on the simplified, first-order transistor model for long channel devices from Shockley [Sho50]. Although much more elaborate models are used today for transistor simulations [Sak90], the mentioned model is greatly meaningful and reproduces transistor functionality accurate enough to clarify its mode of operation.

The following description relates to the characteristic of the nMOS transistor, although it also applies analogously for the pMOS transistor with opposite polarities of charges and voltages [Wes05, Rab03]. In any case, three different regions need to be distinguished. Firstly, the transistor is said to be **cutoff** when the gate-source voltage  $V_{gs}$  is smaller than the threshold voltage  $V_{th}$  and no electric current flows between drain and source (see equation 1). Hence, the other two regions come into play as  $V_{gs}$  exceeds  $V_{th}$  so that a conducting channel originates between drain and source. Furthermore, the second region is called **linear region** because  $I_{ds}$ increases almost linearly with the drain-source voltage  $V_{ds}$  (see equation 2). The delineation to the third region is plotted in figure 2-2 b) as a dashed line and is given by  $|V_{gs} - V_{th}| = |V_{ds}|$ . This means that for large drain-source voltages  $V_{ds}$  the conducting channel is no longer fully inverted in the vicinity of the drain. Hence, the channel between source and drain is pinched off and  $I_{ds}$ saturates at a constant level for increasing  $V_{ds}$  (see equation 3). Therefore, the third region is termed **saturation region**. Two further parameters appear in the equations that refer to the materials of the transistor: the permittivity of the gate oxide  $\varepsilon_{ox}$  and the mobility of charge carriers  $\mu_0$ . Consequently, it can be concluded from the I-V characteristic and the given equations that device dimensions and voltages as well as materials affect transistor operation, and thus need to be considered when technology is scaled.

$$0 \qquad \qquad \text{for} \quad V_{\rm gs} < V_{\rm th} \qquad (1)$$

$$I_{\rm ds} = \frac{\mu_0 \frac{\varepsilon_{\rm ox}}{T_{\rm ox}} \frac{W}{L} \left( V_{\rm gs} - V_{\rm th} - \frac{V_{\rm ds}}{2} \right) V_{\rm ds}}{for \quad V_{\rm ds} < V_{\rm gs} - V_{\rm th}}$$

(2)

$$\frac{\mu_0}{2} \frac{\varepsilon_{\rm ox}}{T_{\rm ox}} \frac{W}{L} \left( V_{\rm gs} - V_{\rm th} \right)^2 \qquad \qquad \text{for} \quad V_{\rm ds} \ge V_{\rm gs} - V_{\rm th} \tag{3}$$

#### 2.1.1 Fundamentals of scaling and their impact on performance

The pertinent questions of scaling are to what extent the miscellaneous parameters are changed and how the continuous scaling affects the operating properties of MOS transistors. The original scaling analysis considered three different models that are based on two independent factors: *S* refers to the physical dimensions and *U* applies to the voltages [Rab03, Den74, Bac82]. The first model was **full scaling** whereas dimensions and voltages are reduced by the same factor *S*. Thus, the electric field across the gate oxide remains constant and the physical integrity of the transistor is ensured across different technology generations. Furthermore, such scaling leads to smaller area usage (i.e. greater device density), higher performance and reduced power consumption. However, this scenario was no viable option, as well-defined levels for component compatibility and noise-error margins needed to be maintained. Consequently, the second model in practice was **fixed-voltage scaling**. Thereby, the dimensions are scaled down but the voltages are kept constant. Therewith, this model became prohibitive with the emergence of short channel effects [Bjö81]. Against this background, fixed-voltage scaling does not give a significant performance benefit over full scaling but comes with a major power penalty and undesirable

**Table 2-1:** Summary of the different scaling scenarios (with the scaling factor *S* being historically roughly  $\sqrt{2}$  and S > U > 1)

|                     | Full<br>scaling | Fixed-voltage<br>scaling | General<br>scaling | Equivalent<br>scaling |

|---------------------|-----------------|--------------------------|--------------------|-----------------------|

| Physical dimensions | 1/S             | 1/S                      | 1/S                | < 1/S                 |

| Voltages            | 1/S             | 1                        | 1/U                | < 1/U                 |

| Materials           | Unchanged       | Unchanged                | Unchanged          | Changing              |

| Device structure    | Unchanged       | Unchanged                | Unchanged          | Changing              |

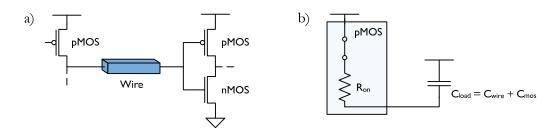

**Figure 2-3 :** a) Common scenario in a contemporary digital circuit and b) its equivalent RC circuit model for a delay estimate

physical phenomena. A sustainable compromise between the first two models leads to the third model named **general scaling**. Here, physical dimensions and voltages are scaled down by different independent factors whereas the voltages do not drop as fast as the dimensions. Table 2-1 summarizes the introduced scaling scenarios with their appropriate scaling factors.

The further downsizing of physical dimensions and voltages poses exceptionally difficult challenges, as current nanotechnology has reached atomic scales by now. Hence, miniaturization is slowing down which is represented in the last column of table 2-1 by smaller scaling factors. However, in order to retain the previous performance growth, new materials and modified device structures come into consideration. This scenario of **equivalent scaling** enables further performance improvements without such aggressive geometric scaling as seen in earlier technology generations. Examples of corresponding changing materials are the integration of high- $\varkappa$  dielectrics and diverse gate materials [Pig06, Doy06]. Moreover, sophisticated changes of device structures cover for instance elevated and extended diffusion areas, halo implants as well as offset spacer [Cho02, Won04].

Tightly coupled to the pursuit of smaller device area and reduced costs is the striving for increased transistor speed. Thus, it is necessary to estimate MOS performance without resorting to complex simulation models. A simple approach resulting in quite accurate delay estimates is to regard transistors as idealized switches in series with resistors and the rest of the circuit as a network of capacitors. A common scenario of a digital circuit is shown in figure 2-3 a) where a pMOS charges the attached node of a wire and a subsequent logic gate –here, an inverter composed of two transistors. The difficulty to obtain the equivalent RC circuit model in figure 2-3 b) is to average the load capacitance  $C_{\text{load}}$  and the on-state resistance  $R_{\text{on}}$  that are based on dynamic and non-linear characteristics. However, based on equation 2 and the time constant  $\tau$  for the RC model, the following expression can be derived for the **delay time of a transistor**  $t_{\text{MOS}}$  to charge or discharge a capacitor:

$$t_{\text{MOS}} = k_{\text{vr}} \cdot \tau = k_{\text{vr}} \cdot R_{\text{on}} C_{\text{load}} = k_{\text{vr}} \cdot \left(\frac{\partial I_{\text{ds}}}{\partial V_{\text{ds}}}\right)^{-1} C_{\text{load}}$$

$$\Rightarrow t_{\text{MOS}} \approx k_{\text{vr}} \cdot \frac{T_{\text{ox}}}{\mu_0 \varepsilon_{\text{ox}}} \frac{L}{W} \frac{C_{\text{load}}}{(V_{\text{dd}} - V_{\text{th}})} \quad \text{with } \begin{cases} V_{\text{dd}} = V_{\text{gs}} \\ \mu_0 = \mu_0(T) \text{ and } V_{\text{th}} = V_{\text{th}}(T) \end{cases}$$

(4)

Whereas  $k_{\rm vr}$  is a factor related to the voltage range of the delay time,  $V_{\rm dd}$  denotes the supply voltage and the load capacitance  $C_{load}$  subsumes the capacitances due to the wire  $C_{wire}$  and all transistors  $C_{\text{mos}}$  involved (with  $C_{\text{mos}} \propto W \cdot L$ ). It should be stressed that a large gate width W of the driving transistor, a small threshold voltage  $V_{\rm th}$  and a high supply voltage  $V_{\rm dd}$  result in a short delay time  $t_{MOS}$ . By contrast, enlarging the oxide thickness  $T_{ox}$ , the load capacitance  $C_{load}$  or the gate length L leads to an increased delay time  $t_{MOS}$ . Beyond that, the carrier mobility  $\mu_0$  and the threshold voltage  $V_{\rm th}$  are subject to a complex dependence on temperature T. Based on these correlations, one can say that transistor performance generally also degrades with higher temperatures [Gut01, Hun05, Tsa00]. Furthermore, the consideration of wire capacitance Cwire in the delay estimate already indicates its impact on performance. However, as wires are also affected by scaling, their parasitic effects increase drastically and play a significant role for system characteristics and design decisions. This fact is reflected in the following sections and is investigated thoroughly in sections 3.1 and 3.2. Lastly, even though transistor performance in terms of the delay time  $t_{MOS}$  is also the foundation for performance estimates on other design layers, the definition of particular metrics varies considerably -ranging from gate delay to frequency and throughput. Thus, such additional metrics are introduced in the appropriate sections.

#### 2.1.2 Physical limits and their connected issues

Atomic scales of devices in current technology limit the further downsizing both due to obvious geometrical reasons and due to intrinsic material characteristics. For example, the gate oxide thickness is in the range of a few nanometers – which is equivalent to a few atomic layers – and there are just a sparse number of dopant atoms in the transistor channel of less than a hundred. Such tiny structures are not only extremely difficult to manufacture in order to obtain homogeneous devices and operating characteristics, but lead to a large number of new and aggravated issues. Moreover, intrinsic material characteristics as the silicon bandgap or the built-in junction potential can simply not be scaled to keep the physical integrity of transistors. Lastly, to modify device voltages (e.g. supply or threshold voltage) is in addition restricted by physical factors that relate to power consumption and reliability (see sections 2.2 and 2.3). In summary, the given limits of various physical parameters are connected with a wide range of issues that impact all layers from manufacturing to system design [Bor99]. An extract of the most important and relevant ones for this work is given in the following.

Manufacturing technology needs to experience major changes in order to fabricate ever smaller and consistent devices as well as to integrate new materials and refined process steps. In particular, current lithography and its connected requirements (e.g. masks and resists) represent a key limiter due to the used deep ultraviolet light sources with a wavelength of 193 nm, which mainly affects the smallest critical dimension that can be uniformly reproduced. Even though process advances do slightly relieve the issue –such as immersion lithography or optical proximity correction – they cannot completely circumvent the need for a fundamental change in the long term [Itr07c]. Furthermore, additional and refined process steps are prospectively required to allow following those principals of equivalent scaling (see subsection 2.1.1). This means first and foremost that innovative materials have to be integrated which requires the consideration of decisive chemical and physical side-effects. An example for the former is the unintentional diffusion of interfacing materials, and the thermal and mechanical implications of low- $\varkappa$  dielectrics are examples of the latter [Itr07e]. After all, the introduction of entirely new device structures –like multi-gate MOSFETs and insulated substrates – will also help to mitigate the miscellaneous short channel effects [Bjö81]. Hence, the combined efforts in manufacturing might alleviate the significant issues of scaling that conventional bulk CMOS is facing.

Further physical limits become apparent in circuit design as the propagation speed of charge carriers and thermal noise determine how fast and how reliable signals can be communicated across the die [Rab03]. Hence, as die size does not shrink, neither the length of global wires nor their delay time does decrease. Even local wires in dense logic impact system metrics significantly due to increasing wire resistance and capacitance (see section 3.1). Accordingly, overall system performance is about to being restricted by rather data communication than computation [Nur04]. This fundamental shift has already led to the introduction of multi-level caches and task switching. Such approaches try to mask the latencies due to slow memory access whereas communication delay plays a decisive role. However, the confined signal propagation delay also influences design decisions on system level. For example, higher operating frequencies delimit the distance that can be reached by a signal within a single clock cycle [Liu04]. Thus, fully synchronous designs will be prohibitive and globally asynchronous architectures with latency tolerant components will have to be implemented.

The list of connected issues due to the limits of scaling comprehends further domains. One domain is power consumption that includes considerations not only related to the absolute power dissipation but also secondary effects such as power density and thermal implications. Other domains are reliability and robustness because the increasing number of components as well as additional physical phenomena increases the probability of disturbances or system failure. These three challenges together with convenient approaches are thoroughly discussed in sections 2.2 and 2.3, respectively. Finally, the design process in general is also inevitably affected as all technical changes and new solutions have to be accounted for within the design flow and the corresponding design tools. This vast field comprises manifold aspects including the modeling of diversified components (like digital, RF, analog or memory), test and verification, design for manufacturing and many others. Because of the substantial complexity of these issues, they are only covered where due consideration is necessary.

Concluding, albeit the stated physical limits are diverse and impair miscellaneous aspects, they have all in common that the costs for manufacturing, design and test drastically increase with further scaling of technology. Thus, besides essential individual solutions, new design paradigms, architectures as well as combined efforts are required that also exploit the interlocking characteristics of the different design steps and abstraction layers –as for instance Design For Manufacturing (DFM) is already aimed at.

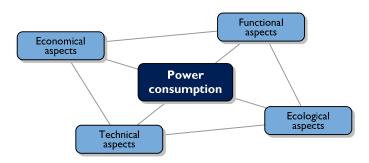

**Figure 2-4 :** Illustration of various intertwined aspects related to power consumption that affect developers, vendors as well as customers

## 2.2 Power consumption

The term electric power consumption defines the amount of electrical energy that is transferred by a consumer in a given time – and is thus another critical design parameter alongside performance. Similarly to the performance of integrated circuits, the overall power consumption has seen a dramatic increase over the last decades due to non-ideal scaling and the connected physical constraints (see subsection 2.1.2). Therefore, it is said that "the power problem is the number one issue in the long term for computing" [Pap04]. However, the fact that Information and Communication Technologies (ICT) account for more than 10 % of the entire power dissipation in Germany [Bmw08] emphasizes its relevance not only for computing. In conclusion, power consumption is one of the most challenging issues because it affects diverse aspects for developers, vendors and customers:

- Economical: Direct costs arise for power consumption but also for cooling due to the heating of electronic products.

- Technical: Appropriate materials, devices and solutions are required to avoid performance loss or degraded reliability in the case of high currents and thermal issues.

- Functional: Weight or run-time of mobile devices and the noise of fans for cooling limit market opportunities.

- Ecological: Efficient and eco-friendly usage of natural resources is obligatory.

Figure 2-4 illustrates that the introduced aspects are intertwined. Moreover, such aspects are also linked to further system characteristics besides the absolute amount of power consumption -e.g. instantaneous power or energy. Such parameters are introduced in the following subsections together with a classification of low-power approaches and a selection of viable solutions.

#### 2.2.1 Constituents of power consumption

The instantaneous power P(t) that is drawn from the power supply is defined as the product of the supply current I(t) and the supply voltage  $V_{dd}$  (see equation 5). Hence, the average

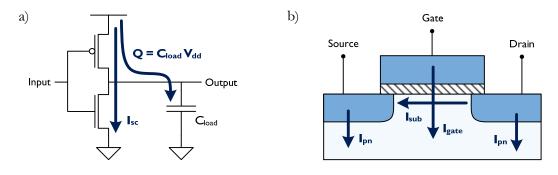

**Figure 2-5 :** Constituents of power consumption: a) Dynamic and short circuit power of an inverter b) Basic leakage mechanisms of a transistor (here nMOS)

dissipated power  $\overline{P}_{avg}$  over a given time interval  $[0, t_x]$  can be derived by integrating the instantaneous power (see equation 6). However, it is common practice to assume that the current is constant so that the instantaneous power equals the average power. Given this backdrop, the different constituents that add up to the **total power consumption**  $P_{tot}$  (see equation 7) are introduced in the following.

$$P(t) = I(t) \cdot V_{dd}$$

<sup>(5)</sup>

$$\overline{P}_{avg} = \frac{1}{t_x} \int_{0}^{t_x} I(t) \cdot V_{dd} dt$$

(6)

$$P_{\text{tot}} = P_{\text{dyn}} + P_{\text{sc}} + P_{\text{leak}} \left( + P_{\text{glitch}} + P_{\text{static}} \right)$$

(7)

The first constituent, the **dynamic power**  $P_{dyn}$ , comprises the power that is dissipated when digital data is processed. Figure 2-5 a) depicts such a common scenario of an inverter implemented in static CMOS logic [Wes05, Rab03]. The total charge of  $Q = C_{load}V_{dd}$  is transferred there through the pMOS from the supply rail to the load capacitance. In the second cycle, the same charge is transferred to ground, which means that no additional charge is taken from the supply rail. The frequency of such a complete event is expressed by the activity factor  $\alpha$  in relation to the clock frequency f of the circuit. Thereupon, equation 8 can be derived for the dynamic power consumption  $P_{dyn}$ :

$$P_{\rm dyn} = \alpha \cdot f \cdot C_{\rm load} \cdot V_{\rm dd}^{2} \qquad \text{with} \quad \alpha \in [0, 0.5]$$

(8)

In an ideal logic gate the output node is connected through transistors to either the supply rail or to ground. However, as the input signal has a finite slope both transistors are conducting for a short period of time  $t_{sc}$  when the logic gate is switching. The consequence is a short circuit current  $I_{sc}$  between the power rails that does not contribute to charging or discharging the load capacitance – see the illustration in figure 2-5 a). This second constituent is called **short circuit power**  $P_{sc}$  and can be computed with equation 9. Thereby the frequency of the occurrence of short circuits is twice as high as for  $P_{dyn}$  because a conducting path can emerge every time when the input signal changes. Furthermore, both the time  $t_{sc}$  and the short circuit current  $I_{sc}$  depend on the slopes of the input/output signals, the load capacitance and the size of the transistors.

$$P_{\rm sc} = 2\alpha \cdot f \cdot t_{\rm sc} \cdot I_{\rm sc} \cdot V_{\rm dd} \qquad \text{with} \quad \alpha \in [0, 0.5] \tag{9}$$

In contrast to both other constituents, leakage power  $P_{\text{leak}}$  is also dissipated when the circuit is in its idle state. Since a great number of miscellaneous technological causes contribute to the total amount of leakage power, no all-embracing equation exists to model these effects. However, the strongest impact originates from the subthreshold current  $I_{sub}$ , the gate oxide current  $I_{gate}$  and the junction current  $I_{pn}$ , which are illustrated in figure 2-5 b) and which are introduced below. The former is the current  $I_{sub}$  between drain and source of a transistor when the device should in fact be cutoff ( $V_{gs} < V_{th}$ ). The second contributor is the gate oxide current  $I_{gate}$  that evolves from charge carriers with sufficient kinetic energy to tunnel through the gate oxide. Here, the main physical cause is direct tunneling that results in a current from the gate to both the substrate and the diffusion areas. The third essential leakage current is the junction leakage  $I_{\rm on}$ , which bases on diffusion currents through the reverse-biased diodes that form on the interface between substrate and diffusion areas. Common approximations for the introduced currents are given in equation 10 to 12 whereas  $k_{p1}$ ,  $k_{p2}$ , ... are auxiliary parameters, and  $V_{pn}$  and  $I_{diode}$  denote the voltage and the reverse-biased saturation current across the diode [Nar05, Wes05]. Even though the causes for leakage currents are manifold, three of the most critical parameters should be pointed out, which partly result in an exponential increase of leakage currents. These are the threshold voltage  $V_{\text{th}}$ , the oxide thickness  $T_{\text{ox}}$  and the temperature T [Roy03, Rab03, Wes05].

$$I_{\rm sub} = \mu_0 \frac{\varepsilon_{\rm ox}}{T_{\rm ox}} \frac{W}{L} k_{\rm p1} T^2 \cdot e^{\frac{V_{\rm gs} - V_{\rm th}}{k_{\rm p2}T}} \cdot \left[ 1 - e^{\frac{-V_{\rm ds}}{k_{\rm p3}T}} \right]$$

(10)

$$I_{\text{gate}} = k_{\text{p4}} W L \cdot \left(\frac{V_{\text{gs}}}{T_{\text{ox}}}\right)^2 \cdot e^{\frac{-k_{\text{p5}}T_{\text{ox}}}{V_{\text{gs}}}}$$

(11)

$$I_{\rm pn} = I_{\rm diode} \cdot \left( e^{\frac{k_{\rm p6}V_{\rm pn}}{T}} - 1 \right)$$

(12)

Two further constituents add to the total power, as shown in equation 7. The power consumption due to glitches  $P_{\text{glitch}}$  depends on small-scale timing conditions of internal signals and can hardly be modeled or predicted beforehand. Thus, empirical data is applied as an estimate. Lastly, certain circuit techniques – such as ratioed logic in address decoders – explicitly implement a resistive path to the power rails that results in power dissipation due to static currents  $P_{\text{static}}$  [Vee00]. As these two constituents can hardly be affected in the design phase or their occurrence is rather rare, they are not further taken into account.

In order to preserve power, it is important to identify the most relevant constituents and the most critical parameters that are to be tackled in the design phase. The smallest impact originates

from short circuit power  $P_{\rm sc}$  whereas a fraction of clearly less than ten percent is generally reported for designs with appropriate slope ratios [Ped02, Wes05, Elr97]. However, this percentage will further diminish in the future because of steeper signal slopes and the correlations of supply and threshold voltages under the influence of scaling – consider that  $P_{\rm sc} = 0$  for  $V_{\rm dd} < 2 \cdot |V_{\rm th}|$ . Moreover, the dynamic power  $P_{\rm dyn}$  contributes with about 60 % to the total power dissipation although leakage power  $P_{\rm leak}$  has also been reported with up to half of the overall power [Yeo04, Sou09, Nar05]. Concluding, this distribution highly depends on the activity factor of the circuit as well as the application domain – for instance, compare high-performance computing and mobile devices. Yet in the future, leakage currents will further gain in importance as the ITRS also predicts an increase of leakage currents by a factor of ten per technology generation [Itr07b].

After all, the most critical parameters to cut down on power cannot always be changed in the design phase or are contradicting with performance optimizations. For example, when technology has been selected, process-relevant parameters are generally fixed – such as charge carrier mobility  $\mu_0$ , the gate oxide thickness  $T_{ox}$  or the gate length L. In addition, a slower clock frequency f, a scaled supply voltage  $V_{dd}$  or an increased threshold voltage  $V_{th}$  greatly result in low-power integrated circuits. However, these parameters also have significant impact on performance (see equation 4), so that power and performance characteristics have to be traded off carefully. In the end, little load capacitance  $G_{load}$  and low temperature T both yield in better system characteristics so that the management of temperature becomes highly beneficial during system operation (see also section 5.3).

The power consumption as introduced is a commonly used design metric. It needs to be used with care though as it is not related to the delay time  $t_d$  of a given operation, and thus can be brought down by computing more slowly. Therefore, the **energy per operation** is often expressed in terms of the **Power-Delay-Product** (PDP =  $P_{tot} \cdot t_d$ ), which offers a better comparison of different circuits as long as general requirements are similar. In addition, power is not only crucial in terms of the average amount (as  $\overline{P}_{avg}$  or rather  $P_{tot}$ ) or in relation to the timing (as PDP), but also with respect to the spatial occurrence. This kind of metric is called **power density**  $P_{\Box}$  and is defined as the power densities directly translate into heat, and thus exacerbate thermal impact on performance, reliability and power in itself (see equation 4, 10 and 12). Moreover, power dissipation also affects further system characteristics. Peak power, IR-drop, thermal stress and electromigration are just some of the related issues that result in design overhead to cope with them or in serious reliability concerns (see section 2.3). If expedient, such additional considerations are introduced and discussed in the appropriate sections below.

#### 2.2.2 Classification of low-power approaches

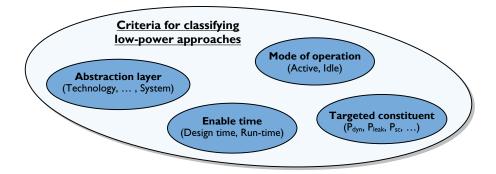

Herein, the digest of viable approaches to preserve power is aimed at complex integrated systems. To classify such approaches, figure 2-6 depicts different criteria that can be used. Thereby, the **abstraction layer** distinguishes mechanisms based on the level where the underlying implementation is performed – ranging from technology to system level. For example,

**Figure 2-6 :** Illustration of different criteria for the classification of viable low-power approaches in complex integrated systems

designers deal with the layout and the detailed physical effects on the technology level, whereas the interaction between complex functional modules (e.g. processors) is taken care of on the system level. Furthermore, the **mode of operation** relates to the state of the system when power savings are achieved. Accordingly, the circuit is said to be in the active mode of operation when digital data is processed. By contrast, no data is processed in the idle mode – albeit the clock network or registers might still be switching. Another criterion is the **enable time** whereas the differentiation is based on the time when the mechanism takes effect. Hence, design time approaches result in constant system parameters. On the other hand, run-time approaches dynamically influence power as well as performance parameters during the operation (e.g. by modifying the supply voltage). Lastly, as not all constituents of power dissipation can be reduced in equal measure, the **targeted constituent** (e.g.  $P_{dyn}$  or  $P_{leak}$ ) is a further criterion.

Because the total power consumption  $P_{tot}$  can be dominated by different constituents (e.g.  $P_{dyn}$  or  $P_{leak}$ ) depending on the specific application, it does not make sense to target at a certain constituent of power without appropriate specific knowledge given. Moreover, the criterion of the enable time might be misleading, as all approaches have at least to be implemented at design time. Therefore, a convenient classification was compiled for this thesis (see also table 2-2) that is based on the abstraction layer and the mode of operation. Besides, the stated power savings refer to the total power dissipation  $P_{tot}$  as defined in subsection 2.2.1. Finally, the last column in table 2-2 contains additional remarks that are to be considered when applying such approaches. Those diverse low-power proposals are briefly introduced in the following, starting with the technology level at the bottom of the table.

Attempts on the technology level mainly focus on short channel effects in nanotechnology, that is to say, balancing the need for large drive currents and minimized leakage currents [Liu93, Tau98, Roy03]. Both retrograde well and halo implants employ thereto substrate engineering to change the doping profile of the channel region. Thus, the distribution of the electric field and potential contours can purposefully be adapted [Won04, Nar05, Mud06, Roy03]. Another device modification is the use of offset spacers alongside the gate electrode, which can reduce gate leakage and parasitic overlap capacitance. However, transistor performance decreases due to higher resistance in the channel [Nar05].

|                                   | Abstraction layer | Mode of operation | Remark                                           |

|-----------------------------------|-------------------|-------------------|--------------------------------------------------|

| DVS                               | System            | Active / Idle     | Decelerated adaptation                           |

| DFS                               | System            | Active / Idle     |                                                  |

| Body biasing                      | System            | Active / Idle     | Low-level wiring                                 |

| Clock gating                      | System            | Idle              |                                                  |

| Parallelization                   | Architecture      | Active            | Area overhead                                    |

| Voltage islands                   | Architecture      | Active / Idle     | Voltage level conversion                         |

| Input vector control              | Module            | Idle              |                                                  |

| Power gating                      | Gate / System     | Idle              | Increased delay                                  |

| Dual $V_{\rm dd}$                 | Gate              | Active / Idle     | Voltage level conversion<br>and low-level wiring |

| Dual $V_{\rm th}/T_{\rm ox}$ CMOS | Transistor / Gate | Active / Idle     | $\geq$ 2 device types needed                     |

| Circuit techniques                | Transistor        | Active / Idle     | Need for tool support                            |

| Stack forcing                     | Transistor        | Active / Idle     |                                                  |

| Offset spacer                     | Technology        | Active / Idle     | Increased delay                                  |

| Halo implants                     | Technology        | Active / Idle     |                                                  |

| Retrograde well                   | Technology        | Active / Idle     |                                                  |

**Table 2-2 :** Compiled classification of convenient low-power approaches for the application in complex integrated systems

The following layer deals with transistors as abstract models based on differential equations. For instance, stack forcing exploits the fact that leakage currents are significantly smaller in a series connection of transistors [Nar05]. Corresponding series connections can be forced by splitting a single transistor into two devices in series whereas area and performance constraints limit the general application. Moreover, a wide range of varying circuit techniques facilitates power optimizations [Cor07]. Since static CMOS logic is by far the most widespread technique though, other logic styles have a lack of automated design tools to implement complex systems [Cor06c].

Further solutions take advantage of the heterogeneous significance of specific transistors, gates or modules on system characteristics. For example, Dual  $V_{th}$  and Dual  $T_{ox}$  CMOS identify non-critical paths of a circuit. Subsequently, transistors (or gates) in these paths are exchanged for slower components that feature less leakage currents [Sul04, Sun99, Wei99]. Thereby, circuit performance remains constant because those performance-relevant paths are kept untouched (see also subsection 3.4.2). Dual  $V_{dd}$  works similarly whereas here non-critical gates are identified and powered with different supply voltages. While the aforementioned two approaches require at least two device types for nMOS and pMOS at a time, Dual  $V_{dd}$  demands voltage level conversion between different domains and an additional supply network for the second supply voltage. Besides, power dissipation of logic gates can largely be circumvented in the idle mode of operation by disconnecting the power rails. This is called power gating and requires additional transistors in series to the logic gates themselves [Ani03]. Therefore, the reduced voltage drop across the logic gate results in derogated performance (see equation 4) as well as in an additional delay to power up the virtual supply rails after an idle mode. That is why the identification of active and idle modes on system level is highly important for the power gating.

Another proposal, the input vector control, provides the inputs of the modules with specific signal patterns during the idle mode [Yua05, Tsa04]. This yields reduced power consumption because the extent of leakage currents bases on the state and the composition of transistors. In addition, different modules in a given architecture can be supplied with miscellaneous supply voltages. Hence, an architecture of such voltage islands can be adapted to the application constraints by powering non-critical modules once again with lower supply voltages. Although power is preserved in the active and in the idle mode of operation, voltage level conversion needs to be performed when crossing module borders. A further approach on the architecture level is to parallelize modules and therewith functionality. The halved clock frequency f of the modules, which is needed to process the same amount of data in parallel, is then exploited to decrease the power consumption during the active mode -e.g. by applying reduced supply voltage  $V_{dd}$  (see also equation 8). However, the power savings are accomplished at the price of an area overhead.

Lastly, the system level offers several alternatives for power management, which have in common that they rely somehow on a global and temporal system perspective. This policy facilitates to adapt system characteristics to current application needs. On the one hand, power can be scaled by turning off the clock signal of idle modules. Thereby, such clock gating prevents the unnecessary power loss in the clock network and due to registers. On the other hand, transistor characteristics can be adjusted by changing the potential of the substrate potential – called body biasing [Tsc02]. Therewith, the subthreshold voltage  $V_{th}$  is modified, which in turn significantly affects leakage currents and transistor performance. However, to provide an adjustable substrate potential wastes costly die area. Furthermore, both the clock frequency and the supply voltage can dynamically be customized for low-power operation, whereas Dynamic Frequency Scaling (DFS) and Dynamic Voltage Scaling (DVS) are common practice in commercial products – consider such techniques as Intel SpeedStep, AMD Cool 'n' Quiet or VIA PowerSaver [Int04]. Even though the adaptation of DVS is decelerated due to the time constant of the large power network, it allows a quadratic cutback of dynamic power (see equation 8).

More low-power approaches have been published in the past. However, techniques that are industry standard and that have long been integrated in common design tools are already applied for the implementations of this work, but are not enumerated here – as for example transistor sizing, state encoding or retiming [Sch06, Syn09]. Moreover, mechanisms of power reduction in such vast areas as for example analog or memory design are not in line with the objectives of this thesis and would go beyond the scope of the created classification here. The interested reader is referred to corresponding literature [Nar05, Ped02, Vee00].

#### 2.2.3 Interim conclusion for viable low-power solutions

Of primary importance for the evaluation of expedient low-power approaches is the quantity of power that can be preserved. However, the impairment of other design parameters has to be kept at a minimum. In particular, performance is highly critical, as it does not increase as fast as power dissipation across greater system complexities and smaller technologies – see also Pollack's law [Bor07]. According to that, the Power-Delay-Product (PDP) is a first measure for power efficiency in accordance to performance requirements as long as design and area costs are still kept in mind.

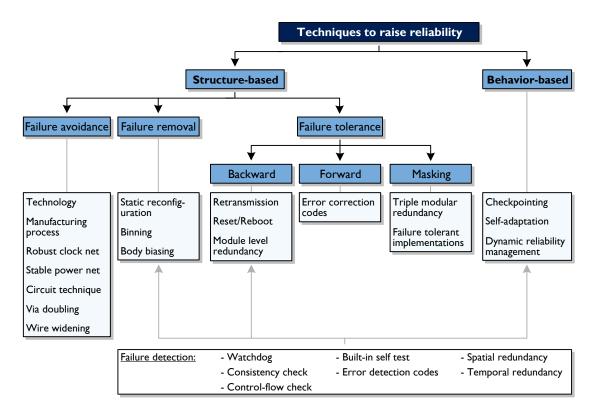

Against this background and the utilization in complex integrated systems, architecture and system level approaches appear highly promising for an implementation (see table 2-2). In doing so, the architectures of complex systems with a large number of modules can effectively be exploited due to the implicit concurrency of computation and communication modules. Beyond that, the different system level approaches can be combined within a global power management to dynamically adapt system characteristics to current requirements. For instance, idle modules can be fully shut down or at least be decelerated when they are not needed for system operation or a specific application, respectively. While DVS and power gating offer the largest savings due to the dependencies on supply voltage, they come at the price of increased delay after an idle phase. By contrast, DFS and clock gating provide less savings but are fairly simple to implement without affecting other system characteristics. The subjacent abstraction layers provide the possibility for further savings whereby their applicability is independent of system size. Here, those approaches modifying non-critical paths are particularly interesting, as they do not affect system performance at all. Among these approaches, Dual  $V_{\rm th}$  and Dual  $T_{\rm ox}$  CMOS are the preferential choices because they do not necessitate voltage conversion and two device types are de facto standard in current technologies. Finally, transistor and technology level solutions can also offer great improvements. However, circuit designers rely in general on a given technology and a specific library of logic gates. Hence, these solutions are not applicable for the most part.

Concluding, since the dominating constituents of power consumption and further design constraints greatly vary across specific applications and domains, there is no exclusive solution to preserve power in complex integrated systems. However, high-level approaches seem most beneficial as they can consider and exploit the changing requirements. In fact, the miscellaneous causes demand a combined approach of various solutions [Itr07b]. That is the only way to simultaneously exploit the many degrees of freedom across different abstraction layers and, likewise, to target at the diverse constituents of power consumption both during the active and the idle mode of operation.

## 2.3 Reliability and robustness

Besides requirements for performance and power dissipation, integrated circuits are expected to be robust against temporary disturbances as well as to operate reliably over their entire operational lifetime. As an example of robustness, a user demands from his mobile device to maintain its familiar properties across a wide range of varying ambient temperatures. Beyond that, the device is supposed to work fully reliably in the long term in order to keep malfunctions and downtimes as rare as possible. Admittedly, to satisfy these requirements is becoming an increasingly serious concern as nanotechnology continues to scale down. For a start, individual tiny transistors comprehend structures of just a few atomic layers and materials with just a sparse number of dopant atoms. Hence, these devices are highly susceptible to material imperfections, particles and deviant physical dimensions as a result of the manufacturing process. Moreover, as the number of transistors on a single die increases, it becomes more likely that some of the billion devices depart considerably from their expected behavior or fail completely. Lastly, circuit behavior is also put at risk during operation in consequence of intermittent intrinsic and extrinsic disturbances – such as capacitive or inductive coupling. This is because noise margins decrease similarly to the related voltage levels of integrated circuits.

Therefore, reliability and robustness issues need to be considered during design and manufacturing of integrated circuits. Such issues are even of increasing crucial concern as smaller technologies further aggravate the impact on engineering and manufacturing costs, product quality as well as time to market. To be able to access these concerns in detail, the following subsection introduces at first the common terminology and analytical definitions. Subsequently, both failure causes and techniques to raise reliability are introduced and classified before an interim conclusion summarizes the findings.

#### 2.3.1 Terminology and analytical definition

The literature on reliability engineering often applies distinctive terms to differentiate between the cause of an abnormal condition and the manifestation in a higher abstraction layer. However, the suggested terms are not consistent and the distinction of causes and their manifestation is ambiguous, because this depends on the considered abstraction layer and the logical state (compare [Kor07], [Joh89], [FedXX], [DinXX] and [IsoXX]). Therefore, in this work the notion of a **failure** is used in the widest sense and in compliance with ISO/CD 10303-226 [IsoXX]. That is, a failure denotes the component's lack of ability to operate its intended function as designed.

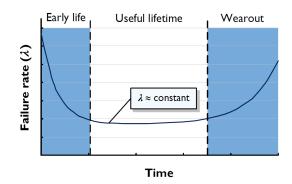

Based on this definition, the underlying parameter for reliability analysis is the **failure rate**  $\lambda$  that states how many components fail on average in a determined time interval. For clarification, assume that 16 out of 100 components fail in a given year, hence, that year's failure rate is 0.16 and an individual component fails with a probability of 16 % in that same year, respectively. Strictly speaking, the failure rate represents a conditional probability since it needs to be known how many components survived until the specific time interval of investigation. In addition, the failure rate  $\lambda$  is not only a function of time but also of the chosen technology and external operating parameters – that is  $\lambda = \lambda(t, \varepsilon_{ox}, \mu_0, T_{ox}, T, V_{dd}, ...)$ . Although an analytical definition can hardly be given due to the complex correlations, the course of the failure rate over time can in general empirically be found and is perceived as the bathtub curve [Joh89, Kor07]. Such an example of the failure rate over time is depicted in figure 2-7 with the three main phases of the overall lifetime highlighted. The first one thereof is called **early life** phase, often also referred to as infant mortality phase. This phase ideally ends when the components are shipped to the

**Figure 2-7 :** The dependency of the failure rate on system lifetime is usually perceived as the bathtub curve that splits into three phases – whereas the failure rate is mostly considered constant during the useful lifetime

customer and is characterized by a high but decreasing failure rate. The reasons are attributable to manufacturing imperfections and borderline components, which tend to fail early during operational demands. The period of the early life phase is commonly compressed by various techniques of accelerated testing [Cro01], whereas the proportion of functional components after testing is termed yield. Subsequently, the components enter the phase of the **useful lifetime**. Here, individual random failures are the dominating cause for system outages. According to that, the failure rate is rather low and can mostly be supposed as being constant. A rising failure rate, due to aging and wearing, marks the end of this phase. Lastly, within the adjacent **wearout** phase, components suffer from the increased number of failures as they reach the end of their lifetime.

Moreover, the IEEE defines the term reliability as the "ability of a device or system to perform a required function under stated conditions for a specified period of time" [Iee94]. This implies that a component is named unreliable both as it produces a logical failure and as it does not conform to the stated conditions – for instance, an operation takes too long. Hence, the analytical definition of **reliability** R(t) is to be understood as the probability of a component to operate as desired until time t [Joh89]. For example,  $R(t_x) = 0.72$  states that there is a 72 % chance that the component is still running at time  $t_x$ . To express the entire course of reliability R(t) across the three lifetime phases, the Weibull distribution is often used because it can simply be adapted by the parameter  $\beta$  [Kor07]. Thus, equation 13 represents the reliability R(t) for all three lifetime phases based on different parameters for  $\beta$ :

$$R(t) = e^{-\lambda \cdot t^{\beta}} \qquad \text{with} \begin{cases} \beta < 1 & \text{for early life} \\ \beta = 1 & \text{for useful lifetime} \\ \beta > 1 & \text{for wearout} \end{cases}$$

(13)

Closely connected to the rather probabilistic definition of reliability is the **Mean Time To Failure** (MTTF), which is the average time a component operates until it fails. Therefore, the MTTF is equal to the expected lifetime of a component in case that the affected component cannot be recovered. This metric can be derived from integrating the reliability over time (see equation 13). Thereby, most calculations assume a constant failure rate, which corresponds to  $\beta = 1$  for the Weibull distribution and an exponential function for the reliability R(t). Accordingly, the MTTF is then given by the reciprocal of the failure rate [Kor07]:

MT\*TF =

$$\int_{0}^{\infty} \mathbf{R}(t) dt = \int_{0}^{\infty} e^{-\lambda \cdot t} dt = \frac{1}{\lambda}$$

for  $\beta = 1$  (14)

Even though the assumption of a constant failure rate is common practice and adequate for most investigations, it should be stressed that other intricate considerations need to be applied for the early life and the wearout phase.

The inaugurated metrics so far reference to outages in the long term. In contrast, **robustness** is the capability to withstand temporary disturbances, which can originate from the operating environment as well as intrinsic and extrinsic noise sources. In the context of integrated circuits, varying ambient temperatures and mechanical stress are examples of environmental disturbances. Moreover, noise stands for unwanted voltage and current variations of any kind inside the integrated circuit – for instance in consequence of inconstant power supplies, capacitive coupling or electromagnetic radiation. After all, the number of disturbance sources that is considered important as well as the extent of each individual disturbance greatly varies across the miscellaneous application domains (e.g. medical, consumer or aerospace). Thus, an acknowledged quantitative measure of robustness does not exist. Instead, most investigations simply state whether an evaluated device does fulfill the application-specific robustness requirements or not.

#### 2.3.2 Categorization of failure causes

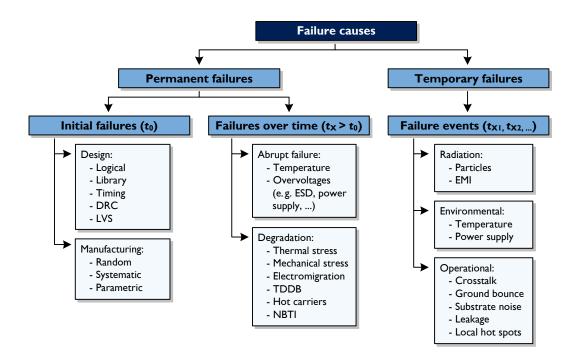

Failure causes can be classified according to their chronological appearance and according to their severity for system operation. The latter scheme distinguishes between benign and malicious failures whereas a benign failure does not trigger additional failures at other components. By contrast, malicious failures also derogate other components by producing for instance reasonable looking but incorrect results. However, if an individual failure becomes malicious for system operation often depends on changing conditions of the appropriate applications and is thus ambiguous. Therefore, a convenient categorization of failures was compiled for this thesis that is based on the notion of time (see figure 2-8).

The primal level in figure 2-8 splits failure causes depending on their duration of occurrence. According to that, systems can at best adapt to permanent failures whereas temporary failures make it possible to recover the entire system state without any lasting damage. Moreover, the date of origin allows a further arrangement in the next level. First, **initial failures** do already exist at the time that the component is to enter its useful lifetime – marked as time  $t_0$ . Thus, such failures arise from circuit design or the manufacturing process. The listed design examples comprehend failures during the logical implementation and synthesis, in the underlying transistor and gate

**Figure 2-8 :** Categorization of different failure causes with respect to their temporal duration (first level) and their date of origin (second level)

libraries as well as during the timing analysis. In addition, design steps that are commonly fully automated by design tools can be the cause for failures too – such as Design Rule Check (DRC) or Layout Versus Schematic (LVS). Concerning the manufacturing, three types of failures can be identified. On the one hand, random failures occur for instance due to undesirable particles on the wafer. On the other hand, systematic failures are the repeatable result of mask patterns, process steps or applied chemical substances. Lastly, manufacturing related parameter variations can cause parametric failures, which describe the fact that integrated circuits work logically correct but do not conform to given design constraints (e.g. on performance or power dissipation) [Shi03, Bor05].

Another group of causes is the permanent **failures over time**. These can be brought forth at any point in time  $t_x > t_0$  due to abrupt incidences or due to steady degradation based on wearing and aging. The abrupt occurrence is mostly the result of mishandling – by way of example, exceeding temperatures and voltages, such as Electro-Static Discharge (ESD) [Wes05]. Unlike these fast effects that take place in less than a second, degradation rather happens in the range of years. The most familiar causes are thermal and mechanical stress whereas other effects require a deeper analysis of physical and chemical coherencies. Electromigration for one is the unwanted material transport in conductors because of the gradual movement of ions, which finally leads to open circuits (voids) and shorts (hillocks) [Hu95, Wu02]. Further causes relate to the impairment of transistor characteristics as a result of derogations in the gate oxide. For instance, tunneling currents from the gate inflict irreversible damage on the gate oxide – called Time-Dependent Dielectric Breakdown (TDDB) [Moa90]. Similar damage of the dielectric is also brought on by high-energy charge carriers (termed hot carriers) that tunnel from the transistor channel into the gate oxide [Hu92]. Lastly, Negative-Bias Temperature Instability (NBTI) designates unintentional charge traps at the interface between gate oxide and channel in pMOS devices due to dangling bonds [Sch03, Pau05]. Even though the root causes are different, the three last named failure effects all result in a critical drift of the threshold voltage over time.

A simple model that is often applied in the first instance to illustrate the coherencies of the diverse permanent failures over time –in particular due to degradation– is the Arrhenius model [Jed02, Cro01, Wan08]:

MTTF

$$\propto k_{\rm fm} \cdot e^{\frac{E_{\rm a}}{k_{\rm Boltz} \cdot T}}$$

(15)

Here,  $k_{\rm fm}$  is an empirical constant,  $k_{\rm Boltz}$  stands for Boltzmann's constant (8.62·E-5 eV/K), *T* denotes the absolute temperature and  $E_a$  is the activation energy of the failure mechanism. Hence, it can be concluded from equation 15 that wearout and aging failures increase exponentially with temperature and system reliability decreases, respectively [Hua04, Sri03, Sri04]. Thus, temperature represents a main challenge in current and future nanotechnology [Itr07a].

Last but not least, failure events come about at different times  $(t_{x1}, t_{x2}, ...)$  during operation and last just temporary. Hence, such events only involve a change of data, and no harm of the physical circuit itself. Those effects of radiation are generally also referred to as soft-errors - for instance, in consequence of particle strikes (like  $\alpha$ -particles or neutrons) and Electro-Magnetic Interference (EMI). Such mechanisms induce charge variations on internal nodes and thus possible failures [Mit05, Haz03, Muk05]. Furthermore, environmental impacts can originate from the ambient temperature and the power supply [Teh10]. Indeed, it should be emphasized that if deviations of these impacts exceed a critical threshold, they could also lead to permanent failures as aforementioned. Finally, the intrinsic operation itself can be the trigger for a great number of diverse failure causes and consequences. These influences range from signal transmission, power supply network and substrate potentials to state preservation on critical nodes and parametric discrepancies – appropriate examples are stated in figure 2-8. Most of these different failure events are reproducible as they rely on certain logical states or transitions. In the end, figure 2-8 can only list an extract of all operational issues due to their large number. The interested reader is referred to appropriate literature for a comprehensive and detailed presentation [Hey03, Hei02, Sri98, Wes05, Rab03, Cat67].

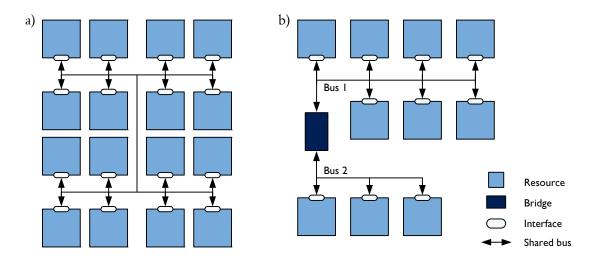

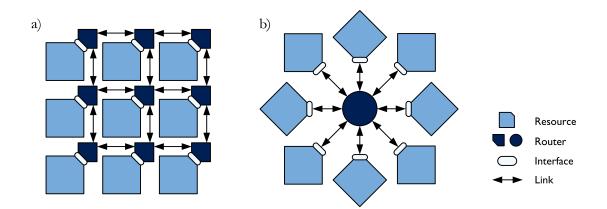

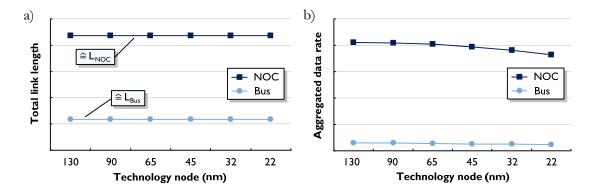

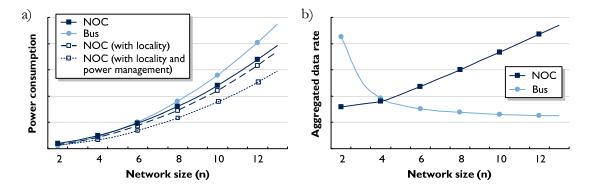

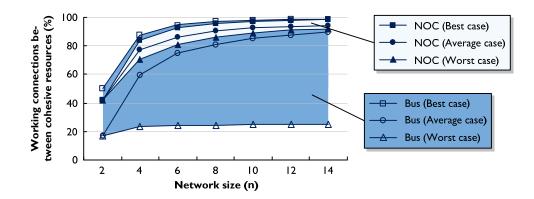

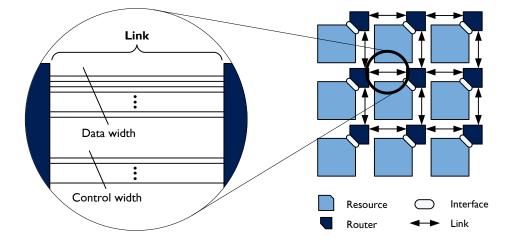

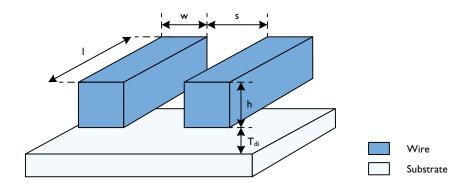

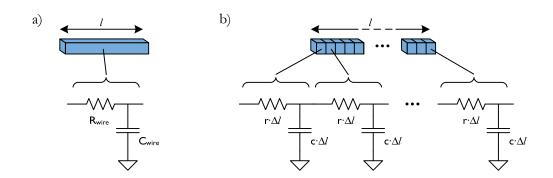

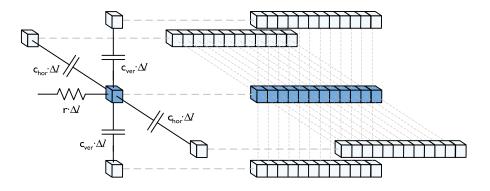

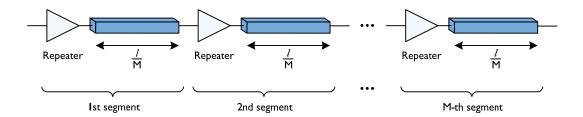

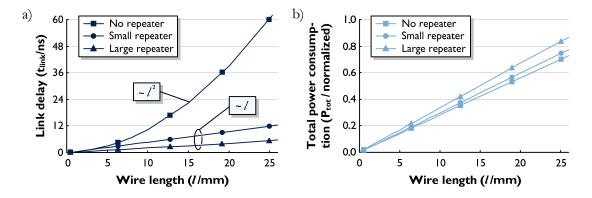

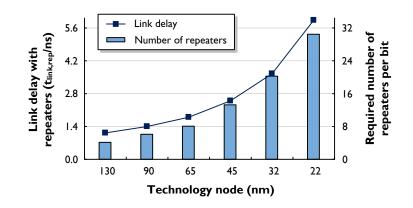

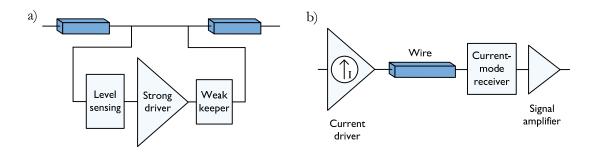

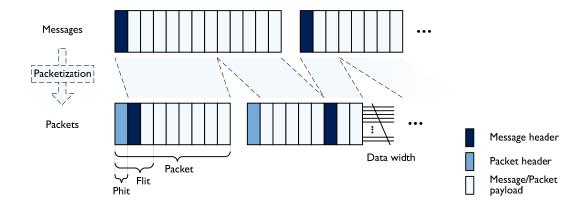

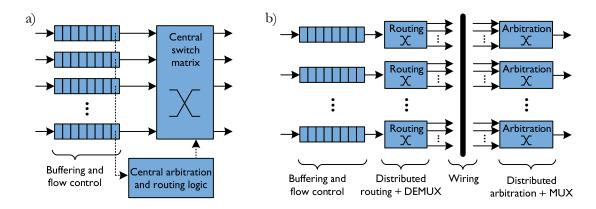

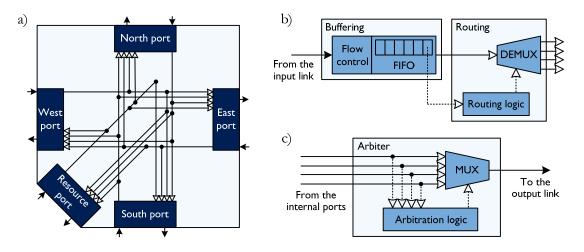

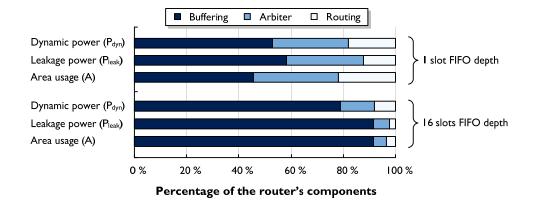

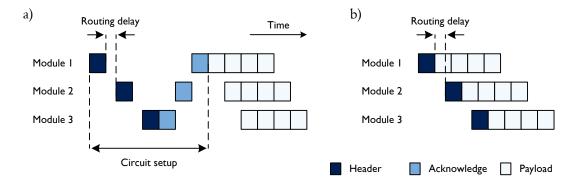

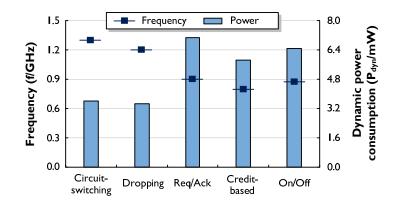

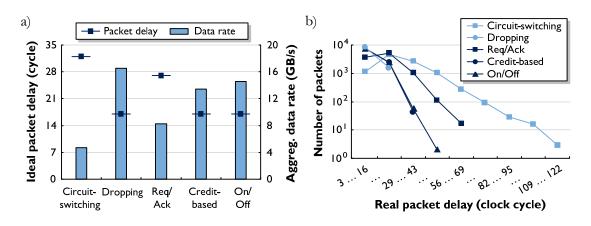

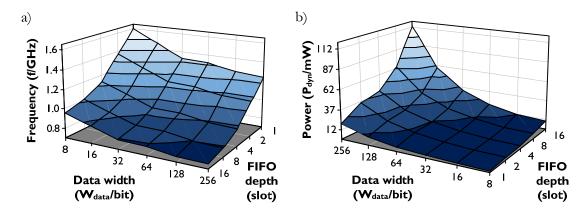

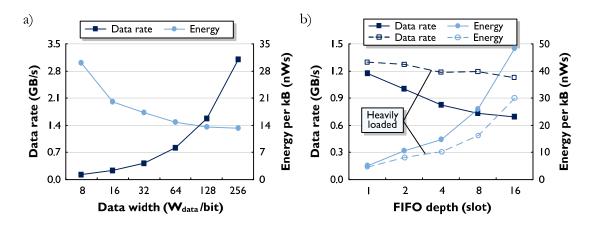

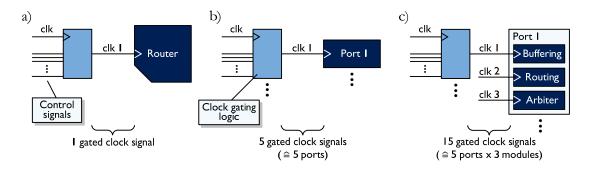

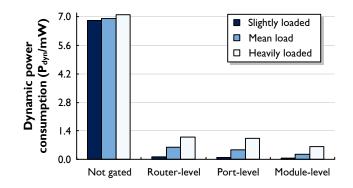

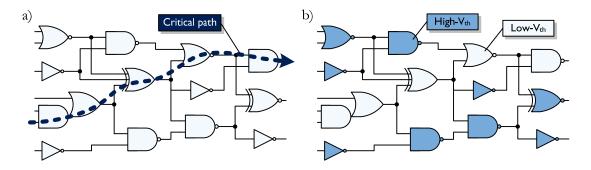

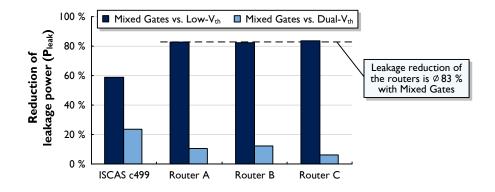

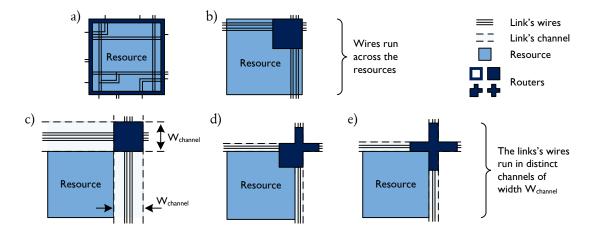

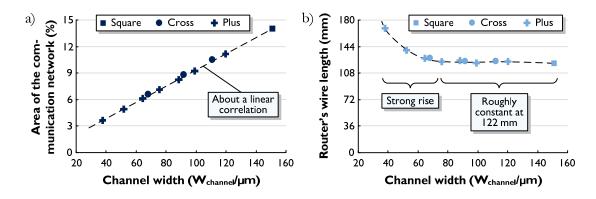

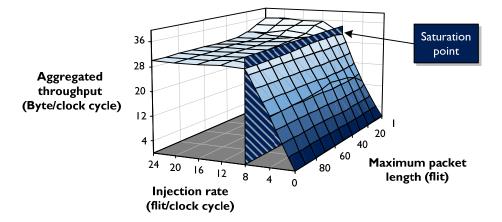

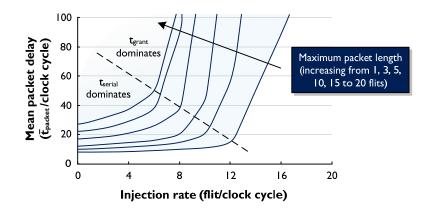

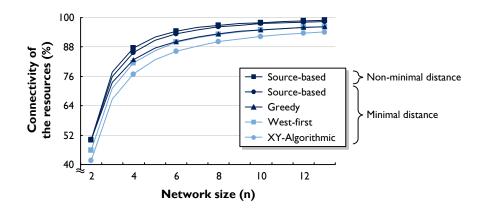

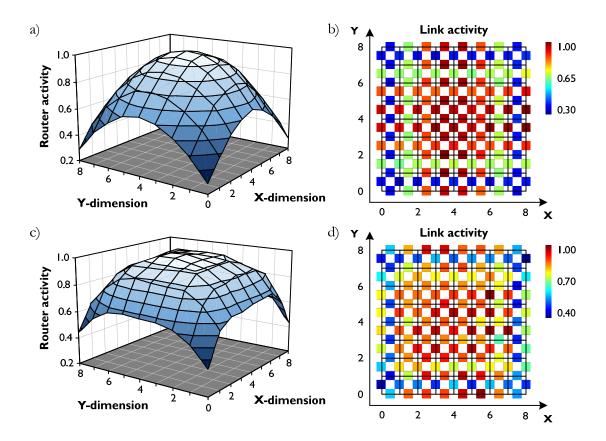

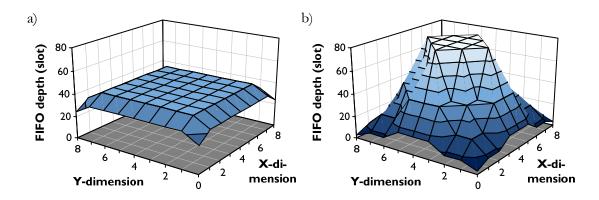

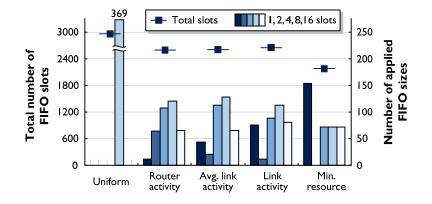

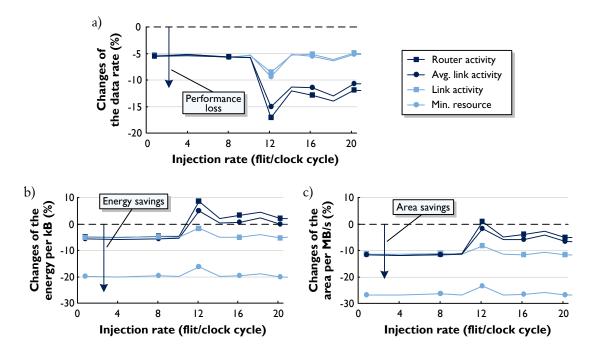

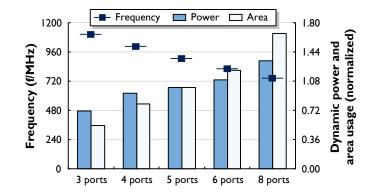

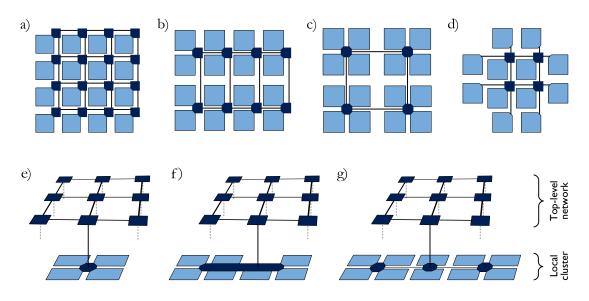

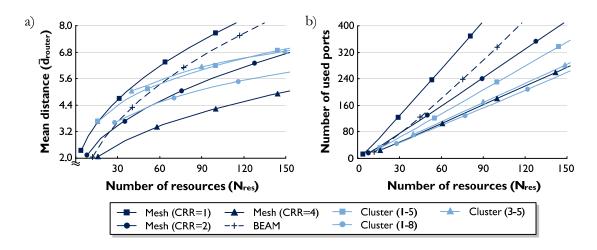

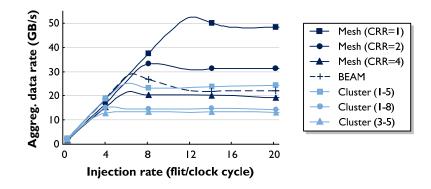

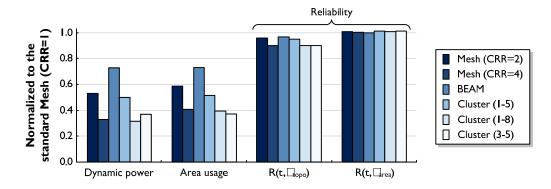

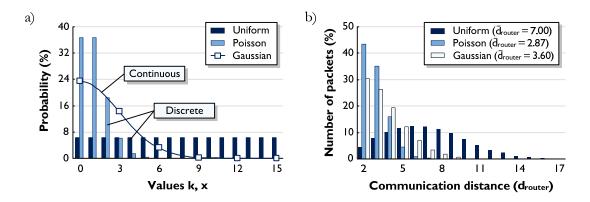

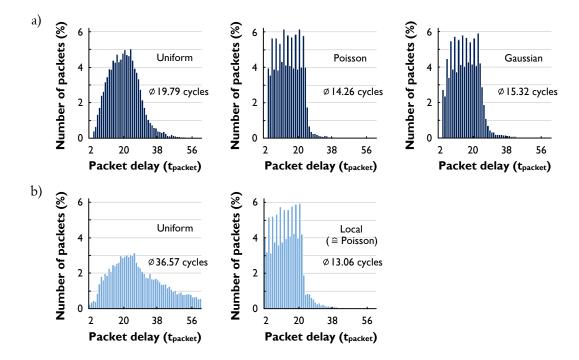

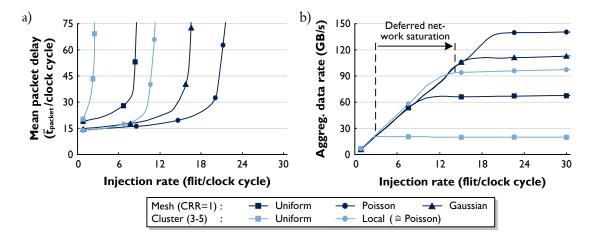

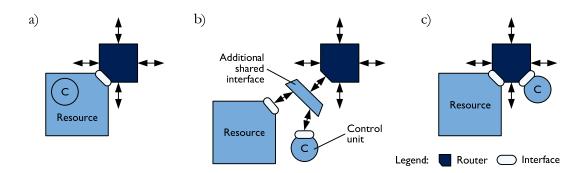

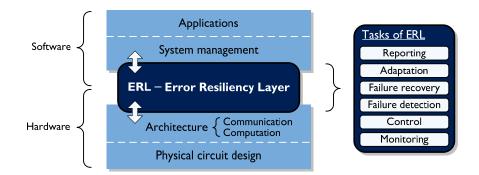

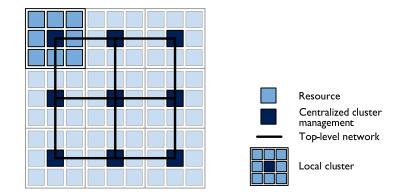

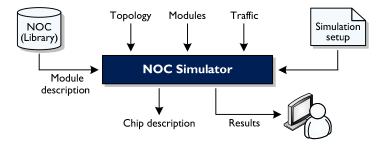

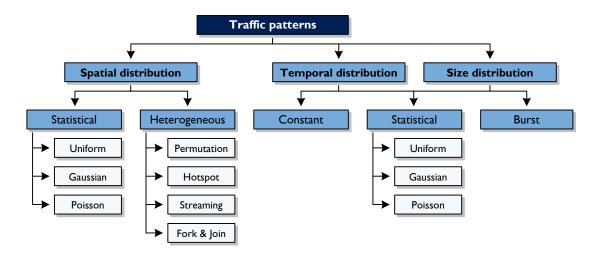

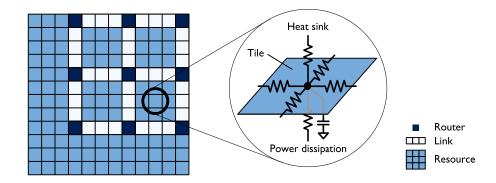

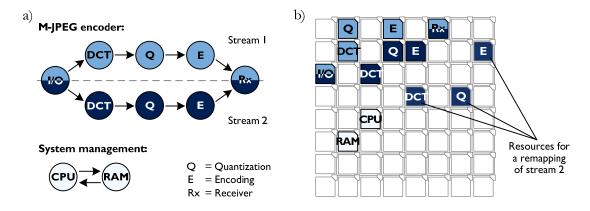

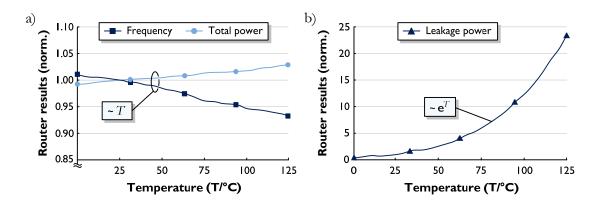

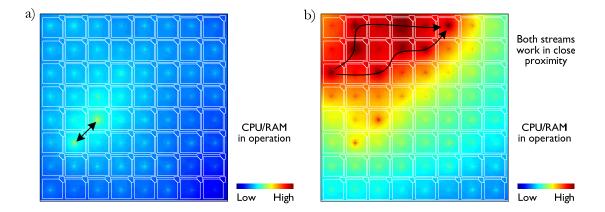

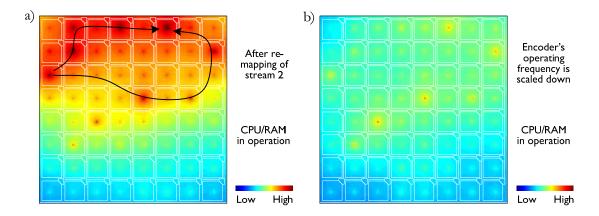

There is no common consensus on what particular failure cause is deemed to be the most critical, as this depends on the application domain and often also on a personal perspective. However, intensified research efforts can be identified in three different fields. Firstly, parameter variations have traditionally rather been considered an issue of manufacturing. As variations of device characteristics – and thus also of system characteristics – have drastically increased though, such parameter variations have to be accounted for during the design stages and system operation as well. Secondly, with the rising appearance of soft-error related outages not long since, models, test equipment and countermeasures have increasingly been published [Shi02, Mit05]. Finally,