THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

# Parallel and Distributed Processing in the Context of Fog Computing High Throughput Pattern Matching and Distributed Monitoring

CHARALAMPOS STYLIANOPOULOS

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2019

#### Parallel and Distributed Processing in the Context of Fog Computing

High Throughput Pattern Matching and Distributed Monitoring Charalampos Stylianopoulos

Copyright © Charalampos Stylianopoulos, 2019.

Technical report 179L ISSN 1652-876X Department of Computer Science and Engineering

Chalmers University of Technology SE-412 96 GÖTEBORG, Sweden Phone: +46 (0)31-772 10 00

Author e-mail: chasty@chalmers.se

Printed by Chalmers Reproservice Göteborg, Sweden 2019

#### Parallel and Distributed Processing in the Context of Fog Computing High Throughput Pattern Matching and Distributed Monitoring

Charalampos Stylianopoulos

Department of Computer Science and Engineering, Chalmers University of Technology

#### ABSTRACT

With the introduction of the Internet of Things (IoT), physical objects now have cyber counterparts that create and communicate data. Extracting valuable information from that data requires timely and accurate processing, which calls for more efficient, distributed approaches. In order to address this challenge, the fog computing approach has been suggested as an extension to cloud processing. Fog builds on the opportunity to distribute computation to a wider range of possible platforms: data processing can happen at high-end servers in the cloud, at intermediate nodes where the data is aggregated, as well as at the resource-constrained devices that produce the data in the first place.

In this work, we focus on efficient utilization of the diverse hardware resources found in the fog and identify and address challenges in computation and communication. To this end, we target two applications that are representative examples of the processing involved across a wide spectrum of computing platforms. First, we address the need for high throughput processing of the increasing network traffic produced by IoT networks. Specifically, we target the processing involved in security applications and develop a new, data parallel algorithm for pattern matching at high rates. We target the vectorization capabilities found in modern, high-end architectures and show how cache locality and data parallelism can achieve up to *three* times higher processing throughput than the state of the art. Second, we focus on the processing involved close to the sources of data. We target the problem of continuously monitoring sensor streams —a basic building block for many IoT applications. We show how distributed and communication-efficient monitoring algorithms can fit in real IoT devices and give insights of their behavior in conjunction with the underlying network stack.

**Keywords:** fog computing, resource-constrained devices, high throughput, pattern matching, vectorization, distributed processing, distributed monitoring ii

## Preface

Parts of the contributions presented in this thesis have led to the following manuscripts.

Charalampos Stylianopoulos, Magnus Almgren, Olaf Landsiedel, Marina Papatriantafilou,

"Multiple Pattern Matching for Network Security Applications: Acceleration through Vectorization", appeared in the 46th International Conference on Parallel Processing (ICPP), Bristol, United Kingdom, 14-17 August, 2017

Charalampos Stylianopoulos, Magnus Almgren, Olaf Landsiedel, Marina Papatriantafilou,

"Geometric Monitoring in Action: a Systems Perspective for the Internet of Things",

under submission, 2018

#### PREFACE

## Acknowledgments

First, I would like to express my gratitude to my supervisors Magnus Almgren, Olaf Landsiedel and Marina Papatriantafilou. I feel privileged to have the continuous support and guidance of three excellent mentors. Without them, this thesis would not be possible.

I am also grateful to my past and current colleagues in the Division of Networks and Systems, for making these first years of my PhD studies a fun and rewarding experience. Many thanks to Adones, Ali, Aljoscha, Amir, Aras, Bapi, Bastian, Bei, Beshr, Boel, Carlo, Christos, Dimitris, Elad, Elena, Fazeleh, Georgia, Hannah, Yiannis N., Iosif, Ivan, Joris, Karl, Katerina, Nasser, Oliver, Paul, Philippas, Romaric, Thomas R., Thomas P., Tomas, Valentin T., Valentin P., Vincenzo, Vladimir and Wissam. Also, thanks to my collaborators Oskar, Linus and Simon.

Special thanks go to my friends in Göteborg that made it a lovely place to live in. Thank you Petros, Vaggelis, Stavros, Yiannis S., Angelos, Chloe, Maria, Vasiliki, Manos and Suvi for enduring my endless talking. Also, many thanks to old friends, especially Nikos, Kostas, Efi, Elias and Dinos, for all the great times we had and will keep having.

My thanks go to my family, my parents and my siblings for their unconditional love and trust in me. I owe it all to them. Finally, I want to thank Kelly for being there for me and for all the moments we share together.

> Charalampos Stylianopoulos Göteborg, June 2019

#### ACKNOWLEDGMENTS

# Contents

| Abstract |            |         |                                                            | i  |  |

|----------|------------|---------|------------------------------------------------------------|----|--|

| Pr       | Preface ii |         |                                                            |    |  |

| Ao       | cknow      | vledgme | ents                                                       | v  |  |

| I        | IN         | ГROD    | UCTION                                                     | 1  |  |

| 1        | Intr       | oductio | n                                                          | 3  |  |

|          | 1.1        | Challe  | nges in processing IoT data: the need for scalability on a |    |  |

|          |            | range   | of new architectures                                       | 4  |  |

|          | 1.2        | Backg   | round                                                      | 5  |  |

|          |            | 1.2.1   | Advances in processing hardware                            | 5  |  |

|          |            | 1.2.2   | Wireless sensors networks                                  | 6  |  |

|          | 1.3        | Scope   | of the thesis                                              | 7  |  |

|          | 1.4        | Repres  | sentative problems in the context of fog computing         | 8  |  |

|          |            | 1.4.1   | Data processing in the context of cyber-security           | 8  |  |

|          |            | 1.4.2   | Distributed monitoring of sensor readings                  | 11 |  |

|          | 1.5        | Resear  | rch questions and contributions                            | 12 |  |

|          |            | 1.5.1   | Research questions                                         | 13 |  |

|          |            | 1.5.2   | (Paper I) Multiple Pattern Matching for Network Secu-      |    |  |

|          |            |         | rity Applications: Acceleration through Vectorization      | 13 |  |

|      | 1.5.3   | (Paper II) Geometric Monitoring in Action: a Systems |   |

|------|---------|------------------------------------------------------|---|

|      |         | Perspective for the Internet of Things               | 4 |

| 1.6  | Conclu  | sions and Future Directions                          | 6 |

| Bibl | iograph | y 1                                                  | 7 |

#### **II PAPERS**

#### 23

| 2 | PAP  | ER I    |                                                   | 27         |

|---|------|---------|---------------------------------------------------|------------|

|   | 2.1  | Introdu | uction                                            | 28         |

|   | 2.2  | Backg   | round                                             | 31         |

|   |      | 2.2.1   | Traditional Approach to Multiple-Pattern Matching | 31         |

|   |      | 2.2.2   | Filtering Approaches and Cache Locality           | 31         |

|   |      | 2.2.3   | Vectorization                                     | 32         |

|   | 2.3  | System  | n Model                                           | 33         |

|   | 2.4  | Algori  | thmic Design                                      | 34         |

|   |      | 2.4.1   | S-PATCH: a vectorizable version of DFC            | 34         |

|   |      | 2.4.2   | V-PATCH: Vectorized algorithmic design            | 38         |

|   | 2.5  | Evalua  | tion                                              | 42         |

|   |      | 2.5.1   | Experimental setup                                | 42         |

|   |      | 2.5.2   | Overall Throughput                                | 44         |

|   |      | 2.5.3   | The effects of the number of patterns             | 46         |

|   |      | 2.5.4   | Filtering Parallelism                             | 48         |

|   |      | 2.5.5   | Changing the vector length: Results from Xeon-Phi | 48         |

|   | 2.6  | Relate  | d Work                                            | 50         |

|   |      | 2.6.1   | Pattern matching algorithms                       | 50         |

|   |      | 2.6.2   | SIMD approaches to pattern matching               | 51         |

|   |      | 2.6.3   | Other architectures                               | 52         |

|   | 2.7  | Conclu  | ision                                             | 52         |

|   | Bibl | iograph | y                                                 | 53         |

| 3 | рдр  | ER II   |                                                   | 59         |

| 5 | 3.1  |         | action                                            | <i>6</i> 0 |

|   | 5.1  | muou    |                                                   | 00         |

| 3.2          | Backg                                                       | round                                                  | 63 |  |

|--------------|-------------------------------------------------------------|--------------------------------------------------------|----|--|

|              | 3.2.1                                                       | The Geometric Monitoring Method (GM)                   | 63 |  |

|              | 3.2.2                                                       | In the context of wireless sensor networks             | 65 |  |

| 3.3          | Practical GM-based threshold-monitoring: design aspects and |                                                        |    |  |

|              | algorit                                                     | hmic implementation                                    | 66 |  |

|              | 3.3.1                                                       | Addressing system challenges: processing, communi-     |    |  |

|              |                                                             | cation                                                 | 66 |  |

|              | 3.3.2                                                       | Tunable system-parameters                              | 69 |  |

| 3.4          | Experi                                                      | mental methodology                                     | 69 |  |

| 3.5          | Evalua                                                      | tion from a holistic system perspective                | 72 |  |

|              | 3.5.1                                                       | Full-system simulations                                | 72 |  |

|              | 3.5.2                                                       | Validation through Testbed Experiments                 | 75 |  |

|              | 3.5.3                                                       | Runtime insights: a closer look                        | 76 |  |

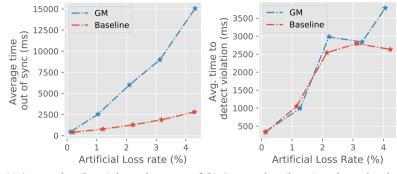

|              | 3.5.4                                                       | Accuracy/Responsiveness: The effect of packet losses . | 79 |  |

| 3.6          | Related                                                     | d Work                                                 | 82 |  |

| 3.7          | Conclu                                                      | sions and Future Work                                  | 83 |  |

| Bibliography |                                                             |                                                        |    |  |

#### CONTENTS

# List of Figures

| 1.1 | An example fog computing architecture that includes a cloud<br>layer with high-end servers, an intermediate layer close to the<br>gateways and the IoT layer with resource-constrained devices.<br>The work in this thesis targets representative problems on Area<br>A (centralized, high throughput processing) and Area B (dis-<br>tributed processing and communication) 9 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Filter Design of S-PATCH. HT stands for the <i>Hash Tables</i> that contain the full patterns                                                                                                                                                                                                                                                                                  |

| 2.2 | Input Transformation from consecutive characters to sliding windows of two characters                                                                                                                                                                                                                                                                                          |

| 2.3 | Figure describing the filter merging optimization. In the upper half, lookups on two filters require two gather invocations.<br>Once the filters are merged in memory in the lower half, one gather brings information from both filters to the registers 41                                                                                                                   |

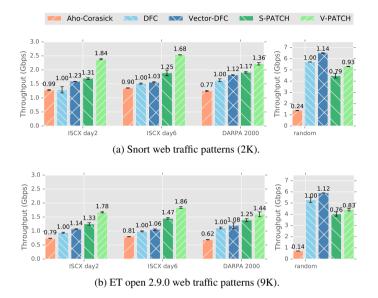

| 2.4 | Performance comparison between the different algorithms for<br>public and random data sets on the Xeon platform                                                                                                                                                                                                                                                                |

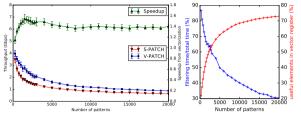

| 2.5 | a) comparison between the scalar and vectorized versions of         |

|-----|---------------------------------------------------------------------|

|     | our approach, as the number of patterns increases. b) filtering-    |

|     | to-verification ratio (left axis), as well as the average number    |

|     | of useful elements in the vector registers after filter 2 (right    |

|     | axis), as the number of patterns increases. c) comparison be-       |

|     | tween the scalar and vectorized approach, as the fraction of        |

|     | matches in the input increases                                      |

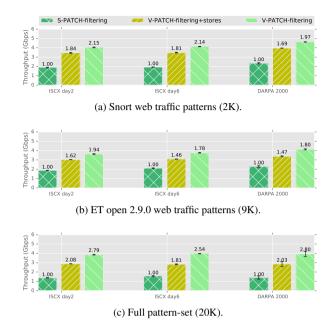

| 2.6 | Measuring the performance of the filtering part only. "V-PATCH-     |

|     | filtering+stores" includes the cost of storing the results of the   |

|     | filtering phase to temporary arrays                                 |

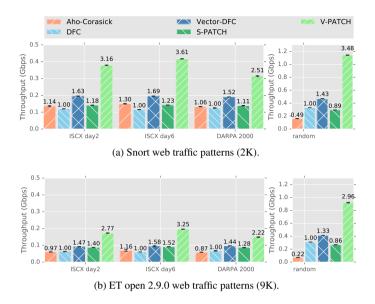

| 2.7 | Performance comparison between the different algorithms for         |

|     | public and random data sets on the Xeon-Phi platform 50             |

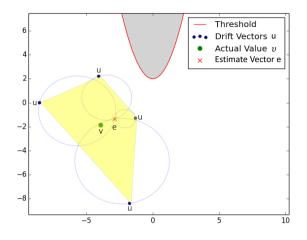

| 3.1 | An example illustrating the GM method                               |

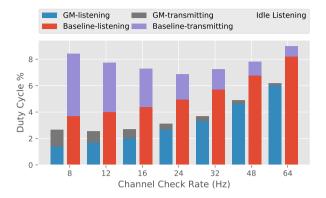

| 3.2 | Full system simulations: The duty cycle, broken down to send-       |

|     | ing and listening, as well as the cost of idle listening 74         |

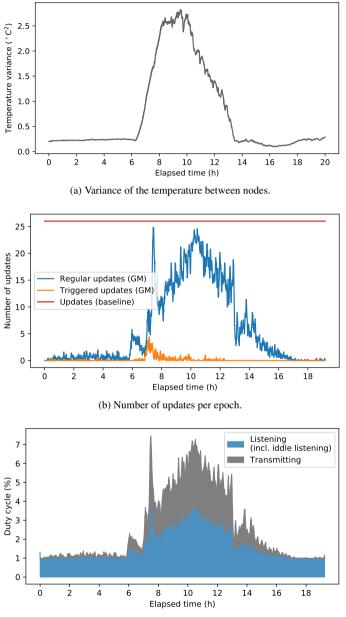

| 3.3 | Runtime insights from the execution of GM over a period of          |

|     | 20 hours                                                            |

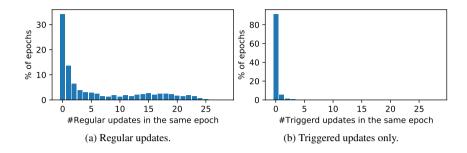

| 3.4 | Runtime insights: Percentage of epochs with concurrent up-          |

|     | dates (regular on the left part and triggered on the right part) 78 |

| 3.5 | Accuracy/Responsiveness of the algorithm measured as we in-         |

|     | troduce packet losses                                               |

|     |                                                                     |

xii

# Part I INTRODUCTION

# 1

## Introduction

The last decade has been marked with many disruptive technologies where the Internet of Things (IoT) is one of the most well known. An increasing number of objects are now becoming "smart" by getting sensing and networking capabilities. The number of devices that are expected to be connected to the internet in the coming years is impressive [1], including everyday objects, cars, as well as devices that are part of the electricity grid and the industry [2]. However, what is even more impressive is the amount of data that they will produce. The upcoming challenge associated with all that data is now this: how, when and where to process the high volumes of data, in order to extract value [3] [4]?

# **1.1** Challenges in processing IoT data: the need for scalability on a range of new architectures

The usefulness of IoT computing comes from the fact that small devices and sensors are able to continuously provide readings about their state and the state of their environment. That data then needs to be processed to provide valuable information about the system, and often to create control commands that are fed back to the devices. IoT devices are typically resource-constrained nodes, sometimes equipped with only enough computational power to acquire readings and send them onwards. In order to accommodate the heavy processing required for many IoT applications, IoT networks rely on a connection with the cloud, where the hardware resources are abundant. This computing model, however, has scalability problems and fails to meet the requirements of many IoT applications. Primarily, the vast number of connected devices, in conjunction with the increasing volume of data generated by each device, means that it is impossible to send all this data to the cloud without exhausting the available bandwidth. Moreover, IoT applications often have tight latency requirements, which means that aggregating data to the cloud, processing it and sending back the control commands adds an unacceptably high overhead.

As a way to address these limitations, fog computing<sup>1</sup> has been proposed as an alternative extension to cloud computing described above [5]. The core idea of fog computing is to move the processing to where it is most needed, closer to the data origin. In this paradigm, the processing and control logic that would typically be found on cloud servers is now pushed down to intermediate nodes, closer to the sources of data. Base stations and gateways will thus be enhanced with processing capabilities and storage, enough to quickly act on aggregated data coming from IoT networks. Moreover, the networks themselves will take over some of the processing and control logic, so that a significant portion of data do not have to be forwarded upwards. It is estimated that this way, more

<sup>&</sup>lt;sup>1</sup>The term fog computing is often used interchangeably with edge computing, with the later focusing more on processing at the devices that produce the data. We will use the term fog computing from now on, to emphasize the need for distributed processing.

than 40 percent of IoT data [6] will be processed on devices physically close to the data sources, by 2019. Hence, the up-link network bandwidth will no longer a limiting factor and there is opportunity to significantly reduce the overall processing latency.

The introduction of fog computing opens new, interesting research questions in several ways. On one hand, fog computing comes with a new set of challenges, that mainly revolve around the problems of (i) how to distribute computational tasks on the layers of fog [7], (ii) how to move them there, (iii) in what ways the different components of fog interact and connect with each other [3] and (iv) how to maintain Quality of Service [8]. On the other hand—and this is important in the context of this thesis—fog computing brings together processing applications with different requirements that target different platforms, under the same computing approach. Processing methods originally designed for servers in the cloud now also become relevant at the intermediate layer of fog and must adapt to the hardware found there. At the same time, computational tasks designed to operate on aggregated data on a single node can benefit if the processing logic is made distributed and handled *close to*, or even by the nodes that produce that data. This increases the design space of existing solutions and poses interesting research questions along the whole spectrum of processing involved in fog computing.

#### 1.2 Background

This section outlines background topics that are relevant in the context of this thesis. We start by discussing relevant advances in hardware, followed by background information on wireless sensor communication.

#### 1.2.1 Advances in processing hardware

Commodity hardware is constantly changing and evolving. Every new generation of platforms is enriched with new hardware features, designed to better serve the needs of applications. The introduction of such features enables new techniques that applications can use to gain performance.

A characteristic example of such important techniques is vectorization. It utilizes processing units that operate on a vector of elements simultaneously, instead of separate elements at a time, in a Single Instruction Multiple Data (SIMD) manner [9, 10]. SIMD vectorization is traditionally used in computationally intensive, number-crunching applications, where computation is performed on independent data, *sequentially* stored in memory.

Vectorization has been available on commodity hardware for many years. Recent advances in hardware platforms have made it relevant again for the following reasons: (i) new vector instruction sets have introduced the *gather instruction* [11] that allows accessing data from *non-contiguous* memory locations and (ii) modern processor designs are shifting towards new architectures with more emphasis on vectorization. As an example Intel's Xeon Phi [12] supports 512 bit vector registers. On those platforms, vectorization is not just an option but a must, in order to achieve high performance [13].

Along with the introduction of new hardware techniques, existing features become more widespread and are adopted by a wider range of platforms. As an example, even embedded devices [14] are now massively parallel and support programmable Graphics Processor Units (GPUs), allowing some of the techniques found on high-end servers to be used on those devices as well.

#### 1.2.2 Wireless sensors networks

Considering the lower layer of fog computing, the hardware found there has substantially different characteristics compared to the high-end servers described in the previous section. Typical devices at this layer are small, battery powered sensors. The main hardware components on these nodes are usually: (i) a set of simple sensors that periodically collect data from the environment (ii) a resource constrained microcontroller unit (MCU) for simple data and packet processing, and (iii) a radio transceiver for communication with other nodes that is used to form networks (either structured or mesh).

In wireless sensors networks (WSN), the battery lifetime is the most valu-

able resource. Thus the design of hardware and software for wireless sensors emphasizes on minimizing the energy footprint. As a consequence, applications on wireless sensors need to deal with the fact that processing components are very simple and resource constrained.

In addition to computation, communication in WSN is also expensive. In fact, the radio is the most energy-hungry component, often consuming up to 10 times more energy than the MCU. For this reason, the goal of most communication protocols is *radio duty cycling* (RDC), where the radio is kept off as much as possible and is turned on for only a small fraction of the total time. A simple and commonly used RDC policy is to turn the radio on a fixed number of times per second, called the *channel check rate* (CCR) [15]. A node that wants to transmit, will keep transmitting for a duration of at least 1/CCR seconds to ensure that all neighbouring nodes had a chance to turn their radio on and receive. The channel check rate is a tunable parameter of the protocol that directly affects the battery lifetime of the nodes.

In addition to energy reservation, latency and reliability are other important considerations in WSNs. Sensors usually form multi-hop networks over unreliable and lossy links that are constantly subject to interference. For this reason, a large body of WSN research has focused on how to design reliable and low-latency network protocols, with interesting new advances over the last few years [16–18].

#### **1.3** Scope of the thesis

This thesis covers aspects of processing and communication in fog, through representative applications that pose challenges stemming from two key problems: (i) *hardware diversity* and (ii) *data diversity*.

Hardware diversity is important since processing can happen on a wide and heterogeneous range of platforms, from resource-constrained embedded devices to high-end servers. On each of these platforms, understanding and making efficient use of the new architectures' features enable new possibilities. Part of the work in this thesis focuses on how to make efficient use of new architectures and features found on these platforms to enable new processing methods.

Data diversity ranges from high-rate data aggregated to a single point, to lower-rate data from many sources, where processing needs to happen in a distributed manner. Applications that operate on accumulated data usually require high throughput processing rates, while distributed applications require minimal, energy efficient communication and distributed control.

We use two applications that instantiate the problems just described and highlight challenges and solutions. Those applications span across the two ends of the spectrum of fog computing: processing for security applications close to the cloud and distributed monitoring of sensor readings inside IoT networks. These applications target different hardware and address different challenges and they become relevant in the context of fog computing, as part of the same processing pipeline. We return to these applications in the next section.

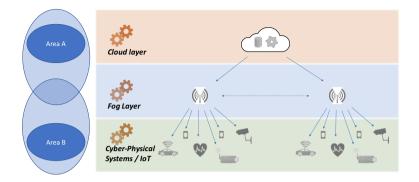

Figure 1.1 shows a conceptual representation of a fog computing architecture. The two problem domains that this thesis focuses on are shown in this figure.

### **1.4 Representative problems in the context of fog** computing

This section introduces the two problem domains that are used as a basis for the work in this thesis. We summarize the challenges in this section and elaborate further on the contributions in each domain in Section 1.5.

#### **1.4.1** Data processing in the context of cyber-security

In the first problem domain, we consider the problems and challenges involved in pattern matching, with a focus on its application for Network Intrusion Detection Systems (NIDS).

**Motivation.** NIDSs are typically found at the entry point of networks and their purpose is to analyze the incoming and outgoing network traffic to detect

**Figure 1.1:** An example fog computing architecture that includes a cloud layer with high-end servers, an intermediate layer close to the gateways and the IoT layer with resource-constrained devices. The work in this thesis targets representative problems on Area A (centralized, high throughput processing) and Area B (distributed processing and communication).

any malicious behavior, ranging from unauthorized access, malware that exploit software vulnerabilities, data exfiltration etc. They typically employ sophisticated analysis that considers not only the packet headers but also the contents of each packet (deep packet inspection [19]). There are many available NIDSs, with Snort [20] and Bro [21] being some of the most popular and mature in the open source community.

Network Intrusion Detection Systems gain new significance in the context of fog computing. IoT networks are connected to the Internet, sending sensor readings upwards towards the cloud and receiving back control traffic. The enddevices producing sensitive data are potential attack targets. However, since they are typically resource-constrained, traditional security mechanisms cannot be employed on them. Hence, it is important to add protection mechanisms, both at the entry point of the network and along the data path towards the cloud.

**Challenges.** An essential building block of many such systems is *pattern matching*, i.e., to discover if any of many predefined patterns exist in an input stream (*multiple* pattern matching), for whitelisting or blacklisting.<sup>2</sup> Consid-

<sup>&</sup>lt;sup>2</sup>Apart from its role in intrusion detection, pattern matching is also a core function in many other

ering the processing involved in NIDSs, pattern matching is the most computationally intensive part and represents a major performance bottleneck. More than 70% of the running time of a NIDS is spent on pattern matching [25, 26]. This fact, in conjunction with the ever increasing rates of traffic that needs to be processed, pushes the performance of NIDSs to their limits. Achieving high pattern matching throughput is challenging yet crucial for these systems: if the processing throughput cannot match the incoming traffic rate, the system will have to start dropping packets and maybe miss significant attacks.

**Related work.** Pattern matching has been an active field of research for many years and there are many proposed approaches. The algorithm proposed by Aho and Corasick [27] is one of the most well known and the one currently used by Snort. The first step of Aho-Corasick is to create a finite-state automaton from the malicious patterns. Then, the algorithm scans the input traffic byte-by-byte to traverse the automaton, until it arrives at a final state that indicates the detection of an attack. Even though Aho-Corasick performs only a small number of operations per byte, it fails to perform well in practice, due to poor cache locality.

State of the art approaches have been proposed to address the limitations of Aho-Corasick. A family of algorithms in the literature replace the state machine of Aho-Corasick with filters. Choi et al. [22] use a series of succinct filters, created using a small part of each malicious pattern. In this way, most of the benign input traffic is quickly filtered out, using cache-resident data structures. The part of the input that matches the information in the filters is further examined in a later verification phase that involves lookups in hash tables that contain the actual patterns. Similarly, Moraru et al. [28] use a modification of Bloom Filters [29] to scan both the input and the subset of patterns that are relevant.

**Open problems.** Even though the state of the art approaches have substantially increased the achieved throughput, they perform sub-optimally in modern architectures, because they fail to make use of the new characteristics and features available. As an example, most pattern matching algorithms do not make

tasks, such as virus detection [22], text search [23] and genome analysis [24].

use of the vector execution units and leave them underutilized. In this thesis we present techniques that allow us to make the most out of the available hardware and achieve considerable speedups in throughput. A summary of this work follows in Section 1.5.2.

#### 1.4.2 Distributed monitoring of sensor readings

In the second problem domain, considering the computation involved in resourceconstrained IoT networks, we focus on the important problem of distributed monitoring of sensor readings.

**Motivation.** We address the issue of continuously monitoring a distributed set of sensor values and keeping track of a function of interest, defined over the network-wide aggregate of these values. Often, the goal is to always be able to detect whether the value of the monitored function has exceeded a predefined threshold. Keeping track of such a function is a basic building block for many IoT applications and control loops, e.g. for detecting outliers [30], hot-spots [31] or denial-of-service attacks [32].

Monitoring sensor values is a prime example of the applications that fog computing is designed for. The need for timely monitoring and low latency detection of a threshold violation calls for local processing, close to the sources of data. Ideally, the monitoring logic can even be placed inside the IoT network and distributed to the sensor nodes themselves.

**Challenges.** Keeping track of a function defined over a network-wide aggregate is a challenging task in practice. A simple solution is to aggregate every reading from every node in the network to a central entity and compute the aggregate there. Such an approach is impractical in networks with batteryconstrained devices: using the radio for transmission or reception is the single most expensive operation in terms of energy [33]. Thus, the challenge associated with this problem is to reduce the number of sensor readings that need to be transmitted, by letting all nodes locally determine whether a reading should be transmitted. However, finding such local criteria is challenging when the function to monitor is non-linear (e.g. the variance of the readings), yet it is non-linear functions that are particularly interesting for many real-world applications (e.g. detecting a denial-of-service attack).

**Related work.** Sharfman et al. [34] proposed a general method called *geometric monitoring (GM)* that can monitor any function (linear or not) defined over the average of network readings and keep track of its value with respect to a threshold. Every node in this algorithm is capable of deriving constraints on its local values and avoid communication as long as those constraints are not violated. The GM method has been extended with sketches [35] and prediction models [36] and has been applied to outlier detection [30] and data stream queries [37].

**Open problems.** Apart from the existing general analysis of algorithms, such as the one described above, the applicability to a real IoT deployment is still unclear, from a practical perspective. Up until now, there are no insights in how the system aspects of IoT networks interact with such algorithms. Specifically, the underlying network stack can have a significant impact on the efficiency of the algorithms, in terms of energy consumption on the nodes, as well as latency and reliability of communication. Moreover, the resource constrained nature of the sensor nodes makes the processing required by the algorithm challenging in practice.

In this thesis we take a step beyond the existing analysis and consider, not just the algorithm in isolation, but also the interplay with system aspects, such as the network stack. A summary of this works follows in Section 1.5.3.

#### **1.5 Research questions and contributions**

Based on the challenges discussed above, in this section, we introduce general research questions that have driven the work in this thesis, as well as a summary of the papers included in this thesis that contribute to these questions.

#### **1.5.1 Research questions**

This thesis addresses the following research questions that emerge in the context of fog computing:

- **RQ1:** How can new hardware support be used to improve the processing throughput of data, across a wide spectrum of platforms.

- **RQ2:** How can distributed algorithms be used to push computation closer to the sources of data, in order to utilize data locality and make efficient use of the limited resources found there?

- **RQ3:** How do system aspects of the different layers of fog computing influence the design of efficient algorithmic approaches?

RQ1 and RQ3 become particularly relevant when considering applications that require high throughput processing of large volumes of data, such as pattern matching. The variety of features found in modern platforms (e.g. advanced vector instructions) offers new possibilities for faster processing, but requires novel, hardware-aware algorithmic designs that make efficient use of those features.

*RQ2* and *RQ3* have an important role in the context of fog computing, where distributing computation is an important way to ensure scalability, in terms of bandwidth and latency. However, turning a centralized algorithm into a distributed one is challenging, especially when it is applied in a resource constrained setting (e.g. in wireless sensor networks).

We relate back to these research questions and how we address them in this thesis, in the context of the following research contributions.

# **1.5.2** (Paper I) Multiple Pattern Matching for Network Security Applications: Acceleration through Vectorization

In this paper, we introduce V-PATCH, a data-parallel algorithm for pattern matching, that uses vector instructions to process multiple bytes of input, in

parallel. This work builds on the observation that recent, state of the art approaches for pattern matching that rely on quick filtering of the input, have brought the problem close to the processor and achieve good cache locality. As a result, long memory latencies are no longer the dominant bottleneck and the computational part of pattern matching becomes significant. With that in mind, we target that computational part and show how to improve it further, through vectorization (see Section 1.2.1). In this way, we contribute towards *RQ1* and show how to make efficient use of the available hardware features.

We follow a two-step approach. First, we propose a refined and extended filtering strategy that: (i) performs filtering based on cache-resident data structures and is effective for the types of patterns found in real traffic, and (ii) is simple enough to allow efficient vectorization. As an example, we deal separately with small, but frequently found patterns and perform more targeted filtering for longer patterns. Second, we design a vectorized version that uses specialized instructions to parallelize the computation performed on the filters, together with optimizations (e.g. filter merging) that allow us to make the most of the filtering design.

We evaluate the effectiveness of V-PATCH using real malicious patterns from Snort [38], against both real and synthetic traffic mixes. The results on two platforms, an Intel Haswell processor and an Intel Xeon Phi co-processor, show up to 1.8x and 3.6x times faster processing throughput respectively, against the state of the art. Furthermore, we find that the vectorized approach retains a stable speedup of 1.4x over the scalar one, as the number of malicious patterns increases.

#### **1.5.3** (Paper II) Geometric Monitoring in Action: a Systems Perspective for the Internet of Things

In this paper, we study geometric monitoring from a full-system perspective, when applied on real IoT networks. We propose a system design for geometric monitoring on top of a wireless sensor network stack. Then, we thoroughly evaluate the performance benefits achieved in practice, the run-time behavior of the algorithm and the effects of packet losses. Through this work, we contribute towards RQ2 and RQ3, by showing that distributing computation to resourceconstrained devices can have significant benefits, as well as by evaluating the effect of the system aspects in the performance of the algorithm.

We design the system on top of multi-hop mesh networks, without the need for maintaining a topology. When a node detects a violation, it will trigger a network-wide broadcast and inform every other node of its new value. This is done by network flooding, where a node that receives "new" information will broadcast it further to its neighbors. In the event that a node fails to receive an update by any of its neighbors, that node will be *out of sync* until a subsequent broadcast from the same originator arrives.

Important considerations that are taken into account are the following. First, upon every new measurement or update, nodes need to check their local violation criteria, which typically involves finding whether two curves intersect. This can be computationally challenging for resource-constrained devices and in some cases, it might be impractical to compute it accurately and in time. To this end, we propose a simple relaxation of the violation check that introduces a trade-off between computational efficiency and communication reduction. Second, we investigate the important parameters of the network stack that affect the effectiveness of the algorithm in practice. As we show in the paper, the rate at which nodes wake-up to receive traffic (Channel Check Rate, CCR) greatly affects the energy savings of the GM method.

We evaluate our design using both full-system simulations and real IoT testbeds. Overall, we find that GM brings significant benefits to monitoring tasks, in terms of communication reduction. Specifically, when monitoring the variance and the average of real temperature data, GM achieves 3x and 11x reduction in duty-cycle, respectively. However, those benefits are limited compared to the communication reduction of the algorithm in isolation (4.3x and 44x respectively), due to baseline energy overhead of the network stack. Closer looks into the run-time behavior of the algorithm show that (i) the communication pattern varies greatly, and (ii) packet losses greatly impact the amount of time a node is *out of sync* and reduce the ability of the algorithm to detect

violations in a timely manner.

#### **1.6 Conclusions and Future Directions**

Motivated by the emergence of IoT and fog computing, this thesis targets the challenges of processing involved across a range of platforms, by focusing on two representative problems, namely pattern matching and continuous monitoring of sensor readings.

On the problem of pattern matching for Network Intrusion Detection, we focus on how to make efficient use of newly introduced hardware features to improve the processing throughput, thus contributing towards RQ1 (cf. Section 1.5.1). The work in this thesis shows that, using advanced vector instructions, it is possible to improve the pattern matching throughput, across a range of data sets and different platforms.

On the problem of continuously monitoring distributed sensor readings, the work in thesis contributes insights towards RQ2. We demonstrate how geometric monitoring can be used to share the processing logic across the resource-constrained devices of IoT networks and give insights from real deployments. Through this work, important aspects of RQ3 are also made clear and we find that a) algorithmic engineering is required to adapt to the needs of battery and CPU-constrained devices and we suggest appropriate approximations, and b) the underlying communication stack greatly influences the performance of the algorithm, in terms of energy, latency and accuracy.

The results presented above target challenges and techniques on two separate sides of the fog computing spectrum. The next challenge is how to bring them closer together and extend them across the different layers of fog.

In the context of pattern matching, it is interesting to consider approaches that would better fit in the intermediate layer, for the following reasons. First, the gateways found at the intermediate layer are points of entry into the IoT network. For this reason, fast intrusion detection is required to secure both the gateways themselves as well as the network to which they provide access. Second, performing intrusion detection closer to the sources of data and not

#### BIBLIOGRAPHY

on remote servers, provides opportunities for bandwidth reservation as well as better response times. Finally, the hardware found at the intermediate layer is becoming increasingly powerful and offers new capabilities. As an example, embedded RaspberryPi-like devices come with multiple cores and even programmable GPUs [14], so they can take the role of gateways with support for processing. Hence, it is interesting to see how to make efficient use of new platforms and the hardware resources they have to offer.

Based on insights from the work in distributed monitoring, described above, there are two interesting aspects that are worth further investigation. First, distributed monitoring algorithms can be extended to take into account the reality of IoT communication. As an example, would it be possible to rely less on a network-wide broadcast mechanism and, instead, resolve violations in a local neighborhood? This would bring overall benefits for both the energy savings and the accuracy of the algorithm. In this direction, we are currently looking at ways to extend the existing literature [31] with a distributed algorithm that is less demanding in terms of communication and is not oblivious to the underlying network stack. Second, it is interesting to see how to design a tailored protocol that serves the communication needs of such distributed applications. Recently, advances in wireless sensor protocols (e.g. synchronous transmissions [16] and channel hopping [39]) have made it possible to achieve fast and highly reliable flooding in mesh networks. One can thus investigate to what extent these protocols can serve the needs of distributed monitoring and how they can be extended further.

#### **Bibliography**

- D. Evans, "The Internet of Things: How the next evolution of the internet is changing everything," Cisco White Paper https://www.cisco.com/c/ dam/en\_us/about/ac79/docs/innov/IoT\_IBSG\_0411FINAL.pdf, January 2011, Accessed: 2018-05-07.

- [2] N. Jazdi, "Cyber physical systems in the context of Industry 4.0," in 2014 IEEE International Conference on Automation, Quality and Testing, Robotics, May 2014,

pp. 1–4.

- [3] M. Chiang and T. Zhang, "Fog and IoT: An Overview of Research Opportunities," *IEEE Internet of Things Journal*, vol. 3, no. 6, pp. 854–864, Dec 2016.

- [4] M. Brodie, "Data: The World's Most Valuable Resource," Lectures in Computer Science on Big Data and Applications, July 2017.

- [5] Cisco, "Fog Computing and the Internet of Things: Extend the Cloud to Where the Things Are," White Paper https://www.cisco.com/c/dam/en\_us/ solutions/trends/iot/docs/computing-overview.pdf, 2015, Accessed: 2018-05-07.

- [6] IDC FutureScape, "Worldwide Internet of Things 2017 Predictions," https://www.idc.com/getdoc.jsp?containerId=US40755816, November 2016, Accessed: 2018-05-07.

- [7] B. Varghese, N. Wang, S. Barbhuiya, P. Kilpatrick, and D. S. Nikolopoulos, "Challenges and opportunities in edge computing," in 2016 IEEE International Conference on Smart Cloud (SmartCloud), Nov 2016, pp. 20–26.

- [8] S. Taherizadeh, A. C. Jones, I. Taylor, Z. Zhao, and V. Stankovski, "Monitoring self-adaptive applications within edge computing frameworks: A state-of-the-art review," *Journal of Systems and Software*, vol. 136, pp. 19–38, 2018.

- [9] "Intel vectorization tools," https://software.intel.com/en-us/ articles/intel-vectorization-tools, Accessed: 2016-12-10.

- [10] O. Polychroniou and Kenneth A. R., "Vectorized Bloom filters for advanced SIMD processors," in *Proc. of the Tenth Int. Workshop on Data Management on New Hardware*. 2014, DaMoN '14, ACM.

- [11] InsideHPC, "Gather Scatter operations," http://insidehpc.com/2015/ 05/gather-scatter-operations/, Accessed: 2016-12-10.

- [12] Intel, "Intel Xeon Phi product family," http://www.intel.com/content/ www/us/en/processors/xeon/xeon-phi-detail.html, Accessed: 2016-12-10.

- [13] Intel, "The importance of vectorization for Intel Many Integrated Core Architecture (Intel MIC architecture)," https://software.intel.com/enus/articles/the-importance-of-vectorization-for-intelmany-integrated-core-architecture-intel-mic, Accessed: 2016-12-10.

- [14] Hardkernel, "Odroid XU4," http://www.hardkernel.com/main/ main.php, Accessed: 2018-05-07.

- [15] A. Dunkels, "The ContikiMac radio duty cycling protocol," Tech. Rep. 2011:13, ISSN 1100-3154, 2011, Swedish Institute of Computer Science.

- [16] F. Ferrari, M. Zimmerling, L. Thiele, and O. Saukh, "Efficient network flooding and time synchronization with Glossy," in *Proceedings of the 10th ACM/IEEE International Conference on Information Processing in Sensor Networks*, Chicago, IL, USA, April 2011, pp. 73–84.

- [17] O. Landsiedel, F. Ferrari, and M. Zimmerling, "Chaos: Versatile and Efficient All-to-all Data Sharing and In-network Processing at Scale," in *Proceedings of the 11th ACM Conference on Embedded Networked Sensor Systems*, New York, NY, USA, 2013, SenSys '13, pp. 1:1–1:14, ACM.

- [18] T. Istomin, A. L. Murphy, G. P. Picco, and U. Raza, "Data Prediction + Synchronous Transmissions = Ultra-low Power Wireless Sensor Networks," in *Proceedings of the 14th ACM Conference on Embedded Network Sensor Systems CD-ROM*, New York, NY, USA, 2016, SenSys '16, pp. 83–95, ACM.

- [19] P. Lin, Y. Lin, Y. Lai, and T. Lee, "Using string matching for deep packet inspection," *Computer*, vol. 41, no. 4, 2008.

- [20] M. Roesch, "Snort Lightweight Intrusion Detection for Networks," in Proc. of the 13th USENIX Conf. on System Administration, Seattle, Washington, 1999, USENIX Association.

- [21] V. Paxson, "Bro: a System for Detecting Network Intruders in Real-Time," Computer Networks, vol. 31, no. 23-24, pp. 2435–2463, 1999.

- [22] B. Choi, J. Chae, M. Jamshed, K. Park, and D. Han, "DFC: Accelerating string pattern matching for network applications," in 13th USENIX Symposium on Networked Systems Design and Implementation (NSDI 16), Santa Clara, CA, 2016, pp. 551–565, USENIX Association.

- [23] G. Navarro, "NR-grep: a fast and flexible pattern-matching tool," Software: Practice and Experience, vol. 31, no. 13, pp. 1265–1312, 2001.

- [24] G. Navarro and M. Raffinot, Flexible pattern matching in strings: practical on-line search algorithms for texts and biological sequences, Cambridge University Press, 2002.

- [25] S. Antonatos, K. Anagnostakis, and E. Markatos, "Generating Realistic Workloads for Network Intrusion Detection Systems," *SIGSOFT Softw. Eng. Notes*, vol. 29, 2004.

- [26] J. B. D. Cabrera, J. Gosar, W. Lee, and R. K. Mehra, "On the statistical distribution of processing times in network intrusion detection," in 2004 43rd IEEE Conf. on Decision and Control (CDC), 2004, vol. 1.

- [27] A. V. Aho and M. J. Corasick, "Efficient String Matching: An Aid to Bibliographic Search," *Commun. ACM*, vol. 18, no. 6, June 1975.

- [28] I. Moraru and D. Andersen, "Exact pattern matching with feed-forward bloom filters," J. Exp. Algorithmics, vol. 17, Sept. 2012.

- [29] B. Bloom, "Space/time trade-offs in hash coding with allowable errors," *Communications of the ACM*, vol. 13, no. 7, pp. 422–426, 1970.

- [30] S. Burdakis and A. Deligiannakis, "Detecting Outliers in Sensor Networks Using the Geometric Approach," in 2012 IEEE 28th International Conference on Data Engineering, Washington, DC, USA, April 2012, pp. 1108–1119.

- [31] I. Sharfman, A. Schuster, and D. Keren, "Aggregate threshold queries in sensor networks," in 2007 IEEE International Parallel and Distributed Processing Symposium, Rome, Italy, March 2007, pp. 1–10.

- [32] L. Feinstein, D. Schnackenberg, R. Balupari, and D. Kindred, "Statistical approaches to DDoS attack detection and response," in *Proceedings DARPA Information Survivability Conference and Exposition*, Washington, DC, USA, April 2003, vol. 1, pp. 303–314 vol.1.

- [33] A. Barberis, L. Barboni, and M. Valle, "Evaluating energy consumption in wireless sensor networks applications," in *Digital System Design Architectures, Methods* and Tools, 2007. DSD 2007. 10th Euromicro Conference on. IEEE, 2007, pp. 455– 462.

- [34] I. Sharfman, A. Schuster, and D. Keren, "A geometric approach to monitoring threshold functions over distributed data streams," in *Proceedings of the 2006* ACM SIGMOD International Conference on Management of Data, New York, NY, USA, 2006, SIGMOD '06, pp. 301–312, ACM.

- [35] M. Garofalakis, D. Keren, and V. Samoladas, "Sketch-based Geometric Monitoring of Distributed Stream Queries," *Proc. VLDB Endow.*, vol. 6, no. 10, pp. 937–948, Aug. 2013.

- [36] N. Giatrakos, A. Deligiannakis, M. Garofalakis, I. Sharfman, and A. Schuster, "Prediction-based Geometric Monitoring over Distributed Data Streams," in *Proceedings of the 2012 ACM SIGMOD International Conference on Management of Data*, New York, NY, USA, 2012, SIGMOD '12, pp. 265–276, ACM.

- [37] M. Garofalakis, "Approximate Geometric Query Tracking over Distributed Streams," *IEEE Data Eng. Bull.*, vol. 38, no. 3, pp. 103–112, 2015.

- [38] Cisco, "Snort Rules and IDS Software Download," https://www.snort.org/ downloads/#rule-downloads, 2018, Accessed: 2018-05-07.

- [39] M. Palattella T. Watteyne and L. Grieco, "Using IEEE 802.15.4e Time-Slotted Channel Hopping (TSCH) in the Internet of Things (IoT): Problem Statement," RFC 7554, RFC Editor, May 2015.

CHAPTER 1. INTRODUCTION

# Part II

# **PAPERS**

# PAPER I

**Charalampos Stylianopoulos**, Magnus Almgren, Olaf Landsiedel, Marina Papatriantafilou

# Multiple Pattern Matching for Network Security Applications: Acceleration through Vectorization

Appeared in the 46th International Conference on Parallel Processing (ICPP) Bristol, United Kingdom August 16, 2017, pp. 472 - 482

# 2 PAPER I

# Abstract

Pattern matching is a key building block of Intrusion Detection Systems and firewalls, which are deployed nowadays on commodity systems from laptops to massive web servers in the cloud. In fact, pattern matching is one of their most computationally intensive parts and a bottleneck to their performance. In Network Intrusion Detection, for example, pattern matching algorithms handle thousands of patterns and contribute to more than 70% of the total running time of the system.

In this paper, we introduce efficient algorithmic designs for multiple pattern matching which (a) ensure cache locality and (b) utilize modern SIMD instructions. We first identify properties of pattern matching that make it fit for vectorization and show how to use them in the algorithmic design. Second, we build on an earlier, cache-aware algorithmic design and we show how cachelocality combined with SIMD gather instructions, introduced in 2013 to Intel's family of processors, can be applied to pattern matching. We evaluate our algorithmic design with open data sets of real-world network traffic: Our results on two different platforms, Haswell and Xeon-Phi, show a speedup of 1.8x and 3.6x, respectively, over Direct Filter Classification (DFC), a recently proposed algorithm by Choi et al. for pattern matching exploiting cache locality, and a speedup of more than 2.3x over Aho-Corasick, a widely used algorithm in today's Intrusion Detection Systems.

# 2.1 Introduction

Security mechanisms, such as Network Intrusion Detection Systems and firewalls, are part of every networked system and are analyzing network traffic to protect from attacks. An essential building block of many such systems is *pattern matching*, i.e., to discover if any of many predefined patterns exist in an input stream (*multiple* pattern matching), for whitelisting or blacklisting. In the context of Network Intrusion Detection, the data stream is the reassembled protocol stream of the *packets* on the monitored network and the set of patterns (usually in the order of thousands) represents *signatures* of malicious attacks that the system aims to detect.

**Motivation and Challenges**. Pattern matching represents a major performance bottleneck in many security mechanisms, especially when there is a need to employ analysis on the full packet's payload (Deep Packet Inspection). In intrusion detection, for example, more than 70% of the total running time in spent on pattern matching [1, 2]. Moreover, with the increasing interest in Network Function Virtualization (NFV) [3, 4], applications like firewalls and Network Intrusion Detection are now moved into the cloud, where they need to rely on commodity hardware features for performance, like multi-core parallelism and vector processing pipelines.

In this paper, we introduce a vectorizable design of an exact pattern match-

ing algorithm which nearly doubles the performance when compared to the state of the art on modern, SIMD capable commodity hardware, such as Intel's Haswell processors or Xeon Phi [5]. *Vectorization* as a technique to increase throughput is gradually taking a more central role [6]. For example, architectures with SIMD instruction-sets now provide wider vector registers (256 bits with AVX) and introduce new instructions, such as gathers, that make vectorization applicable to a wider range of applications. Moreover, modern processor designs are shifting towards new architectures, like Intel's Xeon Phi [5], that, for example, supports 512 bit vector registers. On those platforms, vectorization is not just an option but a must, in order to achieve high performance [7]. In this work we introduce algorithmic designs to utilize these capabilities.

**Approach and Contributions**. The introduction of *gathers* and other advanced SIMD instructions (cf. section 2.3) allows even applications with irregular data patterns to gain performance from data parallelism. For example, SIMD can speed up regular expression matching [8–10]. Here, the input is matched against a single regular expression at a time, represented by a finite state machine that can fit in L1 or L2 cache. Working close to the CPU is crucial for these approaches, otherwise the long latency of memory accesses would hide any computation speedup through vectorization.

The domain of multiple pattern matching for Network Intrusion Detection has challenging constraints that limit the effectiveness of these approaches: applications need to simultaneously evaluate thousands of patterns and traditional state-machine-based algorithms, such as Aho-Corasick [11], use big data structures that by far exceed the size of the cache of today's CPUs. The size of the patterns varies greatly (from 1-byte to several hundred byte patterns) and can appear anywhere in the input. That is why SIMD techniques have not been previously considered for exact multiple pattern matching – with a few exceptions discussed in Section 2.6 – for Network Intrusion Detection.

Building upon recent work [12, 13] that take steps in addressing the cachelocality issues for this problem, our approach fills this gap: we propose algorithmic designs for multiple pattern matching that bring together cache locality and modern SIMD instructions, to achieve significant speedups when compared to the state of the art. Combining cache locality and vectorization introduces new trade-offs on existing algorithms. Compared to traditional approaches that perform the minimum required number of instructions, but on data that is away from the processor, our approach, instead, performs more instructions, but these instructions find data close to the processor and can process them in parallel using vectorization.

In particular, our works build on a family of recent methods [12, 13] that propose filtering of the input streams using small, cache efficient data structures. We argue that, as a result, memory latencies are no longer the dominant bottleneck for this family of algorithms while their computational part becomes more significant. In this work, we follow a two-step approach. First, we propose a refined and extended method, which is able to benefit from vectorization while ensuring cache locality. Second, we design its vectorized version by utilizing SIMD hardware *gather* operations. To evaluate our approach, we apply our techniques to the DFC algorithm [12], as a representative example that outperforms existing techniques in Network Intrusion Detection applications, including [13], on which our proposed approach can be applied as well. In particular, we target the computational part of pattern matching for performance optimization and make the following contributions:

- We propose algorithmic designs for multiple pattern matching which (a) ensure cache locality and (b) utilize modern SIMD instructions.

- We devise a new pattern matching algorithm, based on these designs, that utilizes SIMD instructions to outperform the state of the art, while staying flexible with respect to pattern sizes.

- We (implement the algorithm and) thoroughly evaluate it under both realworld traces and synthetic data sets. We outperform the state of the art by up to 1.8x on commodity hardware and up to 3.6x on the Xeon-Phi platform.

The remainder of the paper is organized as follows: Section 2.2 gives an overview of important pattern matching algorithms and background on vectorization. Section 2.3 describes our system model. In Section 2.4, we present our approach leading to a new, vectorized design. Section 2.5 presents our experimental evaluation. In Section 2.6, we give an overview of other related work and we conclude in Section 2.7.

### 2.2 Background

In this section we present traditional approaches to pattern matching, followed by a brief description of the DFC algorithm (Choi et al. [12]) to which we apply our approach. Next, we introduce the required background on vectorization techniques.

#### 2.2.1 Traditional Approach to Multiple-Pattern Matching

The most commonly used pattern matching algorithm for network-based intrusion detection is by Aho-Corasick [11]. It creates a finite-state automaton from the set of patterns and reads the input byte by byte to traverse the automaton and match multiple patterns. Even though it performs a small number of operations for every input byte, it implies– in practice and on commodity hardware – a low instruction throughput due to frequent memory accesses with poor cache locality [12]: As the number of patterns increases, the size of the state automaton increases exponentially and does not fit in the cache. Nevertheless, the method is heavily used in practice; e.g., both Snort [14], one of the best known intrusion detection systems, as well as CloudFlare's web application firewall [15], use it for string matching.

#### 2.2.2 Filtering Approaches and Cache Locality

Besides state-machine based approaches, there is a family of algorithms that rely on *filtering* to separate the innocuous input from the matches. Recent work focuses on alleviating the problem of long latency lookups on large data structures. Choi et al. [12] present a novel algorithmic design called DFC (Direct Filter Classification), that replaces the state machine approach of Aho-Corasick

with a series of small, succinct summaries called *filters*. Such a filter is a bitarray that summarizes only a specific part of each pattern, e.g. its first two bytes, having one bit for every possible combination of two characters that can be found in the patterns. The algorithm is structured in two phases, the *filtering* and *verification*:

- In the *filtering* phase, a sliding window of two bytes over the input goes through an initial filter, as described above, to quickly evaluate whether the current position is a possible starting point of a match. The two-byte windows that passed the initial filter are fed to other, similar filters, each specializing on a family of patterns depending on their length. Since the filters are small (8KB each), they usually fit in L1 cache. Thus, the main part of the algorithm differs from Aho-Corasick and uses only cache-resident data structures, resulting in up to 3.8 times less cache misses [12].

- If a window of two characters passed all filters, there is a strong indication that it is a starting point of a match. For this reason, in the next *verifica-tion* phase, the DFC algorithm performs lookups on specially designed hash tables, containing the actual patterns and performs exact matching on the input and the pattern, to verify the match.

Other algorithms in this family, like [13] as well as this work, operate on the same idea: the input is filtered using cache resident data structures, and only the "interesting" parts of the input is forwarded for further evaluation.

#### 2.2.3 Vectorization

Single Instruction Multiple Data (SIMD) is an execution model for data parallel applications, which utilizes processing units that operate on a vector of elements simultaneously, instead of separate elements at a time. SIMD vectorization is a desirable goal in computationally intensive, number-crunching applications, where computation is performed on independent data, *sequentially* stored in memory.

Vector instruction sets have evolved over time, introducing bigger registers and support for more complex instructions. Recently, vector instruction sets have been enriched with the *gather* instruction [16] that enables accessing data from *non-contiguous memory locations* (described in detail in Section 2.3). Polychroniou et al. [17] study the effect of vectorization with the *gather* instruction on Bloom filters, hash tables joins and selection scans among others.We are building on these works with SIMD instructions and extend their design to pattern matching with the applications we focus on.

## 2.3 System Model

In this section we introduce the assumptions and requirements that our approach makes on the hardware. We focus on mainstream CPUs, with vector processing units (VPUs) that support *gather* instructions. The latter make it possible to fetch memory from non-contiguous locations using only SIMD instructions<sup>1</sup>

The semantics of *gather* are as follows: let W be the vector length, which is the maximum number of elements that each vector register can hold. The parameters to the instruction are a vector register (I) that holds W indexes and an array pointer (A). As output, *gather* returns a vector register (O) with the W values of the array at the respective indexes. It is important to note that *gather* does not parallelize the memory accesses; the memory system can only serve a few requests at a time. Instead, its usefulness lies in the fact that it can be used to obtain values from non-contiguous memory locations using only SIMD code. This increases the flexibility of the SIMD model and allows to efficiency employ it for workloads previously not considered, i.e., where the memory access patterns are irregular. The alternative is to load the values using scalar code, then transfer them one by one from the scalar registers into vector registers. Generally, switching between scalar and vector code is not efficient [17, 18].

<sup>&</sup>lt;sup>1</sup>In Intel processors, the *gather* instruction was introduced with the AVX2 instruction set and is included in the latest family of mainstream processors (Haswell and Broadwell); *gather* also exists in other architectures, such as the Xeon Phi co-processor [5].

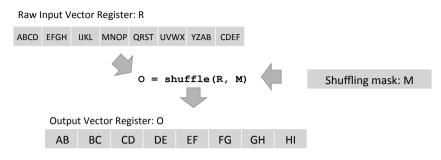

Apart from *gather*, the rest of the instructions we use can be found across almost all the vector instruction sets available. Worth mentioning is the *shuffle* instruction, that makes it possible to permute individual elements within the vector register in any desired order. For example, we employ it for handling the input and output of the algorithm (cf. Section 2.4.2).

The size of the cache, especially the L1 and L2, is very important for the algorithmic design, as we describe later in Section 2.4. Common sizes in modern architectures is 32 KB of L1 data cache with 256 KB of L2 cache and we will use this as a running example. Our design is applicable to other cache sizes as well.

# 2.4 Algorithmic Design

In this section, we begin by introducing S-PATCH, an efficient algorithmic design for multiple pattern matching. It is designed with both cache locality and vectorizability in mind. Next, we propose our vectorization approach V-PATCH, Vectorized PATTern matCHing.

#### 2.4.1 S-PATCH: a vectorizable version of DFC

To enable efficient vectorization, we introduce significant modifications to the original DFC design. The key insight for the modifications, explained later in detail, is that small patterns will be found frequently in real traffic, so they should be identified quickly without adding too much overhead. On the other hand, long patterns are found less frequently, but detecting them takes longer and requires more characters from the input to pinpoint them accurately.

As the original DFC, our approach has two parts, organized as two separate rounds. In the **filtering** round, we examine the whole input and feed it through a series of filters that bear some similarities to DFC, but adapted to consider properties of realistic traffic, as motivated above. The **verification** round is as in DFC and performs exact matching on the full patterns that are stored in hash tables. Compared with DFC, S-PATCH focuses on efficient filtering in the first round, because this is the computationally intensive part of the algorithm that, as we show, can be efficiently vectorized. Splitting the two parts in separate rounds improves cache locality, since the data structures used in each round do not evict each other and, as shown in Section 2.4.2, makes vectorization more practical.

#### Filtering

In this first phase the goals are to (i) quickly eliminate the parts of the input that cannot generate a match and (ii) store the input positions where there is indication for a match. In general, key properties of the filtering phase include:

- Good filtering rate. A big fraction of the input is filtered out at this stage.

- Low overhead. Every filter introduces additional computations and memory accesses, so there needs to be a balance between its overhead and the amount of input that is filtered out.

- Size-efficiency. All the filters need to fit in L1 or L2 cache, while also leaving room for the input and the array for the intermediate results in cache. This is very important, because it ensures that the lookups on the filters will be fast and, as explained later, vectorization using the gather instruction will be feasible.

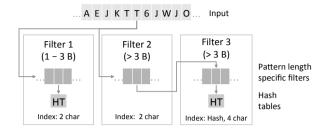

Our proposed filter design (cf. Figure 2.1) consists of three filters, each with a specific purpose. The first one stores information about the short patterns (less than 4 characters). It has one bit for every possible combination of two characters, and if a particular combination is the beginning of a pattern, the corresponding bit is set. Similarly, the second filter uses the same indexing and accounts for the longer patterns together with the third filter. In more detail, (cf. also Algorithm 1):

**First filter.** In the first part of the filtering, we examine two bytes of the input at a time and use them to calculate an index for filters 1 and 2. If the corresponding bit in the first filter is set, we directly store the current input position in an array for further processing (lines 5-7).

**Figure 2.1:** *Filter Design of S-PATCH. HT stands for the* Hash Tables *that contain the full patterns.*

**Second filter.** We also perform a lookup on the second filter using the same index, at line 8. A hit may indicate that we have a match with a longer pattern, but it may also be a false positive (e.g. compare the strings "**at**tribute" and "**at**tack"). Thus, before storing the current input position after a match with the second filter, the algorithm uses more bytes (in our case four) from the input stream with a third filter to gain stronger indications whether there is actually a match. Only when the match in the second filter is corroborated with a match from the third filter is the current position in the input stream stored for further processing (line 11).

**Third filter.** For the third filter, the index is calculated differently; we cannot have a filter with all combinations of four bytes, due to cache-size limitations. Instead, we use a multiplicative hash function for the four bytes of input to compute the index in the filter, at line 9. There is a trade-off between having a large enough filter to avoid collisions (thus providing a good filtering rate) and having it small enough to fit in cache. The reason why we choose four bytes as input will become clear in the next section (4 bytes fit in each one of the 32-bit vector register values).

Note that the performance of the filtering phase is intrinsically tied to the filter designs and the type of input. The reason why our proposed design is more effective is twofold. Short patterns, although few,<sup>2</sup> are likely to generate many matches. As an example, if strings like GET and HTTP are part of the pattern set,

<sup>&</sup>lt;sup>2</sup>21% of Snort's v2.9.7 patterns are 1-4 bytes long [12].

```

Algorithm 1: Pseudocode for S-PATCH.

Data: D: data to inspect

1 # A_short : temporary array for short patterns

2 # A_long : temporary array for long patterns

3 for i=0, i < D.length, i++ do

index = Read two bytes from pos i in D

4

if (Filter1[index] is set) then

5

Store i in A_short

6

end

7

if (Filter2[index] is set) then

8

new_index = hash 4 bytes from input

9

if Filter3[new index] is set) then

10

Store i in A long

11

end

12

13

end

14 end

15

for i=0, i < A_short.length, i++ do

Verification for small patterns

16

17 end

18 for i=0, i < A_long.length, i++ do

Verification for big patterns

19

20 end

```

they will frequently be found in real network traffic. Treating them separately in a dedicated filter allows us to focus on the longer patterns in other filters. Long patterns, found more rarely, require more information to be distinguished from innocuous traffic.

#### Verification

After the filtering, all the possible match positions in the input have been stored in a temporary array. At this point, we need to compare the input at these positions with the actual patterns, before we can safely report a match. As mentioned before, the verification phase is as described by Choi et al. [12], except that it is now done in a separate round, after the current chunk of input has been processed by the filtering phase. For ease of reference we paraphrase here.

Among several optimizations, Choi et al. [12] use specially designed *compact hash tables* that are different for different pattern lengths. Translated to our improved filtering design, if the input at some position i passed the filtering, in the verification phase the algorithm will perform a match on the compact hash table that stores references to all the patterns of appropriate size. For example, if i passed the third filter that stores information on patterns that are four bytes or longer, in the verification phase, the algorithm performs a match on the compact hash table that stores patterns of four bytes or longer (lines 18-20). Each hash table is indexed with as many bytes as the shortest pattern that the hash table contains (in this case, four bytes of the input will be used as an index to the hash table). Each bucket in the hash table contains references to the full patterns and the algorithm has to compare each one of them individually with the input, before reporting a match. Eventually, the algorithm identifies all the occurrences of all the patterns, producing the same output as Aho-Corasick.

In general, the compact hash tables as we use them in this phase, do not fit L1 or L2 cache (but they might fit L3 cache) and accessing them incurs high latency misses. However, the success of the approach lies in the fact that the filtering phase will reject most of the input, so the algorithm resorts to verification only when it is needed (when there is a high probability for a match). That is why our efforts focus on the filtering part, where the data structures are close to the processor and can benefit from vectorization.

#### 2.4.2 V-PATCH: Vectorized algorithmic design

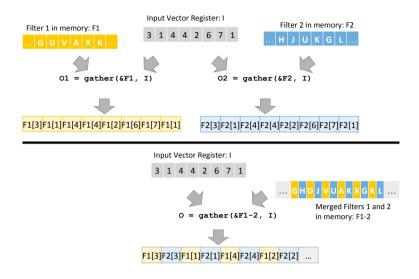

A basic issue when vectorizing S-PATCH is its non-contiguous memory accesses. The sequential version accesses the filters at nonadjacent locations for every window of two characters, whereas in a vectorized design W indexes are stored in a vector register (of length W), each pointing to a separate part of the data structure. For this reason, we use the SIMD *gather* instruction that allows us to fetch values from W separate places in memory and pack them in a vector register.

| Algorithm 2: Pseudocode for the V-PATCH filtering phase.                                            |

|-----------------------------------------------------------------------------------------------------|

| Data: D: input data to inspect                                                                      |

| 1 #W: the vector register length                                                                    |

| 2 # A_short : temporary array for short patterns                                                    |

| 3 # A_long : temporary array for long patterns                                                      |

| 4 # $\overrightarrow{M1}$ : constant mask used to convert the input to 2 byte sliding window format |

| 5 # $\overrightarrow{M2}$ : constant mask used to convert the input to 4 byte sliding window format |

| 6 for $i=0$ , $i < D$ . length, $i + W$ do                                                          |

| 7 $\overrightarrow{R}$ = Fill register with raw input from D                                        |