# On Design and Applications of Practical Concurrent Data Structures

### IVAN WALULYA

Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Gothenburg, Sweden 2018

#### On Design and Applications of Practical Concurrent Data Structures

IVAN WALULYA

Copyright © 2018 Ivan Walulya except where otherwise stated. All rights reserved.

ISBN 978-91-7597-815-4 Doktorsavhandlingar vid Chalmers tekniska högskola, Ny serie nr 4496. ISSN 0346-718X

Technical report 164D

Department of Computer Science and Engineering

Chalmers University of Technology

SE-412 96 Gothenburg, Sweden

Phone: +46 (0)31-772 10 00

Author e-mail: ivanw@chalmers.se

This thesis has been prepared using LATEX. Printed by Chalmers Reproservice, Gothenburg, Sweden 2018.

# On Design and Applications of Practical Concurrent Data Structures

Ivan Walulya

Department of Computer Science and Engineering, Chalmers University of Technology

#### **ABSTRACT**

The proliferation of multicore processors is having an enormous impact on software design and development. In order to exploit parallelism available in multicores, there is a need to design and implement abstractions that programmers can use for general purpose applications development. A common abstraction for coordinated access to memory is a concurrent data structure. Concurrent data structures are challenging to design and implement as they are required to be correct, scalable, and practical under various application constraints. In this thesis, we contribute to the design of efficient concurrent data structures, propose new design techniques and improvements to existing implementations. Additionally, we explore the utilization of concurrent data structures in demanding application contexts such as data stream processing.

In the first part of the thesis, we focus on data structures that are difficult to parallelize due to inherent sequential bottlenecks. We present a lock-free vector design that efficiently addresses synchronization bottlenecks by utilizing the combining technique. Typical combining techniques are blocking. Our design introduces combining without sacrificing non-blocking progress guarantees. We extend the vector to present a concurrent lock-free unbounded binary heap that implements a priority queue with mutable priorities.

In the second part of the thesis, we shift our focus to concurrent search data structures. In order to offer strong progress guarantee, typical implementations of non-blocking search data structures employ a "helping" mechanism. However, helping may result in performance degradation. We propose *help-optimality*, which expresses optimization in amortized step complexity of concurrent operations. To describe the concept, we revisit the lock-free designs of a linked-list and a binary search tree and present improved algorithms. We design the algorithms without using any language/platform specific constructs; we do not use bit-stealing or runtime type introspection of objects. Thus, our algorithms are *portable*. We further delve into multi-dimensional data and similarity search. We present the first lock-free multi-dimensional data structure and linearizable nearest neighbor search algorithm. Our algorithm for nearest neighbor search is generic and can be adapted to other data structures.

In the last part of the thesis, we explore the utilization of concurrent data structures for deterministic stream processing. We propose solutions to two challenges prevalent in data stream processing: (1) efficient processing on cloud as well as edge devices and (2) deterministic data-parallel processing at high-throughput and low-latency. As a first step, we present a methodology for customization of streaming aggregation on low-power multicore embedded platforms. Then we introduce Viper, a communication module that can be integrated into stream processing engines for the coordination of threads analyzing data in parallel.

**Keywords:** atomicity, combining, concurrent data structures, lock-free, locking, multicore, non-blocking, synchronization, stream processing

## List of Publications

#### **Appended publications**

- 1. Ivan Walulya and Philippas Tsigas, "Scalable lock-free vector with combining," in the Proceedings of the 31st International Parallel and Distributed Processing Symposium, pp. 917–926, IEEE 2017.

- 2. Ivan Walulya, Bapi Chatterjee, Ajoy K. Datta, Rashmi Niyoliya, and Philippas Tsigas, "Concurrent lock-free unbounded priority queue with mutable priorities," in the Proceedings of the 20th International Symposium on Stabilization, Safety, and Security of Distributed Systems, LNCS, Springer 2018.

- **3.** Bapi Chatterjee, **Ivan Walulya** and Philippas Tsigas, "Help-optimal and languageportable lock-free concurrent data structures," in *the Proceedings of the 45th International Conference on Parallel Processing*, pp. 360–369, IEEE 2016.

- **4.** Bapi Chatterjee, **Ivan Walulya**, and Philippas Tsigas, "Concurrent linearizable nearest neighbour search in lockfree-kd-tree," in *the Proceedings of the 19th International Conference on Distributed Computing and Networking*, pp. 11:1–11:10, ACM 2018.

- 5. Lazaros Papadopoulos, Dimitrios Soudris, Ivan Walulya, and Philippas Tsigas, "Customization methodology for implementation of streaming aggregation in embedded systems," *Journal of Systems Architecture Embedded Systems Design*, vol. 66-67, pp. 48–60, Elsevier 2016.

- 6. Ivan Walulya, Dimitris Palyvos-Giannas, Yiannis Nikolakopoulos, Vincenzo Gulisano, Marina Papatriantafilou, and Philippas Tsigas, "Viper: A module for communication-layer determinism and scaling in low-latency stream processing," *Future Generation Computer Systems*, vol. 88, pp. 297–308, Elsevier 2018.

## Other publications

The following articles were also published during my PhD studies, but not included in this thesis.

- A. Ivan Walulya, Yiannis Nikolakopoulos, Vincenzo Gulisano, Marina Papatriantafilou, and Philippas Tsigas, "Viper: Communication-layer determinism and scaling in low-latency stream processing," in *Euro-Par 2017: Parallel Processing Workshops*, vol. 10659, pp. 129–140, LNCS, Springer 2018.

- **B.** Lazaros Papadopoulos, **Ivan Walulya**, Philippas Tsigas, and Dimitrios Soudris, "A systematic methodology for optimization of applications utilizing concurrent data structures," *IEEE Transactions on Computers*, vol. 65, no. 7, pp. 2019–2031, IEEE 2016.

- **C.** Lazaros Papadopoulos, **Ivan Walulya**, Paul Renaud-Goud, Philippas Tsigas, Dimitrios Soudris, and Brendan Barry, "Performance and power consumption evaluation of concurrent queue implementations in embedded systems," *Computer Science Research and Development*, vol. 30, no. 2, pp. 165–175, Springer 2015.

- D. Vincenzo Gulisano, Yiannis Nikolakopoulos, Ivan Walulya, Marina Papatriantafilou, and Philippas Tsigas, "Deterministic real-time analytics of geospatial data streams through scalegate objects," in the Proceedings of the 9th ACM International Conference on Distributed Event-Based Systems, pp. 316–317, ACM 2015.

- **E. Ivan Walulya**, Yiannis Nikolakopoulos, Marina, and Philippas Tsigas, "Concurrent data structures in architectures with limited shared memory support," in *Euro-Par 2014: Parallel Processing Workshops*, vol. 8805, pp. 189–200, LNCS, Springer 2014.

- **F.** Lazaros Papadopoulos, **Ivan Walulya**, Philippas Tsigas, Dimitrios Soudris, and Brendan Barry, "Evaluation of message passing synchronization algorithms in embedded systems," in *the Proceedings of the 14th International Conference on Embedded Computer Systems: Architectures, Modeling, and Simulation*, pp. 282–289, IEEE 2014.

#### **Research Contribution**

**Paper 1** was authored in collaboration with Philippas Tsigas. I contributed to the design and implementation of the presented algorithms. Additionally, I participated in the writing of the paper. **Paper 2** builds on previous work by Ajoy K. Datta and Rashmi Niyoliya extending the work in Paper 1 to build a concurrent unbounded binary heap. In this paper, I contributed to the design of the presented algorithms, implementations, and authoring of paper.

In **Paper 3**, I contributed to the design of the algorithms, proof sketches, and developed the C/C++ implementations presented in the paper. Additionally, I developed the benchmark suite utilized for all results presented in the paper.

My contributions to **Paper 4** include participation in the design of Nearest Neighbor Search (NNS) algorithm on the concurrent KD-Tree, proof of correctness of the NNS algorithm. Implementation of the designed algorithms and benchmarks used in the evaluation of the algorithm in addition to co-authoring.

**Paper 5** is an extension of joint work with Lazaros Papadopoulos in **Papers B, C, F**; together, the works were developed for exploiting parallelism available in low-power embedded systems. In this work, my contributions were on the design of concurrent data structures and algorithms ported onto the embedded systems. Additionally, I participated in the writing of the papers, while Papadopoulos performed the bulk of the experiments presented in the papers.

In **Paper 6**, I integrated ScaleGate (a novel interface for the deterministic merging of multiple data streams) into Apache Storm Stream Processing Engine, and extended ScaleGate to include flow-control thus making it usable in a task-based scheduler as opposed to a thread-based scheduler. Additionally, I implemented and performed benchmarks for throughput, latency, and energy measurements on general purpose processors. Benchmarks on Odroid devices were implemented in collaboration with Dimitris Palyvos-Giannas. Additionally, I was the lead on the writing of the paper in collaboration with all other authors. This work was a continuation of collaboration on **Paper D**.

# Acknowledgments

I would like to start by thanking my supervisor Prof. Philippas Tsigas who encouraged me to pursue a research career, has supported and mentored me all these years with great insight and wisdom. I am also grateful to my cosupervisor Prof. Marina Papatriantafilou for great counsel, encouragement, uplifting discussions, and feedback.

A single name appearing on the cover of this thesis is a misrepresentation of the efforts that have gone into the work herein. I owe a debt of gratitude to my co-authors and collaborators that have directly or indirectly contributed to this work. In no particular order, thank you, Bapi Chatterjee, Yiannis Nikolakopoulos, Vincenzo Gulisano, Aras Atalar, Paul Renaud-Goud, Lazaros Papadopoulos, Charalampos Stylianopoulos, Dimitris Palyvos-Giannas, Adones Rukundo, Daniel Cederman, Anders Gidenstam, Dimitrios Soudris, Brendan Barry and, Ajoy K. Datta.

I am honored to have Assoc. Prof. Danny Hendler as the faculty opponent during the thesis defense. I would like to acknowledge members of the grading committee: Dr. Emmanuelle Anceaume, Prof. Håkan Grahn, Prof. Lasse Natvig, and Associate Prof. Pedro Petersen Moura Trancoso. I also wish to thank my examiner Prof. Aarne Ranta, and the follow-up committee for their support during my studies.

I take this opportunity to thank the administration at the Department of Computer Science and Engineering. I received tremendous help on administrative tasks from Eva Axelsson, Rebecca Cyren, Marianne Pleen-Schreiber, Tiina Rankanen, and Peter Helander. I would also like to extend a token of appreciation to my managers Tomas Olovsson and Peter Lundin.

Many thanks to all past and present members of the NS group that have contributed to such a great working environment: Ali, Aljoscha, Amir, Bastian, Elad, Farnaz, Fazeleh, Georgia, Giorgos, Hannaneh, Iosif, Magnus, Nasser, Nhan, Olaf, Oscar, Thomas, Valentin, Valentin, Zhang.

I consider myself particularly lucky to be able to call several current and former members of the department, not just colleagues, but friends. Thank you Alirad, Bhavi, Chloe, Madhavan, Petros, Prajith, Stavros, Stefano, Vagelis, Yiannis, among others.

Special thanks to all the *thirstos*, especially Isaac Muganwa for always pushing me to heights that I might have thought out of reach.

**Funding.** The work in this thesis was supported by the European Research Council under the European Union's Seventh Framework Programme (FP7/2013-2016) / Grant agreement no. 611183, EXCESS Project.

Ivan Walulya Göteborg, November 2018

# Contents

| Li               | List of Publications                     |                                 |                                                      |     |  |

|------------------|------------------------------------------|---------------------------------|------------------------------------------------------|-----|--|

| Pe               | rsona                                    | l Contr                         | ribution                                             | vii |  |

| Acknowledgements |                                          |                                 | ix                                                   |     |  |

| 1 Introduction   |                                          |                                 | on .                                                 | 1   |  |

|                  | 1.1                                      | Shared-Memory Multicore Systems |                                                      |     |  |

|                  |                                          | 1.1.1                           | Caches and Memory Consistency                        | 6   |  |

|                  |                                          | 1.1.2                           | Atomic Primitives                                    |     |  |

|                  | 1.2                                      | Synch                           | ronization                                           |     |  |

|                  |                                          | 1.2.1                           | Blocking Synchronization                             | 10  |  |

|                  |                                          | 1.2.2                           |                                                      |     |  |

|                  |                                          | 1.2.3                           | Power of Synchronization Primitives                  | 12  |  |

|                  | 1.3                                      | Concu                           | rrent Data Structures                                |     |  |

|                  |                                          | 1.3.1                           | Correctness of Concurrent Data Structures            | 13  |  |

|                  | 1.4                                      | Non-b                           | locking Concurrent Data Structures                   | 15  |  |

|                  |                                          | 1.4.1                           | Design and Implementation Approaches                 | 15  |  |

|                  |                                          | 1.4.2                           | Concurrent Data Structures for Efficient Data Stream |     |  |

|                  |                                          |                                 | Processing                                           | 18  |  |

|                  | 1.5                                      | Contri                          | butions                                              | 20  |  |

|                  | Bibl                                     | iograph                         | y                                                    | 22  |  |

| 2                | Scalable Lock-Free Vector with Combining |                                 |                                                      |     |  |

|                  | 2.1                                      | Introd                          | uction                                               | 32  |  |

|                  |                                          | 2.1.1                           | Related Work:                                        | 34  |  |

|                  | 2.2                                      | Systen                          | m Model and Definitions                              | 35  |  |

|                  | 2.3                                      |                                 |                                                      | 37  |  |

|                  |                                          | 2.3.1                           | Overview of the Algorithm                            | 37  |  |

|                  |                                          | 2.3.2                           | Implementation Details                               | 38  |  |

|                  |                                          | 2.3.3                           | Correctness                                          | 46  |  |

XII CONTENTS

|   |                                                 | 2.3.4        | Memory Management and ABA Problems                 | 49  |  |  |

|---|-------------------------------------------------|--------------|----------------------------------------------------|-----|--|--|

|   | 2.4                                             | Perfor       | mance Evaluation                                   | 50  |  |  |

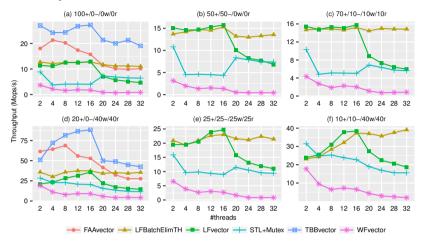

|   |                                                 | 2.4.1        | Experimental Results and Discussion                | 51  |  |  |

|   | 2.5                                             | Conclu       | usion                                              | 53  |  |  |

|   | Bibl                                            | oliography   |                                                    |     |  |  |

| 3 | 3 Concurrent Lock-free Unbounded Priority Queue |              |                                                    |     |  |  |

|   | 3.1                                             | Introd       | uction                                             | 60  |  |  |

|   | 3.2                                             | Prelim       | inaries                                            | 62  |  |  |

|   | 3.3                                             | Algori       | thm                                                | 63  |  |  |

|   |                                                 | 3.3.1        | Lock-free ADT Operations                           | 65  |  |  |

|   |                                                 | 3.3.2        | Design Optimizations                               | 67  |  |  |

|   | 3.4                                             | Correc       | etness Proof                                       | 69  |  |  |

|   | 3.5                                             | Evalua       | ation                                              | 70  |  |  |

|   | 3.6                                             | Conclu       | usion                                              | 75  |  |  |

|   | Bibl                                            | iograph      | y                                                  | 75  |  |  |

| 4 | Help                                            | o-optim      | al and Language-portable Lock-free Concurrent Data |     |  |  |

|   | Stru                                            | Structures   |                                                    |     |  |  |

|   | 4.1                                             | Introd       | uction                                             | 82  |  |  |

|   |                                                 | 4.1.1        | Overview                                           | 82  |  |  |

|   |                                                 | 4.1.2        | Related Work                                       | 85  |  |  |

|   | 4.2                                             | Help-o       | optimality: Motivation                             | 86  |  |  |

|   | 4.3                                             | Help-o       | optimal Lock-free Linked-list                      | 89  |  |  |

|   |                                                 | 4.3.1        | Design                                             | 89  |  |  |

|   |                                                 | 4.3.2        | Correctness and Lock-freedom                       | 93  |  |  |

|   |                                                 | 4.3.3        | Amortized Step Complexity                          | 94  |  |  |

|   | 4.4                                             | Help-o       | optimal Lock-free BST                              | 95  |  |  |

|   |                                                 | 4.4.1        | Design                                             | 95  |  |  |

|   |                                                 | 4.4.2        |                                                    | 101 |  |  |

|   | 4.5                                             | Help-o       | optimality: Specification                          | 101 |  |  |

|   | 4.6                                             | Experi       | imental Evaluation                                 | 102 |  |  |

|   |                                                 | 4.6.1        | Overview                                           | 102 |  |  |

|   |                                                 | 4.6.2        | Experimental Set-up                                | 103 |  |  |

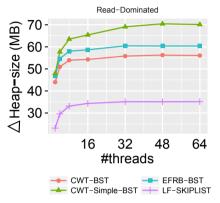

|   |                                                 | 4.6.3        | Performance Results and Discussion                 | 104 |  |  |

|   | 4.7                                             | Conclu       | usion                                              | 108 |  |  |

|   | Ribl                                            | Bibliography |                                                    |     |  |  |

CONTENTS XIII

| 5 | Con                                                           | current | Linearizable Nearest Neighbour Search in LockFree | <b>-</b> |  |  |

|---|---------------------------------------------------------------|---------|---------------------------------------------------|----------|--|--|

|   | kD-tree 113                                                   |         |                                                   |          |  |  |

|   | 5.1                                                           | Introdu | uction                                            | 114      |  |  |

|   |                                                               | 5.1.1   | Background                                        | 114      |  |  |

|   |                                                               | 5.1.2   | A high-level summary of the work                  | 116      |  |  |

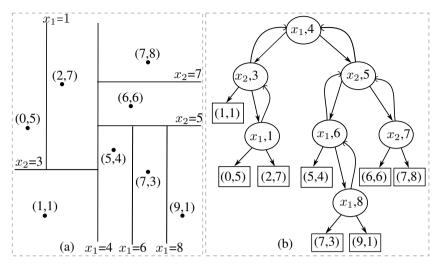

|   | 5.2                                                           | LockF   | ree-kD-tree: Basic Design                         | 118      |  |  |

|   |                                                               | 5.2.1   | Design of the LFkD-tree                           | 118      |  |  |

|   |                                                               | 5.2.2   | Sequential Behaviour of the ADT Operations        | 119      |  |  |

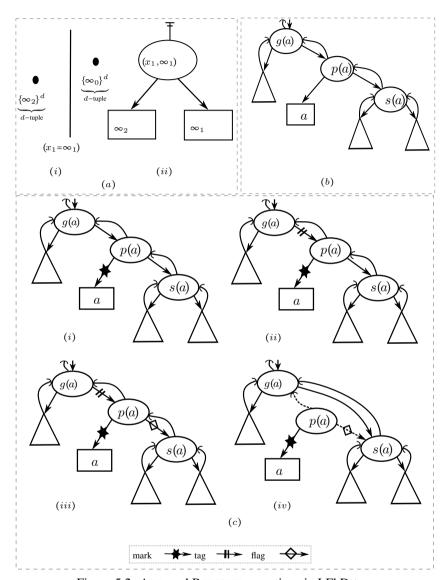

|   | 5.3                                                           | LockF   | ree-kD-tree: Implementation                       | 120      |  |  |

|   |                                                               | 5.3.1   | Lock-free Synchronization: Basics                 | 120      |  |  |

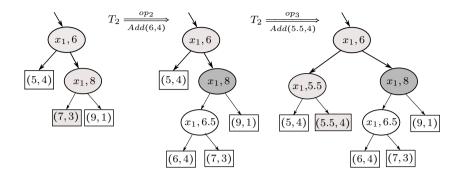

|   |                                                               | 5.3.2   | Linearizable ADD, REMOVE and CONTAINS operations  | 124      |  |  |

|   |                                                               | 5.3.3   | Linearizable Nearest Neighbour Search             | 129      |  |  |

|   | 5.4                                                           | Correc  | etness and Lock-freedom                           |          |  |  |

|   | 5.5                                                           |         | -life application                                 |          |  |  |

|   | 5.6                                                           |         | mental Evaluation                                 |          |  |  |

|   |                                                               | 5.6.1   | Experimental Setup                                |          |  |  |

|   |                                                               | 5.6.2   | Datasets                                          |          |  |  |

|   |                                                               | 5.6.3   | Observations and Discussion                       | 152      |  |  |

|   | 5.7                                                           | Conclu  | usion and Future Work                             | 156      |  |  |

|   | Bibl                                                          | iograph | y                                                 | 156      |  |  |

| 6 | Customization Methodology for Implementation of Streaming Ag- |         |                                                   |          |  |  |

|   | greg                                                          | •       | n Embedded Systems                                | 161      |  |  |

|   | 6.1                                                           |         | uction                                            |          |  |  |

|   | 6.2                                                           |         | d Work                                            |          |  |  |

|   | 6.3                                                           | Stream  | ning Aggregation                                  | 165      |  |  |

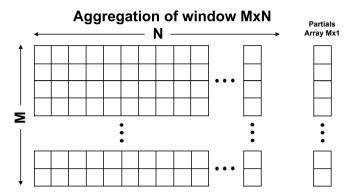

|   |                                                               | 6.3.1   | Streaming Aggregation description                 | 165      |  |  |

|   | 6.4                                                           | Custor  | mization Methodology                              | 168      |  |  |

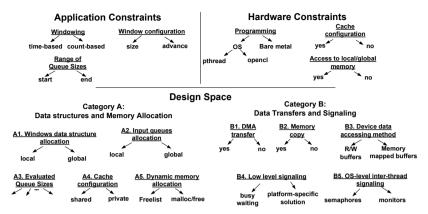

|   |                                                               | 6.4.1   | Design Space                                      | 168      |  |  |

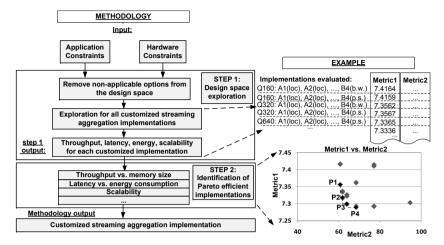

|   |                                                               | 6.4.2   | Methodology description                           | 170      |  |  |

|   | 6.5                                                           | Demoi   | nstration of the Methodology                      | 171      |  |  |

|   |                                                               | 6.5.1   | Platforms description                             | 171      |  |  |

|   |                                                               | 6.5.2   | Experimental Setup                                | 174      |  |  |

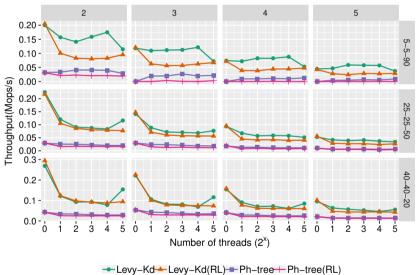

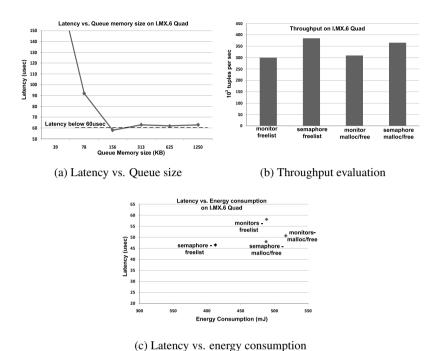

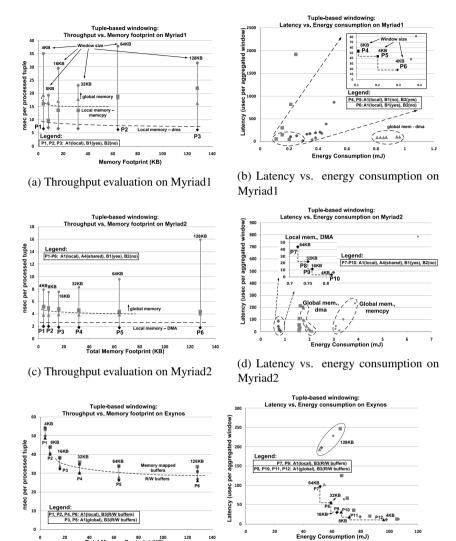

|   |                                                               | 6.5.3   | Time-based aggregation results                    | 175      |  |  |

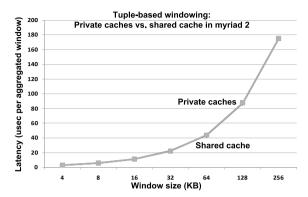

|   |                                                               | 6.5.4   | Count-based aggregation results                   | 181      |  |  |

|   |                                                               | 6.5.5   | Performance per watt evaluation                   |          |  |  |

|   |                                                               | 6.5.6   | Discussion of Experimental Results                |          |  |  |

|   | 6.6                                                           | Conclu  | asion                                             | 189      |  |  |

|   | Bibliography                                                  |         |                                                   |          |  |  |

XiV CONTENTS

| 7 | Viper: A Module for Communication-Layer Determinism and Scal- |                                              |                                                        |       |  |

|---|---------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------|-------|--|

|   | _                                                             |                                              | Latency Stream Processing                              | 195   |  |

|   | 7.1 Introduction                                              |                                              |                                                        | . 196 |  |

|   | 7.2                                                           |                                              |                                                        |       |  |

|   |                                                               | 7.2.1                                        |                                                        |       |  |

|   |                                                               | 7.2.2                                        | Parallelism, determinism and syntactic transparency    | . 199 |  |

|   |                                                               | 7.2.3                                        | Streaming operators' performance metrics               | . 201 |  |

|   | 7.3                                                           | Operator- vs communication-layer determinism |                                                        | . 201 |  |

|   |                                                               | 7.3.1                                        | Limitations of operator-layer determinism              |       |  |

|   |                                                               | 7.3.2                                        |                                                        |       |  |

|   |                                                               |                                              | sioning in the SPE-communication-layer                 | . 204 |  |

|   | 7.4                                                           | The V                                        | iper module                                            | . 205 |  |

|   |                                                               | 7.4.1                                        | Viper as an SPE module: Apache Storm use case          | . 206 |  |

|   | 7.5                                                           | Evalua                                       | ation                                                  | . 210 |  |

|   |                                                               | 7.5.1                                        | Intra-Node Parallel Analysis - Setup                   | . 210 |  |

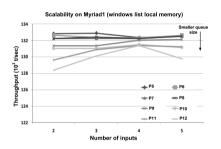

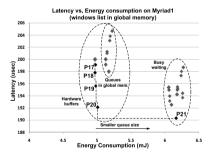

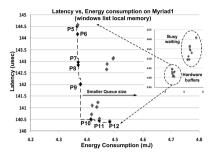

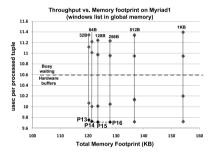

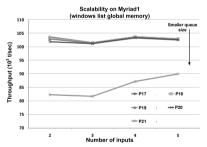

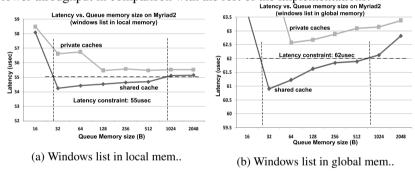

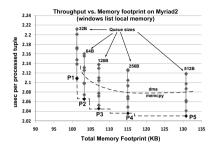

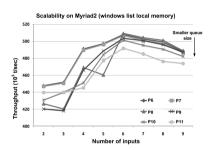

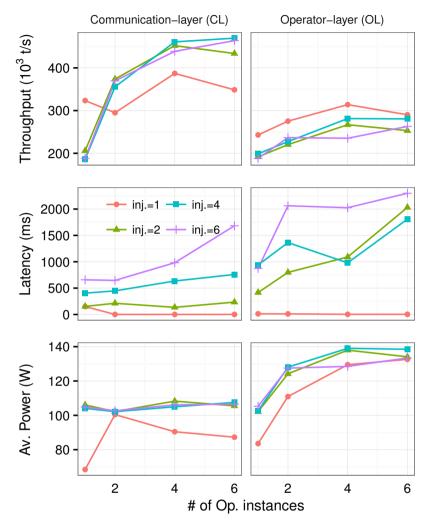

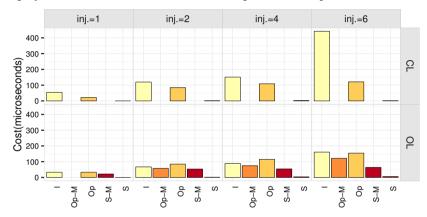

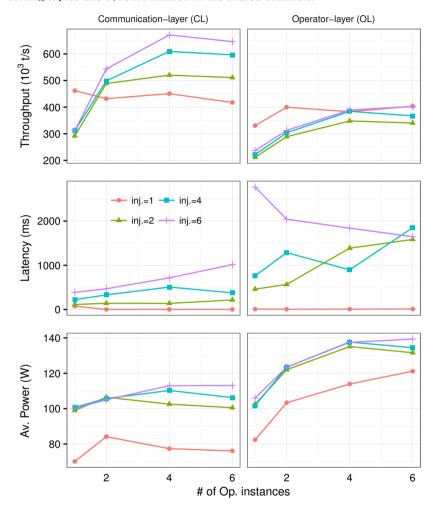

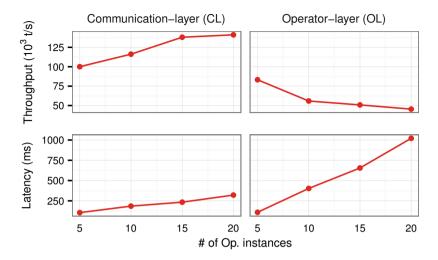

|   |                                                               | 7.5.2                                        | Intra-Node Parallel Analysis - Scalability             | . 211 |  |

|   |                                                               | 7.5.3                                        | Inter-Node Distributed Parallel Analysis - Setup       | . 219 |  |

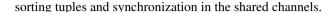

|   |                                                               | 7.5.4                                        | Inter-Node Distributed Parallel Analysis - Scalability | . 220 |  |

|   |                                                               |                                              | d work                                                 | . 222 |  |

|   | 7.7 Conclusions                                               |                                              |                                                        |       |  |

|   | Bibliography                                                  |                                              |                                                        | . 223 |  |

| 8 | Con                                                           | clusion                                      | s and Future Work                                      | 227   |  |

# Introduction

In recent years, multicore systems have become ubiquitous; processors in handheld devices, laptops, desktop computers to super-computers contain multiple cores. This emergence of multicore systems is driven largely by *demand*; demand for more computing power. For more than four decades, two scaling principles guided processor design: Moore's law [1] and Dennard's scaling [2]. Moore's law is an observation that the number of transistors cost-effectively placed on a chip doubles approximately every two years. Dennard scaling is related to Moore's law, in that, the power consumption is proportional to transistor size. When transistors got smaller, voltage and current scaled down; the power density stayed the same from one processor generation to the next.

In the early 2000s, the semiconductor industry started experiencing a break down in Dennard scaling: *threshold voltage*, *current leakage*, and subsequent *heat dissipation* do not scale with size, creating a physical limit to the practical size of a transistor – *Power Wall*. The power wall compelled processor designers to change their approach; rather than to increase the clock rate of a single processor, add multiple processors with lower clock rates on a single chip.

A chip with multiple processing units is commonly referred to as *multicore* and each processing unit as a *core*. Generally, the cores communicate through read and write operations on shared-memory (shared-memory multicores). The primary objective is to achieve more throughput with parallel executions instead

of improving the completion time of a single execution.

This shift in processor design has had a significant impact on software design and implementation as programmers seek to utilize the multiple computing cores efficiently. In the ideal case, multiple cores are employed to perform a large task split into sub-tasks; each core independently executes its sub-tasks to completion. Applications that execute in this manner are considered *embarrassingly parallel*. In practice, however, many tasks cannot be easily divided and executed independently in parallel<sup>1</sup>; computing cores need to coordinate their actions.

As an analogy, consider a family attempting to assemble an IKEA dining table. If the whole family is involved in the assembly, they could "probably" complete the task faster. For this to happen, they need to divide up the task in order to assemble different sections of the table at the same time. However, some parts of the table must be assembled in a given order; consequently, some members may have to wait for others to complete a given component – *synchronization*. If one member takes too long on a given task, he risks delaying others that are waiting – *Blocking*. Additionally, if the group spends too much time sharing tools and the instruction leaflet – *communication costs*, then they lose the anticipated *speed-up*. The challenge becomes harder with a larger family.

As with the analogy, multicore program execution typically comprises of tasks that can be executed in parallel without coordination and tasks that require coordination among the processes. Coordination is generally required when processors concurrently access shared resources or objects. The goal is to prevent inconsistencies that may result from the interleaving of concurrent accesses by multiple processes.

#### Initially SC = 0

P1 P2

1:  $old \leftarrow SC$ 2:  $new \leftarrow old + 1$ 3:  $SC \leftarrow new$ 1:  $old \leftarrow SC$ 2:  $new \leftarrow old + 1$ 3:  $SC \leftarrow new$

Figure 1.1: Shared Counter

Take for example the shared counter in Figure 1.1 incremented by two

<sup>1&</sup>quot;No matter how great the talent or efforts, some things just take time. One cannot produce a baby in one month by getting nine women pregnant." – Warren Buffett

processes. After the two processes complete, we expect that the value of the counter is incremented by 2. However, one of the increments could be lost due to processes overwriting each other's modifications. The program is said to have a "race condition", *i.e.*, the outcome of the execution is dependent on the arbitrary interleaving of events [3].

The need for synchronization in concurrent systems predates multicore architecture [4, 5]; any program that allows concurrent operations must be synchronized, regardless of whether the operations are actually executed in parallel<sup>2</sup>. Synchronization allows one to explicitly dictate which interleavings are acceptable and prohibit those that are unacceptable. Generally, this is achieved by guaranteeing some notion of *atomicity*, in that, a given sequence of instructions executed by a single process appears instantaneous to other processes.

In shared-memory multicore systems, synchronization is ordinarily achieved through mutual exclusion: access to the shared object is guarded by locks. Segments of the execution that are guarded by locks are referred to as *critical sections*. A process that wishes to execute inside a critical section must acquire the respective lock; acquiring the lock guarantees that instructions executed inside the critical section appear atomic to other processes. A process releases the lock on exiting the critical section. The popularity of mutual exclusion locks is attributed to their simplicity in most use cases and efficient implementation in presumably all shared-memory platforms.

However, mutual exclusion is associated with several pitfalls; locks are *blocking* – arbitrary delay or failure of a process holding a lock blocks other processes from making progress. Additionally, care must be taken to avoid deadlocks, priority inversions and convoying.

Non-blocking synchronization has emerged as a solution to many pitfalls associated with locks. It takes a more optimistic approach where a process attempts to access a shared object without blocking other processes. Although non-blocking synchronization was initially desirable for fault-tolerance in asynchronous shared memory systems, recent research has shown that it has the potential to increase parallelism [6–10].

Correct implementation of a synchronization mechanism is required to satisfy *safety* and *liveness* properties [11]. Informally, safety states that "bad" things never happen, such as no two processes execute inside the critical section at the same time. Liveness states that "good" things eventually happen; for example, if a lock is free, then some requesting process eventually acquires the lock.

<sup>&</sup>lt;sup>2</sup>We consider two operations *concurrent* if their execution interval overlaps in time, *parallel* if the operations can actually be executed at the same time.

Regardless of whether blocking or non-blocking, synchronization of processes is a difficult undertaking for application developers. This complexity is often hidden away from the developer through concurrent programming abstractions. A common abstraction for synchronizing access to shared data is in the form of *concurrent data structures*. In a sequential setting, data structures organize data for efficient access. The abstraction of a data structure is described by an Abstract Data Type (ADT), which is an interface definition of operations that can be executed on the data structure.

In concurrent settings, in addition to implementing the ADT, the data structure hides details on the interaction of processes that simultaneously call operations on the data structure. Application developers can utilize a concurrent data structure without concern for the implementation details as long as it observes the interface defined by the Abstract Data Type. Hence, the implementation of efficient, practical concurrent data structure is of paramount importance for application developers at various levels of expertise to fully exploit parallelism available in multicore platforms.

Abstraction does not eliminate the complexity of correct synchronization, but it nevertheless allows us to reason about concurrent interactions at a high-level of interface operations rather than low-level interleaving of machine instructions. The designer of a concurrent data structure takes on the difficult task of choosing how to implement the ADT efficiently and correctly.

Concurrent data structures are generally classified according to safety and liveness properties that they satisfy. At this level of abstraction, the main safety requirement is that operations on the data structure appear indivisible, i.e., every operation appears to take effect without interruption despite any possible interleaving with other operations. Various formalizations of this requirement exist in the literature *e.g.*, Linearizability [12] and Sequential Consistency [13].

Operations on concurrent data structure are associated with different progress guarantees: *blocking* or *non-blocking*. Delay of a process executing a blocking operation can delay others processes, while, execution of non-blocking operations cannot delay or prevent other processes from making progress. There are several levels of non-blocking progress [14].

Concurrent data structures form basic building blocks for more sophisticated applications. One application that has gained significant interest is Data Stream Processing (DSP). The interest in Data Stream Processing is a result of the unprecedented increase in volumes of data generated at high-rates as we integrate computing in all aspects of our lives from smart watches to self-driving vehicles. Users require useful insights from this data in real-time; the data has to be processed in-motion. Stream processing typically has high-throughput and low-latency constraints and thus an excellent application domain for exploitation of

concurrent data structures in order to efficiently utilize multicore platforms.

In this thesis, we contribute to the body of research on efficient, practical concurrent data structures in multicore architectures. We present design mechanisms that efficiently address potential synchronization bottlenecks without sacrificing non-blocking progress guarantees. We design algorithms for portable search data structures that do not rely on the programming language or platform specific constructs. Additionally, we explore the utilizing of concurrent data structures in demanding application contexts such as data stream processing.

The rest of this chapter introduces background on shared-memory multicore architectures, synchronization in shared memory systems and design techniques for concurrent data structures. Section 1.1 briefly describes a basic shared-memory architecture, highlighting the effects of cache coherence and memory consistency on parallel programs. Furthermore, it provides the semantics of various read-modify-write instructions available on many shared-memory platforms that typically underlie implementations of synchronization mechanisms. Section 1.2 presents an overview of synchronization mechanisms in shared-memory multicore architectures. Section 1.3 presents related work, challenges in the design of concurrent data structures, and highlights how concurrent data structures are utilized in solving challenges in deterministic parallel data processing. The contributions of this thesis are summarized in Section 1.5.

## 1.1 Shared-Memory Multicore Systems

A multicore processor is a processor with multiple independent computational units (referred to as cores) on a single chip. Multicore systems may contain one or more multicore processors – *multiprocessor*. We use the terms *processor* and *core* interchangeably to refer to an independent computational unit. Similarly, we use the terms processes and threads interchangeably to refer to active threads of control that potentially share variables in a shared address space.

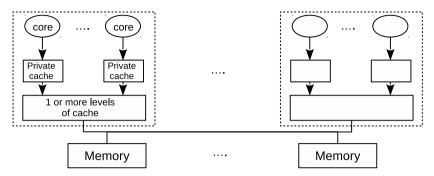

Figure 1.2 depicts a classical architecture for shared-memory multiprocessors, including several processors, each having multiple cores with private and shared caches, all connected via a shared memory subsystem. Shared-memory multicores have a single shared address space accessible to all cores. Processing cores execute independently and communicate through read and write operations on shared objects in memory. We consider an asynchronous shared memory model where processes may execute at varying speeds and can experience arbitrary delays due to scheduling interrupts, memory page faults and cache behavior.

Single shared address space does not imply single memory; multiple memory modules may be attached to the system and will appear as a single address space

Figure 1.2: Typical architecture for a Shared-Memory Multiprocessor.

to the processors. The shared-memory multiprocessors are classified as either Uniform Memory Access (UMA) – memory access latency is uniform for all processors, or Non-Uniform Memory Access (NUMA) – memory latency is dependent on the memory location and the processor that accesses the location.

#### 1.1.1 Caches and Memory Consistency

The divergence in speeds between processors and memory systems compelled system designers to develop techniques for hiding latency in accessing memory systems. For example, write-back store buffers and cache hierarchies between the cores and memory. Each core typically has a cache hierarchy composed of private and shared caches. The cores store temporary copies of data in cache hierarchy for faster access than reading from memory.

Caches create an illusion of fast high-bandwidth memory by exploiting *locality*. Programs generally access small portions of memory at any small interval in time; either an address is accessed repeatedly, and the accesses are close in time (*temporal locality*) or adjacent addresses are accessed close in time (*spatial locality*). Effectively, bandwidth demands on main memory are reduced, allowing multiple processors to share the same memory.

Unfortunately, when cores store copies of shared data in caches, reasoning about executions by different cores is not straight forward<sup>3</sup>. Replicated copies of data in different caches may not be up-to-date; accordingly, cores may have different views of shared memory locations. The first challenge is ensuring

<sup>&</sup>lt;sup>3</sup> "multiprocessor synchronization algorithms assume that each processor accesses the same word in memory, but each processor actually accesses its own copy in its cache. It hardly required a triple-digit IQ to realize that this could cause problems." – Leslie Lamport

that processors agree on the value returned by a read to a memory location – *coherence*. This is addressed by *cache-coherency* protocols [15] which ensure that all caches hold consistent data. The second challenge is determining when and in what order reads by processors can return values written to different memory locations – *consistency*. We cannot always assume that processors immediately observe changes in memory made by a given processor or that processors observe changes in the order they were issued.

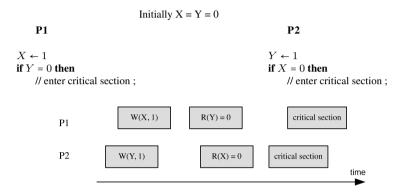

Figure 1.3: Simple algorithm for mutual exclusion

Figure 1.3 illustrates complications that can arise if processors do not have a consistent view of memory access operations. Assume that the processes P1 or P2 are running on different processors, the program should ensure that either process P1 or P2 executes the critical section, but not both. The programmer reasons about the correctness of the program by visualizing its execution, with each line of the program executed line-by-line in  $program\ order$  and that writes to a memory address are immediately visible to the other process.

However, if the writes are stalled or buffered and the processes allowed to continue with the next instruction, then memory accesses may appear reordered. P1 and P2 proceed to enter the critical section, before either write is effected in memory. *Memory consistency* models provide a formal specification on whether such executions are allowed. Essentially, consistency models act as a contract between the system hardware and the software on what access orders are legal when multiple processes access common locations.

Sequential Consistency proposed by Lamport [16] extends the programmers reasoning about line-by-line execution: it requires that memory accesses appear to execute one at a time in some global order, and memory accesses by a single process execute in program order. Sequential consistency guarantees that there is no ordering of instructions in Figure 1.3 where both P1 and P2 enter the critical

section. Writes have to be completed before continuing to the if statement.

Although sequential consistency offers a simple and intuitive programming model, it inhibits many compiler and hardware performance optimizations. Therefore, more relaxed (possibly inconsistent) memory models have been proposed offering substantial performance improvements [17]. Relaxed memory models call for the programmer to explicitly ensure correctness of the program using memory fences (or barriers) and atomic read-modify-write primitives to dictate the appropriate ordering of events.

Modern compiler optimizations may also reorder instructions leading to inconsistent behavior in multicores programs. Therefore, many programming languages provide memory consistency models and synchronization primitives. Explicit synchronization of execution events adds overhead to the execution and therefore should be used prudently to avoid performance degradation.

#### 1.1.2 Atomic Primitives

Modern multicore architectures provide various *read-modify-write* hardware primitives that can atomically read and modify an object in memory. An operation is *atomic* if it appears to complete in a single step or instantaneously to other processes. These atomic instructions are generally used as basic building blocks for implementing synchronization constructs in shared memory multicore systems. Figure 1.4 presents semantics of commonly available atomic primitives.

```

Test-and-Set(addr):

LOAD-LINKED(addr):

temp \leftarrow addr

addr \leftarrow 1

temp \leftarrow addr

mark \ addr

return temp

return temp

FETCH-AND-ADD(addr, val):

temp \leftarrow addr

⊳ called after LL

addr \leftarrow addr + val

\textbf{STORE-CONDITIONAL} (addr,val) \textbf{:}

return temp

if IsMarked addr then

COMPARE-AND-SWAP(addr, old, new):

addr \leftarrow val

if addr = old then

return true

else

addr \leftarrow new

return false

return true

else

return false

```

Figure 1.4: Pseudo-code definitions of common atomic primitives.

Architectures support and hardware implementation details may vary for the atomic primitives in Figure 1.4 in different platforms. Compare-and-Swap (CAS)

1.2. SYNCHRONIZATION 9

and Load-Linked/Store-Conditional (LL/SC) are *universal primitives* (details in Section 1.2.3), thus, can be used to construct simulations of arbitrary atomic read-modify-write operations including those listed in Figure 1.4.

In contrast to CAS, LL/SC pair verifies that the contents of memory address have not been modified, instead of verifying if contents at the address match a given value. This has significant benefits for the programmer using LL/SC over CAS in avoiding the ABA problem. The ABA problem arises as a consequence of the fact that matching the contents at a target address with a given value does not imply that no changes have occurred at the address. A concurrent process may have changed the contents of the address from A to B and then back to A. In some implementations this behavior is tolerable, however, in others, it may lead to incorrect results.

## 1.2 Synchronization

The need for synchronization arises in every area where multiple entities have to agree or commit to a given set of steps. In shared-memory multicore processors, synchronization is used to explicitly dictate which process interleavings are acceptable and prohibit those that are unacceptable. Synchronization is generally achieved by guaranteeing some notion of *atomicity*; a given sequence of instructions executed by a single process appears instantaneous to other processes.

Synchronization mechanisms are required to be scalable and correct. Scalability in this context implies that the cost of synchronization should not rise with increasing number of processes or threads. Correctness requires that the synchronization mechanism satisfy both *safety* and *liveness* properties. Informally, a safety property states that "bad" things never happen, while, liveness property (progress condition) states that "good" things eventually happen [11]. Schneider *et al.* [18] more formally define both properties.

Examples of safety properties are: (1) *Mutual Exclusion*: in any execution, at most one process is in the critical section – "bad thing" happening is two or more processes executing in a critical section. (2) *Deadlock Freedom*: if a process attempts to enter a critical section, then eventually some process executes inside the critical section – "bad thing" happening is a deadlock.

Examples of liveness properties include: (1) *Starvation Freedom*: a process makes progress infinitely often – the "good thing" is making progress. (2) *Livelock freedom*: processes do not run forever without progress – the "good thing" is at least one process makes progress.

Note that "good thing" and "bad thing" are not well-defined concepts; therefore, some properties are an intersection of both safety and liveness [18]. Fur-

thermore, without any notion of progress, a synchronization mechanism would be correct by halting all processes making it impractical. Similarly, liveness without safety is trivial but of little practical value.

#### 1.2.1 Blocking Synchronization

Atomicity is most commonly achieved by mutual exclusion using critical sections guarded by locks. At any point in time, at most one process executes instructions inside the critical section. A process that requests for a lock held by another process will block until the lock is released (by busy waiting or yielding), thus guaranteeing that instructions executed in the critical section appear *atomic*. There are relaxations of this requirement, where multiple processes are allowed to hold a lock and execute inside the critical section as long as no modifications are performed (*ReadWrite* locks).

However, locks are *blocking* - arbitrary delay (scheduling preemption, page-faults or cache misses) or failure of a process holding a lock blocks other processes from making progress. Additionally, if a few locks are used to protect large portions of the program (*coarse-grained*), they prohibit many executions that could have correctly run in parallel, thereby reducing parallelism. *Fine-grained* locking is more difficult to implement correctly; thus, care must be taken to avoid well-known pitfalls associated with locks:

- 1. **Deadlocks**: Circular dependencies might arise where a process  $P_1$  holding a lock  $L_1$  blocks waiting for a lock  $L_2$  held by another process  $P_2$ , while  $P_2$  is also blocked waiting on  $P_1$  to release  $L_1$ . Mechanisms to avoid deadlocks such as acquiring the locks in a specific order may have a significant impact on the synchronization overhead.

- 2. Priority Inversion: If processes share a processor with preemptive scheduling, a high priority process H<sub>P</sub> may have to yield the processor to a low priority process L<sub>P</sub> that holds a lock required by H<sub>P</sub>. A middle priority process M<sub>P</sub> that does not need the lock may preempt the low priority process leading to a priority inversion between high priority and middle priority processes [19]. The system resets on the Pathfinder mission to Mars popularized priority inversion [20].

- 3. **Convoying**: If a process holding the lock is arbitrarily delayed inside the critical sections, other processes that wish to enter the critical section queue up waiting for the lock to be released. When the lock is released, the queued threads form a *convoy* as they gain exclusive access to the critical section [14,21].

1.2. SYNCHRONIZATION 11

As a consequence of their blocking nature, liveness properties associated with lock-based synchronization are dependent on operating system scheduler [22]. Starvation-freedom and livelock-freedom are guaranteed only if no process executes inside the critical section forever, and a process that seeks to enter the critical section is granted access to the critical section unless another process is already in the critical section.

In an asynchronous shared-memory model, synchronization mechanisms are required to be resilient to arbitrary delays and failures of processes. Non-blocking synchronization does not rely on locks; therefore, the arbitrary delay or failure of any process does not cause delay or failure of other processes.

#### 1.2.2 Non-blocking Synchronization

Non-blocking synchronization techniques guarantee atomicity without mutual exclusion; consequently, they are resilient to pitfalls associated with mutual exclusion. Additionally, they do not incur significant performance degradation due to arbitrary process delay.

Generally, non-blocking techniques are optimistic; each process attempts to execute independently or locally for as long as possible and publish their modifications using atomic instructions. An optimistic execution of a process can be invalidated by a concurrent modification, at which point, publication of the modifications will fail, and the process will have to repeat the local execution.

In the literature, there are several levels of non-blocking progress guarantees:

- Wait-freedom [23] guarantees that every process continues to make progress regardless of delays or failures of other processes. Wait-freedom guarantees individual progress; combines non-blocking progress with starvation freedom.

- 2. *Lock-freedom* [24] guarantees that some process makes progress; ensures system-wide progress without starvation freedom.

- 3. *Obstruction-freedom* [25] guarantees that a process will make progress if executed in isolation for long enough (*i.e.*, no interruptions from concurrent processes). It does not guarantee progress under contention; starvation and livelocks may happen if processes are executed concurrently.

Strong progress guarantees such as wait-freedom may be required for systems with real-time constraints and resiliency requirements. However, they are non-trivial to achieve efficiently, thus, on modern shared-memory multicore systems, weaker progress guarantees such as lock-freedom and obstruction-freedom

generally suffice, and are easier to implement efficiently [26]. In contrast to wait-freedom and lock-free, obstruction-freedom is dependent on the scheduler.

#### 1.2.3 Power of Synchronization Primitives

Herlihy [23] constructed an infinite hierarchy of shared objects based on their ability to solve a classical distributed systems problem in an asynchronous shared memory system with n processes: wait-free consensus. Consensus is a coordination problem in which n processes, each with an initial input value unknown to the others agree on a common output value -decision. The decision value must be one of the input values. A consensus protocol is wait-free if every process completes in a finite number of its steps.

A consensus number  $C(\mathcal{O})$  of an object type  $\mathcal{O}$ , is the maximum number of processes for which wait-free consensus can be implemented using any number of objects of type  $\mathcal{O}$  and read/write registers. Wait-free consensus cannot be implemented in an asynchronous system using read/write registers for more than one process [27, 28]. Thus, the consensus number for read/write registers is 1.

An object is considered universal in a system of n processes if its consensus number is at least n ( $C(\mathcal{O}) \ge n$ ). Some consensus objects are universal in any arbitrary systems, thus, together with read/write registers, can be used to solve wait-free consensus for any number of processes, e.g., CAS or LL/SC.

In the wait-free hierarchy, an object at level l has consensus number l; and together with atomic read/write registers can implement any wait-free consensus object at level l or lower, but not objects at higher levels. Universal consensus objects are desirable in hardware and fundamental to non-blocking synchronization: any arbitrary shared object can be implemented wait-free if the hardware or programming language supports wait-free universal consensus objects.

#### 1.3 Concurrent Data Structures

Concurrent data structures are high-level abstractions for synchronized access to shared data. They are a fundamental component for building software systems to exploit parallelism available on multicore systems. Concurrent data structures are essentially adaptations of *abstract data types* (ADT) defined for sequential data structures to support concurrent operations.

Each object has a *sequential specification*, typically defined as a set of operations that can be executed on the object and a set of legal operation sequences. Each operation execution is specified by its pre- and post-conditions. A sequential object implementation is correct, if any operation called when pre-conditions

are true, terminates with correct post-conditions, and operation sequence is a subset of legal operation sequences.

Reasoning about concurrent operations is challenging. Firstly, we require that operations appear atomic, regardless of the execution interval between the invocation and response of the operation. Secondly, when operations issued by distinct processes overlap in time, it may be unclear in what order the operations take effect.

#### 1.3.1 Correctness of Concurrent Data Structures

Safety properties are used to specify the permissible order in which operations by concurrent processes appear to execute. There are various formalizations of this requirement such as Linearizability [12] and Sequential Consistency [13].

A *history* is a log of executions by concurrent processes. A history H is a finite or infinite sequence of operation invocations and responses. A history is sequential if; the sequence starts with an invocation and a matching response immediately follows each invocation. Not all histories are correct; a history is admissible or legal if it adheres to the object's sequential specification.

A history defines a partial order on the operations it includes. An operation  $op_1$  happens before the operation  $op_2$  in H (denoted:  $op_1 \prec_H op_2$ ) if the response to  $op_1$  precedes the invocation of  $op_2$ . Intuitively, the partial order imposes a notion of real-time ordering on the operations in H. Operations are considered *concurrent* if they are unrelated by partial order (neither  $op_1 \prec_H op_2$  nor  $op_2 \prec_H op_1$ ). A history H is concurrent if it contains at least one pair of concurrent operations.

**Linearizability** [12]: A concurrent object is linearizable if for every history H there exists a permutation S of all operations in H such that

- 1. S is sequential and observes the sequential specifications; and

- 2. For each  $op_1 \prec_H op_2$  then  $op_1 \prec_S op_2$ .

Thus, an execution is linearizable if there exists a sequential history S of operations in the execution that (1) respects the object's sequential specification, and (2) observes the *real-time* ordering of events at all processes. S is referred to as a *linearization* of H.

The sequence S may include a subset of pending operations. An operation may complete all modifications on an object but take arbitrarily long to return a response. Other operations on the object will observe the effects of the operation that is yet to return a response. Therefore, by definition of linearizability, there

exists a single instant in time –linearization point, between invocation and response where an operation appears to take effect.

A conventional approach to show that a concurrent execution is linearizable is to define a linearization point for every operation in the execution history. Intuitively, the order induced by a sequence of linearization points preserves the real-time ordering of non-overlapping operations.

Additionally, linearizability is composable; a composition of linearizable histories is linearizable. This property is fundamental; concurrent objects can be designed, verified and implemented independently then combined to make a larger object.

Linearizability strictly requires operations to observe real-time order for all processes. However, in some cases, the real-time order of events at different processes may not be significant. *Sequential Consistency* is a correctness condition that exploits this relaxation in precedence ordering of operations [13]. Formally, an execution is sequentially consistent if there exists a permutation  $\mathcal S$  of all operations in a concurrent history  $\mathcal H$  such that:

- 1. S is sequential and observes the sequential specifications; and

- 2. For each  $op_1 \prec_{H|p_i} op_2$  then  $op_1 \prec_{S|p_i} op_2$ .

Essentially, instead of preserving the real-time behavior of non-overlapping operations at all processes, it only preserves the program order of operations issued by the same process. Sequential consistency is a weaker condition than linearizability; every linearizable sequence is also sequentially consistent, but the reverse is not true. Additionally, sequential consistency is not composable. In order to enhance parallelism and performance, several relaxations of correctness conditions for concurrent data structures have been proposed [29–34].

The choice of synchronization mechanism to satisfy the safety properties of a concurrent data structure generally dictates the liveness or progress conditions associated with the data structure operations. Correctness can trivially be achieved using a single lock to guard the entire data structure (coarse-grained locking); however, this restricts parallelism and may lead to performance degradation. Multiple distinct locks can protect different portions of the data structure (fine-grained locking) leading to more efficient exploitation of available parallelism.

## 1.4 Non-blocking Concurrent Data Structures

Herlihy [23] presented general techniques for constructing a wait-free implementation of any sequential object (generally referred to as universal constructions). However, this approach is costly for practical purposes; the method requires copying the entire data structure for some operations and does not allow concurrent updates to the data structure. Consequently, tremendous effort has been made to construct more efficient and practical non-blocking data structures by exploiting specific semantics of the data structures [35–38].

A non-blocking update operation typically involves reading a memory location, taking steps *locally* based on the value returned by the read, and then modify the memory location using *read-modify-write* atomic primitives such as CAS (which compares the previously read value to the current value and only executes the modification if these are the same). The CAS only fails due to a concurrent modification<sup>4</sup>, in which case the steps are restarted. The execution time of a single operation cannot bounded as it may fail and retry arbitrarily.

Many concurrent data structures are represented as *linked* structures. Processes access the data structure through shared pointer variables to specific nodes in the link. The non-blocking concurrent queue by Michael *et al.* [39] is a classic example of this representation; processes access the link structure through either the *head* or *tail* pointers. Local steps start with allocating a new node and then entering a retry loop in which modifications are made to the new node based on the current state of the data structure, and an optimistic attempt is made to add the new node to the data structure if the a priori state as has not changed.

Memory allocation performed with linked structures results in significant memory management overheads. There are several memory management schemes proposed for programming environments without automatic garbage collection [40–47].

## 1.4.1 Design and Implementation Approaches

#### (A) Helping

In various implementations of non-blocking data structures [39,48–50], a modify operation may require more than a single atomic step to complete or to update multiple memory locations. Consequently, concurrent operations may observe the shared data structure in an inconsistent transient state. This inconsistency may

<sup>&</sup>lt;sup>4</sup>Success does not guarantee that there were no concurrent modifications as we explained in ABA problem (Section 1.1.2).

(1) block other operations from making progress, and (2) cost other operations extra steps (e.g., traversing nodes that are logically deleted).

Operations that observe the inconsistency, help complete the operation so that either they can ensure progress or that other operations do not pay that cost associated with the inconsistency. Helping was initially conceived for achieving wait-freedom [23]; it is also used in several lock-free implementations to coordinate access to shared data structures [39, 49, 51]. Censor-Hillel et al. [52] proposed a formal definition of help in wait-free algorithms based on linearization order: a process p helps an operation  $op_2$  by another process p if a step by p determines that  $op_2$  is linearized before some other operation.

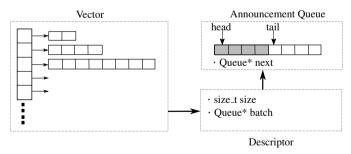

In many cases, helping necessitates that the helper has information about the operation that requires the help. Descriptor objects introduced in the cooperative technique by Barnes [51] contain sufficient information on a pending operation to allow concurrent threads to complete the operation. The main idea is to detach operations from the executing threads. Thus, if a thread  $t_1$  reads a descriptor allocated by another thread  $t_2$ , thread  $t_1$  can complete the pending operation ensuring system-wide progress. This approach is akin to locking, except that, instead of a thread owning a lock, the lock belongs to an operation. Thus, the delay of a thread does not block other threads from completing the operation.

Harris [48] introduced the idea of pointer-marking as a pragmatic solution for operations that require more than one atomic primitive to complete correctly. In his approach, a thread declares its intention to delete a node by marking the next pointer of the node to prevent concurrent operations from modifying the pointer. Then physically deleting the node from the list after.

**Challenges:** Helping may result in performance degradation for the data structure especially when read-only operations such as CONTAINS are compelled to perform writes during helping. These performance concerns have resulted in designs where read-only operations traverse data structure nodes while ignoring concurrent operations that would otherwise have solicited for help [50, 53–58].

Furthermore, pointer marking requires an atomically markable reference, which is expensive or unavailable in some programming languages. A typical mechanism for pointer marking involves utilizing some of the bits in the pointer value for distinguishing the pointer from the marked version of the pointer. Although this is an elegant and practical approach in programming languages such as C/C++, it is not portable to languages where the developer has no access to object references or pointers. Java introduced *AtomicMarkableReference* which maintains an object reference along with a mark bit, however, this is expensive as it utilizes internal objects which create an extra level of dereferencing. As critical components for exploiting multicore processors, designs of concurrent

data structures have to be portable; should not rely on architecture or language specific constructs.

#### (B) Synchronization Bottlenecks

If many threads attempt to modify a shared variable simultaneously, the resulting memory contention may lead to performance degradation, and the shared variable becomes a *hotspot* [59, 60]. The shared variable could be a lock for blocking synchronization or a global variable modified by atomic primitives in non-blocking synchronization [39, 61, 62]. Performance degradation is largely a result of cache invalidation as processes read and modify the shared variable.

Traditionally, *hotspots* in both blocking and non-blocking concurrent data structures are addressed by utilizing fine-grained synchronization. This approach fits naturally to data structures that allow concurrent access to different elements in the structure: bags [63], hash tables [64, 65], linked-lists [49, 57], skiplists [53, 66] and search trees [50, 54–56]. However, some data structures have inherent synchronization bottlenecks where contention cannot be trivially managed with fine-grained synchronization: queues [39,67], priority-queues [68, 69], and stacks [34,61,70]. A well-known approach to reducing contention is *backoff* [9,59,70,71].

Another popular technique to reduce synchronization bottlenecks is for a single process to combine and execute requests on behalf of other processes. Combining has several benefits: 1) eliminate memory contention due to "hotspot" shared variables, and 2) improved cache locality for the combiner thread. Combining was first introduced in software combining trees [72], where requests starting at the leaves of a static tree are combined up the tree. However, static combining trees imply that operations suffer significant synchronization overheads regardless of the level of contention. Combining funnels proposed by Shavit *et al.* [73] reduce the overheads by employing dynamic trees.

Oyama *et al.* [74] proposed a different approach to managing potential synchronization bottlenecks. A shared data structure is protected by a single lock and processes wishing to access the data structure announce their requests in a LIFO list structure. A process that acquires the lock executes in addition to its request, pending requests by other processes and then discards the list.

Hendler *et al.* introduced *flat-combining* [75]; in contrast to Oyama *et al.*, the announcement list typically contains one record per concurrent thread accessing it. If a thread accesses the list for the first time, it adds a record entry to the list which it uses to publish subsequent access requests. After writing each request, the thread attempts to acquire the global lock. A thread that acquires the lock (combiner) scans the list for pending requests, applies them to the

underlying data structure, and then writes responses back to the associated records in the list.

**Challenges:** Combining as well as flat-combining techniques are typically lock-based, and consequently blocking. Fatourou and Kallimanis presented universal constructions that use a FAA and an LL/SC object for implementing combining technique with wait-free progress guarantees [76]. The idea is to have a process that wants to execute an operation, find out which operations have been announced, apply these operations to a local copy of the object, then finally change the global object pointer to refer to this local copy. However, these constructions do not cope well with large shared objects as they copy the state of the object, then apply changes to the local copy. Fatourou *et al.* [77] presented algorithms for efficiently handling shared objects with large state size, however, these approaches include dedicated threads that apply updates to the data structure. Consequently, compromising the non-blocking progress guarantees in [76]. Therefore, it remains an open challenge to develop mechanisms for reducing synchronization overheads in concurrent data structures with inherent bottlenecks that cannot be trivially managed with fine-grained synchronization.

# 1.4.2 Concurrent Data Structures for Efficient Data Stream Processing

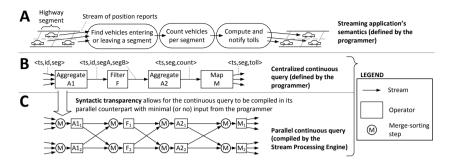

Interest in Data Stream Processing is a result of the unprecedented increase in volumes of data generated at high-rates that need to be processed in real-time. Stream Processing Engines (SPEs) are generally modeled as directed graphs where vertices are processing operators, and the edges are continuous streams of data between the operators. For example StreamCloud [78], Apache Storm [79], Apache Flink [80] and Saber [81]. *Parallelism* in SPEs is paramount for achieving *high-throughput* and *low latency* processing.

Pipeline and task parallelism are extracted naturally from the directed graphs with independent operators or tasks assigned to different processing units. However, data parallelization or fission [82–86], which involves replicating instances of operators careful orchestration of operators' execution is required to preserve *determinism*. Determinism is required to ensure consistent results independently of the way in which the analysis is parallelized.

Additionally, power consumption has gained significance as a metric for evaluating computing systems. Consequently, there is a growing trend towards efficient utilization of both general-purpose multicore architectures and low-power embedded multicore devices. Benefits of utilizing low-power embedded devices are two-fold: (1) can be deployed as edge and fog devices for close-to-the-source

analysis minimizing latency for time-critical applications, (2) they often provide increased performance per watt in comparison with traditional general-purpose multicore servers.

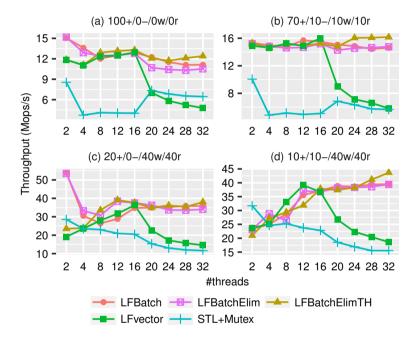

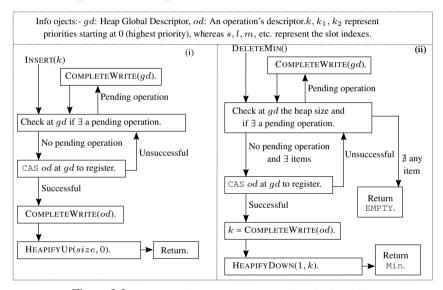

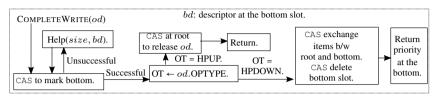

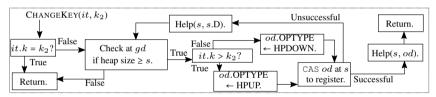

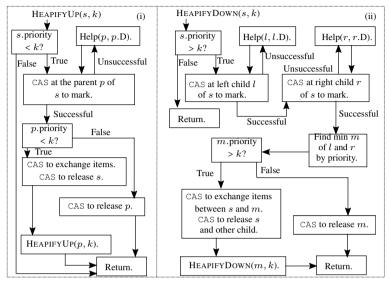

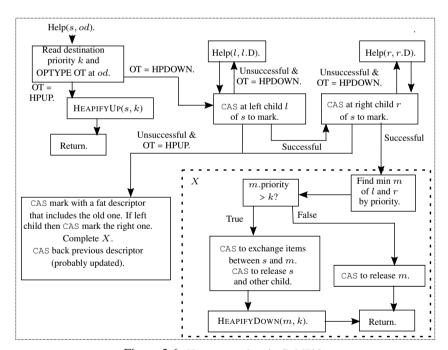

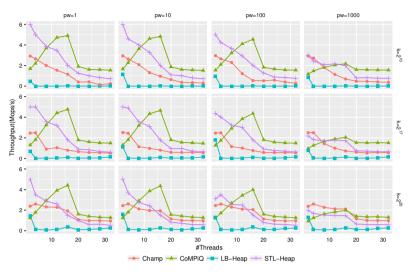

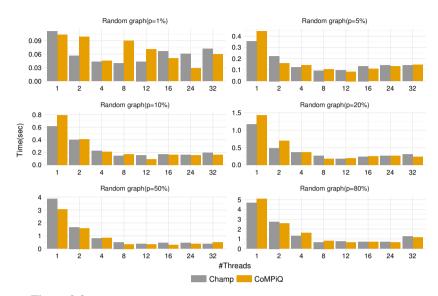

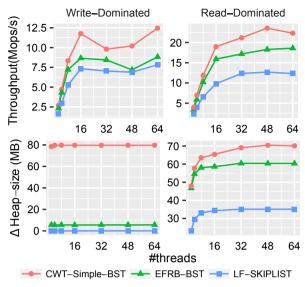

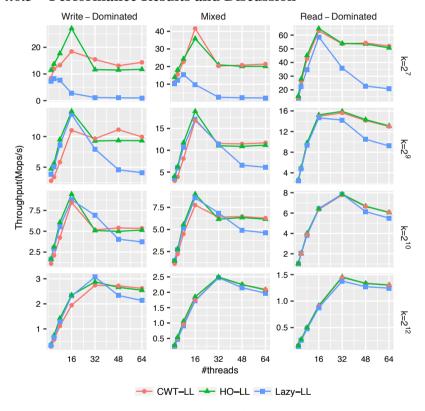

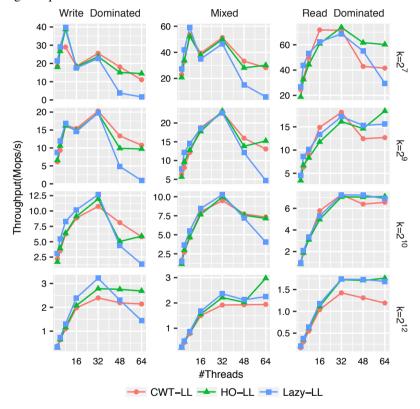

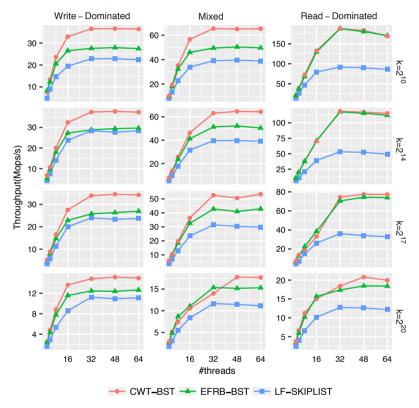

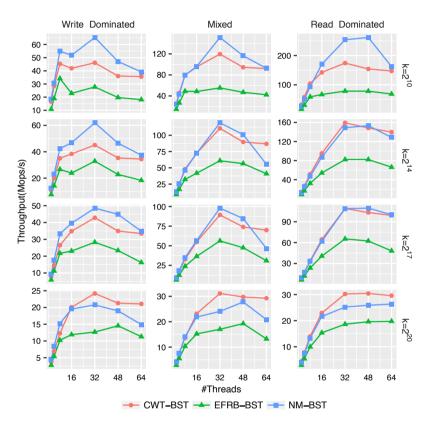

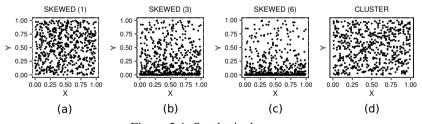

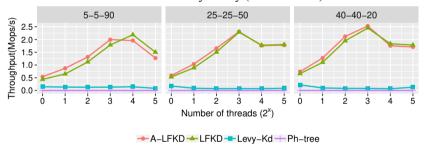

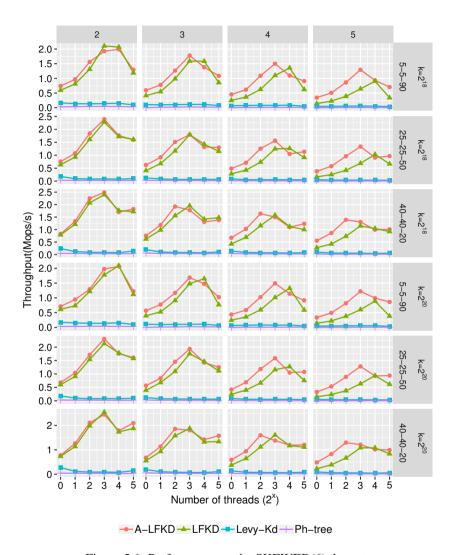

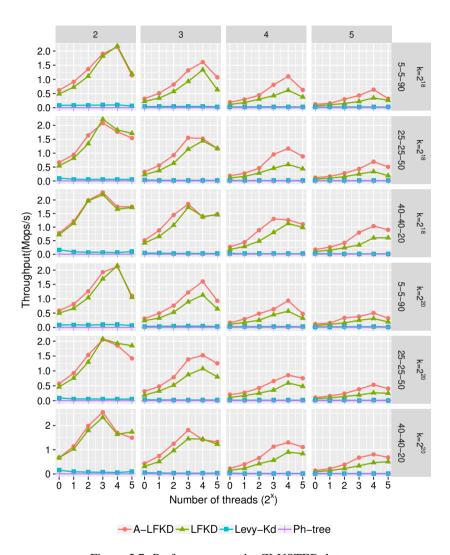

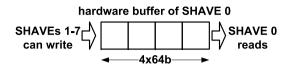

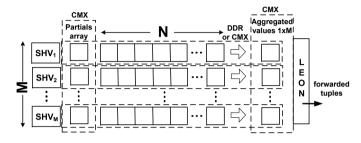

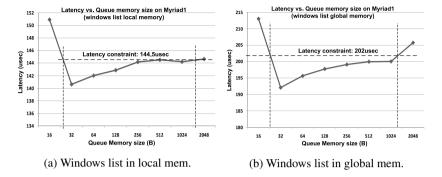

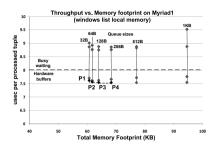

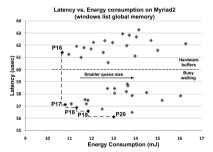

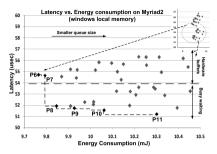

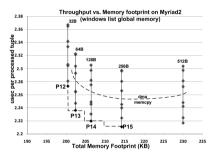

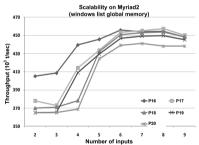

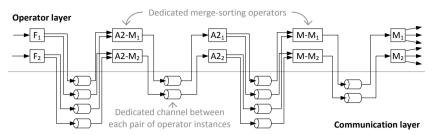

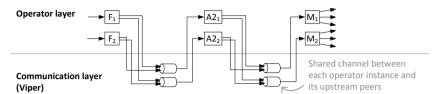

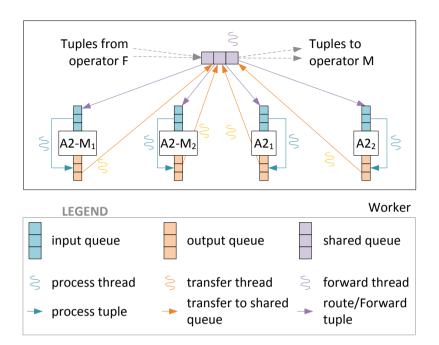

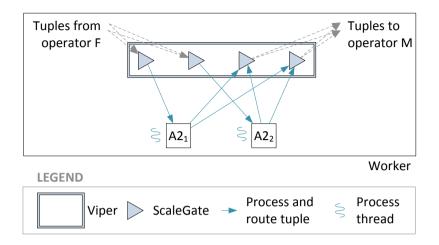

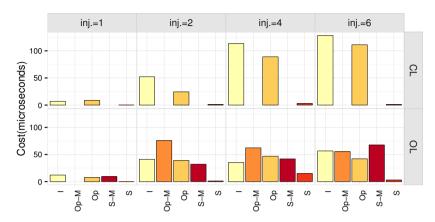

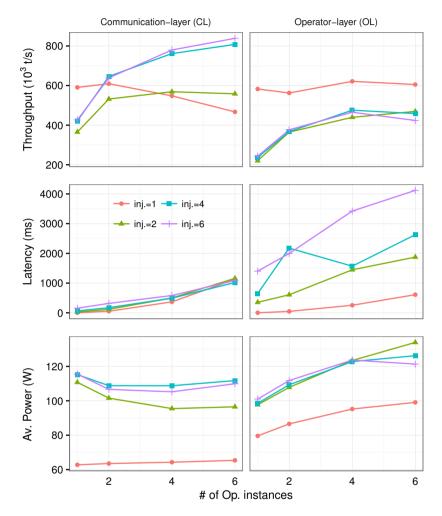

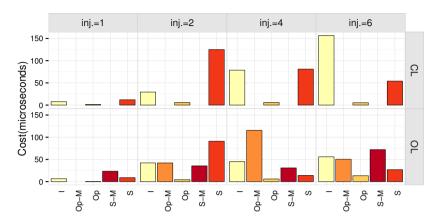

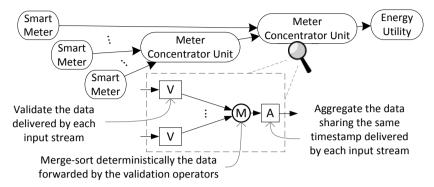

**Challenges:** Attempts to guarantee determinism in SPEs under execution of parallel instances of an operator rely on dedicated merge-sorting operators. These operators are either added to continuous queries by query compilers [78, 84, 85] or left for developers to place within their streaming applications in SPEs, such as Apache Storm [79]. Minimizing the computational overhead introduced by such dedicated operators is challenging, especially for one-at-a-time, fine-grained low latency tuple processing.