# Mikko Pänkäälä

Potential and Challenges of Analog Reconfigurable Computation in Modern and Future CMOS

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 187, December 2014

# Potential and Challenges of Analog Reconfigurable Computation in Modern and Future CMOS

## Mikko Pänkäälä

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Beta on December 5, 2014, at 12 noon.

University of Turku

Department of Information Technology &

Technology Research Center (TRC)

20014 Turun Yliopisto

### **Supervisors**

Adjunct Professor Mika Laiho Technology Research Center University of Turku FIN-20014 University of Turku Finland

Dr. Tech. Jonne Poikonen Technology Research Center University of Turku FIN-20014 University of Turku Finland

### Reviewers

Dr. Christopher M. Twigg

Department of Electrical and Computer Engineering

Binghamton State University of New York

PO Box 6000

Binghamton, NY 13902-6000

United States of America

Victor Manuel Brea Sánchez Department of Electronics and Computer Science University of Santiago de Compostela Edificio Monte da Condesa, Campus Vida 15782 Santiago de Compostela Spain

## Opponent

Associate Professor Ricardo Carmona-Galán Institute of Microelectronics of Seville (IMSE-CNM) Spanish National Research Council (CSIC) Parque Científico y Tecnológico Cartuja, Calle Américo Vespucio s/n 41092 Sevilla Spain

ISBN 978-952-12-3141-4 ISSN 1239-1883

## Abstract

In this work, the feasibility of the floating-gate technology in analog computing platforms in a scaled down general-purpose CMOS technology is considered. When the technology is scaled down the performance of analog circuits tends to get worse because the process parameters are optimized for digital transistors and the scaling involves the reduction of supply voltages. Generally, the challenge in analog circuit design is that all salient design metrics such as power, area, bandwidth and accuracy are interrelated. Furthermore, poor flexibility, i.e. lack of reconfigurability, the reuse of IP etc., can be considered the most severe weakness of analog hardware. On this account, digital calibration schemes are often required for improved performance or yield enhancement, whereas high flexibility/reconfigurability can not be easily achieved. Here, it is discussed whether it is possible to work around these obstacles by using floating-gate transistors (FGTs), and analyze problems associated with the practical implementation. FGT technology is attractive because it is electrically programmable and also features a charge-based built-in non-volatile memory. Apart from being ideal for canceling the circuit non-idealities due to process variations, the FGTs can also be used as computational or adaptive elements in analog circuits.

The nominal gate oxide thickness in the deep sub-micron (DSM) processes is too thin to support robust charge retention and consequently the FGT becomes leaky. In principle, non-leaky FGTs can be implemented in a scaled down process without any special masks by using "double"-oxide transistors intended for providing devices that operate with higher supply voltages than general purpose devices. However, in practice the technology scaling poses several challenges which are addressed in this thesis.

To provide a sufficiently wide-ranging survey, six prototype chips with varying complexity were implemented in four different DSM process nodes and investigated from this perspective. The focus is on non-leaky FGTs, but the presented autozeroing floating-gate amplifier (AFGA) demonstrates that leaky FGTs may also find a use. The simplest test structures contain only a few transistors, whereas the most complex experimental chip is an implementation of a spiking neural network (SNN) which comprises thousands of active and passive devices. More precisely, it is a fully connected (256 FGT synapses) two-layer spiking neural network (SNN), where the adaptive properties of FGT are taken advantage of. A compact realization of Spike Timing Dependent Plasticity (STDP) within the SNN is one of the key contributions of this thesis.

Finally, the considerations in this thesis extend beyond CMOS to emerging nanodevices. To this end, one promising emerging nanoscale circuit element - memristor - is reviewed and its applicability for analog processing

is considered. Furthermore, it is discussed how the FGT technology can be used to prototype computation paradigms compatible with these emerging two-terminal nanoscale devices in a mature and widely available CMOS technology.

## Tiivistelmä

Tässä työssä tarkastellaan kelluvahilaiseen transistoriin (FGT, Floating-Gate Transistor) pohjautuvan analogisen laskenta-alustan toteutettavuutta yleiskäyttöisillä erittäin pienen viivanleveyden CMOS-teknologioilla. Tyypillisesti analogiapiirien suorituskyky heikkenee, kun teknologiaa skaalataan pienemmäksi, koska skaalaukseen liittyy käyttöjännitteiden alentaminen. Lisäksi prosessiparametrit optimoidaan yleensä digitaalipiireille. Yleisesti ottaen analogiasuunnittelun haasteena on, että kaikki oleelliset suunnittelussa käytetyt mittarit, kuten teho, pinta-ala, kaistanleveys ja tarkkuus riippuvat toisistaan. Analogiapiirien heikkouksiksi voidaan lisäksi lukea heikko muunneltavuus, eli suunnitellut piirit eivät välttämättä sovellu suoraan uudelleen käytettäviksi yms. Tämän vuoksi analogiapiirien toimintaa korjataan usein digitaalisilla kalibrointiratkaisuilla suorituskyvyn ja/tai saannon parantamiseksi, kun taas analogiapiirien hyvä muunneltavuus on vaikeampi toteuttaa. Tässä työssä tarkastellaan voidaanko edellä mainitut analogiapiirien heikkoudet kiertää käyttämällä toteutuksessa kelluvahilaisia transistoreita ja analysoidaan käytännön toteutukseen liittyviä ongelmia. FGT teknologia on houkutteleva, koska sitä ohjelmoidaan sähköisesti ja siihen on sisäänrakennettu sähkövaraukseen perustuva haihtumaton muisti. FGT teknologia on ihanteellinen ratkaisu prosessivaihteluista johtuvien epäideaalisuuksien kumoamiseen, mutta sitä voidaan käyttää myös laskenta- tai mukautuvana elementtinä analogiapiireissä.

Kun mennään erittäin pienen viivanleveyden ( $<<1~\mu m$ ) prosesseihin, hilaoksidin nimellispaksuus ohenee niin paljon, että kelluvahilainen transistori alkaa vuotaa, eikä se enää kykene luotettavasti pitämään sähkövarausta muistissa. Periaatteessa vuotamattoman kelluvahilaisen transistorin toteuttaminen on suoraviivaista myös erittäin pienen viivanleveyden prosesseissa käyttämällä paksun hilaoksidin transistoria. Paksun hilaoksidin transistori on tarkoitettu sellaisten piirikomponenttien toteuttamiseen, joiden jännitekestoisuuden tulee olla parempi kuin yleiskäyttöisten piirikomponenttien. Käytännössä teknologian skaalaus aiheuttaa kuitenkin useita haasteita, joita käsitellään tässä työssä.

Riittävän kattavan otoksen saamiseksi skaalauksesta aiheutuvien ongelmien tarkasteluun, tätä tutkimusta varten toteutettiin kaikkiaan kuusi erilaista, kompleksisuudeltaan vaihtelevaa, prototyyppisirua käyttäen neljää eri erittäin pienen viivanleveyden prosessia. Tarkastelun painopiste on vuotamattomissa kelluvahilaisissa transistoreissa, mutta itsestään nollaavan FGT-vahvistimen (AFGA, Autozeroing Floating-gate Amplifier) avulla demonstroidaan miten myös vuotavia kelluvahilaisia transistoreita voidaan hyödyntää. Yksinkertaisimmat testirakenteet sisältävät vain muutaman transistorin, kun taas monimutkaisin siru on toteutus neuroverkosta, joka koos-

tuu tuhansista aktiivisista ja passiivisista piirielementeistä. Tarkemmin sanottuna toteutus on täysin kytketty (256 FGT synapsia) kaksikerroksinen virtasykäyksien avulla kommunikoiva neuroverkko (SNN, Spiking Neural Network), jossa hyödynnetään kelluvahilaisen transistorin mukautumisominaisuutta. Virtasykäyksien avulla kommunikoivan neuroverkon kompakti toteutus, jossa synapsien muovautuvuus riippuu neuronien lähettämien virtasykäyksien keskinäisistä ajoituksista (STDP, Spike Timing Dependent Plasticity), on tämän väitöskirjan yksi keskeisimpiä saavutuksia.

Väitöskirjan alkuosa käsittelee lähinnä CMOS teknologiaa, mutta kirjan lopussa näkökulmaa laajennetaan koskemaan myös uusia nanoskaalan piirielementtejä. Lähempään tarkasteluun otetaan yksi lupaava nanoskaalan piirielementti - memristori - jonka soveltuvuutta analogiaprosessointiin arvioidaan. Lisäksi tarkastellaan miten FGT-teknologian avulla voidaan testata laskentaparadigmoja, jotka ovat yhteensopivia näiden uusien kaksiporttisten nanoskaalan piirielementtien kanssa. Tämän lähestymistavan etuna on, että toteutuksessa voidaan käyttää kypsää ja laajasti saatavilla olevaa CMOS-teknologiaa.

# Acknowledgements

I wish to thank the University of Turku for providing me an interesting place to work and Turku Centre for Computer Science (TUCS) Graduate School for the support.

Professor Ari Paasio, you believed in me, accepted me as a postgraduate student and opened the door to the interesting world of science for me, so without you there would be no this book. I am truly grateful to Dr. Christopher M. Twigg and Dr. Victor M. Brea Sánchez for kindly reviewing this thesis. Especially Dr. Twigg examined the manuscript rigorously and gave very valuable critique which eventually led to significant improvements in the quality of the manuscript. I'm also very grateful to my supervisors Dr. Mika Laiho and Dr. Jonne Poikonen for generously contributing their time, reading my dissertation, providing excellent comments and suggestions, helping me with the measurements and particularly getting me past setbacks experienced in the finishing phase of the work.

I would like to thank all my current colleagues at the TRC and my former colleagues at the IT Department for their encouragement, support, assistance, influence and friendship. I have been privileged to work with many talented, really smart and exceptional individuals over these years. I have spent many long hours at the lab together with some of you desperately trying to finish the chip designs in time for the process runs. I bet that I will never forget that, nor cease being surprised that despite the hurry and tiredness most of the designed chips operate without reproach. Special thanks to Sami Nuuttila and Peter Virta for their patient assistance with the computers in spite of my obsession to always try to persuade the circuit design tools to do things no one in our lab has never tried before. In addition, Peter has done great job in preparing the required PCBs for the chip evaluations.

Last but not least, I want to express my sincerest gratitude to my ever loving wife, Katri, who has had to endure many things throughout this process and still has been with me every step of the way.

# Contents

| Li | st O                 | f Acronyms                                                | 1  |  |  |  |

|----|----------------------|-----------------------------------------------------------|----|--|--|--|

| 1  | Introduction         |                                                           |    |  |  |  |

|    | 1.1                  | The Role of Analog Circuits in Signal Processing          | 3  |  |  |  |

|    | 1.2                  | Programmable Analog Technologies                          | 4  |  |  |  |

|    | 1.3                  | Problem Description and Scope                             | 6  |  |  |  |

|    | 1.4                  | Structure and Contributions of the Thesis                 | 8  |  |  |  |

| 2  | Floa                 | ating-Gate Transistor                                     | 11 |  |  |  |

|    | 2.1                  | Basic Structure of the FGT                                | 11 |  |  |  |

|    | 2.2                  | Programming Methods                                       | 14 |  |  |  |

|    |                      | 2.2.1 Basics of Programming                               | 14 |  |  |  |

|    |                      | 2.2.2 UV Photo Injection                                  | 17 |  |  |  |

|    |                      | 2.2.3 Fowler-Nordheim Tunneling                           | 17 |  |  |  |

|    |                      | 2.2.4 Hot Electron / Hole Injection                       | 20 |  |  |  |

|    | 2.3                  | Performance Aspects of FGTs                               | 27 |  |  |  |

|    | 2.4                  | FGTs and Circuit Simulators                               | 29 |  |  |  |

| 3  | Mig                  | grating FGTs to Deep Sub-Micron Standard CMOS pro-        |    |  |  |  |

|    | cess                 | ses                                                       | 31 |  |  |  |

|    | 3.1                  | Low-Power Subthreshold Electronics                        | 31 |  |  |  |

|    | 3.2                  | Implementing FGTs in DSM CMOS — Getting Started $$        | 35 |  |  |  |

|    | 3.3                  | Feasibility of Programming Methods in DSM CMOS            | 36 |  |  |  |

| 4  | Experimental results |                                                           |    |  |  |  |

|    | 4.1                  | Test Chips 1 and 2                                        | 41 |  |  |  |

|    |                      | 4.1.1 FGT Implementation in 0.18 $\mu$ m CMOS             | 41 |  |  |  |

|    |                      | 4.1.2 FGT Implementation in 130 nm CMOS                   | 45 |  |  |  |

|    | 4.2                  | An FGT Current Source Implemented in a 90 nm CMOS $$      | 46 |  |  |  |

|    |                      | 4.2.1 Measured data                                       | 49 |  |  |  |

|    | 4.3                  | A Thin Oxide AFGA Implemented in a 65 nm CMOS $\ .\ .\ .$ | 54 |  |  |  |

|    | 4.4                  | Constant Charge Injection Implemented in 130 nm CMOS      | 60 |  |  |  |

| <b>5</b> | Introduction to Spiking Neural Networks |         |                                                  | 67           |     |

|----------|-----------------------------------------|---------|--------------------------------------------------|--------------|-----|

|          | 5.1 Background                          |         |                                                  |              | 67  |

|          |                                         | 5.1.1   | Human brains                                     |              | 68  |

|          |                                         | 5.1.2   | Neuron                                           |              | 69  |

|          |                                         | 5.1.3   | Synapse                                          |              | 70  |

|          |                                         | 5.1.4   | Spiking Neural Network                           |              | 72  |

|          |                                         | 5.1.5   | STDP                                             |              | 73  |

| 6        | $\mathbf{FG}$                           | T Imp   | lementation of SNN                               |              | 75  |

|          | 6.1                                     | Floati  | ng-gate Transistor Based SNN                     |              | 75  |

|          |                                         | 6.1.1   | Motivation                                       |              | 75  |

|          |                                         | 6.1.2   | Implementation                                   |              | 77  |

|          |                                         | 6.1.3   | Experimental Results of the Synapse              |              | 98  |

|          |                                         | 6.1.4   | Experimental Results of the Charge Pump          |              | 106 |

|          |                                         | 6.1.5   | Experiments with the Array                       |              | 109 |

| 7        | Em                                      | erging  | Analog Computational Elements Beyond CM          | 10S          | 113 |

|          | 7.1                                     | Memr    | istor                                            |              | 114 |

|          |                                         | 7.1.1   | Definition and Operation Principle               |              | 114 |

|          |                                         | 7.1.2   | Implementing functionalities with Memristors - F | Re-          |     |

|          |                                         |         | flections on the System Level                    |              | 116 |

|          |                                         | 7.1.3   | Applications to Analog Computation               |              | 118 |

|          |                                         | 7.1.4   | FGT vs. Memristor                                | . <b>.</b> . | 120 |

| 8        | Cor                                     | nclusio | ns                                               |              | 123 |

# List Of Acronyms

ADC Analog-to-Digital-Converter

AER Address-Event-Representation

AFGA Autozeroing Floating-gate Amplifier

ANN Artificial Neural Network AR Auger Recombination

ASIC Application Specific Integrated Circuit

ASP Analog Signal Processing/Processor

CHE Channel Hot-Electron

CHH Channel Hot-Hole

CMOL CMOS/Molecular Hybrid

CMOS Complementary Metal Oxide Semiconductor

DAHC Drain-Avalanche Hot-carrier

DC Direct Current

DCT Discrete Cosine Transform

DRC Design rule Check DSM Deep sub-micron

DSP Digital Signal Processor DST Discrete Sine Transform ESD Electrostatic Discharge

FG Floating-gate

FGT Floating-gate Transistor F-N tunneling Fowler Nordheim tunneling

FPAA Field Programmable Analog Array FPGA Field Programmable Gate Array

FPNI Field Programmable Nanowire Interconnect

I-F Integrate-and-Fire

IIHEI Impact Ionized Hot-Electron Injection

IO Input Output

LFBGA Low profile Fine pitch Ball Grid Array

MAC Multiply Accumulate operation MITE Multi Input Translinear Element  $\label{eq:mim-capacitor} \mbox{MIM-capacitor} \mbox{ Metal-Insulator-Metal-capacitor}$

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MRAM Magnetoresistive Random Access Memory

MUX Multiplexer

NDA Non-disclosure Agreement OpAmp Operational Amplifier PDK Process Design Kit

PRAM Phase Change Random Access Memory

RF Radio Frequency SC Switched Capacitor

SGHE Secondarily Generated Hot-Electron

SHE Substrate Hot-Electron

SNN Spiking Neural Network

SNR Signal-to-noise ratio

SoC System on a Chip

STDP Spike Timing Dependent Plasticity

TDDB Time Dependent Dielectric Breakdown

UV Ultraviolet

VLSI Very Large Scale Integration

## Chapter 1

## Introduction

# 1.1 The Role of Analog Circuits in Signal Processing

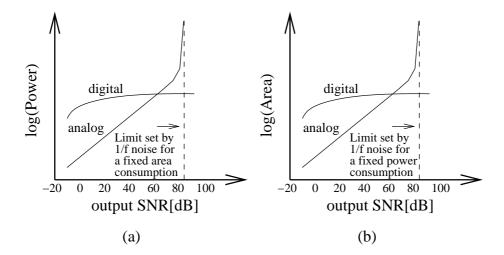

In today's modern affluent society, we are surrounded by a myriad of electronic devices such as digital cameras, mp3 players, cellular phones, laptops and digital TVs. Ubiquitous digital gadgets may easily mislead one to conclude that analog circuits have completely vanished. This illusion stems from labeling a product with a "digital" prefix, e.g. a digital camera, which simply means that it has a digital signal processor (DSP) and information is stored in a digital format. The word digital is often used as a marketing argument, to highlight the efficiency and ease of use of the product. However, a good commercial product can rarely be made with a successful digital design only. A "digital" product often includes a surprising number of analog circuits. For example, DSP manufacturer Texas Instruments stated that for every DSP in an electronic system, there are approximately ten analog components [1]. Indeed, analog circuits are needed as an interface between digital processing and the external world. In this context, the interface circuitry covers tasks like transforming the sensed quantity (for example photons or acoustic waves) into a useful electronic magnitude (for example voltage, current, charge or frequency). Other analog tasks include filtering, data conversions, and transforming an electronic signal back to perceivable signal (for example movement, sound or light intensity). In that sense, analog components are an essential and irreplaceable part of the "digital" systems.

It is not absolutely necessary to visit the digital domain between the analog input and the analog output. However, in practice, this is usually the case at least if more or less a "general purpose" signal processor is considered. This is simply because digital hardware is more flexible than analog hardware. Due to the better flexibility, the implementation of algorithms is

often more straightforward, and for example precision can be adjusted according to the requirements. For some applications, a Field Programmable Gate Array (FPGA) or an Application Specific Integrated Circuit (ASIC) may be a better solution than a DSP. The choice between different processing platforms depends on specifications like power budget and die area constraints. Other factors include the processing architecture (for example serial or parallel) and resources (time and money) that are devoted in the project. Whatever the case, programmability, scalability over different technology nodes, computational accuracy and immunity to noise are properties hard to achieve with analog design. Consequently, Analog Signal Processors (ASPs) are rarely seen on commercial systems, but DSPs are the de facto industry standard. However, in some special cases it can be beneficial or even necessary to rely on ASP instead of DSP. For example, in very highspeed or in very low-power applications the extra data conversions (analog to digital and then back to analog) can be too expensive in terms of delay or power consumption. Nevertheless, it is very unlikely that ASP would widely replace DSPs in the near future, but rather complement them.

Programmable analog signal processors have been successfully implemented, for example the Field Programmable Analog Array (FPAA) [2]. FPAAs have their disadvantages and limitations, as explained in later chapters, which prevents their use as a general purpose computing platform in complicated systems. However, analog circuits have dominated in the implementation of many types of neural networks, because many of the algorithms and functions used in this field map nicely and efficiently to analog hardware. Data processing in neural networks is also organized so that it works even if the elementary processing elements have high noise and low accuracy, which is common to low power, small area analog circuits.

### 1.2 Programmable Analog Technologies

An implementation of an analog Discrete-Cosine-Transform-processor (DCT) was previously studied by the author [3, 4]. In this work, the accuracy of the transistors was identified to be the most serious roadblock for the implementation of a DCT-based motion estimation algorithm. Accuracy enhancement can be achieved simply by using large devices at the cost of silicon area and increased power consumption due to a larger capacitive load.

An alternative to spending more area is to fine-tune the transistors after fabrication for better accuracy. This can be realized by offloading the accuracy constraints to a digital processor, a technique which is commonly known as "digitally assisted analog circuits". The feasibility of this design technique improves with technology scaling, but needs some hardware overhead for data processing and storing the configuration bits (ideally to a non-

volatile digital memory). As an example this technique has been applied to the performance enhancement of Analog-to-Digital-Converters (ADC) and Digital-to-Analog-Converters (DAC) [5].

On the other hand in [3, 4], reconfigurability was also identified to be an important feature that greatly improves the reuse of designed analog circuit blocks. For example, besides DCT the same analog circuit could be used for implementing the Discrete-Sine-Transform (DST) if the coefficients were programmable. Reconfigurability was seen as such an important feature that it eventually led to the exploration of programmable analog technologies.

There are a few technologies for adding programmability to the analog hardware. In this context, programmability means the ability to repeatedly reconfigure the design to implement different functionality and / or to improve the performance by changing the operation point of the transistor(s). This definition excludes traditional post fabrication programming methods like laser trimming, which can be done only once. Post fabrication methods are mainly used for example to cancel mismatches for improved accuracy, or to enhance yield in general. Over the years, there have been many attempts to realize an analog counterpart to the FPGA. Many of these attempts are based on switched Capacitors (SC) accompanied with operational amplifiers (OpAmp). Another technology providing means to achieve reconfigurable analog hardware is the Floating-Gate Transistor (FGT).

The FGT technology provides the basis for the billion dollar flash-memory business, a memory type that is widely used for storing information in any application where compact size and non-volatility are appreciated. The programming of FGTs involves manipulating the charge stored on the floatinggate. This manipulation is effectively done by utilizing quantum mechanical mechanisms like electron tunneling and hot electron injection. In fact, FGT technology is currently in practice the only viable alternative to implement a non-volatile memory in CMOS. Besides digital memory applications, the FGTs can also act as programmable analog computational elements (with intrinsic analog memory feature). In practice, this extension to analog applications is achieved simply by increasing the programming resolution of the FGT from two separate states to a continuum of states. For example, the above-mentioned FPAAs are based on floating-gate technology. FGTs allow for more versatile and compact designs as compared to SC-OpAmp designs. However, there are fundamental difficulties in realizing a truly versatile high performance FPAA, such as the granularity of the building blocks and the influence of routing on performance.

A more recent technology for nonvolatile storage is the memory resistor, or memristor for short, which also enables reconfigurable designs. Although, the theoretical model for the memristor was introduced already in 1971 [6], the physical implementation of this component was successfully linked to the memristor theory just recently [7]. The article in Nature drew a

lot of attention and got more researchers involved. As a result, plenty of academic resources were rapidly devoted to investigating new architectures and applications for the memristor.

Besides memristor, there are other emerging devices rushing to market like Phase Change Random Access Memory (PRAM) [8] and Magnetoresistive Random Access Memory (MRAM) [9] which are capable for storing (non-volatile) their current state. These emerging devices are primarily seen as candidates for non-volatile digital memory applications which can potentially replace the dominant flash memory in the future. However, some of these devices may serve as programmable analog computational elements as well, likewise FGT. There are already many proposals in the literature how to use memristors for analog computation. Most of these new devices are two-terminal thin film structures and their operation principle is essentially based on manipulating the resistivity of the material. From this follows, that their usage as computational elements requires a paradigm shift from the traditional computation architectures which are based on three-terminal (four-terminal, if the bulk terminal is counted in) transistors.

This thesis aims to explore the limitations and opportunities on realizing programmable analog hardware in CMOS, focusing on FGT technology. However, since FGTs share many essential characteristics with memristors, also many design aspects are similar. Furthermore, it is possible to configure an FGT device to be virtually a two-terminal device the channel conductance of which can be electrically manipulated. Therefore all future two-terminal devices based on resistivity change can be mimicked with FGT devices and consequently the CMOS-based FGT technology allows the exploration of computation architectures which are compatible with these emerging devices. To this end, as a case study, a compact realization of Spike Timing Dependent Plasticity (STDP is a biological learning method) is proposed and implemented on CMOS-based FGTs that are configured as two-terminal memory devices. Therefore, in this respect the considerations in this thesis extend beyond CMOS, to memristor-based analog hardware. It is likely that memristive memories will be available as CMOS add-ons.

### 1.3 Problem Description and Scope

There are many research groups who are actively using FGTs in their analog circuits. Most of the research related to the usage of FGTs in analog design is based on the seminal research conducted by Caltech professor Carver Mead, whose students have continued to make good use of the properties of FGTs and gained significant progress for example with the programming framework and extending the application domain.

FGTs are not typically included in the characterization process provided by the foundry. For a previously uncharacterized process, certain empirical parameters are unknown, as is the case with the examined processes in this Therefore, before one can concentrate on designing effective and reliable solution for a given problem, taking full advantage of the properties of FGTs, one should characterize the accessible CMOS process kit very well. The characterization is challenging with an academic budget, as taking into consideration that prototyping especially with deep sub-micron technologies is time-consuming and expensive. As devoting one process run just for device characterization in each new technology is not practical, the emphasis in this study is on experimenting with floating-gate devices without first trying to characterize the process kit. Consequently, the focus is on solving lowlevel problems rather than developing high performance circuits. In practice the most important goal throughout this study has been to have functional FGTs in general. The design is based on intuition and information extracted by interpolation from other processes and studies. From this point of view, the most relevant questions are: What kind of problems will be faced when designing FGT-based circuits using modern sub-micron processes and how to act in the absence of empirical parameters?

A typical System on a Chip (SoC) includes many analog components that must be placed on the same chip due to integration benefits. Despite this, modern general purpose CMOS processes are designed and optimized to support mainly digital designs. The effort to increase the performance of digital hardware is the strongest technological driver and the performance of the analog hardware is secondary. On this account, CMOS analog computation is facing increasingly difficult problems the deeper one proceeds into sub-micron technologies [11].

One of the most essential and fundamental properties of the FGT is the non-volatility of the charge stored on the floating-gate. A metric that is used to evaluate the non-volatility is the retention time. Memory cell's ability to retain charge is dictated by the oxide thickness. That is, only thick enough gate oxide guarantees non-volatility. The nominal gate oxide has become thinner when the CMOS processing technology has evolved toward smaller line widths. This is the main reason (in addition to cheaper manufacturing costs) for using a relatively old technology to implement FGTs.

Retention time that is considered to non-volatile operation is ambiguous in analog memory applications: retention time must be coupled to the allowed amount of error over the examined time period to provide meaningful measure when analog FGT memory cells are considered. However, non-volatility is a term that is frequently used in the literature. In general, the non-volatility and the long-term charge retention are associated to time scales supported by the natural gate oxide thickness roughly down to 0.25 micron technology node. Below this technology node the gate leakage cur-

rent grows rapidly and the retention times decrease accordingly. In this case the term quasi-/pseudo- or semi-floating-gate transistor is often referred to.

In general, research concentrating on non-volatile FGTs is typically implemented with 0.25 micron or older processing technology, whereas pseudo-FGTs are implemented with 0.18 or newer technology. It is also possible to use denser than 0.25 micron technology to implement non-leaky FGTs, since many foundries provide possibility to use thick oxide devices along with thin oxide devices within certain manufacturing rules. The implementation of (mainly) non-leaky FGTs in a modern deep sub-micron general purpose CMOS process is discussed in this thesis. Various aspects of the restrictions posed by the processing technology itself are discussed. For example, certain amount of energy is required in order to manipulate the charge stored on the floating node of the FGT, so that, the thicker the oxide the more energy is required. To achieve a sufficient energy level during the charge manipulation, the gate oxide of the non-leaky FGT must be exposed to harsh electrical stress - a situation that is usually avoided with regular transistors to prevent transistors from breaking down prematurely. For electron tunneling and injection it is necessary to use voltage levels far beyond the nominal supply rails. Either off-chip or on-chip voltage sources can be used to provide the required high voltages. However, an intention to use an off-chip voltage source is typically poorly supported by the IO-cell library provided by the foundry. Also, it can be challenging to implement high-voltage tolerant switches in a given technology for internal routing of the high voltages to a desired target. This thesis provides practical solutions as to how one can try to solve such issues.

### 1.4 Structure and Contributions of the Thesis

This thesis is organized into eight chapters. Chapter 2 provides the reader background information, definitions, terminology and concepts related to the floating-gate transistors frequently used in later chapters of this thesis. Chapters 3, 4 and 6 are devoted to considering the actual problem description. Chapter 3 focuses on discussing the compatibility issues of FGTs with the deep sub-micron technologies in general whereas in chapters 4 and 6 the approach is more application oriented. Chapter 4 deals with FGT circuits which are relatively simple, whereas the prototype chip studied in Chapter 6 is much more complex. Namely, the introduced chip is a complete learning system, where FGTs have a key role as they operate as synapses in a Spiking Neural Network (SNN). Chapter 5 provides a brief introduction to biological and artificial neural networks. It is included into this thesis for sake of consistency and to equip the reader with sufficient preliminary knowledge with respect to Chapter 6. The conducted application oriented study is

supported by the experimental data collected from various prototype chips manufactured with different process nodes. More precisely, experimental tests comprise the following technology nodes:

- 0.18  $\mu$ m, one test chip

- 0.13  $\mu$ m, two test chips

- 90 nm, one test chip

- 65 nm, two test chips

All test chips were implemented with the processes provided by the same foundry. That is, the study offers consistent and comparable data between different process nodes from one foundry. The complexity of the test structures range from a single FGT with all terminals directly connected to respective IO-pads to two layer neural network with 16 neurons in both layers, 256 synapses with interface and auxiliary circuits. Unfortunately, all test chips were not fully functional due to different reasons so that all potentially available measurement data could not be extracted. Extracted measurement data per test chip varies also depending on the implemented test structure itself and applied programming method. Obtained measurement data is compared with simulated data.

In chapter 7, the focus is on emerging devices and their linkage to FGT technology. The discussion concentrates particularly on memristor devices which could potentially replace FGTs in many applications in the future. For the sake of consistency, memristor's potential to replace flash memory and penetration to other digital applications or signal processing in general is also briefly considered.

Finally, the most important findings made in this thesis with associated conclusions are summarized in the last chapter. This monograph contains mostly previously unpublished research results. Due to the focus of this thesis, the individual prototype chips presented in this thesis are mainly very simple and do not implement complex signal processing or similar tasks. That is the reason why only part of the prototype chips is reported outside this thesis. However, all information obtained from experimental prototype chips has been invaluable in creating an overall picture of the feasibility of implementing FGTs in deep sub-micron processes.

## Chapter 2

# Floating-Gate Transistor

A MOSFET with an extra electrical insulation (capacitor) forms a double gate (gates are in series) device which is called a floating-gate transistor. The first experiments on a MOSFET with an insulated gate date back to 1960 [12]. Since then, floating-gate technology has evolved along two different paths. One path has concentrated on how to use FGTs for binary storage. The other path has investigated how to use FGTs as a computational element in analog circuits. Either way, the charge modification requires electrons to be transported through an insulator (normally SiO<sub>2</sub>), which is quite a tricky task and necessitates that certain circumstances are met depending on the method to be used. The performance optimization of an FGT based binary memory has led to the adoption of specialized process options which enables very dense non-volatile binary memory arrays. Currently, there are no process options available which would have been specially designed for implementing analog FGTs, but some process features like double poly layers facilitate the utilization of certain programming techniques. In this thesis, only single poly processes are considered, which means that the discussion is more general and independent of this process option.

The non-disclosure Agreement (NDA) with the process foundry prevents revealing the non-public technological details related to the manufacturing process. Due to this, the evaluation of numerical values is not possible for all equations presented in this thesis. One essential parameter related to FGT technology is the thickness of the gate oxide layer  $t_{ox}$ . Nominal  $t_{ox}$  of thick oxide devices is less than 6 nm for all technology nodes discussed in this thesis.

### 2.1 Basic Structure of the FGT

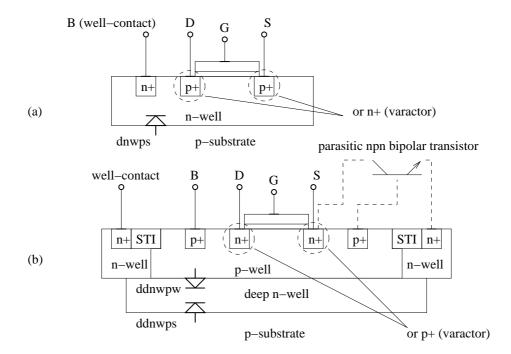

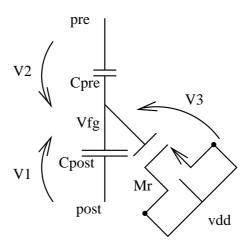

A floating-gate transistor is a device with a capacitively coupled gate (see Fig. 2.1). In other words, the gate has no direct connections to any other

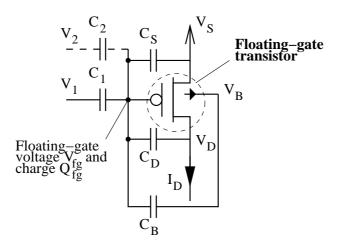

Figure 2.1: Simplified schematic of a single p-type FGT. Charge  $(Q_{fg})$  stored on the floating-gate defines the threshold voltage of the FGT.  $C_1$  and  $C_2$  are capacitive inputs and  $C_D$ ,  $C_S$  and  $C_B$  are internal capacitances.

conductors, but is connected to at least one capacitor. Because the actual gate of the transistor is floating, the extra capacitors are usually referred to as control gates. It is instructive to think of this circuit as a basic transconductance amplifier with a capacitive divider in its gate. The capacitive division,  $\kappa$ , is defined as  $\frac{C1}{C_{tot}}$ , where C1 is the input capacitance and  $C_{tot}$  the total capacitance connected to the floating-gate, respectively.

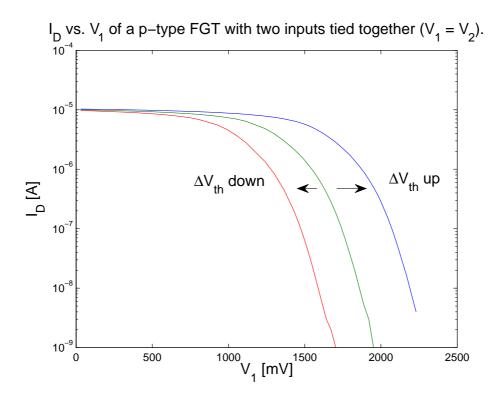

It is possible to change the potential on the floating-gate either by capacitively controlled signals or by changing (programming) the charge stored on the gate capacitance. Charge modification is only possible by moving charge carriers (electrons or holes) through the gate insulator. The programming effectively changes the threshold voltage  $V_{th}$  of the transistor (see Eq. 2.1 and Fig. 2.2), thus providing means to change the biasing of the transistor, which in turn enables FGT to be used as a computational element. The effective change of  $V_{th}$  from the perspective of the control gate is given by

$$\Delta V_{th} = \pm \frac{\Delta Q_{fg}}{C_{tot}} \tag{2.1}$$

where  $V_{th}$  is the threshold voltage of the FGT and  $Q_{fg}$  is the charge at the floating-gate. The sign of equation is – for the n-type FGT and + for the p-type FGT respectively <sup>1</sup>.

The quality and the thickness of the insulators surrounding the floatinggate define the leakage rate of the charge, i.e. the retention time. Even if a memory element is considered non-volatile, the retention time (powered

<sup>&</sup>lt;sup>1</sup>Here, the charge  $Q_{fg}$  is assumed to be positive.

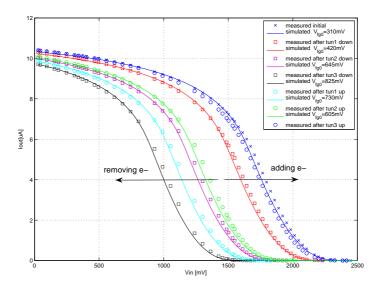

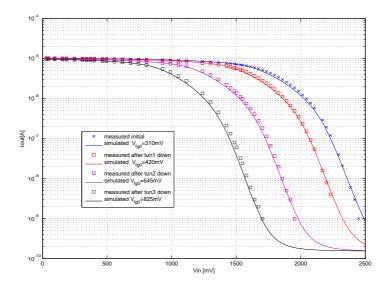

Figure 2.2: Measurement data with a similar setup to that of Fig. 2.1 showing how the programming changes the effective threshold voltage  $V_{th}$  of the FGT and how the shift reflects to the  $I_D$  vs.  $V_{GS}$  curve. Data obtained from a prototype chip manufactured in a 90 nm CMOS process. FGTs are made of thick oxide transistors.

or unpowered FGT) is always finite because of the finite resistivity of the insulator (gate oxide). The retention time dt can be derived from Eq. 2.1.

$$i_{Gtot}dt = \pm C_{tot}dV_{th} \tag{2.2}$$

where  $i_{Gtot}$  is the sum of gate currents (leakage). From Eq. 2.2 it becomes apparent that the retention time is related to some allowed value  $dV_{th}$  for the threshold voltage shift. Ideally, the preset charge remains nearly unchanged even for years if the power supplies are shut down, hence the name non-volatile memory.

The number of capacitors connected to the floating-gate is dependent on the chosen programming scheme as well as the number of inputs connected to the gate. In general, an FGT has only one actual input, but typically the programming requires connecting more than one capacitor to the floatinggate, therefore it is more useful to mathematically examine the multi-input FGT. By connecting more input capacitors to the floating-gate the result is a Multiple Input Translinear Element (MITE) [13]. Effectively, a MITE produces a drain current that is related to a weighted sum of its input voltages according to Eq. 2.3.

$$\Delta V_{fg} = \frac{Q_{fg} + C_D \cdot V_D + C_S \cdot V_S + C_B \cdot V_B + \sum_{i=1}^n \Delta V_i \cdot C_i}{C_{tot}}$$

(2.3)

where  $V_{fg}$  is the floating-gate voltage,  $V_{D/S/B}$  and  $C_{D/S/B}$  are respective terminal voltages and capacitances that are assumed to be constant <sup>2</sup>. Well-capacitance and well-bias can be considered to be one of the inputs. Now, the change in  $V_{fg}$  can be used to evaluate the respective change in drain current  $I_D$  according to the standard  $I_D$  versus  $V_{GS}$  equations.

Basically, an FGT can be either n-type or p-type. However, while both types are functionally similar, n-type transistors are not so well suited for some of the programming methods as explained in the next section. This is the reason why p-type FGTs are often preferred. For, example all FGTs presented in this thesis are p-type devices.

### 2.2 Programming Methods

The purpose of this section is to provide necessary information for the reader to facilitate the understanding of circuit topologies presented in the following chapters. Principles of different programming methods are discussed, and their usability on a general level is estimated. From this perspective, it is not necessary to go deeply into the physical mechanisms that these methods are based on, nor detailed mathematical models. A selected set of programming methods presented in this section is examined in more detail in Chapter 3, and verified through experimental measurements in Chapter 4.

### 2.2.1 Basics of Programming

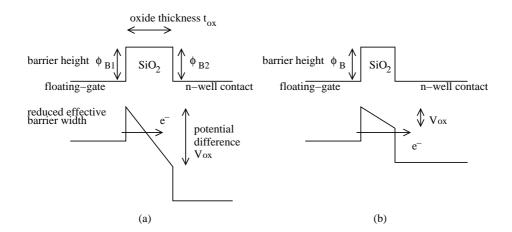

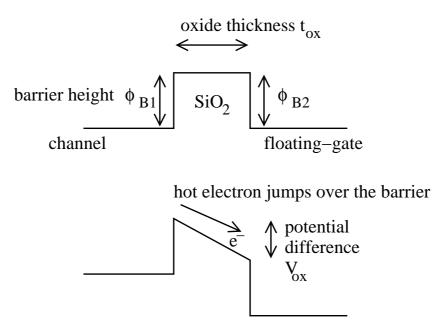

The aim of the programming is to transfer charge carriers (electrons or holes) through  $Si - SiO_2 - Si$  layer structure where the  $Si - SiO_2$  interface introduces an approximately 3.15 eV energy barrier to electrons and 4.63 eV energy barrier to holes [19]. The effective width of the energy barrier is determined by the potential difference between the silicon layers. The carriers must gain sufficient energy so that they can either travel through or jump over the energy barrier (see Figs. 2.4 and 2.6). When the energy barrier heights for electrons and holes are examined, it can be readily seen, that less energy is needed to move electrons through the  $SiO_2$  layer. Consequently, most methods are based on moving electrons through the insulator.

<sup>&</sup>lt;sup>2</sup>This simplified equation neglects the fact that capacitance values and drain voltage may change according to the bias point.

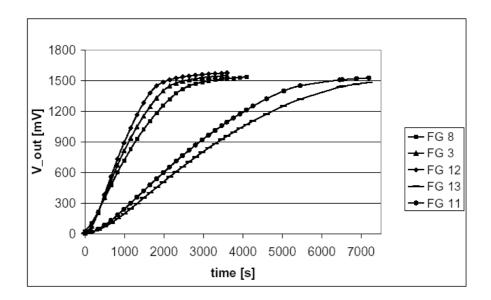

The programming of FGTs can be dynamic or static. One example of dynamic programming is the Autozeroing Floating-Gate Amplifier (AFGA) [17], which adapts the floating-gate charge in response to the applied input signal. Static programming means that FGTs are programmed deterministically to a given target. An example of static programming is presented in [18], where the matrix coefficients needed in image processing are programmed on analog FGTs. There are certain applications that do not fall in either of these groups. For example, the amount of transferred charge itself can be the desired result, e.g. in dosimetric applications [16]. Another study [43] reports how the accumulated charge on FGTs can be used for fatigue monitoring in biomechanical implants. It was shown how the piezo-electric voltage generated by the sensor can be directly used as a source for the programming pulses thus making the monitoring sensor self-powered.

The exact amount of stored charge is relevant for analog applications, whereas binary programming (a lot of charge versus a little bit charge) suffices for digital applications. Thus, it is obvious that the transition from binary programming to continuous programming involves several issues that need to be addressed to achieve desired functionality with an acceptable level of accuracy. Flash-memories based on Multi Level Cells (MLC) are also available, for storing more than a single bit of information on an FGT. The programming of the MLCs is more complicated than the binary case, but needs far less accuracy than the pure analog, continuously valued memory. When programming to a target, the state of the FGT has to be measured: The programming is typically performed in cycles (the iterative process applies also to MLCs). One cycle includes both the programming phase and the measuring phase where the effect of the applied programming is evaluated. In principle any of the following quantities of the FGT, namely charge stored on the floating-gate  $Q_{fg}$ , floating-gate voltage  $V_{fg}$ , drain current  $I_D$ , drain voltage  $V_D$  or related quantity such as channel conductance can be chosen as the quantity to be monitored. However, in practice the easiest way is to measure the  $I_D$ .

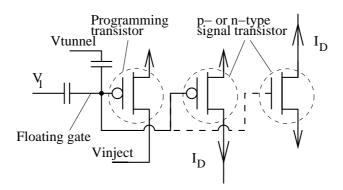

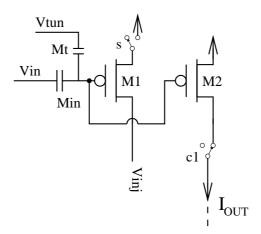

Fig. 2.3 presents a circuit setup for an indirect FGT programming scheme [15] where the signal and programming transistors are separate devices. Another possibility is direct programming that uses the same transistor for signal and programming. Typically, more switches are needed in the direct programming scheme because the FGT must be disconnected from other circuitry during the programming phase and then reconnected for the run-time phase. These switches both increase the complexity of the circuit and introduce additional resistances and capacitances and thus decrease the performance. An indirect scheme permits in-circuit programming but increases the capacitance  $C_{tot}$  connected to the floating-gate. The direct consequence of the increased  $C_{tot}$  is that more charge has to be transferred for the same threshold voltage shift (see Eq. 2.1). It is noteworthy, that the

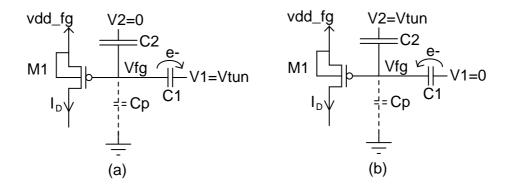

Figure 2.3: Schematic of an FGT with bidirectional programming capability. Fowler-Nordheim electron tunneling is used to remove electrons from the floating-gate and hot electron injection to add electrons to the floating-gate. Indirect programming scheme is applied with either p-type or n-type signal transistor.

indirect method allows transistors connected to a common floating-gate to be of different type. For example, the p-type signal transistor in Fig. 2.3 can be replaced with an n-type transistor.

Bidirectional programming is required in nearly all practical applications. The programming can be global or local, or a combination of these, i.e. global in one direction and local to the other. Furthermore, the programming mechanism can be the same or different in order to add charge (electrons or holes) to the floating-gate or to remove charge from it. On the other hand, some of the presented programming techniques can be used only to add electrons to the floating-gate and therefore need to be supplemented with some other method in order to achieve bidirectional programming.

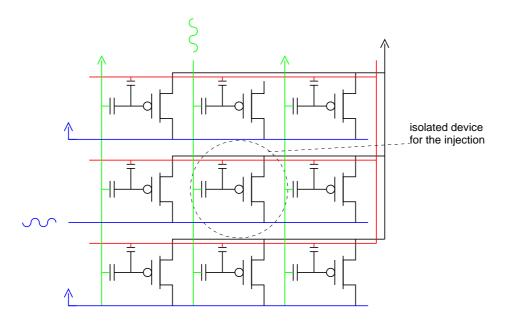

In nearly all practical cases regarding multiple FGTs on the same chip, it is necessary to organize the programming scheme so that it allows a possibility to program each FGT independently, so that the programmed charge of neighboring FGTs remains unchanged. The difficulty in guaranteeing such selectivity with a given programming method depends on the number of parameters that need to be set for the programming.

It is important to understand that the transfer processes are quantummechanical by nature and therefore it is only possible to increase or decrease the probability of charge transfer rather than define strict limiting values for them. Essentially, it is the wave-like properties of charge carriers that enable them to cross the energy barrier. Understanding these effects on the atomic level would take us deep into quantum mechanics, and therefore, it is beyond the scope of this thesis. Instead, the principles of different programming methods on the macroscopic or qualitative level are briefly summarized.

### 2.2.2 UV Photo Injection

Exposing FGTs to UltraViolet (UV) light is perhaps the easiest way to neutralize the negative charge stored on the floating-gates. The mechanism is based on the ability of short wave ultraviolet light (high energy per photon) to impart enough energy (>3.15 eV) to the floating-gate electrons in the Si valence band to enter the  $SiO_2$  conduction band. These excited electrons induce an electrical current through the oxide [20]. The UV Photo Injection method does not require high voltages nor extra capacitors connected to the floating-gate as many other methods, but needs an appropriate chip package to enable light exposure. The process is quite slow and depending on the light intensity needs several minutes or even hours (in ordinary sunlight) to erase the negative charge stored on the gate. It is not possible to add electrons to the floating-gate with the help of UV-radiation and hence it is a one-directional process. It should also be obvious that it is very difficult to design an FGT array that supports selective UV-light programming, because the mechanism is controlled by only two parameters: UV-light intensity and exposure time.

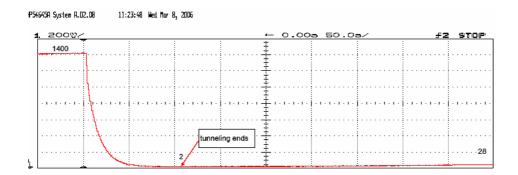

### 2.2.3 Fowler-Nordheim Tunneling

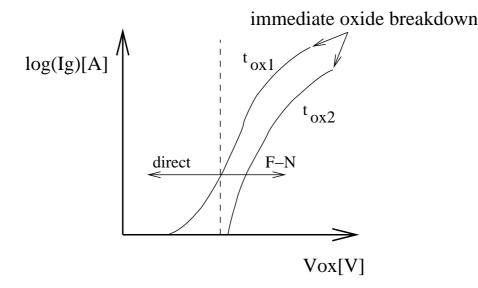

Fowler-Nordheim tunneling (F-N tunneling) [27], which is sometimes also called cold electron tunneling, is a process which allows electrons to penetrate through the energy barrier at the  $Si-SiO_2$  interface. It is also possible to tunnel holes in a standard CMOS process [22], but only through an ultrathin oxide layer (2-4 nm) because of the larger energy barrier height. This is in contrast to electrons, which are able to travel through much thicker dielectric. Such an ultra-thin oxide does not support long-term charge retention. Furthermore, only standard CMOS processes having a  $Si-SiO_2-Si$  at the gate are considered within this thesis. Hence, hole tunneling is beyond the scope of this thesis. The fundamental reason why the FGT becomes leaky if the dielectric is made too thin is that, an ultra-thin dielectric allows so called direct tunneling [23]. In this process electrons can spontaneously travel through the gate oxide almost independently of the electrical field, see Fig. 2.4.

A higher energy level than 3.15 eV is required for electrons to pass over the energy barrier  $\Phi_B^3$ , however the barrier width is also relevant. At room temperature, the thermal energy level of electrons is sufficient for penetrating approximately 5 nm into the oxide. In the absence of the electric field, the electrons will fall back to the silicon (or polysilicon) if the oxide layer is wider than 5 nm. However, the effective barrier width can be reduced

<sup>&</sup>lt;sup>3</sup>Interfacial barrier heights may be unequal for both sides of the dielectric. However, for rough calculations it is reasonable to assume that  $\Phi_{B1} = \Phi_{B2}$ , see Fig. 2.4.

Figure 2.4: A conceptual energy band diagram of the physical differences between F-N and direct tunneling. (a) If the  $SiO_2$  layer is thick enough, electrons have almost negligibly small probability to escape the conduction band of the floating-gate. When  $V_{ox}$  is elevated from zero (the upper figure) to a sufficient level ( $V_{ox} > \Phi_B$ ) (the lower figure) the effective barrier width is reduced so that electrons can tunnel through the triangular-shaped energy barrier. (b) In direct tunneling the electrons can tunnel through the trapezoidal-shaped energy barrier even if the  $V_{ox} < \Phi_B$ .

by applying an electric field across the oxide. Thus, in this process the energy level of electrons is not elevated but the effective barrier width is reduced allowing electrons to tunnel through the energy barrier. This mechanism enables electron tunneling at a relatively low current density. Hence, the name cold electron tunneling, albeit the electrons do become hot (their energy increases) when entering the oxide.

The potential difference  $V_{ox}$  across the oxide decreases the effective barrier width so that electrons can pass through the triangular-shaped barrier into the oxide conduction band, see Fig. 2.4. From the oxide conduction band, these electrons are swept over to the side of the oxide determined by the polarity of the electric field. Naturally, a positive voltage relative to the floating-gate voltage attracts electrons and negative voltage repels them. To initiate significant current flow through the oxide, an electric field larger than  $6.4 \times 10^8 \text{ V/m}$  must be applied across the oxide layer [29]. This information can be used to estimate necessary  $V_{ox}$  for a certain oxide thickness.

F-N tunneling is very sensitive to gate oxide thickness  $t_{ox}$  because of its exponential relationship to current flowing through the dielectric. Several empirical or semi-empirical equations presented in the literature describe the current flow through the  $SiO_2$  under F-N tunneling conditions. One

example is given below [28].

$$J = K_1 F^2 \exp(\frac{-K_2}{F}) \tag{2.4}$$

where J is the current density, F is the electric field across the  $SiO_2$  and  $K_1$  and  $K_2$  are constants determined from the measured data. Typically, F can be approximated by  $V_{ox}/t_{ox}$ .  $K_1$  and  $K_2$  are in the order of 1  $\mu$ A/V<sup>2</sup> and 200 MV/m for oxide thickness > 5 nm. The distinct current density may be higher or lower than the one predicted by Eq. 2.4, because of the trapped charge in the insulator or the geometrical shape of the tunneling junction, which contributes to the tunneling efficiency [29].

Hence, electron tunneling requires only two parameters (voltage across the oxide and the tunneling time) to be set. On the other hand, using F-N tunneling for selective programming of an FGT array can be expensive in terms of area and power due to the required high voltages. The area of the high-voltage switching circuitry can become large and complex in order to properly isolate the programmed and non-programmed devices. This is one reason why F-N tunneling is typically used for global erase.

It is not practical to tunnel electrons through the signal transistor's oxide, because adding high-voltage switches to the signal path increases the complexity and area, deteriorates the signal to noise ratio and can cause undesirable modifications to the functionality of the device. Therefore, a tunneling junction should be added to the floating-gate. The capacitance of the tunneling junction must be small enough relative to  $C_{tot}$  in order to achieve a sufficient electric field with a reasonable tunneling voltage.

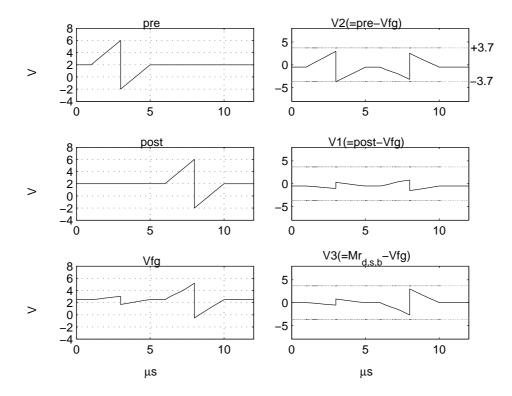

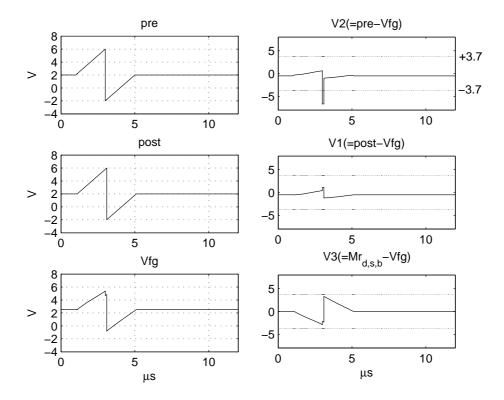

Electrons can be added to and removed from the floating-gate by the tunneling mechanism because the direction of electrons is exclusively determined by the polarity of the electric field across the oxide. Hence, in principle one tunneling junction suffices for bidirectional programming. However, this approach may lead to difficult challenges in practical implementations. This topic is addressed in more detail in Chapter 3. Alternatively, two capacitors of sufficient capacitance ratio can be used to realize a bidirectional tunneling scheme. The operation principle of such a programming scheme is shown in Fig. 2.5, where C2 is a control capacitor that sets the floating-gate voltage  $V_{fg}$  while C1 provides a tunneling junction. C2 dominates the Ctot so that  $V_{fg}$  is a strong function of V2 and a weak function of V1. Thus, according to Eq. 2.3  $V_{fg} \approx V2$ . Consequently, the polarity of the electric field across C1 can be reversed by reversing the voltages applied to C1 and C2. In addition, it must be taken into account that the parasitic capacitance Cp decreases the effective tunneling voltage.

Using two capacitors offers an extra advantage of better support for selective programming, because adding an extra capacitor effectively equals adding an extra parameter. The weakness of this technique is that the gate

Figure 2.5: The principle of bidirectional tunneling scheme. (a) electrons are removed from the floating-gate due to  $V1 >> V_{fg}$ . (b) electrons are added to the floating-gate due to  $V1 << V_{fg}$ .

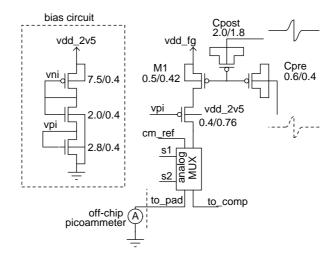

oxide of the signal transistor M1 is exposed to a high electric field when  $V_{tun}$  is applied to C2, see Fig 2.5 (b). The tunneling current through the gate of M1 can be minimized by disconnecting the drain of M1 of its run-time circuit and coupling it to  $vdd_-fg$  for the programming phase. Furthermore, if M1 is replaced with an n-type transistor, also source (and bulk) should be connected to  $vdd_-fg$  for the programming phase in order to minimize the electrical stress of M1.

### 2.2.4 Hot Electron / Hole Injection

When electrons or holes are accelerated in an electric field their energy increases. Energetic carriers are often called hot because thermal energy E and temperature T are related through Boltzmann's constant k: E = kT. These energetic carriers can be injected into the oxide to become trapped charge, drift through the dielectric layer  $(SiO_2)$ , create interface trapped-charge, or generate photons [33]. Many of these events are unwanted in normal operation because they cause undesirable device behavior modifications such as threshold voltage shift and mobility degradation. However, charge transfer by hot electron / hole injection through the  $SiO_2$  layer can be exploited in the programming of FGTs for intentional threshold voltage modification.

There are several mechanisms that can give rise to oxide current when a MOSFET is biased under hot-carrier conditions [23, 34]. These are Substrate Hot-Electron (SHE), Auger Recombination (AR), Secondarily Generated Hot-Electron (SGHE), Channel Hot-Electron (CHE) and Drain-Avalanche Hot-carrier (DAHC). Occurrence of significant hot-carrier effects in silicon requires electric fields greater than 4 x  $10^6$  V/m [23]. This is roughly 150 times lower than that required by F-N tunneling, because the kinetic energy

of the carriers is exploited in the injection process. Hot carriers have enough energy to pass over the energy barrier, see Fig. 2.6. Unlike electron tunneling, hot electron injection is a one-way process (carriers can be accelerated only on the channel side). That is, it can only be used to add electrons to the floating-gate. While in principle, it is possible to inject hot holes to the floating-gate [35], in practice it is very hard because of the higher barrier height for holes and because hot holes tend to generate hot electrons by impact ionization <sup>4</sup>, which can more easily pass over the barrier. In the following, different hot carrier generation mechanisms are discussed briefly.

Figure 2.6: A conceptual energy band diagram of the hot electron injection. The kinetic energy of hot electrons exceeds the barrier height  $\Phi_B$  so that electrons can pass over the barrier. Required vertical field  $V_{ox}$  is within the normal supply voltages, but sufficiently high (typically lateral) field is required to generate hot electrons. It is possible to accelerate i.e. generate hot electrons on the channel side only. Consequently hot electron injection is a one-way process and can be used only to add electrons to the floating-gate.

SHE is mainly used for evaluation of the gate oxide quality. It resembles F-N tunneling, but hot carriers must be externally generated (for example thermally) or injected from a forward-biased pn-junction. The need for thermal excitation or varying substrate bias (back-bias) to control the energy of hot electrons explains why this mechanism is not practical for programming an array of FGTs. Above a certain value of the floating-gate voltage, F-N

<sup>&</sup>lt;sup>4</sup>The result of the impact ionization is two holes and one electron.

tunneling starts to dominate the gate current and the contribution of SHE is masked.

In the Auger process, two carriers recombine and give their energy to a third carrier. In principle, this mechanism allows gate current with drain voltages below the barrier height. However, to reach a sufficient energy level to surmount the barrier, the recombination energy of carriers in equilibrium with the lattice does not suffice [34]. Hence, in practice either the recombining carriers or the receiving carrier must be hot. However, the probability of recombination decreases exponentially with the energy of the carrier. Therefore, it is very difficult to take advantage of this effect to inject carriers to the floating-gate. However, it is probable that the AR enhances the CHE injection for large drain voltages.

SGHE is the most complicated among the HE-processes, involving many overlapping mechanisms for secondary hot carrier generation, such as secondary induced electrons by the hot hole substrate current, photon induced injection and bipolar injection. Basically, the bias conditions in SGHE are similar to those in CHE and in DACH (discussed in the following paragraphs) except for the influence of the substrate's back-bias. The need for back-bias along with the control of many overlapping injection mechanisms simultaneously makes SGHE less attractive for the programming of FGTs.

In the case of CHE, the accelerating electric field is lateral. Hot electrons must be collected into the floating-gate by a properly oriented vertical field. In an n-channel transistor, the combination of low gate voltage  $V_G$  and high drain to source voltage  $V_{DS}$  (high lateral field) creates a large number of hot electrons near the drain. However, high gate voltage  $(V_G > V_D)$  is necessary for a high vertical field that collects part of the hot electrons to the gate. Therefore, it is not possible to maximize both the lateral and the vertical field simultaneously. From this contradiction it follows that for an n-channel MOSFET the injection efficiency peaks when  $V_G$  is approximately equal to  $V_D$  assuming that  $V_S$  and  $V_{SUB}$  are grounded. However, most of the effects caused by CHE are considered harmful in "normal" use of transistors. As these effects are pronounced as the scaling continues, there are several process-control techniques, such as Lightly Doped Drain (LDD), double diffused MOSFET structure and replacing the  $SiO_2$  with the  $Si_3N_4$ , that specifically work to avoid CHE [14]. Consequently, the precise programming of nMOS transistors by using CHE is virtually impossible [15].

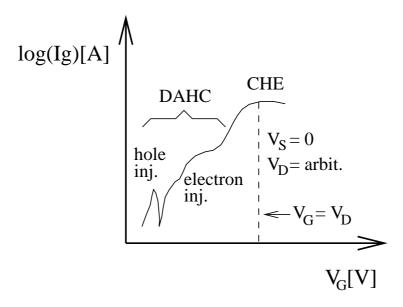

If the accelerating lateral field is high enough and  $(V_G < V_D)$ , hot electrons and holes are generated by impact ionization and avalanche multiplication at the drain (DAHC). The gate current of the DACH as a function of  $V_G$  is not monotonic because the injection efficiencies of hot holes and hot electrons peak at different points, as can be seen from Fig. 2.7. However, the peaks are not equal in height. For an n-channel device, the gate current caused by the injected holes is lower due to the higher energy barrier to the

Figure 2.7: An illustration of  $I_G$  against  $V_G$  for an n-channel device in DAHC for arbitrary  $V_D$  (adapted from [34]). There is a smooth transition from the DAHC to the CHE when the  $V_G$  becomes comparable to the  $V_D$ .

holes in the  $Si-SiO_2$  interface. Although the vertical field of an n-channel device does not favor the collection of electrons to the gate, a part of the ionized hot electrons can be injected against the repulsive field. On this account, the efficiency of DAHC injection compared with CHE injection is lower. When the  $V_G$  is elevated further, the impact ionization decreases and the number of hot electrons in the channel increase, so that there is a smooth transition from the DACH to the CHE.

In a p-channel device, the hot electrons generated by the DAHC mechanism can be injected to the gate. This mechanism is often referred to as Impact Ionized Hot Electron Injection (IIHEI) [36]. The advantage of the IIHEI mechanism is the properly oriented high vertical field under DAHC bias conditions as opposed to nMOS devices under CHE or DAHC bias conditions. This makes IIHEI amenable for the precise programming of a pMOS FGT. Furthermore, the achieved gate current is larger for the p-channel device than for the n-channel device under comparable bias conditions (DACH) due to the smaller energy barrier to the electrons.

The modeling of IIHEI requires the extraction of empirical parameters. For example, a semi-empirical equation of IIHEI gate current was given in [10]

$$I_g = \alpha I_s \exp\left(\frac{-\beta}{(V_{ad} + \delta)^2} + \lambda V_{sd}\right)$$

(2.5)

Figure 2.8: The programmed FGT can easily be isolated from non-programmed devices during injection.

where  $I_g$  is the gate current,  $I_s$  is the source current,  $V_{gd}$  is the gate-to-drain voltage and  $V_{sd}$  is the source-to-drain voltage.  $\alpha, \beta, \delta$  and  $\lambda$  are parameters determined from the measured data. From this equation, the dependence of the gate current on the vertical  $(V_{gd})$  and the lateral  $(V_{sd})$  electrical fields is evident. A more rigorous study of IIHEI with injection efficiency considerations is presented in [37].

In practice, the most useful injection mechanisms are CHE and DACH (or IIHEI), because there is no need for the back-bias. Utilizing these carrier injection mechanisms requires the control of two electric fields simultaneously. With CHE the coexistence of lateral and vertical fields typically makes the  $I_g$  vs.  $V_g$  curve parabolic, because when one field is strengthened the orthogonal field gets weaker. Optimal injection efficiency is obtained by balancing the hot carrier generation efficiency with the vertical field that transports the hot electrons to the floating-gate.

Voltage controlled carrier injection needs three parameters to be set: time,  $V_{DS}$  and  $V_{GD}$ .  $V_{DS}$  and  $V_{GD}$  can be regarded as equivalents to word line and bit line in standard memory architecture. This is advantageous for the selective programming of an array, since the programmed device can be easily isolated, see Fig. 2.8. However, considering especially an analog FGT array, the three parameters need to be controlled simultaneously while taking into account the initial charge. This means that accurate control of electron injection mechanisms is challenging in practical circuits.

Figure 2.9: A simplified schematic of a current biased injection scheme.

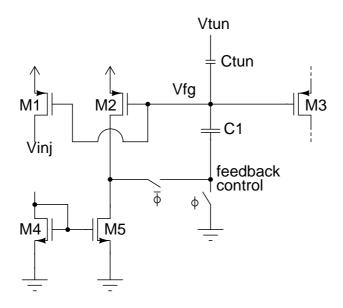

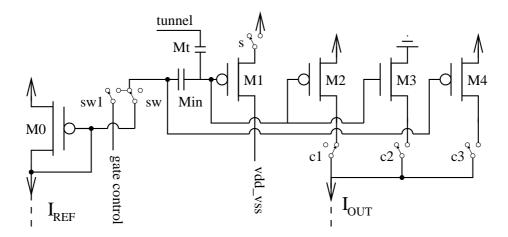

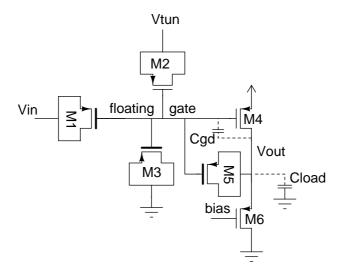

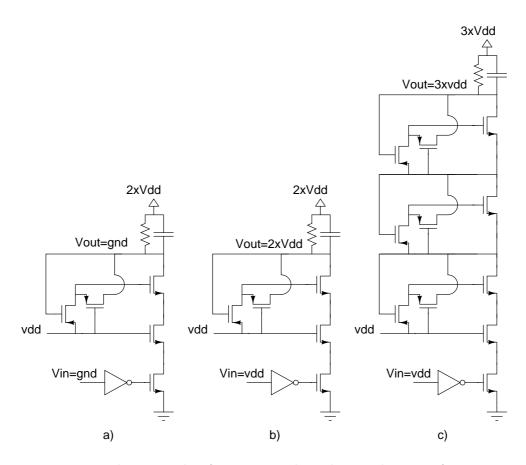

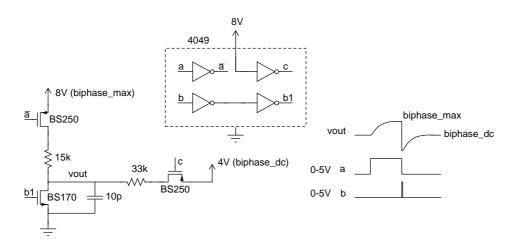

There is also an alternative electron injection programming scheme, which does not require accurate control over  $V_{GD}$ . According to Eq. 2.5, the gate current  $I_g$  is proportional to the source current  $I_s$ . Typically,  $I_s$  is controlled with gate voltage bias  $V_{GD}$ , but current bias can be used as well. A simplified schematic of such an alternative programming scheme [38, 39] is shown in Fig. 2.9. During normal operation, Vtun and Vinj are set to gnd and Vdd, respectively. Transistors M4 and M5 form a current mirror that biases M2 with  $V_{fg}$ . During programming, a feedback loop is established between the drain and gate of M2. As C1 dominates  $C_{tot}$ , the current set by M5 flows through M2, independently of  $Q_{fg}$ . This results in a constant current through M1 as it will mirror the current of M2. The change in charge  $Q_{fg}$  will be a function of the bias current of M1, the Vinj applied to M1, and the duration of the injection pulse.

The current biased injection scheme needs less control in the programming mode than the gate voltage controlled scheme, because a sufficient current bias is determined in the design phase. However, simplified control as compared to the gate voltage controlled scheme is traded for additional power consumption that depends on the chosen current bias, additional switches (increased area) for controlling the feedback loop and loss of one degree of freedom for the gate current adjustment. Also, for these reasons, it is not that amenable for programming large FGT arrays as is the gate voltage controlled scheme. A current bias controlled injection scheme was experimentally tested and the obtained measurement results are discussed in Chapter 4.

While CHE suffices for digital programming, IIHEI is better for accurate hot electron injection for analog applications. This conclusion is based on two things: 1) unintentional CHE is considered harmful and consequently its utilization for programming purposes is efficiently prevented by device level manufacturing optimization 2) the vertical field is incorrectly oriented for supporting CHE but properly oriented for IIHEI. Furthermore, whereas CHE is efficiently prevented, the IIHEI will be available in all DSM CMOS processes because it can not be eliminated without affecting basic transistor operation. Therefore, all FGTs in this thesis are p-channel devices employing the IIHEI mechanism for electron injection. Certainly, the better control of p-channel device programming is traded for lower performance in terms of current gain, transconductance, and speed, in comparison to n-channel devices. However, it is possible to circumvent this trade-off by using an indirect programming scheme, in which a pMOS is used for programming and nMOS acts as a signal transistor.

Finally, some aspects related to injection mechanisms on a system level are considered. While a similar mechanism to the CHE, Channel Hot-Holes (CHH) injection, does exist for p-channel devices, it is not useful due to very low injection efficiency. Thus, in practice, electrons can not be removed from the floating-gate with injection mechanisms. Consequently, any bidirectional programming scheme utilizing a hot electron injection mechanism needs a complementary F-N electron tunneling mechanism to remove electrons. It should also be noted that an injection mechanism, which needs a high lateral field to generate hot carriers, may also limit the use of some important circuit techniques, for example cascading.

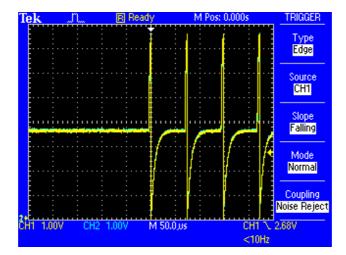

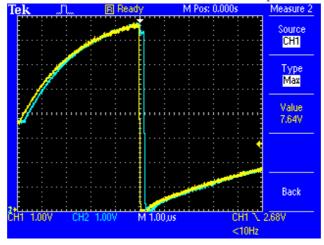

Typically, an FGT is "ramped up" before applying injection pulses. That is, all of the voltages capacitively coupled to the floating node (drain, source, control gate, tunneling junction) are increased in small steps to avoid large potential differences between any nodes. After injection, all terminals are ramped down respectively to observe the change caused by the threshold voltage shift. Ramp up is required when only positive voltages are available to get an adequate drain source voltage for injection. If negative voltage pulses are applied to the drain terminal during injection there is no need for ramp up nor ramp down.

An important long-term effect due to repeated programming is that the oxide wears out. This happens regardless of the selected programming mechanism. In practice the wear out is due to trapped charge and it causes increased gate currents for the same programming parameters and initial state. Another phenomenon that affects the FGT in the long-term causing charge loss is thermionic emission [40]. When the temperature is increased, the energy of charge carriers (sometimes referred to as "thermions" in the literature) is increased so that some of them are able to overcome the energy barrier of the  $Si-SiO_2$  interface. In addition to long-term effects, a short-

term drift can be observed every time FGT is programmed. The short-term drift is due to trapped charge in the oxide and at the interfaces settling to a new equilibrium state after programming. Both of these effects should be taken into account especially when designing and evaluating systems which include analog FGTs.

### 2.3 Performance Aspects of FGTs

More often than not, analog IC design is based on matching devices. The usual way to get a sufficient level of matching is simply to spend more area, thereby increasing the capacitance and power consumption (assuming a fixed operating speed). Respectively, the operating speed (or bandwidth) can be boosted by using wider transistors which also leads to increased power consumption. With FGT technology it is possible to partly decouple the bandwidth-accuracy-power trade-off, since the programming feature of FGTs enables accuracy or matching improvement without the usual proportional increase in the device size and power consumption. The programmability of FGTs also helps in removing extra overhead needed in traditional analog circuit design for linearity improvements, offset removal etc. Naturally, the area needed for the programming infrastructure must be considered when evaluating the trade-offs.

The performance of an FGT is influenced by the unavoidable capacitive divider at the input. The major drawback of the capacitive divider at the input is that it inevitably leads to degraded gain-bandwidth products. This is because the input capacitors act as coupling capacitors which degrade the signal path as the frequency increases. That is why FGTs are in general more suitable for systems with low frequency and bandwidth. On the other hand, [50] reports an FGT-based frequency divider that reaches the -3 dB cut-off frequency at approximately 3 GHz. Even though only simulations were presented without measured results, it can be seen that high frequency applications are feasible. The discussion of the frequency response of the AFGA (Section 4.3) brings additional insight into this issue.

Besides operation speed, there are other performance-related questions of fundamental importance that need to be answered when the use of floating-gate devices is considered. For example, what happens to the Signal to Noise Ratio (SNR) when the gate is isolated by an extra capacitor? This topic is addressed in [51] and those results are briefly summarized in the following. Additional considerations from the technology scaling point of view are addressed in Chapter 3.

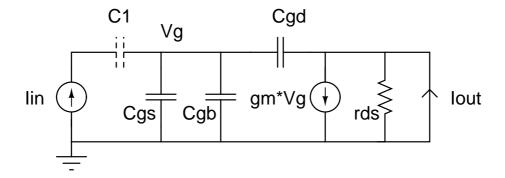

Small signal models of a regular pMOS and a p-type FGT are used as the starting point of this analysis. For simplicity, stand alone devices are assumed so that both devices drive similar loads. The transconductance  $g_m$  of a pMOS transistor in saturation region (and above threshold) can be derived from the small signal model of a transistor (see Fig. 2.10) and is given as

$$g_m = k_p' \frac{W}{L} (V_{GS} - V_{th}) \tag{2.6}$$

where  $k'_p$  is a process transconductance parameter given by

$$k_p' = \mu_p C_{ox} \tag{2.7}$$

where  $\mu_p$  denotes the mobility of holes in the induced channel. An extra capacitor C1 at the input of the FGT device acts as a decoupling capacitor and forms a capacitive divider between the input capacitor and all other capacitors connected to the floating-gate. The ratio of the capacitive divider is given as

$$\kappa = \frac{C1}{C_{tot}} \tag{2.8}$$

so that the transconductance of an FGT  $g_{m,FGT}$  is given as

$$g_{m,FGT} = \kappa g_m \tag{2.9}$$

As opposed to a regular MOS transistor, an FGT device offers an extra degree of freedom for  $g_m$  adjustment by manipulating the effective threshold voltage that affects the overdrive voltage.

The intrinsic cutoff frequency  $f_T$  is defined as the value of the frequency at which the short-circuit current gain of the device drops to unity (i.e Iout/Iin = 1, see Fig. 2.10). The same degradation factor,  $\kappa$ , applies to the cutoff frequency, because  $f_T$  is directly proportional to  $g_m$ . Thus, for an FGT device  $f_{T,FGT}$  is given as

$$f_{T,FGT} = \frac{\kappa g_m}{2\pi (C_{gs} + C_{gd} + C_{gb})}$$

(2.10)

where  $C_{gs}$ ,  $C_{gd}$  and  $C_{gb}$  are intrinsic capacitances of a MOS device (see Fig. 2.1).

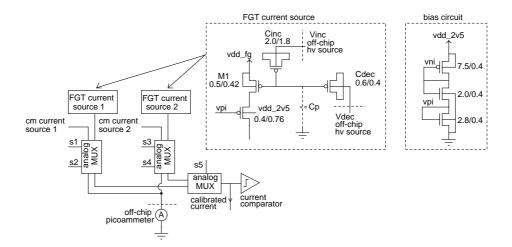

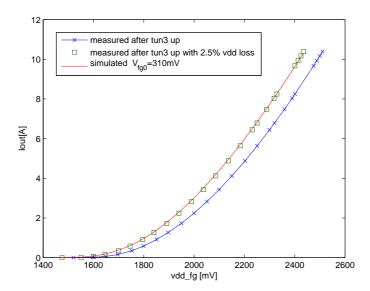

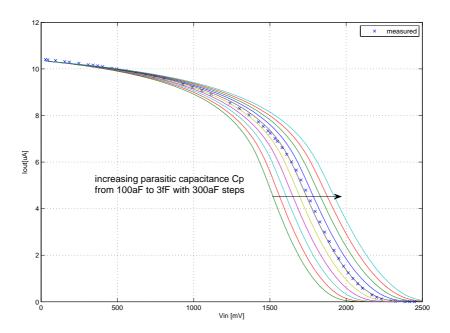

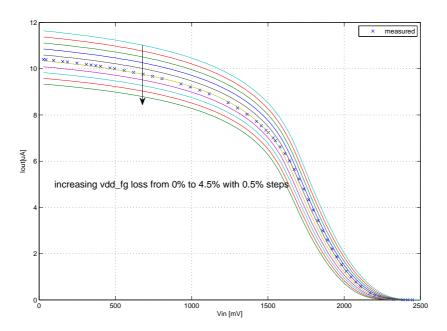

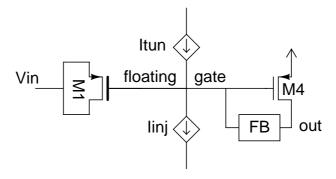

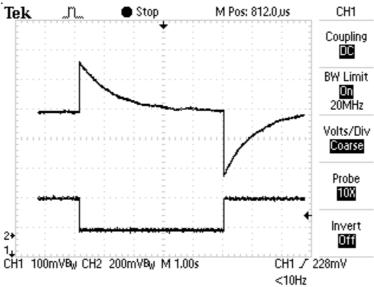

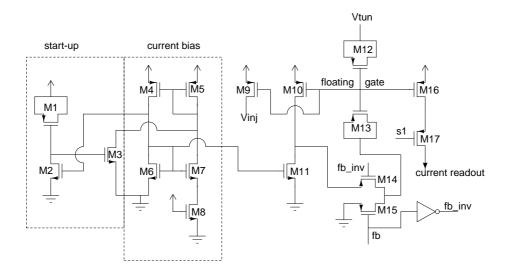

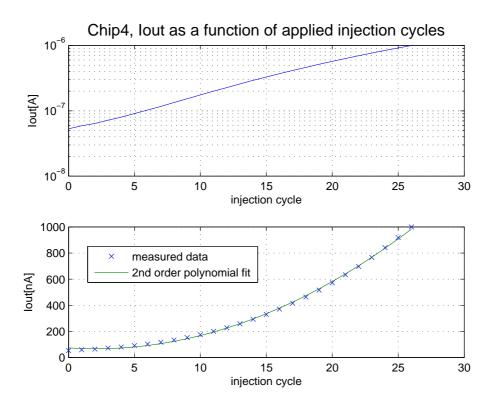

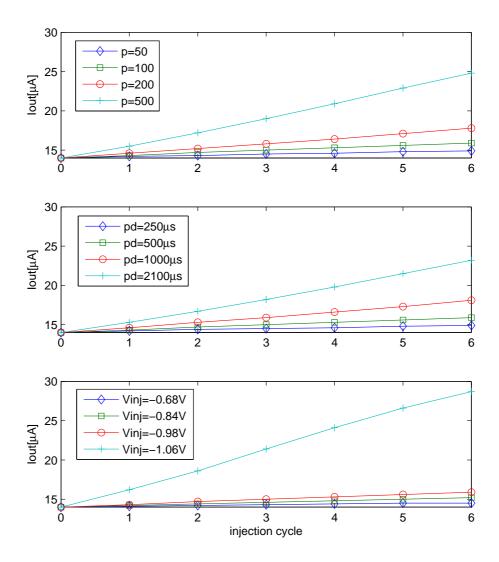

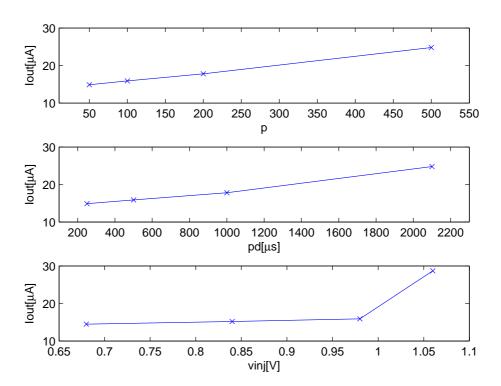

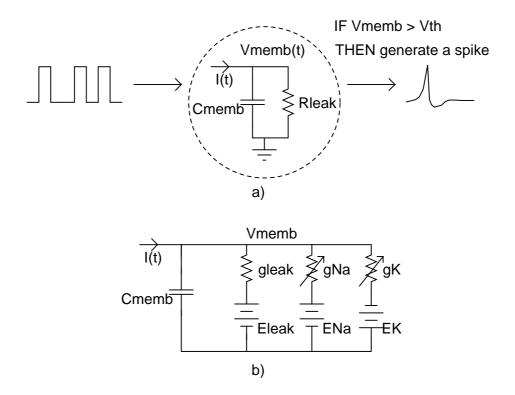

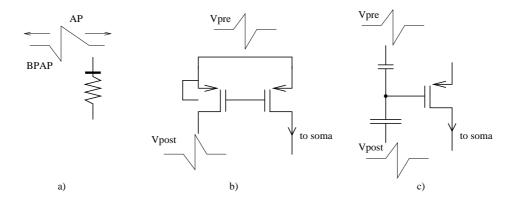

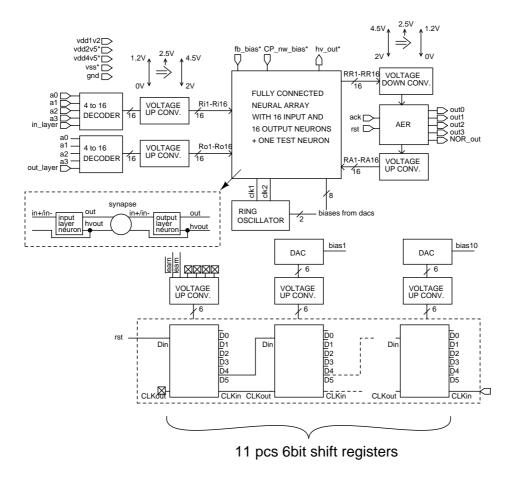

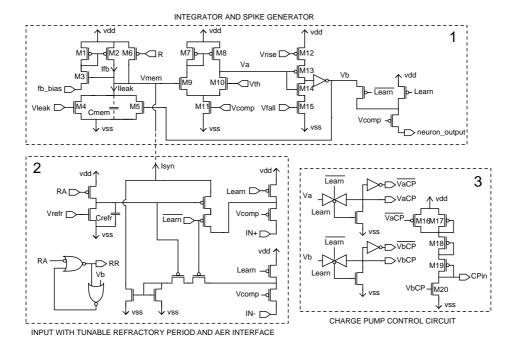

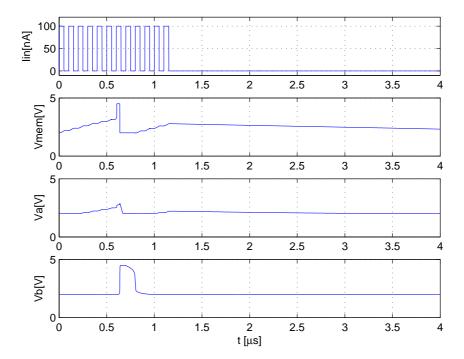

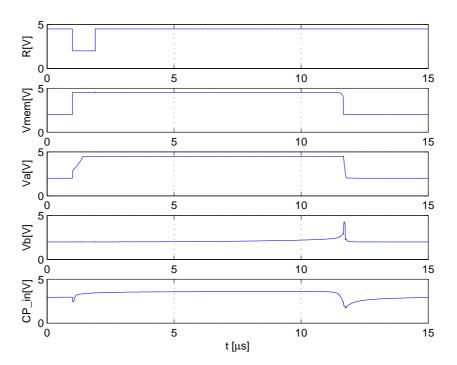

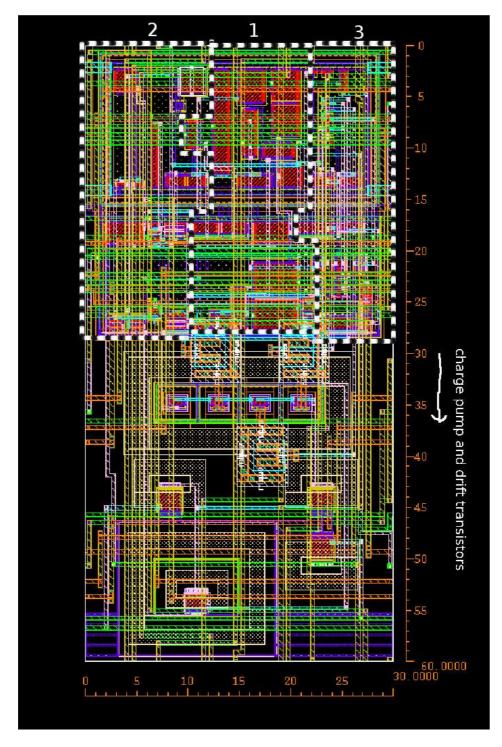

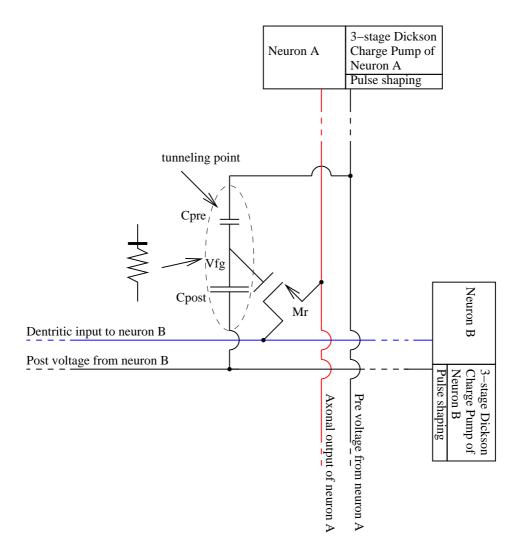

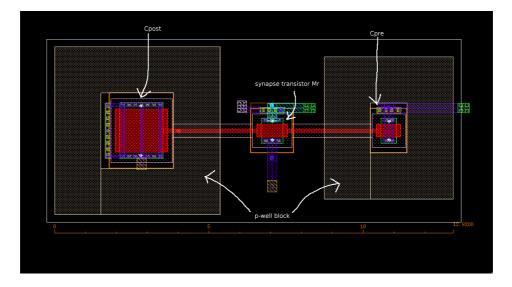

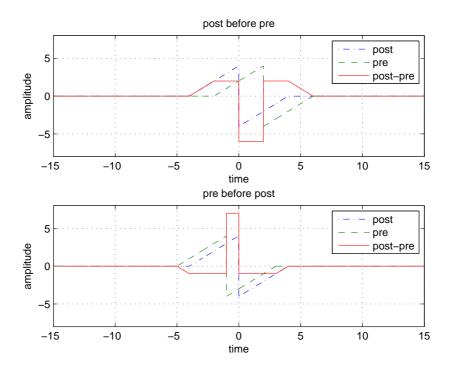

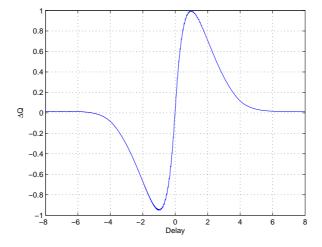

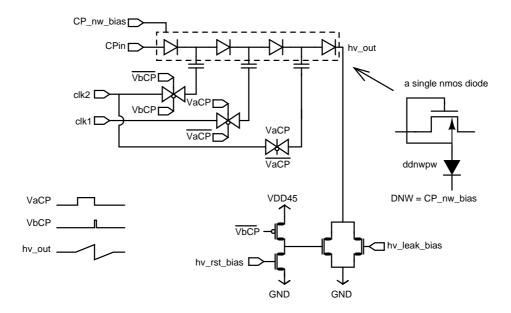

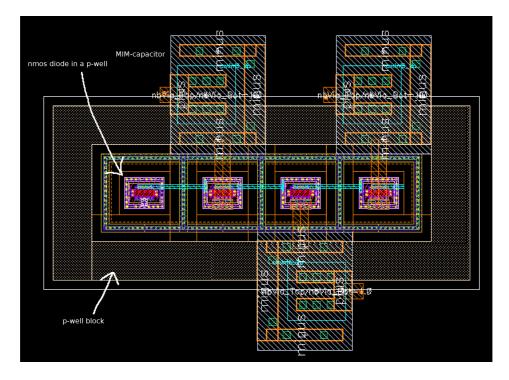

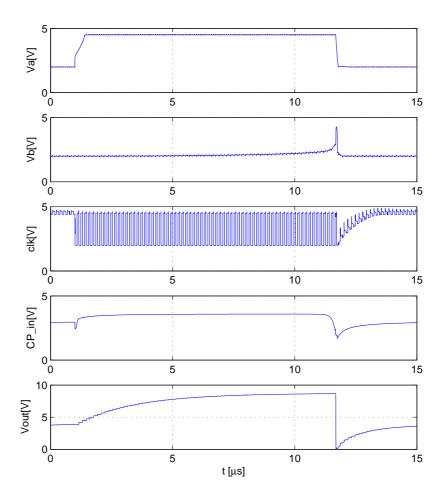

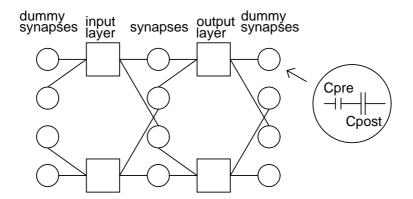

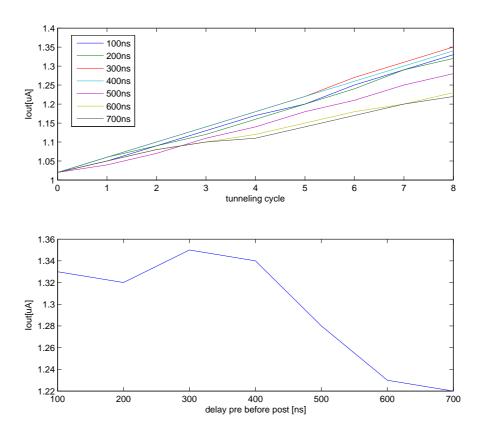

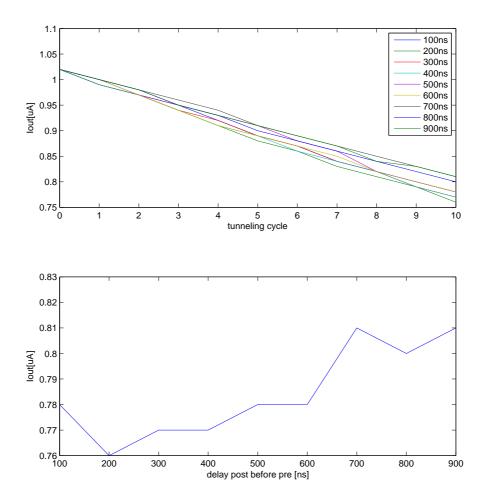

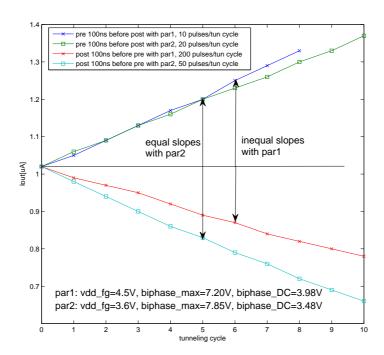

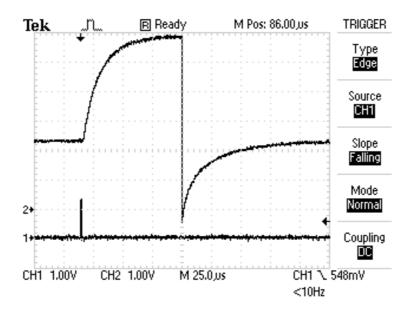

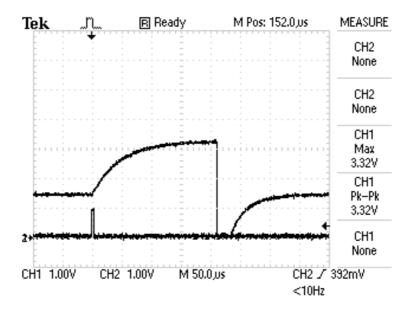

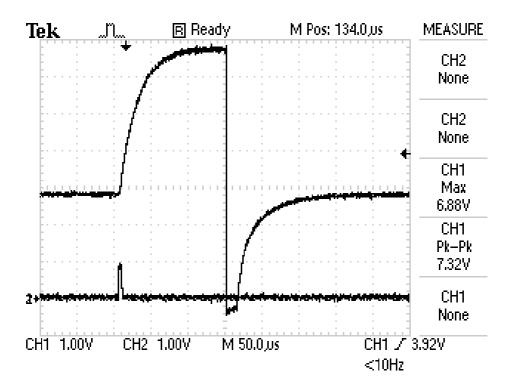

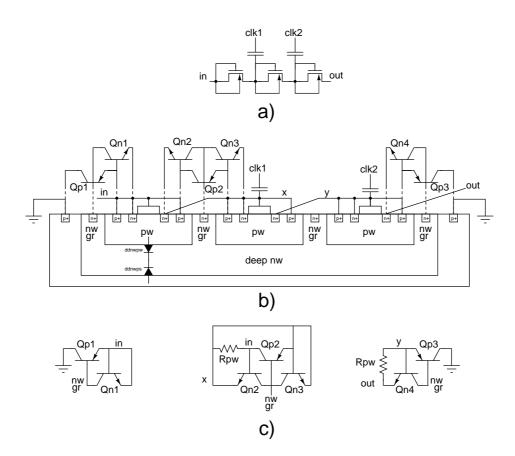

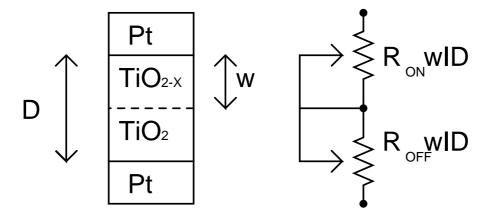

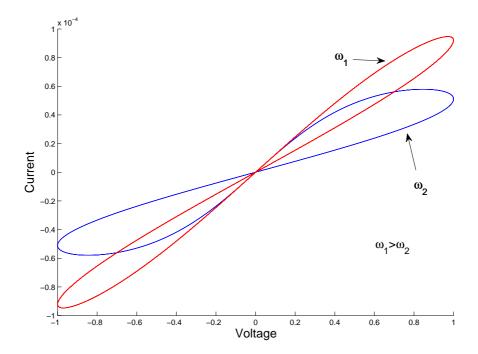

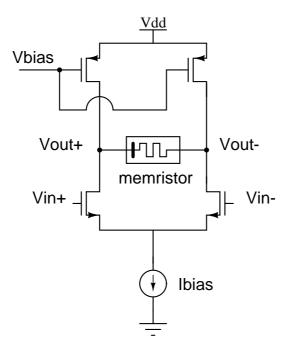

In this simplified analysis only the changes due to the input capacitor C1 were considered. However, it is straightforward to extend the analysis to FGTs with multiple inputs. For example, the tunneling capacitor appears in parallel with the  $C_{gs}$  in the small signal model, and thus adds one linear term to the denominator of Eq. 2.10, further decreasing the  $f_{T,FGT}$  as can be expected.