## Kameswar Rao Vaddina

# Thermal-Aware Networked Many-Core Systems

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 175, May 2014

## Thermal-Aware Networked Many-Core Systems

Kameswar Rao Vaddina

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Beta on May 23rd, 2014, at 12 noon.

University of Turku Department of Information Technology 20014 Turku, Finland

2014

#### **Supervisors**

Assoc. Prof Juha Plosila Department of Information Technology University of Turku 20014 Turku, Finland

Assoc. Prof Pasi Liljeberg Department of Information Technology University of Turku 20014 Turku, Finland

#### Reviewers

Prof. Gert Jervan

Department of Computer Engineering

Faculty of Information Technology

Tallinn University of Technology

Akadeemia tee 15a, 12618 Tallinn, Estonia

Assoc. Prof. Baris Taskin

Department of Electrical and Computer Engineering

Drexel University

3141 Chestnust Street

Philadelphia, PA 19104-2875, USA

### Opponent

Prof. Peeter Ellervee Department of Computer Engineering Faculty of Information Technology Tallinn University of Technology Akadeemia tee 15a, 12618 Tallinn, Estonia

ISBN 978-952-12-3063-9 ISSN 1239-1883

The originality of this thesis has been checked in accordance with the University of Turku quality assurance system using the Turnitin Originality Check service.

## Abstract

Advancements in IC processing technology has led to the innovation and growth happening in the consumer electronics sector and the evolution of the IT infrastructure supporting this exponential growth. One of the most difficult obstacles to this growth is the removal of large amount of heat generated by the processing and communicating nodes on the system. The scaling down of technology and the increase in power density is posing a direct and consequential effect on the rise in temperature. This has resulted in the increase in cooling budgets, and affects both the life-time reliability and performance of the system. Hence, reducing on-chip temperatures has become a major design concern for modern microprocessors.

This dissertation addresses the thermal challenges at different levels for both 2D planer and 3D stacked systems. It proposes a self-timed thermal monitoring strategy based on the liberal use of on-chip thermal sensors. This makes use of noise variation tolerant and leakage current based thermal sensing for monitoring purposes. In order to study thermal management issues from early design stages, accurate thermal modeling and analysis at design time is essential. In this regard, spatial temperature profile of the global Cu nanowire for on-chip interconnects has been analyzed. It presents a 3D thermal model of a multicore system in order to investigate the effects of hotspots and the placement of silicon die layers, on the thermal performance of a modern flip-chip package. For a 3D stacked system, the primary design goal is to maximise the performance within the given power and thermal envelopes. Hence, a thermally efficient routing strategy for 3D NoC-Bus hybrid architectures has been proposed to mitigate on-chip temperatures by herding most of the switching activity to the die which is closer to heat sink. Finally, an exploration of various thermal-aware placement approaches for both the 2D and 3D stacked systems has been presented. Various thermal models have been developed and thermal control metrics have been extracted. An efficient thermal-aware application mapping algorithm for a 2D NoC has been presented. It has been shown that the proposed mapping algorithm reduces the effective area reeling under high temperatures when compared to the state of the art.

## Tiivistelmä

Integroitujen piirien valmistusteknologian edistys on johtanut kulutuselektroniikan innovaatioihin ja alan kasvuun sekä tätä eksponentiaalista kasvua tukevan IT-infrastruktuurin kehittymiseen. Yksi vaikeimmista kasvua haittaavista tekijöistä on elektroniikkajärjestelmän suorittaman laskennan ja kommunikaation tuottama lämpö ja sen poisto järjestelmästä. Piiriteknologian kehitys kohti pienempiä viivanleveyksiä ja tehotiheyden kasvu aiheuttavat lämpötilan nousua järjestelmissä. Tämä johtaa haastaviin jäähdytysteknisiin ratkaisuihin ja vaikuttaa sekä järjestelmän luotettavuuteen että suorituskykyyn. Lämpötilan alentamisesta on täten tullut tärkeä tekijä nykyaikaisten mikroprosessorisirujen suunnittelussa.

Tässä väitöskirjassa tarkastellaan planaaristen 2D-järjestelmien ja pinottujen 3D-järjestelmien lämmöntuoton haasteita eri tasoilla. itetään itseajoittuva lämpötilan monitorointistrategia perustuen sirunsisäisten lämpötila-anturien vapaaseen käyttöön. Tämä strategia soveltaa kohinasietoista ja vuotovirtaperusteista lämpötilan ilmaisutekniikkaa monitorointitarkoituksiin. Tarkka terminen mallinnus ja suunnittelunaikainen analyysi ovat keskeisessä asemassa, kun pyritään tutkimaan lämmöntuoton hallintaan liittyviä kysymyksiä järjestelmän suunnitteluprosessin varhaisissa vaiheissa. Tähän liittyen työssä analysoidaan kuparipohjaisten sirunsisäisten johtimien lämpötilaprofiilia. Profiili esittää moniydinprosessorin kolmiuloitteisen lämpömallin, jonka avulla voidaan tutkia ns. kuumien pisteiden ja piisirukerrosten sijoittelun vaikutusta modernin "flipchip"-tyyppisen monisirukotelon termiseen suorituskykyyn. Pinottuja 3Dpiirejä suunniteltaessa ensisijainen tavoite on maksimoida suorituskyky siten, että tehonkulutus ja lämpötila pysyvät annettujen rajojen sisällä. Tätä silmälläpitäen väitöstyössä esitetään lämpötilaherkkä reititysalgoritmi verkkopiiri- ja väylärakenteet yhdistävälle 3D-hybridiarkkitehtuurille. Perusajatuksena on ohjata suurin osa tiedonsiirtoon liittyvästä piiriaktiviteetista sirulle, joka on lähimpänä jäähdytyselementtiä. väitöskirjassa tarkastellaan erilaisia lämpötilatietoisia sijoittelumenetelmiä 2D- ja 3D-järjestelmille. Tähän liittyen kehitetään useita lämpömalleja ja johdetaan lämpötilakontrollin mittareita. 2D-verkkopiirirakenteelle esitetään tehokas lämpötilatietoinen sovellusten hajautusalgoritmi. Työssä

osoitetaan, että verrattuna aikaisemmin esitettyihin ratkaisuihin tämä algoritmi pienentää korkeassa lämpötilassa olevan pinta-alan osuutta verkkopiirisirulla.

This thesis is dedicated to my parents Vaddina Narasimha Murthy and Vaddina Kalavathi.

## Acknowledgements

"Begin at the beginning," the King said, very gravely, "and go on till you come to the end: then stop." - Lewis Carroll, Alice in Wonderland.

It was not an easy journey for me to embark on my doctoral adventure. Sometimes, it was riddled with despair and anguish, and sometimes with hope and delight. But overall, it was 'fun' and I enjoyed the ride. A lot of people supported, inspired, encouraged and influenced my research career in Finland. Many of them shaped my understanding, curated my thought process and helped me to evolve into a better human being. Thanks to them I am now here and waiting for life's next great adventure. As Alice would say, "I can't go back to yesterday because I was a different person then". But now, today, it is time for me to thank all the people who have helped me achieve this.

First and foremost, I would like to express my sincere gratitude to my supervisor and research director Adj. Prof. Juha Plosila for his guidance and encouragement during the PhD program. Without his high-level guidance and inspiration, this thesis would not have been possible. His great sense of humor has always kept me at ease in many technical discussions we had over the years. I would also like to thank Adj. Prof. Pasi Liljeberg for cosupervising my thesis and helping me to improve the quality of my research and the thesis text. Both of you have given me the liberty in choosing the topic and were flexible enough when I was moulding it to suit my research interests. Moreover, you have trusted me with the research and financially supported me throughout the years for which I am immensely grateful. This thesis work has been financially supported by the Academy of Finland, the Nokia Foundation, the Ulla Tuominen Foundation, Turku University Foundation and all the Finnish tax payers. I am infinitely indebted to all the financial supporters.

I would like to thank Prof. Gert Jervan from Department of Computer Engineering, Tallinn University of Technology and Assoc. Prof. Baris Taskin from Department of Electrical and Computer Engineering, Drexel University for their detailed reviews and constructive comments of this work. Their suggestions have greatly improved the quality and relevance of this work. I addition, I would like to sincerely thank my fellow colleagues in the lab who have helped me stay sane during the years. Especially, Dr. Ethiopia Nigussie, Dr. Khalid Latif and Dr. Liang Guang. Incidentally, all of whom also happen to be my co-authors and have reviewed my thesis. I really cherish the time we spent together in the coffee room discussing everything under the sun. From research topic in question to various aspects of living in Finland to immigration issues, you were there all the time helping and guiding me along the process. I had some of the best time in Turku with you all and value your friendship forever.

I have had the great pleasure of working, authoring and co-authoring publications with some of the best minds in the lab. Our common passion for research has made us an ideal team to work together. Especially, I would like to thank Dr. Amir Mohammad Rahmani and Mohammad Fattah from UTU and Tamoghna Mitra (from Åbo Akademi University) for sharing their insights and understanding on varied subjects. Others from the lab with whom I have had pleasure to interact with on a daily basis, but was not fortunate enough to work together are Thomas Canhao Xu, Rajeev Kumar Kanth, Bo Yang, Masoud Daneshtalab, and Masoumeh Ebrahimi. Thank you all for making my stay in the lab a comfortable one and I learnt a great deal from each and every one of you. I would also like to thank immensely my tutor Dr. Teijo Lehtonen for helping me settle down in Turku during my initial days. Special mention and thanks should also go to Sami Nuuttila for answering many of my silly questions on Linux and for his immense help in setting up various tools and benchmarks. I would also like to thank TUCS secretary, Irmeli Laine and former graduate programme coordinator for TUCS, Satu Jääskeläinen for going out of their way and helping me to come to Finland so that I could pursue my passion.

All work and no play makes Jack a dull boy. The Indian community in Turku made sure that there is no dearth of social activities and gatherings. They were always there through think and thin and have showered me with their love, hospitality and amazing food. Shishir, when I said amazing food, I did not count you in. Thanks to the Indian community, Turku always felt like home for me.

I was very fortunate to be in the great company of friends who have varied interests, broad and liberal values, and yet have similar outlook towards life like me. I have enjoyed the long and endless conversations with them and remember that many times we had to "agree to disagree" just so that we can go home. I would like to express my sincere gratitude to Shishir Jaikishan, Anil Kumar Alla, Senthil Palani, Hariharan Dandapani and Pasi Kankaanpää. Shishir, Senthil and Hari are avid Cricket followers whose conversations I never followed. They all are great both on and off the field. Anil and me are co-founders of a startup which failed quickly. But then again, it was so much fun to be around you all and I enjoyed each

and every moment sharing and laughing with you. Special thanks to Pasi for all the great sailing trips (the best one is yet to come though) and for being a window into Finnish culture and society. Pasi, I have always told you otherwise, but I love to read those long e-mails you send. Sometimes!! Also, special thanks goes to my trekking buddies Bineet Panda, Anil Kanduri, Kartiek Kanduri, Tamoghna Mitra and Debanga Nandan. Thanks a lot Ponnuswamy Mohanasundaram for accompanying me for lunch everyday during the past year and a half and listening and sharing. Frankly guys, you all are irreplaceable.

I have to forcefully stop myself from extending this acknowledgment section lest it becomes a thesis in itself. But before I do that I have to thank the most important people of my life without whom I would not have been here. My parents have made several sacrifices in their adult life just so that their kids can have the best possible education. Despite facing several odds, they both believed in the power of knowledge and enlightenment which is bestowed by education, and education alone. I really hope that they have realized that they have succeeded in planting the seed of knowledge in me and have made me into a learner for life. I dedicate this thesis to both my parents who made this possible. I also greatly acknowledge the support of both my brother and sister during this entire process. I am truly thankful to them.

Finally, I would like to thank my wife Manjusha Kasu. Her constant support, encouragement and unwavering love is what made this thesis possible. Her smile alone used to light my days up. I would like to express my heartfelt thanks to her for being with me during the past 5 years which were the best years of my life.

Turku, May 2014 Kameswar Rao Vaddina.

## Contents

| 1        | $\mathbf{Intr}$ | roduction                                                               | 1          |

|----------|-----------------|-------------------------------------------------------------------------|------------|

|          | 1.1             | Background and Motivation                                               | 2          |

|          | 1.2             | Temperature Issues with 3D Stacked Systems                              | 5          |

|          | 1.3             | Thermal Control Optimization Strategies                                 | 6          |

|          | 1.4             | Thesis Objectives                                                       | 8          |

|          | 1.5             | Thesis Contributions                                                    | 9          |

|          | 1.6             | Research Publications                                                   | 10         |

|          | 1.7             | Organization of Thesis                                                  | 12         |

| <b>2</b> | The             | ermal Management Techniques for Microprocessors                         | <b>15</b>  |

|          | 2.1             | Power Management vs Thermal Management                                  | 17         |

|          | 2.2             | Classification of Temperature Control Mechanisms                        | 19         |

|          |                 | 2.2.1 Off-Chip Thermal Management Techniques                            | 20         |

|          |                 | 2.2.2 Design-Time Thermal Management Techniques                         | 20         |

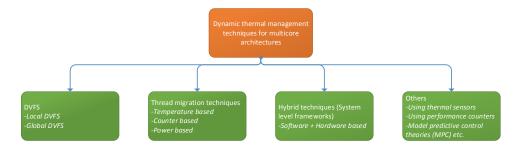

|          |                 | 2.2.3 Dynamic Thermal Management Techniques                             | 21         |

|          | 2.3             | Summary                                                                 | 28         |

| 3        | Self            | -Timed Thermal Sensing and Monitoring of Multicore                      |            |

|          |                 |                                                                         | <b>2</b> 9 |

|          | 3.1             | Introduction and Motivation                                             | 29         |

|          | 3.2             | Thermal sensing architecture                                            | 31         |

|          | 3.3             | Sensing interconnection network                                         | 36         |

|          | 3.4             | Noise and supply voltage variation analysis                             | 40         |

|          |                 | 3.4.1 Power supply noise (PSN) analysis                                 | 41         |

|          |                 | 3.4.2 Input signal noise (ISN) analysis                                 | 42         |

|          |                 | 3.4.3 Supply voltage variations                                         | 42         |

|          | 3.5             | Summary                                                                 | 43         |

| 4        | The             | ermal Modeling and Analysis                                             | 45         |

|          | 4.1             | Thermal analysis of on-chip interconnects in multicore systems          | 46         |

|          |                 | Thorna didi, sis of our our printer confidence in management s, stories | 10         |

|          |                 | 4.1.1 Resistivity vs Temperature                                        | 48         |

|          | 111             |                                                                         |            |

|   |     | 4.1.4 Wide line vs narrow line                              | 52  |

|---|-----|-------------------------------------------------------------|-----|

|   |     | 4.1.5 Summary                                               | 52  |

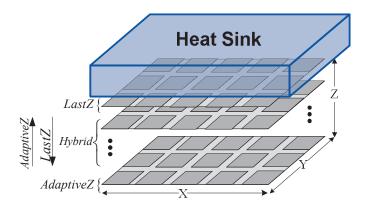

|   | 4.2 | Thermal modeling and analysis of 3D stacked systems         | 54  |

|   |     | 4.2.1 Nomenclature                                          | 55  |

|   |     | 4.2.2 Flip-Chip package                                     | 55  |

|   |     | 4.2.3 Thermal modelling and Analysis                        | 56  |

|   |     | 4.2.4 Simulation results                                    | 59  |

|   |     | 4.2.5 Summary                                               | 65  |

| 5 | The | ermally Efficient Inter-Layer Communication Scheme          | 67  |

|   | 5.1 | Introduction to Hybrid NoC bus 3D architecture              | 67  |

|   | 5.2 | Thermally efficient routing strategy for 3D NoC             | 68  |

|   | 5.3 | Thermal model to evaluate the thermally efficient routing   |     |

|   |     | strategy for a 3D NoC                                       | 70  |

|   | 5.4 | Simulation results and analysis                             | 73  |

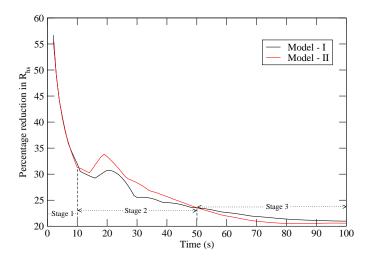

|   |     | 5.4.1 Thermally efficient routing for 3D NoC                | 73  |

|   | 5.5 | Summary                                                     | 75  |

| 6 | The | ermal-Aware Mapping                                         | 77  |

|   | 6.1 | Thermal-Aware Placement in 2D and 3D Chip Systems           | 77  |

|   |     | 6.1.1 Uniform power distribution                            | 78  |

|   |     | 6.1.2 Thermal-aware placement for a 2D chip system          | 78  |

|   |     | 6.1.3 Thermal-aware placement for a 3D stacked chip systems | 79  |

|   | 6.2 | Thermal modeling and simplifications                        | 82  |

|   |     | 6.2.1 Thermal modeling using Hotspot                        | 82  |

|   |     | 6.2.2 Thermal modeling using COMSOL                         | 82  |

|   | 6.3 | Thermal analysis                                            | 84  |

|   |     | 6.3.1 Uniform power distribution case                       | 84  |

|   |     | 6.3.2 Thermal-aware placement for a 2D chip system          | 84  |

|   |     | 6.3.3 Thermal-aware placement for a 3D stacked chip systems | 86  |

|   | 6.4 | Proposed temperature mitigation techniques                  | 96  |

|   |     | 6.4.1 Thermal-aware mapping for 2D NoC                      | 96  |

|   |     | 6.4.2 Thermal Modelling                                     | .00 |

|   | 6.5 | Simulation results and analysis                             | 02  |

|   |     | 6.5.1 Thermal-aware mapping for 2D NoC                      |     |

|   | 6.6 | Summary                                                     | .03 |

| 7 | Con | nclusions and Future Work 1                                 | 05  |

|   | 7.1 | Summary and Conclusions                                     | .05 |

|   | 7.2 | Future Work                                                 | .08 |

## List of Figures

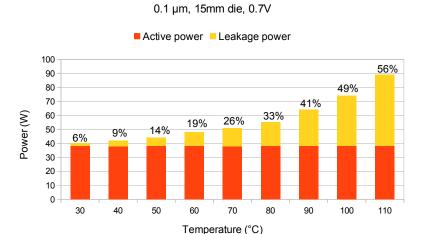

| 1.1  | Power consumption of a die as a function of temperature. It is a 15-mm Intel fabricated die in a $0.1\mu$ m technology and a supply voltage of $0.7V$ [1] | 2   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

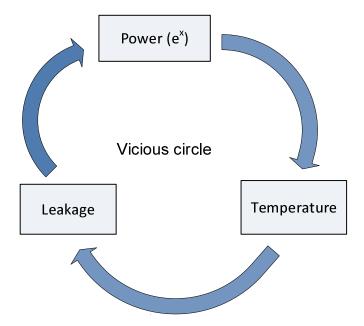

| 1.2  | The vicious circle of power, temperature and leakage cycle                                                                                                | 3   |

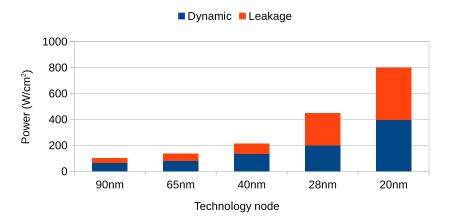

| 1.3  | Increase in leakage power with technology scaling (IBS Elec-                                                                                              | 0   |

| 1.0  | tronics [2])                                                                                                                                              | 4   |

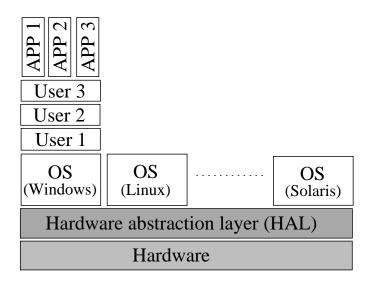

| 1.4  | Futuristic virtualization platform                                                                                                                        | 6   |

| 2.1  | Future trends for static and dynamic power for both the logic                                                                                             | 1 = |

| 2.2  | and memory [3]                                                                                                                                            | 17  |

|      | logic and memory $[3]$                                                                                                                                    | 18  |

| 2.3  | Classification of temperature control mechanisms                                                                                                          | 20  |

| 2.4  | Classification of dynamic thermal management techniques and control algorithms                                                                            | 22  |

| 2.5  | Classification of dynamic thermal management techniques in                                                                                                |     |

|      | multicore architectures                                                                                                                                   | 23  |

| 2.6  | A simple thermal equivalent circuit for a 3D stacked system                                                                                               |     |

|      | in a flip-chip package                                                                                                                                    | 26  |

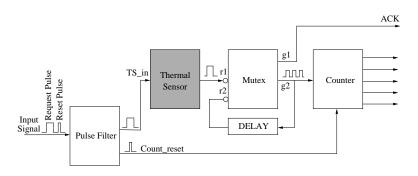

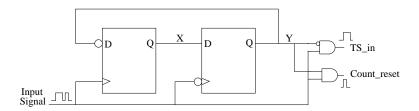

| 3.1  | Thermal Sensing Circuit (TSC)                                                                                                                             | 31  |

| 3.2  | Self-timed handshaking protocol for the thermal sensing ar-                                                                                               |     |

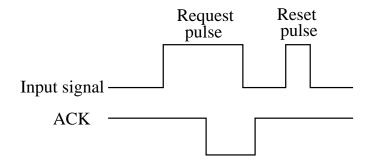

|      | chitecture.                                                                                                                                               | 32  |

| 3.3  | Pulse Filter                                                                                                                                              | 32  |

| 3.4  | Timing diagram of the Thermal Sensing Circuit (TSC) at 27°C.                                                                                              | 33  |

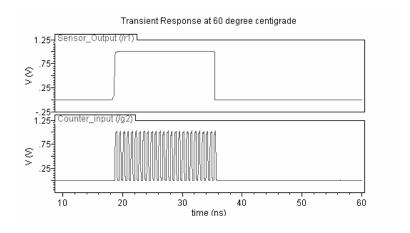

| 3.5  | Timing diagram of the Thermal Sensing Circuit (TSC) at 60°C.                                                                                              | 33  |

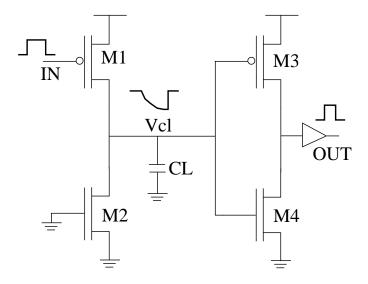

| 3.6  | Leakage current based thermal sensor [4]                                                                                                                  | 34  |

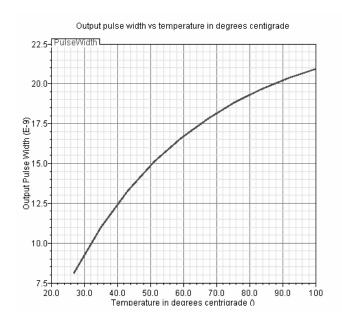

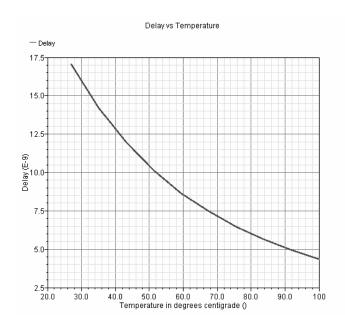

| 3.7  | Response of the sensor in the 27°C to 100°C range as simu-                                                                                                |     |

|      | lated in 65nm technology                                                                                                                                  | 35  |

| 3.8  | The delay through the sensor, plotted against the temperature.                                                                                            | 35  |

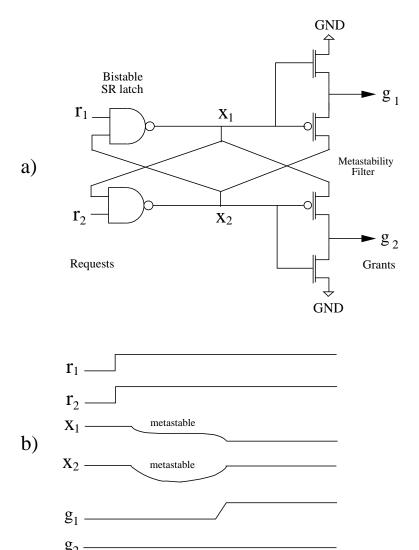

| 3.9  | MUTEX and its timing diagram                                                                                                                              | 37  |

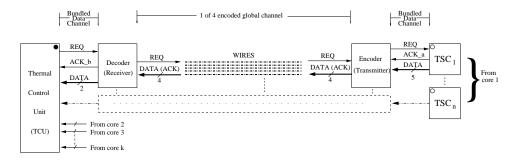

| 3.10 | Self-timed signaling architecture for sensing interconnection                                                                                             |     |

|      | network                                                                                                                                                   | 38  |

|      |                                                                                                                                                           |     |

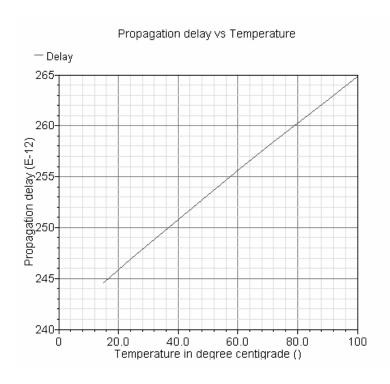

| 3.11       | Propagation delay of the delay element vs temperature                                                                                                                                                                  | 39 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

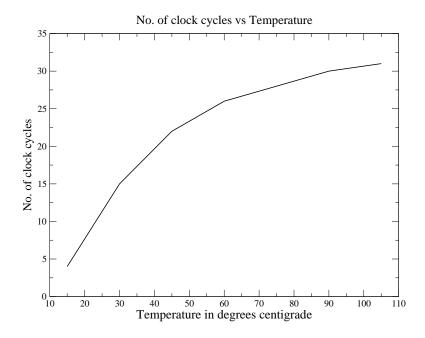

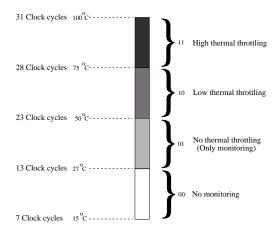

| 3.12       | No.of clock cycles vs temperature                                                                                                                                                                                      | 39 |

| 3.13       | Encoding of temperature                                                                                                                                                                                                | 40 |

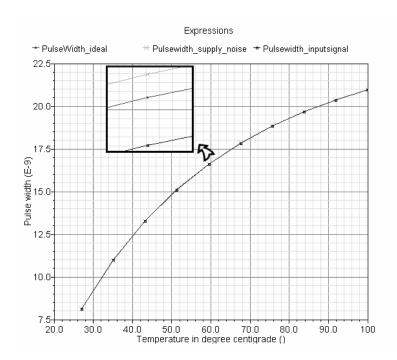

| 3.14       | Output pulse-width of the thermal sensor with noisy power supply rails and input signal noise vs the one with the ideal power supply for different temperature values                                                  | 41 |

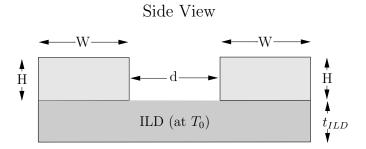

| 4.1<br>4.2 | Conductor of length $L$                                                                                                                                                                                                | 49 |

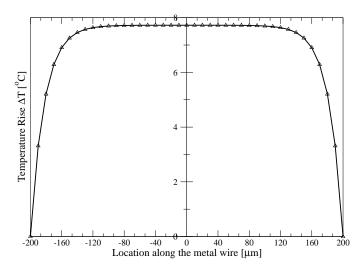

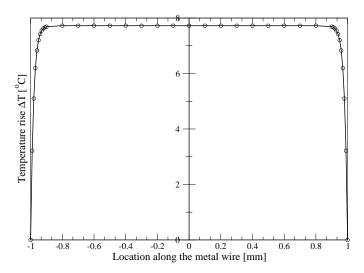

|            | via separation. The dimensions and other material properties of the global interconnect used are for 65nm technology node from ST microelectronics [5]                                                                 | 51 |

| 4.3        | Temperature distribution along the total length of the conductor optimally divided into different segments and interspersed with vias                                                                                  | 51 |

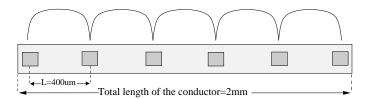

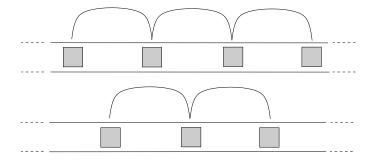

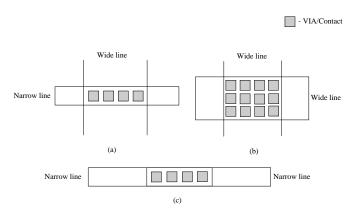

| 4.4        | Interleaving of repeaters                                                                                                                                                                                              | 52 |

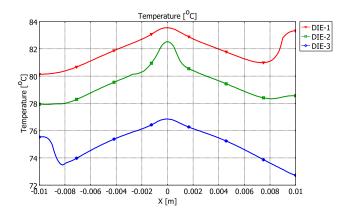

| 4.5        | Spatial temperature profile along the Cu nanowires with $2mm$ via separation. The dimensions and other material properties of the global interconnect used are for $65nm$ technology node from ST microelectronics [5] | 53 |

| 4.6        | Connection between the interconnect segments with a group of vias                                                                                                                                                      | 53 |

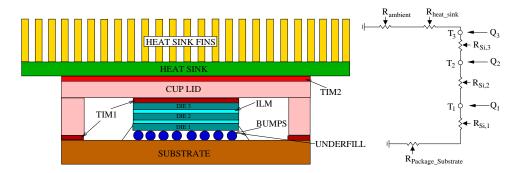

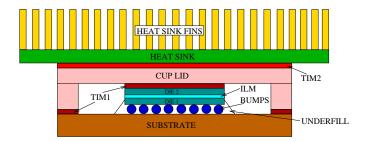

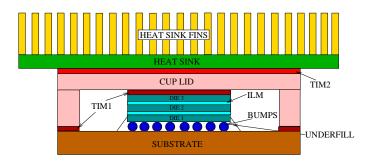

| 4.7        | Cross-Sectional view of a modern 3D Flip-Chip package with 2 stacked dies.                                                                                                                                             | 56 |

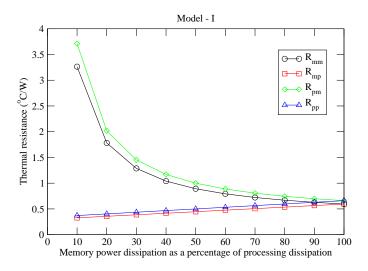

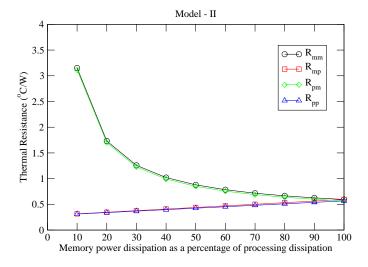

| 4.8        | Thermal resistance measurements for both the dies in model-I at steady-state.                                                                                                                                          | 61 |

| 4.9        | Thermal resistance measurements for both the dies in model-<br>II at steady-state                                                                                                                                      | 61 |

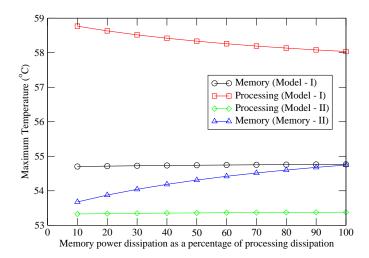

| 4.10       | Maximum temperature on the processing and memory die for both models                                                                                                                                                   | 62 |

| 4.11       | 10% Maximum temperature on the processing and memory die for both models                                                                                                                                               | 63 |

| 4.12       | 10% Thermal Resistance on the processing and memory die for both models                                                                                                                                                | 63 |

| 4.13       | Improvement required in heat sink thermal resistance for a 3D system (both models) whose memory layer is consuming 50% of the processing die power. It has been compared with                                          |    |

|            | a single die package system                                                                                                                                                                                            | 64 |

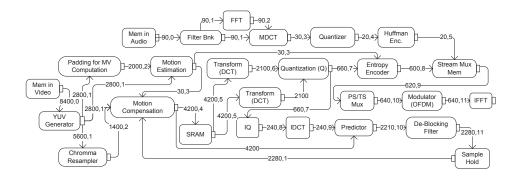

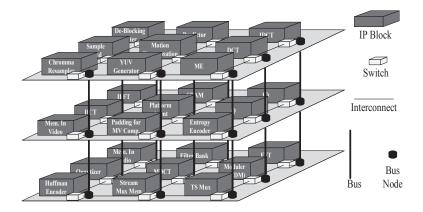

| 5.1<br>5.2 | The proposed thermally efficient routing algorithm Communication trace of encoder part of a H.264 video con-                                                                                                           | 70 |

|            | ference                                                                                                                                                                                                                | 74 |

| 5.3  | Partition and core mapping of the video conference encoding application                                                                                                                                                                                                                             | 75 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

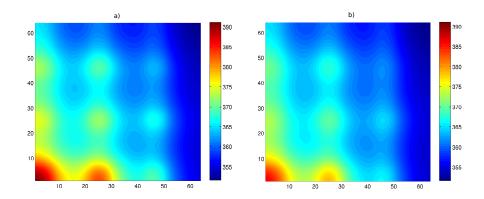

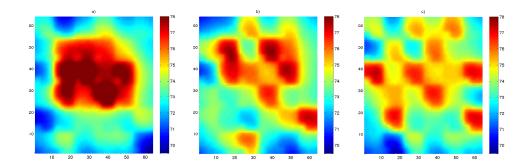

| 5.4  | Steady-state grid level thermal maps for the die 1(layer 0) for both the normal routing and (a) and our thermal-aware hybrid routing (b)                                                                                                                                                            | 76 |

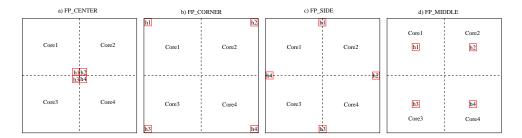

| 6.1  | Four different hotspot placement cases that were analyzed for a 2D chip system                                                                                                                                                                                                                      | 79 |

| 6.2  | Cross-Sectional view of a modern 3D Flip-Chip package with 3 stacked dies                                                                                                                                                                                                                           | 79 |

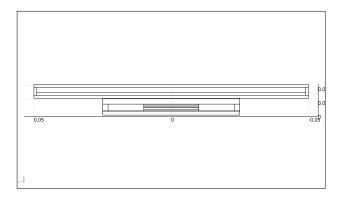

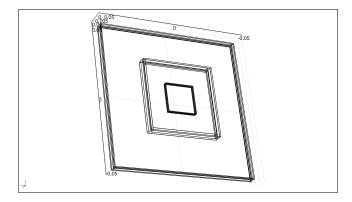

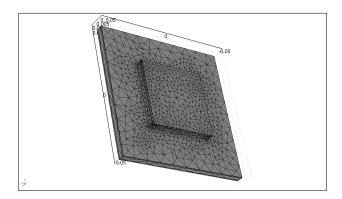

| 6.3  | Side view of the thermal model using COMSOL                                                                                                                                                                                                                                                         | 83 |

| 6.4  | Front view of the thermal model using COMSOL                                                                                                                                                                                                                                                        | 83 |

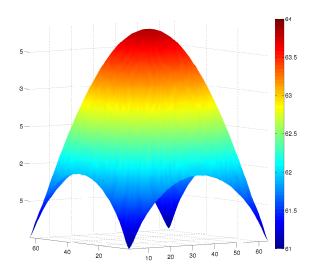

| 6.5  | Uniform power distribution does not lead to uniform temperature distribution on the silicon die in a Flip-Chip package                                                                                                                                                                              | 85 |

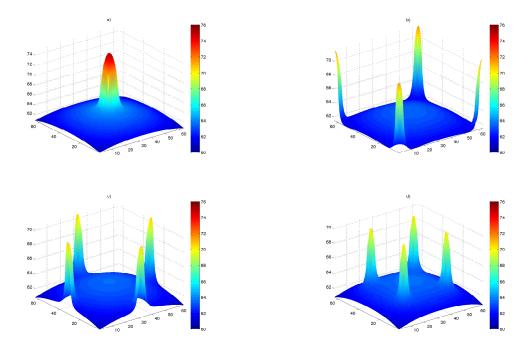

| 6.6  | Thermal profiles of a) $FP\_CENTER$ , b) $FP\_CORNER$ , c) $FP\_SIDE$ and d) $FP\_MIDDLE$ cases of a 2D chip system                                                                                                                                                                                 | 86 |

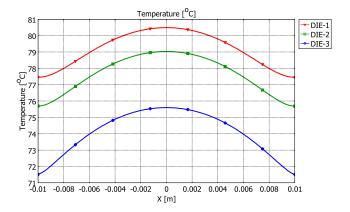

| 6.7  | Thermal profiles of all the 3-layers of a 3D stacked system when the worst case hotspot scenario occurs in a die which is i) BOTTOM: farther from the heat sink $(a,b,c)$ , ii) MID-DLE: equidistant from the heat sink and the heat spreader $(d,e,f)$ iii) TOP: closer to the heat sink $(g,h,i)$ | 88 |

| 6.8  | Coarse grained meshing of the thermal model                                                                                                                                                                                                                                                         | 89 |

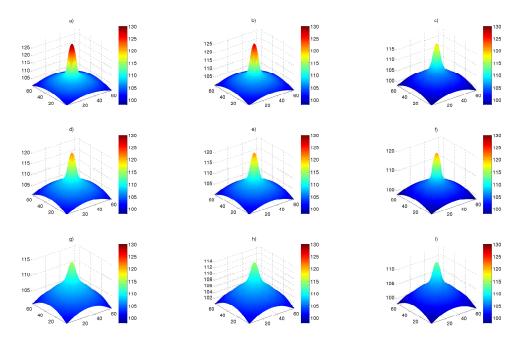

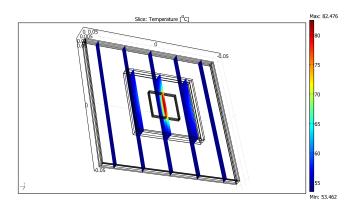

| 6.9  | Slice plot of the thermal model in the <i>Static</i> case. $P = 200W$ , $P_{die1} = P_{die2} = P_{die3} = 66.66W$                                                                                                                                                                                   | 90 |

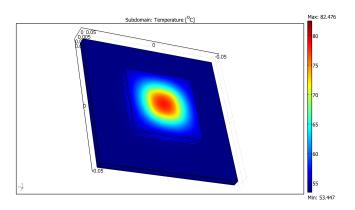

| 6.10 | Subdomain plot of the thermal model in the <i>Static</i> case. P = 200W, $P_{die1}=P_{die2}=P_{die3}=66.66$ W                                                                                                                                                                                       | 90 |

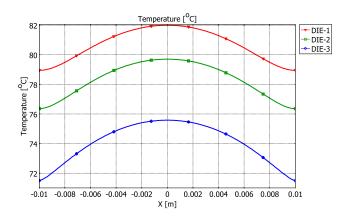

| 6.11 | Peak temperatures on all the three dies in the <i>Static</i> case. P = 200W, $P_{die1}=P_{die2}=P_{die3}=66.66$ W                                                                                                                                                                                   | 91 |

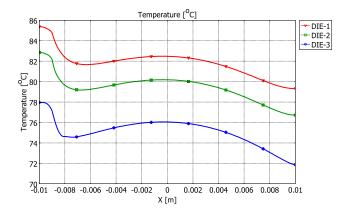

| 6.12 | Peak temperatures on all the three dies in the <i>Adaptive</i> case. $P = 200W$ , $P_{die1} = 40W$ , $P_{die2} = 60W$ , $P_{die3} = 100W$                                                                                                                                                           | 91 |

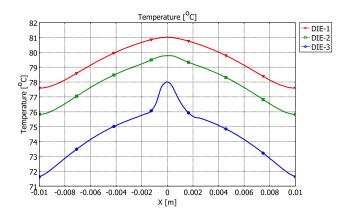

| 6.13 | Peak temperatures on all the three dies in the Adaptive_hotspot case. $P = 200W$ , $P_{die1} = 40W$ , $P_{die2} = 60W$ , $P_{die3} = 100W$ , $P_{d.hotspot} = 100W/cm^2$                                                                                                                            | 92 |

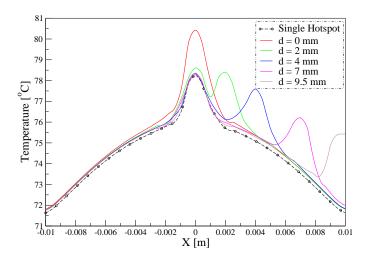

| 6.14 | Interaction of two hotspots located on the same die (DIE-3). The plot is obtained by fixing the location of one hotspot at the center of the die and varying the location of the other. The distance 'd' in the plot is the distance between the centers of two hotspots                            | 95 |

| 6.15 | Interaction of hotspots located in different vertically stacked layers. Each hotspot is located at the center of its die edge                                                                                                                                                                       |    |

|      | respectively.                                                                                                                                                                                                                                                                                       | 95 |

| 6.16 | Interaction of hotspots located in different vertically stacked    |    |

|------|--------------------------------------------------------------------|----|

|      | layers, but distributed efficiently so that their thermal fields   |    |

|      | do not interact with each other                                    | 6  |

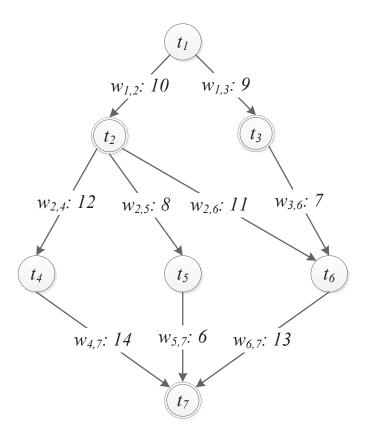

| 6.17 | An example task graph of an application consisting of 7 tasks.     |    |

|      | Hotspot tasks are depicted as concentric circles 9                 | 7  |

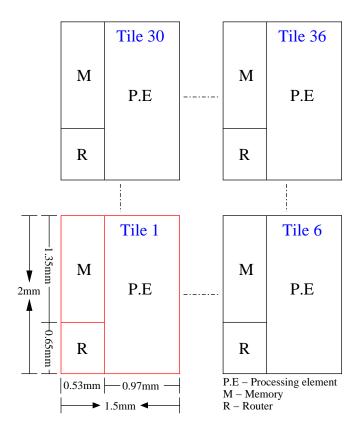

| 6.18 | A $6\times6$ NoC depicting the blocks and dimensions of each tile. |    |

|      | The dimensions are adopted from Intel's 65nm based 80-core         |    |

|      | processor [6]                                                      | 1  |

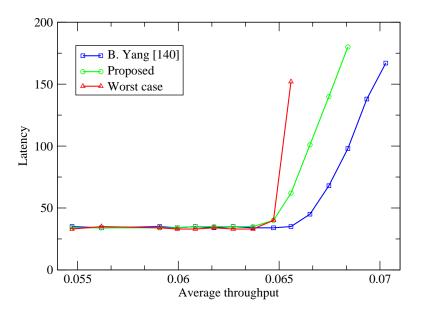

| 6.19 | Latency vs throughput                                              | 3  |

| 6.20 | Thermal maps of a) Worst case b) TMB mapping case and              |    |

|      | c) Thermal-aware case                                              | 14 |

## List of Tables

| 3.1        | PSN-ideal  and  ISN-ideal  values at different temperatures.<br>Where PSN and ISN stands for power supply noise and input signal noise respectively                                                         | 42       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | ations at 27°C and 100°C as compared to the one with no voltage variations                                                                                                                                  | 43       |

| 4.1        | Modelling parameters [7] [8] [9] [10]                                                                                                                                                                       | 57       |

| 5.1<br>5.2 | Power Consumption and Average Packet Latency Layer temperature profile of the Hybrid Bus-NoC 3D Mesh-                                                                                                       | 75       |

| 5.3        | based system running the video conference application Layer temperature profile of the proposed Hybrid Bus-NoC 3D Mesh-based system running the video conference application (thermal-aware hybrid routing) | 75<br>76 |

| 6.1<br>6.2 | Modelling parameters [7] [8] [9] [10]                                                                                                                                                                       | 81<br>87 |

| 6.3        | 3D stacked system: Maximum/peak, average and minimum temperatures in all the three placement cases for a chip system that is consuming a total power of 300W                                                | 87       |

| 6.4        | Simulation run 1: Peak temperatures on all the three dies for all the three cases in a 200W system                                                                                                          | 89       |

| 6.5        | Simulation run 2: Peak temperatures on all the three dies for                                                                                                                                               |          |

| 6.6        | all the three cases in a 100W system                                                                                                                                                                        | 92       |

| J.0        | all the three cases in a 600W system                                                                                                                                                                        | 93       |

| 6.7        | Table depicting the amount of chip area under a particular                                                                                                                                                  | 100      |

|            | temperature                                                                                                                                                                                                 | 103      |

## List of Abbreviations

**ACK** Acknowledgment

**ADC** Analog-to-Digital Converter

**ADI** Alternating Direction Implicit

APL Average Packet Latency

**AWMD** Average Weighted Manhattan Distance

**BJTs** Bipolar Junction Transistors

CBGA Ceramic Ball Grid Array

CMOS Complementary Metal Oxide Semiconductor

**CoC** Cloud on a Chip

Cu Copper

**DSD** Digital System Design

**dTDMA** dynamic Time-Division Multiple Access

**DTM** Dynamic Thermal Management

**DVFS** Dynamic Voltage And Frequency Scaling

FCBGA Flip-Chip Ball Grid Array

**HAL** Hardware Abstraction Layer

**HCI** Hot Carrier Injection

IC Integrated Circuit

**ILD** Interlayer Dielectric

**ILM** Interlayer Material

**ISN** Input Signal Noise

MPC Model Predictive Control

MPSoC MultiProcessor System-on-Chip

MTTF Mean Time to Failure

**NBTI** Negative Bias Temperature Instability

**NoC** Network-on-Chip

**PCM** Phase-Change Material

PE Processing Element

**PSSN** Power Supply Noise

**PTAT** Proportional To Absolute Temperature

**SoC** System-on-Chip

TCU Thermal Control Unit

**3D** Three-Dimensional

**TIM** Thermal Interface Material

TMB Tree-Model-Based

**TSC** Thermal Sensing Circuit

**TSV** Through-Silicon-Via

VMM Virtual Machine Monitor

WLP Wafer Level Packaging

## Chapter 1

## Introduction

In Greek mythology the Titan Prometheus is credited with stealing the heavenly fire from the gods and giving it to the humans thus enabling the process of progress and civilization for the entire humanity. This generous act brought the wrath of Zeus, king of the Olympian gods, who then sentenced Prometheus to eternal torment for his transgression before being freed by the hero Hercules. Great stories like these which are common to all of humanity follow the journey of a hero and usually culminate with the accomplishment of greater good for the entire mankind. For several millennia, humans made fire to generate heat and light which enabled them to cook food, stay warm and to keep nocturnal predators at bay. Despite sophisticated advances throughout human history in controlling and managing fire and heat, several challenges still remain. Especially, in the design of high performance electronic systems, the problem of heat is predominant and steps need to be taken in controlling and managing that heat. This thesis is a very small step in that direction.

Microprocessor chips are the building blocks of todays information world. Their performance has grown by over 1000-fold during the past 20 years which has been driven by both speed and energy scaling, as well as the advances in the microarchitecture design [11]. As was stated by Moore's law [12], the transistor density gains that were obtained by continuous scaling aided in the increased usage of microprocessor chips, from battery powered devices to data centers. At the same time, software applications are becoming more complex with every iteration and have a large impact on power and thermal maps of the system. Most of the energy consumed by the microprocessor is dissipated as heat, which could result in numerous undesirable effects, like performance degradation, reliability deterioration, high-energy costs, and physical damage leading to system failures. Hence, managing temperature at the chip, server and data center level has become one of the big concerns for the technology industry.

Figure 1.1: Power consumption of a die as a function of temperature. It is a 15-mm Intel fabricated die in a  $0.1\mu$ m technology and a supply voltage of 0.7V [1]

#### 1.1 Background and Motivation

As the technology scales down and power density increases, a lot of factors such as power dissipation, leakage, data activity, negative bias temperature instability (NBTI), hot carrier injection (HCI), and electro-migration contribute to higher temperatures, larger temperature cycles and increased thermal gradients all of which impact multiple failure mechanisms [7]. New improvements in process technology like the usage of low-k dielectrics and deep-trench isolation are also unfavorable for heat conduction [13]. The increase in temperature leads to increase in leakage power which in turn exacerbates an already serious thermal problem, thereby causing thermal runaway [14]. Fig. 1.1 depicts the significant increase in leakage power as a function of substrate temperature for a 15-mm die fabricated by Intel, at  $0.1\mu$ m technology and a supply voltage of 0.7V [1].

This exponential dependance on temperature results in thermal runaway, which is sort of a vicious circle as shown in Fig. 1.2. This leads to significant drop in the performance of the system. Fallah et al. state that the leakage of transistors consume more than 40% of the total power consumption in 90nm process technology [15]. For still smaller nodes of technology the leakage power dominates the dynamic power consumption as shown in Fig. 1.3.

Also, the increase in temperature, increases interconnect delay due to the linear increase in electrical resistivity. These delay variations pose significant reliability problems with already dense interconnect structures. Joule self-heating, which is defined as the amount of heat generated when a maximum current of  $j_{max}$  passes through an interconnect wire, and delay variations

Figure 1.2: The vicious circle of power, temperature and leakage cycle

combined with the introduction of low-k dielectrics with low thermal conductivity increases the need for accurate thermal analysis and estimation of interconnect temperature. At the same time, it is not enough to just address thermal hot spots that might arise on the chip, as temperature gradients in both time and space determine the reliability of the system at moderate temperatures [16]. Instantaneous high temperature rises in the devices can cause catastrophic failure, as well as long-term degradation in the chip and package materials, both of which may eventually lead to system failure [17].

The ITRS report [7] projects that the power density for 14nm technology node will be greater than  $100\mathrm{W}/cm^2$  and the junction-to-ambient thermal resistance will be less than  $0.2^{\circ}\mathrm{C}$ . It is very important to keep the thermal resistance at bay as this may increase the package cost and thereby the overall cost of the product. Observation of the thermal contours of certain industrial chip shows that the temperature at the hotspots can really exceed  $100^{\circ}\mathrm{C}$  [18]. Recent statistical analysis on component failures show that more than 50% of all integrated circuit failures are related to high temperatures. It means, that the aging process of the components increases with sustained high temperatures, thus leading to their failures [1].

If the heat cannot be transferred to the ambient at a rate equal to or greater than its generation, then junction temperatures will rise on the silicon die. As the junction temperatures increases, there will be a reduction in the mean time to failure (MTTF) [1]. Ambient temperatures vary a lot.

Figure 1.3: Increase in leakage power with technology scaling (IBS Electronics [2])

During the year 2013 in Turku, Finland, the temperature varied from -26°C to +30°C [19]. Also, depending on the industry segment under consideration, the ambient temperatures can be very harsh. For example in the automotive industry the temperature near the wheel ABS system can be greater than 150°C and the temperature near the exhaust system can be greater than 400°C. Similarly the temperature varies from engine oil, alternator to the interior of a car [20]. Hence it is important to consider detailed package models while performing thermal simulations.

The prevailing temperature crisis is a multi-scale problem. It can be seen at the chip/component level, server/board level, rack level and at the room level [21]. The temperature problem is worsened when the level of abstraction is scaled up from processor core to server, and from there to a data center, requiring equally expensive cooling solutions and increase in greenhouse carbon emissions.

The conventional strategy to increase performance of a microprocessor by increasing the frequency and taking advantage of innovations in process technology has hit the power wall [22]. To overcome the power wall, the semiconductor industry has started using multiple cores and parallelize execution to achieve the performance targets. With the increase in the number of cores on the chip we have now hit the thermal wall [21]. The total chip power is exceeding the thermal design power which is essentially the power that is dissipated by the chip through the package and to the ambient. This forces the designers and manufacturers of systems to only power part of the system resources at any point of time. It essentially means that most of the system is reeling under dark silicon. Dark silicon is a big problem for mobile

platforms, as there is very less scope to use complex and expensive cooling solutions in the light of the imposed functional and regulatory requirements by governmental agencies.

#### Futuristic virtualization platform

With the advent of cloud computing the systems of the future will become very complex with possibly thousands of cores running in parallel on a single silicon die. All of those cores could be tightly packed to form a data center on a chip which works on Cloud on a Chip (CoC) [23] paradigm. Virtualization platforms like the one shown in Fig. 1.4 can be an ideal solution for cloud computing. The hardware abstraction layer (HAL) is a small piece of software which interacts with the naked hardware and runs on top of it. Intel calls this hardware abstraction layer as Hypervisor, Microsoft calls it as Hyper-V and other vendors call it as Virtual Machine Monitor (VMM). There will be multiple operating systems running on the hardware simultaneously. Multiple users will be logged into those operating systems running multiple applications. The hardware abstraction layer provides access to the hardware resources and make them visible to the guest operating systems. The guest operating systems may not need to know the existence of other operating systems running in parallel. This increases the system robustness and stability. The time to deploy and debug new operating systems and applications without jeopardizing existing ones is a feature inherent to this technology. Such futuristic virtualization platforms would suffer from immense thermal challenges and needs dynamic thermal management techniques to be deployed.

#### 1.2 Temperature Issues with 3D Stacked Systems

The processes required for stacking active device layers while preserving the intrinsic electrical characteristics of on-chip devices has been demonstrated by the industry [24]. On the other hand, several 3D chip design strategies that exploits the vertical dimension thereby facilitating heterogeneous integration technologies has also been demonstrated by the academia [25]. Therefore, three-dimensional (3D) integrated circuits have been proposed which would overcome the problems associated with the interconnects and the limits that are being posed by the traditional CMOS scaling [26]. At the same time, there exists several challenges in designing 3D integrated circuits. Some of them include the problem of placement, floorplanning and insertion of thermal-vias. Several techniques have been proposed to solve these issues [27] [28].

Thermal problems are also exacerbated with the transition from 2D chip systems to 3D stacked system [29]. 3D integrated circuits take advantage of

Figure 1.4: Futuristic virtualization platform.

dimensional scaling approach and are seen as a natural progression towards future large and complex systems. They increase device density, bandwidth and speed. On the other hand, due to increased integration, the amount of heat per unit footprint increases, resulting in higher on-chip temperatures and thereby degrading the performance and reliability of the system. In this case, heat sinks need to be very efficient in transferring the internally generated heat to the ambient. Most modern flip-chip devices [30] are designed to operate reliably with a junction temperature falling under a certain range. To ensure that the package can perform thermally well under this range a thermal model is simulated and tested. This thermal model can then be used to gauge the reliability of the package. This shortens the package development time and also provides an important analytical tool to evaluate its performance under different operating conditions.

#### 1.3 Thermal Control Optimization Strategies

As the increase in temperature is directly related to power consumption of the chip, most of the power reduction techniques can be touted as modes to reduce temperature as well. But, in reality temperature reduction is a more complex problem. It is because, power is mainly an instantaneous effect, whereas increase in temperature is a long term process which is spread in both space and time. Temperature also depends on the physical properties of the chip layout and are not captured very well by just doing power reduction analysis (for example, metallization and thermal propagation) [31].

An excellent way to address temperature issues during design time is to ensure that circuit blocks are placed in such a way that they even out the thermal profile: in other words, using temperature-aware placement. Simplistically speaking, if we spread high-power cells across the chip evenly, the temperature profile will be flat and we can avoid hot-spot related thermal issues. In reality though, thermal placement is a more complex problem, and a uniform distribution of power sources does not lead to uniform temperature [31].

It has been shown that for large multi-core 3D systems minimizing power is only part of the thermal optimization goal without sacrificing performance. The use of active liquid cooling is needed in future 3D servers and other temperature reduction techniques need to be explored for efficient thermal management [32]. It is clear that the cooling technology that gives the best results without sacrificing performance are always active (external cooling) options, but they cost power which can be quite high if they are not combined with other thermal optimizations [33] [32].

It should be noted that it is not completely possible to make a full categorization of thermal-control benefits for different thermal optimization techniques as they are dependent on various factors like how accurately the workloads are known, how tight the timing deadlines are, how close the utilization of the system is with respect to the maximum load, etc. As a general rule of thumb, the most effective thermal control optimization strategies which do not degrade performance are [33]:

- 1. At design time, we must correctly choose the architectural components and place them on the layout based on the expected application loads (memory access, computing power, etc.).

- 2. At run time, the longer we apply the operating system level corrections, the better results we get, but this implies that one has to have full knowledge of the possible workloads and arrival times of application jobs, which is a restrictive precondition.

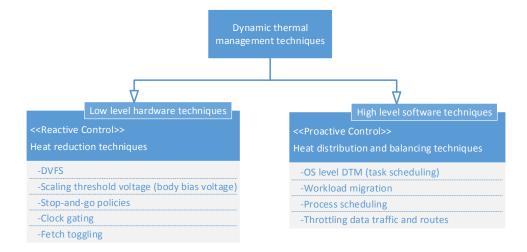

Different thermal control mechanisms like dynamic voltage and frequency scaling (DVFS) [34], scaling threshold voltage (or body bias voltage), changing the workload, throttling traffic and routes [35] can be employed to great effect to improve the thermal performance and reliability of the overall system. There are several hardware mechanisms like hardware counters for cores and memories, integrated thermal sensors among others, which can be used to get an idea of temperature of the system under different workload conditions and which form the basis for broader thermal management of the system.

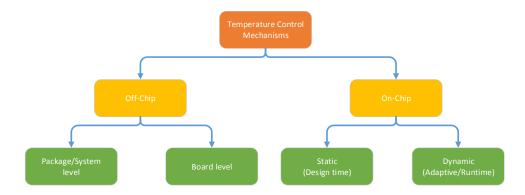

A more detailed and broad classification of the state-of-the-art temperature control strategies and their principles are described in chapter 2. There, we classify the strategies into off-chip and on-chip ones. Later we delve deep into the on-chip temperature control techniques which we further classify into static (design time) thermal management and dynamic/runtime (adaptive) thermal management techniques. We present the context and perspective for the thesis and show where exactly our contributions fit in that larger context.

#### 1.4 Thesis Objectives

Motivated by the aforementioned observations, this thesis targets: (1) Understanding and identifying the problem of increased temperature contributed by different components of the system by performing extensive thermal modeling and analysis based simulations; (2) developing novel thermal sensing and thermal management techniques. More precisely, the objectives of this thesis include:

- 1. To build a novel self-timed thermal sensing architecture which converts analog temperature information into digital form. The objective is also to make the sensing architecture more resilient towards various types of noise variations that may occur in the system and also prove that the system is robust enough under different operating temperatures.

- 2. To understand and identify the problem of temperature that is contributed by various system components such as interconnects, analyse the effect of packaging on the thermal performance of the system, and to tackle the thermal problems in the emerging 3D stacked systems.

- 3. To develop a thermally efficient interlayer communication algorithm for 3D stacked NoC architectures. The objective is to hybridize a proposed congestion-aware routing algorithm with other available algorithms and mitigate the thermal issues by herding most of the switching activity closer to the heatsink where most of the thermal conduction happens.

- 4. To develop an efficient thermal-aware application mapping algorithm for 2D planer NoC platforms. The objective of this multi-application mapping algorithm is to best place the blocks which are hotspot prone within a region dedicated for a particular application on the 2D NoC by using a set of extracted metrics obtained from extensive thermal modeling and analysis based simulations. How the presented placement algorithm can keep a balance between temperature on the chip and its performance while running applications is a major consideration.

#### 1.5 Thesis Contributions

To reach the objectives that were set for this thesis, we have built several thermal models and carried out extensive simulations for 2D NoC and 3D stacked NoC architectures. We started our investigations by developing a novel thermal sensing circuit which can be used in a thermal sensing and monitoring infrastructure. Our later work on thermal modeling and analysis of interconnects and 3D stacked systems laid the ground work for a thermally efficient inter-layer communication scheme for 3D NoC systems and an efficient thermal-aware mapping algorithm for a 2D NoC system. The proposed thermal management scheme which relies on herding most of the switching activity to the die closer to the heat sink in a 3D stacked system can be combined with our novel thermal-aware mapping technique for additional thermal safety. This section summarises the main contributions of this thesis work. They are:

- 1. One of the most cost-effective and accurate temperature measurement technique is the use of thermal sensors in the system. We proposed a self-timed thermal monitoring strategy which is based on the use of thermal sensors. Since leakage currents are sensitive to temperature and increase with scaling, we propose the use of a leakage current based thermal sensing for monitoring purposes. We have implemented a novel thermal sensing circuit, which converts analog temperature information into digital form. We have also proposed a novel thermal sensing and monitoring interconnection network structure based on self-timed signaling, comprising of an encoder/transmitter and decoder/receiver. We have performed power supply noise, additive noise on sensor input signal and dynamic power supply voltage variation analysis on the thermal sensing circuit and show that it is robust enough under different operating temperatures.

- 2. The complexity of addressing the issue of temperature is such that, that one has to address it starting from earliest design stages of the system. The early design choices like the number and complexity of cores, types of materials and packaging used, dictate the temperature patterns of the system. As a result system designers have begun to study thermal management issues from the early design stages. In order to do so, accurate thermal modeling and analysis at design time is essential. We performed thermal analysis on interconnects and 3D stacked systems by building various thermal models. More specifically,

- (a) We analysed the spatial temperature profile of global Cu nanowire for on-chip interconnects. The impact of the temperature rise

- along the interconnects has been analysed with two different signal transmission systems namely current-mode and voltage-mode signaling.

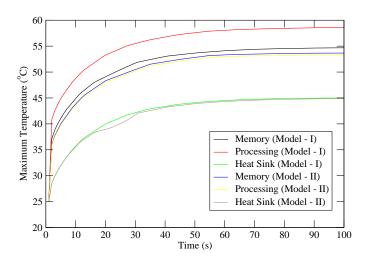

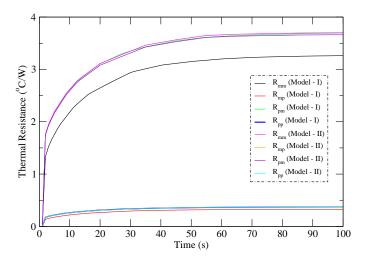

- (b) A 3D thermal model of a multicore system is developed to investigate the effects of hotspot, and placement of silicon die layers, on the thermal performance of a modern flip-chip package. In this regard, both the steady-state and transient heat transfer analysis has been performed on the 3D flip-chip package. Two different thermal models were evaluated under different operating conditions. Through experimental simulations, we have found a model which has better thermal performance. The optimal placement solution is also provided based on the maximum temperature attained by the individual silicon dies. We have also provided the improvement that is required in the heat sink thermal resistance of a 3D system when compared to the single-die system.

- 3. One of the primary design goal of any high-performance system is the maximization of performance within the given power and thermal envelopes. If the system is a 3D stacked system, the temperature problem is all the more prominent due to the increased power density. Hence there is an urgent need for thermal management in 3D stacked systems. So, we proposed a thermally efficient routing strategy for 3D NoC-Bus hybrid architectures, which helps in mitigating the on-chip temperatures by herding most of the switching activity to the die which is closer to the heat sink. Our simulations with a real world benchmark show that there has been a decrease in the peak temperatures when compared to a typical stacked mesh 3D NoC architecture.

- 4. An exploration of various thermal-aware placement approaches for both the 2D and 3D stacked systems is presented. We have developed various thermal models which were used to investigate the effect of thermal-aware placement in 2D chip and 3D stacked systems. A set of metrics were developed which were used to propose an efficient thermal-aware application mapping algorithm for a 2D NoC. Our extensive steady-state simulations show that the proposed thermal-aware mapping algorithm reduces the effective area reeling under high temperatures when compared to the *Tree-Model-Based (TMB)* mapping and *Worst case* mapping.

#### 1.6 Research Publications

The work presented in this thesis is based on and extended from the following peer-refereed journal/articles and peer-refereed conference proceedings. The contributions of the author in the multi-authored publications has also been elucidated.

- Kameswar Rao Vaddina, Amir-Mohammad Rahmani, Mohammad Fattah, Pasi Liljeberg, Juha Plosila, "Design space exploration of thermal-aware many-core systems", Journal of Systems Architecture, Volume 59, Issue 10, Part D, November 2013, Pages 1197-1213, ISSN 1383-7621. http://dx.doi.org/10.1016/j.sysarc.2013.08.007. [36]

- Author's contributions: The author contributed with a well-structured problem formulation, algorithm for thermally-efficient inter-layer communication scheme is developed in cooperation with Amir-Mohammad Rahmani, thermal-aware mapping algorithm has been developed in cooperation with Mohammad Fattah, performed thermal simulations and wrote most of the manuscript. System-level simulations for 2D NoC and 3D NoC are performed by Mohammad Fattah and Amir-Mohammad Rahmani respectively.

- Kameswar Rao Vaddina, Pasi Liljeberg and Juha Plosila. "Exploration of Temperature-Aware Placement Approaches in 2D and 3D Stacked Systems." International Journal of Adaptive, Resilient and Autonomic Systems (IGI-Global IJARAS), Vol. 4, No. 3, pp 61-81, 2013. http://dx.doi.org/10.4018/jaras.2013070104. [37]

- Author's contributions: The author contributed with a well-structured problem formulation, performed thermal simulations and wrote the entire manuscript.

- 3. Rahmani, A-M., Khalid Latif, Kameswar Rao Vaddina, Pasi Liljeberg, Juha Plosila, and Hannu Tenhunen. "Congestion aware, fault tolerant, and thermally efficient inter-layer communication scheme for hybrid NoC-bus 3D architectures." In Networks on Chip (NoCS), 2011 Fifth IEEE/ACM International Symposium on, pp. 65-72. IEEE, 2011. [38] Author's contributions: The author contributed with a well-structured problem formulation, performed thermal simulations for the hybrid NoC-bus 3D architectures and wrote the manuscript.

- Kameswar Rao Vaddina, Amir-Mohammad Rahmani, Khalid Latif, Pasi Liljeberg, Juha Plosila, "Thermal Analysis of Job Allocation and Scheduling Schemes for 3D Stacked NoC's." In Digital System Design (DSD), 2011 14th Euromicro Conference on, pp. 643-648. IEEE, Oulu, 2011. [39]

Author's contributions: The author contributed with a well-structured problem formulation, performed thermal simulations and wrote the entire manuscript.

5. Kameswar Rao Vaddina, Tamoghna Mitra, Pasi Liljeberg, and Juha Plosila. "Thermal modelling of 3D multicore systems in a flip-chip package." In SOC Conference (SOCC), 2010 IEEE International, pp. 379-383. IEEE, 2010. [40]

Author's contributions: The author contributed with a well-structured problem description, built thermal models and performed thermal simulations with Tamoghna Mitra, and wrote the entire manuscript.

Kameswar Rao Vaddina, Ethiopia Nigussie, Pasi Liljeberg, and Juha Plosila. "Self-timed thermal sensing and monitoring of multicore systems." In Design and Diagnostics of Electronic Circuits & Systems, 2009. DDECS'09. 12th International Symposium on, pp. 246-251. IEEE, 2009. [41]

Author's contributions: The author contributed with a well-structured problem formulation, performed simulations and wrote the entire manuscript.

Kameswar Rao Vaddina, Pasi Liljeberg, and Juha Plosila. "Thermal analysis of on-chip interconnects in multicore systems." In NORCHIP, 2009, pp. 1-4. IEEE, 2009. [42]

Author's contributions: The author contributed with a well-structured problem formulation, performed thermal simulations and wrote the entire manuscript.

#### 1.7 Organization of Thesis

The rest of the thesis is organized into 7 chapters. In Chapter 2 we broadly classify the state-of-the-art temperature control techniques and provide their working principles and implementation details. Later, we introduce the concepts of Networks-on-Chip (NoC), 3D NoC's, and describe the problems of temperature associated with those systems and delve into the reasons as to why it is important to deal with those issues at all levels of system abstraction. This chapter puts the contributions of this thesis into context and perspective. Chapter 3 introduces to the self-timed thermal sensing and monitoring approach for multicore systems. It provides a novel thermal sensing architecture and proposes a unique sensing interconnection network. Various noise and supply voltage variation analysis has been detailed in this chapter. The Chapter 4 is divided into two important sections, one of which studies the thermal performance of on-chip interconnects in multicore systems and the other deals with thermal modeling and analysis of 3D stacked systems in a Flip-Chip package. Chapter 5 introduces hybrid

NoC-bus 3D architecture and proposes a thermally efficient routing strategy for 3D NoC's which helps in mitigating on-chip temperatures by routing most of the switching activity closer to the heat sink. Chapter 6 presents an exploration of thermal-aware placement approaches for 2D and 3D systems. It starts by arriving at various metrics which provide thermal guidance to circuit designers. Using the developed metrics a thermal-aware application mapping for a 2D NoC system has been developed and simulation results presented. Finally, Chapter 7 concludes this thesis and presents possible direction towards future research work on thermal-aware software programming.

## Chapter 2

# Thermal Management Techniques for Microprocessors

Temperature related challenges in modern microprocessor architectures has emerged as one of the key design constraints during the past several years. Higher on-chip temperatures are posing significant reliability concerns thereby causing thermal wear-outs of chips. Thermal wear-outs are the result of several aging mechanisms like electro-migration, hot-carrier injection, negative bias temperature instability (NBTI) and dielectric breakdown. These aging mechanisms are exponentially dependant on temperature. In the case of FPGAs, one of the most important wear out mechanisms are the failure of antifuses. Depending on the physics of the failure mechanism, additional stresses, such as elevated current or voltage, accelerates these failures [43].

Temperature induced errors in on-chip interconnects are also becoming a major cause for concern as the links become more susceptible to faults with the scaling down of technology. Defective links show unacceptably high resistance and therefore increase propagation delays [44]. As their resistivity drops with increasing temperature, the operating frequency of the chip degrades further. While most faults are temporary, about 20% of all errors are caused by permanent or intermittent (lasting up to several cycles) faults [44]. These faults occur because of manufacturing defects or run-time variations, such a multi-cycle delay failures during extended high temperature conditions or permanent faults caused by thermal runaway.

Given that supply voltage is not scaling commensurate to decrease in feature sizes, and the impending approach to the limits of possible air cooling, it is predicted that power densities will continue to rise even if micro-architectural complexity stops increasing [7]. Li et al [45] have concluded that for aggressive cooling solutions, reducing power density is at

least as important as reducing total power consumption. Whereas, for low-cost cooling solutions, reducing total power is more important, as raising power dissipation raises on-chip temperatures even if the power density remains constant [45]. Also, ambient temperatures can vary a lot and hence detailed package models are needed to understand the thermal behaviour of the system under various workloads. For example, depending on the field of application, electronic components are required to operate at different ambient temperatures. Many computing based and factory applications are required to operate at a maximum ambient temperature of 60°C and under natural convection and forced air-cooling [46]. Whereas, for automotive sector, the specified maximum ambient temperature under which the electronic components are supposed to operate for passenger compartment and for under the hood use is around 85°C and 105°C respectively [46]. Hence, any inadequate thermal management and control would lead to a complete system failure.

As discussed in the previous chapter, temperature is a more complex problem and hence the system designers should try to solve it at different levels of design flow, starting from the very early design stages. The early design choices like the number and complexity of cores, types of materials and packaging used, dictate the temperature profile of the system. Hence, in order to arrive at efficient thermal management techniques, accurate thermal modeling and analysis is warranted at design time. But, due to the involvement of complex equations of heat transfer, for thermal simulations and the heavy dependence of RC thermal time constant on environmental, material and packaging parameters, making accurate thermal simulations at design time is complex and time consuming process without the involvement of proper simulation tool chains [47] [48].

# Power Consumption Trends for Portable and Stationary Systems

The power consumption and power efficiency requirements for mobile/portable systems is considerably different from the stationary systems which are always plugged into the power source. The power consumption trends for both of those systems are presented below.

### Consumer Portable Devices

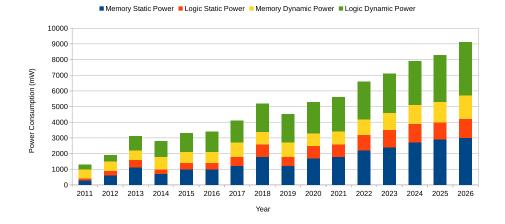

The current and future power consumption trends for mobile and portable platforms as given by the ITRS roadmap [3] is shown in Fig. 2.1. The figure depicts the total power consumption which is decomposed into static and dynamic power across both the logic and memory. The power consumption

Figure 2.1: Future trends for static and dynamic power for both the logic and memory [3]

trends far exceed the power efficiency requirements [3]. This, combined with the global quest for greener and more energy efficient portable consumer products will lead to a more power-centric designs for the future.

### **Stationary Devices**

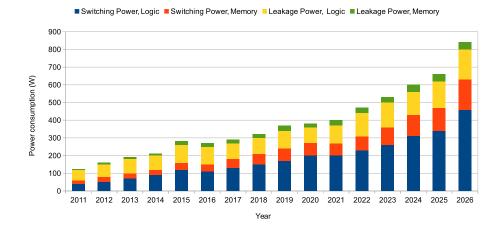

The current and future power consumption trends for devices which are stationary and do not have any battery life issues, as given by the ITRS roadmap [3] is shown in Fig. 2.2. The figure depicts the total power consumption which is decomposed into switching and leakage power across both the logic and memory. A look at the trends leads us to believe that the huge increase in power consumption will result in increased chip packaging and cooling costs. At the same time, due to variability and temperature effects, the leakage power might be much greater than what is shown in the Fig. 2.2.

## 2.1 Power Management vs Thermal Management

A simple equation which is used to measure the operating temperature of a chip and one which gives the relationship between chip power and temperature can be represented by the following linear equation [1]:

$$T_{chip} = T_a + R_{\theta} \cdot \frac{P_{tot}}{A} \tag{2.1}$$

where  $T_{chip}$  is the average silicon junction temperature,  $T_a$  is the ambient temperature,  $R_{\theta}$  is the equivalent thermal resistance of the silicon (Si)

Figure 2.2: Future trends for switching and leakage power for both the logic and memory [3]

substrate, its package and heat sink (in  $cm^2$  °C/W),  $P_{tot}$  is the total power dissipation ( $P_{dynamic} + P_{short-circuit} + P_{static}$ ) of the circuit and A is the total chip area in  $cm^2$ .

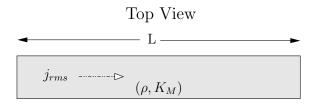

The temperature of the metal interconnect can be represented by the following self-heating equation [49]:

$$T_{metal} = T_{chip} + \Delta T_{self} \tag{2.2}$$

$$\Delta T_{self} = R_E I_{rms}^2 R_{\theta, self} \tag{2.3}$$

where  $\Delta T_{self}$  is the temperature rise of the metal interconnect due to the flow of current  $(I_{rms})$ ,  $R_E$  is the electrical resistance of the interconnect wire, and  $R_{\theta,self}$  is the thermal impedance of the interconnect line to the substrate.

As the increase in temperature is directly related to the chip power dissipation, reducing it would in fact reduce power density and thus help control on-chip temperature issues. However, reducing power alone is not always an effective strategy and may indeed conflict with thermal management [48]. That means, power density increases when underused system components are turned off to reduce power and thereby concentrating more system activity in a smaller area. Conventional power saving techniques typically have very less impact on processor performance, as they try to take advantage of the under-utilization of the processor resources [50]. Whereas, thermal management is mainly a concern when the processor is very heavily used

and any power saving techniques could then hamper the performance of the system [48].

Conventional power management techniques which are used for energy efficiency, might have very limited impact on temperature, as they may target system units which might not be hot at all. Also, power is mainly an instantaneous effect, whereas increase in temperature is a long term process which is spread across in both space (due to the material mass of the silicon die) and time (microseconds or longer). Temperature also depends on the physical properties of the chip materials and also its dimensions and layout, which are not captured very well by just doing power reduction analysis. For example phenomenon like metallization and thermal propagation cannot be captured by using just the power analysis [31]. This means that power management will only affect on-chip temperature if the power reduction optimizations are applied for a sufficiently longer duration. For all the above reasons, power management techniques which are traditionally been used for energy efficiency concerns may not have sufficient impact on thermal related issues. This is attributed to the fact that the energy efficiency policies may be different for both the cases and may even sometimes potentially be in conflict with each other [48].

# 2.2 Classification of Temperature Control Mechanisms