# Moazzam Fareed Niazi

A Model-Based Development and Verification Framework for Distributed System-on-Chip Architecture

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 171, March 2014

## A Model-Based Development and Verification Framework for Distributed System-on-Chip Architecture

### Moazzam Fareed Niazi

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Beta on March 26, 2014, at 12 noon.

University of Turku

Department of Information Technology

FIN-20014 Turku, Finland

2014

### Supervisors

Principal Scientist, Dr. Tiberiu Seceleanu ABB Corporate Research Forskargränd, 721 78 Västerås Sweden

Professor Hannu Tenhunen Adjunct Professor Pasi Liljeberg Department of Information Technology University of Turku FIN-20014 Turku Finland

### Reviewers

Professor Detlef Streitferdt Software Architectures and Product Lines Group Ilmenau University of Technology Helmholtzplatz 5, 98693 Ilmenau Germany

Dr. Vassilios A. Chouliaras School of Electronic, Electrical and Systems Engineering Loughborough University Ashby Road, Loughborough, Leicestershire, LE11 3TU United Kingdom

### Opponent

Professor Jari Nurmi Department of Electronics and Communications Engineering Tampere University of Technology FIN-33101 Tampere Finland

The originality of this thesis has been checked in accordance with the University of Turku quality assurance system using the Turnitin OriginalityCheck service.

ISBN 978-952-12-3028-8 ISSN 1239-1883

## Abstract

The capabilities and thus, design complexity of VLSI-based embedded systems have increased tremendously in recent years, riding the wave of Moore's law. The time-to-market requirements are also shrinking, imposing challenges to the designers, which in turn, seek to adopt new design methods to increase their productivity. As an answer to these new pressures, modern day systems have moved towards on-chip multiprocessing technologies. New architectures have emerged in on-chip multiprocessing in order to utilize the tremendous advances of fabrication technology.

Platform-based design is a possible solution in addressing these challenges. The principle behind the approach is to separate the functionality of an application from the organization and communication architecture of hardware platform at several levels of abstraction. The existing design methodologies pertaining to platform-based design approach don't provide full automation at every level of the design processes, and sometimes, the co-design of platform-based systems lead to sub-optimal systems. In addition, the design productivity gap in multiprocessor systems remain a key challenge due to existing design methodologies.

This thesis addresses the aforementioned challenges and discusses the creation of a development framework for a platform-based system design, in the context of the SegBus platform - a distributed communication architecture. This research aims to provide automated procedures for platform design and application mapping. Structural verification support is also featured thus ensuring correct-by-design platforms. The solution is based on a model-based process. Both the platform and the application are modeled using the *Unified Modeling Language*. This thesis develops a *Domain Spe*cific Language to support platform modeling based on a corresponding UML profile. Object Constraint Language constraints are used to support structurally correct platform construction. An emulator is thus introduced to allow as much as possible accurate performance estimation of the solution, at high abstraction levels. VHDL code is automatically generated, in the form of "snippets" to be employed in the arbiter modules of the platform, as required by the application. The resulting framework is applied in building an actual design solution for an MP3 stereo audio decoder application.

## Tiivistelmä

Sulautettujen järjestelmien tarjoama laskentakapasiteetti, niiden koko mitattuna transistorien määrällä sekä kompleksisuus ovat kasvaneet huomattavasti viimevuosien aikana Mooren lakia mukaillen. Näiden laitteiden tuotantovaatimukset ovat myös kiristyneet tehden suunnitteluprosessista entistä vaativamman suunnittelijoille. Tämä on pakottanut etsimään yhä uusia suunnittelumenetelmiä jotta pystytään vastaamaan kiristyneihin tuotantovaatimuksiin. Eräs vastaus näihin vaatimuksiin on ollut siirtyminen moniprosessorijärjestelmiin. Tämä teknologia puolestaan tuo uusia arkkitehtuuriasi haasteita ja mahdollisuuksia hyödyntää teknologisen kehityksen tuomia mahdollisuuksia.

Sovellusalustapohjainen suunnittelu on eräs ratkaisu näihin haasteisiin. Tämän paradigman kantavan ajatuksena on eriyttää kyseessä olevan sovelluksen funktionaalisuus ja järjestelmän sisäinen tiedonsiirto useilla eri abstraktio tasoilla. Olemassa olevat sovellusalustapohjaiset suunnittelumenetelmät eivät ole täysin automatisoituja kaikilla suunnitteluprosessin osaalueilla. Lisäksi järjestelmän sisäinen tiedonsiirto aiheuttaa ongelmia tässä prosessissa, sillä useasti järjestelmät eri osat eivät ole täysin yhteensopivia.

Tässä väitöskirjatyössä pyritään ratkaisemaan yllämainittuja ongelmia sekä esitetään kehitetty sovellusalustapohjainen sulautettujen järjestelmien suunnittelumenetelmä. Menetelmää on sovelluttu hajautettuun SegBus kommunikaationa arkkitehtuuriin. Tähän liittyen työssä on kehitetty automatisoituja menetelmiä sekä alustan suunnitteluun että sovellusten vaatimien resurssien sijoitteluun kyseiseen järjestelmään. Menetelmä tukee strukturaalista oikeellisuuden varmistamista joka perustuu mallipohjaiseen lähestymistapaan. Objektipohjaista konseptia on sovellettu tukemaan strukturaalisesti oikeellista rakenteen varmistamista. Työssä on kehitetty myös emulaattori, jonka avulla on mahdollista arvioida tarkasti suorituskykyä. Työssä kehitetty sovellusalustapohjaista menetelmää on sovellettu audiojärjestelmän dekoodaukseen.

To the memory of my beloved mother (1958-2007)

## Acknowledgments

First praise is to ALLAH, the Almighty, on whom ultimately we depend for sustenance and guidance. Without His help and blessings, I was not able to bring this work to its completion.

The completion of this doctoral thesis is an exciting moment of my life and I am feeling glad while writing this part of my thesis. I would like to express my gratitude to several people and institutions that have influenced the research work presented in this thesis.

First and foremost, I would like to express my heartfelt gratitude to my first two supervisors, Adjunct Professor *Tiberiu Seceleanu* and Professor *Hannu Tenhunen*, for their guidance, encouragement and support that they have provided to me during the course of this work. Especially, I wish to thank Dr. *Tiberiu Seceleanu* for considering me for this research work, and for all the support and guidance that he provided to me on numerous occasions in Turku as well as in Västerås. I have always experienced the true inspiration from him every time we discussed the ongoing work in a much friendlier environment.

I would also like to extend my gratitude to my third supervisor Adjunct Professor *Pasi Liljeberg* for comprehensive guidance throughout my doctoral studies, and especially for handling the practical matters during the last phase of this work. I am also very thankful to Dr. *Dragoş Truşcan* and Dr. *Torbjörn Lundkvist* from Åbo Akademi for providing me guidance related to UML modeling and tools in the start of this research work.

I would also like to thank Professor *Detlef Streitferdt* from Ilmenau University of Technology, Germany and Dr. *Vassilios A. Chouliaras* from Loughborough University, United Kingdom for the detailed reviews and constructive feedback on this thesis. Furthermore, I wish to sincerely thank Professor *Jari Nurmi* from Tampere University of Technology, Finland for accepting to be the opponent in the public defense of my thesis.

I gratefully acknowledge the financial support from different institutions that made this research work possible. I am grateful to Academy of Finland and Turku Centre for Computer Science (TUCS) for providing me the financial support during the initial four years of this research work. I

wish to express my sincerest gratitude to TES-Tekniikan edistämissäätiö and University of Turku Graduate School (UTUGS) for their financial support through incentive grants on two different occasions.

I owe my deepest gratitude to my friend Dr. Qaisar Malik for all the support, help and kindness that he has provided to me while he was completing his doctoral studies in Åbo Akademi. I wish to appreciate him for everything that he has done for me during all those years we spent together in Turku. Similarly, I would also like to take this opportunity to thank my oldest friend Ali Hanzala Khan for providing me a pleasant company during all those years which we have spent together in Pakistan, Sweden and Finland as well. He always showed me that there is a life outside the academic environment. Moreover, I am also grateful to Syed Asad Jafri, Ali Shuja Siddiqui, Fareed Ahmed Jokhio, Adnan Ashraf and many others for providing me a good company during my stay in the ICT House, and also to all others for exchanging smiles and saying greetings while passing through the department corridors.

I would also like to extend my gratitude to my teachers from my former university (Bahria University, Pakistan): Dr. *Muhammad Mohiuddin*; Dr. *Syed Aley Imran Rizvi*; and *Salman Zafar*. Their continuous motivation throughout my post-graduate studies kept my mind fertile, productive and focused to my career goals.

I would also like to thank all the secretaries especially *Irmeli Laine*, *Maria Prusila*, *Heli Vilhonen*, *Päivi Rastas*, administrative and support staff especially *Tomi Mäntylä* and *Sami Nuuttila*, both at TUCS and Department of Information Technology of the University of Turku for running the departments in an efficient and hassle-free manner.

Most importantly, none of this would have been possible without the best wishes, love, prayers and patience of my family. I am truly indebted to my mother for everything that she has done for me. Although she is no longer with us but she will be remembered for the rest of my life. I also gratefully acknowledge the support and motivation from my father and all my brothers, especially the elder ones. I am truly thankful to all of them.

Finally, I am truly grateful for the all the support, understanding and love from my wife throughout the time we spent together while completing this research work and writing this thesis as well. I appreciate her for all the unconditional support, patience and nice advices that she provided to me in difficult times.

Turku, March 2014 Moazzam Fareed Niazi "Seek knowledge from the cradle to the grave."

Prophet Muhammad (Peace and blessings be upon him)

## Contents

| 1        | Intr | oduction 1                                            |

|----------|------|-------------------------------------------------------|

|          | 1.1  | The Y-chart approach                                  |

|          | 1.2  | The Model-Based Paradigm and UML 5                    |

|          | 1.3  | Design and Verification Challenges 6                  |

|          | 1.4  | Thesis Approach and Contributions 8                   |

|          | 1.5  | Related Work                                          |

|          | 1.6  | Research Publications                                 |

|          | 1.7  | Summary of the Research Publications                  |

|          | 1.8  | Thesis Organization                                   |

|          | 1.9  | Thesis Navigation                                     |

| <b>2</b> | The  | SegBus Platform 21                                    |

|          | 2.1  | Platform Communication                                |

|          | 2.2  | Platform Characteristics                              |

|          |      | 2.2.1 Topology                                        |

|          |      | 2.2.2 Number of Segments                              |

|          |      | 2.2.3 Package Size                                    |

|          | 2.3  | Platform Constraints                                  |

|          | 2.4  | Summary                                               |

| 3        | The  | Model-based Development and Verification Framework 29 |

|          | 3.1  | Design Methodology                                    |

|          | 3.2  | Model-Based Development Paradigm                      |

|          | 3.3  | The Unified Modeling Language                         |

|          | 3.4  | The Object Constraint Language                        |

|          | 3.5  | The SegBus UML Profile                                |

|          | 3.6  | Application Modeling using the P-SDF                  |

|          | 3.7  | DSL for the SegBus Platform                           |

|          |      | 3.7.1 The SegBus Component Library                    |

|          |      | 3.7.2 Extensible Markup Language 41                   |

|          |      | 3.7.3 Model Transformation                            |

|          | 3.8  | The SegBus Emulator                                   |

|    | 3.9   | The VHDL Snippets                                        | 13 |

|----|-------|----------------------------------------------------------|----|

|    | 3.10  | Summary                                                  | 13 |

|    |       |                                                          |    |

| 4  | _     |                                                          | 5  |

|    | 4.1   | 1                                                        | 16 |

|    | 4.2   |                                                          | 18 |

|    | 4.3   |                                                          | 51 |

|    | 4.4   | 0 1                                                      | 53 |

|    |       | v                                                        | 53 |

|    |       | 1 11                                                     | 58 |

|    |       | 4.4.3 Plug-in Setup                                      | 35 |

|    | 4.5   | Summary                                                  | 66 |

| 5  | Segl  | Bus Emulator 6                                           | 9  |

|    | 5.1   | Basic Concepts                                           | 70 |

|    | 5.2   | -                                                        | 71 |

|    | 5.3   |                                                          | 74 |

|    | 5.4   | <del>-</del>                                             | 78 |

|    | 5.5   |                                                          | 36 |

|    | 5.6   |                                                          | 37 |

| 6  | The   | VHDL Snippets 8                                          | 89 |

| Ü  | 6.1   |                                                          | 90 |

|    | 6.2   |                                                          | )4 |

|    | 6.3   |                                                          | )7 |

| 7  | The   | Overall Framework 9                                      | 9  |

| •  | 7.1   | Example using the Framework                              |    |

|    | 1.1   | 7.1.1 Application Partitioning and Modeling              |    |

|    |       | • • • • • • • • • • • • • • • • • • • •                  |    |

|    |       |                                                          |    |

|    |       |                                                          |    |

|    |       | 7.1.4 Model transformation of the example application 10 |    |

|    |       | 7.1.5 Execution with 3-Segments Configuration            |    |

|    |       |                                                          |    |

|    |       | 7.1.7 Emulation Results                                  |    |

|    | 7.0   | 7.1.8 VHDL "Snippets" Generation                         |    |

|    | 7.2   | Discussion                                               |    |

|    | 7.3   | Summary                                                  | .3 |

| 8  |       | clusions 11                                              |    |

|    | 8.1   | Thesis Contributions                                     |    |

|    | 8.2   | Future Directions                                        | 6  |

| Bi | bliog | raphy 11                                                 | .8 |

# List of Figures

| 1.1          | Comparison of gaps among other important trends of SoC design [18]             | 2  |

|--------------|--------------------------------------------------------------------------------|----|

| 1.2          | The Y-chart approach [30]                                                      | 4  |

| 1.3          | Navigation of the thesis                                                       | 20 |

| 2.1          | Traditional bus-based system                                                   | 21 |

| 2.2          | Segmented bus structure [20][50]                                               | 22 |

| 2.3          | Inter-segment package transfer                                                 | 24 |

| 2.4          | Difference between linear and circular topologies                              | 25 |

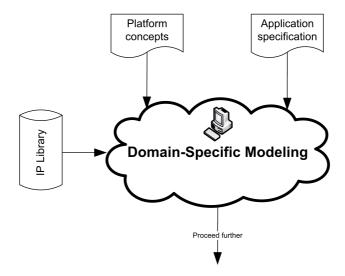

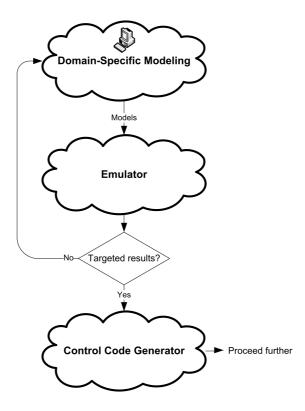

| 3.1          | The macro-level view of the $SegBus$ design process based on                   |    |

|              | the proposed framework                                                         | 30 |

| 3.2          | UML language units / diagrams                                                  | 34 |

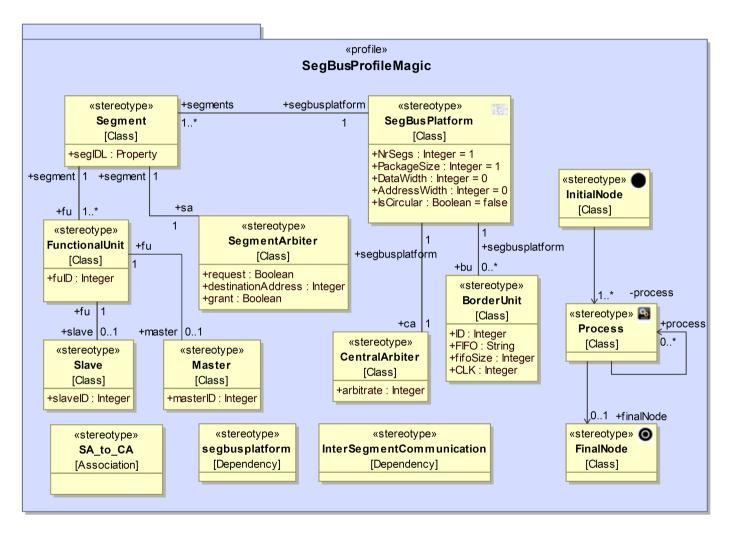

| 3.3          | The SegBus profile elements [38]                                               | 37 |

| 3.4          | The micro-level view of the proposed framework and its internal distinct units | 40 |

| 3.5          | The SegBus library component structure                                         | 41 |

| $4.1 \\ 4.2$ | High-level design entry to application development                             | 45 |

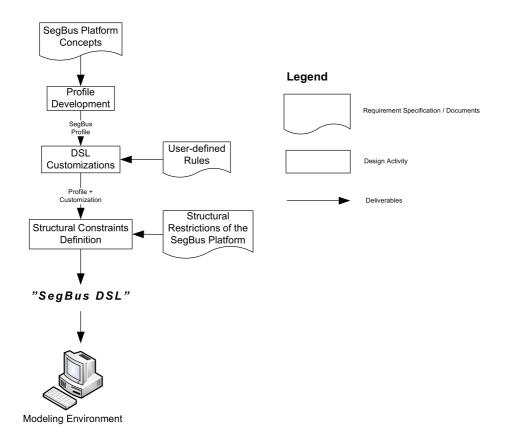

| 1.2          | DSL                                                                            | 46 |

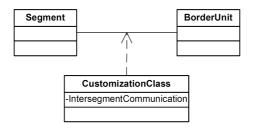

| 4.3          | Platform elements and their association in profile                             | 47 |

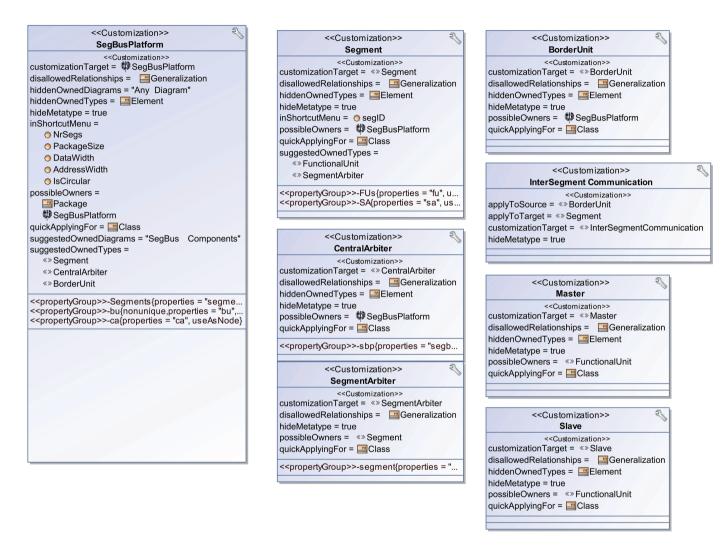

| 4.4          | DSL Customization classes for each element of the SegBus                       |    |

|              | platform                                                                       | 49 |

| 4.5          | User-defined rules for different attributes of the Customiza-                  |    |

|              | tion classes                                                                   | 50 |

| 4.6          | Dependency link between two profile elements                                   | 51 |

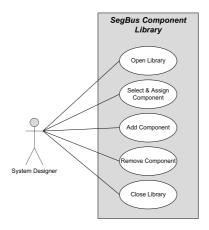

| 4.7          | Use case model of the $SegBus$ components library                              | 55 |

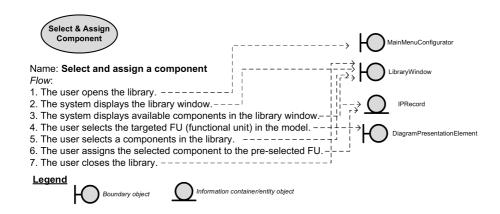

| 4.8          | An analysis model of a "Select and assign component" use-case.                 | 57 |

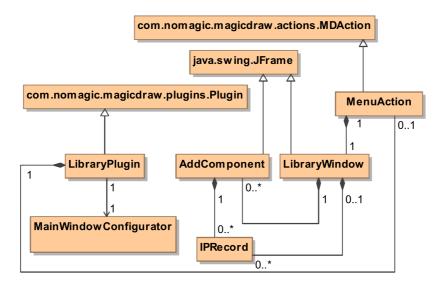

| 4.9          | The class diagram of the $SegBus$ components library                           | 58 |

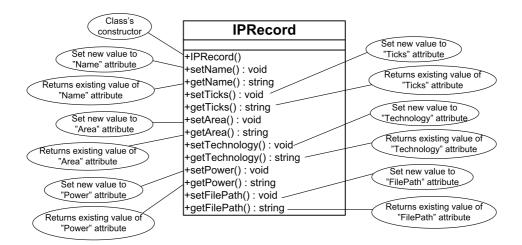

| 4.10         | IPRecord class structure and operations' description                           | 59 |

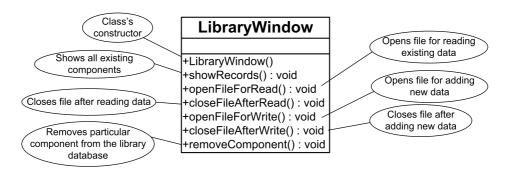

| 4.11         | Library Window class structure and operations' description                     | 60 |

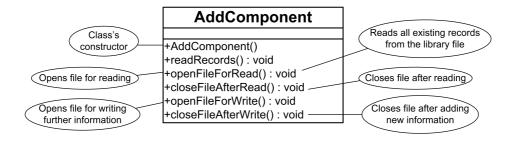

| 4.12         | AddComponent class structure and operations' description                       | 61 |

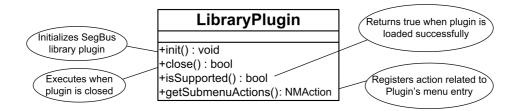

| 4.13         | Library Plugin class structure and operations' description                     | 63 |

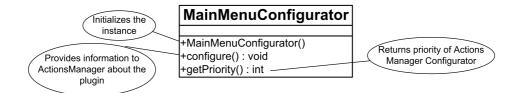

| 4.14 | MainMenuConfigurator class structure and description of its                             |

|------|-----------------------------------------------------------------------------------------|

|      | methods                                                                                 |

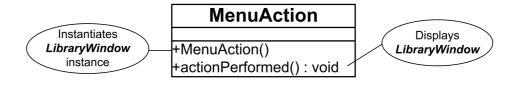

| 4.15 | MenuAction class structure and operations' description 64                               |

| 5.1  | High-level view of design entry to SegBus emulator 69                                   |

| 5.2  | Operating flow of the emulator                                                          |

| 5.3  | Hierarchical structure of the SegBus profile elements 73                                |

| 5.4  | P-SDF model of an example application                                                   |

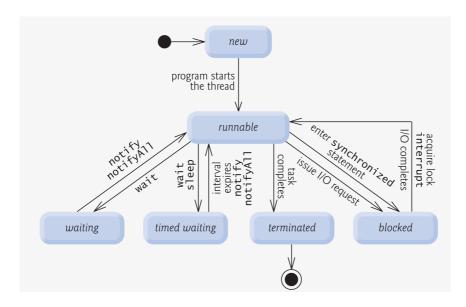

| 5.5  | Thread life cycle in different states [9]                                               |

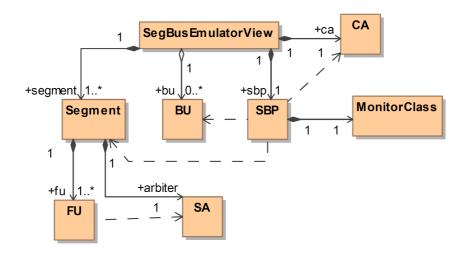

| 5.6  | Class diagram of the emulator application 80                                            |

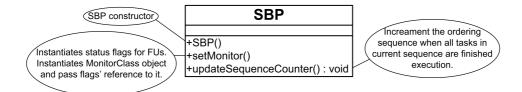

| 5.7  | SBP class operations' description 80                                                    |

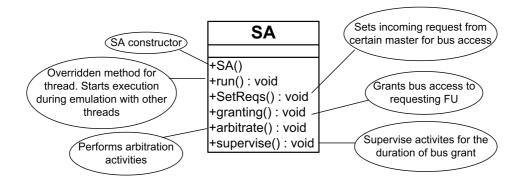

| 5.8  | SA class operations' description 81                                                     |

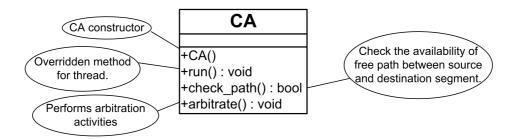

| 5.9  | CA class operations' description                                                        |

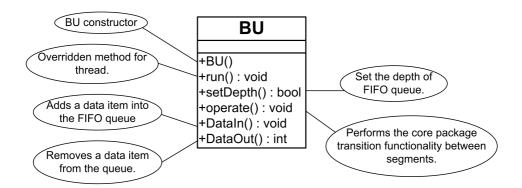

| 5.10 | BU class operations' description                                                        |

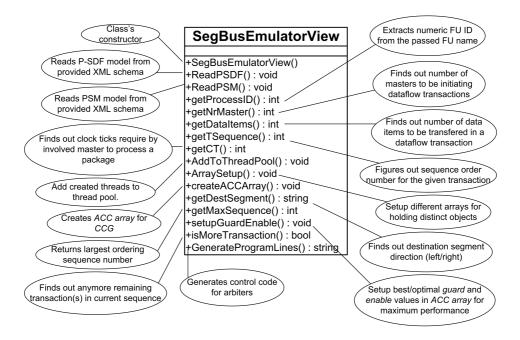

| 5.11 | SegBusEmulatorView class operations' description 84                                     |

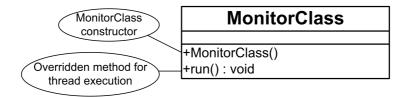

| 5.12 | MonitorClass class operations' description                                              |

| 6.1  | High-level view of design and verification activities leading to                        |

|      | ultimate code generation                                                                |

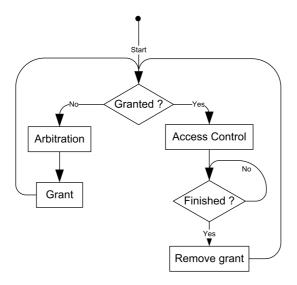

| 6.2  | Arbiter control flow [41]                                                               |

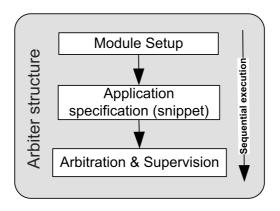

| 6.3  | Arbiter code structure [41]                                                             |

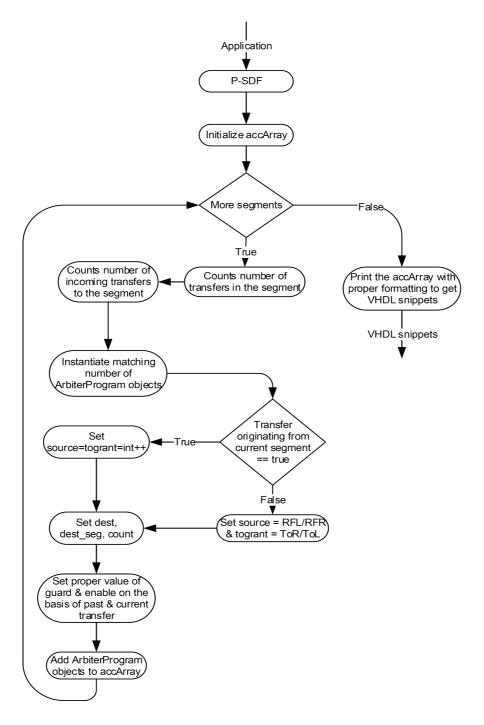

| 6.4  | Code extraction process for segments in the platform 93                                 |

| 6.5  | P-SDF model of an example application 95                                                |

| 7.1  | Block diagram of the Layer III simplified MP3 decoder [17] 99                           |

| 7.2  | P-SDF model of the MP3 decoder                                                          |

| 7.3  | The communication matrix of the partitioned-application 102                             |

| 7.4  | Example configuration of the <i>SegBus</i> platform with 3 segments and linear topology |

| 7.5  | Allocation of processes on different platform configuration 104                         |

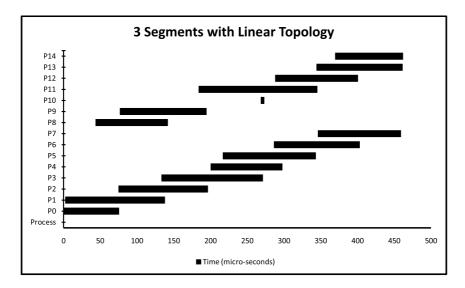

| 7.6  | Progress on time of each application process in 3 segment,                              |

|      | linear topology with package size of 36 data items configuration. 110                   |

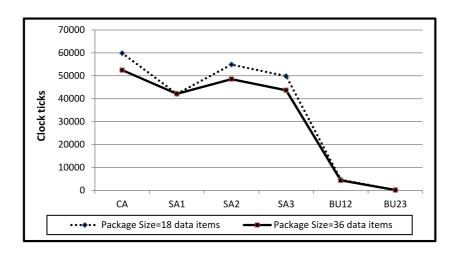

| 7.7  | Activity graph of different platform elements in 3 Segments                             |

|      | and linear topology configuration for 18 and 36 bit package                             |

|      | sizes                                                                                   |

|      |                                                                                         |

## List of Abbreviations

$\mu \mathbf{s}$  micro second

ACG Automatic Code Generation

**AM** Application Model

**API** Application Programming Interface

${f BU}$  Border Unit

CA Central Arbiter

CAD Computer-Aided Design

CIM Computation Independent Model

**CoD** Complexity of Design

**CoPE** Correctness of Platform Execution

**CPM** Complete Platform Model

**CWM** Common Warehouse Metamodel

**DE** Designer Expertise

**DocA** Distributed on-chip Architecture

**DSL** Domain Specific Language

**DSM** Domain Specific Modeling

**EDA** Electronic Design Automation

**FIFO** First In, First Out

FPGA Field-Programmable Gate Array

**FU** Functional Unit

GI Graphical Interface

**HDL** Hardware Description Language

**HLDE** High-Level Design Entry

IP Intellectual Property

M2M Model-to-Model transformation

M2T Model-to-Text transformation

MDA Model Driven Architecture

MDD Model Driven Development

MOF Meta-Object Facility

MP3 MPEG-1/MPEG-2 Audio Layer III Encoding Format

MPEG Moving Picture Expert Group

MPSoC Multiprocessor System-on-Chip

NoC Network-on-Chip

OCL Object Constraint Language

OOP Object-Oriented Programming

**OS** Operating System

**P-SDF** Package SDF

PAM Partitioned Application Model

PC Personal Computer

**PE** Platform Emulation

PIM Platform Independent Model

**PO** Performance Optimization

**PSM** Platform Specific Model

RTL Register Transfer Level

SA Segment Arbiter

**SAM** Segmented Application Model

**SDF** Synchronous Dataflow

SoC System-on-Chip

**SoPC** System-on-Programmable Chip

**SPM** Synthesizable Platform Model

Systems Modeling Language

TCT Total Clock Ticks

UML Unified Modeling Language

**UP** Useful Period

VHDL VHSIC HDL

VHSIC Very High Speed Integrated Circuit

**WP** Waiting Period

**XMI** XML Metadata Interchange

**XML** Extensible Markup Language

## Chapter 1

## Introduction

An *embedded system* is a special-purpose computer which is generally part of a larger physical system and provides a dedicated, and sometimes programmable, functionality to its ambient environment. Nowadays, such systems are widely used in airplanes, automobiles, industrial systems, cameras, medical equipment, house-hold appliances and inside so many other application areas.

In recent years, the complexity of the embedded systems has increased tremendously, along with the shrinking silicon features. The time-to-market is also shrinking, imposing challenges for the designers to adopt new design methods.

As an answer to the new capabilities and pressures, embedded computing systems have moved towards on-chip multiprocessing architectures. These include on-chip multiprocessing to utilize the tremendous advances of fabrication technology. The Distributed on-chip architectures (DocA) [20] or multiprocessor system-on-chip (MPSoC) [4] paradigm have gained increasing support from system designers. MPSoC is seen as one of the foremost means through which performance gains are still to be sustained even after Moore's law expected demise [27]. The most common DocA / MPSoC platforms are network-on-chip (NoC) [1], and segmented bus platforms [16][20].

As the complexity of the application is increasing with time, the designers are facing software and hardware challenges when designing applications targeting MPSoCs. However, it is also a challenge to take full benefits from all the distinguished features provided by the MPSoC platforms such as programability, enormous potential for performance gains, multiple clock domains, scalability, heterogeneity support, parallelism, etc. At the moment, there are a number of difficulties in MPSoC development and the prominent one is the lack of comprehensive design methodologies that can deal with almost every aspect of the design processes [27].

The platform-based design approach [3][33][34] provides the means to address these challenges. Few important features of this approach include: fast time-to-market, programability, short design cycle, design reusability (both hardware and software), design customization, huge potential for optimizations (performance, power consumption, etc.). The principle behind that approach is to separate the functionality of an application from the structural organization and communication architecture of a hardware platform at several levels of abstraction. This not only eases the design process but also delivers efficiency for concurrent engineering in specific aspects of the system by different members of the design team. The essential step in this approach is the mapping process where functions of the application to be implemented are assigned (mapped) to the components of the hardware platform spread within a single chip or on a number of chips. Targeting initially single chip designs, the approach gains even more importance in the context of DocA / MPSoC.

The existing design methodologies don't provide full automation in every level of the development process, and sometimes, the co-design of platform-based systems lead to sub-optimal systems. In order to offer an optimum match, platform specific characteristics must be taken into consideration for each application.

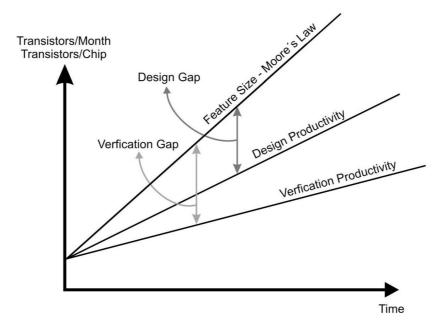

Figure 1.1: Comparison of gaps among other important trends of SoC design [18].

Moreover, the design productivity gap in MPSoC design remains one of a key challenge in the existing design methodologies. This challenge can be addressed by developing new computer-aided design (CAD) tools/frameworks based on modern design methods while improving the reusability of IP components. This not only enables the designers to take full advantages of MPSoC platforms, but further satisfies other important constraints e.g. time-to-market, quality of results, costs, etc. Figure 1.1 compares the design productivity gap with the advances in silicon technologies and with the growth trends in design verification [18]. Here, the gap between the chip complexity (Moore's law) and design productivity is increasing with the passage of time, which is important to realize now and must be addressed by the Electronic Design Automation (EDA) community.

Design decisions taken at higher abstraction levels are expected to have the highest impact on the quality of the system implementation. Given the complexity of modern on-chip multiprocessor solutions, this seems to gain even more in importance. On the other hand, optimality of design is strictly affected by platform parameters; hence, such platform-level aspects, if taken into account at high abstraction levels will lead to a solution that maximizes the benefits of the distinguished features offered by the MP-SoC platform. The specific platform considered in this study is the SegBus platform [20], which is an on-chip communication platform architected to provide communication infrastructure between the connected IP-cores in an MPSoC environment.

The three basic and most commonly used approaches of the design methodologies used for the embedded system design are: top-down;  $meet\text{-}in\text{-}the\text{-}middle}$  [2]; and bottom-up. The top-down methodology begins with a high-level system specification which specifies initially a system structure with required elements. Next, the specification is iteratively refined by decomposing system into sub-systems and components until enough details are gathered for each component. The design is then partitioned into hardware and software parts, and co-optimized. Hence, the approach is also well-known as hw/sw co-design. On the other hand, a bottom-up approach is an inverse approach where, firstly, individual components are built, and integrated afterward to eventually develop a target system.

In the meet-in-the-middle [2] approach, the application(s) and the platform are developed independently. The platform is developed by employing a bottom-up design flow where the low-level aspects of the platform are considered, whereas the application is developed by following a top-down flow starting from the high-level aspects of the application. When both specifications are complete, the application is then mapped on to the platform and this is the distinguished feature of the meet-in-the-middle approach. This approach is heavily dependent on a comprehensive library of software and hardware elements which reduces the design time and efforts and improves reusability. However, the establishment of such a library requires significant efforts beforehand.

In this thesis, the work is highly influenced by the meet-in-the-middle approach because of two important reasons. First, the thesis considers a particular platform (the SegBus platform), which is intended to be used as a communication platform. A number of applications from the same family can be mapped on that platform, and thus those applications can be executed in parallel. Second, the platform promotes the reuse of *intellectual property* (IP) components at different levels of abstraction which addresses other important complexity challenges e.g. design cost, time-to-market, etc.

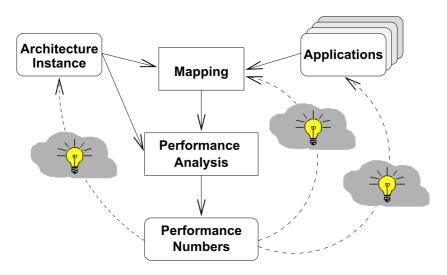

Figure 1.2: The Y-chart approach [30].

### 1.1 The Y-chart approach

The Y-chart [29][30] is a generic and iterative design space exploration methodology for platform-based designs. The methodology is based on the meet-in-the-middle approach where the application and platform are developed independently but the platform is fine-tuned *iteratively* to achieve the performance required by that application(s) at a certain level of abstraction.

In this methodology, an instance of the platform is known as a *configu*ration. In the mapping process, the mapping of the application onto a platform configuration is performed. The general overview of this approach is depicted in Figure 1.2. The artifacts (application(s), platform/architecture and mapping) are equally important to achieve an optimal configuration and thus, performance level. The performance aspects of the mapped application running on a platform configuration are examined in *Performance*  Analysis step and these performance numbers determine the efficiency of chosen configuration. If the configuration is not optimal, then the designer get another chance to further explore the design space to produce a new configuration and the process continues iteratively. This way, the author can truly exploit all the essential parameters of the employed platform in order to achieve the target performance goals.

### 1.2 The Model-Based Paradigm and UML

Software-based computing systems have been around for a few decades now. Their increasing complexity with time is a known challenge to all those associated with their design. At the beginning, it was relatively easy to design and implement such software systems with some low-level programming languages such as FLOW-MATIC, COBOL, Autocode, etc. But as the time went by, system specifications became more difficult for newer generation of software systems and designers realized that abstraction levels had to be raised. Consequently, high-level programming languages like C, FORTRAN and Pascal were developed and employed in the 1970s. At the time, these high-level programming languages were not competent enough to tackle increasingly complex specifications, and as a result, the objectoriented paradigm came into existence. The paradigm was based on a simple idea - Everything is an object. Later, the object-oriented paradigm gained popularity among designers and larger systems were developed by employing this paradigm [5]. However, the ever increasing complexity of such systems approached the limits of object-oriented paradigm and a new paradigm introduced: the model driven paradigm. The paradigm is based on a simple idea: Everything is a model. In fact, the idea is not so new because it has been used previously in database systems.

The software engineering community gradually adopted the model based paradigm, and as a result, the system specification moved from textual description (C, C++, Java, etc.) to visual/graphical modeling languages, which provide a higher-level of abstraction in modeling environments for system specification. The Unified Modeling Language (UML) [65] is one of them.

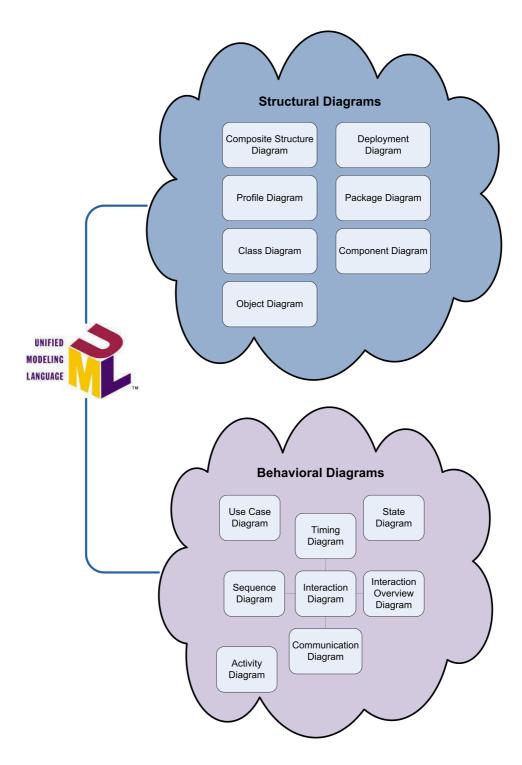

A notation is a graphical entity, and basically, forms the syntax of a modeling language. UML is a general-purpose modeling language which includes a set of graphical notations which are used in a particular diagram (e.g., class diagram, state diagram, etc.) for specifying various aspects of a software system in a generic manner. It can be applied to a variety of application domains, most importantly to object-oriented and component-based systems. Furthermore, the UML's extensibility mechanism (i.e., stereotypes, tagged values and constraints) enables the introduction of new building blocks from

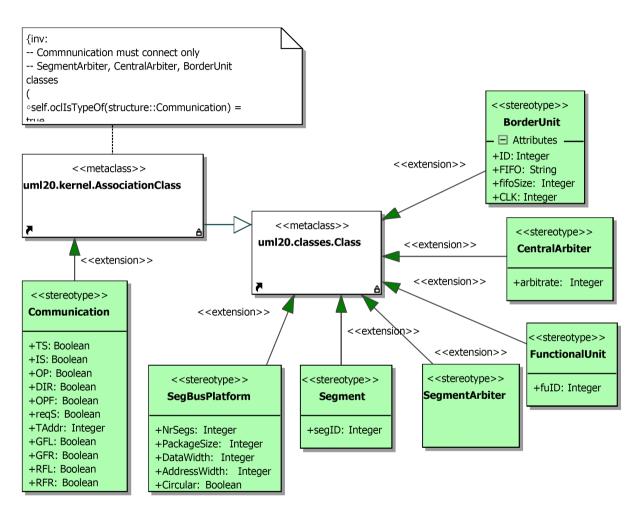

the existing ones. This capability opens the door to raising the abstraction level further - a modeling area, known as, domain specific modeling (DSM). For DSM, UML is extensively applied initially to build domain specific language (DSL) based on an associated UML profile targeted for a particular domain (discussed briefly in Chapter 4).

The paradigm shift from programming languages to modeling languages, as discussed earlier, for system specification has introduced a new methodology for software engineering known as the Model Driven Architecture (MDA) [61] promoted by the Object Management Group (OMG). The primary focus of MDA is on models, automation (by model transformations) and code generation which in turn, shifts the targeted system's design concerns from low-level implementation to high-level solution modeling. UML is the key enabling technology for MDA, and thus, it is the default modeling language for MDA. The model transformation is a key feature in the MDA approach. It enables the transformation of a model from one abstraction level to another, and hence, is the driving force which shifts models from higher to lower-levels of abstraction, and finally towards implementation. The important kinds of model transformation are: model-to-model (M2M), and model-to-text (M2T). The thesis employs the model-to-text (M2T) transformation in its intended approach, as it is briefly discussed in Chapter 5.

In a networking session [28] a few years ago, on-chip MPSoCs were identified as the preferred architecture for future complex embedded system design. Still, as discussed earlier, lack of right tools, design frameworks and methodologies didn't allow EDA vendors to support it as the mainstream architecture for embedded systems implementations. This thesis intends to take a small step further by making use of UML and MDA, towards developing a unitary framework for design and verification of applications targeting an MPSoC platform.

### 1.3 Design and Verification Challenges

A few of the challenges in designing applications targeting DocA (in general) and SegBus platform (in particular) addressed here in this thesis are as follows.

#### CoD - complexity of design

In the context of embedded system design, the term *complexity* refers to amount of uncertainty to move from one phase of design process to another. Embedded systems are inherently complex [52]. This is particularly true for modern embedded systems executing complex software applications and always demanding new features. The sys-

tem complexity further increases as the number of specific design constraints increase. Some of these design constraints includes:

- real-time constraints relating to particular functions of the system.

- crucial time-to-market constraints that become essential for the success or failure of system under development.

- power consumption constraints which are always important for battery-operated systems.

- low-cost constraints which decide the commercial viability of system.

- endless pressure for increasing functionality.

The above mentioned and many other design constraints play a key role in the immense growth of system complexity. One way of dealing with complexity is with the use of models and model-based development (MBD) (briefly elaborated in Chapter 3.2). Generally, the word 'model' refers to describe any given system aspect with simplicity. Here, simplicity refers to hiding details which are less important pertaining to a certain concern, but those details could be important ones in some other models when concern changes. The process of building models is called *modeling*. At the moment, modeling plays a significant role in systems engineering (especially core software systems). The modeling process is based on divide-and-conquer approach where the designer limits his/her focus only to certain aspects of the systemunder-development. Different members with specific expertise from the development team then concentrate on particular aspects of the system and provide solutions in a quick manner. This bring the thesis to its definition of the term 'model-based development' that the thesis follows, because there can be numerous interpretation of the generic term. Model-based development or MBD is a development approach with the use of models which are specified in a particular domain specific language, relating to a specific application domain. MBD has been used in different application domains [62][63] to minimize development effort and time.

#### PO - performance optimization

This is an important, and most of the times a primary challenge in embedded system design. In recent years, it has got foremost attention especially in digital signal processing (DSP) applications. Consequently, it plays a major role in the increased CoD. New multiprocessing architectures have been introduced to deal with CoD and PO. An intelligent *mapping* of application functions on the multiprocessing

architectures is key to exploit tremendous features (including performance) from such architectures. A bad mapping mostly makes the chosen architecture a sub-optimal and unnecessary cost(s).

The approach for PO, which is discussed in this thesis, various mappings and allocation scenarios will provide different performance results, given the inter task communication requirements both at application and at platform levels.

#### CoPE - correctness of platform execution

This deals with the proper ordering of application tasks after allocation, considering the support for parallelism.

#### DE - designer expertise

Following CoD, experienced developers may be required in the process, possessing detailed knowledge about platform characteristics and how issues may be solved at platform levels.

### 1.4 Thesis Approach and Contributions

This thesis presents an approach to addressing the previously mentioned challenges. The thesis presents a model-based development and verification framework for embedded systems in general, and MPSoC in particular. As mentioned earlier, the particular MPSoC platform that the thesis considers is the SegBus platform. From a high-level perspective, the key contributions of this thesis are structured around the following directions.

#### HLDE - high level design entry

The thesis uses the *Unified Modeling Language* (UML) for high-level design entry for both the platform (*SegBus*) and to support the allocation and mapping of application tasks on that platform. By providing the HLDE solution, the thesis addresses the CoD, CoPE and DE challenges, while also providing the necessary support for the solutions detailed below.

#### PE - platform emulation

Emulation is used here to provide estimative results prior to having an actual implementation of the application on the platform. This is an important step in observing at early design stages the quality and performance of design. Addresses PO, CoPE and DE.

#### ACG - automatic code generation

A general solution to address CoD and DE. In the present context, it also addresses CoPE.

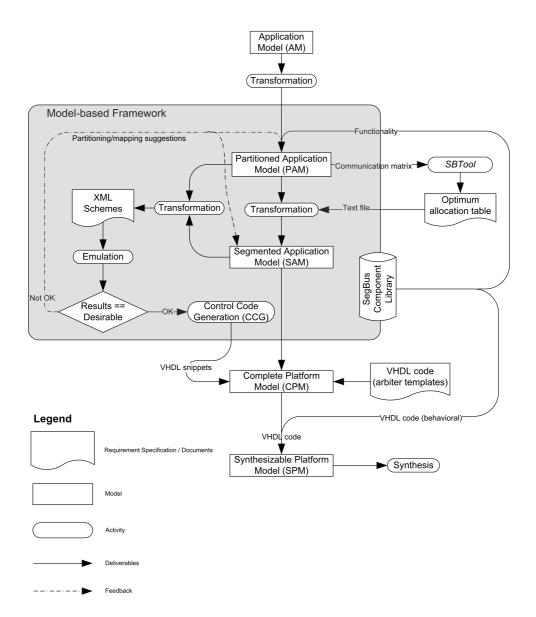

The *Unified Modeling Language* (UML) [65] has been utilized in novel design methods proposing a solution for the challenges in the design of complex electronic systems. Here, the purpose is to provide a unified environment for platform modeling, application mapping and system emulation, such that performance is estimated and adjusted to optimal levels in a correct and efficient manner. The key contributions of this thesis are briefly listed below.

1. The thesis introduces **model-based development** (MBD) support for *SegBus* design. The choice of MBD helps the designers to address CoD (by HLDE), CoPE (support for structured design, and correctness related aspects - customization classes, OCL constraints, etc., support for design reuse - library). It also addresses DE, as a hardware non-specialist (such as a software designer) may also develop applications without being fully aware of the specifics of the underlying hardware platform.

The thesis then presents a technique to create a **graphical interface** (GI) in the form of SegBus DSL within an existing modeling tool [60] to leverage modeling infrastructure for the analysis of various SegBus instances that may answer to specific application requirements. The customization of each platform element is defined in the form of user-defined rules. These customization rules set properties on each profile element about their relationships, ownerships (briefly discussed in Chapter 4.2). The customization rules impose restrictions on profile elements during application / platform modeling, in order to provide a structurally correct version of the platform instance.

The GI answers especially the CoD and CoPE challenges, providing the HLDE solution. By including model validation features, the GI also serves the DE challenge.

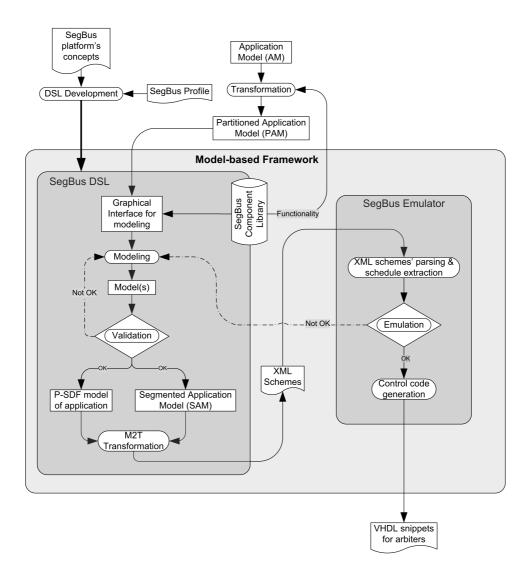

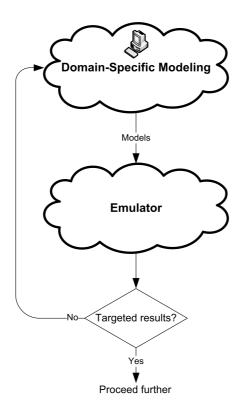

2. The thesis develops an emulator program targeting the SegBus platform as part of the framework to perform emulation on the modeled configuration in DSL. A code generation engine transforms the platform-independent and platform-dependent models of application, as modeled in DSL, into XML schemes. The generated XML schemes are then employed by the emulator program to estimate the utilization of platform elements with respect to data transfers and total application's execution time. After the analysis of the emulation results, the designer is able to take decisions on whether the emulated configuration is the best/optimal or not for the target application, and can fine-tune platform configuration before moving towards lower levels of the design process.

Hence, the realization of the emulator addresses, via PE the PO, CoPE and DE challenges.

3. The thesis presents methods to generate the application's execution schedule from system models which are used later to implement the communication platform's arbiters. Such capability is developed within the emulator program. If designer finds the performance aspects from the emulated system at an optimum/best level, the designer can generate the "application dependent" arbiter-level control code based on VHDL [41], in an automated manner.

Hence, with this technique, the thesis addresses the CoPE and DE challenges via GI, PE and ACG.

#### 1.5 Related Work

As it has been discussed in section 1, the design methodologies and frameworks being used today for embedded systems development lack automation in many stages of their design process. While building the proposed framework, several research studies have been studied where the authors present concepts in particular areas of embedded system design. For instance, few studies, which have come across, deal with high-level modeling of the embedded systems while others express ideas specifically for system emulation. Following are listed few studies which are similar to the proposed framework up to some extent.

The UML Profile for MARTE [69] has been standardized by OMG a few years ago. As the name suggests, MARTE is intended for the modeling and analysis of real-time and embedded systems in a generic way. The profile consists of various packages and notations, which help to specify and validate target systems at a number of abstraction levels. However, MARTE does not provide a methodology for designing any particular systems (realtime and embedded) [48]. A lack of a proper methodology, for mapping applications on a particular platform (SegBus platform in the context of this thesis), gets prime focus when considering prospective improvements in the designer productivity. Gamatié et al. [22] introduced Gaspard framework for designing massively parallel embedded systems. The framework is based on MARTE profile where system is defined initially, and refined in a stepby-step manner for final implementation. Since their framework does not target to any specific implementation platform (unlike this thesis's approach which targets the SeqBus communication platform), therefore it provides them opportunities to explore a comparatively wider design space. The refinements in their framework are based on model-driven principles, which are similar to the work presented in this thesis in many aspects.

Moreover, Architecture Analysis & Design Language (AADL), standardized by SAE International [70], is a modeling language for software-intensive system, which has gained popularity especially in safety-critical systems in recent years. However, the issues highlighted in [23] makes it less attractive for use in the proposed framework.

Kangas et al. [21] introduced a UML-based framework named as Koski for MPSoC design and implementation. Koski provides tools ranging from application modeling to architecture implementation. The framework is based on a custom UML profile (the TUT profile) similar to this research. The framework also supports synthesis and automated design space exploration for identifying the right architecture for the target application. At the same time, their approach does not consider a definite architecture/platform for application implementation, unlike this work which focused on the Seg-Bus platform. Another difference compared to this approach is that they do not employ MDA and package-based communication in their approach as this research do since the communication is a primary design concern for modern MPSoC systems. Despite that their design flow seems to be inspired by the MDA principles.

R. Thomson et al. [49] developed and implemented a H.264 decoder unit in an UML environment, exposing models for both hardware and software components. The *FalconML* tool is used to model different aspects of the applications via various UML diagrams, and the flow eventually produces RTL code (VHDL) which can be used to synthesize the design. The difference to the approach of this thesis is that this research work considers a target platform for implementation whereas their approach generates a customized solution.

Many DSLs have been proposed targeting a variety of application domains and this research considers the SegBus platform as the backbone of the embedded MPSoC system. Consel et al. [32] introduced the Spidle - DSL for specifying streaming applications and a compiler for generating source code for the intended software. The approach was validated experimentally by comparing the source code generated by Spidle compiler with an equivalent C source code. A number of optimizations in the Spidle compiler are missing, such as, temporal and spatial locality in data and instruction caches, the performance impact of input streams buffering, etc. Similarly, Arora et al. [31] presented a DSL for introducing an application-level Checkpointing and Restart (CaR) mechanism in heterogeneous and distributed environments such as computational grid. The idea is to make sequential and parallel system fault-tolerant by introducing code for the CaR mechanism in high-level specifications.

Riccobene et al. [53] presented a UML profile for SystemC and defined a language to specify, analyze, design, and visualize different artifacts of the SystemC language in a SoC design flow. These SystemC artifacts includes,

for example, SystemC primitive channels (signal, mutex, semaphore, etc.), SystemC core language artifacts (modules, ports, processes, etc.), SystemC data types (bits, bit vectors, 4-valued logic type, etc.). The profile provides a modeling framework for systems in which high-level models can be refined down to an implementation language. However, the work concluded that there is still a need to develop appropriate mechanisms and tools to fully utilize UML-based profiles system development with automation support. Unlike their work, this research proposes a comprehensive UML-based profile for the SegBus platform embedding structural semantics in a graphical form while imposing restrictions among graphical elements at the same time.

Seceleanu et al. [19] introduced SBTool - a tool for handling optimum device allocation on the SegBus platform based on the criteria to minimize and balance traffic loads between devices across the platform. This work takes advantage of the SBTool in the design methodology to get estimates of the optimal placement of different devices over specified number of bus segments.

Truscan et al. [50] introduced a model-based design methodology for implementing applications on the SegBus platform. Their methodology allows both application and platform to be modeled independently in earlier phases, and after refinements in both models (application and platform), the application can be mapped onto the platform in a stepwise manner. The proposed methodology has been inspired by their methodology in many aspects and the proposed methodology has been further evolved and customized for the objectives of this thesis.

The primary objective in designing system emulator is to obtain as much as possible accuracy in estimating the execution characteristics that can be expected from a real platform. Several research studies have been presented in recent years where the target was to develop emulators for different hardware platforms, specially for the Network-on-Chip (NoC) platform [1], but there exists a number of emulation tools for other areas as well.

Jaber et al. [7] presented early architecture exploration methodology based on DIPLODOCUS framework [46][47] to examine the effects of shared resources (CPU, bus, memory, etc.) on a system's performance metrics such as throughput, latency and resource utilization at high levels of abstraction. Their methodology also facilitates the modeling of interactions of the system with its environment. Their architecture modeling approach divides the architecture into 3 classes of nodes: computations nodes (CPUs, DSPs, hardware accelerators, etc.); communication nodes (buses, routers, switches, etc.); and storage nodes (shared memories). They employed a library of pre-defined abstract models of different nodes (limited only to architecture) which is similar to this thesis's approach of employing a library of reusable IP components. On the contrary, the proposed framework's library can also store the application-related functional components which is dissimi-

lar to their library approach. Further, they introduced a SystemC-based simulation environment for monitoring and analyzing the modeled system. This is comparatively similar to the proposed emulator in this thesis which is also used for monitoring and analyzing the utilization of platform elements with respect to data transfers and execution time. In addition, their study is focused only to architectural exploration and analysis of simulation results, and the comparisons with actual execution results over real architecture setup are missing, unlike to this thesis's approach which compares the emulated execution results with the real ones for the sake of predicting emulator's accuracy.

Schelle et al. [54] introduced an emulation tool - NoCem, for NoC exploration. The tool provides the capability to emulate memory architectures, asymmetric processor configuration, special purpose offload engines, etc. The tool calculates path latencies in clock cycles, used for any particular transfer between processor cores and provides a detailed view of the communication bottlenecks within the NoC platform. This is fairly similar to the platform emulator developed in this framework, which is used to emulate a particular configuration of SegBus platform. Performance bottlenecks can be discovered and then can be adjusted.

Liu et al. [39] presented NoCOP - an emulation and verification framework for exploring on-chip interconnection architectures. An instruction-set simulator (ISS) and universal serial bus (USB) communicator (the terms mentioned in their paper) have also been introduced. The ISS and USB communicator execute on a host computer and are used to set the parameters of the emulation environment. Through the experimental results using both software and hardware, the authors proved that the proposed emulation/verification framework can speed up the simulation of the network-onchip (NoC) architecture, and decrease resource usage when targeting Field Programmable Gate Array (FPGA) silicon. The design under emulation needs to be programmed onto a FPGA device. A separate host computer is responsible for initializing and managing emulation of the programmed design in the FPGA. This makes it less flexible compared to the proposed approach which is more flexible and does not require any FPGA device and consideration about deeper levels of abstraction in the early stages of the design process.

Genko et al. [24] presented a NoC emulation platform implemented on FPGA. The NoC hardware platform has been implemented on a Virtex-II Pro FPGA, which consists of network injection, reception and controller components. The integrated PowerPC processor core functions as a controller. Instead of merely being the platform where the circuit is prototyped, the method can speed up functional validation and add flexibility to the NoC configuration exploration. The major drawback in their approach is the use of FPGA device as a prototyping platform with the purpose of predicting

performance scores, unlike the proposed approach in this thesis, which does not require any prototyping platform for performance estimation.

MDA has been utilized in different design areas to provide automation in design activities up to some extent [IV]. MDA provides a set of guidelines which designers use to specify the system requirements in a structured manner. The resulting system specifications are expressed as models. With the refinement techniques, the designer can ultimately converge the system models toward a complete system with the help of the transformation techniques (Model-to-Model, Model-to-Text, etc.) applied to different models. Below, a few studies are listed where the authors employ MDA in embedded system development at different abstraction levels.

Vidmantas et al. [26] introduced MDA methods where the designer can create "Platform Independent Model" (PIM) of an application using UML together with SysML plug-in. They introduced techniques to transform PIM into a PSM model, which is later transformed into textual source code specifically for one operating system (OS). The authors have considered more than one OS where the modeled application can be run, unlike the proposed approach where there is no consideration of OS is required. Further, this thesis discusses PIM (known as P-SDF in this thesis) and PSM models of any target application similar to their approach, but this thesis does not generate source code of actual application's functionality which is dissimilar to their approach. Instead the thesis generates the control code for different arbiters of the SegBus communication platform, which supports application execution on the platform and eliminates the need of an OS.

Koudri et al. [35] presented a design flow for System-on-Chip/System-on-Programmable Chip design based on the use of UML and dedicated profiles. They supported the use of the Model-Driven Development (MDD) for hardware-software co-design with an example of *Cognitive Radio Application*, implemented on FPGA. The modeling tool they used generates thousands of lines of code for the modeled example application but further improvements need to be done.

M. Thompson et al. proposed a highly automated framework titled as *Daedalus* for system-level architectural exploration, system-level synthesis, programming and prototyping of heterogeneous MPSoC platforms [44][45]. Their framework allows to construct customizable MPSoC platforms from a library of pre-defined and pre-verified IP components, similar to the proposed approach of having a library of pre-built functional components. At the same time, their approach is dissimilar as this research is closely linked to a communication platform - the *SegBus* platform.

#### 1.6 Research Publications

During the course of conducting this research, the following articles have been published in journal and international conference proceedings. Hence, the thesis is fully or partially based on each of them.

- I. Moazzam Fareed Niazi, Khalid Latif, Tiberiu Seceleanu, Hannu Tenhunen. "A DSL for the SegBus Platform", in Proceedings of the 22<sup>nd</sup> IEEE International System-on-Chip Conference (SOCC), pp. 393-398, 2009, Belfast, United Kingdom.<sup>1</sup>.

- II. Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "An Emulation Solution for the SegBus Platform", in Proceedings of the 17<sup>th</sup> IEEE International Conference and Workshops on Engineering of Computer-Based Systems (ECBS), pp. 268-275, 2010, Oxford, United Kingdom.

- III. Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "A Performance Estimation Technique for the SegBus Distributed Architecture", in Proceedings of the 39<sup>th</sup> International Conference on Parallel Processing Workshops (ICPPW), pp. 89-98, 2010, San Diego, USA.

- IV. Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "An Automated Control Code Generation Approach for the SegBus Platform", in Proceedings of the 23<sup>rd</sup> IEEE International System-on-Chip Conference (SOCC), pp. 199-204, 2010, Las Vegas, USA.

- V. Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "Towards Reuse-based Development for the On-Chip Distributed SoC Architecture", in Proceedings of the 36<sup>th</sup> Annual IEEE Computer Software and Applications Conference Workshops (COMPSACW), pp. 278-283, 2012, Izmir, Turkey.

- VI. Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "A Development and Verification Framework for the SegBus Platform", Journal of Systems Architecture, vol. 59, nr. 10, part C, pp. 1015-1031, 2013. http://dx.doi.org/10.1016/j.sysarc.2013.07.005

## 1.7 Summary of the Research Publications

Paper I - Moazzam Fareed Niazi, Khalid Latif, Tiberiu Seceleanu, Hannu Tenhunen. "A DSL for the SegBus Platform", in Proceedings of

<sup>&</sup>lt;sup>1</sup>The above papers have been referred in this thesis many times with a usual citation referring style e.g., [I], [II], [IV], etc.

the  $22^{nd}$  IEEE International System-on-Chip Conference (SOCC), pp. 393-398, 2009, Belfast, United Kingdom.

High-level design entry is essential for the designing and verification of systems at higher levels of abstraction. In this paper, a *Domain Specific Language* (DSL) for a multi-core segmented bus platform - *SegBus*, is presented. The DSL, based on a UML profile, consists of graphical platform elements in the form of stereotypes with the necessary tagged values depicting platform aspects at high levels of abstraction. Customizations are applied to each stereotyped element in the form of user-defined rules to restrict relationship between platform elements. The *Object Constraint Language* (OCL) is employed to introduce structural constraints, in order to impose structural requirements between platform elements and mechanisms were introduced to validate them during system-level modeling. The paper presents a simplified example of a H.264 video encoder application where the DSL is used to specify and validate the application and platform models in a step-by-step unified way.

The author's contribution: The author has been responsible for all related work in this publication including profile development, customization of platform's elements inside the modeling tool, specification of the structural constraints, DSL viability in the problem domain, and writing the manuscript.

Paper II - Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen.

"An Emulation Solution for the SegBus Platform", in Proceedings of the 17<sup>th</sup> IEEE International Conference and Workshops on Engineering of Computer-Based Systems (ECBS), pp. 268-275, 2010, Oxford, United Kingdom.

This paper presents an emulation solution for a multi-core segmented bus platform, SegBus, to assess the performance of any specific application on a particular platform configuration, modeled in UML. The paper presents method to transform a Platform Specific Model (PSM) of the application into Java source code using a modeling tool and the generated code is utilized by the emulator program to get the execution results. The solution enables the estimation of the performance on different platform configurations at early stages of the design process.

The author's contribution: The author has been responsible for all related work in this publication including writing Java source code for each of the platform elements, emulator development, performance estimation and analysis, and writing the manuscript.

Paper III - Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen.

"A Performance Estimation Technique for the SegBus Distributed Architecture", in Proceedings of the 39<sup>th</sup> International Conference on Parallel Processing Workshops (ICPPW), pp. 89-98, 2010, San Diego, USA.

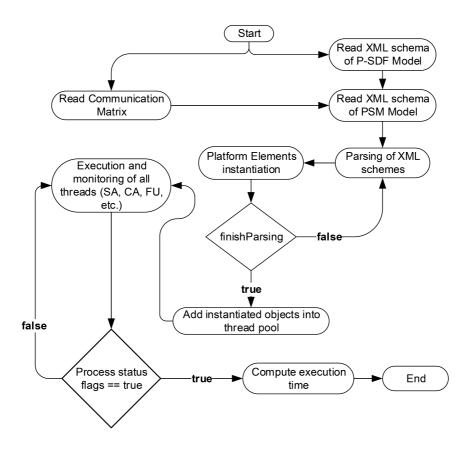

The approach presented in this paper is a modified and enhanced approach of performance estimation to that discussed in paper II. Here, the paper proposes a performance estimation technique for a multi-core segmented bus platform, SegBus. The technique enables the assessment of the performance of any specific application on a particular platform configuration, modeled in Unified Modeling Language (UML). The paper presents methods to transform Package Synchronous Data Flow (P-SDF) and Platform Specific Model (PSM) models of the application into Extensible Markup Language (XML) schemes using a modeling tool. The generated XML schemes are utilized by the emulator program to get the execution results. The technique facilitates the performance estimation of the application mapped on a number of different platform configurations during the early stages of the design process.

The author's contribution: The author has been responsible for all related work in this publication including enhancing DSL to model P-SDF models, emulator development, development of XML parser inside the emulator, performance estimation and analysis, and writing the manuscript.

**Paper IV** - Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "An Automated Control Code Generation Approach for the SegBus Platform", in Proceedings of the  $23^{rd}$  IEEE International System-on-Chip Conference (SOCC), pp. 199-204, 2010, Las Vegas, USA.

The transition from higher abstraction levels towards an implementation in an automatic manner is very important when addressing the embedded system design productivity challenge. This paper presents a model-based approach for the generation of low-level control code for the (segment- and central-level) arbiters of the SegBus communication platform in order to support application implementation and scheduled execution. The approach considers Model-Based Development (MBD) as a key to modeling the application at two different abstraction levels, namely as Package-Synchronous Dataflow and Platform Specific Model, using the SegBus platform's DSL. Both models are transformed into XML schemes and then utilized by an emulator to generate the "application-dependent" VHDL code, the so-called "snippets". The obtained code is inserted in a specific section of the platform arbiters.

The paper presents an example of a simplified MP3 stereo audio decoder where the methodology is employed to generate the control code of the arbiters.

The author's contribution: The author has been responsible for all related work in this publication including writing the engine for generating the control code from the P-SDF model, embedding the developed engine in the emulator, code generation and analysis of its accuracy, and writing the manuscript.

Paper V - Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "Towards Reuse-based Development for the On-Chip Distributed SoC Architecture", in Proceedings of the 36<sup>th</sup> Annual IEEE Computer Software and Applications Conference Workshops (COMPSACW), pp. 278-283, 2012, Izmir, Turkey.

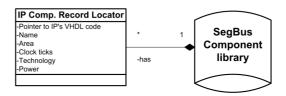

Reusability in the platform-based design approach is key to dealing with increasing embedded systems design complexity. In this paper, the development of a library of reusable components for a multi-core segmented bus platform, the SegBus, is presented. The library is based on a plug-in that was developed and deployed within a modeling tool and used by the SegBus DSL for developing applications targeting the SegBus platform. The steps required in building the library and embedding it into a plug-in are discussed together with its use in the proposed design methodology.

The author's contribution: The author has been responsible for all related work in this publication including plug-in development, plug-in integration with the SegBus DSL in the modeling tool, establishing components list in the library, and writing the manuscript.

Paper VI - Moazzam Fareed Niazi, Tiberiu Seceleanu, Hannu Tenhunen. "A Development and Verification Framework for the SegBus Platform", Journal of Systems Architecture, vol. 59, nr. 10, part C, pp. 1015-1031, 2013. http://dx.doi.org/10.1016/j.sysarc.2013.07.005

This paper integrates all the ideas been presented in previous papers to form a distinct framework for modeling and verification. Here, the paper describes the creation of a development framework for a platform-based design approach, in the context of the distributed architecture of the SegBus platform. The work aims to provide automated procedures for platform build-up and application mapping. Structural verification support is also featured. The solution is based on a model-based process. Both the platform and the application are modeled using the Unified Modeling Language (UML). A Domain Specific Language (DSL) is developed to support the platform modeling,

based on a corresponding UML profile. Object Constraint Language (OCL) constraints, in the form of a validation suite, are employed to support a structurally-correct platform construction. The DSL helps designers to correctly model application and platform in a fast manner and further helps in model transformation at later stages of development process. The validation suite embedded in the DSL helps the designer to rectify the structural problems in models and correct them with necessary measures. An emulator is consequently introduced to allow an as much as possible accurate performance estimation of the solution, at high levels of abstraction. VHDL code is automatically generated, in the form of "snippets" to be employed in the arbiter modules of the platform, as pertaining to the application specification. The resulting framework is applied to building actual design solutions for a MP3 audio decoder application. The emulation-based solution enables analyzing any platform configuration with respect to performance figures. Based on emulation results, it's the job of the designer to decide which configuration will be best suited for the final implementation. Such decisions made in the early stages of design process improve the quality of eventual system in terms of performance.

The author's contribution: The author has been responsible for all related work in this publication including DSL analysis and development in the modeling tool, construction of validation suite, emulator development, design and development of the control code generator in the emulator, verification of the presented methods on an actual example application, and writing the manuscript.

#### 1.8 Thesis Organization

The remainder of this thesis is organized as follows. In Chapter 2, the thesis provides a short description of the SegBus platform with its structural characteristics. Next, in Chapter 3, the thesis discusses the proposed design methodology that employs the proposed model-based framework while designing applications targeting the SegBus platform. The development of the SegBus DSL and the associated library of reusable components are described in Chapter 4. The approach of emulating and estimating the modeled system is presented in Chapter 5, while the method of execution schedule generation from the modeled system is briefly discussed in Chapter 6. Furthermore, in Chapter 7, the thesis formally employs and validates the proposed framework on a real application as an example, followed by a discussion of the proposed framework. Finally, the thesis concludes in Chapter 8.

# 1.9 Thesis Navigation

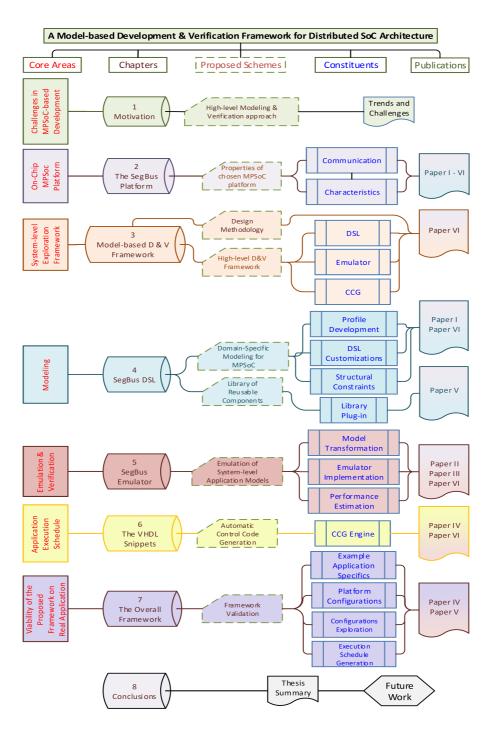

Figure 1.3: Navigation of the thesis.

# Chapter 2

# The SegBus Platform

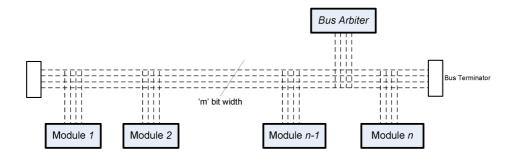

A bus-based computing system comprises of a variety of modules, each with particular functionality. Each module communicates with other modules through a shared bus which connects with every module. A data exchange between these modules is termed a bus transaction which is administered by a set of specific rules known as transaction protocol. The modules are generally classified as: masters, slaves and arbiters.

Master refers to a module which initiates a transaction on the bus and remains active for the duration of transaction. In contrast, slave refers to a passive module which is basically the "target" of a particular bus transaction and in return, it delivers a service to requesting master. In principle, one master and possibly many slaves can be involved in a bus transaction. As the bus is a shared communication link, only one master can be allowed to own the bus at any time, that is, transfer data to or from the slave module. Hence, an arbiter does *arbitration* based on a specific priority scheme between masters on the bus. Figure 2.1 represents high-level view of a traditional bus-based computing system.

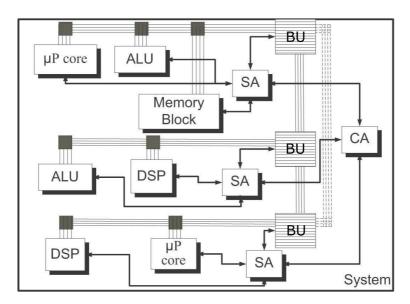

Figure 2.1: Traditional bus-based system.

The maximum bus speed is largely limited by the physical length of the bus and the number of modules connected on the bus. A lengthy bus introduce transmission delays in bus lines or wires due to physical effects. The major physical effects on the bus wires includes: capacitance, resistance and impedance, which put a restriction on the maximum bus frequency. Additionally, the number of modules connected on the bus should be within the maximum limit as defined by the bus to operate properly. Failure to consider these two important concerns result in performance degradation, increased power consumption, etc.

The bus arbiter follows a certain priority scheme for granting the bus among different masters. The priority scheme can be either *fixed priority* or rotating priority (also known as round-robin scheme). In the fixed priority scheme, the priority of each module remains the same all the time irrespective of how many times a master has been granted the bus; while in rotating priority scheme, the priority of each module changes based on the usage history. Both priority schemes have certain advantages and disadvantages and their selection is purely based on their suitability for the target system.

Figure 2.2: Segmented bus structure [20][50].

A segmented bus is a "collection" of individual buses (segments), interconnected with the use of FIFO structures. Each segment acts as a normal bus between modules that are connected to it and operates in parallel with other segments. Due to segmentation, each segment executes at a certain clock frequency independent from the clock rate of the neighboring segments. Therefore, the platform can be seen as a set of buses operating in parallel with different clock frequencies. Neighboring segments can be dynamically

connected to each other to establish a connection between modules located on different segments. In this case, all dynamically connected segments act as a single bus during the duration of transaction. Due to the segmentation of the bus lines, and their relative isolation, parallel transactions can take place, thus increasing the performance. The *passive* segments, which are not involved in transactions, are isolated from the rest of the bus. Hence, the *active* segments, the ones that currently transfer data, offer faster operation along with lesser energy consumption per transferred bit. A high level block diagram of the segmented bus system is illustrated in Figure 2.2.

The SegBus communication platform [20] is built of components that provide the necessary separation of segments -  $Border\ units\ (\textbf{\textit{BU}})$ , arbitration units - the  $Central\ Arbiter\ (\textbf{\textit{CA}})$  and local,  $Segment\ Arbiters\ (\textbf{\textit{SA}})$ . The application then is realized with the support of (library available)  $Functional\ Units\ (\textbf{\textit{FU}})$ .

The SegBus platform has a single CA unit and several SAs, one for each segment. In addition, each segment is composed of a group of masters, a group of slaves and physical wires for data, address and control signals of the bus. A BU connects two neighboring segments. A particular segment with its connected units (masters, slaves, SA) acts as standalone bus operating in parallel with other segments, where masters primarily requesting services from slaves within the same segment. The SA of each bus segment decides which device (FU), within the segment, will get access to the bus in the following burst transfer. At times, a master may ask for services from a slaved resident in a remote bus segment. In this case, the local SA forwards the request to CA in order to perform inter-segment communication.

The  ${\it CA}$  stores information about the current status of each segment. This includes which segments are currently involved in an inter-segment communication and which new inter-segment communication requests are still pending. In every polling cycle, the  ${\it CA}$  decides, based on this information, which pending request will be qualified to grant ownership for inter-segment communication, and eventually, the  ${\it CA}$  activates certain control signals in the relevant segments. This way, the  ${\it SegBus}$  platform can be seen as a  ${\it centralized}$ , two-level arbitration platform. At the first-level, local arbitration is used inside each segment, while at the second-level, central arbitration is employed to handle inter-segment communication requests from different  ${\it SA}$ s. In this case, the  ${\it CA}$  treats individual  ${\it SA}$ s as  ${\it virtual}$  masters requesting services from other segments.

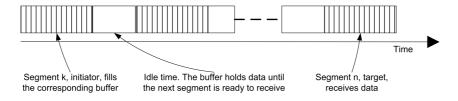

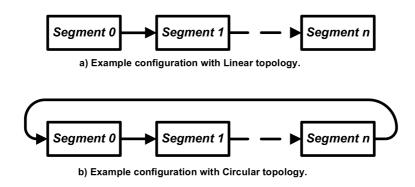

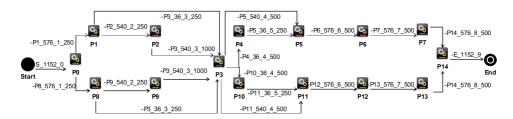

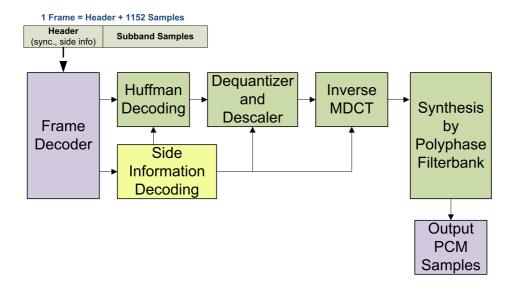

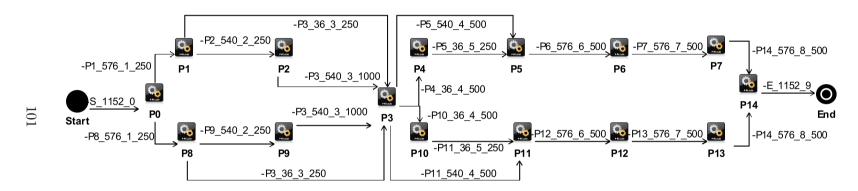

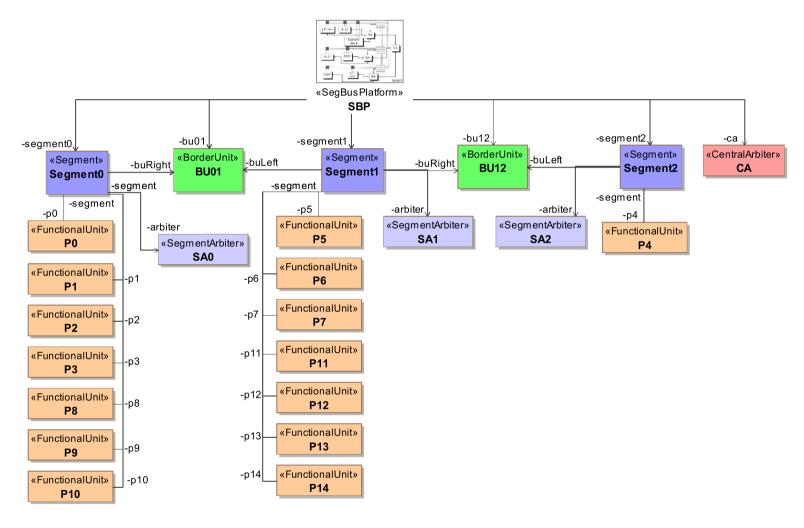

#### 2.1 Platform Communication