# Alexander Wei Yin

# On Energy Efficient Computing Platforms

TURKU CENTRE for COMPUTER SCIENCE

TUCS Dissertations No 160, August 2013

# On Energy Efficient Computing Platforms

## Alexander Wei Yin

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Lambda on August 28, 2013, at 12 noon.

University of Turku Department of Information Technology 20014 Turku, Finland

2013

## **Supervisors**

Professor Hannu Tenhunen Department of Information Technology University of Turku 20014 Turku, Finland

Associate Professor Pasi Liljeberg Department of Information Technology University of Turku 20014 Turku, Finland

Professor Jouni Isoaho Department of Information Technology University of Turku 20014 Turku, Finland

## Reviewers

Professor Maurizio Palesi Kore University 94100 Cittadella Universitaria Enna, Italy

Professor Shashi Kumar Department of Electronics and Computer Engineering Jönköping University SE-551 11 Jönköping, Sweden

## Opponent

Professor Zheng Yan Docent, School of Electrical Engineering Aalto University, Espoo, Finland Professor, School of Telecommunications Engineering Xidian University, Xi'an, China

ISBN 978-952-12-2918-3 ISSN 1239-1883

# Abstract

In accordance with the Moore's law, the increasing number of on-chip integrated transistors has enabled modern computing platforms with not only higher processing power but also more affordable prices. As a result, these platforms, including portable devices, work stations and data centres, are becoming an inevitable part of the human society. However, with the demand for portability and raising cost of power, energy efficiency has emerged to be a major concern for modern computing platforms.

As the complexity of on-chip systems increases, Network-on-Chip (NoC) has been proved as an efficient communication architecture which can further improve system performances and scalability while reducing the design cost. Therefore, in this thesis, we study and propose energy optimization approaches based on NoC architecture, with special focuses on the following aspects.

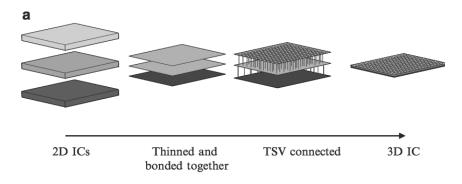

As the architectural trend of future computing platforms, 3D systems have many benefits including higher integration density, smaller footprint, heterogeneous integration, etc. Moreover, 3D technology can significantly improve the network communication and effectively avoid long wirings, and therefore, provide higher system performance and energy efficiency.

With the dynamic nature of on-chip communication in large scale NoC based systems, run-time system optimization is of crucial importance in order to achieve higher system reliability and essentially energy efficiency. In this thesis, we propose an agent based system design approach where agents are on-chip components which monitor and control system parameters such as supply voltage, operating frequency, etc. With this approach, we have analysed the implementation alternatives for dynamic voltage and frequency scaling and power gating techniques at different granularity, which reduce both dynamic and leakage energy consumption.

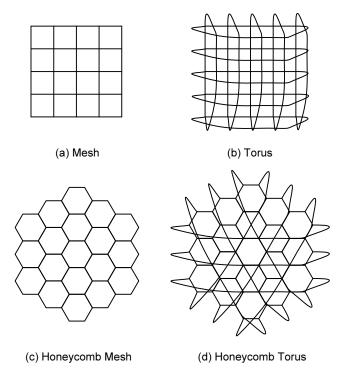

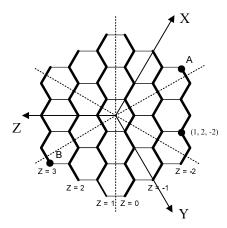

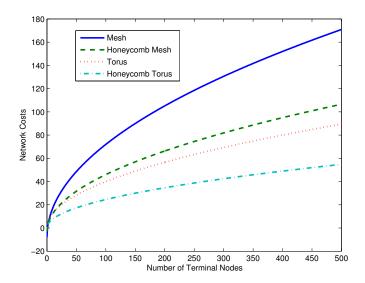

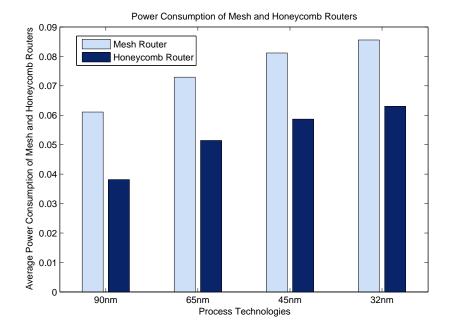

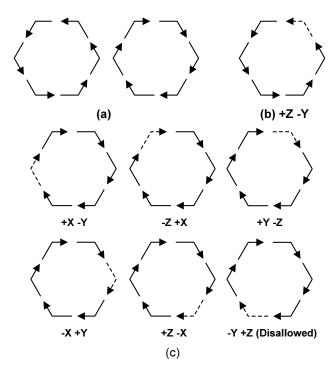

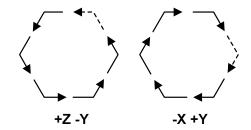

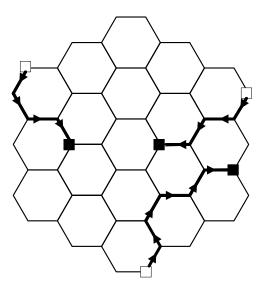

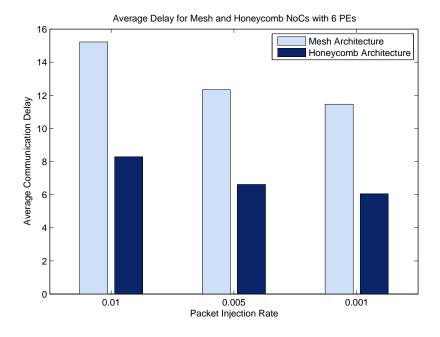

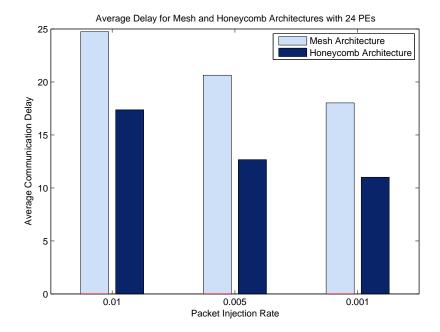

Topologies, being one of the key factors for NoCs, are also explored for energy saving purpose. A Honeycomb NoC architecture is proposed in this thesis with turn-model based deadlock-free routing algorithms. Our analysis and simulation based evaluation show that Honeycomb NoCs outperform their Mesh based counterparts in terms of network cost, system performance as well as energy efficiency.

# Acknowledgements

The completion of this doctoral dissertation is an exciting moment in my life. During the past years, I have received enormous support from several people and organizations, to whom I would like to express my sincere gratitude.

First of all, I am extremely grateful to my supervisors Prof. Hannu Tenhunen, Prof. Pasi Liljeberg and Prof. Jouni Isoaho from the University of Turku. From their innovativeness, diligence and professionalism, I have learned not only how to conduct research, but also how to conquer challenges.

I would like to express my appreciation to Prof. Axel Jantsch and Prof. Zhonghai Lu from the Royal Institute of Technology (KTH), Sweden where I was introduced to the Network-on-Chip technology which is one of the corner stones of this doctoral dissertation.

In addition to my supervisors, I would sincerely thank my fellow colleagues at University of Turku, Turku Centre for Computer Science, Turku School of Economics, as well as Eficode Ov.

I would also like to thank Prof. Maurizio Palesi from Kore University, Italy and Prof. Shashi Kumar from Jönköping University, Sweden for the detailed reviews and constructive comments on this dissertation.

Last but definitely not least, my most gratitude goes to my family. Being ICT professionals themselves, my parents have been always supporting and understanding my career and life choices. I would give my most special appreciation and love to my dear wife Wenjing and son Jeremy for all their love, understanding and support.

# Contents

| 1 | Intr | roduction                                                | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Energy Efficient Computing Platform                      | 1  |

|   |      | 1.1.1 Portable Devices                                   | 1  |

|   |      | 1.1.2 Servers and Data Centres                           | 2  |

|   | 1.2  | System-on-Chip Development and Challenges                | 3  |

|   |      | 1.2.1 Development Progress of Embedded Systems and Elec- |    |

|   |      | tronic Devices                                           | 3  |

|   |      | 1.2.2 SoC Overview                                       | 4  |

|   |      | 1.2.3 Challenges for SoCs                                | 6  |

|   | 1.3  | Thesis Contribution                                      | 7  |

|   | 1.4  | Thesis Organization                                      | 8  |

|   | 1.5  | Research Publications                                    | 9  |

| 2 | Net  | work-on-Chip 1                                           | .1 |

|   | 2.1  | <u>•</u>                                                 | 11 |

|   | 2.2  |                                                          | 12 |

|   | 2.3  |                                                          | 14 |

|   | 2.4  | Routing                                                  | 15 |

|   | 2.5  | _                                                        | 16 |

|   | 2.6  | •                                                        | ۱7 |

|   |      |                                                          | ۱7 |

|   |      | _                                                        | 18 |

|   |      | 2.6.3 Mesh                                               | 18 |

|   |      |                                                          | 19 |

|   |      | 2.6.5 Fat-tree                                           | 20 |

|   | 2.7  |                                                          | 20 |

| 3 | Ene  | ergy Efficiency in NoCs 2                                | 23 |

|   | 3.1  | •                                                        | 23 |

|   |      | 55 1                                                     | 24 |

|   |      |                                                          | 24 |

|   |      | •                                                        | 25 |

|   |     | 3.1.4  | · ·                                          |

|---|-----|--------|----------------------------------------------|

|   |     | 3.1.5  | Glitch Power Consumption                     |

|   | 3.2 | Power  | vs. Energy                                   |

|   |     | 3.2.1  | Low Power Systems                            |

|   |     | 3.2.2  | Energy Efficiency                            |

|   | 3.3 | Power  | Challenges of NoC based Systems              |

|   |     | 3.3.1  | Processing Element                           |

|   |     | 3.3.2  | Communication                                |

|   |     | 3.3.3  | Leakage Power Consumption                    |

|   | 3.4 | Power  | Models                                       |

|   |     | 3.4.1  | OSI 7-Layer Model                            |

|   |     | 3.4.2  | Abstraction Layers in NoC Communication 34   |

|   | 3.5 | Chapt  | er Summary                                   |

| 4 | 3D  | _      | uting Platform 39                            |

|   | 4.1 | Develo | opment of Three Dimensional Circuits         |

|   |     | 4.1.1  | Stacking Approaches                          |

|   | 4.2 | Survey | y of 3D Architectures                        |

|   |     | 4.2.1  | Single Layer Circuit                         |

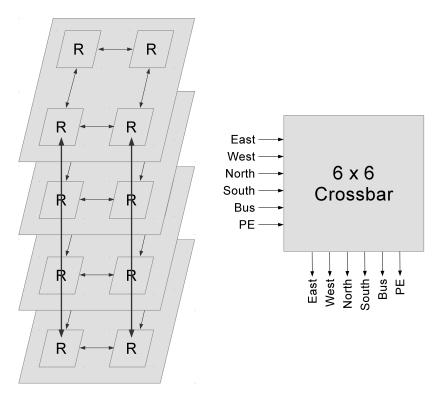

|   |     | 4.2.2  | 3D NoC-Bus Hybrid Architecture               |

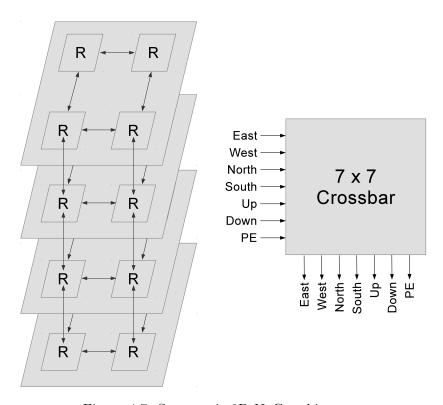

|   |     | 4.2.3  | Symmetric 3D NoC Architecture 43             |

|   | 4.3 | Chang  | ge Function of 2D and 3D NoCs                |

|   |     | 4.3.1  | Overview                                     |

|   |     | 4.3.2  | System Performance                           |

|   |     | 4.3.3  | Power Consumption and Thermal Concerns 49    |

|   |     | 4.3.4  | TSV Analysis                                 |

|   |     | 4.3.5  | Circuit-level Analysis                       |

|   |     | 4.3.6  | Yield Analysis                               |

|   |     | 4.3.7  | Testing Costs                                |

|   |     | 4.3.8  | Functional Integration                       |

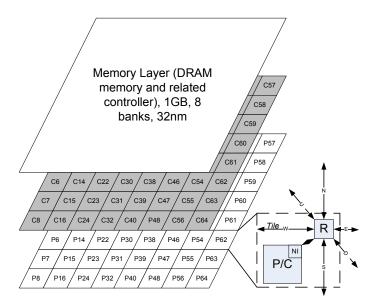

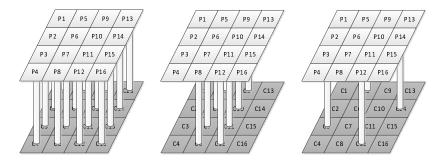

|   | 4.4 |        | Study: 3D Integration with On-Chip           |

|   |     | DRAN   | M Memory                                     |

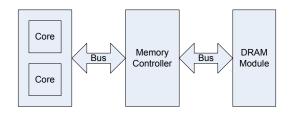

|   |     | 4.4.1  | Introduction of 3D NoC with DRAM 59          |

|   |     | 4.4.2  | Modelling of 3D NoC with DRAM Integration 61 |

|   |     | 4.4.3  | Experimental Setup                           |

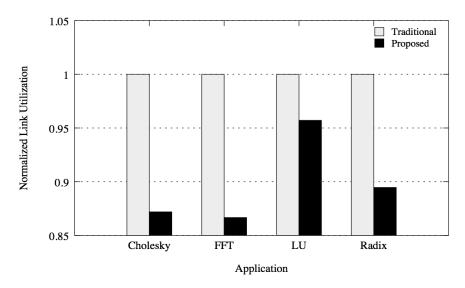

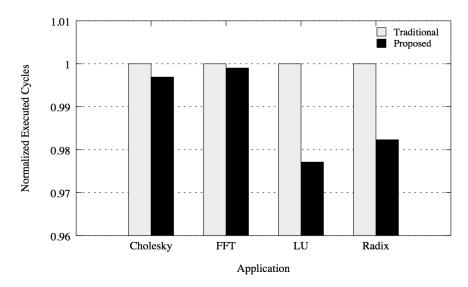

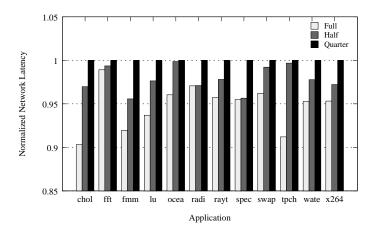

|   |     | 4.4.4  | Performance Evaluation                       |

|   |     | 4.4.5  | TSV Evaluation                               |

|   | 4.5 | Chapt  | er Summary                                   |

| 5 | _   |        | sed System Design 69                         |

|   | 5.1 |        | round of Agent based System 69               |

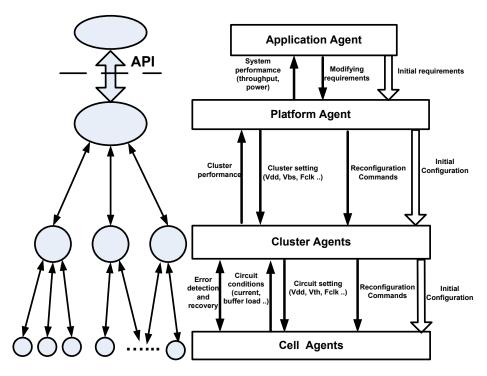

|   | 5.2 |        | chical Monitoring Agents                     |

|   |     | 5.2.1  | Agent Hierarchy                              |

|   |     | 5.2.2 Hierarchical Monitoring Approach                                                  |

|---|-----|-----------------------------------------------------------------------------------------|

|   |     | 5.2.3 Implementation of Agents                                                          |

|   | 5.3 | Communication Scheme                                                                    |

|   |     | 5.3.1 Monitoring Communication Interconnect Alternatives 74                             |

|   |     | 5.3.2 Performance Analysis                                                              |

|   |     | 5.3.3 Design Trade-offs                                                                 |

|   | 5.4 | Fault and Variation Tolerance                                                           |

|   |     | 5.4.1 Overview                                                                          |

|   |     | 5.4.2 Case Study: 64-point FFT/IFFT 83                                                  |

|   | 5.5 | Chapter Summary                                                                         |

| 6 | Dvv | namic Voltage and Frequency Scaling 87                                                  |

| U | 6.1 | Run-time Power Optimization                                                             |

|   | 6.2 | Island based DVFS                                                                       |

|   | 0.2 |                                                                                         |

|   |     | V                                                                                       |

|   | 6.2 | O                                                                                       |

|   | 6.3 | Per-core based DVFS                                                                     |

|   |     | 0 0 0                                                                                   |

|   |     | 0 1 0 11 0                                                                              |

|   |     | 6.3.3 System Architecture of Per-Core DVFS 95<br>6.3.4 Per-core level DVFS Algorithm 95 |

|   | 6.4 | <del>-</del>                                                                            |

|   | 0.4 |                                                                                         |

|   |     | 6.4.1 Experiment Setup                                                                  |

|   |     |                                                                                         |

|   | 6.5 | 6.4.3 Experiment Analysis                                                               |

|   | 0.5 | 6.5.1 Q-Learning based Routing Algorithm                                                |

|   |     | 6.5.2 Deadlock Handling Mechanism                                                       |

|   |     |                                                                                         |

|   | 6.6 |                                                                                         |

|   | 0.0 | Chapter Summary                                                                         |

| 7 | Hor | neycomb NoC 111                                                                         |

|   | 7.1 | J 1 00                                                                                  |

|   | 7.2 |                                                                                         |

|   | 7.3 | Implementation Feasibility                                                              |

|   | 7.4 | Router Designs                                                                          |

|   | 7.5 | Routing Algorithms                                                                      |

|   | 7.6 | Simulation Results                                                                      |

|   | 7.7 | Chapter Summary                                                                         |

| 8 | Con | nclusion 127                                                                            |

|   | 8.1 | Summary of Contributions                                                                |

|   | 8.2 | Future Direction                                                                        |

# Chapter 1

# Introduction

Gone are the days when Integrated Circuit (IC) designers focused solely on the creation of faster chips or more powerful processors. With the development of computer technologies and network infrastructure, a large variety of computing platforms are becoming unprecedentedly important in many aspects of the human society. At the same time, energy efficiency has been recognized as the most critical challenge and has drawn significant attention from both industry and academia. In this chapter, we will firstly explain the energy challenges for different types of computing platforms.

## 1.1 Energy Efficient Computing Platform

A computing platform includes a hardware architecture and a software framework where the combinational efforts allow application software to be run. With the current technologies, all computing platforms are powered by either AC power or batteries. In this section, we introduce the energy concerns for portable devices which are powered by batteries as well as servers and data centres using AC power.

#### 1.1.1 Portable Devices

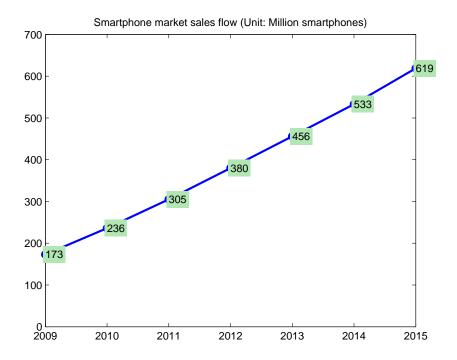

During the past decades, the demand and popularity of portable devices has been growing tremendously, such as laptops, smart phones, mobile Internet devices, pocket video recorders, digital single-lens reflex cameras and hand-held game consoles. These devices conveniently provide many services including communication, computation, entertainment, information management and Internet access [66]. Smart phones, for example, have gained extreme popularity thanks to the increasing processing capability, powerful functionalities and applications, as well as easy access to Internet via 2G, 3G, Blue-tooth and Wi-Fi networks. Figure 1.1 illustrates the market growth during the previous years and forecast until the year 2015.

Figure 1.1: Market and Sales Growth of Smart phones

Portable devices commonly run on rechargeable batteries to support user mobility. The requirements for small size and light weight imply that its battery be proportionately small in volume [73]. According to Moore's Law, the number of on-chip integrated transistors has doubled approximately every 18 months and thus power consumption of processors has increased significantly. Over the last 30 years, the power consumption of microprocessors has gone up from under 1 Watt [90] to over 130 Watts (e.g., Intel i7 9-Series). However, the development of battery technology has not kept pace. Since 1990s, battery energy density has only tripled [13].

Therefore, energy efficiency is of obvious importance for portable devices since people like neither replacing or re-charging their batteries frequently, nor carrying heavy batteries with their sleek gadgets.

#### 1.1.2 Servers and Data Centres

Unlike battery operated portable devices, workstations, servers and data centres are usually operated by AC power and are not restricted by battery capacity. However, there are at least two important energy related aspects that make energy efficiency a crucial concern.

Environmental Cost - According to the U.S. Environmental Protec-

tion Agency's Report to Congress on Server and Data Center Energy Efficiency made in the year 2007 [3], the aggregate electricity use associated with U.S. servers and data centres is expected to rise from 61.4 billion kWh in 2006 to 124.5 billion kWh in 2011, representing about 2.5 percent of total projected nationwide electricity use. Many organizations have expressed severe concerns over the rising electricity consumption attributed to the Internet and to commercial desktop computation including workstations and servers. This is because of not only the rising financial cost, but also the process of electricity generation which is a major source of pollution. Therefore, inefficient energy usage in computing equipment will exacerbate the currently challenging enough environmental problems.

Reliability and Heat Concerns - In addition to environmental cost, there are concerns of reliability and heat dissipation. Computer platforms with high energy consumption tend to increase the silicon temperature, and high temperature will exacerbate various failure mechanisms. According to [34], every 10°C increase in operating temperature roughly doubles an electrical component's failure rate. For modern computing platforms, the die surface temperatures are already over 100°C and thus sophisticated packaging and cooling mechanisms are required. This fact has increased system cost substantially. As presented in [90], a processor with less than 1 W power consumption requires a plastic package costing about 1 cent per pin, while if the power consumption is over 2 W, ceramic packages costing about 5 cents per pin would be required. For data centres, high energy consumption also leads to the usage of large scale and expensive liquid and air cooling solutions [78].

## 1.2 System-on-Chip Development and Challenges

With the digitalization of modern society, embedded systems have spanned all aspects and play increasingly important roles in people's everyday lives. An embedded system is a computing platform designed for a specific function, often within a larger system such as a personal computer (PC). It is embedded as a part of a complete device which often includes both hardware and software systems.

# 1.2.1 Development Progress of Embedded Systems and Electronic Devices

The Apollo Guidance Computer (AGC) is usually recognized as one of the first modern embedded systems. It was designed at the MIT Instrumentation Laboratory in early 1960s. Serving as a digital computer produced for the Apollo program, it was installed on-board each Apollo Command

Module and Lunar Module. The AGC provided computation and electronic interfaces for guidance, navigation, and control of the spacecraft.

At its early stages, embedded systems were used intensively for military purposes. Autonetics D-17, an early mass produced embedded system, was the guidance computer for the Minuteman missile, released in 1961. It was built from transistor logic and had a hard disk for main memory. The main reason for the lack of commercial applications was the price for quad nand gate ICs which was as high as 1000 USD per piece.

Another milestone of electronic systems is the invention of Dynamic Random-Access Memory (DRAM) by IBM in late 1960s. It stored each bit of data in a separate capacitor within an integrated circuit. The capacitor can be either charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1.

In 1971, Intel launched the first microprocessor known as Intel 4004 which cost 60 USD each. This 4-bit processor was also the first complete Central Processing Unit (CPU) on one chip.

Over the next several years, Intel 8008 and other more capable microprocessors became available in the IC industry. However, processors still required external chips to implement a working systems, which hindered their commercial usages due to high cost. To solve this problem, Texas Instrument released the first micro-controller known as TMS 1000 in 1974, which integrated processor, memory and clock on one chip.

In 1980s, the introductions of Application-Specific Integrated Circuit (ASIC) and Field-Programmable Gate Array (FPGA) brought revolutionary changes to the IC industry. The initial ASICs used gate array technology known as uncommitted logic array which was invented by Ferranti. This technology was successfully commercialized via 8-bit ZX81 and ZX Spectrum low-end personal computers in early 1980s. Later in 1985, the co-founders of Xilinx invented the first commercially viable field programmable gate array the XC2064 which had programmable gates as well as programmable interconnects between gates.

In 1990s, the introduction of intellectual property (IP) blocks and virtual components brought in a new implementation format called System-on-Chip (SoC) where a single chip contained mostly reusable IP based logic blocks. Comparing with the aforementioned systems, SoC is a completely integrated on-chip system and has much powerful processing capabilities.

#### 1.2.2 SoC Overview

SoC is a chip which holds all the necessary hardware and electronic circuitry for a complete system. It normally contains a large number of components integrated on a single substrate, such as microprocessor, micro-controller, memory blocks (ROM, RAM or flash), I/O logic control, data converters,

etc. Peripherals such as USB interface and communication modules including radio frequency module and Ethernet components are also commonly used in SoCs.

With the increasing number of integrated components, on-chip communication is undoubtedly one of the most critical issues and can easily become a performance bottleneck. In current SoC based systems, the most commonly used communication medium among different components is based on the on-chip bus architecture.

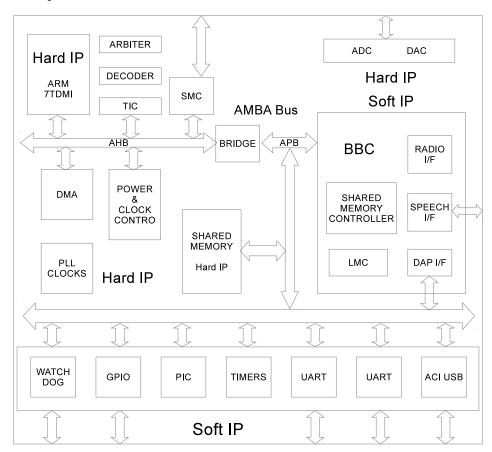

Figure 1.2: An Example of SoC [86]

As an example of SoC implementation, Figure 1.2 shows the block diagram of a mix-signal SoC developed at the University of British Columbia [86]. This SoC is a Bluetooth device for low-power wireless personal area networks (WPANs) and its overall architecture consists of a RF front-end, a baseband controller, and software to implement the Bluetooth protocol stack.

As shown in Figure 1.2, one major advantage of SoCs is the usage of IP cores, which greatly shortens the production lead time. An IP core is usually

a hardware circuit design that is lent, sold, or licensed from one designing or engineering company to another. There are two main categories of IP cores, namely, hard IP cores and software IP cores.

Hard cores refer to the IP circuits that are delivered to the customer in the form of a final silicon layout. It is worthwhile to notice that hard cores do not mean the physical chips of silicon, but all the necessary information to manufacture such a chip. This is the most restrictive form for delivery, but also provides the highest reliability. Delivering a hard core leaves little room for the recipient of the IP to make any manufacturing mistakes. Hard cores are usually delivered in the form of a GDS-II database.

Soft cores, also known as synthesizable cores, do not have to be manually ported to specific manufacturing process. Thus, soft cores avoid the problems with process porting that hard cores have. Soft cores can be synthesized for different types of silicon processes, and the conversion is now automated hence becomes the responsibility of the synthesis tools, rather than the IP supplier or customer. Soft cores delivery makes IP cores more universal and less specific to individual customers or their silicon manufacturing processes. However, comparing with hard cores, software cores usually cost more silicon area, manufacturing cost and power consumption since they are not explicitly optimized for a specific technology process.

## 1.2.3 Challenges for SoCs

During the past years, the transistor counts on a single chip have entered the billion era for both microprocessors and graphical processing units. As a result, the number of IP blocks integrated on chip has been increasing dramatically which leads to an exponential rise in the complexity of their interaction. With this technology trend, it is predictable that the traditional digital system design methods, especially bus based SoC designs, will soon face the following performance bottleneck and design challenges [44] [63].

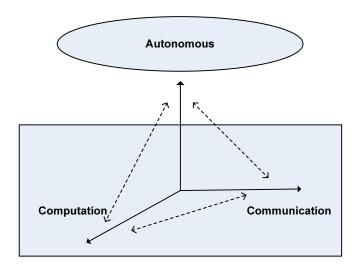

Communication verses Computation - As the technology develops, the scale of on-chip systems grows exponentially. With the use of reusable IP blocks, the design of computing component and circuit is no longer the most critical challenge in system design since the reusable IP blocks can provide satisfying circuit features and performances. Researches have unveiled that the data transmission and communication have profound effects on system performance and communication often becomes the bottleneck in large scale systems.

**Deep Submicron Effects** - Signal integrity effects such as interconnect delay, crosstalk, substrate coupling, transmission line effects, etc. did not draw significant attention in the early era of IC design with relatively slow clock speed and low integration density. However, as the transistor density increases, wires are getting neither fast nor reliable [37]. Meanwhile, more

noise sources due to inductive fringing, crosstalk and transmission line effect are coupled to other circuit nodes via substrate, common ground and electromagnetic interference [63]. Consequently, signal integrity analysis has become as important as timing, area and power analysis in modern chip designs.

Global Synchronization - IC designs have been following a globally synchronous design style where a global clock tree is distributed throughout the chip, driving logic blocks to function synchronously. However, this style is unlikely to hold for future wire interconnect. With the technology scaling, gate delay has been reduced more significantly than wire delay. Therefore, in large scale SoCs with small feature size, it usually takes several clock cycles for the clock signal to transfer from one component to another. It is predicted in [44] that large chips will no longer be synchronous designs with only one clock domain.

Design and Productivity Gap - The design and productivity gap is the gap between what we are capable of building and what we are capable of designing [63]. According to [9], the development of compiling and synthesizing tools does not keep pace with the IC manufacturing technology. This problem has been alleviated thanks to the reusable IP blocks which can largely reduce the design time of computing components in systems. Therefore, It is naturally expected that the on-chip communication architecture is also reusable in different systems.

In order to solve these challenges, the Network-on-Chip (NoC) architecture was introduced at the beginning of 21st century based on the existing computer network principles. By adopting this architecture, the performance of inter-component intra-chip communications can be largely improved. Since there is no arbitration requirement in a network, more transaction can occur simultaneously and thus let a resource (usually an IP block as a component in the network) transmit a message whenever it is ready, which can decreases the response time (delay) of messages and enhance the usage as well as the throughput of a system. Moreover, as each link in a NoC system is based on point-to-point (P2P) mechanism, the network wires and consequently the communications among resources can be pipelined. In terms of scalability, network architectures can be increased by inserting repeaters without severe performance degradation. The details of NoC architecture will be introduced in the next chapter.

## 1.3 Thesis Contribution

The main contributions of this thesis are:

1. To achieve higher energy efficiency, different Three Dimensional (3D) NoC implementations are studied with the analysis on benefits and

limitations. We have presented a 3D on-chip DRAM architecture which alleviates the thermal challenges. A quarter connection TSV placement architecture is proposed to reduce the total TSV cost with little performance cost.

- 2. A 2D/3D change function is presented in this thesis, which quantifies the pros and cons of each architecture. The principle of this function is based on the analysis of perceived crises using 2D NoC architectures and pains of 3D NoC adoption. While illustrating the change function, we have compared 2D and 3D NoCs in terms of benefits, including communication delay, power consumption, area consumption, reduction in the number of metal layers, as well as costs including cooling, TSV manufacturing, yield and testing.

- 3. A hierarchical monitoring agent based design approach is proposed in this thesis where agents are either software or hardware components monitoring and configuring the operations on a NoC based system. By the joint efforts of all agents at different hierarchical levels, the system is able to perform autonomous optimizations during run-time and thus achieve higher system robustness and energy efficiency. Low power techniques including DVFS and power gating are studied using the proposed agent based architecture. Together with a reinforcement learning adaptive routing algorithm, this approach effectively improves the energy efficiency for complex NoC based systems.

- 4. Different 2D network topologies have also been explored for lower energy consumption. In this thesis, we propose a Honeycomb NoC architecture together with the deadlock free routing algorithms. Comparing with Mesh based NoCs, the Honeycomb topology provide lower implementation cost, shorter communication delay as well as higher energy efficiency.

## 1.4 Thesis Organization

The rest of the thesis is organized as follows. The concept and architecture of NoC are illustrated in Chapter 2. Chapter 3 starts with the introduction of energy efficiency for NoC based systems and then explains the power challenges as well as the abstraction layer model for communication on NoCs. In Chapter 4, we study the 3D NoC architecture which provides benefits in terms of both system performance and power efficiency. However, these benefits do not come for free. Thus we propose a change function method which can quantify the pros and cons. A hierarchical monitoring agent based design approach is introduced in Chapter 5. By using this approach, a NoC based system can autonomously adjust the operations to achieve higher

robustness and energy performance. DVFS and power gating techniques are then studied in Chapter 6 with their implementation alternatives on agent based NoCs. A reinforcement learning adaptive routing algorithm is also presented with different case studies. In Chapter 7, we propose a Honeycomb NoC architecture and prove that it outperforms the Mesh based architecture in terms of system performance as well as energy efficiency. Chapter 8 concludes the thesis.

#### 1.5 Research Publications

During the course of conducting research presented in this thesis, the following papers have been published in international journals and proceedings of conferences.

- Alexander Wei Yin, Liang Guang, Pasi Liljeberg, Pekka Rantala, Jouni Isoaho, Hannu Tenhunen. Hierarchical Agent Based NoC with DVFS Techniques. International Journal of Design, Analysis and Tools for Integrated Circuits and Systems (IJDATICS) 1(1), pages 32 - 40, 2011.

- 2. Thomas Canhao Xu, Alexander Wei Yin, Pasi Liljeberg, Hannu Tenhunen. A Study of 3D Network-on-Chip Design for Data Parallel H.264 Coding. *Microprocessors and Microsystems* 35(7), pages 603 612, 2011.

- 3. Alexander Yin, Nan Chen, Pasi Liljeberg, Hannu Tenhunen. Comparison of Mesh and Honeycomb Network-On-Chip Architectures. In *Proceedings of the 7th IEEE Conference on Industrial Electronics and Applications*, pages 1713 1717, Singapore, July 2012.

- 4. Alexander Wei Yin, Thomas Canhao Xu, Bo Yang, Pasi Liljeberg, Hannu Tenhunen. Change Function of 2D/3D Network-on-Chip. In Proceedings of the 11th IEEE International Conference on Computer and Information Technology, pages 181 188, Pafos, Cyprus, August 2011.

- Thomas Canhao Xu, Liang Guang, Alexander Wei Yin, Bo Yang, Pasi Liljeberg, Hannu Tenhunen. An Analysis of Designing 2D/3D Chip Multiprocessor with Different Cache Architecture. In *Proceedings of the 28th IEEE Norchip Conference*, pages 1 - 6, Tampere, Finland, November 2010.

- 6. Thomas Canhao Xu, Bo Yang, Alexander Wei Yin, Pasi Liljeberg, Hannu Tenhunen. 3D Network-on-Chip with on-chip DRAM: an empirical analysis for future Chip Multiprocessor. In *Proceedings of the*

- 2010 International Conference on Computer, Electrical, and Systems Science, and Engineering, pages 18 24, Kyoto, Japan, October 2010.

- 7. Alexander Wei Yin, Gangming Lv, Cheng Tao, Pasi Liljeberg, Hannu Tenhunen. RF NoC: A New Paradigm for Very Large Scale Three Dimensional On-Chip Interconnect Networks. In *Proceedings of the 3D Integration Workshop in Design Automation and Test Europe Conference (DATE 2010)*, Dresden, Germany, March 2010.

- 8. Thomas Canhao Xu, Alexander Wei Yin, Pasi Liljeberg, Hannu Tenhunen. A Study in 3D Network-on-Chip Design for Data Parallel H.264 Coding. In *Proceedings of the 27th IEEE Norchip Conference*, pages 1 6, Trondheim, Norway, November 2009.

- 9. Alexander Wei Yin, Liang Guang, Pasi Liljeberg, Pekka Rantala, Ethiopia Nigussie, Jouni Isoaho, Hannu Tenhunen. Hierarchical Agent Based NoC with Dynamic Online Services. In *Proceedings of the 4th IEEE Conference on Industrial Electronics and Applications (ICIEA 2009)*, pages 434 439, Xi'an, China, May 2009.

- 10. Alexander Wei Yin, Liang Guang, Ethiopia Nigussie, Pasi Liljeberg, Jouni Isoaho, Hannu Tenhunen. Architecture Exploration of Per-Core DVFS for Energy-Constrained On-Chip Networks. In *Proceedings of the 12th Euromicro Conference on Digital System Design (DSD 2009)*, pages 141 146, Patras, Greece, August 2009.

- 11. Alexander Wei Yin, Thomas Canhao Xu, Pasi Liljeberg, Hannu Tenhunen. Explorations of Honeycomb Topologies for Network-on-Chip. In *Proceedings of the 6th IFIP International Conference on Network and Parallel Computing (NPC 2009)*, pages 73 79, Gold Coast, Australia, October 2009.

- 12. Alexander Wei Yin, Liang Guang, Pekka Rantala, Pasi Liljeberg, Jouni Isoaho, Hannu Tenhunen. Hierarchical Agent Monitoring NoCs: A Design Methodology with Scalability and Variability. In *Proceedings* of the 26th NorChip Conference, pages 202 207, Tallinn, Estonia, November 2008.

# Chapter 2

# Network-on-Chip

As the predominating on-chip communication architecture, buses can efficiently connect 3-10 communication partners but do not scale to higher numbers [44]. Even worse, for each connected component, the performance of the bus is unpredictable due to the fact that there are many other components waiting for the bus access. In large scale on-chip systems, it has been proved that designing and verifying the inter-task communication are more challenging than achieving higher performances for computation resources. Moreover, each system has its own communication structure, making reuse difficult.

As the consequence, from year 1999, researchers have started investigating a systematic approach to separate the design of communication infrastructure from that of computation resources such as processors and memory banks. The first scientific article with the term Network-on-Chip (NoC) was then published in November, 2000 [36].

#### 2.1 NoC Overview

Like many other computer networks, NoCs are defined based on key system characteristics including topology, flow control, switching mechanism, routing, etc.

Topology of a network means the connection pattern of communication resources including links, routers, interfaces, etc. Different topologies have different characters and thus will result in different system performances. The most commonly used NoC topology is Two-Dimensional (2D) Mesh network. In depth discussion on NoC topologies and their impacts on system performances will be presented later in Section 2.6.

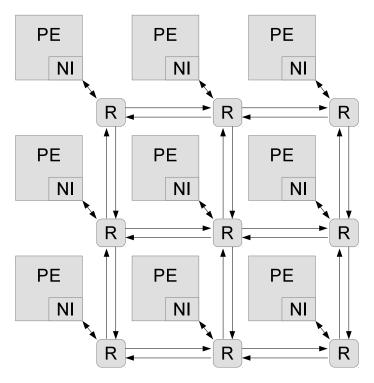

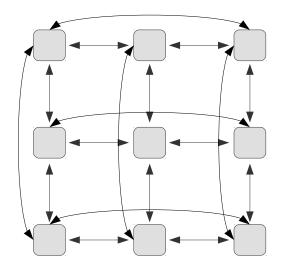

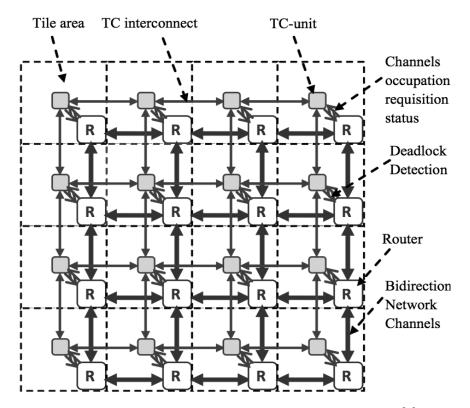

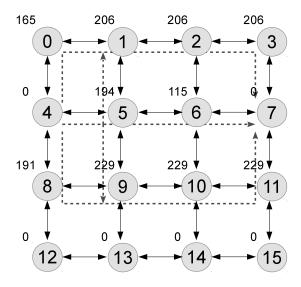

Figure 2.1 shows an example of NoC with 2D Mesh topology. In this  $3\times3$  NoC based system, the core of the communication infrastructure is the Mesh network consisting of 9 routers. Routers are connected to each other

via bi-directional links. Attached to each router is one or several Processing Elements (PEs). The functionalities of PEs can be heterogeneous, such as processor cores, DSP cores, memory banks, specialized I/O blocks including Ethernet or Bluetooth protocol stack implementations, graphics processors, FPGA blocks and even bus based subsystems. Routers and PEs are connected by Network Interfaces (NIs) which provide communication capability between the two parties, based on the chosen communication protocol such as AMBA AXI or OCP.

Figure 2.1: An example of NoC with 2D Mesh topology

#### 2.2 Flow Control

Flow control determines the allocation of network resources such as link bandwidth and buffer capacity for data traversing the network. A good flow control method allocates the resources in an efficient way so that the network achieves higher real bandwidth and delivers data with low and predictable latency.

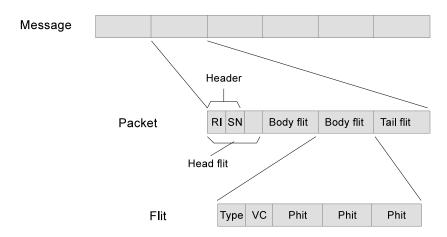

Figure 2.2 shows the units in which flow control is conducted. At the top level is the message, which is a logically continuous group of bits containing the information sent from source node to the destination. However, messages

are usually too long to be allocated to network resources. Therefore, in practice, they are divided into one or more packets that have a pre-defined maximum length.

As the basic unit for routing and sequencing, a packet consists of a segment of message to which a packet header is prepended. The packet header includes routing information (RI) and, if needed, a sequence number (SN). A packet can be further divided into flits which are the basic units of bandwidth and storage allocation. Thus, a packet consists of a head flit which allocates link state, one or more body flits which carry the real information, and a tail flit which deallocates the network resources.

Furthermore, a flit can be divided into one or more phits which are the unit of information that is transferred across a link in a single clock cycle. Phits are usually between 1 bit and 64 bits in size, with 8 bits being typical [24].

Figure 2.2: Units of resource allocation

In general, there are two categories of flow control mechanisms, namely, bufferless flow control and buffered flow control.

Bufferless flow control is the simplest form of flow control which uses no buffering and simply act to allocate link state and bandwidth to packets. As a result, when there are more than one packets requesting for the same link, the flow control method must perform an arbitration to decide which packet can get access to the link. After the arbitration, the winning packet is sent through the link while the losing packets are either misrouted which will waste network bandwidth by sending packets into wrong directions or even dropped.

To overcome these challenges, more commonly, buffers are added to NoC for more efficient flow control. When a packet loses in the arbitration process, instead of being dropped or misrouted, it will be stored in the buffer while waiting for the link.

## 2.3 Switching Mechanisms

Switching is the mechanism of how a message traverse its route. There are two main switching mechanisms, namely, circuit switching and packet switching. Circuit switching is a form of bufferless switching that operates by first allocating links to form a circuit from source to destination and then sending one or more packets through this circuit. Four phases are involved during a circuit switching process. The source node firstly sends a request to propagate to the destination and allocate the links. After the circuit is allocated, an acknowledgement is transmitted back to the source. Once the acknowledgement is received, the circuit is successfully established and all packets are sent along the circuit. Finally, when there is no further packet to be sent, a tail flit is sent from source to destination deallocating the reserved links as it passes. For on-chip systems, circuit switching has two major weaknesses comparing to packet switching: high latency and low throughput.

In a packet switching process, each packet is transmitted individually and may even follow different routes to its destination. Once all packets are received by the destination, they are recompiled according to the given order into the original message. Typical packet switching mechanisms include store-and-forward, virtual cut-through and wormhole.

With store-and-forward switching, each router along the communication path waits until a packet has been completely received and stored in the buffer and then forward the packet to the next router. Two resources must be allocated to the packet before it can be sent forward: a packet-sized buffer on the other side of the link, and the exclusive use of the link. While waiting to acquire these resources, no link needs to be held idle and only a packet-sized buffer on the current router is occupied. It is obvious that the store-and-forward switching has the major drawback of very high latency.

Virtual cut-through overcomes the latency penalty of store-and-forward switching by forwarding a packet as soon as the header is received and the needed buffer and link have been allocated. As with store-and-forward switching, virtual cut-through allocates buffers and links in units of packet-size. However, transmission over each hop is started as soon as possible without waiting for the whole packet to be received and stored.

Wormhole switching operates similarly to virtual cut-through, but with link and buffer allocations in the unit of flit rather than packet. When the head flit of a packet arrives at a router, it requires the network resources and can be forwarded immediately along a route. The body flits and tail flit then follow the route allocated to the head flit, while the tail flit releases the resources as it passes. Comparing with virtual cut-through, wormhole switching makes far more efficient usage of buffers which reduces the sizes, costs and power consumption of routers. The main disadvantage of worm-

hole switching comes from the fact that only the head flit has routing information. In case the head flit is blocked due to resource contention, all trailing flits will also be blocked along the route which may further block other transmissions.

## 2.4 Routing

Routing is the progress to select a communication path from the source node to the destination in a given network. Topology determines the ideal performance for a given network, whereas routing is one of the key factors which determines how much of the potential can be achieved. A good routing algorithm will lead to more balanced loads on the links across the network, with shorter communication delay. The more balanced the loads are, the closer the network throughput is to ideal.

Based on how the routing path is selected among the set of possible paths between source node and destination, routing algorithms are divided into three main categories, namely deterministic routing, oblivious routing and adaptive routing.

Deterministic routing algorithms always choose the same path between given source node and destination, even if there are more than one possibilities. These routing algorithms take into account neither the routing diversity nor the real-time network situation. As a result, poorly balanced loads on links are to be expected across the network. However, these algorithms are common in practice mainly because they are easy to implement and deadlock-free can be achieved with less efforts. The most commonly used deterministic routing algorithm is the X-Y routing for Mesh topology.

Oblivious routing algorithms, which include deterministic algorithms as a subset, have the performance advantages thanks to the consideration of path diversity. However, the real-time network situation is still not considered when making the routing decision. An example of oblivious routing algorithms is the random algorithm which uniformly distributes packets across all possible paths.

As the most advanced category of routing algorithms, adaptive routing algorithms take the real-time network situation into consideration when making routing decisions. Therefore, they are able to efficiently balance the link loads across the network, and react to the topological changes or faulty nodes during run-time. The considered information may include states of a router or link, lengths of waiting queues, historical routing information and etc.

## 2.5 Quality of Service

In the field of computer networking and other packet-switched telecommunication networks, the traffic engineering term quality of service (QoS) refers to resource reservation control mechanisms rather than the achieved service quality. Quality of service is the ability to provide different priorities to different applications, users, or data flows, or to guarantee a certain level of performance to a data flow [111]. For example, a required bit rate, delay, jitter, packet dropping probability or bit error rate may be guaranteed.

A network or protocol that supports QoS may agree on a traffic contract with the application software and reserve capacity in the network nodes, for example during a session establishment phase. During this session it may monitor the achieved level of performance, such as the data rate and delay, and dynamically control scheduling priorities in the network nodes. It releases the reserved capacity during the tear down phase [111].

Many problems are prone to occur to packets as they travel from origin to destination, some of them are as follows:

**Dropped Packets** - Routers may fail to deliver some packets if they arrive when all buffers are already full. Depending on the state of the network, some of, or even all, the packets can be dropped, which is very hard to predict in advance. The receiving application may require these packets to be retransmitted, possibly causing severe delays in the overall transmission.

**Delay** - It might take a long time for a packet to reach its destination, because it gets held up in long queues, or takes a less direct route to avoid congestion. In some cases, excessive delay can render an application, such as VoIP or on-line gaming, unusable.

**Jitter** - Packets from the source will reach the destination with different delays. A packet's delay varies with its position in queues of the routers along the path between source and destination and this position can vary unpredictably. This variation in delay is known as jitter and can seriously affect the quality of streaming audio and video.

Out-of-Order Delivery - When a collection of related packets is routed through a network, different packets may take different routes, causing different communication delays. The result is that the packets arrive in a different order than they were sent. This problem requires additional protocols responsible for rearranging out-of-order packets to an isochronous state once they reach their destination.

*Error* - Sometimes packets are misdirected, or combined together, or corrupted, while being delivered. The receiver has to detect these errors and if any error is found, it should be able to correct it or ask the sender to send again.

In certain interconnection networks, it is useful to divide network traffic

into a number of classes to more efficiently manage the allocation of resources to packets. Different classes of packets may have different requirements; some classes are latency-sensitive, while others are not. Some classes can tolerate latency but not jitter [26].

The traffic classes in NoC based systems fall into two broad categories: guaranteed service classes and best effort classes.

Guaranteed service classes guarantee a certain level of performance as long as the traffic they inject complies with a set of restrictions. There is a service contract between the network and the client. Once the client satisfies the restrictions in the service contract, the network will deliver the performance. The client side of the agreement usually restricts the volume of traffic that the client can inject, that is, the maximum offered throughput.

In contract, the network makes weak promises to the best efforts packets. Depending on the network, these packets may have arbitrary delay or even be dropped. As depicted by its name, the network will make its best effort to deliver the packets to their destination.

## 2.6 NoC Topologies

Interconnect networks are composed of a set of shared routers and channels, and the topology of the network refers to the arrangement of these elements. The topology of an interconnect network is analogous to a roadmap where the channels (like roads) carry packets (like cars) from one router (like intersection) to another [23]. A good topology exploits the characteristics of given network resources, providing high bandwidth while maintaining low communication latency. In this section, we present and study different existing NoC topologies including Ring, Torus, Mesh, Spidergon and Fat-tree.

#### 2.6.1 Ring

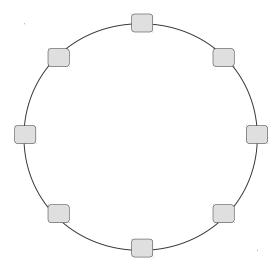

A ring network is a network topology in which each router connects to exactly two other routers, forming a single continuous pathway for signals through each router. Figure 2.3 shows a case of eight-router ring network. Comparing with bus-based systems, a ring network does not require a central node to manage the connectivity between routers, and therefore provides better performance under heavy network load. However, since a ring topology provides only one pathway between any two nodes, the entire network may be disrupted by the failure of a single link or router. Moreover, the scalability of ring topologies is limited because removing, adding and changing of a router can affect the whole network. From the energy point of view, the power consumption of routers in Ring topology is expected to be lower than in many other topologies. However, in communication intensive systems, the total energy consumption can be higher due to the potentially

long network delays. Moreover, larger buffers are needed to be implemented in the routers in order to store the delayed packets, which will become a major static energy consuming source.

Figure 2.3: An example of Ring topology

#### 2.6.2 Torus

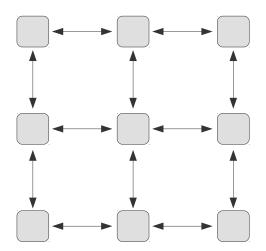

Another well-known symmetric topology is hypercubes which is a k-aray n-cubes network consisting of  $N=k^n$  nodes arranged in an n-dimensional cube with k nodes along each dimension. Ring topology can be regarded as a subset of hypercubes where n=1 and k equals the number of nodes in the ring. When n=2, the hypercube becomes a radix-k 2D Torus network where each node is assigned with an n-digit radix-k address  $\{a_{k-1},\ldots,a_0\}$  and is connected by a pair of channels to all nodes with addresses that differ by  $\pm 1 \pmod{k}$ . The regular physical arrangement in Torus network is well matched to on-chip packaging constraints. The main drawback of this topology is the long wrap-around links which require not only higher implementation cost but also power consumption. Figure 2.4 shows a 3-ary 2-cube Torus network which is also often known as  $3 \times 3$  Torus.

#### 2.6.3 Mesh

As shown in Figure 2.5, a Mesh network is subset of Torus network without the connecting channels between address  $a_{k-1}$  and address  $a_0$  in all directions. Thus Mesh outperforms Torus by lower power consumption and easier implementation and has become the mostly used NoC topology. However, it gives up the edge symmetry of Torus network which can cause load imbalance for many traffic patterns. More detailed studies of Mesh topology

Figure 2.4: An example of Torus topology

will be elaborated and compared with the proposed Honeycomb topology in the later sections.

Figure 2.5: An example of Mesh topology

## 2.6.4 Spidergon

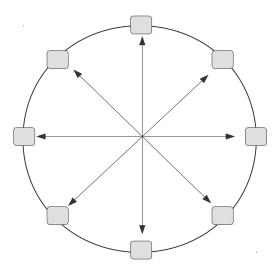

Spidergon is another on-chip communication architecture which was proposed in [47]. As shown in Figure 2.6, a basic Spidergon unit consists of 8 nodes and 12 bidirectional links. The advantages of Spidergon topology include two-hop communication between any pair of nodes, higher aggregate throughput under certain conditions, simpler routing algorithm and

less wiring than a crossbar based interconnect. The main constraint of Spidergon topology is its scalability especially when the number of nodes is more than eight which will result in complex physical layout.

Figure 2.6: An example of Spidergon topology

#### 2.6.5 Fat-tree

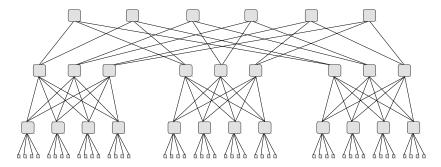

The fat-tree network is a universal network topology designed for efficient communication. It has been adopted by on-chip networks as an alternative of Torus-based architectures [2]. In a fat-tree based NoC, as shown in Figure 2.7, several PEs (4 PEs in this example) are connected to a router at the lowest level, which is then connected to the rest of the network through multiple upper links. By judiciously choosing the fatness of links, the network can be tailored to efficiently use any bandwidth made available by packaging and communications technology. The advantage of this topology is that the number of switches is smaller than other topologies. However, routers at higher level are prone to become bottlenecks in communication intensive scenarios which will result in lower energy efficiency and unbalanced heat dissipation.

## 2.7 Chapter Summary

In this chapter, we introduce the NoC architecture which can solve the challenges that current SoC based systems are facing, as described in the previous chapter. With the maturity of technologies, NoC based systems have gained wide acceptance not only in the academia and research institutes, but also in industries with emerging commercial applications. As the

Figure 2.7: An example of fat-tree topology

number of on-chip components grows, NoC is regarded as one of the most promising architecture for future IC designs.

Thereafter, several key system characteristics of NoC architectures are discussed, including flow control, switching mechanism, routing, quality of service as well as topologies. Each of these characteristics has multiple attributes, the choice of which are dependent on the system requirements including performance, power consumption, etc.

## Chapter 3

# Energy Efficiency in NoCs

NoC is a communication platform specially designed for large scale SoCs with many densely integrated on-chip electrical components. Therefore there are two main reasons making energy efficiency crucially important. First, the biggest market for NoC based systems is the portable devices and thus it will confront the bottleneck of battery capacity and energy limitation. Second, with the shrink of feature sizes, the integration density of on-chip components are getting higher than ever, which makes heat hard to dissipate. Hence, low power consumption and heat dissipation are two of the most important design concerns in NoC based systems.

## 3.1 Sources of Energy Consumption

In order to improve the energy efficiency, in this section, we firstly examine the sources of energy consumption.

Equation 3.1 shows the main sources of power dissipation in CMOS devices  ${\cal C}$

$$P = \underbrace{\left(\frac{1}{2}C_L V_{DD}^2 + Q_{SC} V_{DD}\right) f N}_{P_{Dunamic}} + \underbrace{I_{leak} V_{DD}}_{P_{Leakage}}$$

(3.1)

where  $V_{DD}$  is the supply voltage,  $P_{Dynamic}$  is the dynamic power consumption caused by changes to the outputs of the CMOS circuit, such as transitions from logic 0 to 1 or vice versa,  $P_{Leakage}$  is the static power consumption which is dissipated whenever the circuit is powered on. The leakage power consumption is independent of the switching activity and operating frequency and therefore can be assumed to be constant for a certain circuit.

#### 3.1.1 Dynamic Power Consumption

There are two major components of dynamic power consumption, namely, switching power  $(P_{SW})$  and short circuit power  $(P_{SC})$ , as shown in Equation 3.2. Both sources of dynamic power consumption are dependent on the switching activity, i.e. the number of gate output transitions per clock cycle N, and the operating frequency f.

$$P_{Dynamic} = P_{SW} + P_{SC} (3.2)$$

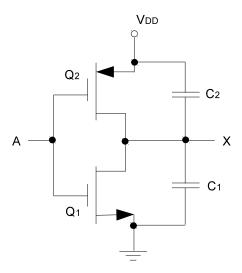

In the following of this chapter, we take an inverter shown in Figure 3.1 as a general model of any CMOS gate.

Figure 3.1: An Example of Inverter

#### 3.1.2 Switching Power Consumption

The switching power is dissipated by charging and discharging the nodes capacitance  $C_L$ , and therefore it is also referred as capacitive power consumption. For the sake of simplicity, we assume all capacitances are at the output side. As shown in Figure 3.1, the total capacitance  $C_L$  consists of  $C_1$  which is the capacitance to ground and  $C_2$  which is the capacitance to  $V_{DD}$ . When the input A is at logic 0, the n-channel transistor  $Q_1$  is open and the p-channel transistor  $Q_2$  is closed, leading to a logic 1 at the output X. At the same time, the capacitance  $C_2$  is emptied, shortened by  $Q_2$  and the capacitance  $C_1$  is charged. A change on A from logic 0 to 1 causes  $Q_1$  to close, which will discharge  $C_1$  and  $Q_2$  to open, which will charge  $C_2$ . During this single transition, a charge of  $C_2V_{DD}$  was taken from the power supply. On the next input change the charge  $C_1V_{DD}$  will be taken from

the power supply. Assuming that  $C_L=C_1+C_2$ , we can say that after one input transition from 0 to 1 and back to 0 the inverter has taken a charge of  $(C_1+C_2)V_{DD}$  from the power supply. Therefore, we can average this for one single output transition to  $\frac{1}{2}C_LV_{DD}$ . The power dissipated by this is  $\frac{1}{2}C_LV_{DD}^2$  which leads to Equation 3.3 for the switching power  $P_{SW}$ .

$$P_{SW} = \frac{1}{2} C_L V_{DD}^2 f N (3.3)$$

### 3.1.3 Short Circuit Power Consumption

During the input transition of a CMOS circuit, there is a period in which both the nMOS and pMOS will conduct, causing a short circuit to flow from power supply to ground, as shown in Figure 3.1 for an inverter without load. This current flows as long as the input voltage  $V_{in}$  is higher than a threshold voltage  $V_T$  and lower than  $(V_{DD} - V_T)$  [100].

The short circuit current is also depending on the gain factor  $\beta$  (amplification) of a MOS transistor and input rise and fall times  $\tau$ . According to [100], the mean current during a time T (equal to one period of the input signal) can be seen as Equation 3.4.

$$I_{SCmean} = \frac{1}{12} \frac{\beta}{V_{DD}} (V_{DD} - 2V_T)^3 \frac{\tau}{T}$$

(3.4)

In CMOS circuit, power is the product of current and supply voltage, and operating frequency  $f = \frac{1}{T}$ . Therefore, the short circuit power consumption can be calculated by Equation 3.5.

$$P_{SC} = \frac{\beta}{12} (V_{DD} - 2V_T)^3 \tau f \tag{3.5}$$

### 3.1.4 Leakage Power Consumption

Leakage consumption is the main source of static power consumption. It is caused by the leakage currents of transistors and pn-junctions. In Figure 3.1, when the input signal is logic 0, the n-channel transistor  $Q_1$  is open. The leakage power is determined by the leakage current  $I_{0n}$  of  $Q_1$ . Likewise, when the input signal is logic 1, the n-channel transistor  $Q_2$  is open. The leakage power is determined by the leakage current  $I_{0p}$  of  $Q_2$ . Therefore, the leakage power can be calculated by Equation 3.6.

$$P_{Leakage} = P_S = V_{DD} \frac{I_{0n} + I_{0p}}{2} = I_{leak} V_{DD}$$

(3.6)

With the development of CMOS technology, the threshold voltage, channel length and gate oxide thickness are reduced from generation to generation. At the same time, however, leakage currents increase accordingly [84].

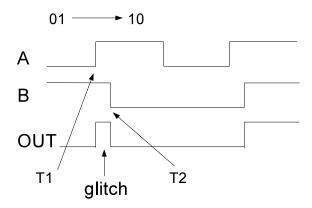

Figure 3.2: An Example of Glitch

Since dynamic power consumptions with more advanced CMOS are lower, it is projected that leakage power will become the dominant part of the overall power consumption [27].

### 3.1.5 Glitch Power Consumption

Glitches are unwanted transitions of a signal after an input change until the final output value is reached. This behaviour is caused by having input that are not switching simultaneously, called logic hazard. Glitches occur when the output node temporarily has a value that is not the steady-state value.

Figure 3.2 shows an example of glitch in an "AND" gate OUT = AB. When input signals come, they arrive at the "AND" gate at different time stamps, i.e., signal A arrive at time stamp T1 while signal B at time stamp T2. Therefore, when input pattern changes from "01" to "10", an unexpected behaviour happens, which is the logic 1 at the gate output between time stamps T1 and T2.

In CMOS circuits, glitches can cause significant dynamic power consumption since they represent at least two binary transitions per clock period.

### 3.2 Power vs. Energy

Before beginning the discussion of energy efficiency in NoCs, it is worthwhile firstly to review the difference between two concepts, namely, power and energy.

Energy has units of Joules and can be related to the amount of work done or electrical resources expended to perform a computation. Power, on the other hand, is a measure of the rate at which energy is consumed per unit time, and is typically expressed in units of Watts, or Joules/second [10]. Equation 3.7 shows the relationship between these two concepts.

$$Power = Energy/Time (3.7)$$

### 3.2.1 Low Power Systems

Reducing power consumption is obviously an important aspect in optimizing energy efficiency, which keeps the design of low power systems at the top on the list of design issues for researchers in both academia and industry. Some main stream power optimization methods are described as follows [95] while more innovotive solutions are to be explored.

Using digital circuits whenever possible - During the 1960s, analog circuits were preferred whenever possible in order to avoid the large standby power drain of bipolar digital circuit [68]. With the development of CMOS technology, the static power consumption of digital circuits was greatly reduced, and therefore, digital CMOS circuits have received the primary focus in low power circuit design.

Use the lowest possible supply voltage for digital circuit - As shown in Equation 3.3, switching power consumptions are heavily dependent on supply voltage  $V_{DD}$  and operating frequency f. Order of magnitude power reduction has been achieved by scaling the both  $V_{DD}$  and f. Therefore, for certain applications such as wireless sensor networks or radio frequency identifiers, this method offers an ideal solution which prevents power waste by providing "just enough" computing capabilities.

Use the smallest possible feature size - As can be seen from the previous section, several sources of power consumption are dependent on capacitances. Since capacitance decreases with decreasing feature size, improvements in IC fabrication technology yield more efficient power dissipation. As device geometries continue to shrink, power consumption will be further optimized.

*Optimize circuit architectures* - To achieve higher system performance, especially the computing speed, different architectural techniques have been proposed which trade computing speed with area costs. Parallel processing and pipelining, as two well-known techniques, can be utilized to lower power consumptions by reducing the supply voltages and operating frequencies without majorly affect system performances.

Parallel processing uses duplicated hardware components to achieve better circuit performance, thus also allows power reduction by lowering supply voltages and operating frequencies. Considering a datapath with supply voltage  $V_{DD}$ , frequency f and capacitance C, the power consumption is then  $P_0 = CfV_{DD}^2$ . If the operation is parallelized to N identical modules, each operates at the frequency of  $\frac{f}{N}$ , the supply voltage can be reduced accord-

ingly since the speed requirement for each module is reduced. Assume the new voltage is  $\alpha V_{DD}$  where  $\alpha$  is the voltage reduction factor. Theoretically, the total capacitance increases also by a factor of N, to NC. Therefore, the new power consumption can be calculated by  $P = (NC) \frac{f}{N} (\alpha V_{DD}^2) = \alpha^2 P_0$ .

Pipelining is another technique in which a synchronous digital circuit is constructed by partitioning the combinational logic into stages and inserting a set of memory elements, generally called an internal register, or simply a register or synchronizer, to provide temporary storage for the computed data between successive pipeline stages [14]. By doing so, the delay of the critical path can be reduced at the cost of longer latency introduced by the registers. Smaller delay allows reduced supply voltage and therefore power consumption can be lowered.

Very often, parallel processing and pipelining are combined in a circuit to multiply the performance and power benefits.

Exploit low power circuit techniques - Standard techniques include dynamic voltage and frequency scaling, clock gating, power gating, glitch reduction, intelligent selection of algorithms and numeric representations, multi-threshold voltages, etc. These techniques require changes and optimizations of both hardware and software. Designs at all levels of an electronic system are involved including circuit level, architecture level, algorithm level and even the application program which is run on top of the system.

Use dedicated hardware - Dedicated hardware always achieves lower power consumption than programmable circuits. Consequently, an optimal low-power design provides only as much programmability as absolutely necessary. Moreover, dedicated hardware can be optimized for the software system. An example is Apple's laptop which have much longer battery life than other laptops. One of the main reason is that it is dedicated to Apple's operating system and thus has optimized power consumption solution.

### 3.2.2 Energy Efficiency

As depicted in Equation 3.7, energy is the product of power and time. Therefore, low power consumption of electronic systems can not be always translated into energy efficiency.

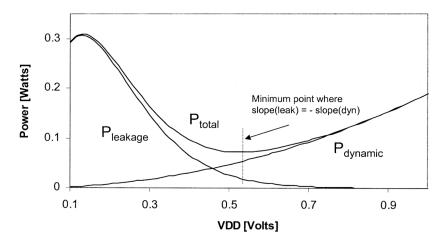

When supply voltages and operating frequencies are reduced, the power consumption of an electronic system is surely lowered according to the equations shown in the previous subsection. However, as speed is reduced approximately by the factor of  $(V_{DD} - V_T)$  [93], the duration to complete a task is expected to increase, and therefore there is potential risk of higher energy consumption. A major contributor is the leakage power consumption which is projected to become a dominating energy consumer in the future.

Therefore, energy efficiency is a balanced factor between power and per-

formance, especially system speed. We introduce the concept of power performance product to reflect this factor, as will be shown in the following chapters.

### 3.3 Power Challenges of NoC based Systems

As it is in all embedded systems, power consumption remains as one of the key challenges in NoC based systems, where power is consumed by processing elements, communication infrastructure and leakage current.

### 3.3.1 Processing Element

Processing elements are made of logic and registers which are usually implemented as digital CMOS circuits. Therefore, the power consumption sources listed in Section 3.1 also applies for NoC based systems.

Furthermore, NoC is especially designed for electronic systems where a large number of processing elements, such as processors, memory banks, blue-tooth, etc., are integrated on a single chip. It is obvious that the total power consumption of the chip will be higher, making both battery life and heat dissipation more challenging design concerns.

Besides, one of the main advantages of NoC based systems is its capability of reusing processing elements by defining network interfaces. However, this admirable feature does not come for free. Reusing the pre-defined IP blocks always means that we use something more general, thus less optimal, than necessary for a particular task [44]. Consequently, the processing elements in NoC based systems may consume more power comparing with dedicatedly designed circuits.

Apart from the methods mentioned in Section 3.2.1, one effective way to reduce NoC power consumption is to reduce the amount of data sent over the network which can be achieved by at least two methods at the processor level. The first method is to optimize the mapping of tasks as well as processing elements. In a tile based NoC, a tile can consist of multiple processing elements. By implementing most frequently communicating components in the same tile, less data will be transmitted to the communication network. The other commonly used method is data compression. During the recent years, researchers have proposed several effective ways of data compression at the cache and network levels [49].

#### 3.3.2 Communication

In SoCs, interconnect wires account for a significant fraction, which can be as high as 50%, of the total power consumption [58]. As the technology scales into the nanometer regime, it is projected that the delay and energy

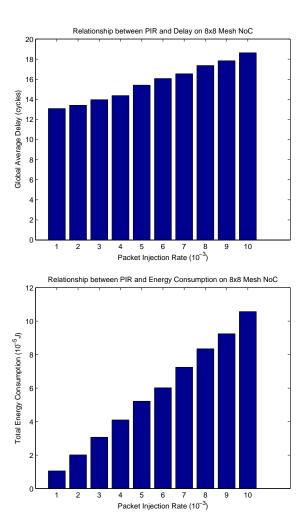

Figure 3.3: Relationships between delay, energy and PIR

consumption of global interconnect structures will consume larger shares of power [81].

Comparing with bus-based SoCs, NoC based systems have higher power efficiency due to the avoidance of long global wires. However, the interconnection network remains as a major power consumer out of all the power contributors. For the Alpha 21364 processor with distributed memory, the integrated switches and link circuits consume 23W out of the total 125W chip power [87]. On the 16-tile RAW processor, the interconnection network accounts for as high as 35% of the total chip power [51].

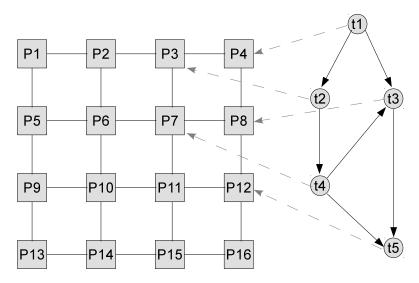

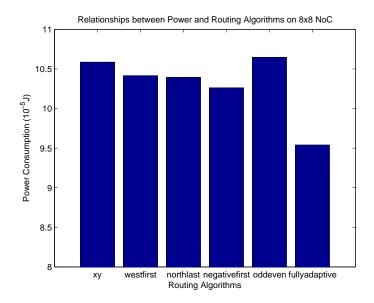

To illustrate the different reactions of communication delay and consumed energy against changes in the number of packets in the network, we perform a network level simulation using Noxim with different packet injection rates (PIRs), starting from 0.001 to 0.01. The PIR is based on memory less Poisson distribution, and the network is of 8x8 Mesh topology.

Figure 3.3 shows the result of this simulation. It is obvious that under this non-congested network environment, the consumed energy grows much faster than the communication delay with the increasing PIR.

### 3.3.3 Leakage Power Consumption

As technology scales to deep sub-micron processes, leakage power becomes increasingly significant as compared to dynamic power. In NoCs, there are two main leakage power consumers, namely, on-chip routers and links. According to the simulation results shown in [15], links only consume approximately 5% of the leakage power. This is due to the fact that wires do not dissipate leakage power, and thus the leakage consumption of just the drivers is minimal, comparing with routers. However, in NoCs with more long or global wirings, the inserted repeaters will consume a large proportion of leakage power, especially with smaller feature sizes. Thus, the avoidance of global wiring is desirable in order to achieve high energy efficiency.

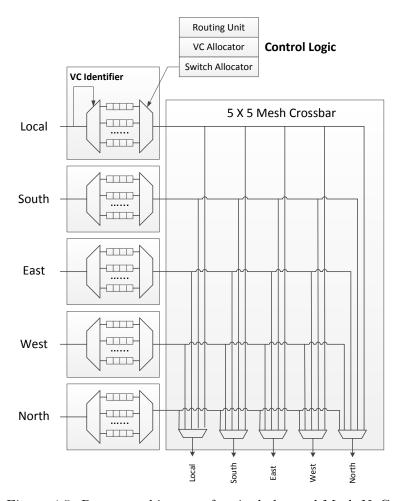

In routers, the major leakage power consumers are buffers, crossbars and arbiters, out of which buffers consume over 64% of the leakage energy [15]. Therefore, to reduce the leakage power consumption, optimization of buffers is of crucial importance.

### 3.4 Power Models

To optimize the energy efficiency in NoCs, it is worthwhile to investigate into the communication layers and find the power sources in each phase.

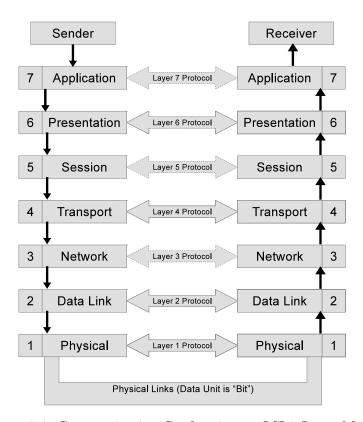

### 3.4.1 OSI 7-Layer Model

Comparing with the conventional bus based on-chip systems, NoCs enable the inter-component communication to be simpler and more predictable, by leveraging the existing technologies of computer networks. Therefore, before introducing the power consumers in NoCs, we firstly present the standard abstract layers in communication systems, namely, Open Systems Interconnection model (OSI model).

There are seven abstract layers in the OSI model performing different roles in data communication. Therefore, this model is also known as OSI 7-layer model. The roles of the layers are described as follows.

**Application Layer** - This layer supports application and end-user processes. Communication partners are identified, quality of service is identified, user authentication and privacy are considered, and any constraints on data syntax are identified. Everything at this layer is application-specific.

This layer provides application services for file transfers, e-mail, and other network software services. Telnet and FTP are applications that exist entirely in the application level.

**Presentation Layer** - This layer provides independence from differences in data representation (e.g., encryption) by translating from application to network format, and vice versa. The presentation layer works to transform data into the form that the application layer can accept. This layer formats and encrypts data to be sent across a network, providing freedom from compatibility problems. It is sometimes called the syntax layer.

**Session Layer** - This layer establishes, manages and terminates connections between applications. The session layer sets up, coordinates, and terminates conversations, exchanges, and dialogues between the applications at each end. It deals with session and connection coordination.

**Transport Layer** - Usually TCP (the top half of TCP/IP). This layer provides transparent transfer of data between end systems, or hosts, and is responsible for end-to-end error recovery and flow control. It ensures complete data transfer.

**Network Layer** - Typically IP (the bottom half of TCP/IP). This layer provides switching and routing technologies, creating logical paths, known as virtual circuits, for transmitting data from node to node. Routing and forwarding are functions of this layer, as well as addressing, internetworking, error handling, congestion control and packet sequencing.

Data Link Layer - Ethernet, ATM, Frame Relay, etc. At this layer, data packets are encoded and decoded into bits. It furnishes transmission protocol knowledge and management and handles errors in the physical layer, flow control and frame synchronization. The data link layer is divided into two sub-layers: The Media Access Control (MAC) layer and the Logical Link Control (LLC) layer. The MAC sub-layer controls how a computer on the network gains access to the data and permission to transmit it. The LLC layer controls frame synchronization, flow control and error checking.

*Physical Layer* - This layer conveys the bit stream - electrical impulse, light or radio signal – through the network at the electrical and mechanical level. It provides the hardware means of sending and receiving data on a carrier, including defining cables, cards and physical aspects. Fast Ethernet, RS232, and ATM are protocols with physical layer components.

Figure 3.4 shows a scenario where a sender transmits data to a receiver via communication network. The data firstly go through the seven layers from the sender's side until it reaches the physical communication links which transfer data bit by bit. The data will then be transmitted upwards via the seven layers at the receiver's end until reaching final destination. In a typical communication system, energy will be consumed at every layer during the communication process.

Figure 3.4: Communication Conforming to OSI 7-Layer Model

### 3.4.2 Abstraction Layers in NoC Communication

Inspired by the OSI 7-layer model, NoC researchers have proposed similar layered stacks. Instead of seven layers, NoC design focuses mostly on five layers, namely, application layer, transport layer, network layer, data link layer and physical layer [45], [111].

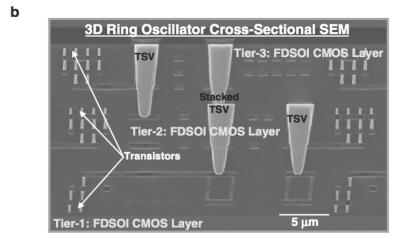

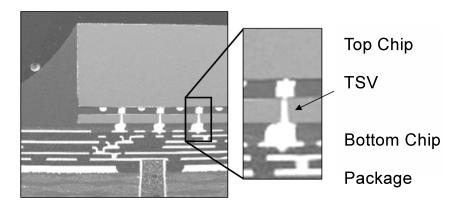

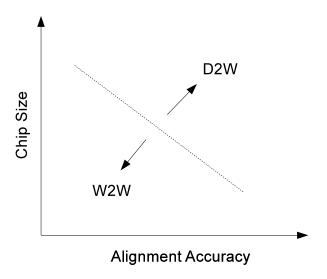

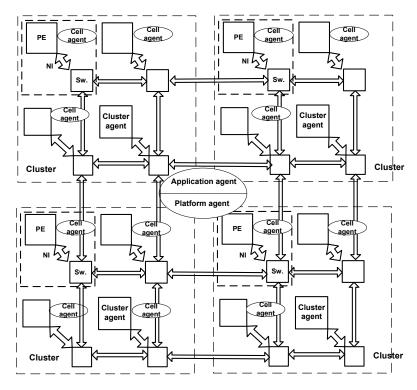

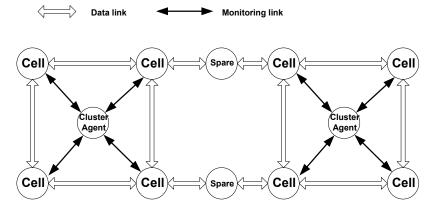

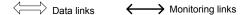

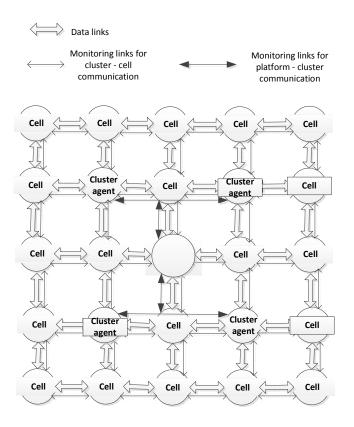

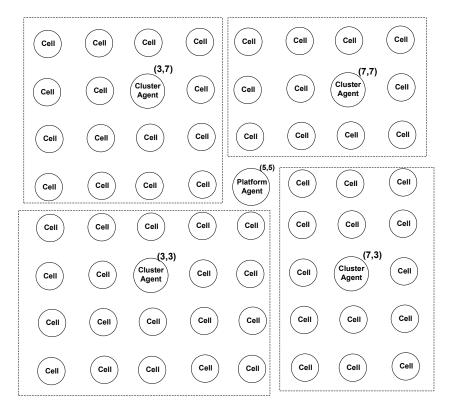

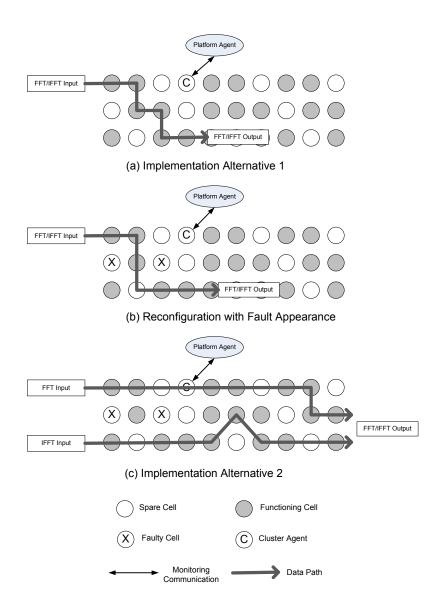

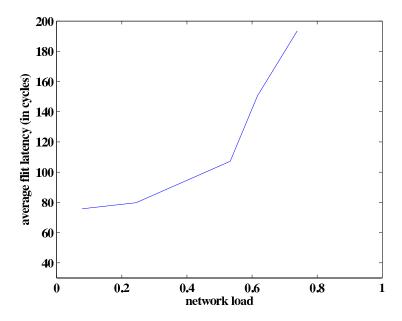

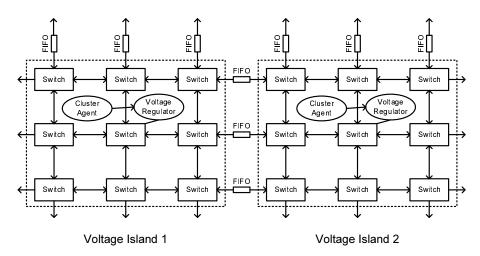

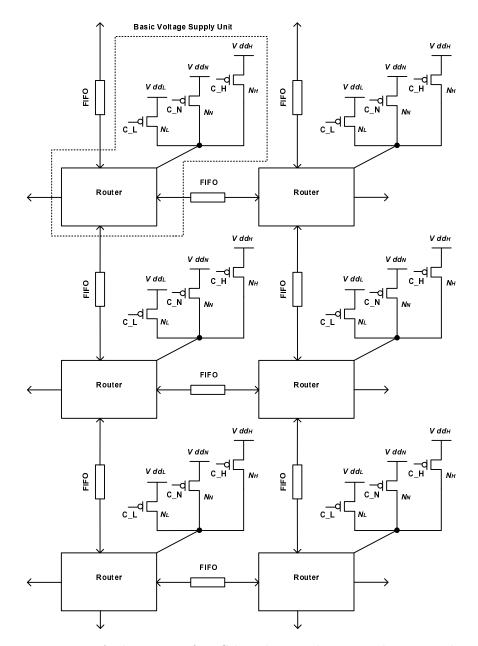

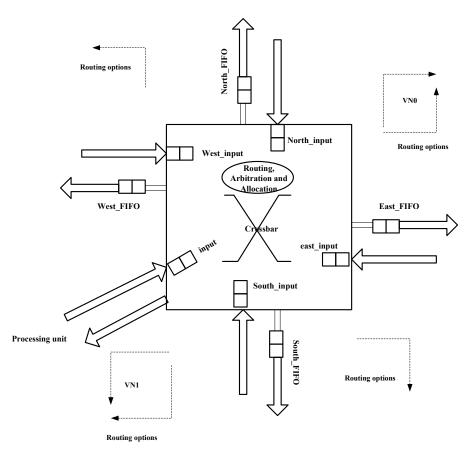

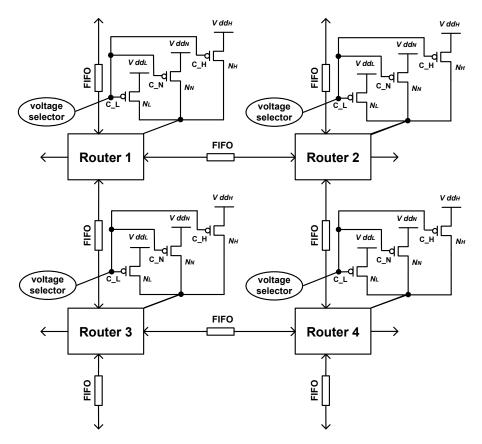

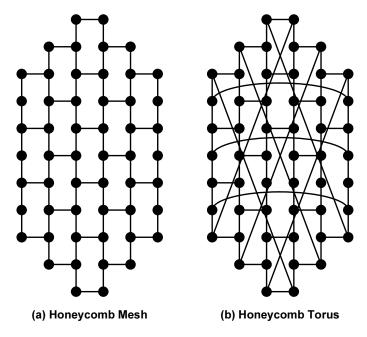

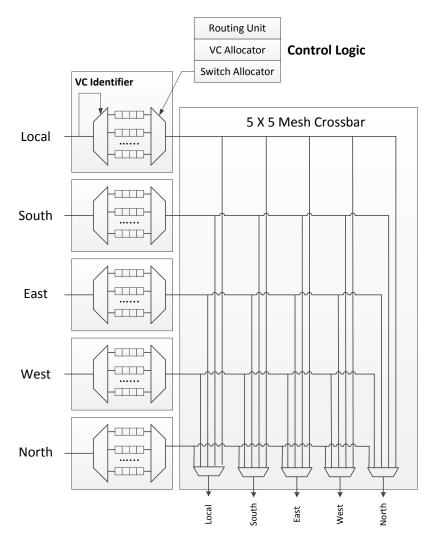

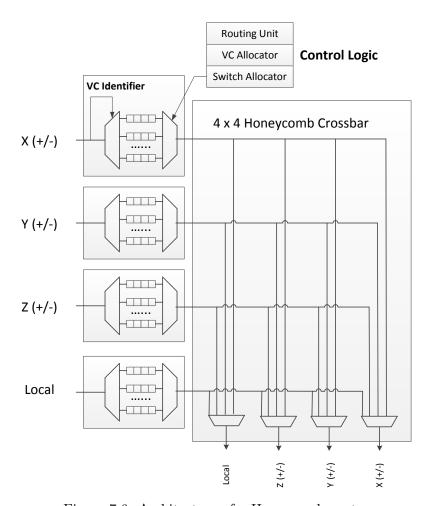

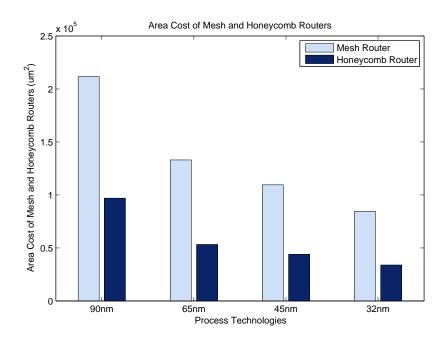

### **Application Layer**