## Hierarchical Agent-based Adaptation for Self-Aware Embedded Computing Systems

#### Liang Guang

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Beta on December 10th, 2012, at 12 noon.

University of Turku

Department of Information Technology

20014 Turun Yliopisto

#### Supervisors

Professor Hannu Tenhunen

Professor Jouni Isoaho

Associate Professor Juha Plosila

Associate Professor Pasi Liljeberg

Department of Information Technology

University of Turku

Turku, Finland

#### Reviewers

Associate Professor Waltenegus Dargie Chair of Computer Networks Faculty of Computer Science Technical University of Dresden Dresden, Germany

Professor Peeter Ellervee Department of Computer Engineering Tallinn University of Technology Tallinn, Estonia

#### Opponent

Professor Jan Madsen

DTU Informatics

Technical University of Denmark

Kongens Lyngby, Denmark

#### Abstract

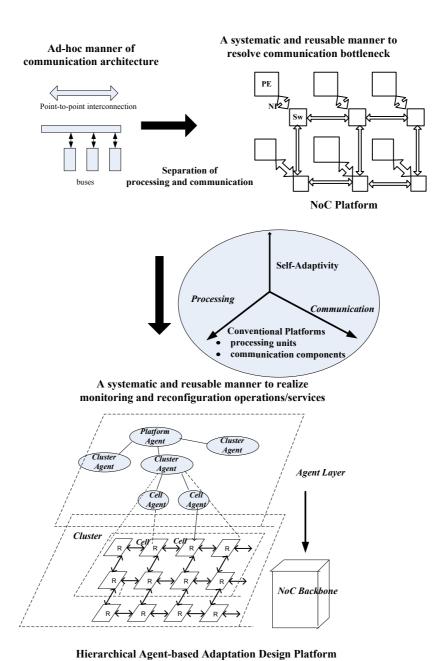

This thesis proposes Hierarchical Agent-based Adaptation (H2A), a scalable platform-based design paradigm for the rapidly expanding parallel embedded systems. With the constant progress of semiconductor industry, the available hardware resources are steadily increasing, while the constraints in power/energy consumption and dependability issues pose tougher challenges than ever before. This phenomenon calls for a system-level paradigm shift towards self-aware and adaptive (SAA) systems, which are able to provide dynamic performance optimization based on self-monitored status and incidents.

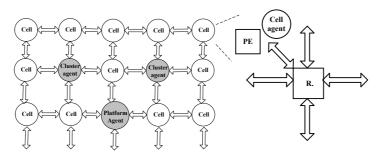

The thesis motivates the paradigm shift towards SAA systems by examining the technology trends in parallel computing and embedded systems. Then it explores the existing techniques for run-time monitoring and reconfiguration, either with centralized, clustered or purely distributed architectures. The design and integration of these existing techniques and potential mechanisms require a scalable management backbone to provide global and local services, in particular for energy management and dependable computing. Answering this need, the thesis introduces the H2A system architecture, which integrates self-adaptation controllers, *Agents*, for monitoring and reconfiguring systems on hierarchical levels. The thesis overviews the functional partition of agents for coarse- and fine-grained services, and formulates the software/hardware (SW/HW) co-synthesis guidelines to implement the agents in a scalable manner.

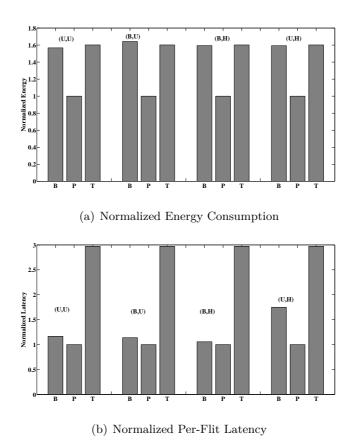

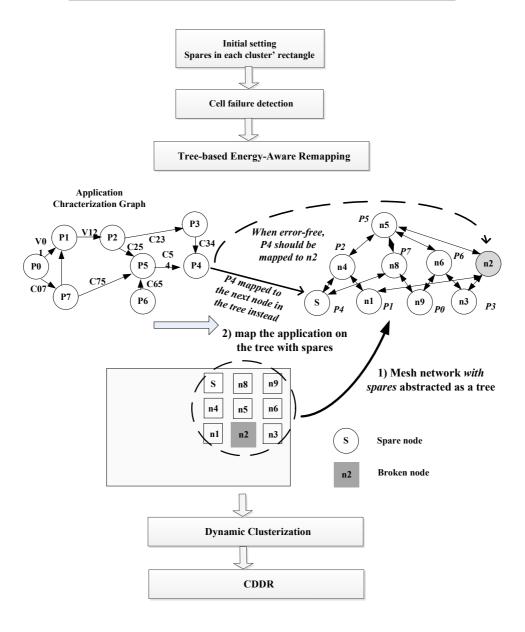

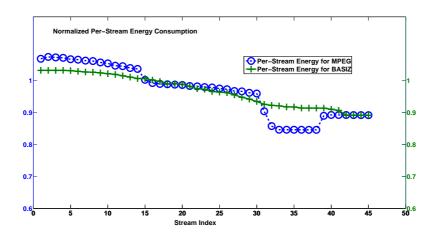

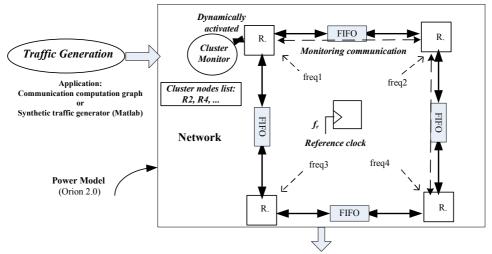

To demonstrate the design of agents for run-time adaptation, the thesis first presents hierarchical energy management service. Energy-aware mapping is performed on the top-level platform agent. Cluster-level energy management is designed as clustered decision-making and distributed reconfiguration (CDDR), which is jointly contributed by both the cluster and cell agents. To support CDDR, hybrid monitoring of local traffic loads and application mile-

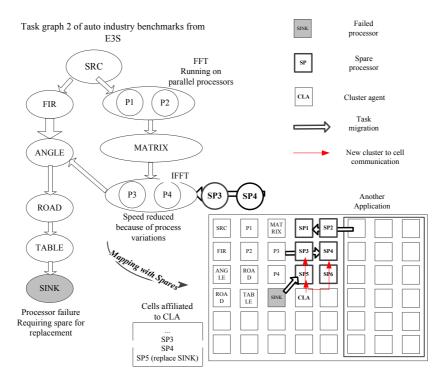

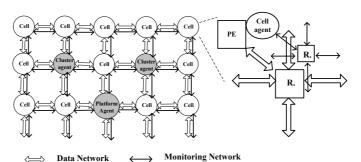

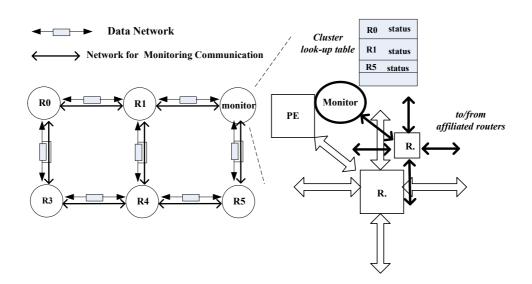

stones is performed by each cell agent. In addition to the energy management services, the thesis presents the design of H2A architecture for dependable computing. In particular, an approach for dynamic clusterization is proposed, where processing elements can be flexibly organized into different clusters lest run-time failures or performance degradation. Three-level supporting structures and a full-mesh-based physically separate monitoring network are designed to enable the dynamic clusterization. The supporting structures can be extended for other run-time adaptation services, such as energy management, thus achieving a portable and compatible system architecture.

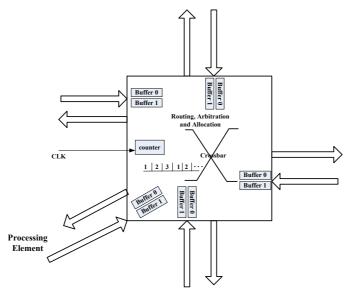

As a proof-of-concept for the H2A design paradigm, a RTL(register transfer level) implementation of Self-Aware and Adaptive Network-on-Chip (SAA-NoC) is presented. The platform agent is implemented as software running on a dedicated Leon processor. Each cluster agent integrates a software thread running on a processor and a hardware-based CLT (cluster look-up table). Each cell agent is implemented as hardware circuits wrapped within one NoC node. Both hierarchical energy management and dynamic clusterization services are implemented. Experiment results validate that the H2A system architecture can fully exploit coarse- and fine-grained adaptation services to reduce the energy consumption under the influence of unpredictable errors, while meeting both system and local performance requirements. The overhead analysis shows that both software and hardware overheads are minimal and scalable for the agent subsystem.

## Acknowledgements

Writing this doctoral thesis, ever since the beginning of my PhD program, has not been an easy process. I would like to firstly express my gratitude to my supervisors, Prof. Hannu Tenhunen, Prof. Jouni Isoaho, Prof. Juha Plosila and Prof. Pasi Liljeberg. Prof. Tenhunen has inspired and encouraged me to explore ambitious research topics, and provided me with high-level guidance towards my academic dream. Prof. Isoaho constantly encourages me to tackle challenging issues, by experimenting unconventional approaches. The H2A design paradigm originates from his vision, which I feel a true privilege to work on. Prof. Plosila has always been a dedicated and supportive supervisor in my research. We have together worked on many research tasks, and I am grateful for his support and encouragement of my sometimes impulsive ideas and plans. Prof. Liljeberg has given me valuable help through commenting and advising on topics and publication contents. We have also cooperated on several research activities, which are appreciated learning experiences in my PhD program. In addition, I wish to specially thank Prof Axel Jantsch from Royal Institute of Technology, Sweden. I have been under his guidance ever since my master thesis. Prof. Jantsch is a researcher and scientist I have been constantly learning from. I am grateful for all the discussions and cooperation we have had, which inspire my passion to research and science.

In addition to my supervisors, I would like to sincerely thank my fellow colleagues. Without their generous help, it is impossible to make progress on the challenging research topic. Foremost, Dr. Ethiopia Nigussie has been a inspiring guide, cooperative partner and loyal friend. My research progress has always been facilitated by her insights, comments and encouragement. It has been a true pleasure to have her as a friend and colleague. Besides, Khalid Latif, Kameswar Rao Vaddina, Syed Asad Jafri and Bo Yang have all given me highly-appreciated help and cooperation in my research path.

Our discussion and joint works inspire each other's study and research. In particular, I would like to sincerely thank Syed Asad Jafri for his cooperation in the implementation of the H2A design paradigm. His expertise and dedication have enabled the concrete demonstration of the novel paradigm.

I would like to thank three external experts for reviewing my thesis and being the opponent for my thesis defence: Prof. Jan Madsen from Technical University of Denmark, Prof. Waltenegus Dargie from TU Dresden, and Prof. Peeter Ellervee from Tallinn University of Technology. Thanks to their insightful comments, the thesis has been modified and improved.

I wish to thank all the colleagues and coworkers in Embedded Computer and Electronic Systems (ECES) lab and Communication Systems (ComSys) lab of Turku Center for Computer Science (TUCS). My research during these four years has been helped by many researchers and fellow students. Working in this environment has been an interesting and fruitful experience.

I would like to acknowledge the financial support from GETA (the Graduate School in Electronics, Telecommunications and Automation), which has been the main funding source of my PhD program. In addition, I would like to thank the support from Nokia Foundation, Wäinö Edward Miettinen and Ulla Tuominen Foundation.

Last but definitely not least, my most gratitude goes to my family. My mother XiaNan and father XiangChong have been supportive and understanding of my career and life choices. Any humble achievement I have made is owing to your nurturing and encouragement. In addition, I would like to thank my best friend Janne Alanen for all his caring and support of my life in Finland.

## Contents

| A  | bstra | act                                                       | iii |

|----|-------|-----------------------------------------------------------|-----|

| A  | ckno  | wledgments                                                | iii |

| Li | st of | Publications                                              | ix  |

| Li | st of | Figures                                                   | xii |

| Li | st of | Tables                                                    | xvi |

| 1  | Intr  | roduction                                                 | 1   |

|    | 1.1   | Era of Massively Parallel Computing                       | 1   |

|    | 1.2   | Design Challenges of Parallel Embedded Systems            | 3   |

|    |       | 1.2.1 Energy Efficiency                                   | 4   |

|    |       | 1.2.2 Dependable Computing                                | 5   |

|    |       | 1.2.3 Scalability                                         | 6   |

|    | 1.3   | Thesis Objectives                                         | 8   |

|    | 1.4   | Thesis Contributions                                      | 9   |

|    | 1.5   | Organization of Thesis                                    | 10  |

| 2  | Par   | adigm Shift towards Self-Aware and Adaptive Systems       | 12  |

|    | 2.1   | SAA Systems                                               | 12  |

|    | 2.2   | Monitoring and Reconfiguration Operations                 | 15  |

|    | 2.3   | Paradigm Evolution towards 3-Dimensional Design Space $$  | 18  |

|    | 2.4   | Chapter Summary                                           | 21  |

| 3  | Des   | ign Exploration of Self-Adaptation Architectures          | 22  |

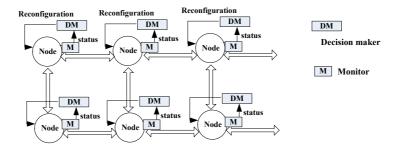

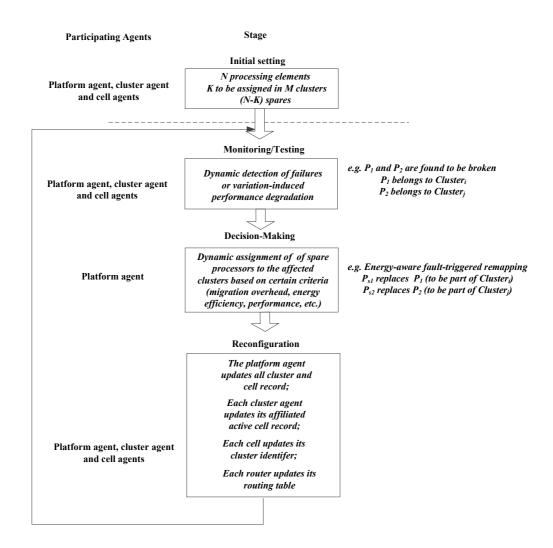

|    | 3.1   | Monitoring, Decision-Making and Reconfiguration Processes | 23  |

|    |       | 3 1 1 Monitoring                                          | 24  |

|   |     | 3.1.2 Decision-Making                                        | 24 |

|---|-----|--------------------------------------------------------------|----|

|   |     | 3.1.3 Reconfiguration                                        | 26 |

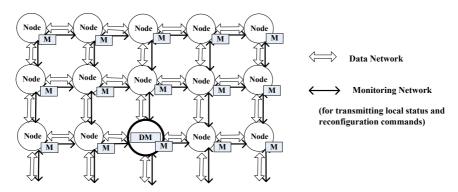

|   |     | 3.1.4 Monitoring Communication                               | 27 |

|   | 3.2 | Centralized, Clustered and Distributed Architectures         | 28 |

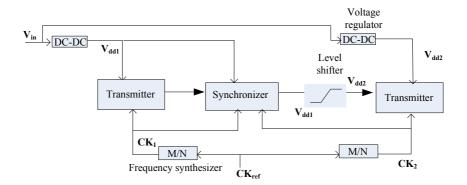

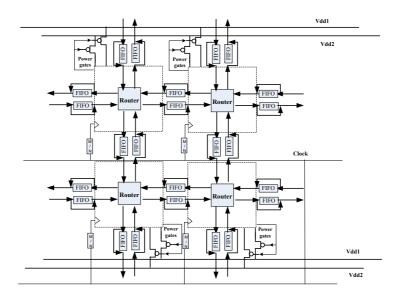

|   |     | 3.2.1 Physical Support for Voltage and Frequency Reconfigu-  |    |

|   |     | ration                                                       | 28 |

|   |     | 3.2.2 Centralized Architecture                               | 30 |

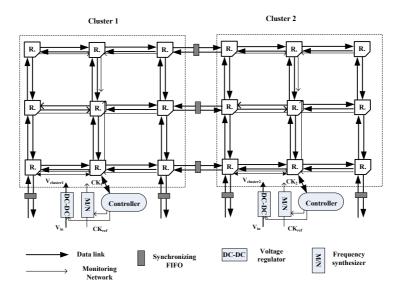

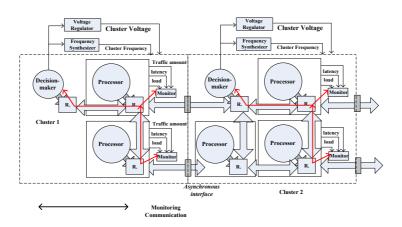

|   |     | 3.2.3 Clustered Architecture                                 | 31 |

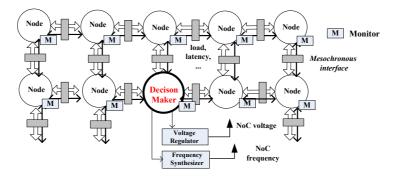

|   |     | 3.2.4 Distributed Architecture                               | 32 |

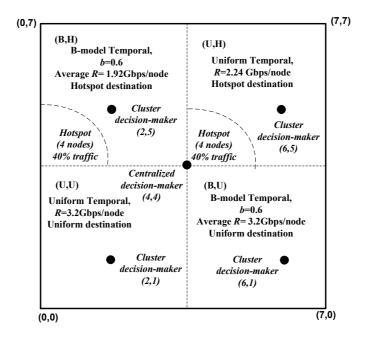

|   | 3.3 | Quantitative Comparison                                      | 33 |

|   |     | 3.3.1 Platform Setting                                       | 33 |

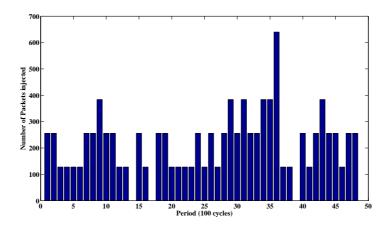

|   |     | 3.3.2 Traffic Generation                                     | 34 |

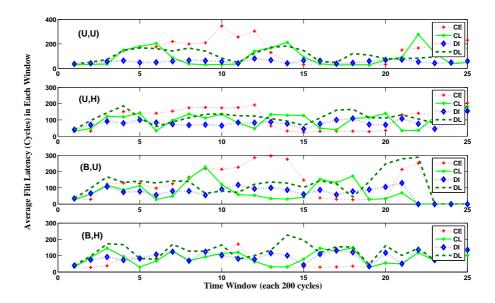

|   |     | 3.3.3 Simulation Results                                     | 36 |

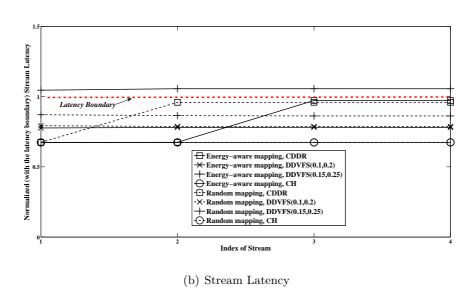

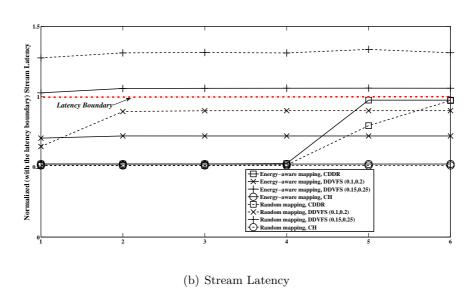

|   |     | 3.3.4 Performance                                            | 37 |

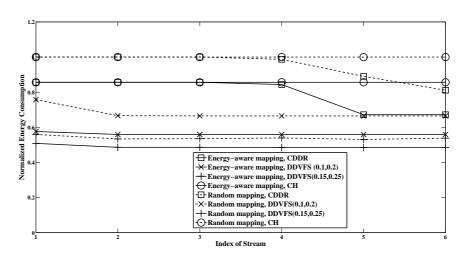

|   |     | 3.3.5 Energy Efficiency                                      | 38 |

|   | 3.4 | Summarizing Comparison                                       | 41 |

|   | 3.5 | Chapter Summary                                              | 41 |

| 4 | Hie | rarchical Agent-based Design Platform                        | 44 |

|   | 4.1 | Agent as a Design Abstraction                                | 44 |

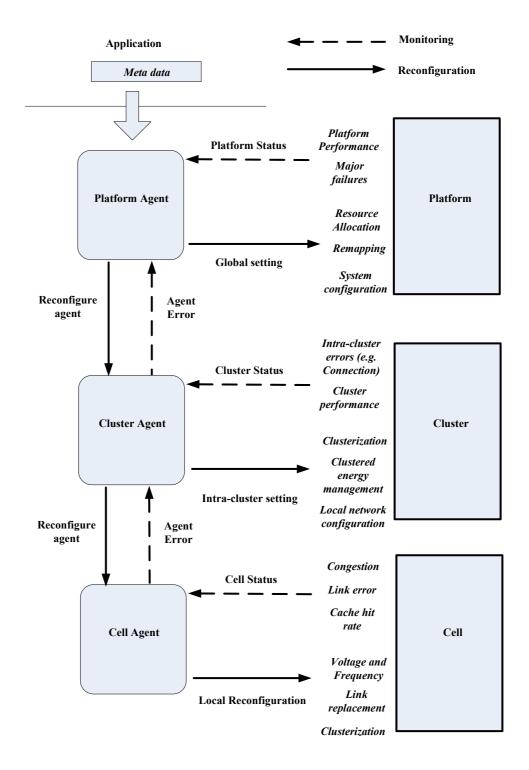

|   | 4.2 | H2A Architecture                                             | 46 |

|   | 4.3 | Agent Implementation Guidelines                              | 49 |

|   |     | 4.3.1 Alternatives                                           | 51 |

|   |     | 4.3.2 SW/HW Co-Design for Agents                             | 52 |

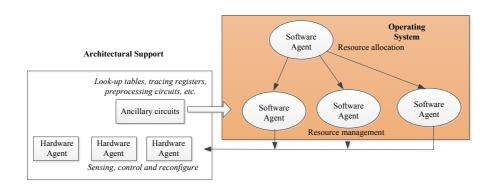

|   | 4.4 | Agents and Operating System                                  | 53 |

|   | 4.5 | Related System Architectures                                 | 55 |

|   | 4.6 | Chapter Summary                                              | 56 |

| 5 | Coa | arse- and Fine-Grained Energy Management                     | 58 |

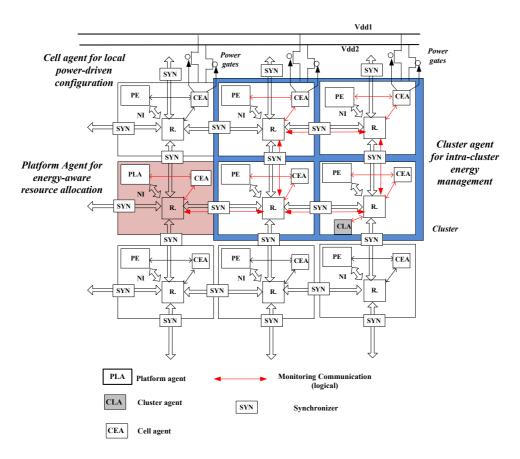

|   | 5.1 | System Architecture                                          | 58 |

|   | 5.2 | Energy-Aware Application Mapping                             | 62 |

|   | 5.3 | Intra-Cluster Energy Management                              | 64 |

|   | -   | 5.3.1 Cluster Architecture Overview                          | 65 |

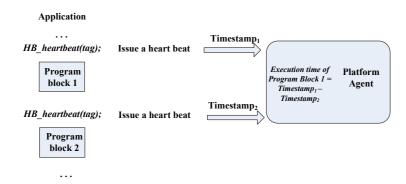

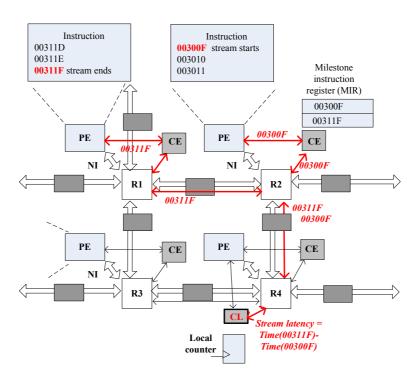

|   |     | 5.3.2 Load and Latency Monitoring                            | 66 |

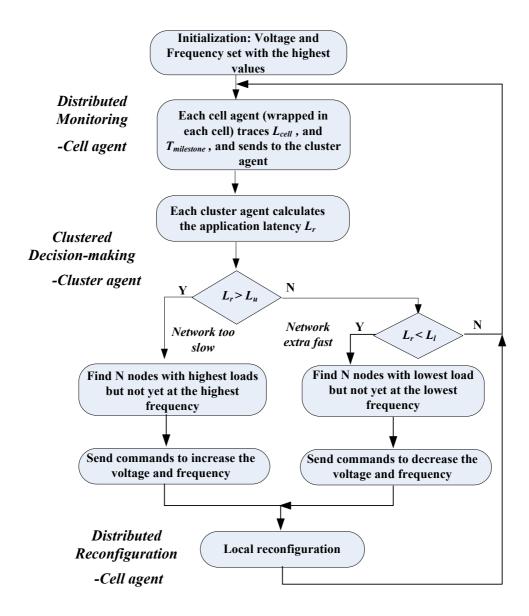

|   |     | 5.3.3 Clustered Decision-Making, Distributed Reconfiguration | 68 |

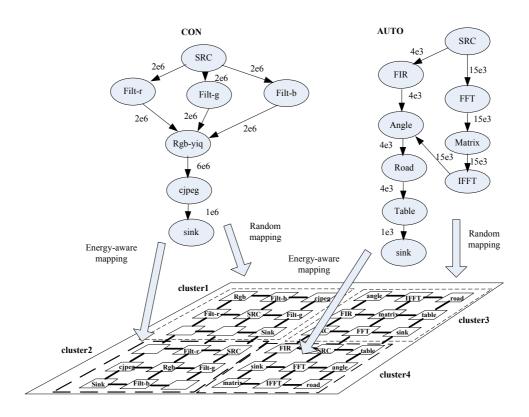

|   | 5.4 | System Integration and Quantitative Evaluation               | 69 |

|   |     | 5.4.1 Experimental Setting                                   | 69 |

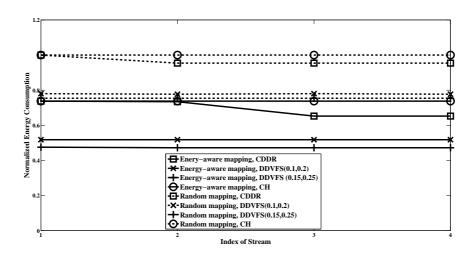

|              |       | 5.4.2 Results                                         |

|--------------|-------|-------------------------------------------------------|

|              |       | 5.4.3 Implementation Discussion                       |

|              | 5.5   | Chapter Summary                                       |

| 6            | Dyı   | namic Clusterization for Dependable Computing         |

|              | 6.1   | System Architecture Overview                          |

|              | 6.2   | Three-Level Supporting Structures                     |

|              | 6.3   | Inter-Agent Monitoring Network                        |

|              | 6.4   | System Integration                                    |

|              | 6.5   | Further Discussion                                    |

|              | 6.6   | Chapter Summary                                       |

| 7            | Imp   | plementation of Self-Aware and Adaptive NoCs          |

|              | 7.1   | NoC Platform                                          |

|              | 7.2   | Three-Level Agents and Supporting Structures          |

|              |       | 7.2.1 Platform Agents                                 |

|              |       | 7.2.2 Cluster Agents and CLT                          |

|              |       | 7.2.3 Cell Agents and CIR                             |

|              | 7.3   | System Integration                                    |

|              | 7.4   | Experiments                                           |

|              |       | 7.4.1 Experimental Setting                            |

|              |       | 7.4.2 Energy Management Results                       |

|              |       | 7.4.3 Fault-Tolerance Result                          |

|              | 7.5   | Overheads                                             |

|              | 7.6   | Chapter Summary                                       |

| 8            | Cor   | nclusion 12                                           |

|              | 8.1   | Design Era of SAA systems                             |

|              | 8.2   | Hierarchical Agent Architecture                       |

|              | 8.3   | Self-Aware and Adaptive NoC Implementation            |

|              | 8.4   | From Parallel to Distributed Computing: Future Work 1 |

| D.           | ofono | ences 12                                              |

|              |       |                                                       |

| $\mathbf{A}$ |       | S-DoNoC: High-Level Simulator for Dynamically Organi- |

|              |       | ional NoCs 14                                         |

|              | A.1   | Modular Overview                                      |

| A.2 | Network Kernel                           | 142 |

|-----|------------------------------------------|-----|

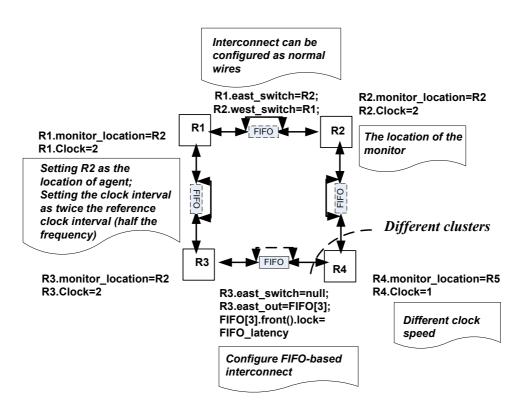

| A.3 | Simulating Dynamic Clusterization        | 142 |

| A.4 | Simulating Cluster-based Reconfiguration | 143 |

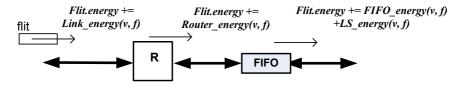

| A.5 | Integrating Power Models for DoNoCs      | 145 |

| A.6 | Traffic Generation                       | 145 |

| A.7 | Simulator Feature Summary                | 146 |

## List of Major Publications

The thesis contains the research in the following publications with new unpublished material (in Chapter 5, 6 and 7).

- 1. Liang Guang, Ethiopia Nigussie, Juha Plosila, Jouni Isoaho, Hannu Tenhunen, Survey of Self-Adaptive NoCs with Energy-Efficiency and Dependability, International Journal of Embedded and Real-Time communication Systems (IJERTCS), 3(2), pp.1-22, 2012.

- Liang Guang, Ethiopia Nigussie, Juha Plosila, Hannu Tenhunen, Dual Monitoring Communication for Self-Aware Network-on-Chip: Architecture and Case Study, International Journal of Adaptive, Resilient and Autonomic Systems (IJARAS), 3(3), pp.73–92, 2012.

- 3. Liang Guang, Juha Plosila, Jouni Isoaho, Hannu Tenhunen, HAMSoC: A Monitoring-Centric Design Approach for Adaptive Parallel Computing, Chapter in book "Autonomic Networking-on-Chip: Bio-inspired Specification, Development and Verification", editor Phan Cong-Vinh, Taylor & Francis/CRC Press, Florida, USA, pp.135-164, 2012.

- 4. Liang Guang, Ethiopia Nigussie, Pekka Rantala, Jouni Isoaho, Hannu Tenhunen, Hierarchical Agent Monitoring Design Approach Towards Self-Aware Parallel Systems-on-Chip. ACM Transactions on Embedded Computing Systems (TECS) 9(3), pp.25(1-24), 2010.

- Liang Guang, Ethiopia Nigussie, Jouni Isoaho, Pekka Rantala, Hannu Tenhunen, Interconnection Alternatives for Hierarchical Monitoring Communication in Parallel System-on-Chip. Microprocessors and Microsystems (Elsevier) 34(5), pp.118-128, 2010.

- 6. Liang Guang, Ethiopia Nigussie, Juha Plosila, Jouni Isoaho and Hannu Tenhunen. Coarse and Fine-Grained Monitoring and Reconfiguration

- for Energy-Efficient NoCs. Proceedings of International Symposium on System-on-Chip, October, 2012, to appear.

- Liang Guang, Ethiopia Nigussie, Juha Plosila, Jouni Isoaho, Hannu Tenhunen. HLS-DoNoC: High-Level Simulator for Dynamically Organizational NoCs, In Proceeding of IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, pp.89-94, 2012.

- Liang Guang, Syed Asad, Tony Yang, Juha Plosila and Hannu Tenhunen, Embedding Fault-Tolerance with Dual-Level Agents in Many-Core Systems, 1st Median Workshop, pp.41-44, 2012

- Liang Guang, Bo Yang, Juha Plosila, Jouni Isoaho, Hannu Tenhunen, Hierarchical Agent Monitoring Design Platform towards Self-Aware and Adaptive Embedded Systems. In: César Benavente-Peces, Joaquim Filipe (Eds.), Proceedings of International Conference on Pervasive and Embedded Computing and Communication Systems (PECCS 2011), pp.573

- 581, SciTePress, 2011.

- Liang Guang, Bo Yang, Juha Plosila, Khalid Latif, Hannu Tenhunen, Hierarchical Power Monitoring on NoC-A Case Study for Hierarchical Agent Monitoring Design Approach. In proceedings of IEEE Norchip 2010, 1-6, IEEE, 2010.

- Liang Guang, Pasi Liljeberg, Ethiopia Nigussie, Hannu Tenhunen, A Review of Dynamic Power Management Methods in NoC Under Emerging Design Considerations. In Proc. of IEEE Norchip 2009, 1-6, IEEE, 2009.

- 12. Liang Guang, Ethiopia Nigussie, Lauri Koskinen, Hannu Tenhunen, Autonomous DVFS on Supply Islands for Energy-Constrained NoC Communication. In: M. Berekovic et al. (Ed.), Proceedings of ARCS (International Conference on Architecture of Computing Systems)09 Conference, LNCS 5545, 183-194, Springer-Verlag Berlin Heidelberg, 2009.

- Liang Guang, Ethiopia Nigussie, Hannu Tenhunen, System-Level Exploration of Run-Time Clusterization for Energy-Efficient On-Chip Communication. In Proc. of 2nd international workshop on Network-on-chip architectures, 63-68, ACM, 2009.

14. Liang Guang, Pekka Rantala, Ethiopia Nigussie, Jouni Isoaho, Hannu Tenhunen, Low-Latency and Energy-Efficient Monitoring Interconnect for Hierarchical-Agent-Monitored NoCs. In Proceedings of IEEE Norchip 2008, 227 - 232, IEEE, 2008.

## List of Figures

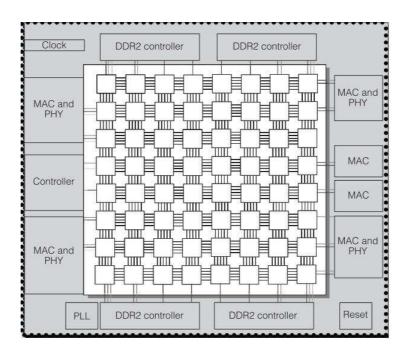

| 1.1  | An 8*8 Network-on-Chip in TILE64 processor [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

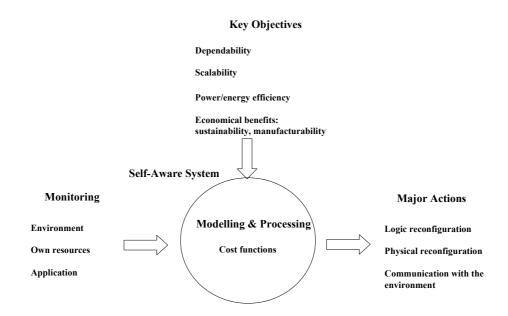

| 2.1  | Functional Overview of Self-Aware and Adaptive Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14 |

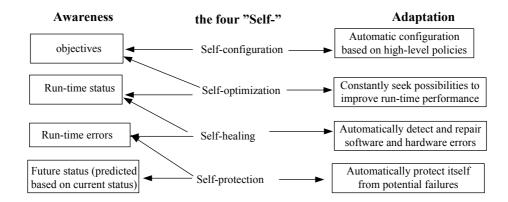

| 2.2  | Self-Aware and Adaptive Systems: A Particular Perspective on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | Autonomic Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 |

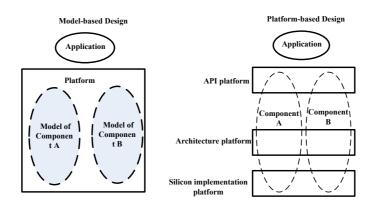

| 2.3  | Conventional Model-based Design vs. Platform-based Design $% \left( 1\right) =\left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right) \left( 1\right) \left( 1\right) +\left( 1\right) \left( 1\right)$ | 19 |

| 2.4  | SAA as a Separate Design Dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20 |

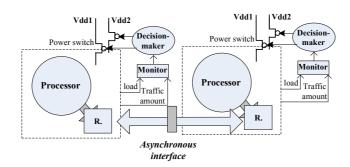

| 3.1  | Monitoring, Decision-Making and Reconfiguration Processes in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | Self-Adaptation Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23 |

| 3.2  | Illustrating Centralized and Distributed Decision-Making on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | NoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

| 3.3  | Overheads of Fine-grained Reconfiguration for Individual Volt-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

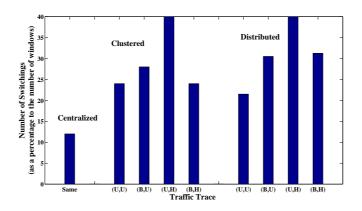

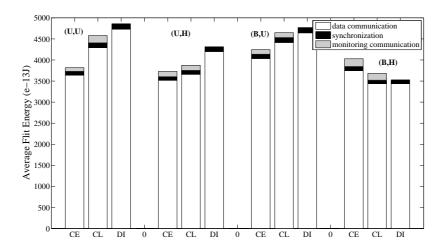

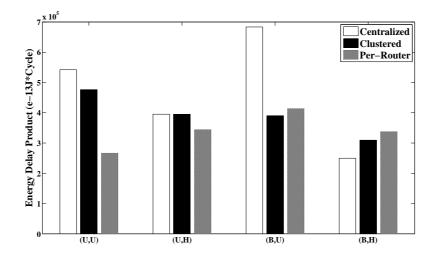

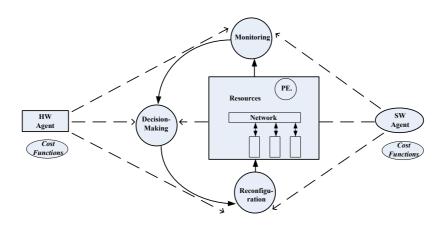

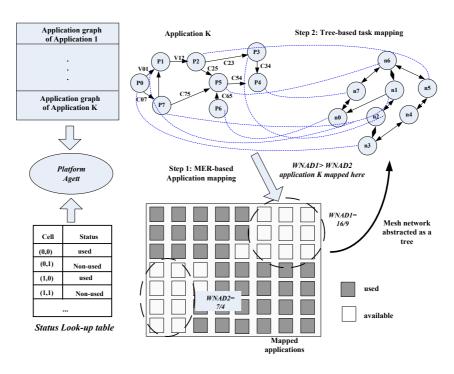

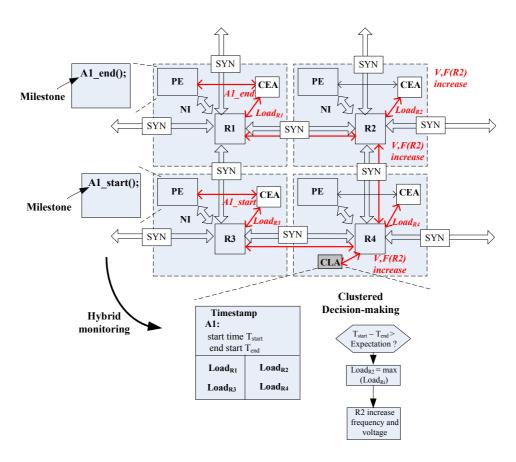

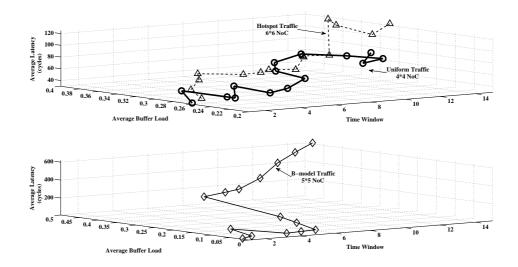

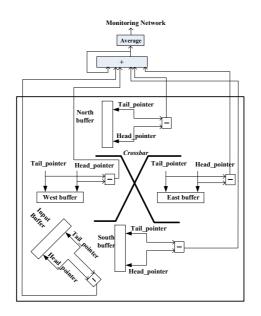

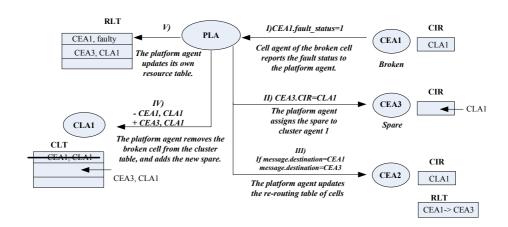

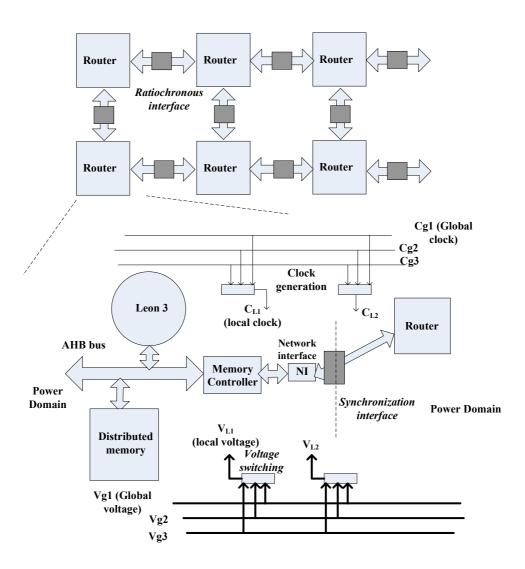

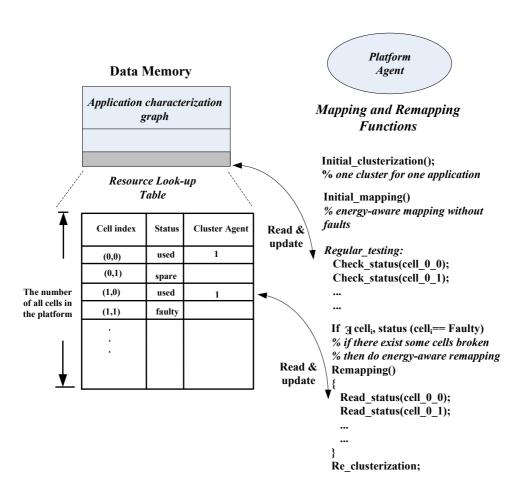

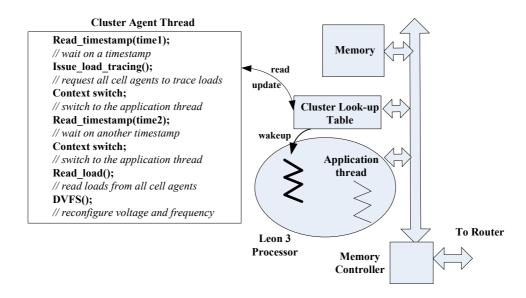

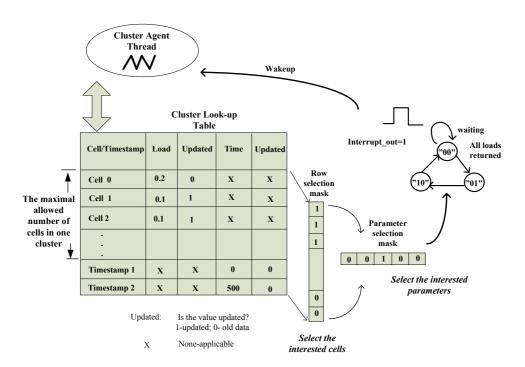

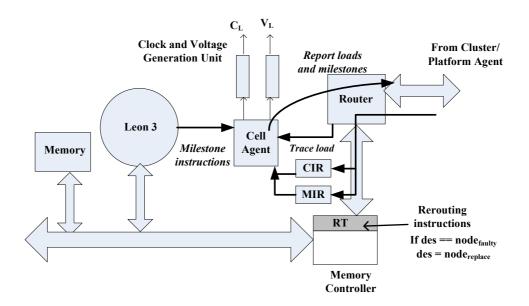

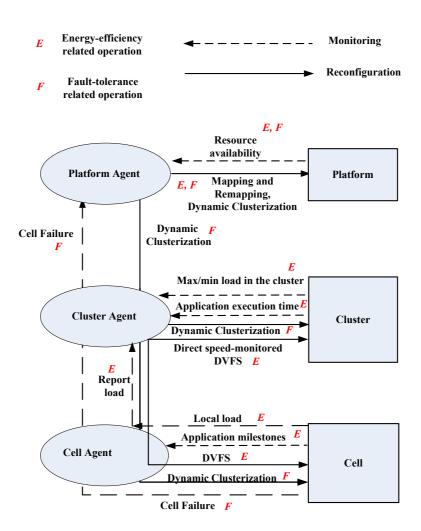

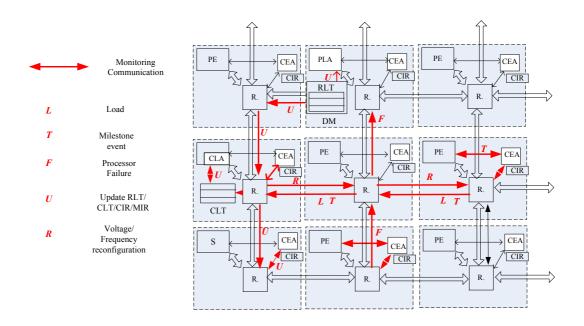

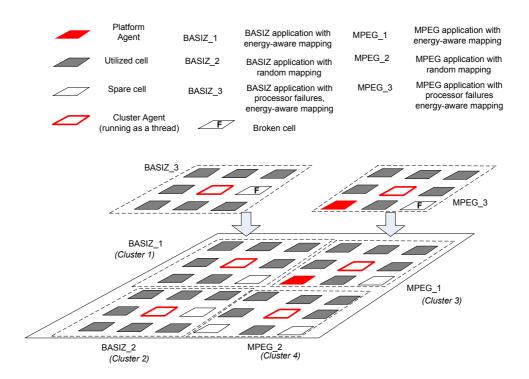

|      | age and Frequency Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 |