# Teijo Lehtonen On Fault Tolerance Methods for Networks-on-Chip Turku Centre for Computer Science

TUCS Dissertations

No 122, October 2009

# On Fault Tolerance Methods for Networks-on-Chip

# Teijo Lehtonen

To be presented, with the permission of the Faculty of Mathematics and Natural Sciences of the University of Turku, for public criticism in Auditorium Lambda on November 13, 2009, at 12 noon.

University of Turku

Department of Information Technology

20014 Turun yliopisto

2009

### Supervisors

Adjunct Professor Juha Plosila Department of Information Technology University of Turku 20014 Turun yliopisto Finland

PhD Pasi Liljeberg Department of Information Technology University of Turku 20014 Turun yliopisto Finland

### Reviewers

Adjunct Professor Elena Troubitsyna Department of Information Technologies Åbo Akademi University Joukahaisenkatu 3-5 A, 20520 Turku Finland

PhD Gert Jervan Department of Computer Engineering Tallinn University of Technology Raja 15, 12618 Tallinn Estonia

### Opponent

Professor Peeter Ellervee Department of Computer Engineering Tallinn University of Technology Raja 15, 12618 Tallinn Estonia

ISBN 978-952-12-2354-9 (PRINT) ISBN 978-952-12-2355-6 (PDF) ISSN 1239-1883

# Abstract

Technology scaling has proceeded into dimensions in which the reliability of manufactured devices is becoming endangered. The reliability decrease is a consequence of physical limitations, relative increase of variations, and decreasing noise margins, among others. A promising solution for bringing the reliability of circuits back to a desired level is the use of design methods which introduce tolerance against possible faults in an integrated circuit.

This thesis studies and presents fault tolerance methods for network-onchip (NoC) which is a design paradigm targeted for very large systems-onchip. In a NoC resources, such as processors and memories, are connected to a communication network; comparable to the Internet. Fault tolerance in such a system can be achieved at many abstraction levels.

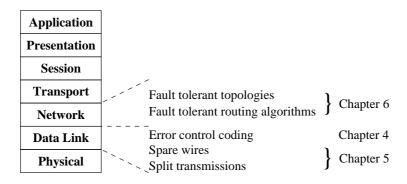

The thesis studies the origin of faults in modern technologies and explains the classification to transient, intermittent and permanent faults. A survey of fault tolerance methods is presented to demonstrate the diversity of available methods. Networks-on-chip are approached by exploring their main design choices: the selection of a topology, routing protocol, and flow control method. Fault tolerance methods for NoCs are studied at different layers of the OSI reference model.

The data link layer provides a reliable communication link over a physical channel. Error control coding is an efficient fault tolerance method especially against transient faults at this abstraction level. Error control coding methods suitable for on-chip communication are studied and their implementations presented. Error control coding loses its effectiveness in the presence of intermittent and permanent faults. Therefore, other solutions against them are presented. The introduction of spare wires and split transmissions are shown to provide good tolerance against intermittent and permanent errors and their combination to error control coding is illustrated.

At the network layer positioned above the data link layer, fault tolerance can be achieved with the design of fault tolerant network topologies and routing algorithms. Both of these approaches are presented in the thesis together with realizations in the both categories. The thesis concludes that an optimal fault tolerance solution contains carefully co-designed elements from different abstraction levels.

# Acknowledgements

This work was carried out at the Department of Information Technology, University of Turku, during years 2005-2009. I would like to express my gratitude to Turku Centre for Computer Science (TUCS) Graduate School for the financial support.

I am truly grateful for all the support that my supervisors, Juha Plosila and Pasi Liljeberg, have given to me during these years. Despite of all the other commitments you have, I cannot remember a time when you would not have time for my questions. I would also like to thank Professor Paul Ampadu for inviting me to join his EdISon research group at the University of Rochester for summer 2008. I learned a lot during those months.

Adjunct Professor Elena Troubitsyna and PhD Gert Jervan are gratefully acknowledged for reviewing this thesis.

I would like to thank all my colleagues at the IT Department and at the EdISon research group for the enthusiastic atmosphere. I have had the pleasure to share a room with many exceptional individuals. I would like to thank you all for the scientific and also the non-scientific discussions we have had. Thank you for the good co-operation to everyone who have co-authored papers with me, especially David for writing together the paper also included in this thesis. Special thanks to Jarkko for the valuable comments regarding the coding related parts of the thesis and to Sami for the numerous times I have needed assistance with my computers.

I would like to thank my parents, Sirpa and Tauno, for all the help during different phases of my studies. And finally, my warmest thanks to my wife Sari. You pushed me to start the PhD studies in the first place, followed me to Rochester during my visiting period there, and kept me sane throughout these years by forcing me to every now and then also to put the research work to the background.

This work was financially supported by the Academy of Finland, the Varsinais-Suomi Regional Fund of the Finnish Cultural Foundation, the Finnish Foundation for Technology Promotion, the Ulla Tuominen Foundation, the Emil Aaltonen Foundation, the Nokia Foundation, and the Turku University Foundation.

Turku, October 2009 Teijo Lehtonen

# List of original publications

- I Teijo Lehtonen, Pasi Liljeberg, and Juha Plosila. "Analysis of Forward Error Correction Methods for Nanoscale Networks-on-Chip", in 2nd International Conference on Nano-Networks, Nano-Net 2007, Catania, Italy, September 2007, pages 1–5.

- II Teijo Lehtonen, Pasi Liljeberg, and Juha Plosila. "Online Reconfigurable Self-Timed Links for Fault Tolerant NoC", *VLSI Design*, vol. 2007, Article ID 94676, 2007, pages 1–13.

- III Teijo Lehtonen, David Wolpert, Pasi Liljeberg, Juha Plosila, and Paul Ampadu. "Self-Adaptive System for Addressing Permanent Errors in On-Chip Interconnects", to appear in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*.

- IV Teijo Lehtonen, Pasi Liljeberg, and Juha Plosila. "Fault Tolerance Analysis of NoC Architectures", in 2007 IEEE International Symposium on Circuits and Systems, ISCAS 2007, New Orleans, LA, May 2007, pages 361–364.

- V Teijo Lehtonen, Pasi Liljeberg, and Juha Plosila. "Fault Tolerant Distributed Algorithms for Mesh Networks-on-Chip", in 9th International Symposium on Signals, Circuits and Systems, ISSCS 2009, Iasi, Romania, July 2009, pages 149–152.

- VI Teijo Lehtonen, Pasi Liljeberg, and Juha Plosila. "Analysis of Fault Tolerant Deadlock-free Routing Algorithms for Mesh NoCs", in 3rd Workshop on Diagnostic Services in Network-on-Chips, DSNOC '09, Nice, France, April 2009, pages 54–57.

# Contents

| 1 | Intr                         | Introduction 1                             |  |  |  |  |  |  |  |

|---|------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

|   | 1.1                          | Organization                               |  |  |  |  |  |  |  |

|   | 1.2                          | Contributions                              |  |  |  |  |  |  |  |

| 2 | Faults and Fault Tolerance 5 |                                            |  |  |  |  |  |  |  |

|   | 2.1                          | Fault Types                                |  |  |  |  |  |  |  |

|   |                              | 2.1.1 Permanent Faults                     |  |  |  |  |  |  |  |

|   |                              | 2.1.2 Intermittent Faults 6                |  |  |  |  |  |  |  |

|   |                              | 2.1.3 Transient Faults                     |  |  |  |  |  |  |  |

|   | 2.2                          | Fault Sources                              |  |  |  |  |  |  |  |

|   |                              | 2.2.1 Manufacturing Process                |  |  |  |  |  |  |  |

|   |                              | 2.2.2 Physical Changes During Operation 8  |  |  |  |  |  |  |  |

|   |                              | 2.2.3 Internal Noise                       |  |  |  |  |  |  |  |

|   |                              | 2.2.4 External Noise                       |  |  |  |  |  |  |  |

|   | 2.3                          | Fault Tolerance Metrics                    |  |  |  |  |  |  |  |

|   | 2.4                          | Static Fault Tolerance                     |  |  |  |  |  |  |  |

|   |                              | 2.4.1 Hardware Redundancy                  |  |  |  |  |  |  |  |

|   |                              | 2.4.2 Time Redundancy                      |  |  |  |  |  |  |  |

|   |                              | 2.4.3 Information Redundancy               |  |  |  |  |  |  |  |

|   | 2.5                          | Dynamic Fault Tolerance                    |  |  |  |  |  |  |  |

|   |                              | 2.5.1 Fault Detection                      |  |  |  |  |  |  |  |

|   |                              | 2.5.2 Fault Location                       |  |  |  |  |  |  |  |

|   |                              | 2.5.3 Fault Recovery                       |  |  |  |  |  |  |  |

| 3 | Network-on-Chip 23           |                                            |  |  |  |  |  |  |  |

|   | 3.1                          | Topology                                   |  |  |  |  |  |  |  |

|   | 3.2                          | Routing                                    |  |  |  |  |  |  |  |

|   | 3.3                          | Flow Control                               |  |  |  |  |  |  |  |

|   | 3.4                          | Fault Tolerant NoC                         |  |  |  |  |  |  |  |

| 4 | Erre                         | or Control Coding for On-chip Signaling 33 |  |  |  |  |  |  |  |

|   | 4.1                          | Linear Block Codes                         |  |  |  |  |  |  |  |

|   |                              | 4.1.1 Hamming Codes                        |  |  |  |  |  |  |  |

|   |             | 4.1.2 Cyclic Codes                                         | 36 |  |  |  |  |  |

|---|-------------|------------------------------------------------------------|----|--|--|--|--|--|

|   |             | 4.1.3 BCH Codes                                            | 36 |  |  |  |  |  |

|   |             | 4.1.4 Reed-Solomon Codes                                   | 37 |  |  |  |  |  |

|   | 4.2         | Other Coding Approaches                                    | 38 |  |  |  |  |  |

|   | 4.3         | Error Recovery Methods                                     | 38 |  |  |  |  |  |

| 5 | Pro         | tection Against Permanent Faults in On-chip Links          | 41 |  |  |  |  |  |

|   | 5.1         | Permanent Fault Detection                                  | 42 |  |  |  |  |  |

|   |             | 5.1.1 In-Line Test Method                                  | 42 |  |  |  |  |  |

|   |             | 5.1.2 Syndrome Storing-Based Detection Method              | 43 |  |  |  |  |  |

|   | 5.2         | Spare Wires                                                | 44 |  |  |  |  |  |

|   |             | 5.2.1 Reconfiguration Control and Logic                    | 46 |  |  |  |  |  |

|   |             | 5.2.2 Transmission of the Reconfiguration Information      | 47 |  |  |  |  |  |

|   | 5.3         | Split Transmissions                                        | 47 |  |  |  |  |  |

| 6 | Net         | work-level Fault Tolerance in NoCs                         | 49 |  |  |  |  |  |

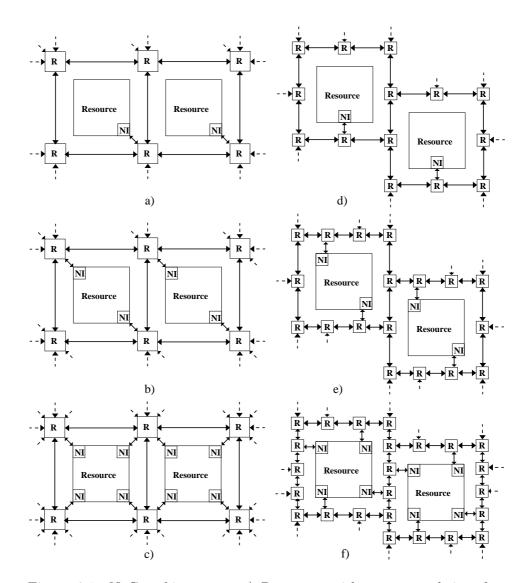

|   | 6.1         | Fault Tolerant NoC Topology                                | 49 |  |  |  |  |  |

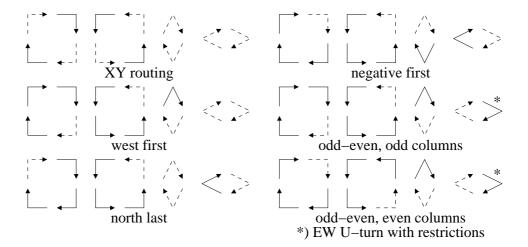

|   | 6.2         | Fault Tolerant Routing                                     | 51 |  |  |  |  |  |

| 7 | Sun         | Summary of Papers                                          |    |  |  |  |  |  |

|   | 7.1         | Paper I: Analysis of Forward Error Correction Methods for  |    |  |  |  |  |  |

|   |             | Nanoscale Networks-on-Chip                                 | 57 |  |  |  |  |  |

|   | 7.2         | Paper II: Online Reconfigurable Self-Timed Links for Fault |    |  |  |  |  |  |

|   |             | Tolerant NoC                                               | 58 |  |  |  |  |  |

|   | 7.3         | Paper III: Self-Adaptive System for Addressing Permanent   |    |  |  |  |  |  |

|   |             | Errors in On-Chip Interconnects                            | 58 |  |  |  |  |  |

|   | 7.4         | Paper IV: Fault Tolerance Analysis of NoC Architectures    | 59 |  |  |  |  |  |

|   | 7.5         | Paper V: Fault Tolerant Distributed Algorithms for Mesh    |    |  |  |  |  |  |

|   |             | Networks-on-Chip                                           | 60 |  |  |  |  |  |

|   | 7.6         | Paper VI: Analysis of Fault Tolerant Deadlock-free Routing |    |  |  |  |  |  |

|   |             | Algorithms for Mesh NoCs                                   | 60 |  |  |  |  |  |

| 8 | Conclusions |                                                            |    |  |  |  |  |  |

| Ō | Cor         | nclusions                                                  | 61 |  |  |  |  |  |

# Chapter 1

# Introduction

The ever continuing technology scaling further into the very-deep sub-micron or nanometer regime in CMOS chips results in increasing number of problems in the reliability of circuits. The shrinking geometries, smaller transistors, lower supply voltages, higher frequencies and denser integration, among others, cause faults in a chip. Although most of them can be detected at the manufacture test, larger and larger proportion of faults will not occur until at run-time. The only way to cope with run-time faults is to design the system to tolerate them. Furthermore, fault tolerance structures may provide better manufacturing yield when some faults can be allowed to exist in a chip.

Faults can be classified to permanent, intermittent and transient faults according to their duration [17]. Because there are different types of faults also the methods for tolerating them are different. In most cases, a single fault tolerance method is not an optimal solution for all types of faults. This gives rise to the idea of combining a set of fault tolerance methods which together can provide the desired fault tolerance. The different fault types are discussed further in Chapter 2 together with the typical fault sources in the modern technologies. A survey of available fault tolerance methods and classification for them is also presented.

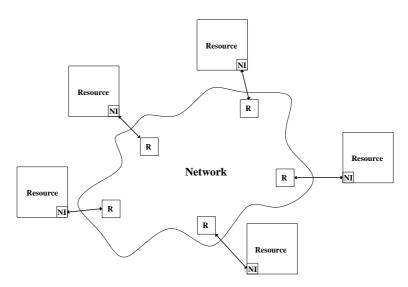

Network-on-chip (NoC) is a design paradigm targeted for large systems-on-chip (SoC). The main principle in the NoC paradigm is to replace buses with a communication network somewhat similar to the Internet. The resources, processors, co-processors, memories, etc., are connected via network interfaces to the communication network created from point-to-point links and routers. The design of networks-on-chip concerns various aspects, such as the network topologies, routing protocols, and flow control methods.

When considering fault tolerance of a NoC, the first thing to do is to separate the communication infrastructure from the resources such as processing elements, memories, etc. According to the principles of the NoC paradigm, the resources can be of a variety of types, which indicates that a variety of fault tolerance methods could be applied. Indeed, a fault tolerance method most feasible for a particular resource type should be selected. This work focuses on the fault tolerance methods for the communication infrastructure, although some methods presented in the survey of Chapter 2 can also be applied for the resources in a NoC.

The NoC communication infrastructure is commonly described as a pile of abstraction layers following the well known OSI reference model [91]. Therefore, it is logical to view also the fault tolerance methods at these layers. The fault tolerance methods presented in this thesis fall mainly to the data link and network layers, the second and third lowest layers of the OSI reference model. Above the mentioned layers are issues such as the software mapping to the underlying hardware platform, which are out of the scope of this thesis. On the other hand, below these layers is the physical layer, which consist of implementation-specific details such as the signaling method in the links and the selection between synchronous and asynchronous design style. In asynchronous design the clock signal, which schedules the system operation, is replaced with handshake signals between components. The use of an asynchronous design style makes it possible to get rid of the many clock-related problems present in many large synchronous systems. It has a positive impact on the robustness and reliability of systems.

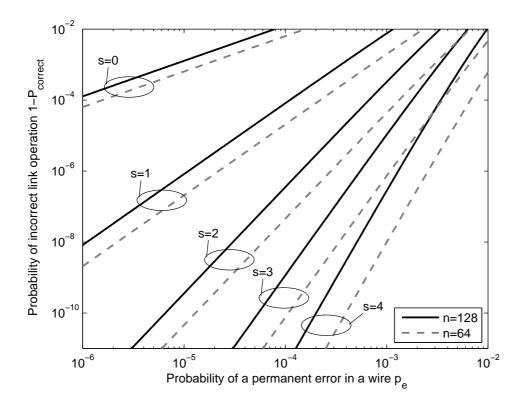

The data link layer provides reliable transfer over a physical link. The error protection of communication channels is commonly achieved by the utilization of error control coding (ECC). Only a subset of the available ECC can be used in the error protection of on-chip signaling because of the strict area, latency and power-efficiency requirements typically set to the implementations of them. ECC has its strengths in tolerating transient faults. As already stated above, most of the fault tolerance methods are not at their best against all types of faults. The same stands for ECC, its effectiveness against permanent and intermittent faults is not that good as it is against transient faults. Spare wires and split transmissions are two methods proposed for the tolerance against intermittent and permanent faults. These methods are combined with ECC to achieve a system that tolerates all types of faults.

The links also include the transmitter and receiver circuitry, which in the presence of an ECC also consist of an encoder and decoder. The reliability of these circuits should be taken into consideration as it affects the reliability of the overall link system. In the papers included in this thesis the focus has been on the link structures and fault tolerance of the transmitter and receiver circuitry has been omitted. However, the survey of fault tolerance methods presented in Chapter 2 contains methods that could be used for this purpose.

Fault tolerance methods at the network layer include the selection of and possible modifications to a network topology so that it contains redundant routes, which increases the overall reliability. The procedure includes the identification of vulnerable parts in the topology and introduction of redundant links and components into such parts. Following the principle the overall reliability of the topology is increased.

Another network layer fault tolerance method is the development of fault tolerant routing algorithms. The fault tolerance a routing algorithm provides is either originated from redundant packets travelling in the network, i.e. multiple copies of each packet is transmitted, or from the adaptive selection of redundant routes in the topology. The design of fault tolerant algorithms includes important design choices such as the property to provide always the shortest route or resiliency against deadlocks, among others.

### 1.1 Organization

The thesis is divided into two parts. The first part is an introduction to the topics related to this research field, and the second part contains reprints of six published research papers related to the topic. The introductory part gives a motivation for the work and presents related work. It also explains the research field at a wider perspective which makes it easier to understand the design choices made in the works presented in the papers included in the second part of the thesis.

The introduction chapter has given an overview of the thesis. The rest of the thesis is organized as follows. Chapter 2 classifies the faults and discusses the most common sources for them in the modern technologies. It further provides a survey of fault tolerance methods. In Chapter 3 the concept of Network-on-Chip is introduced and its main design choices are addressed. At the end of the chapter an overview of fault tolerance in a NoC is given. Chapter 4 discusses the utilization of error control coding for the error protection of on-chip signaling. This is followed by an introduction of methods against permanent faults in Chapter 5. The network-level fault tolerance methods, topology and routing algorithms, are addressed in Chapter 6. A summary of the papers included in the second part is found in Chapter 7, which is followed by concluding remarks and discussion of future work in Chapter 8. The second part containing the included papers follows after the bibliography.

Paper I contains an analysis of error control codes suitable for on-chip interconnects. In Paper II error control codes are used for tolerating transient faults while spare wires and split transmissions are introduced for tackling intermittent and permanent faults. The paper introduces a self-timed reconfigurable link system and a permanent error detection method based on

evaluating consecutive error syndromes. The reconfigurable framework is further developed in Paper III, which enables the reconfiguration to proceed without stopping the normal link operation. The paper also introduces another method for detecting permanent errors, in which rotating tests are run for each wire in the link. Furthermore, an enhanced detection method based on evaluating consecutive syndromes is introduced.

Paper IV evaluates the reliability of a NoC at the topology level. The paper introduces additional network interfaces for each resource and presents modifications to the network structure. A number of approaches are analyzed in the paper. Papers V and VI introduce distributed fault tolerant routing algorithms and a comparison of them in the classes of deadlock-free, minimal and maximal fault tolerance.

### 1.2 Contributions

The main contributions of this thesis are:

- 1. Analysis of error control codes suitable for on-chip links in Paper I.

- 2. Combination of error control coding for tolerating transient faults and spare wires and split transmissions used to tolerate intermittent and permanent faults in Paper II.

- 3. Methods for detecting permanent faults in on-chip interconnects and a reconfigurable framework to be used with spare wires and split transmission in Papers II and III.

- 4. Introduction of additional network interfaces per resource in a NoC and modifications to the network to increase the overall reliability in Paper IV.

- 5. Distributed fault tolerant routing algorithms and an analysis of them in Papers V and VI.

# Chapter 2

# Faults and Fault Tolerance

A fault is a physical defect, imperfection, or flaw that occurs within some hardware or software component. A fault may or may not cause an *error*, deviation of accuracy or correctness. A failure occurs if the system performs one of its functions incorrectly due to an error. [39]

In this chapter the fault types are classified and the most common fault sources are discussed and connected to different fault types. The fault tolerance methods are divided into static and dynamic methods addressed at the end of the chapter.

The chapter provides a thorough view to the available fault tolerance methods. From this set of methods the suitable ones for network on chip realizations can be selected as will become evident in the later chapters of this thesis.

### 2.1 Fault Types

Faults can be divided into three main groups: permanent, intermittent and transient faults according to their duration and occurrence. In the following these main groups are briefly defined. [17]

### 2.1.1 Permanent Faults

Permanent faults are irreversible physical changes in a chip. The most common source for this kind of faults is the manufacturing process, but permanent faults also occur during the operation of the circuit, especially when the circuit is old and starts to wear out. Common to all permanent faults is that once they have occurred they will not vanish, and therefore the test to detect them can be easily repeated with the same results.

Manufacture testing is used to detect the permanent faults caused by the manufacturing processes and dismiss the circuits containing such faults. If a permanent fault emerges during the operation of the chip which has no fault tolerance properties, the faulty circuit needs to be replaced. Fault tolerance methods can also provide a mean to achieve higher yield by accepting chips with some faults which are then masked by the fault tolerance properties.

### 2.1.2 Intermittent Faults

Intermittent faults are occasional fault bursts that usually repeat themselves every now and then but are not continuous as permanent faults, even though they may last for several clock cycles. The faults are caused by unstable hardware which can be operable under some environmental conditions, but an alteration in those conditions, such as temperature or voltage change, violates the operation. Intermittent faults often precede the occurrence of a permanent fault, for instance there may be an increased resistance in a wire before it totally breaks down creating an open circuit. These types of faults are commonly observed when a system operates most of the time correctly, but for some input instance it fails. The reason for this is that some path in a circuit may be slower than supposed to but not completely broken.

Intermittent faults are very hard to detect because they may occur only under certain environmental constraints or for some specific input combination. The way to repair these faults is to replace the faulty circuit or to bypass the faulty part of the circuit.

### 2.1.3 Transient Faults

Transient faults are momentary single malfunctions caused by some temporary environmental conditions which can be external phenomena such as radiation, or noise originating from the other parts of the chip. Transient faults do not make any permanent damage on the chip and therefore they are also called *soft errors*. A common impact of a transient fault is a change of value in a single bit. Another term *single-event upset* is used for a soft error, which describes the fact that malfunctions (upsets) are commonly caused by single events such as absorbed radiation.

The occurrence of transient faults is commonly random and therefore difficult to detect. Because of the random nature of these faults, a common measure for transient faults is the *soft error rate (SER)*, the probability of error occurrence. This rate describes both the tolerance of the circuit against variable phenomena causing soft errors and the amount of these in the environment where the circuit is operating. For example, the SER is much higher in space, because of the larger amount of background radiation than for the same chip operating in terrestrial conditions. The SER can be decreased e.g. by giving special concern to low-noise properties during the circuit design.

Transient faults are the most common fault type to cause system failures in nanoscale circuits; up to 80 % of all the system failures are associated with transient faults [6].

### 2.2 Fault Sources

Fault sources can be classified according to the phenomenon causing the fault. Such origins are for instance: manufacturing process, physical changes during operation, internal noise caused by other parts of the circuit and external noise originating from the chip's environment.

### 2.2.1 Manufacturing Process

Common defects in a chip are *spot defects* and *bridging faults* caused by silicon impurities, lithography variations and process deviations. These defects cause permanent faults in a circuit. The probability of these defects is likely to increase as a greater amount of transistors will be integrated in a single chip, and at the same time the devices and wires get smaller.

The move towards nanoscale circuits introduces also a set of new problems originating from the manufacturing process. As the dimensions shrink the relative extent of deviations becomes larger and their effects more severe. Lithography deviation is the main reason for gate length variations [26]. Doping profile fluctuations on the other hand cause changes in the threshold voltage [26, 84]. These together with an increasing number of resistive vias and contacts result in a large operation speed deviation [33]. At the same time the operation frequencies of the circuits are expected to increase rapidly. In the worst case scenario, series of "slow" devices may lead to timing violations and therefore to a malfunction of the circuit. This is considered an intermittent fault because the circuit might work correctly for most of the time, which would not be the case with a permanent fault.

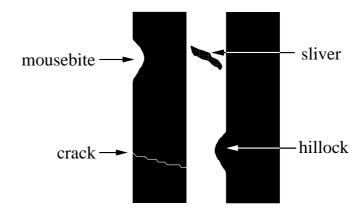

Metal slivers are small pieces of metal between two metal wires demonstrated in Figure 2.1. In normal conditions this metal piece does not touch the wires but when the temperature increases it could create a short between wires due to the metal expansion. This is a typical intermittent fault but a high voltage may also cause the sliver to burn in and hence, lead to a permanent fault. [33]

The opposite of slivers are *cracks* in metal wires illustrated as well in Figure 2.1. They cause open circuits at low temperatures but do not alter the wire functionality at all or occur as an increased resistance at normal temperatures. Cracks are another example of intermittent fault sources.

Figure 2.1: Manufacturing faults in wires.

### 2.2.2 Physical Changes During Operation

Electromigration means current-induced atom-level transport which is generated by collisions of electrons with metal atoms [65]. This phenomenon is especially critical if there are mousebites or hillocks in the metal wires, both of which are illustrated in Figure 2.1 [5]. In the place of a mousebite the wire is narrower, which means that the current density is higher and so the electromigration effect is stronger. Additionally, the wire is already narrower in that place so the impact of electromigration causes rapidly increasing resistivity and finally an open. In the place of a hillock material is accumulated and electromigration moves more material to such a place because now the current density is lower than in other parts of the wire. This can eventually result in a short to another wire. The electromigration impact is observed often first as an intermittent error, and later as a permanent error if an open or short circuit is formed.

Electromigration is becoming a more and more severe problem as the dimensions of wires and insulators between wires decrease at the same time as their relative deviations increase. Also the increasing operation temperature strengthens the effect of electromigration. One improvement that has reduced the electromigration problems has been the replacement of aluminium with copper in wires due to copper's higher electromigration threshold than that of aluminium [84].

The ever thinner gate oxides are prone to current tunneling resulting in a breakdown which means a permanent fault. On the other hand, a *soft breakdown (SBD)* in ultrathin gate oxides slows down transistors causing intermittent faults in the same way as other device deviations [33]. The soft breakdown differs from the traditional *hard breakdown* in that it causes current fluctuations while the hard breakdown brings about shorts and thus a measurable current. The SBD effects can be regarded as tiny breakdowns

that only partially violate the operation of the transistor. The SBD is also a typical source for an increased power consumption.

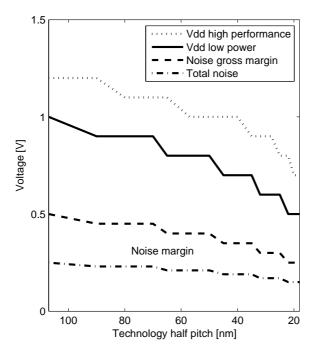

### 2.2.3 Internal Noise

When technology is scaled down also the supply voltages are lowered. In addition to the lower power consumption the benefit of the voltage scaling is the better durability of the components and wires. High voltages expose thin gate oxides for breakdown and high current densities in narrow wires accelerate electromigration. The drawback is a degraded noise tolerance, which is illustrated in Figure 2.2. The impact is further amplified by the large variation of the threshold voltage, which means that for some circuits or some parts of the circuit the noise margin is negligible. At the same time the amount of noise is increasing as the relative fluctuations in the manufacturing processes get larger.

The impact of crosstalk noise between signal lines is increasing because the height and width of the wires are not scaled by the same factor. The width of the smallest wires scales with the same factor as the length of the gate, but the technology scaling factor for the height of the wires is smaller

Figure 2.2: The noise margin decreases as the technology is scaled down [38]. The gross noise margin is calculated from the low power  $V_{dd}$  and the total noise with independent noise of 50 mV and relative noise of 0.2 [19].

in order to keep the resistance of the wires tolerable. This increases the capacitive area between adjacent wires. At the same time, the wire spacing and also the distance of adjacent layers get smaller, which additionally increases the capacitive coupling.

The higher frequency in nanoscale circuits gives rise also to inductance based noise called the *skin effect* [19]. When the current changes rapidly it flows near the wire surface, which means an increase in the resistance. Since the current flow proximity to surface depends on the frequency of current changes, also the wire resistance will vary with the frequency.

The timing uncertainty is another type of noise source. As the relative deviations of components and wires increase it will be impossible to get a signal to two or more distinct nodes in the circuit exactly at the same moment. The resistive vias and contacts worsen the situation even further. The increasing skew and jitter is a problem not only in synchronous systems but also in asynchronous designs that use delay elements, because the delay value cannot be set exactly. [19]

The impact of noise can usually be modeled as a transient or sometimes as an intermittent fault.

### 2.2.4 External Noise

Radiation has not been regarded as a severe noise source unless the circuit is to be used in space, aeroplanes, nuclear plant or similar places where the background radiation is higher than usual terrestrial amounts. As technology scales down the radiation should be taken into consideration also in other circuits, because the shrinking dimensions increase the probability that an  $\alpha$ -particle, proton or neutron hitting the chip also causes a change in a bit value. The occurrence of an upset is more likely since a lower supply voltage together with smaller transistors mean that the charge the particle introduces is sufficient to flip a bit. The charge needed to flip a bit and cause a particle-induced transient is called the *critical charge* and it is dependent on the charge a transistor can hold. For instance for a 90 nm CMOS technology the charge a transistor holds is 1–10 fC, which is less than one tenth of the charge of over 100 fC delivered by an  $\alpha$ -particle hitting the circuit [40].

Other external noise sources are electromagnetic interference and electrostatic discharge. A common source for the former are other devices especially those emitting high energy signals, and for the latter the users releasing static charge accumulated in their clothing. The faults are normally transient but in principle also permanent faults may result especially from an electrostatic discharge [17].

### 2.3 Fault Tolerance Metrics

Fault tolerance of a system can be described in many metrics. The most common of these is the reliability R(t) which has been defined as the probability that a system operates correctly under given set of operating conditions over a given period of time  $[t_0, t]$ , given that the system was performing correctly at time  $t_0$ . Other metrics include the availability A(t) which is the probability that a system can perform its task correctly at the instant of time t, and safety S(t) which is the probability that a system performs its task correctly or discontinues its operation in a safe manner. Safety is defined over a period of time  $[t_0, t]$  corresponding with the definition of reliability. Dependability is used to indicate all of these properties. [39, 81]

The occurrence of failures can be described with the failure rate  $\lambda$ , which is the expected number of failures per a given time period. Its reciprocal is the mean time to failure (MTTF), MTTF =  $\frac{1}{\lambda}$ . The relation of the reliability and failure rate is  $R(t) = e^{-\lambda t}$  for a constant  $\lambda$ . [39]

### 2.4 Static Fault Tolerance

A circuit is said to be utilizing static fault tolerance when it is built in such a way that a fault somewhere in the circuit will not violate the correct operation of the circuit. The word static stands for the fact that fault tolerance is built into the system structure and it effectively masks the fault effects. The method to create such fault masking properties is to use some kind of redundancy. Static fault tolerance can be categorized to hardware, information and time redundandy according to the resource that is used to create the redundancy. Also a combination of these can be used.

### 2.4.1 Hardware Redundancy

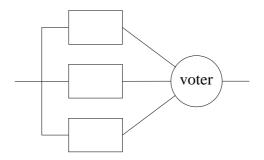

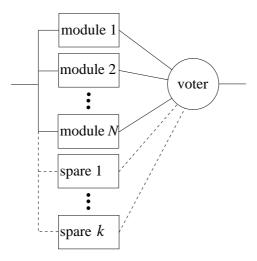

Hardware redundancy generally means making copies of the processing module and providing a voting circuit to decide the correct output value based on the outputs of the module and its copies. A higher reliability is gained because when a component fails, the voter can decide the correct output based on the results of the working copies. The method can be used at many different abstraction levels, the modules can be as simple as single gates but also as complex as whole processors or even larger constructs. The voter can be a simple bitwise hardware implementation or a software algorithm running on a processor. This versatility makes the method a good candidate for large systems such as networks-on-chip, where solutions for multiple abstraction levels is required. Common to all hardware redundancy realizations is the need for additional area. Therefore the methodology is also called physical, area or space redundancy.

Figure 2.3: Triple modular redundancy.

The most common hardware redundancy realization is triple modular redundancy (TMR) which consists of three redundant modules and a voting circuit as illustrated in Figure 2.3. The voter normally performs majority voting, which means that the output is the same as the output of twoout-of-three of the modules. TMR is capable of masking a single error in the processing modules. The weak point of the circuit is the voting circuitry itself where an error can cause the whole system to fail. This has been tackled by making also three copies of the voter and connecting the module outputs to each of the three voters [39]. Other possibility is to modify the voting circuitry in such a way that possible errors can be detected. Approaches include e.g. a voter that is on-line self-testing for internal faults [14, 58] and a voter that can be checked based on the quiescent current  $(I_{DDQ})$  [13]. Another important issue to consider is the mismatch and crosstalk in lines from module outputs to voter inputs, which can cause severe malfunctions [25]. For this reason synchronization between the voter inputs may be required. The simplest method for realizing synchronization is to insert registers to voter inputs [39].

A more generalized hardware redundancy realization is n-modular redundancy (NMR), which means that there are n copies of a module and a voter. This structure is capable of masking  $\lfloor (n-1)/2 \rfloor$  errors in different processing modules. The most common structures besides TMR are 5- and 7-modular redundancies capable of masking 2 and 3 errors, respectively.

The voting algorithms can be divided according to their functionality to generic and hybrid voting algorithms and to purpose-built voters. Generic voters use only the information of input signals to produce the output while hybrid voters have also some additional information such as the reliability of different modules or history of previous votes. The purpose-built voters are e.g. special microprocessor systems designed for space shuttles [48].

**Generic voters** produce the output according to the present output values of the modules. The most common algorithm is the *exact majority*

voting, which means that when the majority of the module outputs have the same value, this value is forwarded to the output. This is easily achieved in bitwise voting because the only possible values are logic '0' and '1'. If the module outputs are not just one bit wide but for instance integers, then it is possible that there is no majority agreement. In this case the voter can have an output "no result", which is an exception signal. The values of different modules can be slightly different because of noise or e.g. sensor elements cannot be physically at the exactly same place. Therefore *inexact* majority voting has been introduced, where the output is decided if the majority of the module outputs lie inside a certain threshold. A "no result" is output only if majority of the outputs are more than a threshold apart from each other. The threshold effect can be easily achieved by dropping a couple of least significant bits from the voting procedure [39]. In plurality voting the majority of the module outputs do not necessarily have the same value (exact) or values in threshold limits (inexact), only the number of the same value or values within a threshold is larger than the number of modules having some other value. For instance, if there are five modules, it is enough that two of them have the same value if each of the other three has a different value. In inexact voting the selection of the output value can be a random selection of one of the majority or plurality output values or it can be mid-value selection, where the output is calculated as the mid-value of the majority or plurality outputs. [41, 80]

Another voting scheme is *median voting*, where the median of all the module outputs is selected as the voter output. An efficient software realization is to sort the output values and then select [(n+1)/2]th value as the output, where n is the (odd) number of redundant modules. [45]

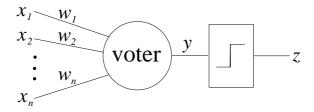

In weighted average voting a weight is given to each module output and the output is calculated as the average of the module outputs scaled by these weights. The output is scaled down by the sum of the weights in order to produce an output that is at the same scale as the inputs. In bitwise voting the output is returned to one of the logic states according to a threshold value which is adjusted to some level between the logic states.

Figure 2.4: Weighted average voting with threshold:  $y = \sum_{i=1}^{n} w_i x_i / \sum_{i=1}^{n} w_i$ , z = 1 if  $y \geq T$  and z = 0 if y < T, where T is the set threshold.

The operation is demonstrated in Figure 2.4. The weights are calculated based on the distance of the output value to the other output values. If a module's output value is far away from all the other output values, it is given a smaller weight than a module whose output is close to many other module's output values. Advanced methods to calculate these values have also been presented. These include e.g. a voter that uses the concept of the soft threshold for determining the closeness of all voter input pairs and a tunable roll-off parameter which gives the possibility to adjust the voter behaviour from a majority voter to an average voter [51], and a fuzzy voter using fuzzy set theory to adjust the weights [50]. Circuit realizations of voters include e.g. weighted bit-wise voters with a threshold [15, 64] and an analog weighted average voter [74] together with a threshold circuit using capacitive threshold logic [73].

The adjustment of the threshold is an essential task for the operation of the circuit. Threshold can be static or dynamic. A static threshold can be based on circuit realization or set after the manufacturing. Dynamic threshold, in contrast, adapts to the changes in the operation environment. For instance, the use of an artificial neural network learning algorithm in adjusting the thresholds has been suggested [72].

The selection of a voting method for a particular application depends on the required properties. In some applications even a single incorrect data bit may violate the operation of the whole system whereas for some other application few corrupted data bits make no harm. For the former ones high safety is demanded, which means that it is better to indicate even the small possibility of an incorrect result even though it may decrease the total number of correct answers. For the latter case the number of correct outputs is maximized without paying any concern to the potentially incorrect results.

Majority voting is a rather safe voting scheme because it is more likely to output a "no result" than a faulty result. The weighted average voting on the contrary gives more correct results but also the amount of incorrect results increases, thus the safety is not that good [49]. Above mentioned is true when module outputs are wider than just one bit. However, for bitwise voting the safety of a majority voter is poor because in the case of multiple errors the output is likely to be incorrect instead of "no result". The weighted average voting for bitwise voters is shown to result in a higher number of correct results in the presence of multiple defects [75].

Hybrid voters combine the information on present module outputs and some other information regarding the module circuits or output sequence. An example of the use of history data together with the information on present outputs is weighted average voting, where the weights are based on history records [47]. The voting procedure can be also totally based on the history, e.g. by choosing for the output of the voter the output of the module

that has been the best in the history. The best module is the one that has had output closer than a threshold to majority of the module outputs for the most times [46]. The use of history values can be also a backup system if no agreement can be found among the module outputs [46]. In addition to using the history data to detect the most reliable modules, it can also be used to predict the next output value. Many system outputs are somehow dependent on the previous outputs, which gives the justification for this procedure. One of the simplest ways to predict the value in the case of a module output disagreement, is to check if any of them is closer than a threshold to the previous voter output. If such an output is found, the one closest to the previous value is selected [49].

### 2.4.2 Time Redundancy

The principle in time redundancy is to use the same resource many times and compare the results obtained from different rounds of computation. The method saves area since no copies of the processing module are required. The drawback is the longer processing time because of the recalculations, which on the other hand may be acceptable for certain types of applications. The method of repeating the same calculation many times is effective in detecting transient errors but permanent and in many cases also intermittent errors occur at the same place during all calculations and cannot therefore be detected and corrected. This problem can be overcome by encoding the operands before processing and decoding afterwards. Commonly the operation is first performed with the original operand and after that with the coded ones.

In alternating logic method complementation is the used coding method. In order to be able to use this coding, the self-duality of the circuit is required or possibly an additional input is needed. Recomputing with shifted operands (RESO) means shifting the operands before calculation to left and back to right after calculation. This method makes arithmetic operations wider. Alternatively, cyclic shift can be used which in turn means complex logic for carry signals in adder circuits. One more coding approach is recomputing with swapped operands (RESWO), where upper and lower parts of the operands are swapped before and after the calculation. The method needs no additional bits, and the logic for handling carry bits in adder circuits is more straightforward than in RESO. [39]

The error correcting properties are obtained by repeating the operation at least three times and performing voting for the three results. Different coding is used at different calculation rounds, e.g. no coding, shift 1 and shift 2. Bitwise majority voting can be problematic because the arithmetic operations commonly affect many bits. The different voting approaches were already discussed in the previous section. [39]

### 2.4.3 Information Redundancy

Information redundancy in general means appending additional bits to stored or transmitted data. Error control codes (ECC) can be used to detect and/or correct errors in a codeword, the data word into which check bits have been appended. The application of an ECC to extract the exact location of the error in order to correct it is called forward error correction (FEC), to distinguish it from approaches where a code is used only for detection of an error in a codeword. The codes can be classified to separable and non-separable codes according to how the additional information is appended. If the data is left unchanged and check bits are appended for the correction, the code is separable. A non-separable code needs a decoding circuit to return the data to its normal form before further processing. Separable codes are also called systematic codes and non-separable non-systematic, respectively.

A simple separable ECC is the *parity code*, which means appending one bit to every word. The value of this appended bit is adjusted to make the number of bits with value '1' odd (odd-parity code) or even (even-parity code). The parity code itself can be used only for detecting single errors in a codeword, but when a parity is calculated separately for both rows and columns for instance in a memory block, the exact location of a single error can be extracted. [39, 44]

Error control codes are an important tool in designing fault tolerant signaling also in on-chip communication as well as for other communication. This usage of ECC will be discussed in detail in Chapter 4 and therefore it is omitted here.

The redundant residue number system (RRNS) is used for error correction in arithmetic operations such as addition, subtraction and multiplication. In residue number system each number is presented as the residues for a set of relatively prime moduli. For instance, if the moduli set is  $\{3,5\}$  then a  $9_{10}$  is presented as  $04_{RNS}$  because  $9 \equiv 0 \pmod{3}$  and  $9 \equiv 4 \pmod{5}$ . The set  $\{3,5\}$  can be used to present numbers  $0_{10} - 14_{10}$ , which is determined by multiplying the moduli of the set  $(3 \cdot 5 = 15)$ . The operations are performed bitwise as mod  $m_i$ , where  $m_i$  is the moduli used to create the numbers at this bit location. When additional moduli are inserted to the set, a redundant residue number system is obtained, which can be used to detect and correct errors. If r redundant moduli are added, the system can correct up to  $\lfloor r/2 \rfloor$  errors. The use of RRNS has been proposed to be used e.g. in digital filters and in software-defined radio. [24, 35, 39]

### 2.5 Dynamic Fault Tolerance

Dynamic fault tolerance is based on active operations as opposite to the passive nature of static fault tolerance. It can be divided into four phases

the first of which is *fault detection*. After the detection of an erroneous behaviour the next thing to do is to *locate the fault*. The third phase is *fault containment* which means isolating the error source so that no new errors can occur. The final phase is *fault recovery* meaning usually reconfiguration of the system so that the erroneous part has been disabled. [39]

Dynamic fault tolerance typically requires special control circuitry and elements. Unfortunately, the design of these control parts is not always straightforward. The benefit of dynamic fault tolerance is better reliability especially in the occurrence of permanent and multiple errors, and quite often the reliability increase is obtained with a smaller area overhead than in the corresponding static fault tolerance approach. Many network-on-chip implementations contain means for controlling traffic flows and processing resources. The control required for dynamic fault tolerance could be integrated with such systems, which makes dynamic fault tolerance a promising method for networks-on-chip.

### 2.5.1 Fault Detection

The fault detection is an essential part of dynamic fault tolerance. If the fault is not detected the circuit can produce erroneous outputs and it can falsely be considered fault-free. The fault detection can be organized as periodic tests, self-checking circuits or watchdog timers [44].

The principle of the periodic tests is to stop the circuit operation every now and then and perform a self-test. The method cannot guarantee that every fault is detected because the test is run only occasionally. Furthermore, the time needed for testing is a drawback of this method.

Watchdog timers are used especially in multi-processor environments. A control circuit sets a timer when a processor starts to execute a certain task. At some predefined point of the procedure the processor resets the timer. If for some reason the processor halts during the operation, the control circuit detects it by observing the timer value exceeding some limit. To recover from this situation the control circuit can for instance reset the halted processor or start a reconfiguration process. [39]

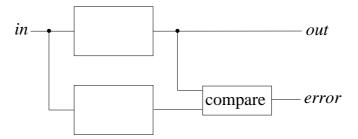

There are numerous ways to create self-checking circuits. The most straightforward method is duplication with comparison, which means creating two identical modules and comparing their outputs as illustrated in Figure 2.5. Sometimes there can be small deviations between the two components although they are operating correctly. In these cases the comparison process can ignore least significant bits. The method can also be extended to tolerate common mode failures which are failures that affect both the modules in the same way. One such an enhancement is to replace the duplicate module with a module that calculates the complement function of the original module's function. The circuit works correctly when the output of the

original module and the output of the module calculating the complement function are complements of each other. [39]

Duplication can be done also in time domain. The information is sent twice and the results are compared. In order to gain better detection abilities, the data can be complemented or swapped at the second iteration and an inverse transformation is performed at the output. [39]

A number of error control codes can be used to detect errors in data. Possibly the most common error detecting code is the parity code which is extensively used e.g. in memory circuits. The code can detect single errors, but in the presence of multiple errors the parity bit may have a correct value, and therefore the error is not detected. More sophisticated error control codes are presented in Chapter 4, where coding for on-chip signaling is addressed in more detail.

Errors are commonly expected to occur randomly, independently of each other. This is not a realistic model for all cases. In some situations errors only in one direction can occur, meaning that '0' can turn to '1' but '1' cannot flip to '0' or vice versa. Errors occurring only in one direction are called *unidirectional* and errors that can occur in both directions are *bidirectional*. Errors can also occur as bursts which are common for instance in communication signaling, where burst errors originate from disturbances in the signaling medium. Intermittent faults in the signaling medium typically cause error bursts.

M-out-of-n codes are able to detect not only single errors but also multiple unidirectional errors. The basic principle of the code is that every codeword has m ones and n-m zeros while the length of a codeword is n. The code is not separable except in some special cases. Such a special case is k-out-of-2k code where there are two bits per one data bit. The code is called k-pair two-rail code, when the check bits are bitwise complements of the information bits [39, 44]. An example of the use of m-out-of-n codes is an online error detecting adder, where 1-out-of-3 code has been used [82].

The *Berger code* requires the fewest number of checkbits of the available separable codes for detecting arbitrary number of unidirectional errors. The

Figure 2.5: Duplication with comparison.

code is based on counting the number of '1's in the word and appending a complement of the count to the word. The number of checkbits is  $\lceil \log_2(k+1) \rceil$ , where k is the number of information bits [39, 44]. If it is not necessary to detect all the possible unidirectional errors, but only maximum t of them, then the amount of checkbits can be further decreased. Such codes are e.g. the modified Berger code, Borden code and Bose-Lin codes [44]. A set of codes for detecting unidirectional errors and error bursts of length t, the unidirectional burst error detecting codes, includes e.g. codes by Berger, Bose, and Blaum [44].

One way to detect an error occurred during signal transmission is to calculate a *checksum* of the data words and transmit it together with the data words. At the receiving end the checksum is recalculated and compared with the received one. Examples of checksums are *single- and double precision checksums* as well as *Honeywell* and *residue checksums*. The length of the single-precision and residue checksum is the same as the width of the data words, while the other two have the length of double the width of the data words. The mentioned checksums are calculated by summing up all the data words. They differ in the way the data words are organized and carry bits handled in the addition process [39].

Arithmetic codes are used to detect errors in arithmetic operations. One example of such a code is the AN code which can be used for addition and subtraction. Every operand is multiplied by A before the operation and the result should be evenly dividable by A, otherwise an error has occured. A commonly used AN code is the 3N code. Other arithmetic codes include residue and inverse-residue codes. In these codes, the operands are divided by integer m (e.g. by 3 for mod-3 residue), and the remainder is appended to the data, thus the code is separable. The arithmetic operation for the appended remainder is computed modulo m and the result is checked against the remainder of the operation result divided by m. The procedure is eligible for addition, multiplication and logical units [44]. Residue number systems, described in Section 2.4.3 along with their error correcting capabilities, can also be used for error detection. [39]

Checkers are circuits that are used to determine if an error has occured or not. A checker commonly compares two values and signals an error if they differ or are equal, depending on the used method. The robust design of checkers is very important because an error in the checker circuit may invalidate the fault tolerance of the whole system.

In the design of checker circuits the concepts of fault-secure and self-testing design are commonly used. The circuit is fault-secure if every valid input produces either a correct output or an output which can be easily observed to be incorrect. This kind of incorrect outputs are called non-code outputs, which indicates that they do not fulfill the requirements set

for the codewords. A self-testing circuit, in turn, is such where for every fault in some set of faults there is an input combination which produces a non-code output so that the fault can be observed. The circuit that is both fault-secure and self-testing is called *totally self-checking*. [44]

The fault-security in a circuit can be achieved by designing the circuit in a way that there is separate logic for separate outputs. This ensures that a single error affects only one output signal. The self-testability is achieved by non-redundant design.

A common checker is a two-rail checker, which has four inputs and two outputs. The inputs consist of two input pairs, both of which consist of two complementary signals. The circuit checks that the signals of an input pair are indeed complementary. The output signals are complementary when there are no errors, and in the presence of an error in the input or in the checker circuit the output signals are the same. A checker for a larger number of input pairs can be constructed by forming a tree connection from the two-rail checkers. Totally self-checking two-rail checkers have been presented, and a combination of these checkers forming a larger checker is also totally self-checking. [44]

### 2.5.2 Fault Location

After the detection of a fault situation the fault source has to be located, if it is not already known based on fault detection information. One way to accomplish this is to start a specific self-diagnostic procedure after the fault detection [39]. The self-diagnostics may consume too much time to be used in some time-critical applications, but for most applications the additional time is tolerable since it is needed reasonably seldom, i.e. only during a fault occurrence. Another way to locate a fault is to use two different detection methods. For example, if both duplication with comparison and parity check are used, the faulty module can be easily located. [3]

### 2.5.3 Fault Recovery

There are two common ways to accomplish fault recovery. The transmission or calculation repetition,  $automatic\ repeat\ query\ (ARQ)$ , needs additional time while the use of  $spare\ modules$  and reconfiguration causes area overhead.

ARQ is suitable for recovering from transient and in some cases also from intermittent errors. However, it cannot be used against permanent errors since the system will not work regardless of how many times the operation is repeated. Different approaches to ARQ are introduced at the end of Chapter 4.

The use of spare modules and reconfiguration is especially suitable for recovering from permanent and intermittent errors. On the other hand, it is not very efficient to discard a whole module and replace it with a spare one if the error is only temporary. Therefore a combination of ARQ and reconfiguration might give the best result. The operation is first repeated and if the error remains, the reconfiguration process is commenced. [44]

The spare modules can be divided into hot and cold spares, depending on whether the spare modules are immediately ready for use (hot) or do they need to be initialized before usage (cold). Cold spares are also called standby spares and the use of hot spares is referred to as reconfigurable duplication. The standby spare system leads to higher reliability but the reconfigurable duplication provides higher safety. [39, 44]

Spares have also been combined with N-modular redundancy (NMR). In these systems N modules are part of the voting procedure and in addition to them, there are spare modules as illustrated in Figure 2.6. After voting the output is compared to the output of each individual module and in the case of a disagreement, the module is replaced with a spare. The combination leads to a higher reliability than the normal NMR system. [39, 44]

A self-purging system is an NMR system which in the presence of a module failure reconfigures itself and the result is an (N-1)MR system. The isolation of modules is done similarly as in NMR with spares or it can be based on evaluation of the distances between different module output values. The method is also called *shift-out modular redundancy*. In conjunction with self-purging systems the use of weighted average voting with a dynamically adjustable threshold has been suggested. [15, 39, 64]

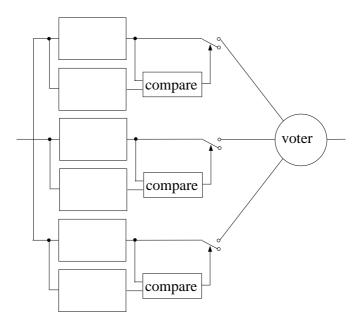

Yet another combination of dynamic redundancy and static NMR is the *triple-duplex architecture* presented in Figure 2.7. In this combination every module is duplicated and in the case of a disagreement the module is isolated

Figure 2.6: N-modular redundancy with k spares.

from the voting unit. One system therefore consists of six modules and a voter unit. [39]

The insertion of spare modules to a system causes easily a large area overhead, because for every kind of module a special spare has to be implemented. If the modules are similar, but not identical, heterogeneous redundancy can be used. Redundant blocks that can be programmed like field-programmable gate arrays (FPGA) to execute many different functions are inserted to a circuit. One such reconfigurable module can be used to replace different types of modules and therefore the overall number of spare modules can be decreased. The disadvantage is that these programmable modules are generally slower than fixed-logic blocks and also the reconfiguration takes more time. [43]

Another way for relaxing the need for additional area, is to take advantage of redundant structures inherently present in a system. For instance, there are parallel structures in many radio structures, where a single redundant module can act as a spare module for many modules in use [52].

Figure 2.7: Triple-duplex architecture.

# Chapter 3

# Network-on-Chip

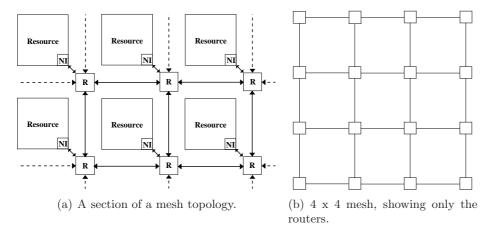

Network-on-Chip (NoC) is a communication infrastructure paradigm targeted to large on-chip systems consisting of tens or hundreds of resources such as processor cores, memories, etc. The idea in NoC is to replace buses with a communication network consisting of routers or switches and point-to-point links connecting the resources to routers as well as the routers to each other to form a network. The generic structure of a NoC is illustrated in Figure 3.1. NoC realizations borrow ideas from both circuit switching networks such as the landline phones as well as packet switching networks, the most known example of which is the Internet. Packet switching provides flexibility while circuit switching comes with a more predictable performance. Network interfaces (NI) connected between each resource and

Figure 3.1: In a NoC resources are connected via network interfaces (NI) to routers (R). Routers are connected to each other to form a network.

the network are used to create and unpack packets or establish a connection between the source and destination resources. In packet switching network each packet contains information needed for routing of the packet to the correct destination.

The motivation for the NoC approach is the poor scalability of buses for systems consisting of a large number of resources. The longer the bus is the higher capacitive load it introduces to the drivers connected to it, and therefore results in a longer latency and higher power consumption. The same effect results from the increasing number of devices connected to the bus emphasized by the effect on the scheduling of the bus: the more resources connected to the bus, the less time is left for each of them to use the bus. Furthermore, the arbitration becomes more complex and time-consuming as the number of devices connected to a bus increases. NoC provides better scalability because as more resources are introduced to a system, also more routers and links are introduced to connect them to the network. The additional links and routers provide the communication capacity needed for the new resources. Many NoC realizations also inherently contain some redundancy in the communication media, which can be used to provide a higher reliability and traffic balancing. This is in contrast to bus structures, which rely on a single communication medium.

The NoC paradigm was first introduced at the beginning of this millennium by multiple independent research groups [6, 20, 31, 34, 76]. After that a lot of design efforts have been put to the topic, examples include Ætheral [28], MANGO [9], Nostrum [42], SPIN [1], and Xpipes [7]. Some approaches are already in commercial use, such as Arteris<sup>TM</sup> [4] and STNoC<sup>TM</sup> [79].

The main design choices in NoC are the way the routers are connected to each other, the *network topology*, the principles how the packets are routed from a source to a destination, the *routing protocol*, and the allocation of network resources to packets travelling in the network, the *flow control*. These are discussed in the following subsections. The network components, the routers, network interfaces and links, implement the topology, routing protocol, and flow control.

### 3.1 Topology

The network topology defines the way the routers are connected to each other to form a network. Most of the proposed topologies for NoC are borrowed from the world of inter-processor networks in supercomputers and computer networks.

Probably the most often proposed topology for NoC is the *mesh* presented in Figure 3.2. Resources are organized into a two-dimensional array and each resource is connected to one router assigned to it. Each router is

Figure 3.2: Mesh network topology.

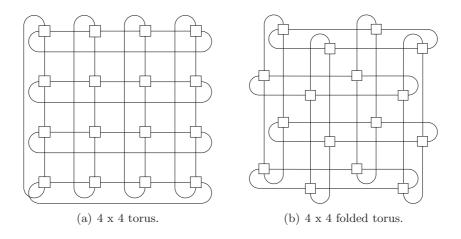

Figure 3.3: Torus and folded torus network topologies.

connected to its neighbors in four directions, typically named East, South, West and North, excluding the ones at the edges of the structure having only 2–3 neighbors. The topology is highly symmetric which makes the addressing and routing straightforward. Furthermore, the inherently horizontal and vertical links organized in an array shape between the resources simplify the creation of the chip layout.

The torus topology, presented in Figure 3.3(a), fixes one of the drawbacks of the mesh topology, namely the long distance between opposite edges. In a torus the routers at the edges are directly connected to the routers at the opposite edge of the system, thus decreasing the hop count on a route. The drawback of this approach is the uneven length of links, the edge-to-edge connections are longer than the links inside the mesh. To overcome this, a

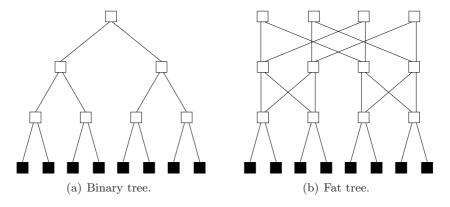

Figure 3.4: Binary and fat tree network topologies (the black squares represent resources).

structure called *folded torus* has been presented [21]. In a folded torus all the links are of the same length, illustrated in Figure 3.3(b).

Besides the mesh, most commonly used NoC topologies are variations from the *tree* topology, where the resources are the leaves and the routers form the nodes of the tree. Figure 3.4 presents two tree structures, the *binary tree* and *fat tree*. In the binary tree topology each router is connected to two resources or routers below it (children, descendants) and to one router above it (parent, ancestor). Fat tree [53] provides a more balanced capacity by having more links closer to the root of the tree. When also the number of routers is increased the fat tree topology provides the possibility to balance traffic and therefore decrease the possibility for congestion. The drawback of the fat tree topology is its complexity for on-chip implementation. While a binary tree can be easily created with an *H-structure*, the layout of the fat tree topology is not that obvious.

Other NoC topologies include *ring*, *star* and *spidergon*. The ring and star are very descriptive names: in a ring topology the routers are connected so that a ring is formed and in a star topology all routers are connected to one central router. Spidergon is a modification of the ring with an even number routers. In addition to the ring connections, each router is connected to its counterpart at the other side of the ring [18].

The regular structures explained above are suitable for general-purpose systems. However, they may loose some effectiveness when used with application specific systems. For this kind of systems custom topologies have been presented [7]. Their design starts from a thorough analysis of the traffic between the system components. A custom topology may contain links of different lengths and widths, odd-sized resources and it may have hybrid communication media combining buses, point-to-point links and networks.

#### 3.2 Routing

The routing protocol defines the way a message is transmitted from the source to the destination. For routing a header is introduced to the packet at the network interface. The header contains information about the route to the destination. In source routing this information includes routing directives for each router in the route, i.e. should the packet be forwarded straight at the particular router or is a turn required. In this case the network interfaces contain a routing table which provides information about every route in the network. Another approach is to give an address to each router in the network and include the destination address in the packet header. The routers then read this address, compare it to their own address and make the decision about the direction in which to forward the packet. In this approach the routing tables or decision logic is in the routers.

The selection of the route through the network from a source to a destination is defined by the routing algorithm, which can be either *oblivious* or *adaptive*. *Oblivious* routing algorithms do not take into consideration any possible changes in the state of the network. An important subset of the oblivious routing algorithms are the *deterministic* routing algorithms, which always provide the same route through the network. Adaptive routing algorithms, in contrast to oblivious routing algorithms, change the route based on the circumstances in the network. For instance a congested part of the network may be bypassed through other routes, and therefore better traffic balance may be achieved. The drawback of adaptive routing is the higher complexity and the possibility that packets arrive at the receiver in different order than they were sent. *In-order delivery* is one of the strengths of deterministic routing algorithms.

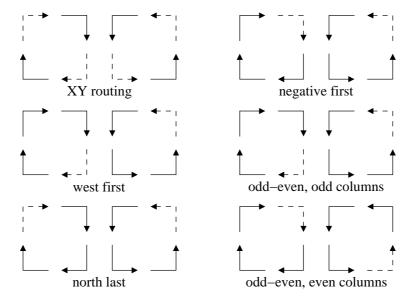

The chosen network topology sets guidelines for the routing algorithm. The simplest deterministic routing algorithm for the mesh topology is dimension order routing, better known as XY routing. In XY routing a packet is first routed along the x-dimension to the correct column and then along the y-dimension to the correct row. XY routing algorithm is minimal because it provides the shortest route from the source to the destination. The minimality is achieved by routing packets only in progressive directions in each routing stage.

An example of an oblivious routing algorithm which is not deterministic is the Valiant's randomized routing algorithm [21]. A packet sent from some source s to a destination d is first routed to a random intermediate terminal node x and from there to the destination d. The routing from s to x and from x to d can be done e.g. using dimension order routing. The algorithm effectively distributes the traffic in the network, thus minimizing congestion.

Adaptive routing can be minimal or fully adaptive. In minimal adaptive routing the direction of routing is selected among the possible progressive

routes. A variant of XY routing called *dynamic XY routing* [55] is an example of minimal adaptive routing. In that algorithm, the progressive direction with less traffic is selected if there are multiple options. Otherwise the algorithm follows the principles of XY routing.

Fully adaptive routing algorithms do not restrict the packets to the minimal routes. Some algorithms even allow U-turns. When using non-minimal routing algorithms, there is a possibility for a *livelock*, a situation where a packet travels in the network without ever reaching the destination. A livelock can be detected with the inclusion of a *hop counter* in the message header. The counter is set to some initial value at the source and in each router the hop count is decreased by one. If the counter value equals zero before it reaches the destination, the packet is probably in a livelock, and as a solution it is dropped from the network. The dropping should be recognized by the flow control, and a retransmission of the packet commenced.

Besides livelock, other exceptions in the routing include deadlock and starvation. Deadlock means a situation, where two, or more, messages wait for a resource reserved by the other, and at the same time reserve a resource the other one is acquiring. Therefore, neither of these messages cannot proceed and the network is halted. Deadlock is a severe malfunction which should be either prohibited in advance (deadlock avoidance) or handled when it occurs (deadlock recovery). Starvation may occur if packets have different priorities and a lower priority packet must wait its routing turn forever.

Deadlocks can be prevented at the routing algorithm level by admitting only such turns and routes that will not lead to a deadlock. Basically this means the prevention of cyclic dependencies between packets. XY routing is an example of a deadlock-free routing algorithm, because it admits only four of the eight possible turns (East-North EN, East-South ES, West-North WN and West-South WS, see Figure 3.5), which guarantees that no cyclic dependencies are possible.