## UNIVERSITY OF VAASA

## FACULTY OF TECHNOLOGY

## **AUTOMATION TECHNOLOGY**

Mathias Björk

# DEVELOPMENT AND TESTING OF IEC 61850 NETWORK INTERFERENCE EQUIPMENT – A CASE STUDY

Master's thesis in Technology for the degree of Master of Science in Technology submitted for inspection, Vaasa, March 26, 2014.

Supervisor

Professor Jarmo Alander

Instructor

Professor Jarmo Alander, D.Sc. (Tech.) Petri Välisuo

## FOREWORD

First I want to acknowledge my supervisor and instructors for all their effort in helping me with this project. I would like to thank Mika Ruohonen for his expertise in the IEC 61850 standard along with his contribution to the TehoFPGA project. Finally I would like to thank Olli Rauhala and Staffan Järn for their co–operation and great workmanship in this project.

Vaasa March 26, 2014

Mathias Björk

## TABLE OF CONTENTS

| FC | REW    | ORD                                                                 | 1  |

|----|--------|---------------------------------------------------------------------|----|

| SY | MBC    | LS AND ABBREVIATIONS                                                | 4  |

| TI | IVIST  | ELMÄ                                                                | 7  |

| AE | BSTR   | ACT                                                                 | 8  |

| RE | EFER A | хТ                                                                  | 9  |

| 1. | INTI   | RODUCTION                                                           | 10 |

|    | 1.1.   | Related work                                                        | 10 |

|    | 1.2.   | Outline of the thesis                                               | 11 |

| 2. | ETH    | ERNET ARCHITECTURE                                                  | 13 |

|    | 2.1.   | Ethernet frames and building blocks                                 | 13 |

|    |        | 2.1.1. Internet protocol suite                                      | 18 |

|    |        | 2.1.2. IEC61850 – Communication networks and systems in substations | 19 |

| 3. | EVO    | LUTIONARY COMPUTING                                                 | 22 |

|    | 3.1.   | Evolutionary Algorithms                                             | 23 |

|    | 3.2.   | Genetic Algorithms                                                  | 25 |

|    |        | 3.2.1. Mutation                                                     | 27 |

|    |        | 3.2.2. Recombination (crossover)                                    | 28 |

|    |        | 3.2.3. Selection and GA types                                       | 31 |

| 4. | EME    | EDDED SYSTEMS                                                       | 35 |

|    | 4.1.   | Field–programmable gate arrays                                      | 37 |

|    |        | 4.1.1. Altera DE4                                                   | 39 |

|    |        | 4.1.2. EtherTester software                                         | 40 |

| 5. | PRO    | TOTYPING, SIMULATION AND IMPLEMENTATION OF A GENETIC                | 1  |

|    | ALC    | ORITHM                                                              | 43 |

|    | 5.1.   | Simulation of EthGA on a PC-computer                                | 46 |

|    | 5.2.   | Implementation of EthGA on a FPGA/NIOS microprocessor               | 49 |

page

| 6.         | CASE STUDY                              |                                                                         | 52 |  |

|------------|-----------------------------------------|-------------------------------------------------------------------------|----|--|

|            | 6.1.                                    | Case 1: Preliminary system test                                         | 56 |  |

|            | 6.2.                                    | Case 2: Speed test                                                      | 56 |  |

|            | 6.3.                                    | Case 3: Burst test                                                      | 58 |  |

|            | 6.4.                                    | Case 4: Normalisation test                                              | 62 |  |

|            | 6.5.                                    | Case 5: Effect of packet structure in relation to message exchange time | 65 |  |

|            | 6.6.                                    | Summary                                                                 | 70 |  |

| 7.         | CON                                     | CLUSION                                                                 | 73 |  |

| 8.         | DISC                                    | USSION                                                                  | 74 |  |

|            | 8.1.                                    | Future work                                                             | 75 |  |

| RE         | FERE                                    | NCES                                                                    | 77 |  |

| APPENDICES |                                         |                                                                         | 81 |  |

|            | APPE                                    | NDIX 1. EthGA user manual                                               | 81 |  |

|            | APPENDIX 2. EthGA parameter explanation |                                                                         |    |  |

# SYMBOLS AND ABBREVIATIONS

## Greek symbols

| $\lambda$ | Offspring size  |

|-----------|-----------------|

| $\mu$     | Population size |

## Other symbols

| $L_{ch}$ | Chromosome length               |

|----------|---------------------------------|

| $loc_i$  | Locus index                     |

| $cr_i$   | Crossover index                 |

| $R_{cr}$ | Crossover rate                  |

| $N_{cr}$ | Number of crossover points      |

| $P_{cr}$ | Crossover probability parameter |

| $P_m$    | Mutation probability            |

## Abbreviations

| ASIC   | Application-specific integrated circuit               |

|--------|-------------------------------------------------------|

| CPLD   | Complex programmable logic device                     |

| CRC    | Cyclic redundancy check                               |

| DoS    | Denial-of-Service                                     |

| DSP    | Digital signal processor                              |

| DUT    | Device under test                                     |

| EC     | Evolutionary computing                                |

| EA     | Evolutionary algorithm                                |

| EEPROM | Electronically erasable programmable read-only memory |

| ES     | Evolutionary strategies                               |

| EP     | Evolutionary programming                              |

| FCS    | Frame check sequence                                  |

| FPS    | Fitness proportional selection                        |

| FPGA   | Field programmable gate array                         |

| FSM    | Finite state-machine                                  |

| GA     | Genetic algorithm                                     |

| GAL    | Generic array logic                                   |

| GMEC  | Gosling message exchange time                        |

|-------|------------------------------------------------------|

| GOOSE | Generic object-oriented substation event             |

| GP    | Genetic programming                                  |

| HDL   | Hardware description language                        |

| IC    | Integrated circuit                                   |

| ICBF  | Idle cycles between frames                           |

| IEC   | International Electrotechnical Commission            |

| IED   | Intelligent electronic device                        |

| IEEE  | The institute of Electrical and Electronic Engineers |

| IO    | Input–output                                         |

| IP    | Internet protocol                                    |

| ISO   | International organisation for standards             |

| JTAG  | Joint test action group                              |

| LAN   | Local area network                                   |

| LC    | Logic cell                                           |

| LE    | Logic element                                        |

| MAC   | Media access control                                 |

| NIC   | Network interface card                               |

| OSI   | Open systems interconnection                         |

| PAL   | Programmable array logic                             |

| PCB   | Printed circuit board                                |

| PID   | Proportional-integral-derivative                     |

| PLD   | Programmable logic device                            |

| PLA   | Programmable logic array                             |

| RPI   | Raspberry PI                                         |

| SAS   | Substation automation system                         |

| SFD   | Start frame delimiter                                |

| SPLD  | Simple programmable logic device                     |

| SV    | Sampled values                                       |

| ТСР   | Transmission control protocol                        |

| TTL   | Time to live                                         |

| UART  | Universal asynchronous receiver/transmitter          |

|       |                                                      |

| USB  | Universal serial bus                                             |

|------|------------------------------------------------------------------|

| VHDL | Very high-speed integrated circuit hardware description language |

| VLAN | Virtual local area network                                       |

| WAN  | Wide area network                                                |

|      |                                                                  |

| VAASAN YLIOPISTO               |                                                      |

|--------------------------------|------------------------------------------------------|

| Teknillinen tiedekunta         |                                                      |

| Tekijä:                        | Mathias Björk                                        |

| Diploomityön nimi:             | Tapaustutkimus IEC 61850 verkkohäiriölaitteiston     |

|                                | kehityksestä ja testauksesta                         |

| Valvojan nimi:                 | Professor Jarmo Alander                              |

| Ohjaajan nimi:                 | Professor Jarmo Alander, D.Sc. (Tech.) Petri Välisuo |

| Tutkinto:                      | Diplomi-insinööri                                    |

| Koulutusohjelma:               | Sähkö– ja energiatekniikan koulutusohjelma           |

| Suunta:                        | Automaatiotekniikka                                  |

| Opintojen aloitusvuosi:        | 2011                                                 |

| Diploomityön valmistumisvuosi: | 2014 <b>Sivumäärä:</b> 89                            |

## **TIIVISTELMÄ:**

Älykkäissä sähkölaitteiden (IED, intelligent electronic device) lukumäärän kasvaessa sähköasemien automaatiojärjestelmissä (SAS, substation automation system) käytetään enenevässä määrin IEC 61850–standardin mukaista tiedonsiirtoa, jonka useimmiten käytetty tiedonsiirtoprotokolla on GOOSE (Generic Object–Oriented Substation Events). Tämä protokolla asettaa tiettyjä vaatimuksia IED–laitteille ja verkon arkkitehtuurille. Näitä vaatimuksia on seurattava tarkasti jotta voidaan taata turvallinen ja toimiva sähkö-aseman automaatiojärjestelmä.

Tämän tutkielman päätavoitteena oli sellaisen laitteiston kehittäminen, jolla voidaan testata GOOSE–protokollan avulla kommunikoivien IED–laitteiden käyttöä mahdollisimman huonoissa olosuhteissa. Testauslaitteisto pystyy välittämään ethernet–paketteja gigabitin sekunti nopeudella, jotta voidaan analysoida häiriön vaikutuksia testattavaan laitteeseen (DUT, device under test). Testauslaitteisto pystyy geneettistä algoritmia käyttäen myös etsimään paketin, joka on testattavalle laitteelle kaikkein haitallisin.

Kehitetty laitteisto pystyy tulosten mukaan löytämään heikkouksia testattavissa laitteissa, kun ethernet–paketteja välitetään suurilla nopeuksilla ja häiritsevien pakettien määränpääksi asetetaan jonkin toisen kuin testattavan laitteen osoite. Edellä mainittu onnistuu kuitenkin vain tietyn testattavan laitteen kanssa, ei kaikissa tapauksissa. Tässä tutkielmassa testattavan laitteen toiminta pystyttiin pysäyttämään kokonaan. Tulosten mukaan geneettinen algoritmi ei kyennyt löytämään mitään tiettyä haitallista pakettia, mikä tarkoittaa sitä, että pakettien rakenteella ei ole suurta merkitystä testattavan laitteen toiminnan pysäyttämisessä.

AVAINSANAT: Evoluutiolaskenta, IEC 61850, Ethernet, FPGA

| UNIVERSITY OF VAASA              |                                                                                         |

|----------------------------------|-----------------------------------------------------------------------------------------|

| Faculty of Technology            |                                                                                         |

| Author:                          | Mathias Björk                                                                           |

| Topic of the Thesis:             | Development and testing of IEC 61850 network in-<br>terference equipment – a case study |

| Supervisor:                      | Professor Jarmo Alander                                                                 |

| Instructor:                      | Professor Jarmo Alander, D.Sc. (Tech.) Petri Välisuo                                    |

| Degree:                          | Master of Science in Technology                                                         |

| Degree Programme:                | Degree Programme in Electrical Engineering                                              |

| Major of Subject:                | Automation Technology                                                                   |

| Year of Entering the University: | 2011                                                                                    |

| Year of Completing the Thesis:   | 2014 <b>Pages:</b> 89                                                                   |

### **ABSTRACT:**

As the number of intelligent electronic devices (IEDs) is increasing in substation automation systems (SAS), the IEDs have often been extended with network communication conforming with the IEC 61850 standard, where the Generic Object–Oriented Substation Events (GOOSE) communication protocol is mostly used. This protocol sets certain demands on the IEDs and the network architecture, which must be strictly followed to ensure a safe and functional SAS.

The aim of this study is to develop equipment for testing IEDs communicating with the GOOSE protocol in the worst conditions possible. The testing equipment is able to transmit Ethernet packets at the rate of one gigabit per second, in order to analyze the impact of the interference on a device under test (DUT). This testing equipment is also able search for the single most harmful packet for a DUT by using a genetic algorithm.

This study shows that the developed equipment is able to find flaws in DUT's by transmitting Ethernet packets at high speeds, when setting the destination address of the interfering packets to any other address than the physical address of the DUT. However, this only works for a specific DUT, and not in every case. This particular case managed to disable the DUT's functionality completely. This study also shows that the genetic algorithms did not manage to find any specific harmful packet. This shows that the packet structure does not seem to play any role in disabling the functionality of the DUT.

| VASA UNIVERSITET            |                                                      |

|-----------------------------|------------------------------------------------------|

| Tekniska fakulteten         |                                                      |

| Författare:                 | Mathias Björk                                        |

| Titel:                      | Utveckling och testning av störningsutrustning för   |

|                             | IEC 61850 nätverk – en fallstudie                    |

| Övervakare:                 | Professor Jarmo Alander                              |

| Handledare:                 | Professor Jarmo Alander, D.Sc. (Tech.) Petri Välisuo |

| Examen:                     | Diplomingenjör                                       |

| Utbildningsprogram:         | Utbildningsprogrammet för elektro- och energiteknik  |

| Inriktning:                 | Automationsteknik                                    |

| Intagningsår:               | 2011                                                 |

| Diplomarbetet färdigställt: | 2014 Sidantal: 89                                    |

|                             |                                                      |

### **REFERAT:**

Eftersom antalet intelligenta elektroniska anordningar (IED, intelligent electronic device) ökar inom flera ställverks automationssystem (SAS, substation automations system), så har IED–enheter ofta utökats med kommunikationsmöjligheter som följer IEC 61850–standarden. Av dessa är GOOSE (Generic Object–Oriented Substation Event)– protokollet det mest använda. Detta protokoll ställer hårda krav på IED–enheterna vad gäller kommunikation och nätverksarkitektur. Dessa krav måst följas strikt för att garantera ett säkert och fungerande ställverk.

Syftet med min undersökning är att utveckla testutrustning för IED–enheter som kommunicerar med GOOSE–protokollet inom krävande miljöer. Testutrustningen möjliggjör överföring av Ethernet–paket med en hastighet upp till en gigabit per sekund, vilket kan användas för att analysera störningsinverkan på en DUT–enhet (DUT, device under test). Med hjälp av genetiska algoritmer möjliggjör testutrustningen också sökning av enskilda paket som kan vara skadliga för en DUT–enhet.

Min undersökning visar att testutrustningen som jag utvecklat är kapabel till att hitta brister i DUT–enhetens programvara genom att sända störande paket med höga hastigheter till DUT–enheten. Detta är möjligt när destinationsaddressen hos de störande paketen inte är den samma som DUT–enhetens fysiska adress. Detta gäller dock endast för den specifika DUT–enheten som jag analyserade. Testutrustningen som jag utvecklade lyckades också helt inaktivera DUT–enhetens funktionalitet. Undersökningen visar också att störningspaketens struktur inte spelar någon roll när det gäller inaktivering DUT–enheten, vilket testades med genetiska algoritmer.

### 1. INTRODUCTION

As the development of demanding electronics systems grows constantly, the expertise in the area must follow the same pattern to keep up with the increasing demand. Therefore the University of Vaasa has initiated a research project named TehoFPGA (including sub projects named TehoFPGA-I and TehoFPGA-II) to increase the expertise in the area of embedded electronics, where the main focus is on Field-Programmable Gate Arrays (FP-GAs). The aim of TehoFPGA is to increase and share the knowledge of FPGAs amongst all participants, which are both universities and companies in Vaasa region. A FPGA-laboratory will be built in Technobotnia, to enable the attendants to participate in the research of the FPGA-technology hence increasing the expertise in this particular field of study. Initially several studies will be performed where the teaching, programming and testing of FPGAs will be analysed to set up a state-of-the-art FPGA-laboratory. (Alander 2012)

This Master's thesis is focusing mainly on the programming and testing of FGPAs, where a genetic algorithm will be implemented and used for network testing in substation automation systems (SAS), to detect flaws and bugs in protection relays communicating with the Generic Object-Oriented Substation Event (GOOSE) protocol derived from the IEC 61850 standard. More specifically this thesis focuses on the impact of interfering network traffic in a SAS, where the developed software is used to interfere with a functional device under test (DUT) in order to break its Ethernet communication. Primarily the software is used to analyse how the transmission rate of the interfering network traffic affects the DUT, and eventually the genetic algorithms are used to search for how the packet structure of the interfering network traffic is affecting the DUT's functionality.

#### 1.1. Related work

Although there seems to be a lack of previous research concerning the specific research subject of this thesis, similar subjects have been researched earlier. Li (2004) proposed

a genetic algorithm for detecting network intrusion to classify rules for denying certain intrusion patterns, hence blocking incoming connections that are classified as threats. Gong, Zulkernine & Abolmaesumi (2005) managed to implement this behaviour, resulting in Java software capable of identifying network intrusions with a genetic algorithm. These two researches can be analysed as complements of this thesis research, since this thesis presumes that the testing device is physically located inside the substation network with IEC 61850 compliant devices.

Kuffel, Ouellette & Forsyth (2010) on the other hand, have studied the impact of abnormal IEC 61850 GOOSE and Sampled Values (SV) protocol data on a DUT, which is very similar to this thesis research. Kuffel et. al. on the other hand did manage to gather important data from intelligent electronics devices (IEDs) which is not possible in a broad range in this thesis, also they did not use genetic algorithm in their research. Furthermore Hor, Crossley & Millar (2007) managed to create a hybrid of a rough set theory and a genetic algorithm (hybrid RS–GA), to obtain additional knowledge from operational data from IEDs. The above mentioned works does relate to this thesis partly, but in this thesis, more emphasis is put on disabling a DUT's functionality using genetic algorithms.

#### 1.2. Outline of the thesis

The introductory theory which is used as a baseline for this thesis is presented in Chapters 2, 3 and 4. Chapter 2 presents the basics of the Ethernet architecture, where the Internet protocol suite is explained along with the Open–System Interconnection (OSI) reference model (to give the reader an understanding of general networking concepts). Chapter 3 on the other hand studies evolutionary computing, and more specifically the structure and principles of genetic algorithms, which will be used in the developed EthGA software presented in Chapter 5. Chapter 4 presents embedded systems and more specifically the Field–Programmable Gate Arrays (FPGAs), on which the EtherTester software have been implemented that serves as a foundation for the EthGA software.

The practical work in this thesis is presented in chapters 5 and 6, where in Chapter 5 the developed EthGA software is presented along with its simulation on a computer and its implementation on a Nios II microprocessor on an Altera Development and Education board 4 (DE4). The EthGA software is eventually tested and validated in Chapter 6 in a simulated environment where the EtherTester and EthGA is trying to interfere with a DUT, in order to break its Ethernet communication. The results are finally presented in Chapter 7 and discussed in Chapter 8.

## 2. ETHERNET ARCHITECTURE

This chapter will give the reader a brief introduction to the Ethernet network and its different standards and protocols that have evolved over time. The reader will also be given a short history review of the Ethernet, and later on in Section 2.1 the more important building blocks of the Ethernet are presented, including the *Open Systems Inter-connection (OSI) Reference Model* and the Media Access Control (MAC) protocol. The MAC–protocol will be more thoroughly presented in this chapter due to its importance in Ethernet frame transmission(s), whereas specific protocols to the thesis are only briefly presented in Section 2.1.2.

The Ethernet network topology took its toll in 1973 when Bob Metcalfe started extending the use of the Aloha network, which was invented in the late 1960s for radio communication between the Hawaiian Islands. After a few years of research, the paper "Ethernet: Distributed Packet Switching for Local Computer Networks" was presented in 1976, which lead to a U.S patent number 4,063,220 on Ethernet for "Multipoint Data Communication System With Collision Detection". The patent was received by Robert M. Metcalfe, David R. Boggs, Charles P. Thacker, and Butler W. Lampson. Ever since the first patent, the Ethernet have been researched and improved, resulting in more affordable and consumer friendly devices with Ethernet capability. The research lead to the *IEEE 802.3 Standard for Ethernet*, where the newest version is from 2012 (IEEE 802.3:2012 2012; Spurgeon 2000: 3-7).

#### 2.1. Ethernet frames and building blocks

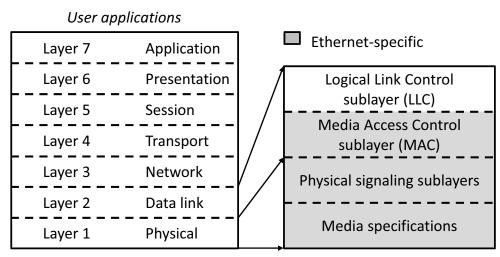

In 1978 the International Organisation for Standards (ISO) developed a standard model for layered network protocol implementation, named the *Open Systems Interconnection* (*OSI*) *Reference Model*. The purpose of the OSI model was to enable an easy implementation and communication between different protocol layers. The OSI model is presented in Figure 1, and consists of seven layers where each have their own purpose and implementa-

tation standards. The higher level layers in the OSI model are application specific, and handles the reliability of data transmission and the presentation of the transmitted data (to the user), whereas the lower two layers are more intended for Ethernet transmission and handles the Media Access Control (MAC) protocol.

Transmission media

**Figure 1.** The Open System Interconnection (OSI) Reference Model *(left)* with corresponding Ethernet 802.3 sublayers *(right)* (Adapted from Spurgeon 2000: 13).

A short description of the seven OSI layers presented in Figure 1 is listed below, where the description begins with the lowest layer.

#### Physical layer

Defines the standards for mechanical, electrical and functional control of data circuits on a physical level including e.g. signal levels, cabling and hardware specifications.

#### Data link layer

Allows direct communication from station to station on a single link provided by the physical layer, where the communication can be point-to-point or point-to-multipoint depending on the network architecture. This layer receives/transmits

frames, defines standards for the Ethernet frame format and also handles the MAC protocol.

#### Network layer

Responsible for the communication from station to station across the Internet. The network layer is partly independent from the two lower layers and can exchange data on a higher level of protocols, only by issuing its requests to the link layer. The protocols defined for the network layer (and the upper layers) are independent from the Ethernet standard. A common protocol that is used is the Internet Protocol (IP) that a majority of devices use to communicate with each other.

#### Transport layer

Handles the end-to-end connection, flow control, congestion control and datagram delivery. Two common protocols used by the transport layer are the Transmission Control Protocol (TCP) and the User Datagram Protocol (UDP), which are used along with the IP protocol of the network layer.

#### Session layer

Concerns the establishment of reliable communication between applications including opening, managing and closing sessions.

#### Presentation layer

Encodes the received data on an application specific basis and presents the data to a particular application.

#### Application layer

The first link between the end-user and the software and provides mechanisms for end-user applications like chat, mail, file-transfer etc.

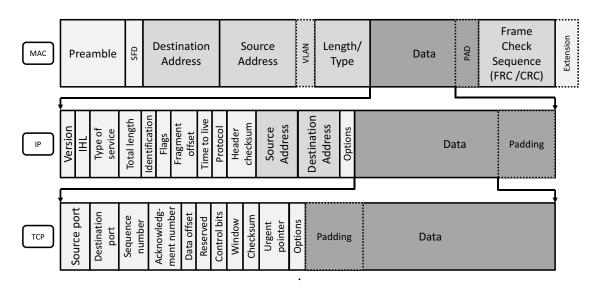

As the OSI model and the IEEE standards was developed for enabling compatibility between different hardware and software manufacturers, the MAC–protocol also plays an important role in Ethernet communication. The MAC–protocol implements (as previously mentioned) the Data Link Layer, and describes the structure of the Ethernet frames that are transmitted over Ethernet networks. Figure 2 shows the structure of an *Ethernet frame* and an *Ethernet packet*. (Edwards & Bramante 2009: 374, 379, 403, 435) (Spurgeon 2000: 10-12).

| 7 octets                         | 1 octet                    | 6 octets               | 6 octets          | 4 octets | 2 octets        | 46 to 1500/1504/1<br>octets (including p |     | 4 octets                                 | n octets  |

|----------------------------------|----------------------------|------------------------|-------------------|----------|-----------------|------------------------------------------|-----|------------------------------------------|-----------|

| Preamble                         | SFD                        | Destination<br>Address | Source<br>Address | VLAN     | Length/<br>Type | Data                                     | PAD | Frame<br>Check<br>Sequence<br>(FCS /CRC) | Extension |

|                                  | High-level protocol packet |                        |                   |          |                 |                                          |     |                                          |           |

| Ethernet FRAME (data link layer) |                            |                        |                   |          |                 |                                          |     |                                          |           |

| Ethernet PACKET (physical layer) |                            |                        |                   |          |                 |                                          |     |                                          |           |

|                                  |                            |                        |                   |          |                 |                                          |     |                                          |           |

Octets transmitted left to right

**Figure 2.** Structure of the Media Access Protocol (MAC) protocol/frame involving fields and their size in octets, where 1 octet equals 8 bits (Adapted from IEEE 802.3:2012: 53).

The Ethernet frame is encapsulated in the Ethernet packet, where the fields *Preamble*, *Start Frame Delimiter (SFD)* and *extension* belongs to the Ethernet packet. According to the IEEE 802.3:2012 standard there are three types of MAC frames that can be transmitted over the Ethernet, where each different frame type affects the total possible size of the frame and its usage:

- Basic frames, used in most cases

- Q-tagged frames, used e.g. by the IEEE 802.1q:2011 standard

- Envelope frames, large frames

The contents of the Ethernet frame along with their uses are described below:

#### **Destination Address**

The destination address field defines the receiver(s) of the Ethernet frame that is transmitted. There exists three types of MAC addresses: *Unicast* where the receiver is a single physical device on a Local Area Network (LAN), *Multicast* where the receivers are a specified group of physical devices on a LAN and *Broadcast* where the receivers are every connected physical device on a LAN.

#### Source Address

The source address is the identifier of the physical device that transmitted the frame and will never change for the sender.

#### Virtual Local Area Network (VLAN) tag header (optional)

The VLAN tag header can be inserted between the source address field and the length/type field and specifies what part of a virtual local area network the transmitted frame belongs to. The VLAN tag header derived in the IEEE 802.1Q standard is used e.g. in the GOOSE protocol that will be discussed in Section 2.1.2. Frames that include the VLAN tag header are called Q-tagged frames, as described earlier in this section. (Jaakohuhta 2005: 366) (Kriger, Behardien & Retonda-Modiya 2013: 709) (IEEE 802.1q:2011).

#### Length/Type

A 2 octet field that specifies the length of the data field (in octets) if the decimal value of the Length/Type field is less than or equal to 1500. If the decimal value is greater than or equal to 1536 the Length/Type field defines the higher layer protocol transmitted in the data field. The values for the protocols can be found in the *Public Registered Ethertype List* provided by the IEEE–organisation (IEEE 2013). The values of the most relevant protocols for this thesis are listed below:

| - IPv4 Internet protocol   | 0x0800 |

|----------------------------|--------|

| - IEC 61850 GOOSE protocol | 0x88b8 |

| - IEC 61850 GSE management services protocol     | 0x88b9 |

|--------------------------------------------------|--------|

| - IEC 61850 Sampled Values Transmission protocol | 0x88ba |

| - IEEE Std 802.1Q – Customer VLAN Tag Type       | 0x8100 |

| - IEEE Std 802.1Q – Service VLAN Tag Type        | 0x88a8 |

#### Data (including PAD)

The Data field (also known as payload) can hold any sequence of octets up to a maximum length defined by the specific implementation, where the maximum length of the data field is defined by the frame types listed below:

- Basic frames, maximum length is 1500 octets

- Q-tagged frames, maximum length is 1504 octets

- Envelope frames, maximum length is 1982 octets

The data field (usually) holds a higher level protocol, such as the (combined) TCP/IP–protocol or the GOOSE protocol, which also have their own protocol headers and data fields. The *pad* field is used to append information to the data field, if length of the data is less than 46 octets.

#### FCS (Frame Check Sequence)

The *FCS* or *CRC* (Cyclic redundancy check) holds a polynomial calculated by the transmitter where all the fields of the MAC–frame are included in the calculation (except the FCS field). The receiver then uses the same equation to determine if the frame was corrupted during the transmission, and if the result achieved by the receiver differs from the value of the FCS field, the frame is discarded. This is to ensure that a correct transmission have occurred.

#### 2.1.1. Internet protocol suite

The Internet protocol suite consists of the IP-protocol and the TCP-protocol, and is considered to be the most used standard of the Internet (can also be referred to as the *TCP/IP*  *protocol suite*). The Internet protocol suite enables data communication (i.e. packet transmission/reception) between nodes that are connected to the Internet, and can be included in many operating systems and devices that implements the Ethernet standard. The Internet protocol suite operates in the five upper layers of the OSI–model shown in Figure 1, enabling the implementation of many different protocols inside the Internet protocol suite. However, the most important ones are the TCP– and IP–protocols. Figure 3 presents the embedding of IP– and TCP–protocols in the MAC–frame, where the underlying protocol is always located in the data field of the parent protocol (Edwards & Bramante 2009: 197-198).

**Figure 3.** The main part of the Internet protocol suite embedded in a MAC–frame, where the underlying protocol is always located in the data field of the parent protocol. (RFC: 791: 38)(RFC: 793: 15)(IEEE 802.3:2012: 53)

#### 2.1.2. IEC61850 – Communication networks and systems in substations

In order to assure high–speed reliable network communication in time–critical Substation Automation Systems (SAS) between Intelligent Electronic Devices (IEDs), a clear and concrete set of rules and protocols must be used. The IEC 61850 standard was developed to achieve this goal when the first version was published in 2003. The main goal of the IEC 61850 was to enable a minimum set–up effort and auto–configurable IEDs giving the

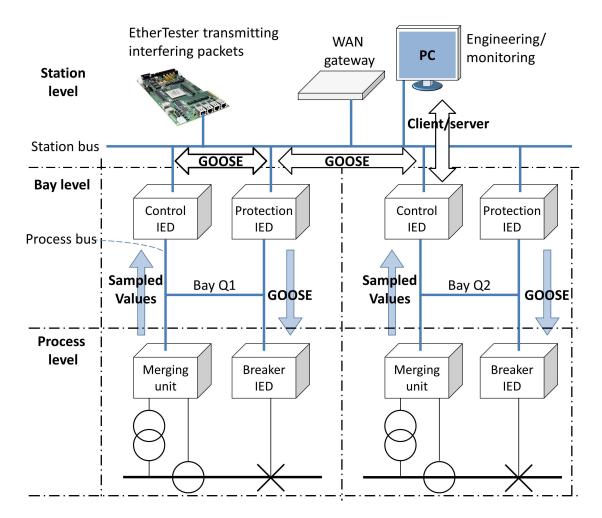

possibility of IEDs from different manufacturer to communicate with each other (Mackiewicz 2006). Figure 4 shows a conceptual implementation of the IEC 61850 standard in a SAS, where the arrows represent IEC 61850 communication protocols transmitted over the Ethernet in a MAC–frame (Söderbacka 2013: 15-17). The developed EtherTester presented in Section 4.1.2, is later connected to a simulated station bus, as shown in Figure 4. (IEC 61850-1 2003).

**Figure 4.** Conceptual implementation of the IEC 61850 standard in a SAS, where the arrows represent IEC 61850 communication protocols and the EtherTester is connected to the station bus. (Adapted from Söderbacka 2013: 15.)

As previously mentioned in Section 2.1.1, nodes supported by the Internet protocol suite that are connected to the Internet can communicate with each other without concerning the type of operating system used. This also applies to IEDs which are connected to the station bus as in Figure 4, shown in the Client/server arrows. However IEDs must also transmit time–critical packets between each other resulting in the Sampled Values (SV) and Generic object–oriented substation event (GOOSE) messages/protocols mapped directly onto the link layer. This time–critical communication proposed by the IEC 61850 standard is the most important target for this thesis and tests will be executed in Chapter

6 to analyse the reliability of the GOOSE communication protocol implementation in IEDs.

## 3. EVOLUTIONARY COMPUTING

This chapter gives the reader an overview to evolutionary computing, where the most important historical events (in evolutionary computing) are presented along with some of the most common evolutionary algorithms. Section 3.1 introduces the reader with the purpose of these algorithms and also the basic structure of an evolutionary algorithm. Later in the Section 3.2 this thesis will go deeper into the genetic algorithm and thoroughly present its functionality and structure, also a simple example of a genetic algorithm will be evaluated on a 1D–landscape with multiple local optima in Section 5.

Evolutionary computing is a (sub)–field of Computer Science, where the fundamentals of problem solving have arisen from the theories of evolution in nature. These theories were presented by Darwin (1859) in "Origin of the species", and they are the basis of for what is today known as evolutionary algorithms (EA). Evolutionary algorithms can be used in vast amount of ways to solve complex problems by using an improved version of the trial–and–error technique, where the so called samples of the trials are evolved between each run into a better sample until an acceptable result is acquired.

The field of the evolutionary computing reaches all the way back to the 1930s, when Sewell Wright introduced the idea of visualizing an evolutionary system for exploring a multi–peaked fitness landscape and forming sections around peaks of high fitness. The field of study however did not take its toll until the 1960s, when computers could be used as a tool for simulating and modelling evolutionary algorithms.

There were a couple of groups in the 1960s that showed a vast amount of interest in evolutionary algorithms, which also shaped this emerging field by their research. Rechenberg and Schwefel at the Technical University in Berlin, presented the idea of using evolutionary algorithms as a method for function optimisation, which evolved to the principle of evolution strategies (ES). Fogel at UCLA developed an evolutionary framework called evolutionary programming (EP), which was able to enhance the function of state machines over time. At the University of Michigan, Holland used evolutionary systems to develop robust adapting systems that could handle irregular and changing environments, by including the feedback from the operational environment to alter the system itself. This formed the basis for what is today called genetic algorithms (GA). These three methods (EV, ES, GA) that were developed in the 1960s have been studied ever since, and is researched and improved continuously. Another milestone was in the beginning of the 1990s when Koza (1992) introduced the concept of genetic programming (GP), which evolved from GA into an evolutionary algorithm that could generate computer programs for specific tasks. These computer programs were composed by a multitude of functions that where selected and connected together (using genetic algorithms) to achieve the desired program. There are also a lot of other evolutionary algorithms that have evolved from the previously mentioned ones but they will not be discussed in this thesis. (Eiben & Smith 2007: 1-3) (Jong 2006: 23-29)

#### 3.1. Evolutionary Algorithms

Even though there are many different kinds of evolutionary algorithms (ES, EP, GA, GP, et al.) they still share the same principle regarding their structure and the abstract means of achieving the desired result. They all have an initial population which is stochastically generated, that will be judged (evaluated) for their suitability (fitness) to the environment, where the environment represents the search space of the specific problem. This population will be bred through recombination into a new population where the parents with higher fitness will have a higher chance to breed (i.e. produce an offspring). Recombination mostly occur between a pair of individuals, resulting in a new pair of individuals that holds the properties of the parents. The resulting offspring might also be stochastically mutated to add some randomness to the evolutionary process. After the recombination and/or mutation the offspring will be evaluated again, and the process circles until an appropriate individual in the population is found, or another desirable search criteria is reached. This search criteria could be for example to maximize a function, generate a fast and efficient computer program, search for the shortest path between a number of routes, or to increase the efficiency of a proportional–integral–derivative (PID) controller

(Mirzal, Yoshii & Furukawa u.d.). The pseudo–code for an evolutionary algorithm is presented in Figure 5.

```

BEGIN

INITIALIZE population stochastically

EVALUATE each individual from population

WHILE (TERMINATION CONDITION IS NOT SATISFIED)

1. SELECT parents

2. RECOMBINE pairs of parents

3. MUTATE the resulting offspring

4. EVALUATE new individuals

5. SELECT individuals for the next generation

END WHILE;

```

END

**Figure 5.** Pseudo–code for an evolutionary algorithm, where the stages are abstract and vary in each different implementation of an evolutionary algorithm. (Adapted from Eiben & Smith 2007: 16.)

The differences between the evolutionary algorithms applies mostly to their application area, but also in the representation of the individuals in the population. An individual in a GA is often represented by a bit-string of length n, which makes it appropriate for this Master's thesis, since Ethernet frames are on a physical level represented by digital voltages i.e. on a software level by binary numbers where n is the length of the Ethernet frame. In ES an individual is represented by real-valued vectors, in EP by a finite statemachine (FSM) and in GP by trees. Another varying aspect in evolutionary algorithms is the way the different stages in Figure 5 are implemented. For example in GA the recombination could be discrete or intermediate whereas an EP can have no recombination at all and the individuals are only evolved by mutation. In this thesis only the stages that apply to genetic algorithms will be presented thoroughly in Section 3.2. (Eiben & Smith 2007)

#### 3.2. Genetic Algorithms

There are many traditional search methods available to address specific problems, when the search space is relatively small and the constraints of the system are within fair ranges. However when the complexity of the system increases and the search space is large, the amount of approaches are limited. This is where the genetic algorithms can be introduced. GAs (and other evolutionary algorithms) are based on the assumption that when randomly combining good sub–solutions, the probability of getting a better new solution is high, which relates good to the idiom *you can't make bricks without straw*. However there is not actual mathematical proofs of the functionality of a GA, and this is one of the main reasons why mathematicians may oppose these search methods. However there have been many successful implementations of GAs where traditional search methods have proven inefficient (Alander 1998: 18).

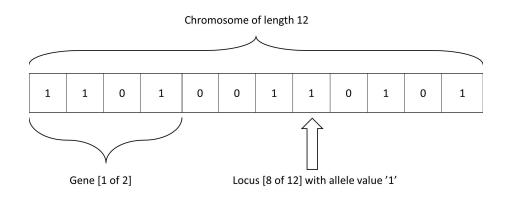

In genetic algorithms, the samples to be evaluated and evolved are often called as *chro-mosomes*, they are constructed like bit strings of length n, as shown in Figure 6. The chromosome can be divided in parts called *genes* that represents the variables or different properties of the chromosome. Every single bit in a chromosome is called a *locus* and can take the *allele* values of '0' or '1'. A chromosome has at least one gene in which case the length of the chromosome is the same as the length of the gene, but usually a chromosome contains many genes. A set of chromosomes is called as a *population*. In a population each chromosome have the same structure and the amount of chromosomes is the size of the population. A single chromosome in a population can also be referred to as an *individual*. (Mitchell 1998: 8).

Figure 6. A bit string chromosome of length 12 with 2 genes and 12 loci.

When simulating a genetic algorithm each iteration of the simulation loop is called a *generation*, where as presented in Figure 5, the population is evaluated, selected, recombined and mutated (more on this in sections 3.2.1, 3.2.2 and 3.2.3). For each chromosome in the population to have high chance of breeding, it must be assigned a high score from a fitness function. The fitness function could be for example to maximize a real–valued one–dimensional function, as shown in Equation 1,

$$f(x) = x + |\sin(32x)|, \quad 0 \ge x \le \pi$$

(1)

where x is a chromosome in the population, and f(x) gives the fitness of that particular chromosome. In case the function would be known one could normalize the result by dividing it with the maximum value of f(x) hence scaling the fitness between 0 and 1. However this is seldom appropriate in search algorithms since if the algorithm would already know the best result in the search space it would not have to search at all. In most cases the optimum is unknown meaning that f(x) returns an unscaled fitness value, and the higher fitness the better since the task was to maximize the function. Because the maximum fitness is not known the genetic algorithm does not know when to stop, and even though the GA might have found a high fitness value, the GA could be stuck on a local optimum. The search space of the previously mentioned problem is defined in equation 1 where a chromosome can only take the values between 0 and pi, this could also be defined as the fitness landscape. Since equation 1 only takes one value as an input arguments, the chromosome will only hold one gene, and this particular gene is usually a binary representation of the real number, where the precision of the binary representation is dependent on its length i.e. the gene length. (Mitchell 1998: 8-9)

The are many kinds of operators in genetic algorithms, however only the operators that apply to binary–string representations are presented in this section. Other representations like integer, floating–point or character representations will not be discussed since this thesis will focus on Ethernet traffic which is constructed of bits. The three main operators that are used in most genetic algorithms are listed below, and will be presented in the succeeding sections.

- Mutation

- Recombination

- Selection

These operators where also defined in the pseudo-code for an evolutionary algorithm showed in Figure 5.

#### 3.2.1. Mutation

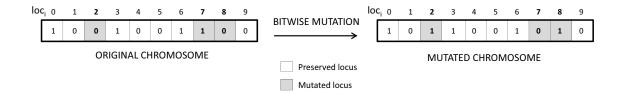

The mutation operator applies to only one individual at a time, and the outcome of the mutation is a slightly altered individual that still has an unchanged structure. The most common mutation operator for binary–string representation is the bitwise mutation operator, however some other types have occasionally been used but will not be discussed here. The bitwise mutation gives each bit (locus) a probability  $P_m$  to be mutated, and if a randomly generated number falls inside that certain probability the bit will be flipped, i.e. the allele value is changed from '0' to '1' or from '1' to '0' (Chambers 2001: 14). Figure 7 shows the original chromosome and the mutated chromosome, where the loci 2, 7 and 8 have been flipped. Note that the indexing  $loc_i$  of the loci ranges from 0 to 9, but the length of the chromosome is the number of loci i.e. 10 (Eiben & Smith 2007: 42-43).

**Figure 7.** Bitwise mutation of a single–gene chromosome with locus index  $loc_i$  from 0 to 9 and chromosome length  $L_{ch} = 10$ , where the loci 2, 7 and 8 have been flipped. (Adapted from Eiben & Smith 2007: 43.)

#### 3.2.2. Recombination (crossover)

Another operator in the GA is the **recombination**, which in some cases is referred to as **crossover**. The recombination occurs between 2 or more parents and produces an off-spring of equal size. Recombination is considered by many to be the most important feature of genetic algorithms, and is the one operator that distinguishes GAs from traditional search operators. The recombination may also implement the crossover parameter  $R_{cr}$ , which determines the probability of the crossover. First two parents are selected, secondly a random number is drawn from the range of [0, 1], if the random number is larger than  $R_{cr}$  the parents will be recombined. Otherwise the parents will be bred asexually, meaning that the resulting offspring is an identical copy of the parents. Note that this offspring might still be altered through mutation as discussed in the previous section. There are three main recombination operators commonly used for binary–representation chromosomes:

- One-point crossover

- n-point crossover

- Uniform crossover

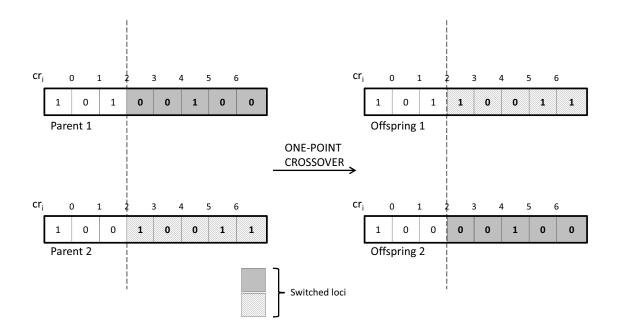

**One–point crossover** is the simplest of all crossover operators. The purpose of the one– point crossover is to split two chromosomes at a randomly selected crossover index  $cr_i$ in the range of  $[0, L_{ch}-2]$ , where  $L_{ch}$  is the chromosome length. The two chromosomes then swap the information that resides after the selected point, i.e. the chromosomes are exchanging their tails (Goldberg 1989: 12). Figure 8 shows the functionality of an one– point crossover with crossover index  $cr_i$  at 2 and a chromosome length  $L_{ch}$  of 8 (Eiben & Smith 2007: 47-48).

Figure 8. One-point crossover at crossover index  $cr_i = 2$  on chromosomes with chromosome length  $L_{ch} = 8$ . (Adapted from Eiben & Smith 2007: 48.)

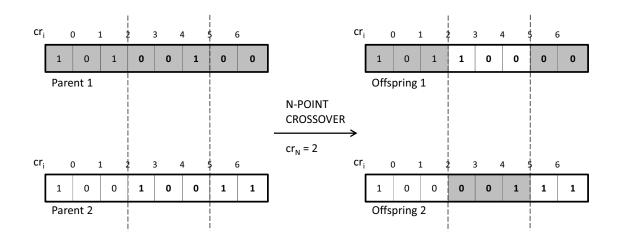

A second more generalized form of crossover is the **N-point crossover**, where the chromosome is broken down to n + 1 segments that are exchanged between the parents to produce a new offspring. In N-point crossover a number of crossover points  $cr_N$  are selected randomly in the range of  $[0, L_{ch}-2]$  where  $L_{ch}$  is the length of the chromosomes, same as in the one-point crossover (Eiben & Smith 2007: 48). Figure 9 shows a N-point crossover where  $cr_i = \{2, 5\}$ ,  $N_{cr} = 2$  and  $L_{ch} = 8$ .

**Figure 9.** N-point crossover at crossover index  $cr_i = \{2, 5\}$  on chromosomes with  $L_{ch} = 8$ . (Adapted from Eiben & Smith 2007: 48.)

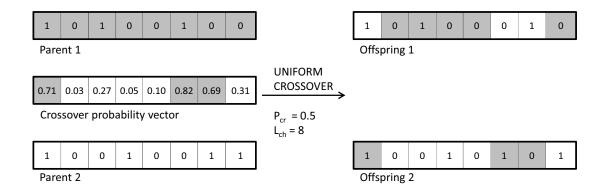

The last type of crossover operator is the uniform crossover, where each locus in the chromosomes are treated individually, as presented in Figure 10. Uniform crossover is implemented by generating uniformly distributed random variables within the range [0, 1] and applying them in a crossover vector of length  $L_{ch}$ . A crossover probability parameter  $P_{cr}$  is then assigned and if a random variable in the crossover vector falls within that probability, the loci at the index of the random variables are then exchanged (Beasley, Bull & Martin 1993: 2). The crossover probability parameter  $P_{cr}$  is often assigned to 0.5 (Eiben & Smith 2007: 48-49).

Figure 10. Uniform crossover with crossover probability parameter  $P_{cr} = 0.5$ . (Adapted from Eiben & Smith 2007: 49.)

The three different kinds of crossover operations that were presented (one-point, N-point, uniform) in Figures 8, 9 and 10 all represents a different kind of strategies. However all crossover operations do work on the principle of randomly mixing parents to produce off-spring. The N-point crossover shows a trend of keeping together sections that are located close to each other in the representation, where as when  $N_{cr}$  is odd (e.g. in one-point crossover) it shows a strong will of preserving the location of genes in the opposite ends of the chromosome. This phenomena is known as **positional bias** and is the most important property of the N-point crossover. The uniform crossover however shows a tendency of mixing 50 % of the loci on the parents, resulting in what is known as **distributional bias**. Even though it cannot be exactly defined which one of the crossover operators is the most suitable in every case, one must know the different properties of the crossover operators in order to select the most appropriate one (Eiben & Smith 2007: 49).

#### 3.2.3. Selection and GA types

In the previous sections the two different operators mutation and crossover have been discussed, where the maximum number of affected individuals by the operators have been two. In this section the **selection operator** will be presented and the focus will be on the entire population, where new terms arise such as population size  $\mu$  and offspring size  $\lambda$ , and also two different types of genetic algorithms will be presented.

For every selection operator that is applied, one must also define how the operator is used based on the current GA model. There are mainly two GA models that will be discussed:

- A generational model.

- A steady-state model.

The generational model has the property of replacing its entire population with an offspring, called the **next generation** that implies ( $\lambda = \mu$ ). More thoroughly described each iteration starts with a population of size  $\mu$ , and by creating a mating pool from the parents, GA operators are applied to the mating pool to create an offspring population where  $(\lambda = \mu)$ . The **steady-state model** on the other hand, does not change the entire model at once which implies that  $(\lambda < \mu)$ , and the so called **generational gap** that occurs is the percentage of the population that is replaced, which equals  $(\lambda/\mu)$ .

With the GA models subject briefly covered the selection operator types listed below will be presented, where the **parent selection** algorithms applies to the beginning of each generation as showed in Figure 5, and defines the parents that will be used for recombination and/or mutation. The **survival selection** algorithm however define the individuals that will survive for the next generation, and is executed last as shown in Figure 5. It must be mentioned that in some cases, individuals that survive can be the whole bred offspring if  $(\lambda = \mu)$ .

- Parent selection.

- Fitness proportional selection.

- Ranking selection.

- Tournament selection.

- Survival selection.

- Age-based replacement

- Fitness-based replacement

The **fitness proportional selection (FPS)** states that the selection probability of an individual depends on the absolute fitness values of the individuals compared to the absolute fitness values of the whole population, where for each individual the probability that it will be selected for mating is equal to equation 2,

$$P_{i} = f_{i} / \sum_{i=0}^{\mu} f_{i}$$

(2)

where  $f_i$  is the fitness of an individual and  $P_i$  is the probability that it will be selected. The FPS however have some problems, one example is that outstanding individuals (i.e. individuals with very high fitness) will take over the population very quickly, resulting in premature convergence. Another problem with the FPS occurs when the fitness values of the population are close together, meaning that there is no selection pressure.

The **ranking selection** algorithm instead implements selection pressure, by sorting the population on the basis of fitness, and then applying selection probabilities based on the rank of the individuals. The ranking numbers can be mapped to selection probabilities in different ways, e.g. by decreasing the selection probability linearly or exponentially. The common formula for mapping selection probabilities based on rank is described in equation 3,

$$P_{lin-rank}(i) = \frac{(2-s)}{\mu} + \frac{2i(s-1)}{\mu(\mu-1)}$$

(3)

where  $P_{lin-rank}(i)$  is the selection probability of the individual and s is a user-defined parameter where  $(1.0 < s \le 2.0)$  that regulates the selection pressure of the algorithm. The selection pressure of the linear ranking is however limited, since the maximum value of s is 2. This limitation originates from the assumption that an individual of median fitness should have one chance (on average) to reproduce. The exponential ranking algorithm in equation 4 allows instead a higher selection pressure and emphasizes more on selecting an individual of above–average fitness,

$$P_{exp-rank}(i) = \frac{1 - e^{-i}}{c} \tag{4}$$

where c is a normalisation factor that is function of the population size, and must be chosen so that the sum of probabilities is unity.

**Tournament selection** is a popular algorithm due to its simplicity and lean use of computational resources. Simply by choosing K number of individuals randomly and selecting the one with the best fitness, one can effectively select new individuals for the mating pool without performing too complex algorithms. The selection pressure is easily regulated by varying the K parameter, but also by introducing a selection probability parameter  $P_{sel}$ . In most cases  $P_{sel} = 1$  leading to deterministic tournaments, but  $P_{sel}$  can also be less than one in stochastic versions of the tournament i.e.  $P_{sel} < 1$ . However, the selection probability parameter is not used in this thesis and will not be discussed further.

Age-based replacement focuses only on the number of generations a particular individual have existed, and for the most simplest cases the whole population is replaced, because the generated new population is of the same size as the old population i.e.  $\mu = \lambda$ . The age-based replacement can be defined as *Time To Live* (TTL) and defines the number of generations a single individual can exist. In case that the new population produced is smaller than the old population ( $\lambda < \mu$ ), the individuals that will be added to the new population will be the youngest individuals (i.e. those that have existed for the least amount of generations). Nonetheless, the age-based replacement technique is not used in this thesis.

**Fitness–based replacement** focuses merely on the fitness of the particular individuals as the name states. After breeding, both parents and offspring exist in a common pool, which size is  $\lambda + \mu$ , from where they can be selected for survival. One can implement **elitism** in a GA, by conserving the most fitted individuals in the population. Another implementation is the **replace worst** scheme, where the least–fitted individuals are selected for replacement. However these two schemes may cause the GA to lead to premature convergence resulting in a stall at a local optimum. (Eiben & Smith 2007: 58-66)

### 4. EMBEDDED SYSTEMS

This chapter gives the reader an introduction to different kinds of embedded devices available on the market along with their functionality and benefits, where the Field– programmable Gate Arrays (FPGAs) will be more thoroughly discussed. The Altera DE4 development board will also be introduced along with the EtherTester software (developed by Olli Rauhala) that serves as the foundation for the EthGA software that has been developed by the author.

Embedded systems is an advanced field of technology, where the number of different applications and implementations are vast. In the early days signal processing was achieved using merely analogue components, but as for today most signal processing is handled by digital logic (i.e. with an embedded system). The founding component for an embedded system is shared among all manufactures, namely the transistor, a semi–conductor that was developed in the late 1940s. The invention of the transistor soon led to the development of discrete digital logic gates (Boolean logic) incorporated into integrated circuits (IC), which enabled the manufacturing of programmable logic devices (PLD), processors and application specific integrated circuits (ASIC).

PLDs are often used when the functionality of the system is too complex for a simple discrete logic IC implementation. The benefit of PLDs is re–programmability (in most implementations) that is not possible in a discrete logic system without re–routing the components and/or the wiring on the printed circuit board (PCB). There are mainly three different types of programmable logic: (*a*) the simple programmable logic device (SPLD), (*b*) the complex programmable logic device (CPLD) and (*c*) the field programmable gate array (FPGA) which will be discussed more thoroughly in Section 4.1. The SPLD has a very simple programming capability and was introduced before the CPLD and the FPGA. A PLA–architecture SPLD has cross–points which can be connected through programming, which connects the inputs to the AND gates and the AND gates to the OR gates located inside the IC. However the PLA–architecture can only be programmed once but the IOs can be connected to each other afterwards by re–routing the wires to the IC. There are

also other architectures of the SPLD e.g. the programmable array logic (PAL) and generic array logic (GAL) architectures. The PAL architecture is simpler than the PLA consisting of only one AND plane, and can also be programmed once. The GAL architecture on the other hand implements the electronically erasable programmable read–only memory (EEPROM) that enables re–programmability. A CPLD is an improvement of the SPLD, and can be considered as an implementation of several SPLDs.

Another set of programmable devices in the embedded family are the processors, where the most common types are: (a) the Microprocessor ( $\mu$ P), (b) the Microcontroller ( $\mu$ C) and (c) the Digital signal processor (DSP). The microprocessor is not developed to solve specific problems but to apply to a vast amount of different tasks, resulting in a lack of optimization due to this generalisation. It is integrated in a single circuit that is programmable through software. The microcontroller is an extension of the microprocessor by embedding interfaces (e.g. UART RS–232) and memory registers/controllers inside the microprocessor. It reduces the implementation costs compared to creating a similar microprocessor system with external interfaces added to a PCB, but limits the flexibility due to the limitations embedded inside the IC.

A DSP is an application specific processor that is designed for real-time complex signal processing algorithms, such as the fast fourier transorm (FFT) for example. Hardware multipliers and hardware loops are often embedded in the DSP and can be accessed trough a programming interface. In a standard microprocessor these operations would be performed using shift operations, additions and software loops. (Grout 2008: 21-22)

An application–specific integrated circuit (ASIC) is an IC that is built for a specific task, that could incorporate any of the functions and components previously mentioned in this chapter into a single chip. The ASIC design is sealed after manufacturing resulting in the loss of modification options. However, the ASIC can be optimized by scaling down the power consumption to only consume what the design needs, in contrast to a general–purpose microprocessor. The advantages of an ASIC solution arises when a certain configuration is used vastly, and that particular can ASIC can be manufactured in great num-

bers, hence lowering the production costs. (Deschamps, Bioul & Sutter 2006: 252)

## 4.1. Field–programmable gate arrays

What differs the FPGAs from the previously mentioned embedded systems in Chapter 4 is the configuration flexibility along with their fairly low power consumption. Since the capacity of the FPGAs are constantly increasing one can program them to perform almost any task that for example a microprocessor or a DSP could perform, and also implement additional functions/tasks besides the processor. It is also possible to perform operations in parallel which enhances the computational speed compared to a microprocessor, where almost all instructions are executed sequentially. FPGAs can often be used as the prototyping platform for products that will eventually be created as ASIC chips, however FPGAs are also often used in the final products, depending on the desired performance, re–programmability, development and production costs. Nowadays FPGAs are found in a vast amount of both consumer and industrial applications such as in automotive systems, wireless communication, signal processing, aerospace, defence, medical imaging and data security only to name a few. (Deschamps et al 2006: 258) (Stavinov 2011: 7)

At the moment the FPGA market holds two leading vendors, namely Altera and Xilinx which in year 2011 held over 90 % share of the total FPGA markets. These two companies both provide a wide range of FPGA families, that offer high flexibility and both low–cost and high–performance solutions. There are also smaller companies e.g. Actel/Microsemi corporation, Lattice Semiconductor Corporation, Achronix Semiconductor and Tabula, which are focusing on different niches with their own FPGA products. (Stavinov 2011: 3-5)

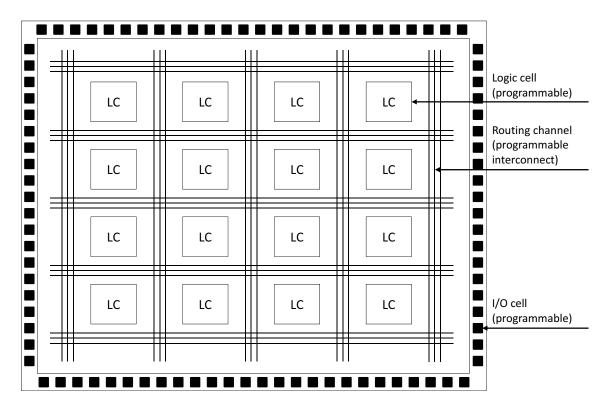

Since all FPGA vendors have their own type of FPGA architectures, this thesis will not go into details at everyone of them. However a generic model of an FPGA architecture is presented in Figure 11, where a logic cell (LC) can be programmed to perform a certain logic operation (e.g. AND/OR/NOT). The LCs can be connected to programmable I/O

cells and other LCs trough programmable interconnect routing channels. The underlying structure of the LCs, I/O cells and routing channels vary between each vendor and FPGA family, along with the functions each object can provide. (Grout 2008: 28-29).

**Figure 11.** Architecture of a generic FPGA, where the underlying structure of the objects: *(a)* logic cell, *(b)* routing channel and *(c)* I/O cell will vary between different FPGA vendors. (Adapted from Grout 2008: 29.)

Nowadays most embedded software developers use the C programming language to manipulate the functionality of a microprocessor, microcontroller or DSP. A microprocessor follows a sequential workflow where a program pointer is used to determine the instruction to be executed. This implies that the processor will work in a non-parallel manner, executing instructions step-by-step (in most cases). The FPGA on the other hand is programmed by a hardware description language (HDL) which can be used in creating parallel hardware components. The developer creates hardware modules, which serve a specific purpose and are connected together inside a top-level design. There are for the moment two main HDLs in use: (*a*) VHDL (very high–speed integrated circuit hardware description language) and (*b*) Verilog–HDL. VHDL was developed in 1980 by the United States Department of Defence (DoD) and merged into the IEEE 1076 standard in 1987, whose most recent version is the IEEE Standard 1076–2002. Verilog–HDL was released in 1983 by Gateway Design System Corporation and was also merged into a IEEE standard, namely IEEE 1364–2001. Both VHDL and Verilog–HDL serve the same purpose; to provide the developer a text–based language in which he/she can describe the hardware. The syntax and the structure of the two languages are different. The choice of the language depends partly on the programmers previous experience and personal preference, but also the results of the HDLs impact on the desired FPGA. (Grout 2008: 193-196).

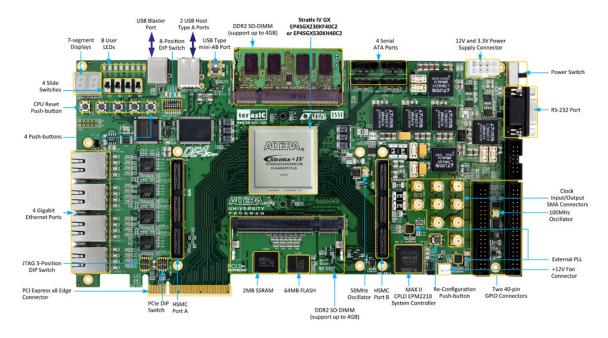

## 4.1.1. Altera DE4

The Altera Developement and Education Board 4 (DE4) shown in Figure 12 was used in this thesis as the hardware platform for the developed EtherTester and EtherTesterGA software. It features the Altera Stratix IV GX FPGA EP4SGX230C2 with the specification listed in table 1. The DE4 was chosen because it holds 4 Gigabit Ethernet ports, which enables a very high frame transmission rate necessary for the case studies performed in Chapter 6. It also features a 100 MHz oscillator, which frequency can be even further increased by using phase locked loops. The EtherTester software described in Section 4.1.2 runs on the standard 100 MHz clock frequency.

**Figure 12.** The Altera Developement and Education Board 4. (Terasic Technologies Inc. 2013).

**Table 1.** Altera Stratix IV GX EP4SGX230C2 specifications. (Terasic Technologies Inc.2010: 9)

| Unit                                          | Number of |

|-----------------------------------------------|-----------|

| Logic elements (LEs)                          | 228,000   |

| Total memory                                  | 17,133 kb |

| 18x18 multipliers blocks                      | 2         |

| PCI Express hard intellectual property blocks | 744       |

| User I/Os                                     | 8         |

# 4.1.2. EtherTester software

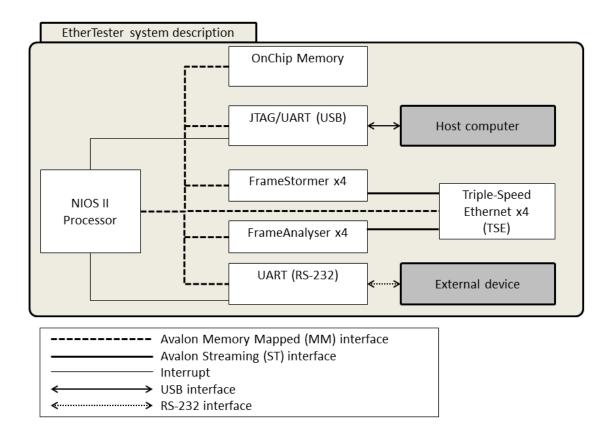

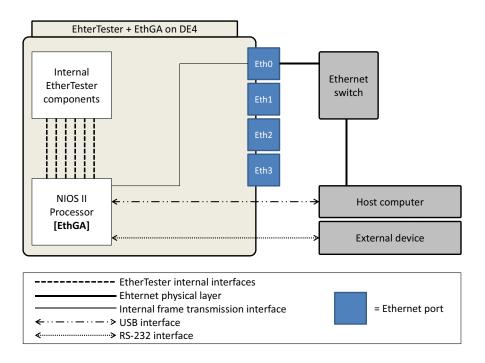

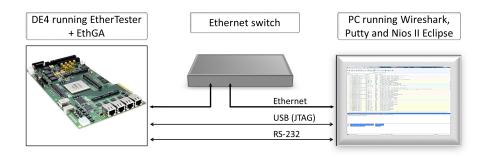

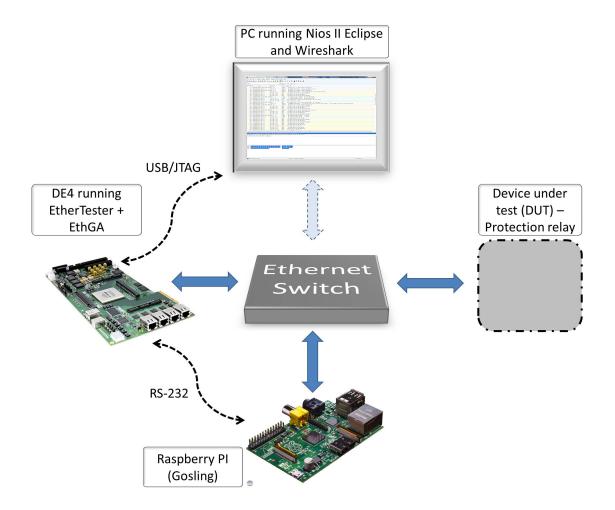

Olli Rauhala have developed the *EtherTester* software for the DE4, which enables it to send, receive and analyse Ethernet frames at gigabit speeds. Figure 13 presents the system description of the EtherTester, where the NIOS processor is the main component that controls the other hardware components. The NIOS processor is a hardware–described

microprocessor developed by Altera, which is embedded into the FPGA and programmed with the embedded C–language (like many other microprocessors). All other components in EtherTester are written in Verilog, and some of them use Altera's own Intellectual Property libraries. The EtherTester is controlled from a host computer with the JTAG/UART (Joint test action group/Universal asynchronous receiver transmitter) interface physically connected over USB. This control type is terminal based using Altera's own software, and the JTAG/UART connection is also required when using Altera's intellectual property cores.

**Figure 13.** System description of Olli Rauhalas EtherTester software implemented on the DE4, where all components are written in Verilog and the NIOS processor controls the whole system. (Adapted from Rauhala 2013b: 3.)

The FrameStormer components handles all outgoing network traffic on the EtherTester, i.e. intended only for packet transmission. The FrameAnalyser component instead han-

dles all incoming network traffic i.e. packet reception. Both the FrameStormer and the FrameAnalyser components exist in a multiple of four, which is the number of Ethernet ports on the DE4. This enables each port to transmit, receive and analyse frames with a maximum frame size of 1600 octets. This configuration requires about 70 % of the system resources, but it can be reduced by decreasing the number of Ethernet ports in use. The microprocessor can also receive and transmit external commands through the RS–232 interface, this feature is explained more thoroughly in Section 5.1 where the EthGA software is described. The OnChip Memory component is used by the microprocessor, and is necessary for downloading and running C–code in the microprocessor.

# 5. PROTOTYPING, SIMULATION AND IMPLEMENTATION OF A GENETIC ALGORITHM

This chapter presents the development stage in the practical part of this project; namely to develop, simulate and implement a genetic algorithm, in a NIOS microprocessor instantiated in an FPGA chip, called as the EthGA software. The main purpose of the *EthGA* is to generate Ethernet frames, which will be transmitted to a Device–Under–Test (DUT). The impact of these frames on the DUT will be evaluated by another device that will provide feedback to EthGA. This feedback serves as the fitness score for the GA and as a result the population will evolve by time to generate the most harmful Ethernet frames for the DUT. The complete functionality of EthGA is presented more thoroughly in Section 5.1 and the test cases are presented in Chapter 6.

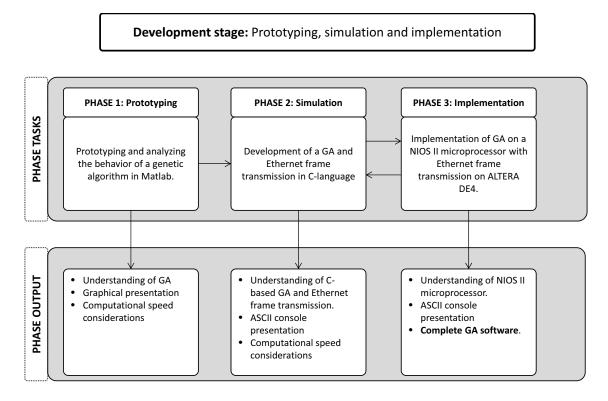

To produce high quality software, one must understand the concepts and functions that the software will implement. Therefore the prototyping, simulation and implementation mentioned in Figure 14, are needed in system development. Nonetheless this thesis emphasises mostly on the latter phases due to their importance to the project, and the prototyping phase will only be presented briefly.

In the prototyping phase a genetic algorithm named *BasicGA* was developed in Matlab to analyse the behaviour of the GA on a multi–peaked 1–dimensional landscape, to make the author more acquainted with the programming of GAs. Matlab was chosen due its large number of additional packages, matrix operations and graphical presentation system, which might speed up the prototyping phase. The prototype was developed in one week with the properties listed in Table 2, and the fitness function used is presented in equation 5,

$$fit(\mathbf{x}) = (\sin(5 * \mathbf{x} * 0.01) + (\mathbf{x} * 0.001) * 2 + \cos(3 * \mathbf{x} * 0.01)) - \exp((\mathbf{x} * 0.01)/15)$$

(5)

where x equals to a particular chromosome in the population.

**Figure 14.** The different phases of the development stage, where the purpose and the outputs of each phase are presented.

**Table 2.** Properties of the genetic algorithm used for prototyping in Matlab, where the purpose of the algorithm is to find the maximum of a multi–peaked 1–dimensional land-scape.

| Parameter           | Value                    |

|---------------------|--------------------------|

| Chromosome type     | 11–bit binary            |

| Population size     | 20                       |

| Selection           | Roulette                 |

| Crossover           | Uniform                  |

| Mutation rate       | 1 %                      |

| Elitism             | No                       |

| Fitness Landscape   | $0 \geq x \leq 2^{11}-1$ |

| Goal                | Max of equation 5        |

| Output presentation | Graphical & numerical    |

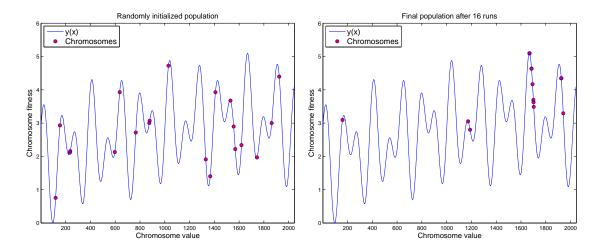

The results from a simulation with the parameters given in Table 2 is shown in Figure 15, with the initial population in the left graph and the final population after 16 runs in the right graph. The algorithm stopped when one of the individuals had obtained the largest possible value from the fitness function within the range of the fitness landscape. However the validity of this test can be questioned, since the 11-bit representation of the chromosome concludes that an individual can only take  $2^{11} = 2048$  different values, resulting in a quite large probability of an individual obtaining the best fitness value at the random initialisation. Several tests showed that the time needed to find the best solution, could range between 1 and over 1000 runs. This concludes that fitness of the individuals at initialisation, plays an important role in finding the best solution in the shortest time possible. Multiple tests also showed that with elitism, the algorithm had a high probability of suffering from a premature convergence, leaving the individuals stuck at one of the lower peaks. This could be avoided by increasing the mutation rate, giving the individuals a chance to escape the lower peaks. It can also be concluded that a GA performs well at quickly finding the areas which gives the best fitness values, but not as well in quickly finding the best possible solution.

**Figure 15.** Test results of a BasicGA simulation with the parameters from Table 2, with the randomly initialized population in the left graph and the final population after 16 runs in the right graph.

# 5.1. Simulation of EthGA on a PC-computer

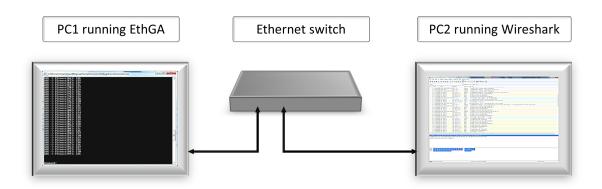

With the knowledge obtained from the prototyping phase, the development continued to the simulation phase, where the EthGA is written in C–language on a PC–computer (running Windows 7). The C–language was chosen because it is the language that the NIOS microprocessor uses, and it also supports transmission of hand–crafted Ethernet frames using the WinPCap library developed by Riverbed Technology. The pseudo–code for EthGA is presented in Figure 16, which describes the high–level functionality. In the simulation phase, there was no external device attached to the computer, and EthGA simulated the fitness by the so called all–ones problem, where a higher occurrence of '1' bits in a chromosome gives a higher fitness value. The usage of the external device is presented more thoroughly in Chapter 6. What differs EthGA from BasicGa is the functionality of the software: EthGA includes the transmission of Ethernet frames (i.e. individuals) and also a wider selection of crossover operations and parent selection algorithms. A complete list of features in EthGA is showed in Table 3.

```

function MAIN

{

INITIALIZE Ethernet frame specifications

INITIALIZE population stochastically OR according to GOOSE/SV/MMS protocols

WHILE (TERMINATION CONDITION IS NOT SATISFIED)

1. CALL FITNESS

2. SELECT parents

3. CROSSOVER pairs of parents

4. MUTATE the resulting offspring

END WHILE;

}

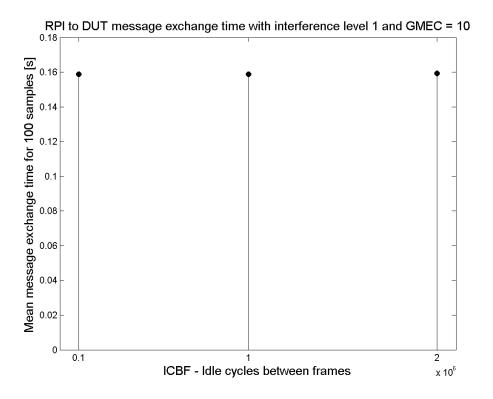

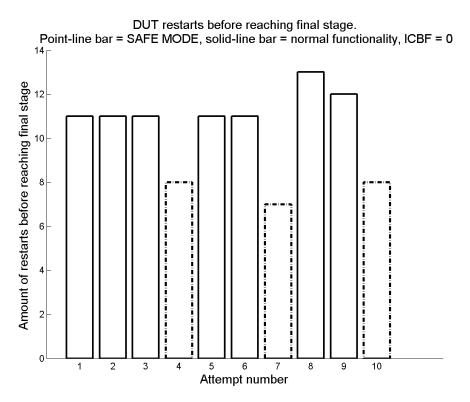

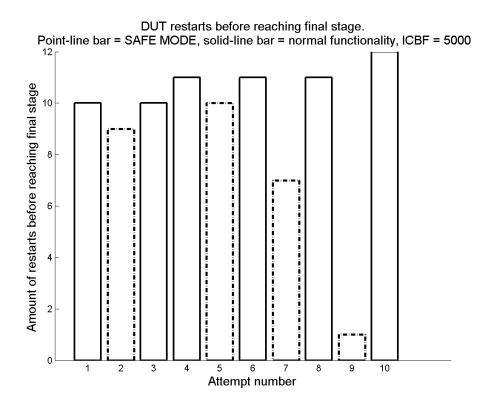

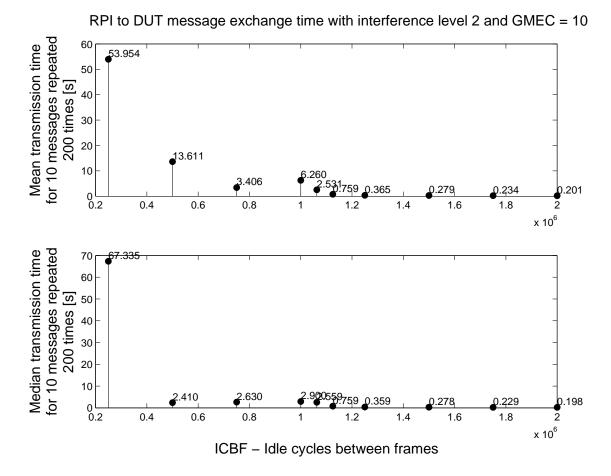

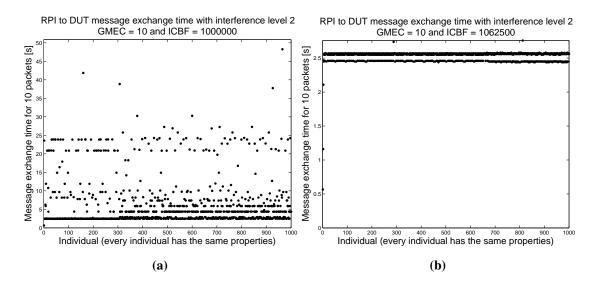

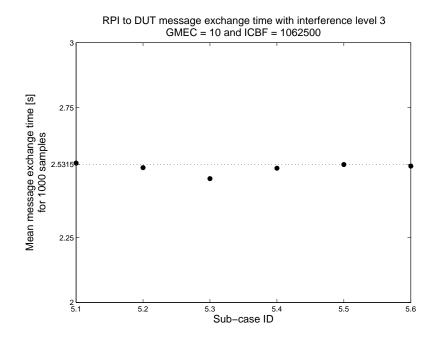

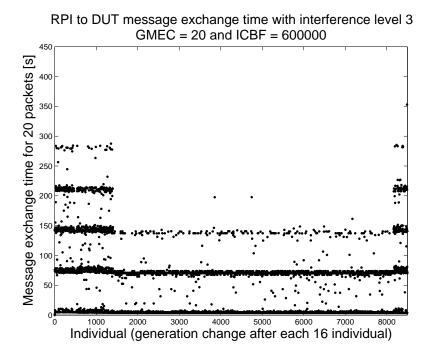

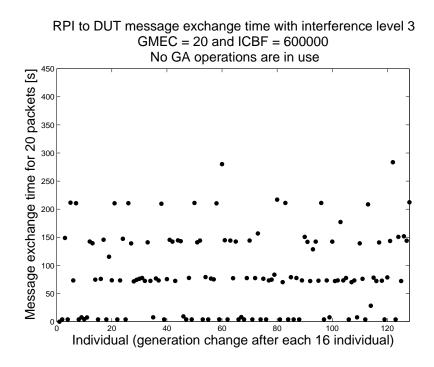

function FITNESS