# On Object Oriented Non-Deterministic Supervisory Control

## Martin Fabian

Ph. D. Thesis Technical Report 282, December 1995

Control and Automation Laboratory Department of Signals and Systems Chalmers University of Technology Sweden

In memory of Terész and János Fábián

## Abstract

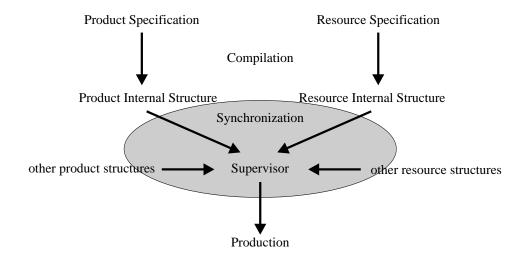

Implementation of complex discrete event fabrication processes can be considerably simplified by use of general reusable software modules representing the physical components. At the same time, construction of the control system can be facilitated by use of formal methods for automatic generation of the control laws. These two aspects can be joined into a general concept with object-oriented modeling and control law synthesis as foundations. The goal is to allow an operator to specify operation lists describing the required sequences of operations for the manufacturing of the product, independently of constraints given by a specific plant. With a suitable model of the capabilities and constraints of the resources of that plant, a product route can be automatically generated from the operation list. Such a product route describes all available paths through the system, for each type of product, irrespective of any other type of product that may be simultaneously present within the production system. Given a set of product routes and a model of the plant, control laws guaranteeing production according to those product specifications can be synthesized.

Based on the supervisory control theory, using interleaved product routes as specification, we show how such control laws can be synthesized. An added complexity is that the a specification becomes non-deterministic, in the sense that the same string of events can lead to different system states. We show that the supervisory control theory can be used with non-deterministic specifications assuming certain properties. We also describe an object-oriented modeling approach to discrete event fabrication processes. It is shown that the properties that have been defined as necessary for the non-deterministic supervisory approach are immediate by the modeling approach. Thus, we show that the approach to non-deterministic supervisory control can be combined with object-oriented modeling techniques, and so we have a powerful framework for implementing control of large and complex discrete event fabrication processes.

**Keywords.** Supervisory Control, Object-Oriented Modeling, Flexible Manufacturing, Finite State Automata

## **Published Papers**

The work presented in this thesis is based on the following technical reports, papers and conference presentations.

- 1. Fabian, M., B. Lennartson, Control of Manufacturing Systems; An Object Oriented Approach, 7th IFAC/IFIP/IFORS/IMACS/ISPE Symposium on Information Control Problems in Manufacturing Technology, INCOM'92, Toronto, Canada, May 1992.

- 2. Fabian, M., B. Lennartson, Object Oriented Structuring of Real Time Control Systems, 31st IEEE Conference on Decision and Control, CDC'92, Tuscon, Arizona, December 1992.

- 3. Fabian, M., Reusable Software Components for Structuring Real-Time Control Systems, Technical Report 143L, Licentiate Thesis, Control Engineering laboratory, Chalmers University of Technology, Göteborg, Sweden, January 1993.

- 4. Fabian, M., B. Lennartson, *Distributed Objects for Real Time Control Systems*, 12th IFAC World Congress, Sydney, Australia, July 1993.

- 5. Fabian, M., B. Lennartson, *Petri Nets and Control Synthesis; An Object Oriented Approach*, 3rd International Intelligent Manufacturing Systems Symposium, IMS'94, Vienna, Austria, June 1994.

- 6. Fabian, M., B. Lennartson, Object-Oriented Supervisory Control with a Class of Nondeterministic Specifications, 33rd IEEE Conference on Decision and Control, CDC'94, Buena Vista, Florida, December 1994.

- 7. Fabian, M., B. Lennartson, A Class of Nondeterministic Marked Specification for Supervisory Control, 3rd SIAM Conference on Control and Its Applications, St Louis, Missouri, USA, April 1995.

- 8. Adlemo, A., S-A. Andréasson, M. Fabian, P. Gullander, B. Lennartson, *Towards a Truly Flexible Manufacturing System*, Computer Engineering Practice, Vol 3, No 4, 545-554, April 1995.

- 9. Tittus, M., M. Fabian, Automated Generation of Plant Specific Recipes in Batch Control, ICCI'95, Hong Kong, June 1995

- 10. Fabian, M., B. Lennartson, A Class of Nondeterministic Specification for Supervisory Control, 3rd IFAC European Control Conference, ECC'95, Rome, Italy, September 1995.

- 11. Fabian, M., B. Lennartson, *Petri Net Constructs for High Level Operation Lists*, 8th IFAC/IFIP/IFORS/IMACS/ISPE Symposium on Information Control Problems in Manufacturing Technology, INCOM'95, Beijing, China, October 1995.

- 12. Fabian, M., P. Gullander, B. Lennartson, S-A Andréasson, A. Adlemo, *Dynamic Products in Control of an FMS Cell*, 8th IFAC/IFIP/IFORS/IMACS/ISPE Symposium on Information Control Problems in Manufacturing Technology, INCOM'95, Beijing, China, October 1995.

- 13. Fabian, M., B. Lennartson, Applying Supervisory Control Theory to Discrete Event Systems Modeled by Object Oriented Principles, INRIA/IEEE Conference on Emerging Technologies and Factory Automation, ETFA'95, Paris, France, October 1995.

- 14. Tittus, M., M. Fabian, B. Lennartson, Controlling and Coordinating Recipes in Batch Applications, 34th IEEE Conference on Decision and Control, CDC'95, New Orleans, Louisiana, USA, December 1995.

- 15. Fabian, M., B. Lennartson, Applying Supervisory Control Theory to Discrete Event Systems Modeled by Object Oriented Priniples; How and When, Internal Report CTH/RT/I-95/008, Control Engineering Laboratory, Chalmers University of Technology, Göteborg, Sweden, 1995.

These will be referenced as, for instance, [14] in the following text

## Acknowledgements

No man is an island.

This work would not have been possible without the support, guidance, inspiring influence, motivation, help, etc., of many other individuals. The first to mention is, of course, my mentor and supervisor Dr. Bengt Lennartson. I am grateful to him for his time invested in me and this work, and for believing in me, even at times when I myself did not. He also pushed me on when it was necessary, and often came up with the right phrase to trigger my thoughts in the right direction; I think, sometimes without even understanding my incoherent ramblings at all. His help in editing this thesis I consider invaluable. Thank you, Bengt. (Chapter 5 was a tough one, wasn't it?)

Dr. Michael Tittus (yes, you're a *Doctor* now, Michael) has been a great counterpart in many discussions. He also helped out in the editing process, and generally made lots of fun jokes (well, *some* of them at least). Thanks, Michael

Professor Bo Egardt pointed out several errors in the propositions and proofs. He asked the innocent question that revealed a serious error. Suddenly it seemed I would not even make it due to this. Thanks (!?). In the end it all worked out, and I am thankful for the all the support. (No tennis game, though, please.)

Dr. Christos Cassandras, of University of Massachusetts at Amhurst, took the time to read this thesis and to explore some of its inner regions, to oppose me so I could defend myself for the dissertation. Thank you. Hopefully, I did get all the pieces together of this puzzle I am laying, and hopefully I put them in their right places with their right sides up.

Professor Bo Egardt, Dr. Bengt Lennartson, Dr. Michael Tittus and me, we are all at the Control Engineering Department. Of course, we are not alone there. All you people at the department have, in one way or another, contributed to this work, though you may not know it. Gunnar Berg, Claes Breitholtz, Catharina Forssén, Adam Lagerberg, Annika Leonard, Torbjörn Liljenvall, Claës Lindeborg, Olof Lindgärde, Ulla-Britt Nilsson, Stefan Petterson, Bengt Schmidtbauer, Lars Wallin, Torsten Wik.

The following individuals, in no particular order, deserve a special "thank you", for various reasons briefly mentioned.

Lars Jansson for keeping the computers going and the dog happy, and for letting me use the car when that uncontrollable event occurred. Lemmy, for inducing that extra strength when needed. Thommy Ekelund, for helping me get rid of that strength. Per Gullander, for all the help with the GeRMs (hope they haven't spread). Domo arigato, gozaimasu. Bonzo the Dog, for just being so happy all the time (sometimes *too* happy, Lars!). Kopparbergs Elk, for the inspiration.

Lars Jansson also made the illustration of what supervisory control can turn out to be, if we do not watch out.

Last, but certainly not least, my life companion Katarina Johnsen. She understood that I had to work so much, without understanding with what. So many things had to be held over, I will make it up to you now, love.

If I forgot someone, thank you too.

And, Tony-you know what you shouldn't do.

August 10, 2000

# Contents

| 1 | $\mathbf{Intr}$            | Introduction |                                   |  |      |  |  |

|---|----------------------------|--------------|-----------------------------------|--|------|--|--|

|   | 1.1                        | An Ex        | xample System                     |  | . 3  |  |  |

|   | 1.2                        | Object       | t-Oriented Modeling               |  | . 4  |  |  |

|   |                            | 1.2.1        | Internal Resources                |  | . 4  |  |  |

|   | 1.3                        | Distril      | buted Product Specification       |  | . 6  |  |  |

|   |                            | 1.3.1        | High-Level Product Specification  |  | . 6  |  |  |

|   |                            | 1.3.2        | Interleaving                      |  | . 9  |  |  |

|   | 1.4                        | Super        | visory Control                    |  | . 10 |  |  |

|   |                            | 1.4.1        | Global Specification              |  | . 11 |  |  |

|   |                            | 1.4.2        | Event Connection                  |  | . 12 |  |  |

|   |                            | 1.4.3        | The Supervisor                    |  | . 13 |  |  |

|   |                            | 1.4.4        | The Controller                    |  |      |  |  |

|   | 1.5                        | Object       | etives of this Work               |  |      |  |  |

|   |                            | 1.5.1        | Contributions                     |  | . 15 |  |  |

|   |                            | 1.5.2        | Assumptions and Restrictions      |  | . 15 |  |  |

|   |                            | 1.5.3        | Thesis Outline                    |  | . 16 |  |  |

| 2 | Finite Transition Machines |              |                                   |  |      |  |  |

|   | Finite Transition Machines |              |                                   |  |      |  |  |

|   | 2.1                        |              | erse of Discourse                 |  |      |  |  |

|   | 2.2                        |              | s and Tracesets                   |  |      |  |  |

|   |                            | 2.2.1        | Tracesets                         |  |      |  |  |

|   |                            | 2.2.2        | Accessibility                     |  |      |  |  |

|   |                            | 2.2.3        | Strings and Languages             |  |      |  |  |

|   | 2.3                        |              | ement And Subprocesses            |  |      |  |  |

|   |                            | 2.3.1        | Subprocesses                      |  |      |  |  |

|   |                            | 2.3.2        | Refinement                        |  |      |  |  |

|   | 2.4                        | -            | ations On Processes               |  |      |  |  |

|   |                            | 2.4.1        | General Operations                |  |      |  |  |

|   |                            | 2.4.2        | Operations On Subprocesses        |  |      |  |  |

|   | 2.5                        |              | ition Machine Modeling Approaches |  |      |  |  |

|   |                            | 2.5.1        | The Failures Model                |  |      |  |  |

|   |                            | 2.5.2        | The Trajectory Model              |  |      |  |  |

|   |                            | 2.5.3        | Automata Equivalence              |  |      |  |  |

|   |                            | 2.5.4        | Event Generation                  |  |      |  |  |

|   | 26                         | Chapt        | tor Summary                       |  | 62   |  |  |

| 3  | Super                | rvisory Control 67                                  |  |  |  |  |

|----|----------------------|-----------------------------------------------------|--|--|--|--|

|    | 3.1 I                | $\operatorname{ntroduction}$                        |  |  |  |  |

|    | 3.2                  | The Basic Supervisory Control Theory                |  |  |  |  |

|    | 3.3                  | The Input/Output Interpretation                     |  |  |  |  |

|    | 3.4 N                | Non-deterministic Supervisory Control               |  |  |  |  |

|    |                      | 3.4.1 Controllability, Completeness and Conformity  |  |  |  |  |

|    | 3                    | 5.4.2 Inverse Properties                            |  |  |  |  |

|    | 3                    | 3.4.3 Blocking and Nonblocking                      |  |  |  |  |

|    | 3.5                  | Some Notes on Non-deterministic Supervisory Control |  |  |  |  |

|    |                      | Chapter Summary                                     |  |  |  |  |

|    | a                    |                                                     |  |  |  |  |

| 4  | _                    | rvisor Synthesis 103                                |  |  |  |  |

|    |                      | Supremal Elements                                   |  |  |  |  |

|    |                      | The Supremal Trim Subprocess                        |  |  |  |  |

|    |                      | The Complete Accessible Subprocess                  |  |  |  |  |

|    |                      | The Supremal Complete and Trim Subprocess           |  |  |  |  |

|    | 4.5 (                | Chapter Summary                                     |  |  |  |  |

| 5  | Conti                | rol of Discrete Event Fabrication Processes 135     |  |  |  |  |

|    |                      | ntroduction                                         |  |  |  |  |

|    |                      | Object Oriented Resource Modeling                   |  |  |  |  |

|    |                      | Product Descriptions                                |  |  |  |  |

|    |                      | 5.3.1 High-Level Operation Lists                    |  |  |  |  |

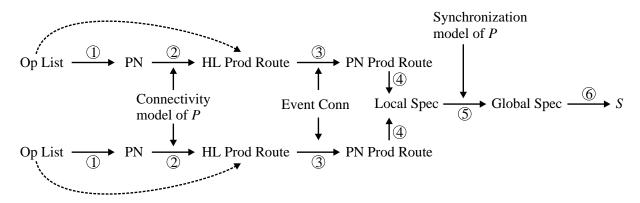

|    |                      | From Operation List to Final Specification          |  |  |  |  |

|    |                      | 5.4.1 Resource Allocation                           |  |  |  |  |

|    |                      | 5.4.2 Event Connection                              |  |  |  |  |

|    | _                    | 5.4.3 Local and Global Specifications               |  |  |  |  |

|    |                      | Applying the Theory                                 |  |  |  |  |

|    |                      | Chapter Summary                                     |  |  |  |  |

|    | 0.0                  | onapter Summary                                     |  |  |  |  |

| 6  |                      | ication Examples 165                                |  |  |  |  |

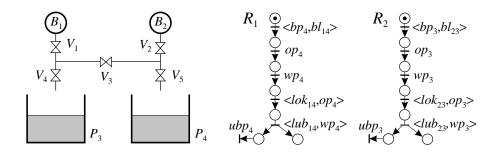

|    | 6.1 A                | Assembly System                                     |  |  |  |  |

|    |                      | Batch Process                                       |  |  |  |  |

|    | 6.3 N                | Manufacturing System                                |  |  |  |  |

| 7  | Conc                 | Conclusions                                         |  |  |  |  |

| Δ  | Basic Set Results 18 |                                                     |  |  |  |  |

| 71 |                      | Singular Sets                                       |  |  |  |  |

|    |                      | _                                                   |  |  |  |  |

|    |                      | Mappings                                            |  |  |  |  |

|    |                      | Sets of Sets                                        |  |  |  |  |

|    | A.4 S                | Set Differences                                     |  |  |  |  |

| R  | Proof                | f of Lomma ??                                       |  |  |  |  |

## Chapter 1

## Introduction

As pointed out by Fox (1992), modern corporations in the industrialized world must seek new paths to be able to compete in the coming decade. These paths ought to result in safe and efficient ways to manufacture customized, high-quality, environmentally benign and technically advanced products. This calls for increasingly flexible manufacturing processes. However, industrial demands for a fast project-implement-run cycle, often limits both the generality and the flexibility of the designed systems. Due to the complexity of the problem, the resulting systems often become not only expensive but also inflexible, despite the fact that their components are themselves highly flexible.

The main reason for this is that the control system is heavily influenced by the product routes relevant at the time of implementation. Implementing only the required routes and no more, gives (in some sense) the minimum amount of work. This minimal work load is often at the cost, though, of decreased flexibility and reusability. For new product routes and for implementation of new systems, much (if not all) code has to be re-implemented. Thus, this approach would (in some other sense) really require a maximum amount of work. For instance, robots and machine tools can be used flexibly in a large variety of applications, while the control software that synchronizes these components most often cannot function with machine tools or products other than those it was designed for, see Sargent (1993). In order to lower costs and increase flexibility, we need a truly flexible manufacturing system that can be reused without the need to reprogram the controller whenever a change in production is introduced.

Flexibility can be incorporated on different time-scales. A long time-scale flexibility permits incorporation of new or different equipment within the system, without having to extensively reprogram the control system. Flexibility on a medium time-scale allows incorporation of new products within the manufacturing system, and flexibility on a very short time-scale permits rescheduling of the manufacturing system on-line. When implementing control of production systems, some high-level support for modeling is of a great advantage. This high-level support should provide means to build a system appropriate for all three levels of flexibility, described above.

Object-oriented modeling has shown to be a valuable tool for structuring complex systems and easing their implementation by providing general software components reusable in different applications with little or no alteration, see for instance Joannis (1992) and Jobling (1994). The systems resulting from object-oriented modeling consist of independent communicating modules. Thus, object-oriented modeling supports the incorporation

of new equipment, without extensive reprogramming of already functional modules. In this way, the long time-scale aspect of flexibility is supported.

Flexibility on the medium time-scale is supported by distributed product specification. Each product is an autonomous entity coexisting with other products simultaneously present within the system. However, we can certainly do without the added complexity of having to specify independent product routes with regard to other products that may be existing at the time of production. It is favorable to be able to specify a distinct product route irrespective of any other products, and have some underlying system tie it all together.

Finally, the automatic synthesis of control laws supports the very short time-scale aspect of flexibility. For the sake of reliability and safety of the constructed system, this synthesis should be supported by a rigid foundation of formal methods. Given an object-oriented model of the system and a number of independent product specifications, together with other specifications on the systems behavior, safe and correct control laws must be synthesized. Since a manufacturing system can be regarded as a discrete event process (DEP), this foundation of formal methods can be found in the supervisory control theory (SCT) initiated by Ramadge (1987) and Wonham (1987).

Being a relatively new discipline within control theory, DEPs have attracted much attention both in the systems modeling area and within the control-law synthesis field. Shlaer (1992) and Adiga (1993) describe methodologies of modeling DEPs, based on object-oriented approaches. A dynamic system is modeled as being composed of objects, whose dynamic behavior is expressed by state automata. These objects communicate by means of events representing state transitions. Ramadge (1987) and Wonham (1987) have, with the SCT, provided a unifying framework for synthesis of control laws for DEPs. Kumar (1991) and Balemi (1992), among others, have proposed their own variations of the SCT, based on different interpretations of the interaction between the controlling and the controlled processes. Giua (1991) bases an approach on Petri nets. Even so, until now there has been very little (possibly no) work done in merging the two domains of object-oriented modeling and supervisory control synthesis.

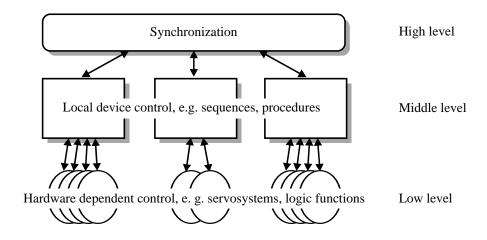

In this work we will show how object-oriented modeling of flexible manufacturing and assembly systems can be used with the SCT. The object-oriented modeling approach builds on the ability to identify and extract the general behavior of production resources into reusable software models, one for each different class of manufacturing device. These reusable models offer generalized functions on a high abstraction level, using lower level, specific instruction sequences to implement that behavior. In this way the synchronizing aspects of the required control will be separated from the control of the actual devices. The general, high-level functionality is represented by message driven DEPs. The messages are modeled as *events*. Thus, the *plant* to be controlled consists of a number of independent (but possibly coupled) DEPs, operating concurrently.

The specification of the product routes will likewise be given as DEPs. Each type of product can be specified without regard for any other product simultaneously present within the system, even though they may require use of the same processing equipment. The product routes thus specified encompass a subset of the events offered by the plant, not necessarily disjoint between different types of products. The concurrently executing product routes can thus be seen as a specification for the plant to exhibit a certain behavior, and it is up to some underlying control system, the *supervisor*, to guarantee

that this behavior is actually accomplished.

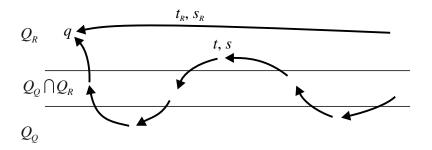

To synthesize a supervisor with a global view of the controlled system, the individual product route specifications have to be composed into a joint specification on the overall system. However, the products are to run asynchronously with respect to each other, though synchronously with respect to the plant. The concurrent sharing of the machining resources by the products can be modeled by *interleaving*, see Hoare (1985). The joint specification is the interleaving of the individual product route specifications, which leads to a *non-deterministic* specification; non-deterministic in the sense that a choice between several products simultaneously wanting to share a resource may arise. Only one of these will be allowed access to the shared resource, and the choice between them is non-deterministic. Non-determinism in this sense means that one and the same sequence of events may lead to any of a number of states. It will in this work be shown that the SCT is valid for the certain class of non-deterministic specification arising in systems as described above. Furthermore, a supervisor does exist and is algorithmically constructable.

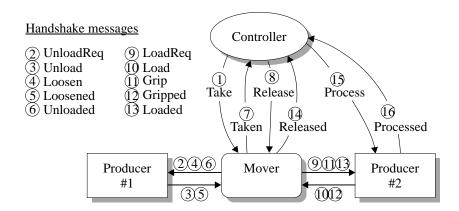

The resulting system contains three basic types of objects all described as DEPs; internal resources that are models of the actual machining equipment; product individuals that model the physical workpieces; and a controller that controls the behavior of the system, so as to fulfill the specification of having the products satisfactorily produced. The controller operates within the boundaries set by the supervisor, since the supervisor expresses all allowable routes through the system, satisfying the specifications.

To set the scene, we will begin with a brief introduction of the concepts to be presented in detail. This introduction comes in the form of an example system modeled by the object-oriented principles described in Chapter 5, with a supervisor synthesized by the variation of the supervisory control theory that will be presented in Chapters 3 and 4. First the example system is described, followed by a short description of the object-oriented modeling approach in general, and its application to the example system. Then some aspects of distributed product specification is discussed, and two products to be produced by the example system are introduced. Finally, the SCT algorithm is briefly described, and applied to the example system. The presented example will by no means be exhaustive, but we feel that this introduction gives a reasonable indication on how object-oriented modeling and the SCT can be used in practice, and, thus, motivates the remaining chapters of this thesis.

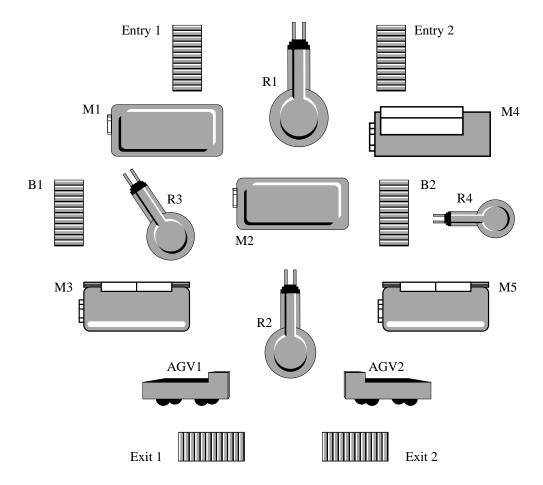

## 1.1 An Example System

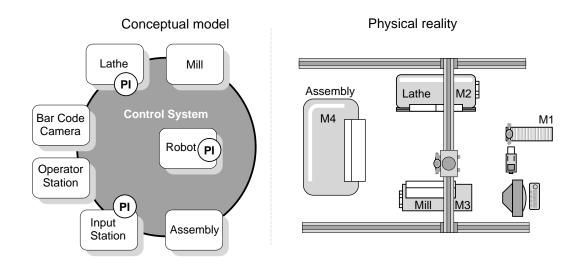

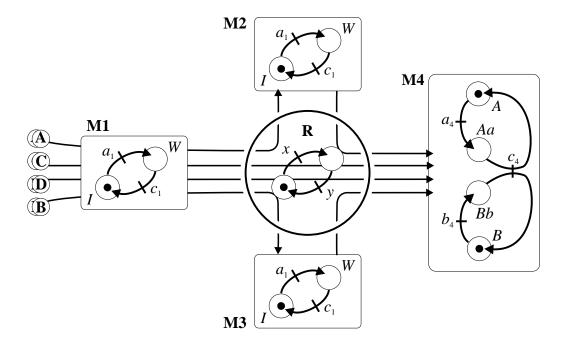

The example assembly system is shown schematically to the right in Figure 1.1. It consists of an input buffer, a lathe, a mill and an assembly unit. The system also contains a robot for loading and unloading the production resources. These are the resources that we will regard here. The operator station for manual supervision of the production, and the bar code reader that registers incoming workparts will not be considered.

The input buffer, M1, has a limited capacity of one product at a time. Products are loaded onto M1 on request, by some external source which is not modeled and is considered to be of infinite capacity. From M1 the products are transported by the robot to either the lathe, M2, or the mill, M3, depending on the specification of the product route. The assembly unit, M4, takes two different products—loaded one at a time—

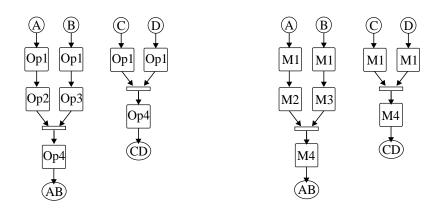

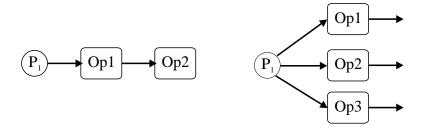

**Figure 1.1:** Object-oriented model of a flexible assembly cell. The PI's represent product route specifications.

assembles them and emits one product to some external sink outside the system. As with the external source, the external sink is not modeled, and considered to be of infinite capacity. **M2** and **M3** can both handle only one product at a time.

Note that this is a purely imaginary system, carefully chosen so as to illustrate the core of the concepts described in this work. However, the example system has many things in common with real life flexible manufacturing and assembly systems.

## 1.2 Object-Oriented Modeling

For the generation of any type of control system, a model of the system to be controlled is needed. It is favorable for this model to lie as close to the physical representation as possible, yet encompass as little information as absolutely necessary. A manufacturing system involves a number of independent manufacturing devices interacting to perform useful work. Object-oriented modeling caters for abstraction by encapsulating data and behavior. It also modularizes the modeled system in a natural way by resulting in an object structure close to the physical structure. The objects are independent software modules interacting by messages.

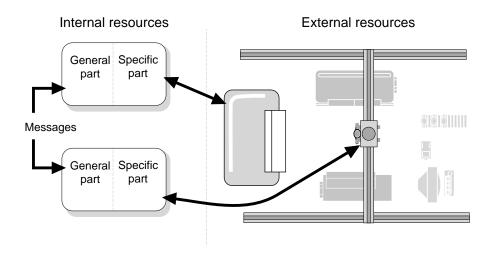

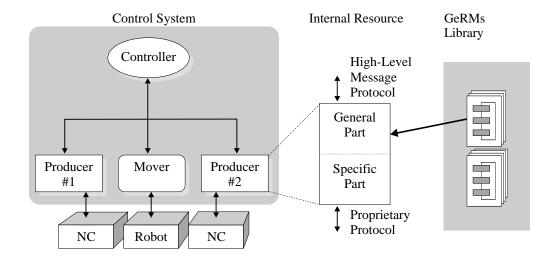

### 1.2.1 Internal Resources

An internal resource is an autonomous reusable software model, described as a DEP. The reusability emanates from the fact that machining devices can be described by their general behavior on an abstract level. On this level, application-specific details are not visible; a crucial requirement for the generation of reusable software components. However, the functionality promised by the abstract level, the general part, has to be implemented somewhere. Therefore, each resource also has a specific part that interacts with the general part. This specific part is tailored to the requirements of the actual physical device

**Figure 1.2:** Each internal resource consists of a general and a specific part, thus separating the control of the assembly process from the control of the individual devices.

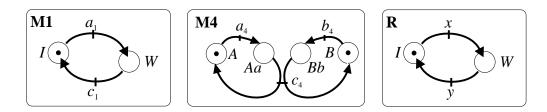

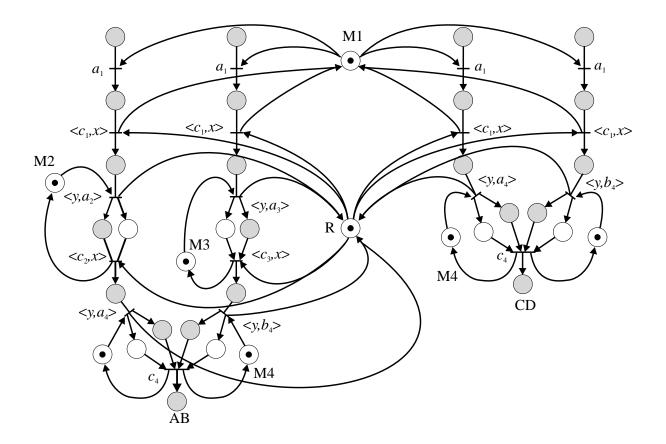

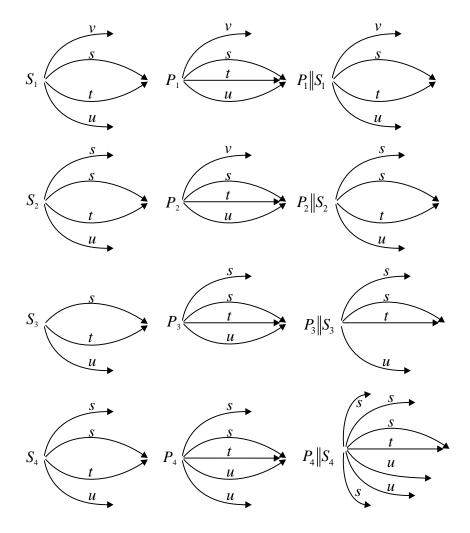

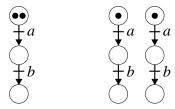

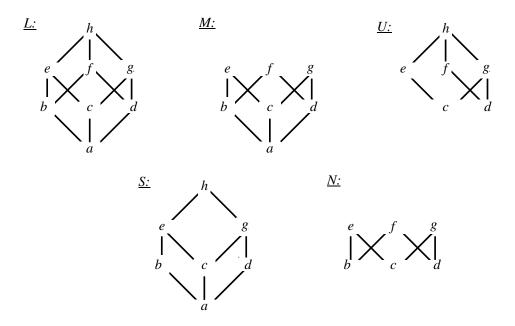

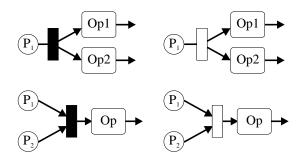

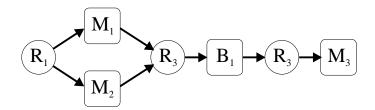

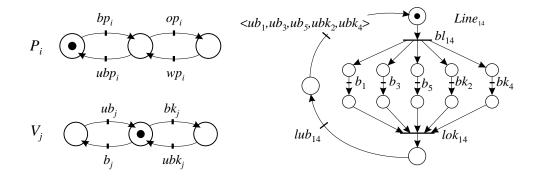

Figure 1.3: M1 represents a general production unit, such as a lathe or a mill. M4 represents a general assembly unit, and R represents a general transporting device.

in the specific application. Thus, control over a physical device is routed through the corresponding internal resource, see Figure 1.2.

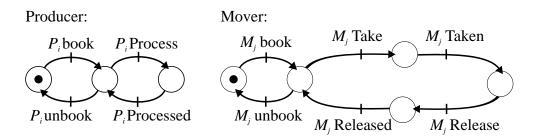

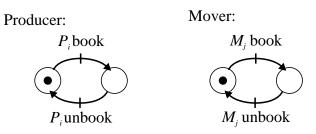

Operating concurrently, the internal resources constitute the plant to be controlled. This concurrent execution is modeled by *full synchronous composition* (FSC) of the internal resources, see Hoare (1985). This allows the internal resources to be coupled and thus able to synchronize, for instance, over mutual use of tools.

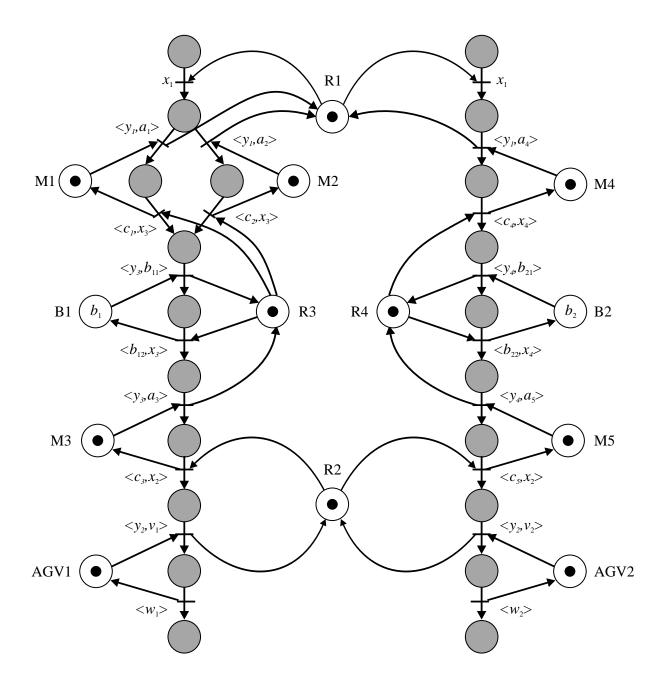

General parts, representing generic production resources such as a milling device and an assembly unit, are given in Figure 1.3; in this case in the form of Petri nets, see Peterson (1981). These models include only details specific for supervisor synthesis. More elaborate resource models usable for actual control can be found in Gullander (1995) and in Section 5.2. Suffice it to say that the models presented in Figure 1.3 are subsets, in some sense, of the more elaborate reusable resource models of Section 5.2. We can also note the work of Tittus (1995b), were reusable resource models are given for control of chemical batch processes.

The resource models of Figure 1.3 simply model whether a resource is available or not. The model of M4 being somewhat more complicated, since it includes the fact that two products have to be loaded, before an assembly operation can take place. The details of the actual operations to perform, or that can be performed, are not included in the

models. Once a product has claimed a resource, the actual operation is of no concern to the supervisor. The supervisor merely coordinates the dynamic resource allocation among the products.

## 1.3 Distributed Product Specification

Products are also modeled as DEPs. Each product specification describes a number of alternative desired routes through the system. It is thus natural to view a product as a specification on the manufacturing process to exhibit a certain event-sequence. However, there can be several independent products using the plant simultaneously. Together these form a joint specification on the system's overall behavior. So as not to overburden the user with an overly detailed knowledge of the system, it is important that there exists support for high-level distributed specification of the product routes.

## 1.3.1 High-Level Product Specification

By a high-level product specification, we mean that the specification of the product route does not explicitly mention specific devices pertaining to a particular application. Rather, the product route is given as an operation list (see Andréasson (1995) and Section 5.3), a sequence of operations that the product has to undergo to be produced. In this way a high-level product specification is independent of any plant that is to manufacture the product. Any plant that offers the required operations can produce the specified product. Compare with the general recipe of Tittus (1995b).

The preferred way to specify operation lists is graphical. The operator lays out the desired operation list, focusing merely on what operations to perform and in which order. A graphical layout is well suited for a computerized tool with a graphical interface. A number of graphical high-level operators for specifying operation lists and product routes are given in Section 5.3.1. High-level operators in an algebraic form are shown in Andréasson (1995).

However, once a plant is chosen to manufacture the product, the specified operations can be mapped onto the capabilities of specific resources within that plant. This mapping procedure is described for batch processes by Tittus (1995a), and briefly exemplified in Example 5.2 on page 156. The result is a specification for the product consisting of all possible sequences of resource allocations that will manufacture the product. Note that this is still a distributed specification. No regard for other products that may be simultaneously produced by the plant is taken. Such a product specification will be called a product route in this work, while it is called a master recipe by Tittus (1995b). Naturally, a product route can be manually specified for a given product and plant

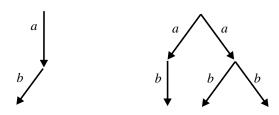

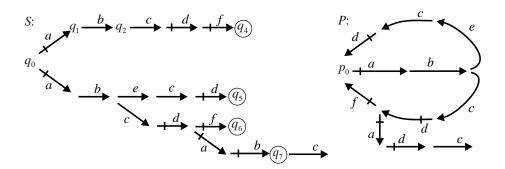

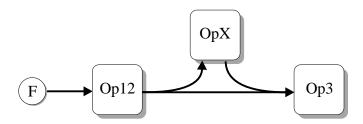

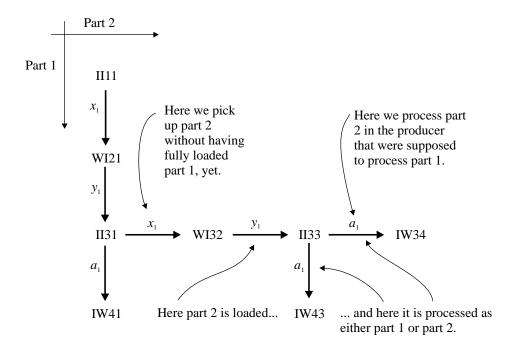

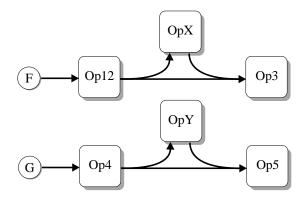

For the example system two operation lists are given to the left in Figure 1.4. These are overly simplistic, for instance, no alternative paths are specified. Nonetheless, they serve well as an example.

The two product types, **AB** and **CD**, are assembled from **A** and **B**, and **C** and **D** parts, respectively. Thus, **A**, **B**, **C** and **D** represent raw material entering the system at **M1**, while **AB** and **CD** represent the finished products. The **C** and **D** parts are not processed upon, other than in the assembly unit, **M4**, while the **A** and **B** parts are

**Figure 1.4:** To the left is shown operation lists for two types of products to be manufactured by the example system. To the right is shown the corresponding high-level product routes, assuming that operation **Opi** can be performed by machine **Mi**, only (i = 1, 2, 3, 4). Note that both product types use **M1** and **M4**.

operated upon by the lathe, M2, and the mill, M3, respectively. The exact specifications for these operations are given as parameters "hidden" within the boxes of Figure 1.4. Note that these parameters can represent an entire program for a numerically controlled production resource, if necessary. However, for the control of the overall assembly process, the nature of the operations being performed within each resource is not important, merely the sequencing between the resources is regarded.

The operation lists of Figure 1.4 can, together with a model of the plant, be translated into product routes that point out specific resources of the given plant. These are shown to the right in Figure 1.4. These are not yet DEPs, since they only describe the available sequences of resources that the products are to visit. A detailed example of this, relating to chemical batch processes, is shown in Tittus (1995d). This example is also briefly discussed in Example 5.2 on page 156. The approach is equally appropriate for manufacturing and assembly systems.

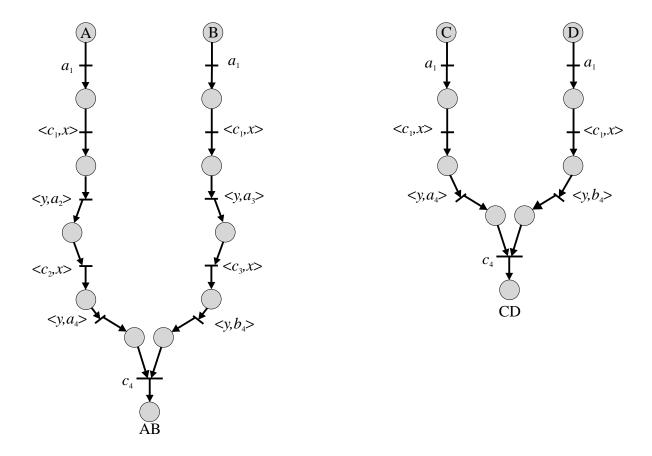

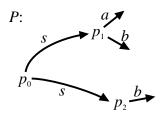

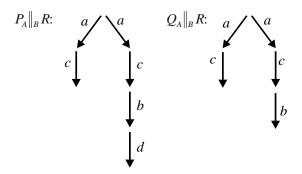

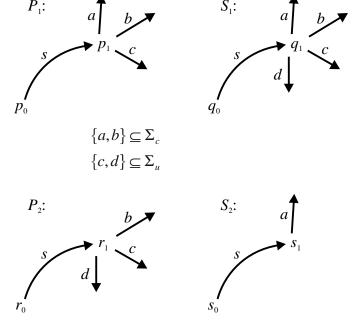

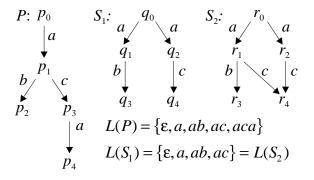

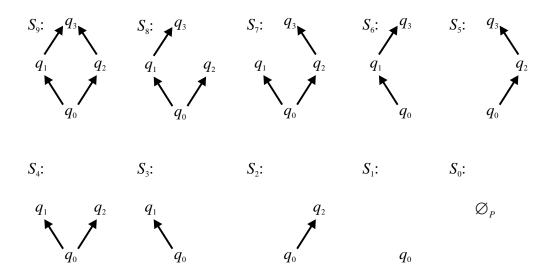

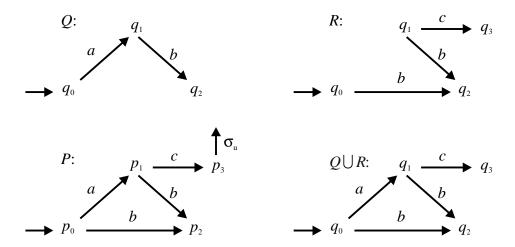

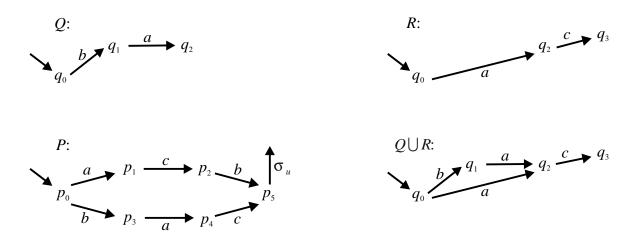

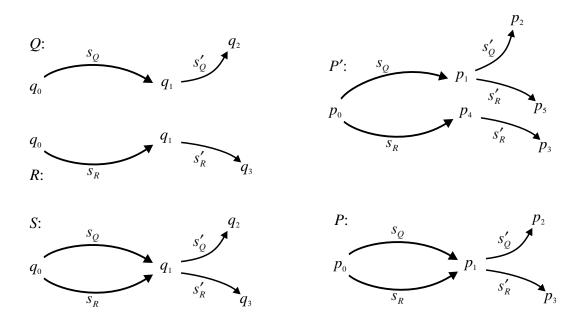

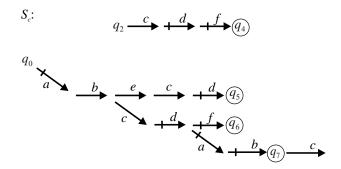

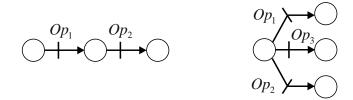

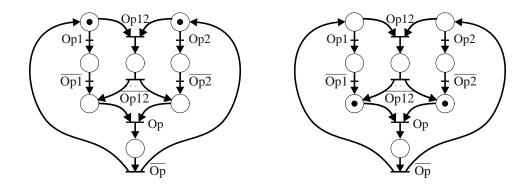

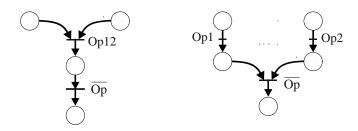

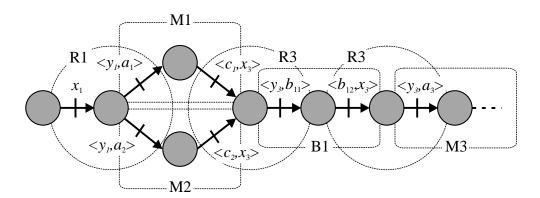

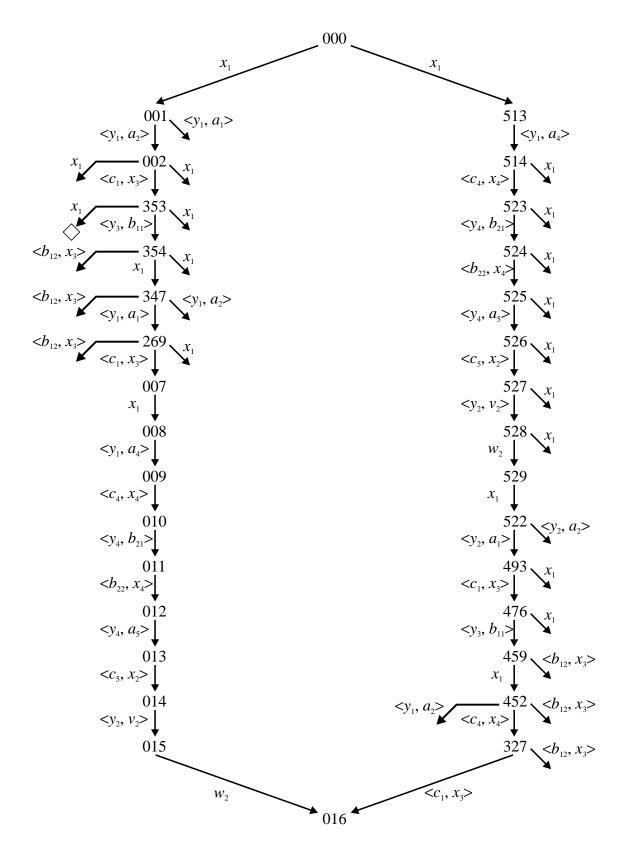

For the synthesis of a supervisor, we need the product routes in a "lower-level" form of DEPs. The resulting "low-level" product routes are given in Figure 1.5. Since there is a well-defined correspondence between a product route given as a DEP, as in Figure 1.5, and given in a more "high-level" way, as in Figure 1.4, we will make no clear distinction between the two. When necessary we will speak of "high-level product routes". Note though, that Tittus (1995d) does distinguish between these two views of a product route; the "high-level" one is called a master recipe, while the "low-level" DEP is called a synchronizable master recipe. The indices of the events denote the respective resources, see Figure 1.3.

We can note that, though the robot is required for moving products between the machines, it is not modeled in Figure 1.4, neither for the operation lists or the high-level product routes. This is not needed, since there is only one robot that is assumed to be able to handle all products and serve all machines. If this was not the case, there were multiple robots each of which could only handle specific types of products, for instance, then these would have been included in the high-level product routes. However, note that the events pertaining to the robot, x and y, are present as elements of the ordered pairs,

**Figure 1.5:** A Petri net describing the high-level product routes of Figure 1.4 in conjunction with the resource models of Figure 1.3.

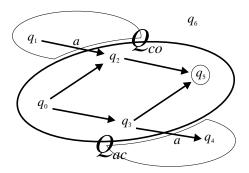

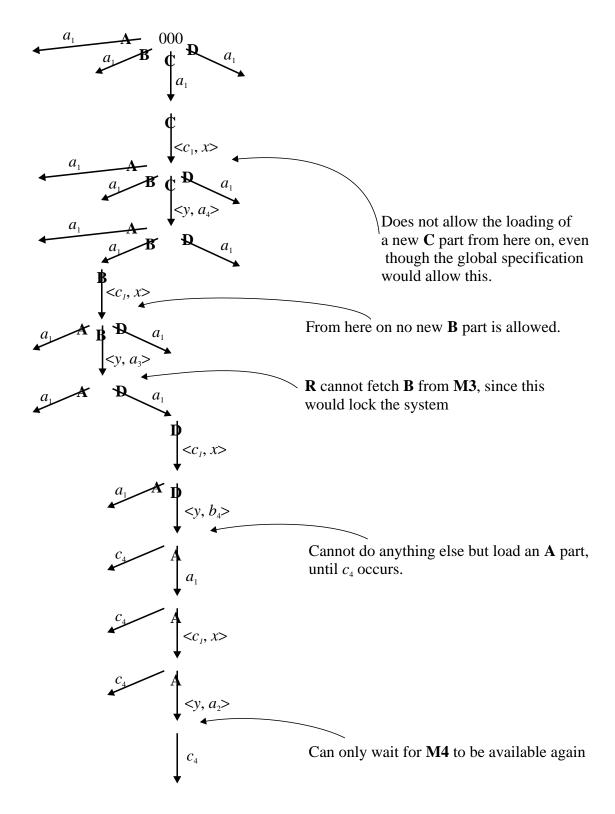

Figure 1.6: The state-machine representation of the product route for the  $\mathbf{CD}$  product of Figure 1.5, assuming one part each of  $\mathbf{C}$  and  $\mathbf{D}$ . The initial state is indicated by the unlabeled arrow to the top left. Note that this state-machine is non-deterministic, since the  $a_1$  event leads from the initial state to either of two states.

## 1.3.2 Interleaving

A distributed product specification means that all products can be specified independently of each other. The operator laying out the operation list does not have to consider any other product that may be present within the system simultaneously. Only the specific product that is being specified is of concern, even though there may be a multitude of different products running concurrently through the same system.

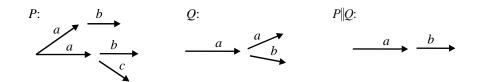

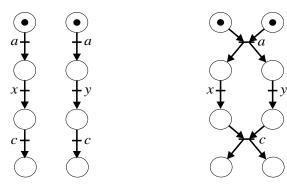

The product routes describe claiming and releasing of resources that constitute the plant. Claiming a resource and releasing it modeled as events, so that the product routes have event sets that are subsets of the plant's event set. Thus, it is not uncommon for different product routes to have common events, on the contrary. In Figure 1.5 we can see that both product routes have the events of M1 and M4 in common. At the same time, for maximal utilization of the plant, all product routes must be able to run as unconstrained by all other product routes as possible. Given distributed product specifications, a joint specification on the overall systems behavior is obtained by composing the independent product routes by *interleaving*.

The concept of interleaving is described by Hoare (1985). Essentially, interleaving means that two DEPs can execute their events asynchronously and irrespective of each other, even though there may exist mutual events. In fact, interleaving explicitly prohibits synchronous execution of any event.

Interleaving is inherent in the asynchronous execution of two or more DEPs. At each time instant any DEP can execute its own event, asynchronously with regard to any of the other DEPs. Thus, at each time instant the total system behaves as either of the DEPs, and at no times will two DEPs engage in the same action synchronously. Furthermore, the execution of an event is considered to be an instantaneous atomic action, without duration. Therefore, no two different events, equally labeled or not, can occur simultaneously. Thus, the event sequences of the interleaved system is the interleaving of the event sequences of the respective DEPs. Figure 1.5 shows the interleaving of the distributed product specifications of the example system in Petri net form. The interleaved product specification of all simultaneously present product routes will be denoted Sp, and is said to be a local specification.

Each product route defines a number of states that the system is desired to be able to reach. The completion of a product is typically such a desired state. Thus, the product routes describe desired paths through the system. These desired paths are naturally retained in Sp. However, in Sp there may also exist states that we do not want the system to be able to reach. These states can be designated as forbidden. With multiple robots, such a state may be that one robot unloads a machine, while at the same time another robot is to load that machine. Furthermore, some paths through Sp may be either desired or forbidden. This can also be introduced by synchronizing Sp with some auxiliary specification expressing these paths. See Lin (1988).

Due to the fact that multiple product routes may have equally labeled simultaneously executable transitions, the local specification may be *non-deterministic*, in the sense that one and the same string of events can lead to any of a number of states. This non-determinism arises naturally, given a number of independent resources and distributed

specifications of products to be manufactured by these resources. However, this non-deterministic specification is also an added complexity with regard to the SCT, which originally only considered deterministic plant and specification. In the following chapters will be shown that the SCT can be extended to handle the case of non-deterministic specification.

We can also note that the individual **A**, **B**, **C** and **D** parts use the same resource **M1** when entering the system. Thus, not only may non-determinism arise due to the interleaved product routes as such, but within each product route the respective parts may also be interleaved, and so the product routes themselves are non-deterministic. In Figure 1.6 the product route for the **CD** product is given in state-machine form, making the non-determinism more explicit.

## 1.4 Supervisory Control

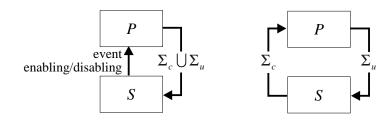

A supervisor is a DEP that operates in synchrony with the plant, influencing the plant so as to have the closed-loop system of plant and supervisor exhibit some pre-specified desired behavior. For our purposes, the full synchronous composition (FSC) adequately models the interaction between the plant and the supervisor. When synthesizing the supervisor, the SCT regards the plant as a generator of events; all events occur as a consequence of some action within the plant. Thus, the supervisor is confined to restrict the actions of the plant by disabling events as the system executes. With the FSC this disabling is a matter of the supervisor not defining some disabled events at each closed-loop system-state. Note that in different closed-loop system-states different events can be disabled.

However, not all events generated by the plant can be disabled by the supervisor. The set of events of the plant is partitioned into two disjoint event-sets, the *controllable* and the *uncontrollable* events. The controllable events can be dynamically disabled by the supervisor so as not to occur. The uncontrollable events are, on the other hand, not subject to influence by the supervisor; the plant can generate any of these whenever it occupies a state from which an uncontrollable event is valid. The completion of an operation is a typical uncontrollable event; once the supervisor has allowed the operation to start (a controllable event), the supervisor has no control over when the task is completed. A machine breakdown, is another typical uncontrollable event<sup>1</sup>. For the supervisor not to become "out of sync" with the plant, it is imperative that the supervisor is able to follow all uncontrollable events that can be generated in each closed-loop system-state; the supervisor must be *complete* with respect to the plant.

It may be desirable for the closed-loop system to always be able to reach some significant state. For instance, the state denoting completion of production with all products satisfactorily manufactured is a typical desired state. For this, the specification includes marked states. The closed loop system must be such that from any state reachable from the initial state, some marked state can always be reached. This ensures that the system will never be controlled into a state from which further production cannot continue. A DEP that is such that all states can reach some marked state is said to be coaccessible. Furthermore, to retain only states that can in practice be reached, we will require the

<sup>&</sup>lt;sup>1</sup>One which we have chosen not to model, see the resource models of Figure 1.3.

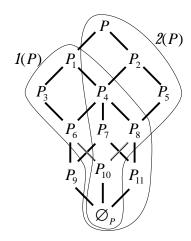

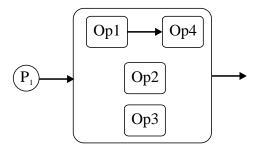

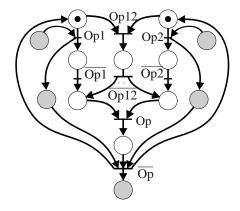

**Figure 1.7:** The global specification  $P \parallel Sp$  expressed as a Petri net. Note that, for clarity, the places corresponding to M4 have been duplicated, and places corresponding to M1 and R have been removed.

closed-loop system to be *accessible*. A DEP which is both accessible and coaccessible is said to be *trim*. When the closed-loop system is trim, any event sequence can be continued into a marked state, ensuring that the specification can always be met.

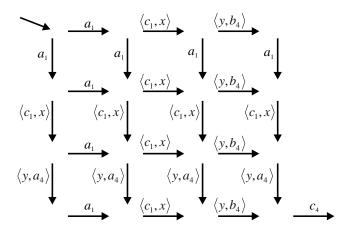

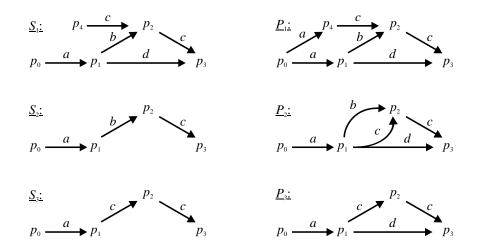

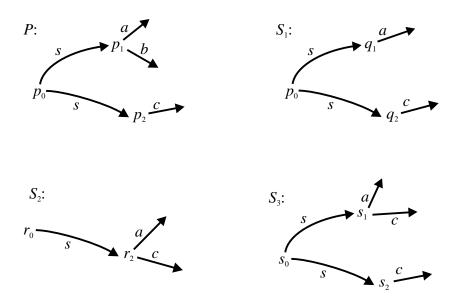

## 1.4.1 Global Specification

The local specification Sp contains all possible interleavings of the desired product routes possibly with other specifications for forbidden or desired states and forbidden paths. Not all of these interleavings are physically possible, though, due to the configuration of the plant, P. In fact, Sp does not fully describe the desired behavior of the plant. This is so, because some events of P may not be in the event set of Sp, and thus the plant can execute any of these whenever in a state to do so.

To retain only the physically possible and desired routes, Sp is synchronized with the plant under full synchronous composition. That is, the global specification  $P \parallel Sp$  is generated, see Figure 1.7. This guarantees that only physically possible routes are expressed, and it also guarantees that the desired behavior, expressed by  $P \parallel Sp$ , is a restriction of the possible behavior, expressed by P. However, in the global specification some combinations of product routing will inevitably block the system from ever reaching a state where all products have been satisfactorily completed. For instance, in Figure 1.7

it is clear that allowing two consecutive C parts to enter the system will indefinitely prohibit the assembly of any product.

Furthermore, the uncontrollable events of P may have as a consequence that not all of the behavior expressed by  $P \parallel Sp$  is controllable. Some states of the global specification must not be reached, otherwise some uncontrollable event may take the plant to some undesirable state, not allowed by the specification. Some combinations of product routing must be prohibited, and this is one of the tasks of the supervisor.

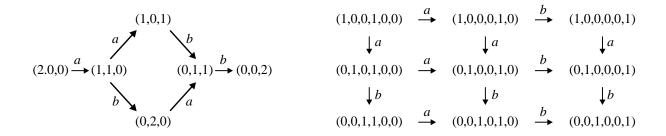

### 1.4.2 Event Connection

The algorithm presented in Chapter 4 concerns finite state automata. Therefore, the (finite) state automaton representing the DEP P||Sp must be generated. This is the reachability graph of the global specification, the Petri net of Figure 1.7. Since P||Sp is a bounded Petri net, this can be done, see Peterson (1981). Naturally, it requires an initial marking vector to be specified for the Petri net. The number of states of P||Sp is considerably smaller than the number of states of Sp, primarily because the number of physically possible routes through the plant is limited. This is one of the reasons for first using some "reduced state" description of DEPs, like Petri nets, to express P, Sp and P||Sp, and then generating a state automaton representation of P||Sp.

Some transitions of Figure 1.7 are labeled by ordered pairs of events from P. These transitions describe the passing of the product from one resource to another, and consists of the "exit" event of the former resource together with the "entry" event of the next. These ordered event-pairs arise when generating the DEP representation of the product routes, and can be automatically introduced. This models the fact that when passing a product from one resource to another, the product actually occupies both resources simultaneously. Thus, no other event can be allowed to happen in-between the two events of such an ordered pair. We say that the events are connected. This means that we regard the connected events as one event, even though the individual events are named differently.

Not including connected events would mean that the model of the system allowed a product to "exit" M2, say, without "entering" any other resource. The robot R could be used to load M2 from M1, even though the product cannot "exit" M2 without the robot being present.

Event connection can be seen as a product-unspecific specification, not dependent on the product routes but on the physical connectivity of the plant. Event connection is a consequence of the fact that we have autonomous resources with mutually disjoint alphabets. Between any type of resources shared by the same product route, event connection is required. Without event connection the resources would have to be explicitly coupled by common events. This would hinder their reusability and the flexibility of the system. The number of required "exit" events, and their labels, of one resource would have to match the number of resources that it is to be "connected" to, as well as having equal event labels. Thus, introduction of a new resource would require altering other resources. The mere instantiation of an appropriate object would no longer be possible when introducing a new resource into the system. Compare the approach of Banaszak (1990), where each resource is modeled specifically for the products it is to operate upon.

In the state automaton representation of  $P \parallel Sp$ , the connected events are "unfolded",

so that the global specification includes the same events as the plant. In Section 5.4.2 this is shown to be valid, since it generates a *subprocess* of  $P \parallel Sp$  from which a valid supervisor for P can be synthesized.

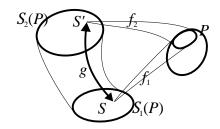

## 1.4.3 The Supervisor

In the state-machine representation of the global specification, arbitrary transitions and states can be removed; states and transitions that are considered unwanted during execution. For instance, two resources may not be allowed to work simultaneously, because of constraints on the amount of power drawn. In such a case, all states representing those two resources working simultaneously can be removed. Removal of the specified states and transitions, results in the *final specification*, within which the supervisor is to control the plant.

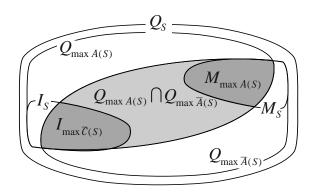

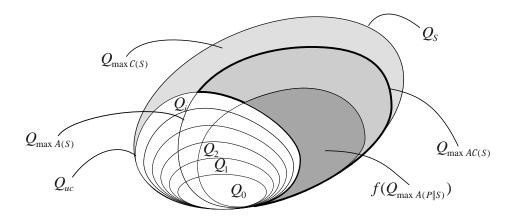

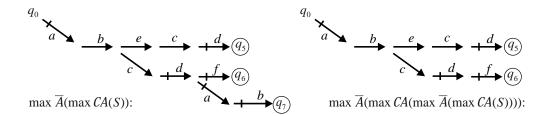

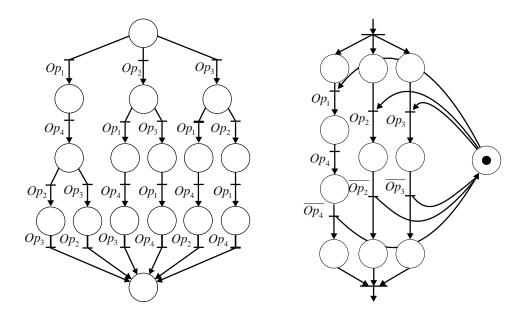

The synthesis of a supervisor is an iterative process. Except for special cases, see Brandt (1990), no closed form expressions exist. In the approach described in this work, a supervisor is a *subprocess* of the final specification. A subprocess is a DEP with its graphical structure contained within another process, the *superprocess*. A subprocess can be generated from a given process by removing states and transitions between states. In generating the supervisor, a complete and trim subprocess of the final specification is synthesized. Naturally, there may exist several solutions to the given problem of finding a complete and trim supervisor for a given plant. However, an additional requirement is to find the supervisor allowing the largest possible behavior, that is, the supervisor is required to be *minimally restrictive*. Since the supervisor is an exact model of the plant under supervision, it is clear that the minimally restrictive complete and trim supervisor is the *maximal complete and trim subprocess* of the control recipe. A formal description of the supervisor synthesis algorithm will be given in Chapter 4.

Usually the number and types of resources are constant and known, while the number and types of products is time-varying. New products are initiated and old ones terminate, asynchronously and independently as the work progresses. Thus the total number of products, and their routes through the system cannot be known a priori. For the sake of flexibility we must allow any possible route through the system. We must also allow inclusion of new products at any time during execution. However, with the introduction of new product routes there may arise additional constraints on how the products can be allowed to run concurrently. Thus, we start up the system with a number of initial product routes and calculate a supervisor for these. When new orders for more products or new product types arrive, we interleave the new routes in their initial-states with the old routes in their current state. The resulting joint specification is then composed with the plant in its current state, and a new supervisor can be calculated. Even as product routes terminate, this calculation can be performed so as to minimize the size of the supervisor.

The supervisor is a state automaton expressing all physically possible and allowable routes through the system, given the final specification. It is within the boundaries set by the supervisor that the system will be driven by the controller.

## 1.4.4 The Controller

We have carefully avoided defining the *controller*, mentioned above. This is for the reason that there are many ways to interpret the controlling entity, and they all come down to the question of event generation. Who sends which message when and to whom? That is, who generates which events and who follows?

The SCT normally regards the plant as generating all events. The supervisor merely follows and restricts the event generation. Thus, the plant and the supervisor operates in synchrony. For the supervisor and the plant to never get "out of synch" it is imperative that the supervisor can follow all events it allows the plant to generate. Restriction of an event is enforced by the supervisor not defining that event in the closed-loop system state. The uncontrollable events cannot be restricted from being generated by the plant. Therefore, it follows that the supervisor must be able to follow all uncontrollable events. It must be *complete* with respect to the plant. This is the philosophy we have adopted in generating the supervisor.

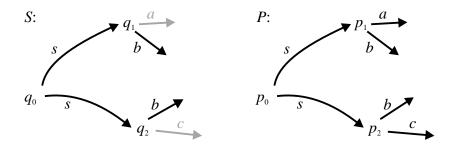

By Balemi (1992) the controller is regarded as a supervisor that generates some events, the commands, while the plant as generating other events, the responses. It is shown by Balemi (1992) that the commands can be equated to the controllable events, while the responses are equal to the uncontrollable events. Furthermore, Balemi (1992) shows that the controller and the plant have to be mutually complete so that the controller only generates events for which the plant is ready. In our case S is derived from P since it is the maximal complete and trim subprocess of the final specification. This means that the generated supervisor and the plant are always mutually complete. Therefore, we can regard the supervisor as a controller; an active entity controlling the plant by generating commands and receiving responses. The closed-loop system is then modeled by the synchronous composition of the plant and the controller. It will be shown, see Chapter 3, that this is in fact equal to the supervisor itself when the supervisor is complete (which it is) and the plant is deterministic (which it is). Thus, the supervisor is an exact model of the plant under supervision.

The supervisor coordinates the usage of the resources, commanding the robot to load and unload the machines as appropriate. At times the supervisor expresses non-deterministic choices of products to load or unload. The optimal choosing between such non-deterministic routes, taking into account aspects like fairness, due dates, etc., is a complex task, the implementation of which is outside the scope of this thesis.

## 1.5 Objectives of this Work

The goal of this work is to show how the supervisory control theory can be combined with an object-oriented modeling approach as applied to, for instance, flexible manufacturing systems. In doing so we primarily extend our previous work on object-oriented modeling of DEPs, mainly presented in [3]. It has been shown by Adiga (1993), Joannis (1992) and Jobling (1994), as well as by others, that object-oriented analysis and modeling caters for the partitioning and structuring of a large problem domain into manageable pieces. The main benefits of object-oriented modeling of manufacturing systems comes from using reusable software modules. This has a great impact on the structuring, modularization and implementation of the system. There arises a natural separation of the control of the

individual subsystems from the synchronization of the system as a whole. This immediately brings about the possibility for distributed high-level product specifications, as was shown in the previous sections.

## 1.5.1 Contributions

The objective is now to show that the supervisory control theory can be adapted to systems with the above properties. The main contributions of this work is then the following:

- We introduce an object-oriented modeling approach for fabrication processes, building on the ability to extract general behavior into reusable models of the physical devices; general in providing functionality common to all devices of a similar class, and reusable from a viewpoint of extendibility. A more elaborate description of this modeling approach is given in references [1], [2] and [3].

- The outcome of that modeling approach is set of internal resources, that constitute the plant to be controlled. These describe the capabilities, restrictions and dynamic behavior of the physical devices. Generic models in the form of discrete event processes will be given.

- We show that for such systems, the specification on the desired behavior can be given as a set of operation lists describing the desired sequences of general operations for production of the respective product.

- The internal resources and the operation lists emphasize the separation of the control of the individual devices from the overall synchronization of the fabrication process. We maintain that this is a crucial issue for reusability and true flexibility.

- Based on the operation lists we generate product routes describing desired routes through the system. The concurrent execution of the product routes is modeled by interleaving so that the joint specification of all products simultaneously present within the system is typically non-deterministic.

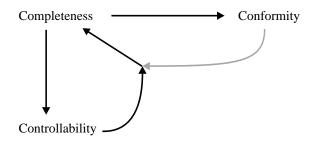

- The supervisory control theory of Ramadge (1987) and Wonham (1987) is extended to encompass non-deterministic specification. It is shown that the notion of controllability is not strong enough to guarantee a complete supervisor.

- We give algorithms for synthesizing a complete supervisor such that the closed-loop system is always nonblocking, given a non-deterministic specification.

- We also show that the input/output formulation of Balemi (1992) is valid for this case, so that the supervisor itself can act as an active controller, driving the plant within the given specification and outside the undesired states.

## 1.5.2 Assumptions and Restrictions

In this thesis we will make the following assumptions and restrictions.

- We will only regard finite state automata, and hence, regular languages.

- We will neglect the combinatorial explosion of the number of states. Automata is used merely as a formal tool for proving our statements and algorithms. In practical implementations efficient approaches like binary decision diagrams, for instance, will probably have to be employed.

- We will disregard the *silent event*, so that non-deterministic choice will only be modeled by equally labeled transitions emanating from the same state.

- The plant that we control will be regarded as non-marked. Marking is introduced as a means of specification.

- We will always assume that the event-set of the supervisor is equal to the set of events defined by the plant. Thus, the supervisor expresses *all* desired and allowed behavior. The plant has no additional freedom in generating events not in the event-set of the supervisor.

- All events are considered to be observable. Non-determinism is not a consequence of un-observable events.

Note also that we elaborate on the applicability of the supervisory control theory for non-deterministic specification as well as non-deterministic plant. However, the application of the presented algorithm is restricted to the case of a deterministic plant.

### 1.5.3 Thesis Outline

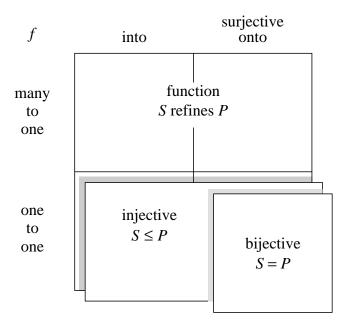

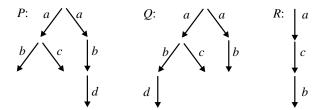

This work is organized as follows. A thorough definition of the *finite transition machines* that we will use to model DEPs, is given in Chapter 2. A number of properties are shown, and the special case of two transition machines, with one being deterministic and the other being non-deterministic, is investigated. It is shown that when the non-deterministic transition machine holds the property of *refinement* relative to the deterministic one, then their synchronous composition will be equal to the non-deterministic transition machine. The definitions and results presented in Chapter 2 are essentially well-known, though the notion of refinement is extended to non-deterministic processes. The definitions of operations on subprocesses seem to be novel. In the literature the state-spaces are required to be disjoint; see Eilenberg (1974) and Hopcroft (1979), for instance.

In Chapter 3 we first restate the original supervisory control problem, as formulated by Ramadge and Wonham. This is given complete with proofs of the propositions, significantly simplified compared to the original proofs. A more "modern" notation has been used, mainly by introducing the full synchronous composition as modeling the interaction between the supervisor and the plant. This has already been done in Kumar (1991), but the treatment there did not include all of the SCT; marked states were not treated, for instance. We feel that the presented notation casts some light on the SCT for the unfamiliar reader, as well as helping the reader familiar with the SCT in its original form to better understand the extensions that follow. The derivation of the controllability property is, as far as we know, our own. Wonham (1987), Ramadge (1987), Balemi (1992) and Kumar (1995), among others, define controllability but do not derive it.

Since the input/output formulation of Balemi (1992) lies closer to a control engineering point of view, this approach is also described in Chapter 3. The inverse properties are not our own, though the terminology is. These properties are defined by Balemi (1992), though he makes no distinction between controllability and completeness.

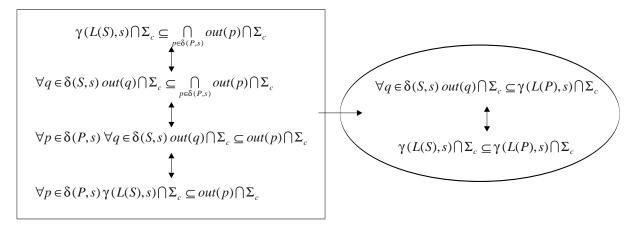

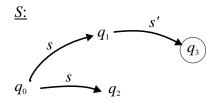

Then follows the application of the SCT to the general case of non-deterministic transition machines in Section 3.4. It is shown that the notion of controllability is no longer strong enough to guarantee a usable supervisor. Necessary and sufficient conditions are given for a non-deterministic supervisor, S, to be complete with respect to a plant, given a controllable language, L(S). Furthermore, it is shown that the input/output formulation is also encompassed by the non-deterministic supervisory control approach as given in this work. The notion of a nonblocking closed-loop system is investigated for the non-deterministic case. It is shown that a nonblocking supervisor is not enough to guarantee that the closed-loop system is nonblocking when non-determinism is present. Necessary and sufficient conditions for the marking of the supervisor relative to the plant is given, so that the closed-loop system is nonblocking. Finally, an overall view is given of a number of combinations of non-deterministic plant, specification and supervisor, with necessary and sufficient conditions for the existence of a supervisor.

Section 3.4 is almost entirely our own. Most of the results seem to be non-existent in the literature. The generalized definition of completeness has also been given by Overkamp (1994), though the generalized condition for a non-deterministic supervisor with a controllable language to be complete is our own. The extension of the input/output interpretation to non-deterministic systems has not appeared anywhere else, as far as we know. Also, to our knowledge the conditions for a nonblocking closed-loop system is not previously known. The theorems presented in the last section is not known to have been given in such a unified framework.

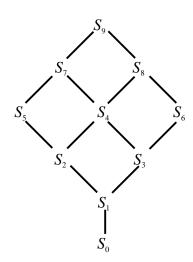

In Chapter 4 an algorithm for synthesis of a non-deterministic supervisor is derived. This is shown for a non-deterministic specification and deterministic plant. It is shown that the set of usable supervisors the specification defines relative to the plant can be ordered in an upper semilattice structure. From this, we show how to calculate the minimally restrictive supervisor such that the closed-loop system is nonblocking. That is, the supremal complete and trim subprocess of the specification.

Some of the lattice results given are well-known and given by Tremblay (1987), for instance. Other results for the specific application of calculating a complete and trim supervisor are new. The definition of the *supremal operator* to calculate the supremal element of the intersection of two upper semilattices, when it exists, is new. The algorithms given for calculating complete, accessible and coaccessible subprocesses are not new, however. Eilenberg (1974) also shows the algorithm for accessibility and coaccessibility, while the algorithm for completeness is well-known within the supervisory control theory. See Kumar (1991), for instance. What is new, is the application to non-deterministic systems, and the short and concise notation of the algorithms resulting from the definition of the various operators.

The object-oriented modeling approach that initiated this work, is briefly described in Section 5.2. This approach is described in detail by our previous work, as shown on page ii. Of greater importance to the present work are the various aspects of specification that are discussed, and the application of the mathematical framework of the previous chapters to the specific class of problems that arises. It is shown that the properties that have been

defined as necessary for the non-deterministic supervisory approach are immediate by the modeling approach. Thus, it is shown that the non-deterministic supervisory approach can be combined with object-oriented modeling techniques, and so we have a powerful framework for implementing large and complex discrete event systems.

A number of application examples are finally described in Chapter 6. The modeling and the synthesis of supervisors are shown to some extent.

## Chapter 2

## Finite Transition Machines

This work concerns control of what is usually known as discrete event processes, acronymed DEP. A discrete event process is a system that at each time instant occupies a state of being, one out of a finite number of possible states. The state has a symbolic value, rather than a numeric, and represents a situation of the process during which certain conditions hold. The DEP transits between the states according to the occurrances of events, occurring instantaneously at discrete intervals of time. Thus, the process' behavior is given by the sequences, strings, of events that occur, and the sequences of states that the process occupies due to these strings. These notions will be formalized in the following definitions.

Let us first, however, note that the term finite transition machine will be used, instead of the more common finite automata (see Eilenberg (1974) and Hopcroft (1979)) or finite state-machine. The reasons for this are similar to those given in Arnold (1994) for using the term finite transition system. Automata can be considered to be the fundamental concept for the formal description of DEPs. The term transition system is used by Arnold (1994) to distinguish automata viewed as formal systems containing states and transitions from automata regarded as machines to recognize certain languages. Also, finite state-machines normally define one or more initial states and a set of final states, see Eilenberg (1974). This is not necessarily so for the finite transition systems of Arnold (1994). See also Cassandras (1993) who gives good reasons for not always demanding an explicit initial state, as well as disregarding a set of final states. We will use the term transition, for the same reason as given in Arnold (1994), that is, to point out that we do not merely regard the DEPs as recognizers of specific languages. However, we will also use the term machine to point out that we do indeed require a specific set of initial states. Furthermore, we will also allow, but not require, a set of marked states. These are not to be regarded as final states, though. Rather, these states can be regarded as states within which the system is allowed to rest. Some subtask may be completed and the system waits for more tasks to perform.

This chapter will lay the formal ground necessary to prove that a finite transition machine can be controlled to adhere to a prespecified behavior. We will formally define what we mean by a finite transition machine and its behavior. A universal set containing all finite transition machines will be defined to bring meaning to the operations on transition machines. A number of properties relevant for the control of transition machines will be proved, and we will define an ordering relation between finite transition machines.

Finally, some other approaches to modeling discrete event processes will be briefly discussed, and compared to the approach described in this work. Mainly, differences arise in the definition of equality of transition machines, and we will show why we feel that the strong equality relation that we define is necessary in the context of this work. Most other approaches give a much weaker definition of transition machine equivalence, see Section 2.5.

## 2.1 Universe of Discourse

A finite transition machine is a system that occupies a distinct state of being, from which it can transit to another state on the occurance of an event. Thus, the fundamental concepts are states, events and transitions. Formally we have the following.

### Definition 2.1 States, Events and Strings

Let Q and  $\Sigma$  be two finite sets. For simplicity we will require the elements of these sets to be singular, that is they are not themselves sets. Let  $Q^+ = \bigcup_{i=1}^{\infty} Q^i$ , where  $Q^1 = Q$ ,  $Q^2 = Q \times Q$  and  $Q^{n+1} = Q^n \times Q$ . Similarly, let  $\Sigma^* = \bigcup_{j=0}^{\infty} \Sigma^j$ . The elements of  $Q^+$ , will be called states, the elements of  $\Sigma$  are referred to as events, and  $\Sigma$  itself will be called an alphabet. The set  $\Sigma^*$  is the set of all finite sequences of events of  $\Sigma$ . An element of  $\Sigma^*$  is called a string. The string of no events,  $\Sigma^0$ , is called the  $null\ string\ and\ is\ denoted\ \varepsilon$ .

**Remark.** The set  $\Sigma^*$  is called the Kleene closure of  $\Sigma$ , see Hopcroft (1979). Of course, the Kleene closure can be applied to any set. Note that, for two arbitrary sets  $E_S \subseteq E_P \Leftrightarrow E_S^* \subseteq E_P^*$ .

Observe that the null string  $\varepsilon = \Sigma^0$  is an element of  $\Sigma^*$ , while the element  $Q^0$  does not belong to  $Q^+$ .

Unindexed lowercase letters, from the greek alphabet or from the beginning of the latin alphabet, will be used to denote events. For example,  $\sigma, \sigma', a, b, c$  will all represent events. Strings will normally be denoted by s, s', s'' and the like. Since  $Q \subseteq Q^+$ , the elements of Q are also states. Lowercase letters from the middle of the latin alphabet, possibly indexed, will denote states. That is,  $q, q', p_0, p_n$  all denote states. Furthermore, states of  $Q^+$  not in Q will be given as ordered tuples of the singular elements of Q, thus  $\langle p_0, q_0 \rangle$  and  $\langle p_i, q_i, r_k \rangle$  are two states of  $Q^+$ .

As a convention we will, following Eilenberg (1974), systematically confuse an element x of any set with the subset of that set  $\{x\}$  consisting of x only. Furthermore, we will regard the sets  $(X \times Y) \times Z$ ,  $X \times Y \times Z$ , and  $X \times (Y \times Z)$  as identical. This is also according to Eilenberg (1974), but note that it is contrary to Tremblay (1987).

The definition of the set of states as being  $Q^+$  may need some elaboration. Normally, a given transition machine will have a state set of Q. In fact we can even claim that the state sets of a number of given transition machines define the state set Q. We will define operations composing different transition machines into new ones. These operations all make the state set of the composed transition machine equal to the cartesian product of

the state sets of the original transition machines, so that transition machines generated by the composition operators will acquire state sets from  $Q^+ - Q$ . These operations are the normal way to compose given transition machines, and for these compositions to be contained within the universe of discourse, this universe must include the cartesian products over all singular states and any number of compositions, that is  $Q^+$ . We will only consider finite number of compositions, though.

The transitions of a finite transition machine will, for historical reasons, be referred to as *edges*, see Eilenberg (1974). Intuitively, an edge defines the state from which the transition is valid, the label of the occurring event and the state that the transition transits to. Because of this, it will not make any sense to distinguish between two edges defining transitions from the same state, labeled by the same event and transiting to the same state. Therefore, for a finite transition machine the set of all edges can be defined.

### Definition 2.2 Edges and the Edgeset

Let  $E = Q^+ \times \Sigma \times Q^+$ . The elements of the set E will be called *edges*, and consequently E is called the (universal) *edge-set*.

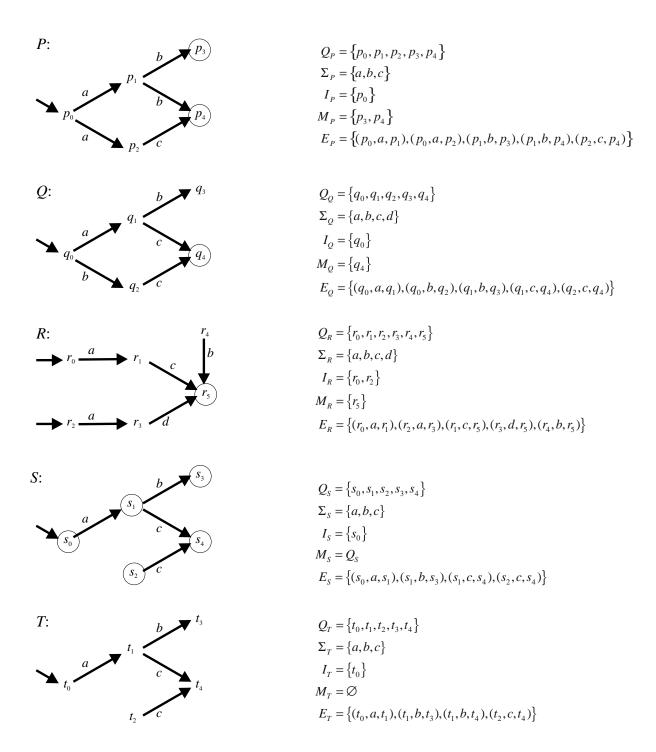

### Definition 2.3 Finite Transition Machine

A finite transition machine P, is described by a 5-tuple  $(Q_P, \Sigma_P, I_P, M_P, E_P)$  where

$$Q_P \subseteq Q^+$$

: the  $state-space$ , the finite set of states  $\Sigma_P \subseteq \Sigma$ : the  $alphabet$ , the finite set of events  $I_P \subseteq Q_P$ : the set of  $initial$  states  $M_P \subseteq Q_P$ : the set of  $marked$  states  $E_P \subseteq Q_P \times \Sigma_P \times Q_P$ : the  $edge-set$  of  $P$

**Remark.** Note that the state-space as well as the alphabet, and hence the edge-set, are all required to be finite.

The edge-set  $E_P \subseteq Q_P \times \Sigma_P \times Q_P$  defines the transitions of P. That is, the ordered triple  $(p, \sigma, p') \in E_P$ , with  $p, p' \in Q_P$  and  $\sigma \in \Sigma_P$ , means that there exists a transition from the state p to the state p' labeled by the event  $\sigma$ . The state p' is then said to be reachable from the state p via the event  $\sigma$ . Since both  $Q^+$  and  $\Sigma$  are required to be finite, so are  $Q_P$  and  $\Sigma_P$  and, hence, also  $E_P$ . This is why we speak of a finite transition machine.

Note also that an edge is equivalent to a directed path (of length one) as defined graph theoretically.  $\Box$

In the following we will define, propose and prove a number of properties concerning finite transition machines. In doing so we will extensively make use of set union and intersection, cartesian product and other operations from set algebra. As noted by Eilenberg (1974), to bring meaning to the operations on the defined entities we first have to define the universe of discourse, see Tremblay (1987), within which all elements are contained.

#### Definition 2.4 Universe of Discourse

For any finite transition machine that we define, the universe of discourse is  $Q^+ \times \Sigma \times Q^+ \times Q^+ \times E$ . That is, for any finite transition machine P, we have that  $P \subseteq Q^+ \times \Sigma \times Q^+ \times Q^+ \times E$ .

**Remark.** Note that we will equate the terms discrete event process, finite state automaton and finite transition machine. These will all be considered to refer to objects of the same type, that is, objects within the universe of discourse defined above. Furthermore, for the sake of brevity, we will often refrain from using the whole terms, merely saying process, automaton, transition machine or even use the more common term state-machine.  $\Box$

It is clear that a finite transition machine has the equivalent expressive power of a finite state-machine, see Hopcroft (1979). However, a finite state-machine is normally defined with a transition function defining its transitions instead of an edge-set. For notational convenience, it is sometimes more appropriate to use the transition function<sup>1</sup>,  $\delta$ , in place of the edge-set.

### **Definition 2.5 Transition Function**

The transition function of a transition machine P, is a mapping  $\delta_P: Q_P \times \Sigma_P \to 2^{Q_P}$  that maps a state  $p \in Q_P$  and an event  $\sigma \in \Sigma_P$  into the set of reachable states,  $\delta_P(p,\sigma) \subseteq Q_P$ . The transition function can be extended into strings over  $\Sigma^*$  as  $\delta_P: Q_P \times \Sigma_P^* \to 2^{Q_P}$ . With  $\varepsilon$  denoting the null string of  $\Sigma_P^*$  we have

$$\delta_P(p,\varepsilon) = p \qquad p \in Q_P

\delta_P(p,s\sigma) = \delta_P(\delta_P(p,s),\sigma) \quad \sigma \in \Sigma_P, s \in \Sigma_P^*$$

(2.2)

The transition function can also be extended to sets of states as  $\delta_P: 2^{Q_P} \times \Sigma_P^* \to 2^{Q_P}$ , as

$$\delta_P(Q,s) = \bigcup_{p \in Q} \delta_P(p,s) \quad Q \subseteq Q_P.$$

(2.3)

Remark. For an event  $\sigma \in \Sigma_P$  for which  $\delta_P$  is undefined at state p we have  $\delta_P(p,\sigma) = \emptyset$ . This distinguishes events that are not feasible in the state p due to the structure of the transitions machine, from events that are feasible but have the property of not changing the state. Though  $\delta_P(\cdot,\cdot)$  is formally defined for  $\Sigma_P$  only, the case that a transition machine will have to consider events not in its alphabet will arise when the transition machine is composed to run concurrently with other transition machines. Events in the alphabet of one of the machines but not in the alphabet of the other machine, is of no concern to the other machine. The other machine is physically incapable of participating in, or even noticing, the execution of the event. Thus, the only reasonable definition of  $\delta_P(p,\sigma)$  when  $\sigma \notin \Sigma_P$  seems to be  $\delta_P(p,\sigma) = p$ . Note that this implicitly includes a self-loop on all events not present in the machines own alphabet.