THESIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

# Measurement, Modeling, and Characterization for Energy-Efficient Computing

BHAVISHYA GOEL

Division of Computer Engineering Department of Computer Science and Engineering CHALMERS UNIVERSITY OF TECHNOLOGY Göteborg, Sweden 2016

#### **Measurement, Modeling, and Characterization for Energy-Efficient Computing** *Bhavishya Goel* ISBN 978-91-7597-411-8

Copyright © Bhavishya Goel, 2016.

Doktorsavhandlingar vid Chalmers tekniska högskola Ny serie Nr 4092 ISSN 0346-718X

Technical Report 129D Department of Computer Science and Engineering Computer Architecture Research Group

Department of Computer Science and Engineering Chalmers University of Technology SE-412 96 GÖTEBORG, Sweden Phone: +46 (0)31-772 10 00

Author e-mail: goelb@chalmers.se

Chalmers Reposervice Göteborg, Sweden 2016

#### Measurement, Modeling, and Characterization for Energy-Efficient Computing

Bhavishya Goel

Division of Computer Engineering, Chalmers University of Technology

#### ABSTRACT

The ever-increasing ecological footprint of Information Technology (IT) sector coupled with adverse effects of high power consumption on electronic circuits has increased the significance of energy-efficient computing in the last decade. Making energy-efficient computing a norm rather than an exception requires that system designers and programmers understand the energy implications of their design and implementation choices. This necessitates a detailed view of system's energy expenditure and/or power consumption. We explore this aspect of energy-efficient computing in this thesis through power measurement, power modeling, and energy characterization.

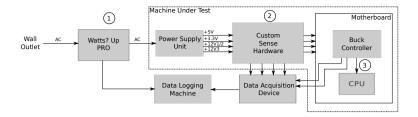

First, we present a quantitative comparison between power measurement data collected for computer systems using four techniques: a power meter at wall outlet, current transducers at ATX power rails, CPU voltage regulator's current monitor, and Intel's proprietary RAPL (Running Average Power Limit) interface. We compare them for accuracy, sensitivity and accessibility.

Second, we present two different methodologies to model processor power consumption. The first model estimates power consumption at the granularity of individual cores using per-core performance events and temperature sensors. We validate the methodology on six different platforms and show that our model estimates power consumption with high accuracy across all platforms consistently. To understand the energy expenditure trends across different frequencies and different degrees of parallelism, we need to model power at a much finer granularity. The second power model addresses this issue by estimating static and dynamic power consumption for individual cores and the uncore. We validate this model on Intel's Haswell platform for single-threaded and multi-threaded benchmarks. We use this power model to characterize energy efficiency of frequency scaling on Haswell microarchitecture and use the insights to implement a low overhead DVFS scheduler. We also characterize the energy efficiency of thread scaling using the power model and demonstrate how different communication parameters and microarchitectural traits affect application's energy when it scales.

Finally, we perform detailed performance and energy characterization of Intel's Restricted Transactional Memory (RTM). We use TinySTM software transactional memory (STM) system to benchmark RTM's performance against competing STM alternatives. We use microbenchmarks and STAMP benchmark suite to compare RTM an STM performance and energy behavior. We quantify the RTM hardware limitations and identify conditions required for RTM to outperform STM.

**Keywords:** power estimation, energy characterization, power-aware scheduling, power management, transactional memory, power measurement

ii

### Preface

Parts of the contributions presented in this thesis have previously been published in the following manuscripts.

- Bhavishya Goel, Sally A. McKee, Roberto Gioiosa, Karan Singh, Major Bhadauria, Marco Cesati, "Portable, Scalable, Per-Core Power Estimation for Intelligent Resource Management" in *Proceedings* of the 1st International Green Computing Conference, Chicago, USA, August, 2010, pp.135-146.

- Bhavishya Goel, Sally A. McKee, Magnus Själander, "Techniques to Measure, Model, and Manage Power," in *Advances in Comput*ers 87, 2012, pp.7-54.

- Bhavishya Goel, Ruben Titos-Gil, Anurag Negi, Sally A. Mc-Kee, Per Stenstrom, "Performance and Energy Analysis of the Restricted Transactional Memory Implementation on Haswell" in Proceedings of 28th IEEE International Parallel and Distributed Processing Symposium, Phoenix, USA, May, 2014, pp.615-624

The following manuscript has been accepted but is yet to be published.

Bhavishya Goel, Sally A. McKee, "A Methodology for Modeling Dynamic and Static Power Consumption for Multicore Processors" in *Proceedings of 30th IEEE International Parallel and Distributed Processing Symposium*, Chicago, USA, May, 2016

The following manuscripts have been published but are not included in this work.

- Bhavishya Goel, Magnus Själander, Sally A. McKee, "RTL Model for Dynamically Resizable L1 Data Cache" in *Swedish System-on-Chip Conference*, Ystad, Sweden, 2013

- Magnus Själander, Sally A. McKee, Bhavishya Goel, Peter Brauer, David Engdal, Andras Vajda, "Power-Aware Resource Scheduling in Base Stations" in 19th Annual IEEE/ACM International Symposium on Modeling, Analysis and Simulation of Computer and Telecommunication Systems, Singapore, Singapore, July, 2012, pp.462-465.

## Acknowledgments

I will like to thank following people for supporting me during my PhD and contributing to this thesis directly or indirectly.

- Professor Sally A. McKee for giving me the opportunity to work with her, for giving me the confidence boost during the lows and for celebrating my highs. She always trusted me to choose my own research path but was always there whenever I needed her for counseling. She is also an excellent cook and her brownies and palak paneers have got me through various deadlines.

- ▷ Magnus Själander for helping me with my research during the early years of my PhD and letting me bounce ideas off him. His unabated enthusiasm for research is very contagious.

- ▷ Madhavan Manivannan for being a great friend and colleague; and for spending loads of his precious time to review my papers and thesis.

- Professor Lars Svensson for helping me with practical issues during his time as division head and for giving me critical feedback to improve the technical and non-technical aspects of this thesis.

- Professor Per Larsson-Edefors for teaching some of the most entertaining courses I have taken at Chalmers and for his valuable feedback from time to time.

- Professor Per Stenström for being an inspiration in the field of computer architecture.

- Professor Lieven Eeckhout for evaluating my licentiate thesis and for his insightful comments on my research.

- Anurag Negi for being an accommodating roommate and a helpful coauthor.

- ▷ Ruben Titos for helping me in getting started with the basics of transactional memory, for doing his part in the paper we co-authored and for cheering me up with his positive vibes.

- Karan Singh, Vincent M. Weaver and Major Bhadauria for getting me started with the power modeling infrastructure at Cornell and answering my naïve questions patiently.

- Roberto Gioiosa and Marco Cesati for helping me run experiments for my first paper.

- ▷ Jacob Lidman for being an amazing study partner, for sharing office space with me and putting up with my rants and bad jokes.

- Alen, Angelos, Bapi, Dmitry, Kasyab, Mafijul, Waliullah, Gabriele, Vinay, Jochen, Fatemeh, Behrooz, Chloe, Petros, Risat, Stavros, Alirad, Ahsen, Viktor, Miquel, Vassilis, Yiannis and Ivan for being wonderful colleagues and friends.

- ▷ Peter, Rune and Arne for proving invaluable IT support.

- ▷ Rolf Snedsböl for managing my teaching duties.

- ▷ Eva, Lotta, Tiina, Jonna, and Marianne for providing excellent administrative support during my time at Chalmers.

- ▷ All the colleagues and staff at Computer Science and Engineering department for creating a healthy work environment.

- $\triangleright$  Anthony Brandon for giving me valuable support when I was working with  $\rho$ VEX processor for ERA project.

- ▷ European Union for funding my research.

- ▷ My family for motivating me to push for my goals and being there as a backup whenever I needed them.

Bhavishya Goel Göteborg, May 2016

# Contents

| Ab | ostrac | t                                        | i   |

|----|--------|------------------------------------------|-----|

| Pr | eface  |                                          | iii |

| Ac | know   | ledgments                                | v   |

| 1  | Intro  | oduction                                 | 2   |

|    | 1.1    | Power Measurement                        | 8   |

|    | 1.2    | Power Modeling                           | 9   |

|    | 1.3    | Energy Characterization                  | 10  |

|    | 1.4    | Contributions                            | 10  |

|    | 1.5    | Thesis Organization                      | 12  |

| 2  | Pow    | er Measurement Techniques                | 13  |

|    | 2.1    | Power Measurement Techniques             | 14  |

|    |        | 2.1.1 At the Wall Outlet                 | 14  |

|    |        | 2.1.2 At the ATX Power Rails             | 15  |

|    |        | 2.1.3 At the Processor Voltage Regulator | 17  |

|    |        | 2.1.4 Experimental Results               | 19  |

|    | 2.2    | RAPL power estimations                   | 24  |

|    |        | 2.2.1 Overview                           | 24  |

|    |        | 2.2.2 Experimental Results               | 24  |

|    | 2.3    | Related Work                             | 31  |

|    | 2.4    | Conclusions                              | 32  |

| 3  | Per-   | core Power Estimation Model              | 33  |

|    | 3.1    | Modeling Approach                        | 37  |

|   | 3.2 | Methodology                                                   | 88 |

|---|-----|---------------------------------------------------------------|----|

|   |     | 3.2.1 Counter Selection                                       | 88 |

|   |     | 3.2.2 Model Formation                                         | 12 |

|   | 3.3 | Validation                                                    | 4  |

|   |     | 3.3.1 Computation Overhead                                    | 16 |

|   |     | 3.3.2 Estimation Error                                        | 16 |

|   | 3.4 | Management 5                                                  | 53 |

|   |     | 3.4.1 Sample Policies                                         | 58 |

|   |     | 3.4.2 Experimental Setup                                      | 58 |

|   |     | 3.4.3 Results                                                 | 50 |

|   | 3.5 | Related Work                                                  | 52 |

|   | 3.6 | Conclusions                                                   | 55 |

| 4 | Ene | gy Characterization for Multicore Processors Using Dynamic    |    |

|   |     |                                                               | 67 |

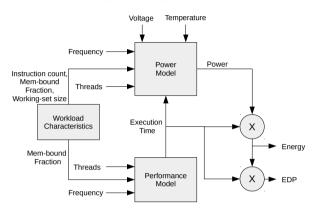

|   | 4.1 | Power Modeling Methodology                                    | 59 |

|   |     |                                                               | 59 |

|   |     |                                                               | 2  |

|   |     | 4.1.3 Uncore Static Power Model                               | 74 |

|   |     | 4.1.4 Core Static Power Model                                 | 75 |

|   |     | 4.1.5 Total Chip Power Model                                  | 7  |

|   | 4.2 | Validation                                                    | 80 |

|   | 4.3 | Energy Characterization of Frequency Scaling 8                | 31 |

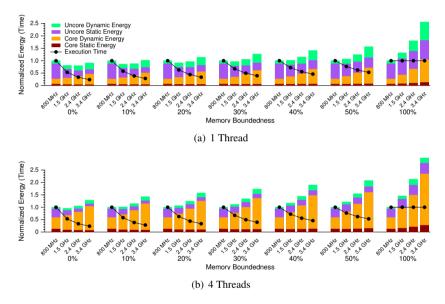

|   |     | 4.3.1 Energy Effects of DVFS                                  | 33 |

|   |     | 4.3.2 DVFS Prediction                                         | 35 |

|   | 4.4 | Energy Characterization of Thread Scaling 9                   | 92 |

|   |     | 4.4.1 Energy Effects of Serial Fraction                       | 96 |

|   |     | 4.4.2 Energy Effects of Core-to-core Communication Overhead 9 | 99 |

|   |     | 4.4.3 Energy Effects of Bandwidth Contention 10               | )2 |

|   |     | 4.4.4 Energy Effects of Locking-Mechanism Overhead 10         | )4 |

|   | 4.5 | Related Work                                                  | )6 |

|   | 4.6 | Conclusions                                                   | )8 |

| 5 | Cha | racterization of Intel's Restricted Transactional Memory 10   | )9 |

|   | 5.1 | Experimental Setup                                            | 0  |

|   | 5.2 | Microbenchmark analysis                                       | 2  |

|     | 5.2.1  | Basic RTM Evaluation        |

|-----|--------|-----------------------------|

|     | 5.2.2  | Eigenbench Characterization |

| 5.3 | HTM v  | versus STM using STAMP      |

| 5.4 | Relate | d Work                      |

| 5.5 | Conclu | sions                       |

|     |        |                             |

| - | <b>A</b> |        |

|---|----------|--------|

| 6 | 1 one    | lusion |

| v | COL      | lusion |

|   |          |        |

| 1 | 2 | 6 |

|---|---|---|

| T | 4 | U |

#### CONTENTS

# List of Figures

| 2.1  | Power Measurement Setup                                          | 14 |

|------|------------------------------------------------------------------|----|

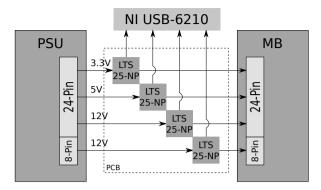

| 2.2  | Measurement Setup on the ATX Power Rails                         | 17 |

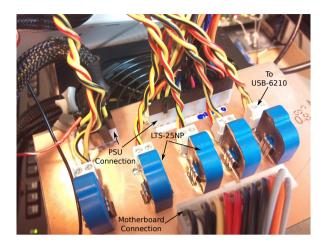

| 2.3  | Our Custom Measurement Board                                     | 18 |

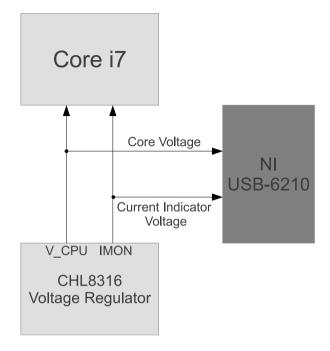

| 2.4  | Measurement Setup on CPU Voltage Regulator                       | 19 |

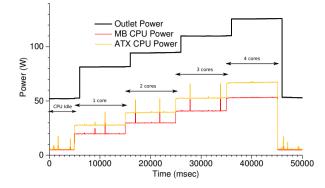

| 2.5  | Power Measurement Comparison When Varying the Number of Active   |    |

|      | Cores                                                            | 20 |

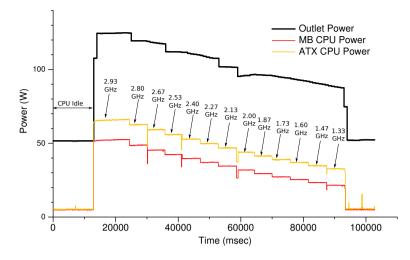

| 2.6  | Power Measurement Comparison When Varying Core Frequency         | 21 |

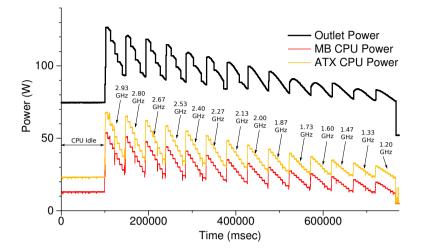

| 2.7  | Power Measurement Comparison When Varying Core Frequency To-     |    |

|      | gether with Throttling Level                                     | 22 |

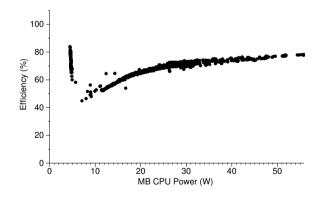

| 2.8  | Efficiency Curve of CPU Voltage Regulator                        | 22 |

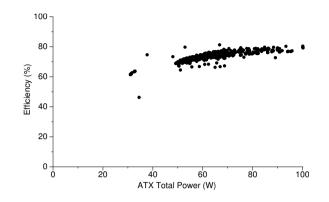

| 2.9  | Efficiency Curve of the PSU                                      | 23 |

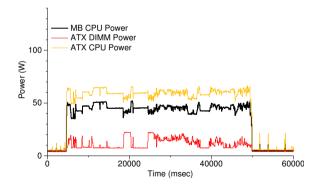

| 2.10 | Power Measurement Comparison for the CPU and DIMM (Running gcc)  | 23 |

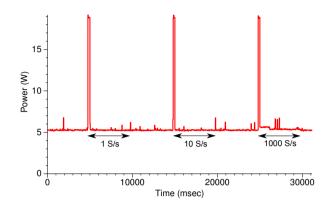

| 2.11 | Power Overhead Incurred While Reading the RAPL Energy Counter .  | 25 |

| 2.12 | Power Measurement Comparison for the ATX and RAPL at the RAPL    |    |

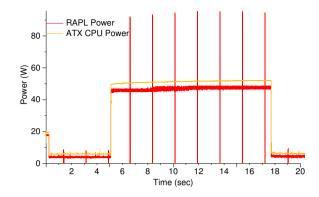

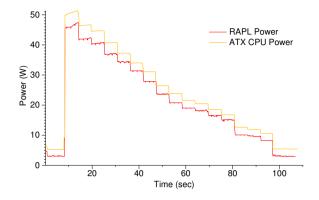

|      | Sampling Rate of 1000 Sa/s                                       | 26 |

| 2.13 | Coarse-grain Sensitivity Test for ATX and RAPL: Frequency Change |    |

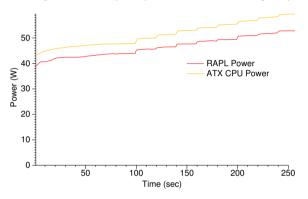

|      | Test                                                             | 27 |

| 2.14 | Fine-grain Sensitivity Test for ATX and RAPL at 3.4 GHz          | 27 |

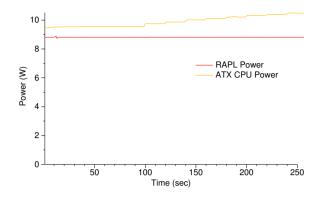

| 2.15 | Fine-grain Sensitivity Test for ATX and RAPL at 800 MHz          | 28 |

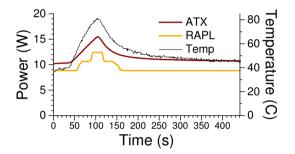

| 2.16 | Power Measurement Comparison for ATX and RAPL with Varying       |    |

|      | Temperature                                                      | 28 |

| 2.17 | Power Measurement Comparison for ATX and RAPL with Varying       |    |

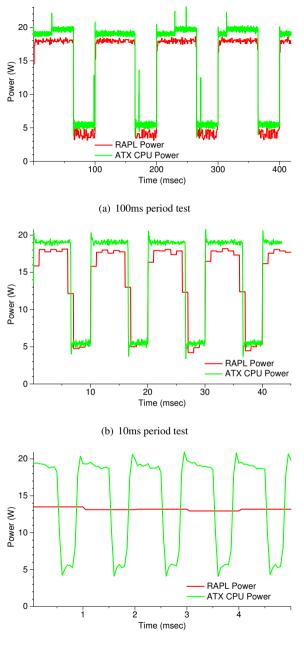

|      | Real-time Application Period                                     | 30 |

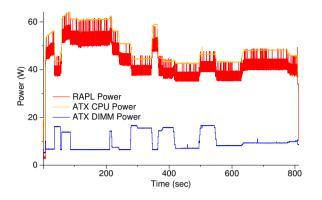

| 2.18 | RAPL Accuracy Test for Test Benchmark                            | 31 |

| 3.1  | Temperature Effects on Power Consumption                         | 36 |

| 3.2  | Microbenchmark Pseudo-Code                                       | 40 |

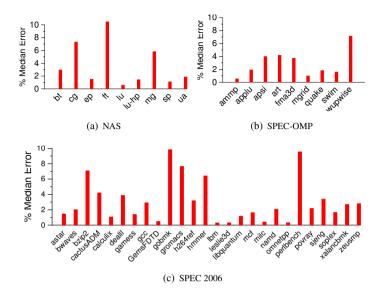

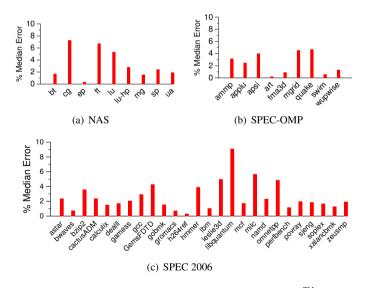

| 3.3  | Median Estimation Error for the Intel Q6600 system               | 47 |

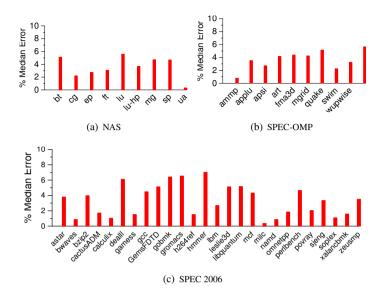

|                                                                                                                                                             | Median Estimation Error for Intel E5430 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

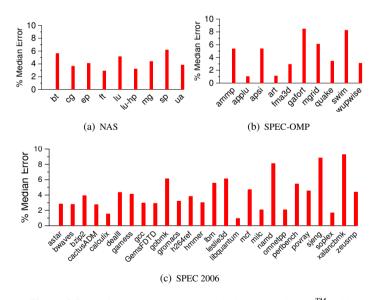

| 3.5                                                                                                                                                         | Median Estimation Error for the AMD Phenom <sup>TM</sup> 9500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48                                                                                                                                             |

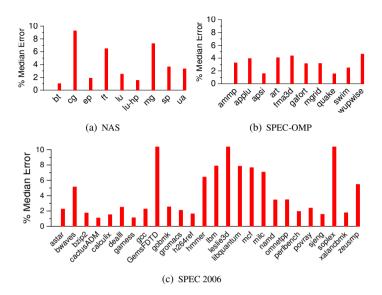

| 3.6                                                                                                                                                         | Median Estimation Error for the AMD Opteron <sup>TM</sup> 8212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                                                                                             |

| 3.7                                                                                                                                                         | Median Estimation Error for the Intel Core <sup>TM</sup> i7 $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49                                                                                                                                             |

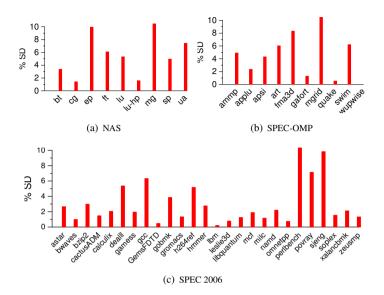

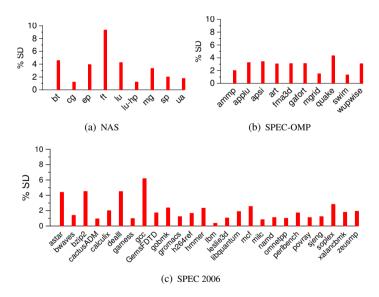

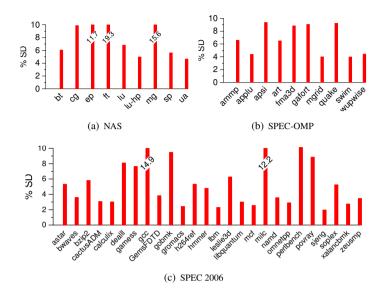

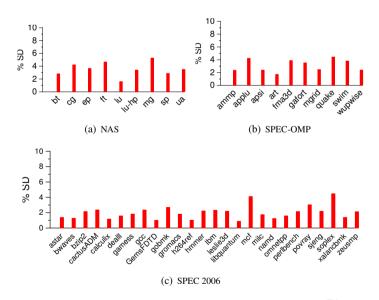

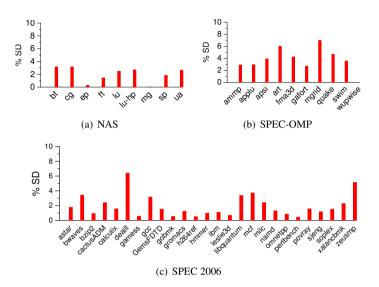

| 3.8                                                                                                                                                         | Standard Deviation of Error for the Intel Q6600 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                             |

| 3.9                                                                                                                                                         | Standard Deviation of Error for Intel E5430 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                             |

| 3.10                                                                                                                                                        | Standard Deviation of Error for the AMD Phenom <sup>TM</sup> 9500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51                                                                                                                                             |

| 3.11                                                                                                                                                        | Standard Deviation of Error for the AMD Opteron <sup>TM</sup> 8212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                                                                                             |

| 3.12                                                                                                                                                        | Standard Deviation of Error for the IntelCore <sup>TM</sup> i7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                                                                                                                                             |

| 3.13                                                                                                                                                        | Cumulative Distribution Function (CDF) Plots Showing Fraction of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                |

|                                                                                                                                                             | Space Predicted (y axis) under a Given Error (x axis) for Each Sys-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                |

|                                                                                                                                                             | tem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                                             |

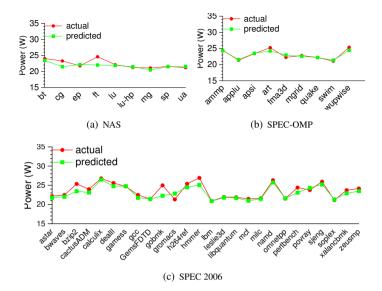

| 3.14                                                                                                                                                        | Estimated versus Measured Error for the Intel Q6600 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                                             |

| 3.15                                                                                                                                                        | Estimated versus Measured Error for Intel E5430 system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55                                                                                                                                             |

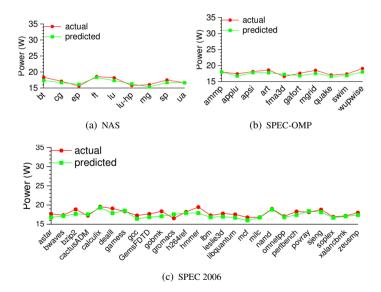

| 3.16                                                                                                                                                        | Estimated versus Measured Error for the AMD Phenom <sup>TM</sup> 9500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                                                             |

| 3.17                                                                                                                                                        | Estimated versus Measured Error for the AMD Opteron <sup>TM</sup> 8212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                                                                                                                                             |

| 3.18                                                                                                                                                        | Estimated versus Measured Error for the Intel Core <sup>TM</sup> i7-870                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                                                             |

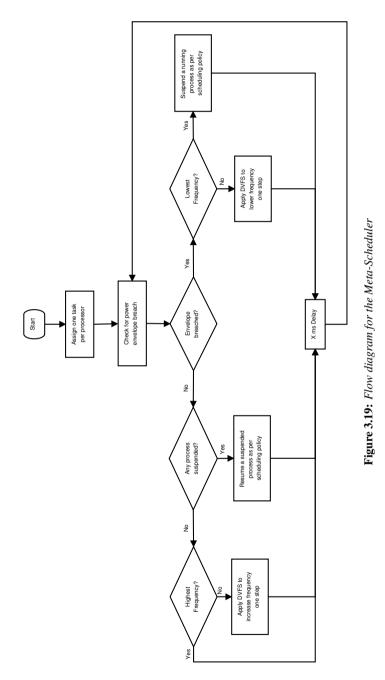

| 3.19                                                                                                                                                        | Flow diagram for the Meta-Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                                                                                                             |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (0                                                                                                                                             |

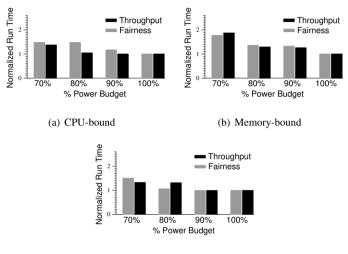

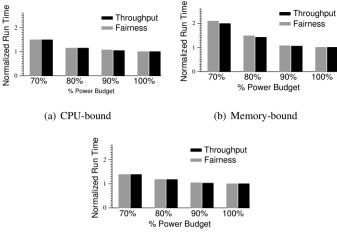

| 3.20                                                                                                                                                        | Runtimes for Workloads on the Intel $Core^{TM}i7-870$ (without DVFS).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                                                                                             |

| 3.20<br>3.21                                                                                                                                                | Runtimes for Workloads on the Intel Core <sup>TM</sup> 17-870 (without DVFS) $\ldots$<br>Runtimes for Workloads on the Intel Core <sup>TM</sup> 17-870 (with DVFS) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60<br>61                                                                                                                                       |

|                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                |

| 3.21                                                                                                                                                        | Runtimes for Workloads on the Intel Core $^{\rm TM}i7\text{-}870$ (with DVFS) $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                |

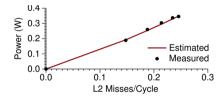

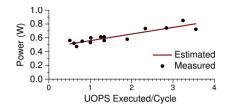

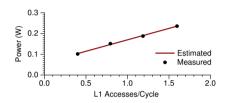

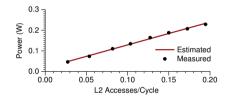

| 3.21                                                                                                                                                        | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) $\ldots$ .<br>Model Fitness for Power Consumed due to L2 Misses at F=800 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                                             |

| 3.21<br>4.1                                                                                                                                                 | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) $\dots$<br>Model Fitness for Power Consumed due to L2 Misses at F=800 MHz<br>and V=0.7V $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61                                                                                                                                             |

| 3.21<br>4.1                                                                                                                                                 | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)<br>Model Fitness for Power Consumed due to L2 Misses at F=800 MHz<br>and V=0.7V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61<br>71                                                                                                                                       |

| <ul><li>3.21</li><li>4.1</li><li>4.2</li></ul>                                                                                                              | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) Model Fitness for Power Consumed due to L2 Misses at F=800 MHz and V=0.7V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61<br>71                                                                                                                                       |

| <ul><li>3.21</li><li>4.1</li><li>4.2</li></ul>                                                                                                              | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) Model Fitness for Power Consumed due to L2 Misses at F=800 MHz and V=0.7V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61<br>71<br>73                                                                                                                                 |

| <ul><li>3.21</li><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                                                                  | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)         Model Fitness for Power Consumed due to L2 Misses at F=800 MHz         and V=0.7V          Model Fitness for Power Consumed due to Non-Memory Execution         Units at F=800 MHz and V=0.7V          Model Fitness for Power consumed due to L1 Accesses at F=800 MHz         and V=0.7V          Model Fitness for Power consumed due to L1 Accesses at F=800 MHz         and V=0.7V          Model Fitness for Power Consumed due to L2 Accesses at F=800 MHz                                                                                                                | 61<br>71<br>73                                                                                                                                 |

| <ul><li>3.21</li><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                                                                                  | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)         Model Fitness for Power Consumed due to L2 Misses at F=800 MHz         and V=0.7V         Model Fitness for Power Consumed due to Non-Memory Execution         Units at F=800 MHz and V=0.7V         Model Fitness for Power consumed due to L1 Accesses at F=800 MHz         and V=0.7V                                                                                                                                                                                                                                                                                         | 61<br>71<br>73<br>73                                                                                                                           |

| <ul><li>3.21</li><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                                                                      | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) Model Fitness for Power Consumed due to L2 Misses at F=800 MHz and V=0.7V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> </ul>                                                                         |

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                                                                   | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS) Model Fitness for Power Consumed due to L2 Misses at F=800 MHz and V= $0.7V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> <li>76</li> </ul>                                                             |

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>                                                      | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)Model Fitness for Power Consumed due to L2 Misses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to Non-Memory ExecutionUnits at F=800 MHz and V= $0.7V$ Model Fitness for Power consumed due to L1 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Uncore Static Model FitnessCore Static Model Fitness                                                                                                                                                                                                 | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> <li>76</li> <li>77</li> </ul>                                                 |

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>                                         | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)Model Fitness for Power Consumed due to L2 Misses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to Non-Memory ExecutionUnits at F=800 MHz and V= $0.7V$ Model Fitness for Power consumed due to L1 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Core Static Model FitnessCore Static Model FitnessAbrupt Jump in Power Consumption at Higher Frequency                                                                 | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> <li>76</li> <li>77</li> <li>78</li> </ul>                                     |

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul>                            | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)Model Fitness for Power Consumed due to L2 Misses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to Non-Memory ExecutionUnits at F=800 MHz and V= $0.7V$ Model Fitness for Power consumed due to L1 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Core Static Model FitnessCore Static Model FitnessAbrupt Jump in Power Consumption at Higher FrequencyAbrupt Jump in Power Consumption at Higher Temperature           | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> </ul>                         |

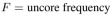

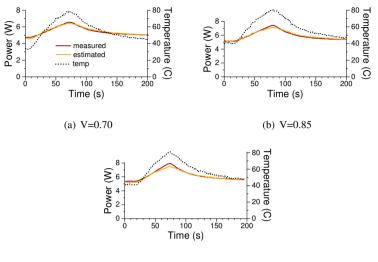

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> </ul>               | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)Model Fitness for Power Consumed due to L2 Misses at F=800 MHzand V=0.7VModel Fitness for Power Consumed due to Non-Memory ExecutionUnits at F=800 MHz and V=0.7VModel Fitness for Power consumed due to L1 Accesses at F=800 MHzand V=0.7VModel Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V=0.7VModel Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V=0.7VCore Static Model FitnessCore Static Model FitnessAbrupt Jump in Power Consumption at Higher FrequencyAbrupt Jump in Power Consumption at Higher TemperatureValidation of Total Chip Power | 61<br>71<br>73<br>73<br>74<br>76<br>77<br>78<br>79<br>81                                                                                       |

| <ul> <li>3.21</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul> | Runtimes for Workloads on the Intel Core <sup>TM</sup> i7-870 (with DVFS)Model Fitness for Power Consumed due to L2 Misses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to Non-Memory ExecutionUnits at F=800 MHz and V= $0.7V$ Model Fitness for Power consumed due to L1 Accesses at F=800 MHzand V= $0.7V$ Model Fitness for Power Consumed due to L2 Accesses at F=800 MHzand V= $0.7V$ Uncore Static Model FitnessCore Static Model FitnessAbrupt Jump in Power Consumption at Higher FrequencyAbrupt Jump in Power Consumption at Higher TemperatureValidation of Total Chip PowerEnergy and EDP generation                                | <ul> <li>61</li> <li>71</li> <li>73</li> <li>73</li> <li>74</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>81</li> <li>82</li> </ul> |

#### LIST OF FIGURES

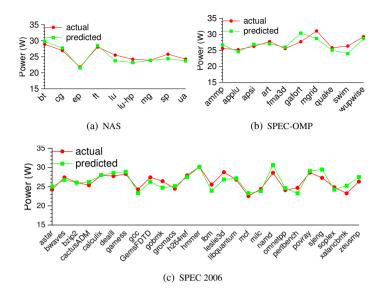

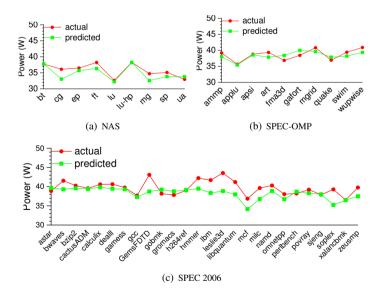

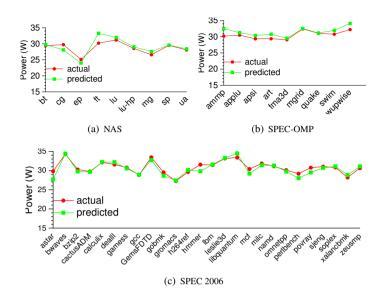

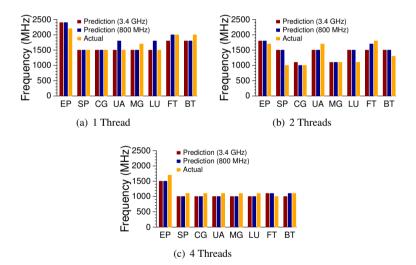

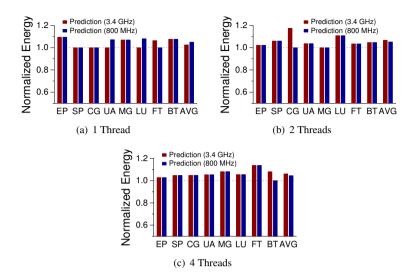

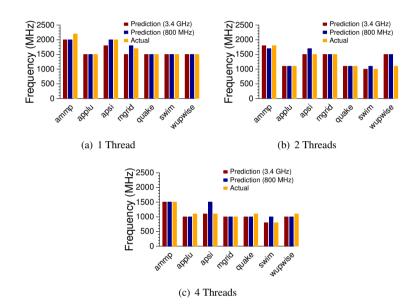

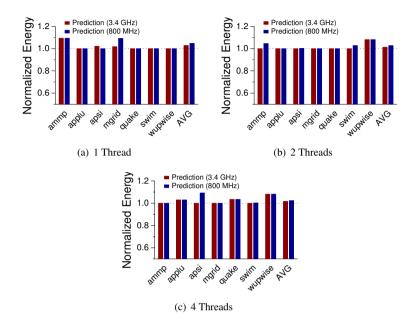

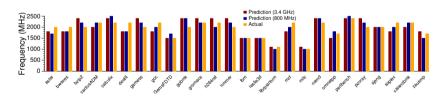

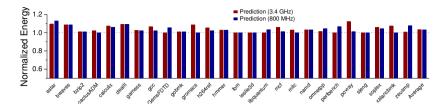

| NAS benchmarks       89         4.14       Actual versus Predicted Frequency at which the Least Energy is Expended for SPEC OMP2001 Benchmarks       90         4.15       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for SPEC OMP2001 Benchmarks       91         4.16       Actual versus Predicted Frequency at which Least Energy is Expended for SPEC 2006 Benchmarks       91         4.17       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC 2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling       102         4.25       Effects of Locking Mechanism Overhead Analysis       103         4.26       Fifects of Locking Mechanism Overhead Analysis       104         4.27       Effects of Locking Mechan             | 4.13 | Energy expenditure at $P(3.4)_E$ and $P(0.8)_E$ normalized to $F_E$ for |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------|------|

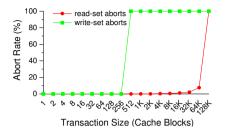

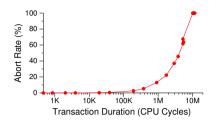

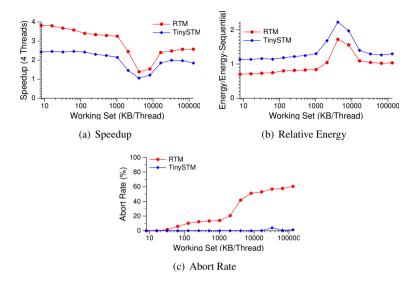

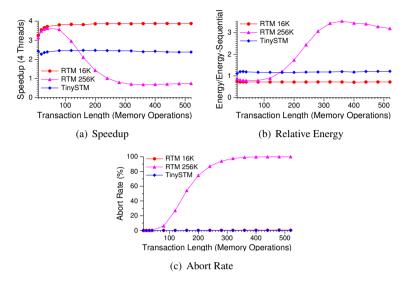

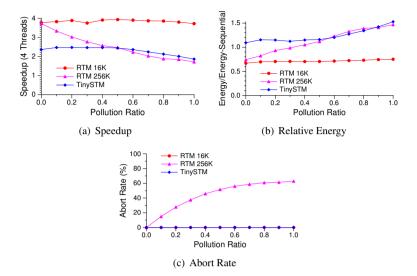

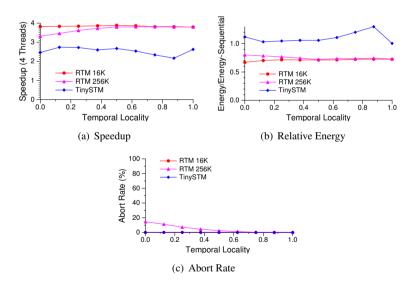

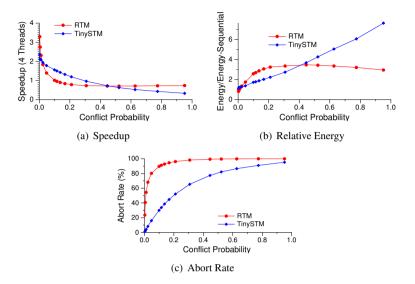

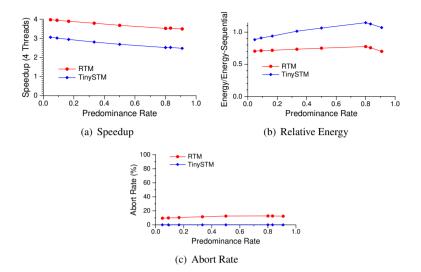

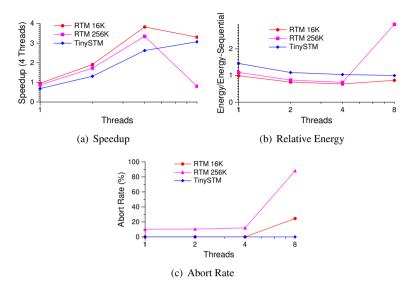

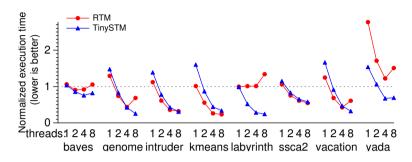

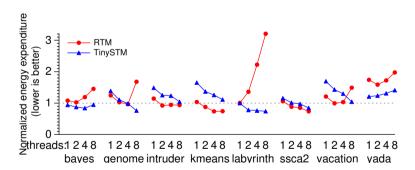

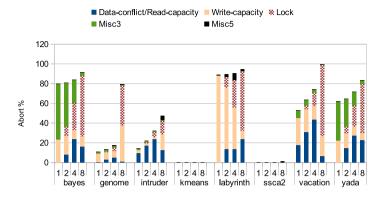

| pended for SPEC OMP2001 Benchmarks904.15Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC OMP2001 Benchmarks914.16Actual versus Predicted Frequency at which Least Energy is Expended<br>for SPEC 2006 Benchmarks914.17Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC 2006 Benchmarks924.18Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks934.19Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks944.20Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks944.21Pseudo-Code for Serial Fraction Analysis984.22Effects of Serial Fraction on the Energy Efficiency of Thread Scaling1004.23Pseudo-Code for Core-to-core Communication Overhead Analysis1014.24Effects of Core-to-core Communication on Energy Efficiency of Thread<br>Scaling1024.25Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling1065.1RTM Read-Set and Write-Set Capacity Test1125.2RTM Abort Rate versus Transaction Duration1135.3Eigenbench Orking-Set Size1155.4Eigenbench Predominance1195.9Eigenbench Concurrency1225.11RTM versus TinySTM Energy Expenditure for STAMP Benchmarks1225.11RTM versus TinySTM Energy Expenditure for STAMP Benchmarks122                                                                                                                             |      | NAS benchmarks                                                          | 89   |

| 4.15       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC OMP2001 Benchmarks       91         4.16       Actual versus Predicted Frequency at which Least Energy is Expended<br>for SPEC 2006 Benchmarks       91         4.17       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       94         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication Overhead Analysis       102         4.25       Effects of Locking Mechanism Overhead Analysis       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling       106         5.1    | 4.14 |                                                                         |      |

| SPEC OMP2001 Benchmarks       91         4.16       Actual versus Predicted Frequency at which Least Energy is Expended for SPEC 2006 Benchmarks       91         4.17       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC OMP2001 Benchmarks       94         4.20       Energy Consumed During DVFS versus Best Static Frequency for SPEC 2006 benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC 2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       94         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Serial Fraction on Energy Efficiency of Thread Scaling       102         4.25       Effects of Locking Mechanism Overhead Analysis       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test                      |      | •                                                                       | 90   |

| 4.16       Actual versus Predicted Frequency at which Least Energy is Expended<br>for SPEC 2006 Benchmarks       91         4.17       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread<br>Scaling       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench T | 4.15 |                                                                         | 0.1  |

| for SPEC 2006 Benchmarks914.17Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC 2006 Benchmarks924.18Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks934.19Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks944.20Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks944.21Pseudo-Code for Serial Fraction Analysis984.22Effects of Serial Fraction on the Energy Efficiency of Thread Scaling1004.23Pseudo-Code for Core-to-core Communication Overhead Analysis1014.24Effects of Core-to-core Communication on Energy Efficiency of Thread<br>Scaling1024.25Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 1034.26Pseudo-Code for Locking Mechanism Overhead Analysis1054.27Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling1065.1RTM Read-Set and Write-Set Capacity Test1125.2RTM Abort Rate versus Transaction Duration1135.3Eigenbench Transaction Length1165.5Eigenbench Transaction Length1165.5Eigenbench Temporal Locality1175.6Eigenbench Contention1185.8Eigenbench Predominance1195.9Eigenbench Predominance1195.9Eigenbench Predominance1205.10RTM versus TinySTM Performance for STAMP Benchmarks122 </td <td></td> <td></td> <td>91</td>                                                                                                              |      |                                                                         | 91   |

| 4.17       Energy Expenditure at $P(3.4)_E$ and $P(0.8)_E$ Normalized to $F_E$ for<br>SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       94         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread<br>Scaling       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Transaction Length       116         5.5       Eigenbench Temporal Locality       117                                         | 4.16 |                                                                         | 01   |

| SPEC 2006 Benchmarks       92         4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       94         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication Overhead Analysis       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Transaction Length       116         5.5       Eigenbench Temporal Locality       117         5.6       Eigenbench Contention       118         5.8                                                                                         | 4 17 |                                                                         | 91   |

| 4.18       Energy Consumed During DVFS versus Best Static Frequency for NAS<br>Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC<br>OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread<br>Scaling       102         4.25       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead Analysis       105         4.28       Effects of Locking-Mechanism Overhead on the Energy Efficiency of<br>Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Transaction Length       116         5.4       Eigenbench Temporal Locality       117         5.6       Eigenbench Co                                                   | 4.17 |                                                                         | 92   |

| Benchmarks       93         4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC         OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC         2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling       100         4.25       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead Analysis       105         4.28       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Transaction Length       116         5.4       Eigenbench Temporal Locality       117         5.6       Eigenbench Contention                                                                                                                      | 4 18 |                                                                         | /2   |

| 4.19       Energy Consumed During DVFS versus Best Static Frequency for SPEC         OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC         2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       94         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication Overhead Analysis       102         4.25       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling 103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       102         4.27       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       102         4.28       Effects of Locking Mechanism Overhead Analysis       105         4.29       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling 103       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Working-Set Size       115         5.4       Eigenbench Transaction Length       116         5                                                                                                    | 1.10 |                                                                         | 93   |

| OMP2001 Benchmarks       94         4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC         2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication Overhead Analysis       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       102         4.27       Effects of Locking-Mechanism Overhead Analysis       105         4.28       Effects of Locking Mechanism Overhead Analysis       105         4.29       Effects of Locking Mechanism Overhead Analysis       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Transaction Length       116         5.4       Eigenbench Transaction Length       117         5.4       Eigenbench Contention       118         5.5       Eigenbench Contention       118         5.8                                                                                                                                                         | 4 19 |                                                                         | 10   |

| 4.20       Energy Consumed during DVFS versus Best Static Frequency for SPEC<br>2006 benchmarks       94         4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication Overhead Analysis       101         4.25       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling 103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       102         4.27       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Working-Set Size       115         5.4       Eigenbench Temporal Locality       117         5.5       Eigenbench Contention       118         5.8       Eigenbench Contention       119         5.9       Eigenbench Concurrency                                                                                                         | ч.17 |                                                                         | 0/   |

| 2006 benchmarks       94         4.21 Pseudo-Code for Serial Fraction Analysis       98         4.22 Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23 Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24 Effects of Core-to-core Communication on Energy Efficiency of Thread       Scaling         4.25 Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling103       102         4.26 Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27 Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling 103       105         4.27 Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling 103       106         5.1 RTM Read-Set and Write-Set Capacity Test       112         5.2 RTM Abort Rate versus Transaction Duration       113         5.3 Eigenbench Working-Set Size       115         5.4 Eigenbench Transaction Length       116         5.5 Eigenbench Pollution       117         5.6 Eigenbench Contention       118         5.8 Eigenbench Contention       118         5.9 Eigenbench Predominance       120         5.10 RTM versus TinySTM Performance for STAMP Benchmarks       122         5.11 RTM versus TinySTM Energy Expenditure for STAMP Benchmarks       122                                                                                                    | 4 20 |                                                                         | 74   |

| 4.21       Pseudo-Code for Serial Fraction Analysis       98         4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead Analysis       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling       106         5.1       RTM Read-Set and Write-Set Capacity Test       112         5.2       RTM Abort Rate versus Transaction Duration       113         5.3       Eigenbench Working-Set Size       115         5.4       Eigenbench Transaction Length       116         5.5       Eigenbench Temporal Locality       117         5.6       Eigenbench Contention       118         5.8       Eigenbench Predominance       120         5.9       Eigenbench Predominance       120         5.10       RTM versus TinySTM Performance for STAMP Benchmarks       122      <                                                                                                                                     | 4.20 |                                                                         | 94   |

| 4.22       Effects of Serial Fraction on the Energy Efficiency of Thread Scaling .       100         4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis .       101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling .       102         4.25       Effects of Bandwidth Contention on Energy Efficiency of Thread Scaling 103       102         4.26       Pseudo-Code for Locking Mechanism Overhead Analysis .       105         4.27       Effects of Locking-Mechanism Overhead on the Energy Efficiency of Thread Scaling .       106         5.1       RTM Read-Set and Write-Set Capacity Test .       112         5.2       RTM Abort Rate versus Transaction Duration .       113         5.3       Eigenbench Working-Set Size .       116         5.5       Eigenbench Transaction Length .       117         5.6       Eigenbench Temporal Locality .       117         5.7       Eigenbench Predominance .       119         5.8       Eigenbench Predominance .       120         5.10       RTM versus TinySTM Performance for STAMP Benchmarks .       122                                                                                                                                                                                                                                                                                                                     | 4.21 |                                                                         | 98   |

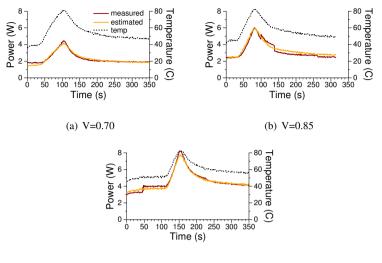

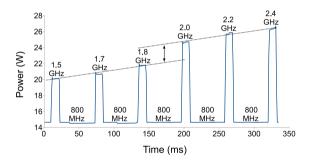

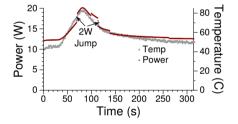

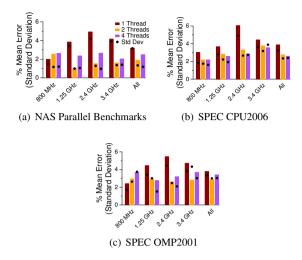

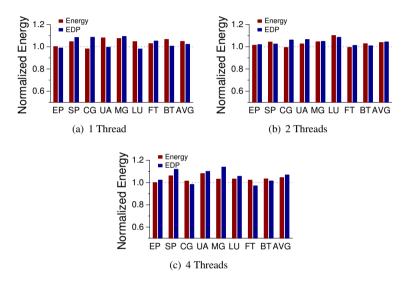

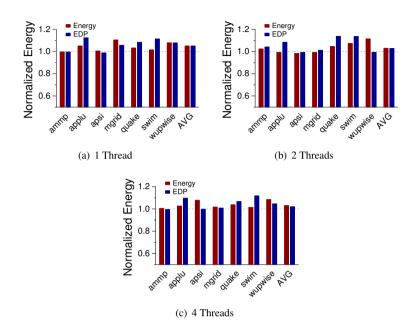

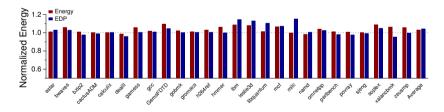

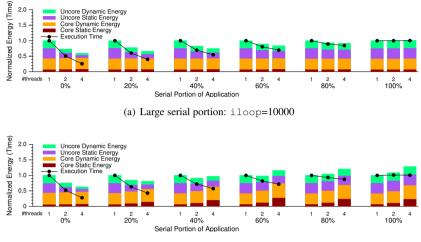

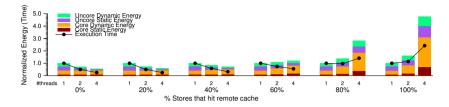

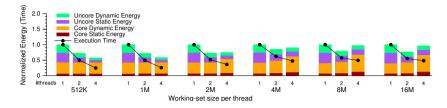

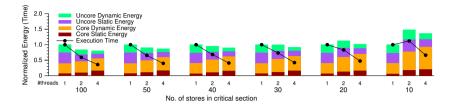

| 4.23       Pseudo-Code for Core-to-core Communication Overhead Analysis 101         4.24       Effects of Core-to-core Communication on Energy Efficiency of Thread Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.22 | •                                                                       | 100  |