## Hybrid Algorithms for Efficient Cholesky Decomposition and Matrix Inverse using Multicore CPUs with GPU Accelerators

Gary Macindoe

A dissertation submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

of

UCL.

| I, Gary Macindoe, confirm that the work present has been derived from other sources, I confirm |   |

|------------------------------------------------------------------------------------------------|---|

| Signature                                                                                      | : |

### **Abstract**

The use of linear algebra routines is fundamental to many areas of computational science, yet their implementation in software still forms the main computational bottleneck in many widely used algorithms. In machine learning and computational statistics, for example, the use of Gaussian distributions is ubiquitous, and routines for calculating the Cholesky decomposition, matrix inverse and matrix determinant must often be called many thousands of times for common algorithms, such as Markov chain Monte Carlo. These linear algebra routines consume most of the total computational time of a wide range of statistical methods, and any improvements in this area will therefore greatly increase the overall efficiency of algorithms used in many scientific application areas.

The importance of linear algebra algorithms is clear from the substantial effort that has been invested over the last 25 years in producing low-level software libraries such as LAPACK, which generally optimise these linear algebra routines by breaking up a large problem into smaller problems that may be computed independently. The performance of such libraries is however strongly dependent on the specific hardware available. LAPACK was originally developed for single core processors with a memory hierarchy, whereas modern day computers often consist of mixed architectures, with large numbers of parallel cores and graphics processing units (GPU) being used alongside traditional CPUs. The challenge lies in making optimal use of these different types of computing units, which generally have very different processor speeds and types of memory.

In this thesis we develop novel low-level algorithms that may be generally employed in blocked linear algebra routines, which automatically optimise themselves to take full advantage of the variety of heterogenous architectures that may be available. We present a comparison of our methods with MAGMA, the state of the art open source implementation of LAPACK designed specifically for hybrid architectures, and demonstrate up to 400% increase in speed that may be obtained using our novel algorithms, specifically when running commonly used Cholesky matrix decomposition, matrix inverse and matrix determinant routines.

## **Original Contributions**

The main contributions in this thesis are a collection of optimised algorithms that may be applied to general blocked linear algebra routines on hybrid and heterogenous architectures, such as systems with a multicore CPU and GPU accelerator, and systems consisting of multiple GPU accelerators. The first contribution is a new automated approach for blocked linear algebra routines that allows a new level of dynamic blocking to balance the workload more efficiently between heterogenous CPU and GPU computing devices, which have varying clock speeds and very different memory capacities. The second contribution considers the problem of transferring diagonal submatrices between CPU memory and GPU memory, which is an essential operation in many blocked linear algebra routines. We develop a novel algorithm for achieving this transfer efficiently and demonstrate the resulting improvement in speed. The third contribution is an original method for running multiple GPU kernel functions simultaneously on GPUs that do not have inherent hardware support for this capability. In these cases, a large number of GPU processors may often be left idle, waiting for a single kernel to complete. We demonstrate our algorithm using an example whereby a Cholesky decomposition kernel may be run concurrently with a matrix multiply kernel, achieving much higher performance and efficiency than previously possible on the same hardware using existing state of the art linear algebra libraries. We employ the Cholesky decomposition, matrix inverse and determinant operations as motivating examples, and demonstrate up to a 400% increase in speed that may be obtained using combinations of the novel approaches presented.

# Acknowledgements

This thesis was funded by the EPSRC grant, EP/E052029/1.

## **Contents**

| 1 | Intr | oductio | n                                                          | 1  |

|---|------|---------|------------------------------------------------------------|----|

|   | 1.1  | Comp    | uter Simulations                                           | 4  |

|   |      | 1.1.1   | Generating Random Numbers on a Computer                    | 4  |

|   | 1.2  | Appro   | aches to Parallel Simulation                               | 5  |

|   |      | 1.2.1   | Communication and Synchronisation                          | 6  |

|   |      | 1.2.2   | Parallel Random Number Generators                          | 6  |

|   | 1.3  | Hardw   | rare Accelerators                                          | 6  |

|   |      | 1.3.1   | Hybrid Multicore Parallel Programming                      | 6  |

|   |      | 1.3.2   | GPGPU                                                      | 7  |

|   | 1.4  | Summ    | ary                                                        | 9  |

| 2 | Rela | ited Wo | rk                                                         | 11 |

|   | 2.1  | Techno  | ologies to Parallelise Existing Code                       | 11 |

|   |      | 2.1.1   | MPI                                                        | 11 |

|   |      | 2.1.2   | OpenMP                                                     | 12 |

|   |      | 2.1.3   | SSE                                                        | 13 |

|   |      | 2.1.4   | Compiler Autovectorisation                                 | 15 |

|   |      | 2.1.5   | CUDA                                                       | 16 |

|   |      | 2.1.6   | OpenCL                                                     | 17 |

|   |      | 2.1.7   | HMPP                                                       | 18 |

|   | 2.2  | Paralle | el MCMC Implementations                                    | 19 |

|   |      | 2.2.1   | Parallel Pseudo-Random Number Generation                   | 19 |

|   |      | 2.2.2   | General Solutions for Parallelising Monte Carlo Algorithms | 26 |

|   |      | 2.2.3   | Specific Parallel Monte Carlo Algorithms                   | 31 |

|   | 2.3  | Paralle | el Numerical Libraries                                     | 35 |

|   |      | 2.3.1   | LAPACK                                                     | 35 |

|   |      | 2.3.2   | Optimised BLAS                                             | 38 |

| Contents | vii |

|----------|-----|

|----------|-----|

|   |     | 2.3.3   | ATLAS                                            | 39 |

|---|-----|---------|--------------------------------------------------|----|

|   |     | 2.3.4   | Linear Algebra on GPUs                           | 41 |

|   |     | 2.3.5   | CULA                                             | 45 |

|   |     | 2.3.6   | MAGMA                                            | 46 |

|   | 2.4 | Summ    | ary                                              | 56 |

| 3 | Gen | eral Me | ethodology                                       | 58 |

|   | 3.1 | Repres  | senting Matrices and Vectors in memory           | 60 |

|   |     | 3.1.1   | Host Memory                                      | 60 |

|   |     | 3.1.2   | GPU Memory                                       | 61 |

|   |     | 3.1.3   | Copying Matrices and Vectors                     | 62 |

|   | 3.2 | Theore  | etical Instruction Throughput                    | 63 |

|   | 3.3 | Design  | n of Linear Algebra functions                    | 65 |

|   |     | 3.3.1   | Automatic Vectorisation of C code for the CPU    | 65 |

|   |     | 3.3.2   | Use of C++ templates for GPU kernels             | 67 |

|   |     | 3.3.3   | Generating Extra Precisions                      | 68 |

|   |     | 3.3.4   | Exploiting the differences between SIMT and SIMD | 69 |

|   | 3.4 | Using   | multiple GPUs                                    | 70 |

|   | 3.5 | Bench   | marks and Error Analysis                         | 71 |

|   |     | 3.5.1   | GPU Occupancy                                    | 71 |

|   |     | 3.5.2   | Timing Methods                                   | 71 |

|   |     | 3.5.3   | Tuning the Block Size                            | 72 |

|   |     | 3.5.4   | Floating Point Error Analysis                    | 73 |

|   | 3.6 | Summ    | ary                                              | 74 |

| 4 | Hyb | rid Cho | olesky Decomposition                             | 75 |

|   | 4.1 | Introdu | uction                                           | 75 |

|   |     | 4.1.1   | LAPACK Unblocked Algorithm                       | 76 |

|   |     | 4.1.2   | LAPACK Blocked Algorithm                         | 77 |

|   |     | 4.1.3   | Hybrid Blocked Algorithm                         | 78 |

|   | 4.2 | Curren  | nt State of the Art Methods                      | 80 |

|   |     | 4.2.1   | GPU Matrix Multiply                              | 81 |

|   |     | 4.2.2   | GPU Symmetric Rank-K Update                      | 86 |

|   |     | 4.2.3   | GPU Triangular Solve                             | 88 |

|   | 4.3 | Improv  | vements on the State of the Art                  | 92 |

viii Contents

|   |     | 4.3.1   | Unblocked Cholesky on the CPU                                       | 92   |

|---|-----|---------|---------------------------------------------------------------------|------|

|   |     | 4.3.2   | Optimising Diagonal Block Transfer                                  | 96   |

|   |     | 4.3.3   | Dynamic Block Sizing                                                | 96   |

|   |     | 4.3.4   | Unblocked Cholesky on the GPU                                       | 99   |

|   |     | 4.3.5   | Combining Unblocked Cholesky and Inverse with Matrix Multiplica-    |      |

|   |     |         | tion on the GPU                                                     | 100  |

|   |     | 4.3.6   | Alternatives to GPU Triangular Solve                                | 102  |

|   | 4.4 | Result  | s                                                                   | 103  |

|   | 4.5 | Using   | Multiple GPUs                                                       | 105  |

|   | 4.6 | Discus  | ssion                                                               | 109  |

| 5 | Hyb | rid Cho | olesky Inverse                                                      | 118  |

|   | 5.1 | Introd  | uction                                                              | 118  |

|   |     | 5.1.1   | LAPACK Unblocked Algorithm                                          | 118  |

|   |     | 5.1.2   | LAPACK Blocked Algorithm                                            | 120  |

|   |     | 5.1.3   | Hybrid Blocked Algorithm                                            | 124  |

|   | 5.2 | Impro   | vements on the State of the Art                                     | 124  |

|   |     | 5.2.1   | GPU Triangular Matrix Multiply                                      | 125  |

|   |     | 5.2.2   | Unblocked Triangular Inverse on the CPU                             | 126  |

|   |     | 5.2.3   | Unblocked Triangular Inverse on the GPU                             | 129  |

|   |     | 5.2.4   | Unblocked Triangular Product on the CPU                             | 130  |

|   |     | 5.2.5   | Unblocked Triangular Product on the GPU                             | 131  |

|   |     | 5.2.6   | Alternatives to GPU Triangular Solve                                | 131  |

|   |     | 5.2.7   | Improving Diagonal Block Transfer                                   | 133  |

|   |     | 5.2.8   | Dynamic Block Sizing                                                | 134  |

|   |     | 5.2.9   | Combining Unblocked kernels with Matrix Multiplication on the GPU . | 135  |

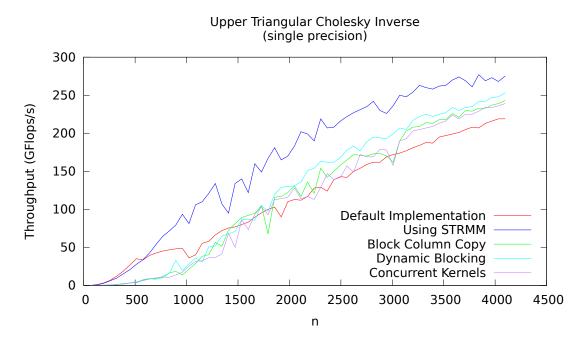

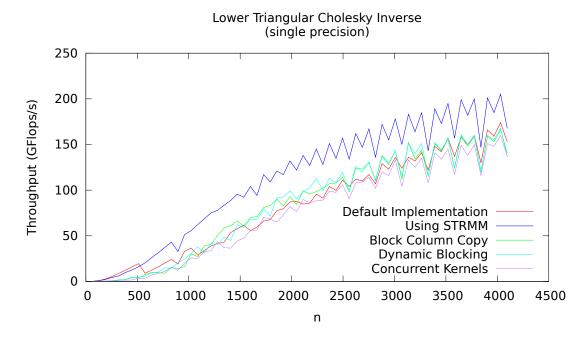

|   | 5.3 | Result  | s                                                                   | 136  |

|   | 5.4 | Discus  | ssion                                                               | 137  |

| 6 | Hyb | rid Cho | olesky Determinant                                                  | 143  |

|   | 6.1 | Introd  | uction                                                              | 143  |

|   | 6.2 | Metho   | ods                                                                 | 144  |

|   |     | 6.2.1   | Parallel Reduction on the GPU                                       | 144  |

|   |     | 6.2.2   | Improving Memory Bandwidth                                          | 145  |

|   | 63  | Pecult  |                                                                     | 1/15 |

|   |     | Contents                | ix  |

|---|-----|-------------------------|-----|

|   | 6.4 | Discussion              | 146 |

| 7 | Con | clusions and Discussion | 148 |

# **List of Figures**

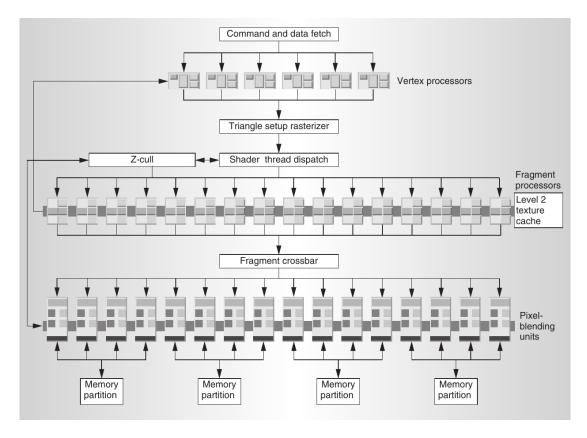

| 1.1  | Vertex and fragment processors in the nVidia GeForce 6800 GPU                     | 8   |

|------|-----------------------------------------------------------------------------------|-----|

| 3.1  | Exploiting the SIMT architecture to execute multiple kernels simultaneously       | 70  |

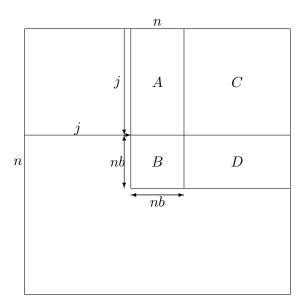

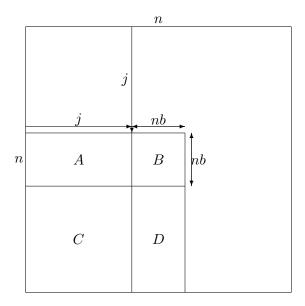

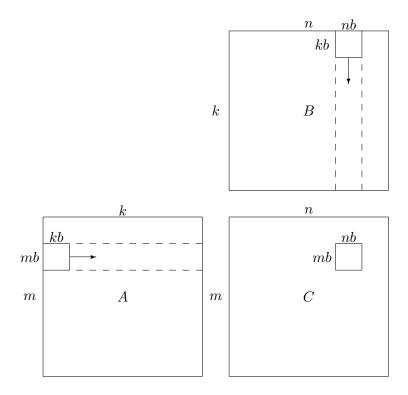

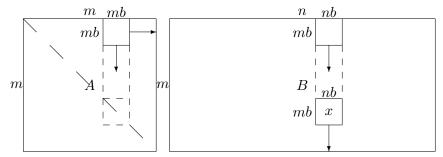

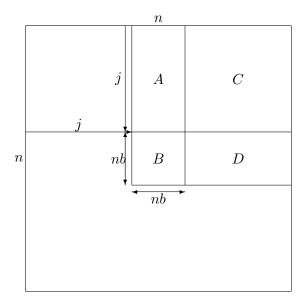

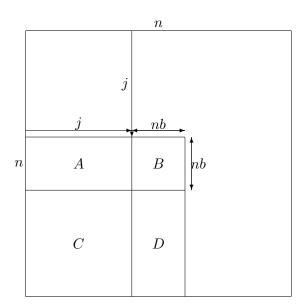

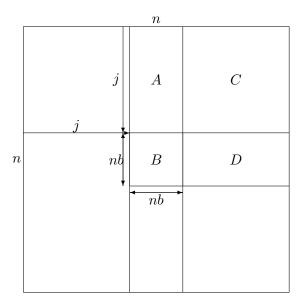

| 4.1  | Submatrices used in the blocked upper triangular Cholesky decomposition           | 78  |

| 4.2  | Submatrices used in the blocked lower triangular Cholesky decomposition $\ . \ .$ | 80  |

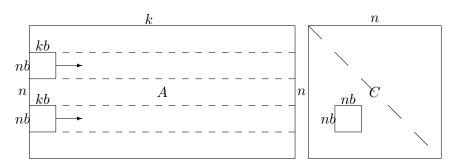

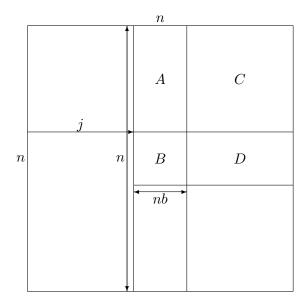

| 4.3  | Blocked matrix multiply                                                           | 82  |

| 4.4  | Blocked symmetric rank-K update                                                   | 87  |

| 4.5  | Blocked triangular matrix solve                                                   | 89  |

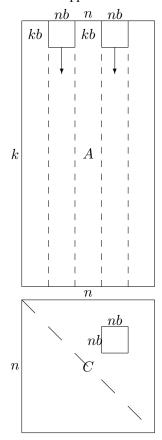

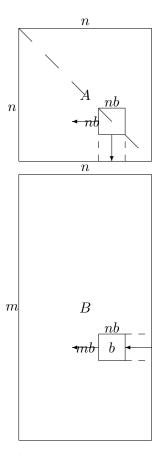

| 4.6  | Extending the diagonal block to a column in the upper triangular Cholesky         |     |

|      | decomposition                                                                     | 97  |

| 4.7  | Extending the diagonal block to a column in the lower triangular Cholesky de-     |     |

|      | composition                                                                       | 98  |

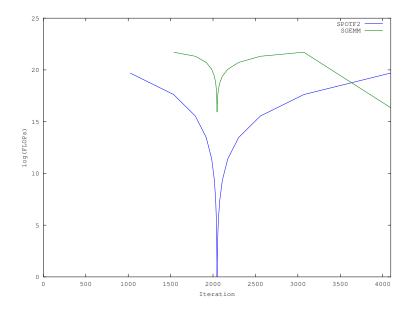

| 4.8  | FLOP counts for each operation in the Cholesky decomposition using a static       |     |

|      | block size                                                                        | 110 |

| 4.9  | FLOP counts for each operation in the Cholesky decomposition using an in-         |     |

|      | creasing then decreasing block size                                               | 111 |

| 4.10 | FLOP counts for each operation in the Cholesky decomposition using a de-          |     |

|      | creasing then increasing block size                                               | 112 |

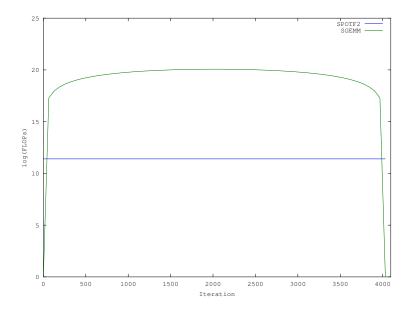

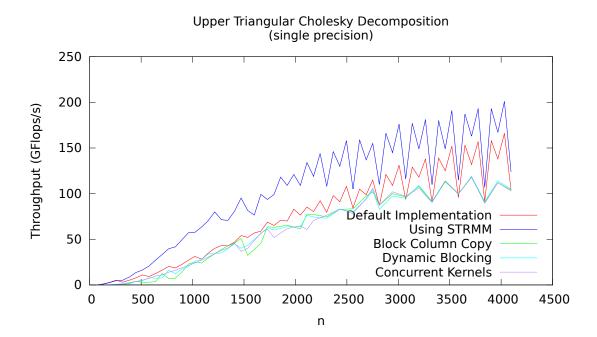

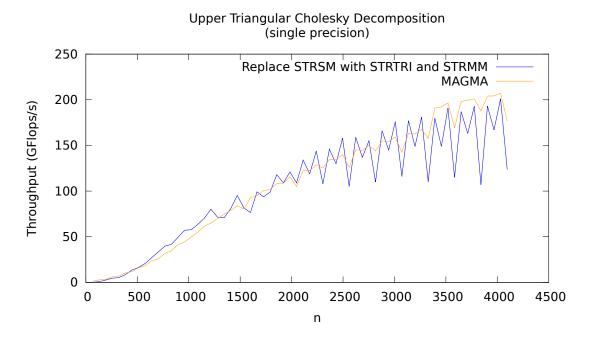

| 4.11 | Performance of our upper triangular hybrid Cholesky decomposition in single       |     |

|      | precision                                                                         | 113 |

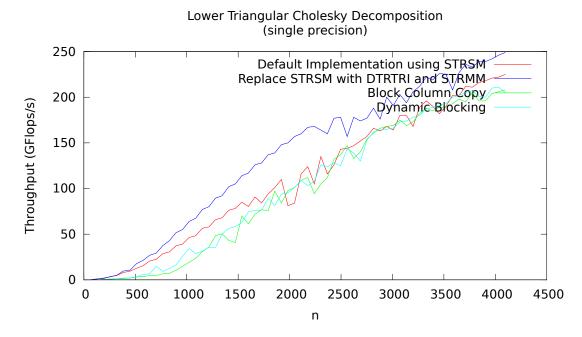

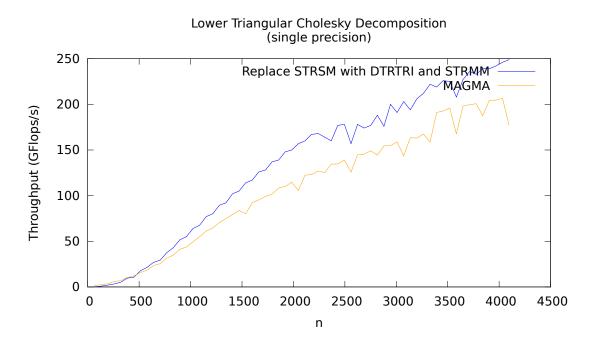

| 4.12 | Performance of our lower triangular hybrid Cholesky decomposition in single       |     |

|      | precision                                                                         | 114 |

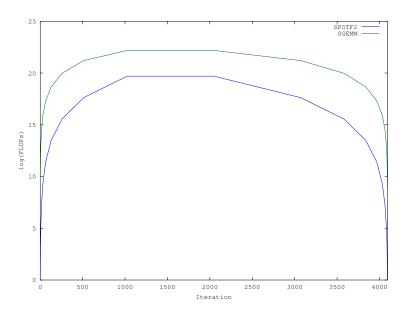

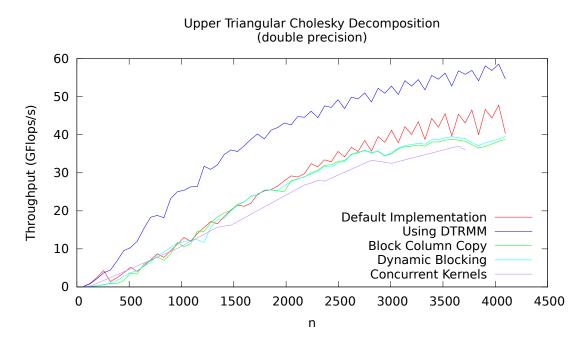

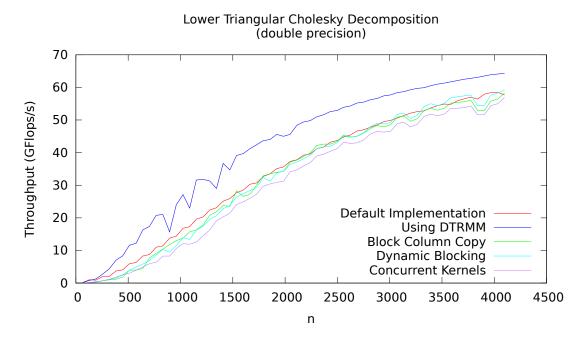

| 4.13 | Performance of our upper triangular hybrid Cholesky decomposition in double       |     |

|      | precision                                                                         | 115 |

| 4.14 | Performance of our lower triangular hybrid Cholesky decomposition in double       |     |

|      | precision                                                                         | 115 |

| 4.15 | Performance of our upper triangular nybrid Cholesky decomposition compared           |                 |

|------|--------------------------------------------------------------------------------------|-----------------|

|      | to the MAGMA library in single precision                                             | l 1 <i>6</i>    |

| 4.16 | Performance of our lower triangular hybrid Cholesky decomposition compared           |                 |

|      | to the MAGMA library in single precision                                             | l 17            |

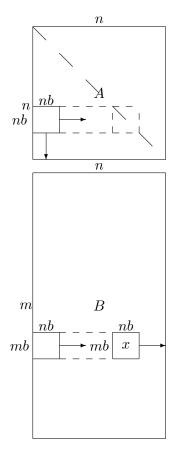

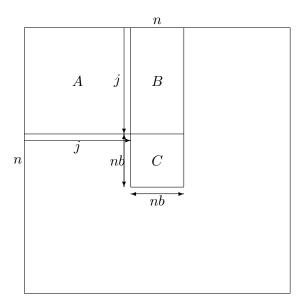

| 5.1  | Submatrices used in the blocked upper triangular matrix product                      | 122             |

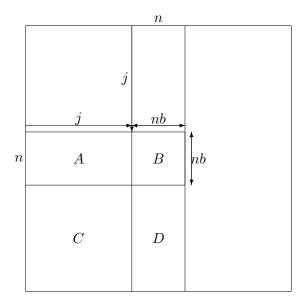

| 5.2  | Submatrices used in the blocked lower triangular matrix product                      | 122             |

| 5.3  | Submatrices used in the blocked upper triangular matrix product                      | 123             |

| 5.4  | Submatrices used in the blocked lower triangular matrix product                      | 123             |

| 5.5  | Blocked triangular matrix multiply                                                   | 127             |

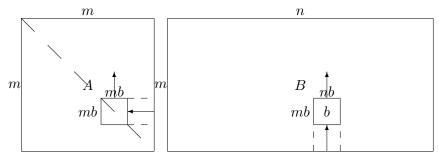

| 5.6  | Extending the block diagonal column in the upper triangular matrix product 1         | 133             |

| 5.7  | Extending the block diagonal column in the lower triangular matrix product $$ . $$ . | 134             |

| 5.8  | Submatrices used in the blocked upper triangular matrix inverse                      | 134             |

| 5.9  | Submatrices used in the blocked lower triangular matrix inverse                      | 135             |

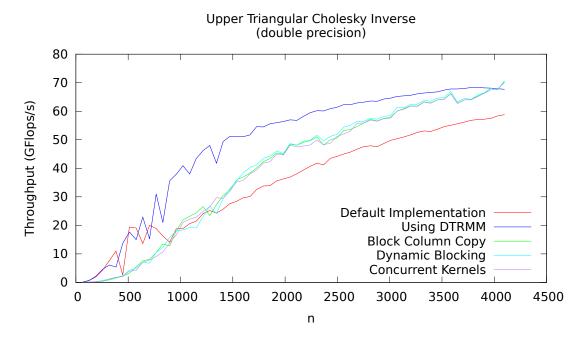

| 5.10 | Performance of the upper triangular hybrid Cholesky inverse in single precision 1    | 137             |

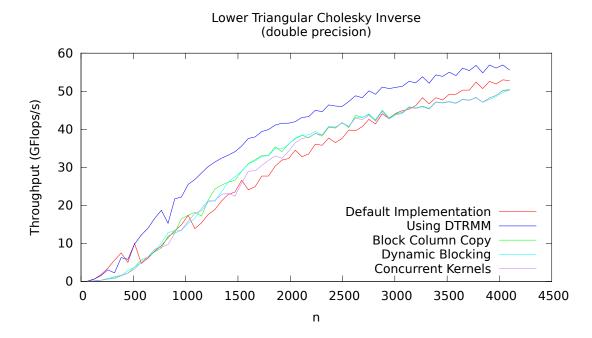

| 5.11 | Performance of the lower triangular hybrid Cholesky inverse in single precision 1    | 138             |

| 5.12 | Performance of the upper triangular hybrid Cholesky inverse in double precision 1    | 139             |

| 5.13 | Performance of the lower triangular hybrid Cholesky inverse in double precision 1    | 140             |

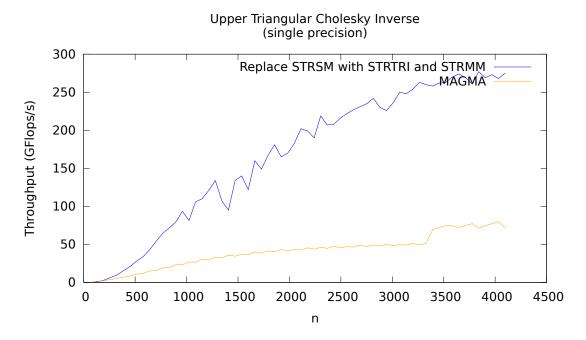

| 5.14 | Performance of our upper triangular hybrid Cholesky inverse compared to the          |                 |

|      | MAGMA library in single precision                                                    | 141             |

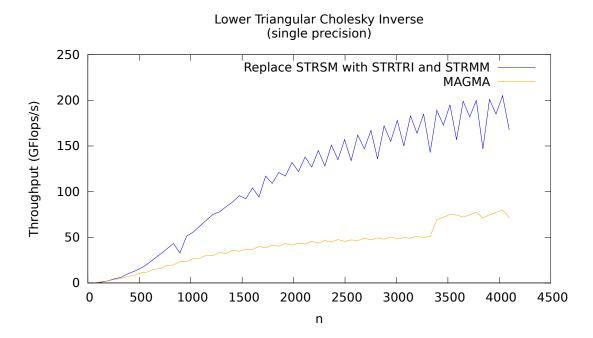

| 5.15 | Performance of the lower triangular hybrid Cholesky inverse compared to the          |                 |

|      | MAGMA library in single precision                                                    | 142             |

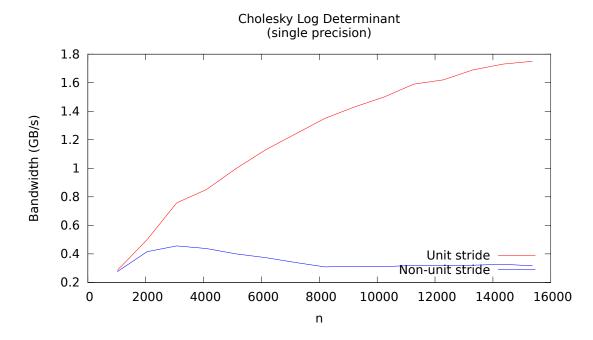

| 6.1  | Performance of the GPU Cholesky log determinant algorithm in single precision 1      | l4 <del>6</del> |

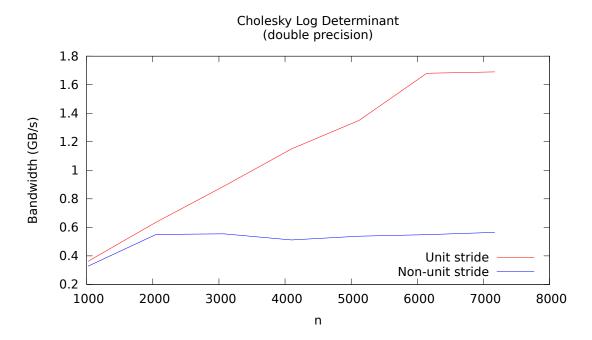

| 6.2  | Performance of the GPU Cholesky log determinant algorithm in double precision 1      | 147             |

## **List of Tables**

| 2.1 | BLAS and LAPACK acronyms used throughout this thesis                           | 37  |

|-----|--------------------------------------------------------------------------------|-----|

| 2.2 | The three variants of the blocked Cholesky decomposition                       | 44  |

| 2.3 | The three variants of the blocked LU decomposition                             | 44  |

| 3.1 | Specifications of the nVidia GeForce GTX 285 GPU used in this study            | 59  |

| 3.2 | Summary of features of CUDA Compute Capability 1.3 GPUs                        | 59  |

| 3.3 | Results from the PCI Express benchmark showing the attainable bandwidth and    |     |

|     | overhead in setting up a copy                                                  | 63  |

| 3.4 | Throughput for floating point instructions on CUDA Compute Capability 1.x      |     |

|     | GPUs                                                                           | 64  |

| 3.5 | Specifications of the Intel Core i7-965 Extreme Edition CPU used in this study | 64  |

| 3.6 | Instruction throughput of the nVidia GeForce GTX 285 GPU                       | 65  |

| 4.1 | FLOP:word ratios for the nVidia GeForce GTX 285                                | 82  |

| 4.2 | Block sizes chosen for GPU SGEMM                                               | 86  |

| 4.3 | Block sizes chosen for GPU DGEMM                                               | 88  |

| 4.4 | Block sizes for GPU STRSM                                                      | 92  |

| 4.5 | Block sizes for GPU DTRSM                                                      | 93  |

| 4.6 | Resource usage of the unblocked Cholesky decomposition kernels for the GPU     | 101 |

| 4.7 | Resource usage of the combined Cholesky decomposition, inverse and matrix      |     |

|     | multiply GPU kernels.                                                          | 102 |

| 4.8 | MultiGPU SGEMM block sizes for $op(A) = A.$                                    | 107 |

| 4.9 | MultiGPU SGEMM block sizes for $op(A) = A^T$                                   | 108 |

| 5.1 | Block sizes and resource usage for the STRMM GPU kernel                        | 126 |

# **List of Algorithms**

| 1 | Blockwise Upper Triangular Cholesky decomposition                              |

|---|--------------------------------------------------------------------------------|

| 2 | Blockwise Lower Triangular Cholesky decomposition                              |

| 3 | Generating random positive definite matrices with desired condition number 104 |

| 4 | Blockwise Upper Triangular Matrix Inverse                                      |

| 5 | Blockwise Lower Triangular Matrix Inverse                                      |

| 6 | Blockwise Upper Triangular Matrix Product                                      |

| 7 | Blockwise Lower Triangular Matrix Product                                      |

# Listings

| 3.1 | GCC requires an extra unsafe math optimisation flag before it will vectorise   |

|-----|--------------------------------------------------------------------------------|

|     | reductions, unlike ICC which vectorises them by default 6                      |

| 3.2 | ICC will vectorise the non-contiguous second loop as well as the contiguous    |

|     | first loop, whereas GCC will only vectorise the first                          |

| 3.3 | GCC and ICC will incorrectly detect a data dependency across iterations of the |

|     | inner loop and refuse to vectorise it                                          |

| 3.4 | GCC and ICC will correctly vectorise the inner loop after one array has been   |

|     | aliased to circumvent the dependency checker                                   |

| 4.1 | Unblocked Cholesky Decomposition of an Upper Triangular Matrix                 |

| 4.2 | Unblocked Cholesky Decomposition of a Lower Triangular Matrix                  |

| 4.3 | Optimised unblocked Cholesky decomposition algorithm                           |

| 5.1 | Unblocked Upper Triangular Inverse                                             |

| 5.2 | Unblocked Lower Triangular Inverse                                             |

| 5.3 | Unblocked Upper Triangular Product                                             |

| 5.4 | Unblocked Lower Triangular Product                                             |

| 5.5 | Optimised unblocked triangular inverse algorithm                               |

| 5.6 | Optimised unblocked triangular product algorithm                               |

| 5.7 | Triangular Inverse using matrix multiplication in place of matrix solve 13     |

#### Chapter 1

## Introduction

Since the 18th century, the use of mathematical models has been successfully employed to make scientific predictions about the world, and indeed the wider universe, in which we live. Nowadays, many of the mathematical models of interest are too complex to be tackled by pen and paper and require high speed computing to realise their utility fully. High performance computing has developed into a vital component of modern scientific inquiry, and this has become particularly noticeable over the last 20 years with the advent of low-cost processing power [98, 24].

Computational modelling enables us to analyse and make sense of larger amounts of data, and allows us to make testable predictions, with computer simulations often taking the place of expensive or sometimes even impossible physical experiments [110]. Perhaps most significantly, this increase in computational power gives us the capability of employing powerful statistical methodology that was previously beyond our reach in many cases; Bayesian approaches are a prominent example [128]. Bayesian methodology uses the language of probability theory and provides scientists with a means of reasoning in a consistent manner about the sources of uncertainty that often strongly affect the scientific questions of interest [67, 96]. Such methods allow us to quantify the uncertainty associated with both the measurements from any given experimental setup and as well as our understanding of the underlying structure of the physical system. In terms of mathematical modelling, they allow us to quantify uncertainty in the unknown parameters of a model as well as the uncertainty in the mathematical form of the model itself [16, 96].

Bayesian computing consists mainly of estimating integrals that are often of high dimension. Such problems can be solved using Monte Carlo methods [52, 104], however these are usually computationally intensive procedures that involve a large number of random simulations from the probability distribution of interest; it is no coincidence that the recent rise in the use of Bayesian methodology has occurred at the same time as wider availability of low-cost

high speed computer hardware [108, 128]. In the rare cases when this distribution is known, samples may be drawn with relative efficiency. Usually however, calculation of the distribution is only available to us by solving a complex mathematical model and employing a more sophisticated, computationally intensive simulation method [106].

As a motivating example, Markov chain Monte Carlo (MCMC) [20, 45, 16] algorithms may be used to generate samples from arbitrary posterior probability distributions given by Bayes' Theorem:

$$p(\boldsymbol{\theta}|\mathbf{y}) \propto p(\mathbf{y}|\boldsymbol{\theta})p(\boldsymbol{\theta})$$

(1.1)

In Bayes' theorem,  $p(y|\theta)$  is the likelihood and offers a measure of mismatch between the observed data y and the mathematical model evaluated with model parameters  $\theta$ . The prior  $p(\theta)$  characterises our prior knowledge regarding the parameter values that might be plausibly correct [105]. The posterior distribution  $p(\theta|y)$  characterises our final estimate of uncertainty, and provides a way of consistently and automatically taking into account information from both the prior and the observed data.

A Markov chain [45] provides a sequence of random variables, in which each value in the sequence depends only on the previous value. Such a Markov chain can be constructed so that it converges to a specified stationary distribution of interest [120]; the posterior distribution in the Bayesian context [105]. The chain is started at a random value, usually a random sample from the prior probability distribution, and a "burn-in" period [20, 33, 57, 128] is necessary to allow the chain time to explore the parameter space and converge to the regions of highest probability. A Markov chain generates correlated samples from the chosen target distribution and may be run to collect as many samples as required to obtain a particular level of statistical accuracy.

The most popular MCMC algorithm is the Metropolis-Hastings algorithm [83, 54] and most other MCMC algorithms can be shown to be special cases of it [16]. Metropolis-Hastings is part of a subclass of MCMC methods called accept-reject algorithms, since they generate samples according to some proposal distribution and then either accept or reject the sample according to some acceptance criteria. In Metropolis-Hastings a new sample is generated according to some proposal probability distribution. The Metropolis-Hastings ratio is then calculated as:

$$\alpha(x,x^*) = \frac{p(x^*)q(x|x^*)}{p(x)q(x^*|x)},$$

where x is the current sample,  $x^*$  is the proposed sample and p and q are the target and proposal probability density functions, respectively. The sample  $x^*$  is accepted as the next sample in the chain with probability  $\alpha$ . The Metropolis-Hastings algorithm is simple to implement but its performance is highly dependent on the choice of proposal distribution [16]. A Markov Chain is said to "mix" well if explores all regions of the distribution and makes large steps that are accepted with high probability [16].

For certain problems, Monte Carlo methods require a great amount of processing time, sometimes even weeks [128]. There is therefore a great demand for high performance numerical algorithms for simulation that harness the potential benefits of parallel processing and reduce computation time [108, 128]. Up until the end of last century numerical algorithms were designed primarily to run efficiently on a single core CPU. These algorithms enjoyed an automatic performance increase with every new generation of CPUs according to Moore's Law [85], which states that the transistor count on a silicon chip will double approximately every 18 months as newer manufacturing processes shrink the size of the transistor and in turn allow an increase in CPU clock speeds. Other components in a computer system however are not governed by Moore's Law and consequently, as CPU speeds were increasing, RAM speeds and latencies did not keep up [39]. Recently there has been a shift in the CPU industry to increase transistor count in CPUs by adding more CPU cores that operate independently of one another while keeping the CPU speed the same [46]. Numerical algorithms are therefore having to be redesigned to exploit the performance available by running operations in parallel on multi-core CPU architectures [13]. In addition, with the advent of general purpose computation on graphics processing units (GPGPU), numerical algorithms are being redesigned to include the use of incredibly powerful parallel processing available from GPUs.

BLAS [69] and LAPACK [15] are two numerical libraries that are currently being redesigned to exploit parallel processing. The BLAS library is split into three sections depending on the algorithmic complexity. BLAS 1 algorithms are O(N) complexity, BLAS 2 algorithms are  $O(N^2)$  and BLAS 3 algorithms are  $O(N^3)$ . GEMM (general matrix multiplication) is a BLAS 3 operation and one of the most basic routines from which all other BLAS 3 operations can be derived [66]. The performance of BLAS 3 algorithms may be more easily improved on parallel architectures than BLAS 1 or BLAS 2 algorithms, as they are more amenable to being split into multiple small independent workloads that can be processed in parallel by separate processing units [37]. They also have a higher ratio of floating point operations (Flops) to memory bandwidth requirements, which is also known as computational intensity [25, 31]. The LAPACK library provides more complicated algorithms than BLAS, including linear system

solvers and matrix decomposition routines. LAPACK uses BLAS operations as integral parts of its algorithms, and therefore its performance is highly dependent on an optimised BLAS library being available. Many hardware vendors supply optimised BLAS libraries for particular architectures, such as the AMD Core Math Library [2] and the Intel Math Kernel Library [4].

#### 1.1 Computer Simulations

Performing a numerical simulation on a computer can bring accuracy problems due to the way floating point numbers are handled [48]. Floating point numbers are represented on a computer as an integer amount (the mantissa) and an integer exponent. This provides a fixed number of significant digits to quantify real numbers and accuracy can be lost when performing mathematical operations on values with large differences in magnitude.

Higham [55] presents a comparison of the theoretical error bounds of five different methods of recursively summing a list of floating point numbers. These include first sorting the list in increasing or decreasing order of value or absolute value; summing in pairs of values of similar magnitude; summing the negative values and positive values separately; and keeping track of a low magnitude error and applying it to each addition in order to correct any error from the previous addition [61]. Each method in the order listed increases the number of operations required to sum the list and it is up to the programmer implementing the summation to choose an appropriate algorithm to balance complexity and speed with numerical error.

#### 1.1.1 Generating Random Numbers on a Computer

Monte Carlo simulations require a large amount of random numbers. This presents a problem as computers are deterministic by nature and need special algorithms, known as pseudo-random number generators, to provide streams of numbers that statistically have the same properties as those produced randomly [72]. Pseudo-random number generators consist of a state, a function to initialise the state to some value dependent on a seed, a function to update the state every time a random number is drawn and a function to generate a random number from the current state. Given the deterministic nature of computations, the pseudo-random number generator will end up repeating its stream of numbers after a certain amount have been generated. This amount is known as the period of the generator. Pseudo-random number generator algorithms fall into several categories including Linear and Non-linear Congruential Generators, Lagged Fibonacci Generators, Linear Shift Feedback Registers and Tausworth Generators [117, 70]. Good random number generators have a small state, efficient functions, a large period and generate numbers with good randomness properties [117, 71].

#### 1.2 Approaches to Parallel Simulation

Since the advent of computers there have been efforts to use multiple machines to work on a problem simultaneously in an attempt to reduce the time taken to solve large problems. All that is needed to have computers work together is a means of communication between the processors doing the calculations. Examples range from local computers with more than one processor installed to multiple computers connected across the internet [121]. Any task can be divided into subtasks and, if they do not depend on one another, can be performed concurrently. Since there is more than one processor with possibly different capabilities involved in the simulation it is more efficient to distribute the workload among processors so that more capable processors do more work. Failure is also an issue when multiple processors are involved and techniques have been developed to cope with this, such as simply having the subtask repeated on a different processor when the original one fails to return a result.

Certain Monte Carlo algorithms such as computing the expected value of a function of a random variable are trivial to implement in parallel as they can be easily broken down into smaller subtasks and the results combined once each subtask has been completed. Parallelising Monte Carlo algorithms can however affect the bias and variance of the resulting estimate unless certain rules are followed when designing the simulation [108]. These rules are discussed in more detail in Section 2.2.2.

Markov chain Monte Carlo methods can also be implemented in parallel although this type of algorithm is less obvious to implement in parallel as the simulation of the next value in the chain is dependent on calculating the current value first. This is known as the Markov property. There are two approaches to completely parallelising MCMC methods: running multiple independent chains in parallel (similar to parallel Monte Carlo) and parallelising the generation of a single chain. Many researchers have investigated ways to speed up the generation of a single Markov chain using parallel processing [63, 24, 26, 119], including the use of parallel libraries for expensive, time-consuming operations, however the options are limited by the inherently sequential nature of this algorithm [128]. We note that MCMC algorithms often make use of Gaussian random variables, which require repeated use of Cholesky decomposition, matrix inverse and matrix determinant routines. For large matrices, the key idea of splitting these expensive operations into independent subtasks that may be computed in parallel becomes vital for achieving efficient running times.

#### 1.2.1 Communication and Synchronisation

When a program is to be implemented on a parallel computer it is critical that the size of each parallel subtask is large enough to outweigh any costs incurred performing interprocess communication [24]. For problems that can be split into large independent subtasks that each take a long time to execute, the speed of communication between processing nodes is not much of an issue. These coarse-grained parallel problems are thus suited to distributed memory clusters, where the speed of communication between nodes is on the order of milliseconds. Programs that are split into smaller parallel subtasks are suited to shared memory processors, such as multicore CPUs, which have faster interprocess communication. These are termed fine-grained parallel problems.

#### 1.2.2 Parallel Random Number Generators

In addition to the previously mentioned properties, pseudo-random number generators for parallel environments must also generate a sequence of random numbers for each processor that appears to be independent of the sequences being generated on the other processors. This means that the sequences cannot overlap at any point and that the numbers being generated on the processors cannot be used to guess the next number in any of the sequences. Methods of parallelising serial pseudo-random number generators include Leapfrog, sequential splitting and independent sequences [32], and shuffling Leapfrog [131]. Each method (apart from independent sequences) relies on being able to efficiently calculate an arbitrary element in the sequence [117, 32].

#### 1.3 Hardware Accelerators

A hardware accelerator is a specialised piece of hardware that performs a specific group of operations faster than it would take a more general purpose piece of hardware. Modern examples of hardware accelerators include graphics cards, which accelerate the numerical operations required to render 3D graphics. Unlike a traditional CPU, GPUs dedicate more space on each silicon chip to processing units, rather than memory caches and flow control, making them able to process data in a highly parallel fashion [94]. Recently there have been developments to allow graphics cards to be used for other applications that would benefit from the parallel processing power available using General Purpose Graphics Processing Unit (GPGPU) computing [74, 25, 73, 97].

#### 1.3.1 Hybrid Multicore Parallel Programming

HMPP [36] is a programming environment consisting of a compiler wrapper and a software library. Special commands are inserted into the application code to tag sections ("codelets")

that are to be executed on a hardware accelerator. These commands are parsed by the compiler wrapper to produce a version of the codelet that targets the hardware accelerator when compiled. A single codelet can be compiled for multiple targets and the required executable code can be determined at runtime depending on the hardware accelerators available. The original unaccelerated version of the program can be easily reproduced by recompiling with the original compiler, since the HMPP commands are inserted into regions of the code that are otherwise ignored (e.g. comments). This provides a way for software companies to experiment with accelerated versions of their products without altering the original code. HMPP currently supports Fortran and C with Java currently being developed. It can target OpenCL [12], CUDA [5] and OpenMP [34].

#### **1.3.2 GPGPU**

Early GPUs had separate types of processor for each stage of the 3D graphics rendering pipeline with the output from one processor being fed directly into the next [84, 75]. Triangles defining a 3D scene would have their orientation calculated by dedicated vertex processors. Fragment processors would then take the triangles and work out which of them are obscured by others in the 3D scene, resulting in fragments of the final image. The vertex and fragment processing stages of 3D graphics rendering have a lot of inherent parallelism [84, 97] and GPUs would take advantage of this by having several vertex and fragment processors to compute each vertex and fragment independently. As human vision is slow in comparison to the speed of GPUs [97], latency can be high with graphics rendering and many pixels can be at different stages of the processing pipeline at once. This is shown in Figure 1.1; in particular, having a fixed number of each type of processor implemented in hardware caused load balancing problems for scenes that have more vertices than fragments and vice versa, which cause one type of processor to have the majority of the processing workload.

As the complexity of 3D graphics increased programmers demanded more functionality from vertex and fragment processors [84]. As a result the processors gained increased functionality and were able to run vertex or pixel shader programs written in languages such as HLSL [99] or GLSL [113]. These languages allowed programs to be written that describe how each pixel of the final scene is to be shaded [84]. The first such graphics card to feature programmable vertex processors was the nVidia GeForce 3 in 2001 [74]. This was followed by the GeForce 6800 in 2005 which additionally featured programmable fragment processors [84]. Toolkits also emerged that enabled these processors to perform general purpose computation on the GPU giving rise to the field of GPGPU [97]. These toolkits allowed programmers to write code to be executed in parallel across the programmable shader cores [78, 25]. As the graph-

Figure 1.1: This is a block diagram of the graphics processing pipeline in the nVidia GeForce 6800 GPU [84]. Data flows into the six vertex processors at the top of the diagram and then into the 16 fragment processors and finally the 16 pixel blending units along the bottom of the diagram. Vertex processors calculate the geometry and orientation of the triangles defining a 3D scene while fragment processors work out which triangles are obscured by others in the final scene. Pixel blending units apply the colour information to the pixels in the final scene. Having a fixed function graphics pipeline creates load balancing issues as certain 3D scenes such as those with a large number of small triangles will use the vertex processors more than the fragment processors while other 3D scenes with a small number of large triangles will use the fragment processors more than the vertex processors.

ics card drivers only exposed Direct X or OpenGL APIs these toolkits provided a layer over the graphics APIs to allow data to be transferred into the vertex and pixel buffers, to execute arbitrary shader programs and download results from the framebuffer [97].

The generic operations added to both the vertex and pixel processors caused their functionality to overlap. In 2005 nVidia introduced the GeForce 6800 with unified graphics processing cores [84]. These are a single type of processor with generic functionality for running vertex or pixel shader programs. With the introduction of the GeForce 8800 nVidia also provides their own toolkit and API for GPGPU computing, named CUDA [89, 73]. AMD has also produced unified architecture GPUs along with several toolkits for GPU computing including CTM [6]. Both companies now contribute towards the OpenCL standard for GPU computing [115].

#### 1.4 Summary

The advent of multicore processors has meant that individual workstations are now inherently parallel computers. This has brought parallel computing into the mainstream, whereas previously it was reserved for those with large enough budgets for several computers and a network to connect them all. An advantage of a multicore processor is that connections between processing cores are many orders of magnitude faster than the connections in a computer network. In addition, current multicore processors have cores that are identical to each other and therefore algorithms may be more easily optimised and the workload more easily balanced across the available cores. In contrast, computer clusters may have processors of varying speed and differing specifications. A final advantage of multicore processing lies with its shared memory, which further simplifies the development of parallel code and allows efficient parallelism of algorithms that otherwise would not benefit from being run in a distributed parallel environment.

With the development of GPGPU computing and hardware accelerated computing however, parallel architectures have moved towards a heterogeneous, distributed memory environment. Although this type of system results in a far larger number of processing units at the programmer's disposal, it also introduces a number of significant challenges that need to be addressed. Firstly, there is greater communication overhead between the CPU and the accelerator, and this must be taken into account during algorithmic design to ensure efficiency. Secondly, we must now deal with multiple processors with differing specifications, which makes it harder to evenly and efficiently balance the workload.

In this thesis we consider these challenges and present novel approaches for redesigning blocked linear algebra operations to benefit from the multitude of parallel architectures currently available through GPUs. We begin in the next chapter by summarising existing technologies for general parallelisation of computer instructions on CPUs and GPUs. We then investigate the Markov chain Monte Carlo method in greater detail. This is a motivating example from Statistics that, due to the Markov property, would appear to have limited scope for parallelism unless one considers lower-level approaches such as the parallelism available in the underlying linear algebra routines that it utilises in order to further increase its computational efficiency and scalability. We discuss high-level approaches to parallelising Markov chain Monte Carlo algorithms, before delving deeper into the underlying linear algebra libraries that are employed within such statistical methods. We give an overview of current BLAS and LAPACK implementations available for different types of processing units, and review existing libraries developed for hybrid architectures, in particular the MAGMA library, which we use for benchmarking the contributions presented in the later chapters.

#### Chapter 2

### **Related Work**

There are many approaches to writing and extending computer codes for parallel distributed and shared memory architectures, and in this chapter we give a brief overview. We begin by giving a summary of technologies available for parallelising existing computer codes. We then consider the example of Markov chain Monte Carlo and review possible approaches to parallelisation of this useful class of algorithms, in particular focussing on parallelised random number generation and examining how the intrinsic structure of these methods limit the extent to which they may be parallelised. We conclude that further improvements in performance are likely to come only from more efficient parallelisation of the underlying linear algebra routines upon which MCMC methods strongly depend. Finally, we give an overview of the parallelised numerical libraries based on BLAS and LAPACK that are currently available for single processor, GPU and hybrid architectures.

### 2.1 Technologies to Parallelise Existing Code

#### 2.1.1 MPI

MPI [125] is a message passing library interface specification for programs using the message passing parallel programming model. The message passing parallel programming model moves data from the address space of one process into the address space of another. It is used primarily on distributed memory multiprocessor machines where the memories are connected by a communications network although it can also be used on shared memory machines. The MPI standard is a specification for a library that implements message passing [50, 43]. It does not specify which programming language it should be implemented in although language bindings for Fortran, C and C++ form part of the standard. Version 1.0 of the MPI standard was released in 1992 and adopted the best features of existing message passing systems [101, 27]. It was created by researchers from academic, government and industrial backgrounds mainly from the EU and US. The advantages of creating a standard for message passing are portability and ab-

straction as the standard does not specify how the library specification is to be implemented allowing vendors to implement part of it using specialised hardware to improve performance. The aim of the MPI Forum [42] is to create a practical, portable, efficient and flexible standard for message passing. The library API that forms part of the standard should allow for efficient and reliable communication in heterogeneous processing environments and also be thread-safe.

MPI has also been considered as the API of choice to implement message-passing between hardware accelerators [116]. Currently GPUs are under explicit control of a CPU and have no peer-to-peer message passing capabilities despite this being one of the features of the PCI-Express bus to which they are connected. MPI also currently only considers CPUs as sources or sinks of messages. Stuart *et al.* [116] compare three attempts at extending MPI to support GPUs, all of which have been made obsolete in some way or another due to improvements in GPU vendor libraries. They introduce their own extensions and discuss the modifications needed to the MPI standard. Firstly GPUs need to be able to communicate directly with each other over the PCI-Express bus and also with the network card in the host machine. Each accelerator will need to be assigned an MPI rank so that it can be the source or sink of any communications and an MPI library consisting of GPU functions would need to be written. MPI will also need new communicators to broadcast messages to all GPUs, all CPUs or all CPUs and GPUs within a particular machine.

#### **2.1.2 OpenMP**

OpenMP [34] is an API standard designed for shared memory parallel programming much in the same way that MPI is a standard for message passing. In order to have a scalable parallel application both scalable hardware and software are needed. Distributed memory systems provide scalable hardware for message passing so their scalability relies on software built on the message passing programming model. With the introduction of shared memory multiprocessing a message passing programming model became too elaborate and complex for software to scale well.

The OpenMP standard builds on existing standards for shared memory multiprocessing including MPI, POSIX Threads (PThreads) [86] and the unfinished X3H5 standard [109]. X3H5 was a project to develop an ANSI standard for shared memory multiprocessing but only got as far as implementing parallel loops when interest was lost due to the popularity of distributed memory systems. Using MPI for shared memory multiprocessing requires a lot of effort by the programmer to explicitly partition data structures across processors [34] and as a result the entire program must be rewritten to use the parallel data structures. PThreads [86] is a threading library for POSIX-compliant operating systems. It provides an interface to directly control op-

erating system threads and is very low-level. It is only available on POSIX-compliant systems so is not entirely portable and is not available for Fortran in which most scientific code is written. It uses a task-based programming model where each thread is assigned a task to perform rather than a data-parallel model which suits scientific code better.

OpenMP is a standard set of compiler directives to allow programmers to express parallelism and an API specification for an accompanying runtime library [29]. The directives are split into three sections to cover control structures, data sharing and synchronisation. An OpenMP aware compiler will process the directives to execute sections of code in parallel whereas a compiler that does not support OpenMP will simply ignore them. The standard is designed to be language agnostic however it specifies a set of compiler directives that are to be available in Fortran, C and C++. The standard builds on X3H5 to include support for coarse-grained parallelism as loop-level parallelism has limited scaling on shared memory architectures due to Amdahl's Law [51]. How well a parallel algorithm scales depends on how well it fits into the parallel programming model being used. OpenMP therefore has an additional set of directives allowing different parallel programming models such as task-based programming [17] and directives that can be nested allowing each sub-thread to further generate more sub-threads.

OpenMP implements parallelism using a "fork-join" model where a team of threads is created when a parallel directive is encountered [28]. It allows the programmer to specify which variables from the data environment are to be shared among threads and which are to be private. The compiler does all the work to efficiently execute sections of code in parallel and the programmer need not know the number of threads being created. This is in contrast to MPI, where data sharing must be done explicitly by the programmer, and in contrast to PThreads, where shared variables must have mutexes created to control accesses by multiple threads.

#### 2.1.3 SSE

Internet Streaming SIMD Extensions (SSE) is an Instruction Set Architecture developed by Intel to improve the performance of 3D graphics rendering on its 32-bit CPUs [118]. Intel's CPUs required a  $1.5-2\times$  increase in floating-point arithmetic performance to produce a noticeable improvement in 3D graphics quality. Graphics operations are SIMD parallel and adding SIMD units is a cost-effective way to improve floating-point performance on a general purpose CPU. This had already been done in earlier Intel CPUs with the MMX instruction set which performed SIMD operations on integers [100, 21]. When designing the new instructions Intel also studied how the CPU uses data and decided to introduce instructions that allow the programmer to differentiate between data that is reused and data that is only used once [118]. Data

that is reused should be loaded into the cache while data that is only used once should not be cached (potentially requiring some reusable data to be removed) and instead should be streamed through the processor. They also included a large amount of customer feedback from software developers when designing the new instructions in order to make them as general purpose as possible so that they would also provide a speed increase to other applications such as speech recognition and multimedia encoding.

SSE implements SIMD parallelism using a new set of 128-bit registers that can accommodate four single-precision floating point variables (or 32-bit integers, or two double-precision floating point variables or 64-bit integers) [21]. This provided the needed increase in floating point performance for 3D graphics while requiring the least increase in processor die area and complexity. Internally, Intel's CPUs already performed floating-point arithmetic in 80bit floating-point units so the increase from 80-bits to 128-bits was less of an implementation challenge than an increase to 256-bits or wider. For problem sizes that are not a multiple of the SIMD width the remaining elements must be processed separately therefore an increase in SIMD width gives diminishing returns as well as requiring increased memory bandwidth to keep the SIMD units supplied with data. The MMX instruction set reused the 80-bit x87 floating point registers to perform two-way SIMD operations on two 32-bit integers in the lower 64-bits of the register. This required no special operating system support [100, 21] although it meant that floating point arithmetic could not be performed at the same time as MMX integer operations and was more complex for the programmer to manage. The decision to use a new set of registers for SSE required explicit operating system support to save and restore the extra registers between context switches but means that scalar integer operations can be performed in parallel to SIMD floating point arithmetic [102] and improves general purpose performance due to an increased number of registers. SSE also moves scalar floating-point arithmetic to the lower bits of the new SSE registers, rather than keeping them in the existing MMX/x87 registers. This keeps results between SIMD and scalar arithmetic consistent as they now both performed in 32-bit precision rather than scalar arithmetic being performed in the extended 80-bit precision x87 registers as with MMX.

Memory operations on vector computers typically require accesses to be aligned on a multiple of the SIMD width as hardware to support misaligned loads and stores is complex [118, 100, 102]. The SSE instruction set provides aligned memory and computational instructions along with load and store instructions that correct misaligned memory accesses. In addition instructions may have memory "hints" applied to them that cause data that will be needed soon to be loaded into the cache early so that by the time it is needed it is already cached. Shuf-

fling memory instructions that dynamically reorganise non-contiguous data such as that stored in an "array of structures" format are also included in SSE although they incur a 25% performance penalty to use over data that is organised in a contiguous "structure of arrays" format [118].

Being motivated primarily by 3D graphics performance SSE contains special instructions such as reciprocal division and square root which are commonly used to calculate surface normals for lighting 3D scenes. These operations are implemented to less than IEEE standard precision in order to be fast although they can be combined with Newton-Raphson iterations to improve accuracy and still be faster than ordinary division or square root instructions [118].

SSE has been implemented in every Intel-compatible processor since the Pentium III in 1996 [102].

#### 2.1.4 Compiler Autovectorisation

Traditional vector computers require programs to be rewritten as a sequence of vector operations on whole arrays at once [14]. This may be impossible in cases where there are data dependencies between elements in the array. SIMD processors are relatively recent and perform the same operation on a small number of contiguous elements contained in a vector register. To use these registers loops within a program need to strip-mined to the SIMD vector length and a separate loop added to operate on remaining scalar elements. Compiler autovectorisation [87] seeks to have these loop transformations applied automatically by the compiler replacing the strip-mined loop with vector instructions that use the SIMD registers within the CPU.

Automatic vectorisation for vector computers is a mature research area and the work is now being applied to modern SIMD processors [87, 21, 41]. The main areas of research are detecting data dependencies and loop analysis, finding loops that are viable targets for transformations that increase parallelism [87]. Most of the theory for automatic vectorisation on vector computers applies to Fortran arrays and so does not take into account pointer aliasing that can be performed in programming languages such as C. SIMD architectures also usually have stricter memory alignment and access requirements and limited, domain-specific mathematical instructions [87].

In GCC vectorisation is applied as part of other loop optimisations to code in GCC's intermediate GIMPLE representation [87]. A number of tests are iteratively applied to loops in this form before a vectorising loop transform is applied. The tests involve checking that a loop has a countable number of iterations, has no loop dependencies and that the operations performed in the loop have corresponding vector instructions on the target architecture. This causes a problem in GCC where the optimisations applied need to be generic and not specific to any par-

ticular platform. If some operations do not have equivalent vector instructions they are left as a sequence of scalar operations. Data dependencies can also be ignored when the vector length is known and the dependency span is greater. Support for non-contiguous or misaligned memory accesses may not be available on the target platform. For misaligned accesses GCC employs loop versioning to test at runtime if the accesses are aligned or not.

#### 2.1.5 CUDA

Driven by the increasing demand for realistic, real-time 3D graphics rendering, GPUs have become highly parallel computing devices with a large number of processing cores, very high instruction throughput and high memory bandwidth. Graphics rendering is SIMD parallel and has a high ratio of arithmetic operations to memory operations so there is less of a requirement for cache and control logic. GPUs consequently have more die area dedicated to data processing and memory latency is hidden by arithmetic operations instead of large caches. CUDA [94] is a GPU architecture, instruction set and programming model for nVidia graphics cards that enables general purpose computing on the GPU (GPGPU). It is distributed as a software environment comprising a compiler, developer tools and a runtime library. The runtime library is callable from Fortran, C and C++ and contains DirectCompute, OpenCL and OpenAAC APIs.

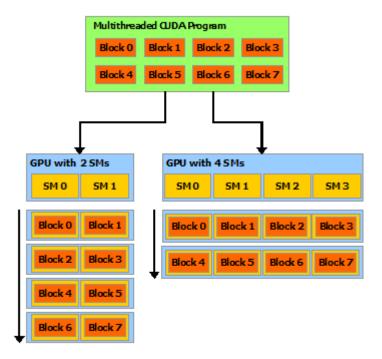

GPU kernel functions are written in "CUDA-C" which is a language similar to C with extensions for synchronisation barriers, thread indices and explicit access to shared cache memory. This provides a familiar programming environment for programmers keeping the learning curve low. A complete maths library is available along with intrinsic GPU functions. Thread indices are organised as a 2 or 3 dimensional grid of 2 or 3 dimensional block of threads. This provides a thread hierarchy allowing both coarse and fine grained parallelism. A block of threads is executed on a single core in a GPU. Each core executes as many thread blocks as will fit in the cache and registers. Because each thread block that is currently being run is resident on a processing core switching between them is fast. Remaining thread blocks are run when other blocks finish and free up resources on a processing core. This allows code written with many blocks to scale well to future GPUs with more cores and more cache or registers per core.

Threads within a thread block can communicate with each other via a shared cache memory that is present on the processing core. Communication in this manner requires that all threads in a block synchronise to ensure that writes by threads are visible by others in the thread block. Communication between blocks on different cores has to be performed via atomic operations in global graphics memory.

GPU code is compiled by the nVidia compiler into generic GPU assembly or a binary object targeting a particular class of GPU. The runtime library provides functions to allocate

memory for function parameters, upload and download data and executable code to the GPU and launch kernels using a particular configuration of thread blocks. Execution is asynchronous with respect to CPU and the library provides an explicit synchronisation function that blocks until the GPU is finished. The library also provides functions to query the "Compute Capability" of a GPU and load either binary images that are compatible or generic GPU assembly which will be just-in-time compiled for the GPU.

CUDA-capable GPUs are implemented as a number of identical multi-threaded "Scalar Multiprocessors". Each thread is pipelined to improve instruction level parallelism although there is no branch prediction or out of order execution in order to keep each SM simple. When a kernel is launched on the GPU, thread blocks are distributed over the SMs until they are full. Any remaining blocks are placed in a queue and scheduled on an SM when others finish. Each SM is capable of running hundreds of software threads concurrently in groups of consecutive software threads called warps. Threads within a warp share the same instruction counter and run similarly to SIMD vector threads except that threads are allowed to follow different code branches. However for best performance it is not advisable to have threads within a warp follow different code paths as the SM has to follow all branches even if some of the threads are suspended. As each warp is multi-tasked nVidia refers to this hybrid multi-threaded SIMD paradigm as SIMT (Single Instruction across Multiple Threads).

#### 2.1.6 OpenCL

As the number of CPU cores increases and GPUs become more general purpose computing devices there is an emerging overlap in technologies and features. OpenCL [9] is a standard for heterogeneous computing resources that targets this overlap. It was created by Khronos - a non-profit industry consortium of hardware and software vendors and academics that creates open standards for parallel computing. nVidia is the chair of the consortium and Apple is in charge of editing the specifications. It took the consortium six months to publish the first version of the OpenCL standard and there are several conforming implementations from companies such as AMD, Intel and nVidia across several operating systems and hardware platforms. The next version of the standard took a further 18 months to publish and is backwards compatible with the first. The consortium manages a developer community and makes the specifications free to obtain. Several books on OpenCL programming have also been published.

OpenCL aims to fully utilise the computational power available in CPUs, GPUs and other hardware accelerators to accelerate parallel computational intense code portably across different platforms. It provides a runtime library to query and set up devices, manage memory and execute code. In OpenCL terminology an N-dimensional compute domain is defined and ker-

nels are run across the domain. The OpenCL platform model consists of one host and many compute devices, each of which has one or more compute units containing many processing elements. An OpenCL application runs on the host and submits work items to the compute devices via an OpenCL context. An OpenCL context groups compute devices and creates and manages work queues and memory.

Kernels are written in a subset of ISO C99 with extensions for intrinsic functions, vector types and a corresponding vector maths library which supports IEEE 754 compliant floating-point error bounds. Being designed to run on GPUs as well as other accelerators thread indexes and memories have a similar hierarchy to that used in CUDA. Kernels can also be compiled to an intermediate representation to be loaded and compiled to machine code by the runtime. For GPUs the intermediate representation is CUDA-compatible GPU assembly.

#### 2.1.7 HMPP

While the high computational power of GPUs makes them attractive for hardware accelerated parallel computing there are many companies with a significant amount of code that do not have the resources required to rewrite their applications from the ground up to use a GPU. Although technologies such as CUDA make it easier to write code targeting GPUs even experienced developers may introduce bugs into an otherwise stable software product and companies cannot risk this.

HMPP [36] aims to simplify the process of converting an existing code base to use hardware accelerators while maintaining application portability. The product documentation compares this to integrating the GPU into an existing application rather than porting the application to use the GPU. It consists of a C and Fortran compiler preprocessor, development tools and a runtime library for a heterogeneous multi-core environment on Unix-like operating systems. In a similar manner to OpenMP, HMPP contains compiler directives that mark functions as candidates for hardware acceleration. These directives are processed by the HMPP preprocessor to automatically convert the existing code to call a GPU version of the function if a compatible GPU accelerator is available. The GPU version of the function is developed using tools from the GPU vendor and the preprocessor automatically handles the transfer of any function arguments onto the GPU. HMPP compiler directives are similar to OpenMP directives in that they are ignored by compilers that don't recognise them. Recompiling code with HMPP directives with the original application compiler produces the original application executable removing any risk that may be inherent in exploring a new technology.

The HMPP programming model transfers arguments onto the GPU, executes the function and downloads the results when the function is complete. More advanced usage of the direc-

tives allows results to remain on the GPU if they are to be used in subsequent GPU functions. Directives also allow a specific accelerator to be chosen for execution and FPGAs will also be targeted by the product. The runtime library is able to detect which accelerators are available on the platform at runtime and run the original function if no accelerators are available. It also handles any exceptions raised by the accelerator hardware and can be used with other multiprocessing technologies such as OpenMP and MPI.

#### 2.2 Parallel MCMC Implementations

We now give a summary of the ways in which Markov chain Monte Carlo algorithms may be parallelised, and discuss the challenges and limitations that result.

#### 2.2.1 Parallel Pseudo-Random Number Generation

Computers are entirely deterministic in that when repeatedly given the same inputs they will generate the same output. This causes problems for algorithms that require a source of randomness, such as Monte Carlo simulations, but which also need to be repeatable. Physical sources of randomness can be connected to a computer, for example, counting the number of ionised particles emitted from a radioactive sample every second using a Geiger counter [126]. However these are often a poor source of randomness as the underlying distribution of samples is often unknown, unbounded, and is not repeatable. A class of algorithms known as Pseudo-Random Number Generators, or PRNGs [71], output a stream of numbers that give the appearance of being distributed randomly while being computed deterministically. PRNGs consist of an initialisation function that initialises the generators' internal state according to a seed value and a generation function that updates the state and outputs a random number. Initialising a PRNG multiple times with the same seed will result in the same stream of numbers being produced which allows simulations based on them to be repeatable exactly and also debugged more easily. Since the state of the PRNG is finite the stream of numbers will begin to repeat at some point. The amount of numbers output before the stream starts to repeat is known as the period of the PRNG. A large period is desirable but often results in a larger state having to be stored. PRNGs are categorised according to the form of their generation functions which may be combined in order to increase the quality of the generated output at the cost of state size and complexity [71].

Linear congruential generators (LCGs) have a generation function of the form

$$x_i = (ax_{i-1} + c) \bmod m \tag{2.1}$$

The state of an LCG consists of solely the previous value generated and so is very small. The parameters a, c and m define the period of the generator and the statistical quality of the stream

of numbers generated. The generation function is short and consists of few operations so should be fast.

Lagged Fibonnaci Generators (LFGs) have a generation function based on a generalisation of the Fibonnaci sequence where the next number in the stream is based on two previous numbers. The general form is

$$x_i = x_{i-j} \oplus x_{i-k}, \quad 0 < j < k$$

(2.2)

The operator  $\oplus$  may be an arithmetic or bitwise operator. Since a generator of this type requires the k previous numbers to be available the state is of size k. The parameters j, k and the operator  $\oplus$  decide the period of the generator. The quality of the output is dependent on the parameters but also on the initialisation of the state which has to be performed with another PRNG.

Tausworthe Generators have a generation function of the form

$$x_i = (a_1 x_{i-1} + a_2 x_{i-2} + \dots + a_n x_{i-n}) \bmod 2$$

(2.3)

where the  $a_0, a_1 \dots a_n$  are the parameters of the generator and define the period and statistical quality of the output stream. The size of the state is n since a combination of the n previous numbers determine the next. The mod 2 at the end of the generation function means that Tausworthe generators produce bit values that are either 0 or 1 hence they are slow, requiring 32 or 64 operations to produce a 32-bit or 64-bit random number respectively.

Linear Shift Feedback Generators (LSFR) are based on a linear shift feedback register which is updated by shifting the bits to the right, inserting a new bit in the most significant position that is the result of a bitwise operation on one or more less significant bits in the register. The operation is commonly XOR giving rise to XORSHIFT PRNGs. The recursion formula can be represented by a characteristic polynomial.

A Weyl PRNG has the simple form

$$x_i = x_{i-1} + c \bmod m \tag{2.4}$$

with c being an odd constant and m being the maximum value to output.

The output of a PRNG is usually a stream of uniformly distributed unsigned integers of the native word size of the computer. The numbers are uniformly distributed over the whole range of the type i.e.  $[0,2^{32}-1]$  on a 32-bit computer. There are several tests which can be performed to assess the statistical quality of the random stream produced by a PRNG. An example of a simple test is to take a large number of samples from the output of a PRNG and calculate the mean. The closer to the middle of the output range the calculated mean is the more

uniformly the output is distributed. There are a large number of more complicated tests that can be performed and most of them are available as part of the DIEHARD [79] and TestU01 [72] batteries of tests. A good PRNG will have a small state, efficient update function and pass all tests related to the statistical quality of the random numbers generated.

When performing a random simulation on a parallel computer extra steps need to be taken to ensure that the streams of numbers output by the PRNGs on each processor are independent of each other. Using the same seed and PRNG on each processor will result in exactly the same stream being reproduced on each processor, essentially replicating the simulation verbatim. It is possible to use a serial PRNG in a parallel context by controlling access to the PRNG using traditional parallel computing techniques such as shared locks and mutexes. With a parallel simulation however this can quickly become the performance bottleneck making it preferable to use a PRNG specifically tailored for use on parallel computers. Methods of converting an existing serial PRNG into a parallel PRNG commonly involve splitting the sequential stream of random numbers into several streams with a much shorter period that can be generated in parallel. In order to do this it needs to be possible to efficiently calculate random numbers at arbitrary positions in the stream, which a lot of PRNGs are incapable of. Even where this can be done there is a non-zero probability that at some point the random number streams will overlap, given that they are all being generated by the same deterministic algorithm. An alternative is to design a parallel PRNG algorithm that can generate multiple independent sequences concurrently. The class of parallel PRNG algorithms, or PPRNGs, is a subclass of the class of PRNGs and so they share the same properties such as state size and period but also have an additional property which is the number of streams that can be generated in parallel.

There are several PPRNGs available for different parallel computing platforms. A PPRNG suited to coarse-grained parallel computing environments, such as those used in Monte Carlo simulations, is presented by C. K. Tan [117]. Their algorithm, PLFG, is based on a 32-bit LFG using parameters suggested by Knuth [65]. The number of independent streams is limited by the period of the generator used to initialise the lag tables, which in this case is a serial Mersenne Twister PRNG with a period of  $2^{19937} - 1$ . The choice of using a PRNG with a large period for initialisation, coupled with the specific lag values used, means the probability of multiple sequences overlapping is minimal. Implementing a parallel PRNG in this way from a serial PRNG is a form of sequence splitting. The authors demonstrate their PLFG algorithm using a 2D Ising Model Monte Carlo simulation where they find the performance, both in statistical quality of the output streams and in random numbers produced per second, is better than a PPRNG from the SPRNG library [80], which combines two LFGs using different operators.

The advantage in performance disappears however in their second example which is solving systems of linear equations using Relaxed Monte Carlo methods.