# Multi - Dimensional Parameter Optimization for RSFQ Circuit Design

R. Koch and W. Benzing

Institut für Elektrotechnische Grundlagen der Informatik, University of Karlsruhe, Hertzstr. 16, 76187 Karlsruhe, Germany

Abstract — Global tolerance parameters give a realistic measure for the feasibility of superconducting circuits, because interactions between the different parameters is taken into account. Algorithms based on the Monte Carlo simulations for calculating and optimizing the global tolerance parameter are presented, which are implemented in the optimization software ABAK. The application of these methods for RSFQ circuit design is discussed and demonstrated for a XOR gate.

## I. INTRODUCTION

With the rising complexity of RSFQ circuits and the application of powerful CAD tools as CADENCE [1], the parameter optimization process becomes more and more important. The goals of careful optimization procedures at the different steps are an improved yield of fabricated circuits and quality factors like the maximum operating frequency and the error rate.

A straight forward method to optimize the margins of an RSFQ circuit comprises of determining the nearest or critical margin  $\Delta_C$  in varying each parameter while all others are kept constant. The critical margin is improved in trying at different nominal sets [2]. Although this method is rather fast, the quality of the result depends on designer intuition. Moreover, the interaction between the different circuit parameters is neglected. Therefore, multi - dimensional parameter optimization methods were adapted for RSFQ circuit design [3,4] to calculate an optimum set of parameters, characterized by a tolerance vector with the maximum available one - dimensional margins  $\Delta_{1C}$ . However, such graphs may be misleading, since all parameters can vary simultaneously around their nominal values. To take this effect into account, a global tolerance parameter  $\Delta_n$  in the sense of a multi - dimensional cube was proposed [5]. A global tolerance parameter of n percent in this sense means, that all parameters are allowed to fluctuate simultaneously about n percent around their nominal values.

In this paper, methods for the calculation and optimization of those global tolerance parameters are presented, which are implemented in the optimization tool ABAK. Optimization strategies for the design process of RSFQ circuits are discussed and a design example is given.

This work was supported in part by the German BMBF under grant number 13 N 6324 2  $\,$

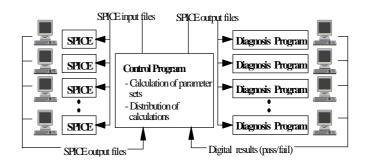

Fig. 1: Functional scheme of the optimization system ABAK

## II. ABAK SOFTWARE

The developed software tool ABAK for margin analysis and parameter optimization and is realized as a distributed application for local UNIX networks. It comprises three components: a control program, which coordinates the calculations, the network analysis program SPICE and a diagnosis program, for testing the function of the investigated circuit by user - defined criteria. The functional scheme of ABAK is sketched in Fig. 1.

The control program calculates a set of parameters dependent on the used algorithm and creates a SPICE input file with these parameter values. The control program chooses one of the available computers in the network to start a SPICE simulation with this file. This procedure is repeated until all computers in the network are busy. The results of the simulations are saved in SPICE output files, which are tested simultaneously with the diagnosis program. When the tests are finished, new parameter sets are calculated by the control program and new SPICE simulations are started. This procedure is repeated, until the goal of the used algorithm (e.g. the estimation of an optimal set of parameters) is reached.

The most difficult problem in this procedure is to find out whether a calculated parameter set is valid or not. Therefore the large analog SPICE output must be reduced into a simple digital decision (pass/fail) in dependence of a specific criterion, which must be defined for every investigated circuit. To achieve maximum flexibility, an object orientated method with the C++ programming language was chosen. In the first step the analog output signals are transformed into a series of discrete events. An event is defined for current or voltage type signals as the rising or

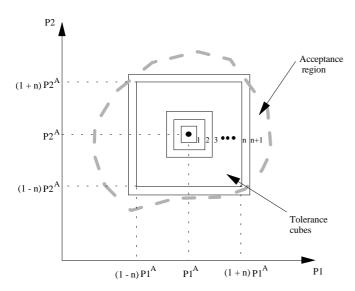

Fig. 2: Onion method for calculating the global tolerance parameter for a given operating point

falling edge; for Josephson junctions phase type events are defined as  $2\pi$  leaps. Those events are described completely by the position on the reference vector (e.g. the timebase) and the switching direction (up/down). ABAK offers a number of pre - defined functions to analyze the behavior of a circuit with those events.

Several one - and multi - dimensional algorithms for margin analysis and parameter optimization are implemented in ABAK. For the calculation and optimization of global tolerance parameters special algorithms have to be developed, which are presented in the following.

To calculate the global tolerance parameter for a given operating point, the algorithm sketched in Fig. 2 is used. In the first step, a multi - dimensional cube according to a global tolerance parameter of one percent is placed around the operating point. A given number of parameter sets is calculated by the Monte Carlo method within this cube and tested with the procedure described before. If all parameter sets were found to be valid, a second multi - dimensional cube according to a global margin of two percent is placed around the operating point. In the intermediate region between the two cubes, a number of parameter sets to be tested is estimated in such way, that the point density compared to the first step is kept constant. If all parameter sets passed the test, in the third step a multi - dimensional cube according to a global tolerance parameter of three percent is placed around the operating point and the difference region between the two and three percent cubes is investigated. This procedure is continued, until a parameter set fails the test. If this happens at the (n + 1) th step, the global tolerance parameter is n percent. Since the partitioning of the acceptance region reminds of onion peels, this algorithm was called "onion method".

For multi - dimensional optimizations with more than five parameters the centers of gravity method (CGM) was found to be most advantageous [4]. In this algorithm, a number of parameter sets are calculated by the Monte Carlo method and tested within a multi - dimensional cube around the operating point. In the next step the averages of the passed and failed parameter sets are calculated, leading to the "centers of gravity". The operating point and the cube are moved by the difference between the nominal vectors of the two centers multiplied with the yield (number of passed parameter sets/number of calculations). This procedure is continued until a cube is found, which contains only valid parameter sets. The algorithm fails, if all components of the difference vector between two centers become negative. A detailed description of that method is given in [6].

This algorithm was extended for the optimization of the global tolerance parameter. At the start, a multi dimensional cube according to a global tolerance parameter of one percent is placed around the operating point and the search with the CGM is started. During the search, the size of the cube is recalculated for every iteration step so that the global tolerance parameter is kept constant. If a valid tolerance cube is found, the size of the cube is enlarged according to a global tolerance parameter of two percent and the search is restarted. This procedure is continued until the CGM fails. If this happens at the n+1 step, the maximum available global tolerance parameter is n percent. The calculation time can be decreased, if all calculated parameter sets are saved and taken into account for further iteration steps. Since the tolerance cube is pushed to its maximum size, this algorithm was called "balloon method".

# III. OPTIMIZATION STRATEGIES

The design process starts with the parameter optimization of the ideal circuit without parasitics in applying the balloon method, where each parameter can assume arbitrary values. The result may be summarized by the multi - dimensional margin  $\Delta_{n1}$ . The layout, designed with these parameters, often reveals that owing to design rule specifications additional circuit elements (parasitics) must be taken into account. Also several parameters can have only a limited set of feasible, often discrete values being different from the calculated first set of nominal parameters. The optimization process is restarted with all additional parameters where some are kept constant to reduce the computation time yielding a second multi - dimensional margin  $\Delta_{n2}$ . Based on the second set of nominal parameters the "onion method" is used to calculate  $\Delta_{n3}$  where all parameters including parasitics are assumed to be variable. The margin parameter  $\Delta_{n3}$  is a measure for the expected yield of the designed circuit. The comparison between the calculated margins  $\Delta_{n1}$ ,  $\Delta_{n2}$  and  $\Delta_{n3}$  gives information for improvements at the different steps of the design process.

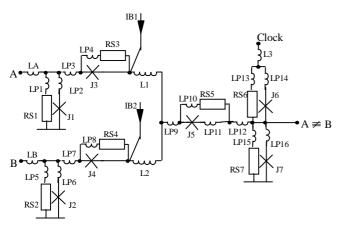

Fig. 3: Equivalent circuit of the extracted XOR gate

#### DESIGN EXAMPLE

Several RSFQ circuits were designed with the procedure described above. The results for the optimization processes for a design of a XOR gate neglecting thermal noise are discussed in the following.

In the first step the ideal circuit as given in [7] was investigated. It consists of 21 parameters: seven Josephson junctions with shunt resistors, five inductances and two bias currents. The result of the multi - dimensional optimization with the balloon method was a global tolerance parameter  $\Delta_{\rm nl}=34$  %. The most critical one - dimensional margin for the so found nominal parameter set was estimated to be  $\Delta_{\rm lC}=-37$  %. The next step was the fabrication of a layout for a Nb technology with four superconducting layers with SiO<sub>2</sub>-insulators, Pd-resistors and Nb-Al<sub>2</sub>O<sub>3</sub>-Nb Josephson junctions having a current density of  $j_{max}=1~kA\ /~cm^2~[8].$

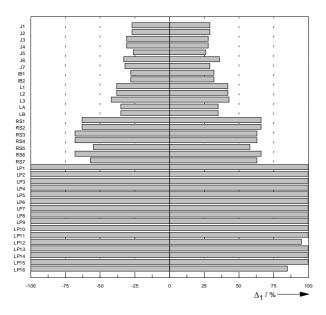

Fig. 4: One - dimensional margins  $\Delta_{l}$  of the extraxted XOR gate shown in Fig. 3

The extraction of the layout leads to a second circuit as shown in Fig. 3, which comprises compared to the ideal circuit 16 additional parasitic inductances. The optimization process was restarted with all Josephson junctions and shunt resistors, the bias currents and the storage inductances. The global tolerance parameter  $\Delta_{n2}$  was optimized to 25 %. In the last step the global tolerance parameter  $\Delta_{n3}$  was calculated to be 25 % with the onion method, where 937 SPICE simulations were needed. If the one - dimensional margins must be known too, additional 518 SPICE simulations are required for an accuracy of 1 %. This yields to the most critical margin  $\Delta_{1C} = \pm 26$  %. Since the global tolerance parameters  $\Delta_{n2}$  and  $\Delta_{n3}$  are equal, no further improvement of the layout seems to be possible.

## V. CONCLUSION

A software tool to optimize the global and the one dimensional tolerances for a large number of parameters has been developed with appropriate algorithms. The global margin  $\Delta_n$  is an indication of the probability to operate a given circuit if all parameters may vary simultaneously. The critical margin  $\Delta_{1C}$  is often on the optimistic, unrealistic side since only a single parameter is allowed to deviate from the nominal set. The deviation between  $\Delta_{1C}$  and  $\Delta_n$  depends on the type of the circuit.

#### ACKNOWLEDGMENT

The authors want to thank G. de Meester for writing part of the ABAK program and numerical evaluations.

# REFERENCES

- V. Adler, C.H. Cheah, K. Gaj, D.K. Brook and E.G. Friedman, "A Cadence - Based Environment for Single Flux Quantum Circuits", Proceedings ASC96

- [2] C.H. Hamilton, K.C. Gilbert, "Margins and Yield in Single Flux Quantum Logic", *IEEE Trans. on Appl. Supercon.*, Vol. 1, pp. 157-163, December 1991

- [3] Q.P. Herr and M.J. Feldman, "Multiparameter Optimization of RSFQ Circuits Using the Method of Inscribed Hyperspheres", *IEEE Trans. on Appl. Supercon.*, Vol. 5, pp. 3337-3340, June 1995

- [4] T. Harnisch, J. Kunert, H. Töpfer and F.H. Uhlmann, "Design centering methods for yield optimization of cryoelectronic circuits", *Proceedings* ASC96

- [5] R Koch, T. Scherer, M. Winter and W. Jutzi, "A 4 Bit YBCO Bicrystal Josephson Junction Flux Shuttle Shift Register", *Proceedings ASC96*

- [6] R.S. Soin, R. Spence, "Statistical exploration to Design Centering", IEEE Proceedings, Vol. 127, Pt. G, pp. 260-269, December 1980

- [7] K.K. Likharev and V.K. Semenov, "RSFQ Logic/memory family: A New Josephson-Junction Technology for Sub-Terahertz-Clock Frequency Digital Systems", *IEEE Trans. on Appl. Supercon.*, Vol. 1, pp. 3-28, March 1991

- [8] R. Dolata, "Laser-Refexionsmessungen zur Optimierung techno- logischer Prozesse bei der Herstellung integrierter Supraleiter- schaltungen", Dissertation Universität Karlsruhe 1994, VDI Fortschrittsberichte, Reihe 8, Nr. 439, VDI-Verlag